Preview text:

lOMoAR cPSD| 59994889

Bài 08: Kiến trúc x86-32bit Phạm Tuấn Sơn ptson@fit.hcmus.edu.vn lOMoAR cPSD| 59994889 Lị ử ể ử ch s phát tri n vi x lý Intel • Intel 4004 (1971)

– Vi x ử lý đầ u tiên c ủ a Intel – 4- bit • Intel 8080 (1972) – Thanh ghi 8-bit

– Đườ ng truy ề n d ữ li ệ u 8-bit

– Đườ ng truy ề n đị a ch ỉ 16-bit (có th ể truy xu ấ t b ộ nh ớ RAM 64 KB)

– Đượ c s ử d ụ ng trên máy tính cá nhân đầ u tiên - Altair • Intel 8086/8088 (1978) – Thanh ghi 16-bit

– Đườ ng truy ề n d ữ li ệ u 16-bit (8088: 8-bit)

– Đườ ng truy ề n đị a ch ỉ 20-bit

– Đượ c dùng trên máy tính cá nhân IBM PC đầ u tiên • Intel 80286 (1982)

– Có th ể truy xu ấ t b ộ nh ớ 16 MB

– Đườ ng truy ề n đị a ch ỉ 24-bit 2 lOMoAR cPSD| 59994889 Lị ử ể ử ch s

phát tri n vi x lý Intel (tt) • ế Ki n trúc x86-32bit (IA-32) – Intel 80386/ i386 (1985) • Thanh ghi 32 bit

• Đườ ng truy ề n đị a ch ỉ 32-bit – Intel 80486/ i486 (1989)

• K ỹ thu ậ t đườ ng ố ng (pipelining) – Pentium (1993)

• Đườ ng truy ề n d ữ li ệ u 64-bit

• Siêu vô h ướ ng (2 đườ ng ố ng song song)

– Pentium Pro (1995), II (1997), III (1999), IV (200 0) , M (2003). 3 lOMoAR cPSD| 59994889 Lị ử ể ử ch s

phát tri n vi x lý Intel (tt) • ế Ki n trúc x86-64bit

– Athlon64 c ủ a AMD (2003)

• B ộ vi x ử lý x86-64bit đầ u tiên – Pentium 4 Prescott (2004)

– Core 2 (2006), Core i3, i5, i7, Atom (2008) – Intel Sandy Bridge (2010) • ế Ki n trúc IA-64 – Itanium (2001) 4 lOMoAR cPSD| 59994889 Kiến trúc x86-32bit • ế độ ạ độ Ch ho t ng • ổ ứ ộ ớ T ch c b nh • ậ T p thanh ghi • ậ ệ T p l nh • ă ế Ng n x p • ủ ụ Th t c 5 lOMoAR cPSD| 59994889 Chế độ hoạt động • Ch ế độ th ự c – 16 bit (8086)

– Truy xu ấ t 1 MB b ộ nh ớ chính – MS-DOS • Ch ế độ b ả o v ệ – 32 bit

– Truy xu ấ t 4 GB b ộ nh ớ chính – Windows, Linux • Ch ế độ 8086 ả o •

Ch ế độ th ự c d ướ i s ự qu ả n lý c ủ a ch ế độ b ả o v ệ •

Cho phép ho ạ t độ ng đồ ng th ờ i ở 2 ch ế độ • Ch ế độ qu ả n lý h ệ th ố ng

– Qu ả n lý ngu ồ n cung c ấ p

– Ch ẩ n l ỗ i và b ả o m ậ t h ệ th ố ng 6 lOMoAR cPSD| 59994889 7 lOMoAR cPSD| 59994889

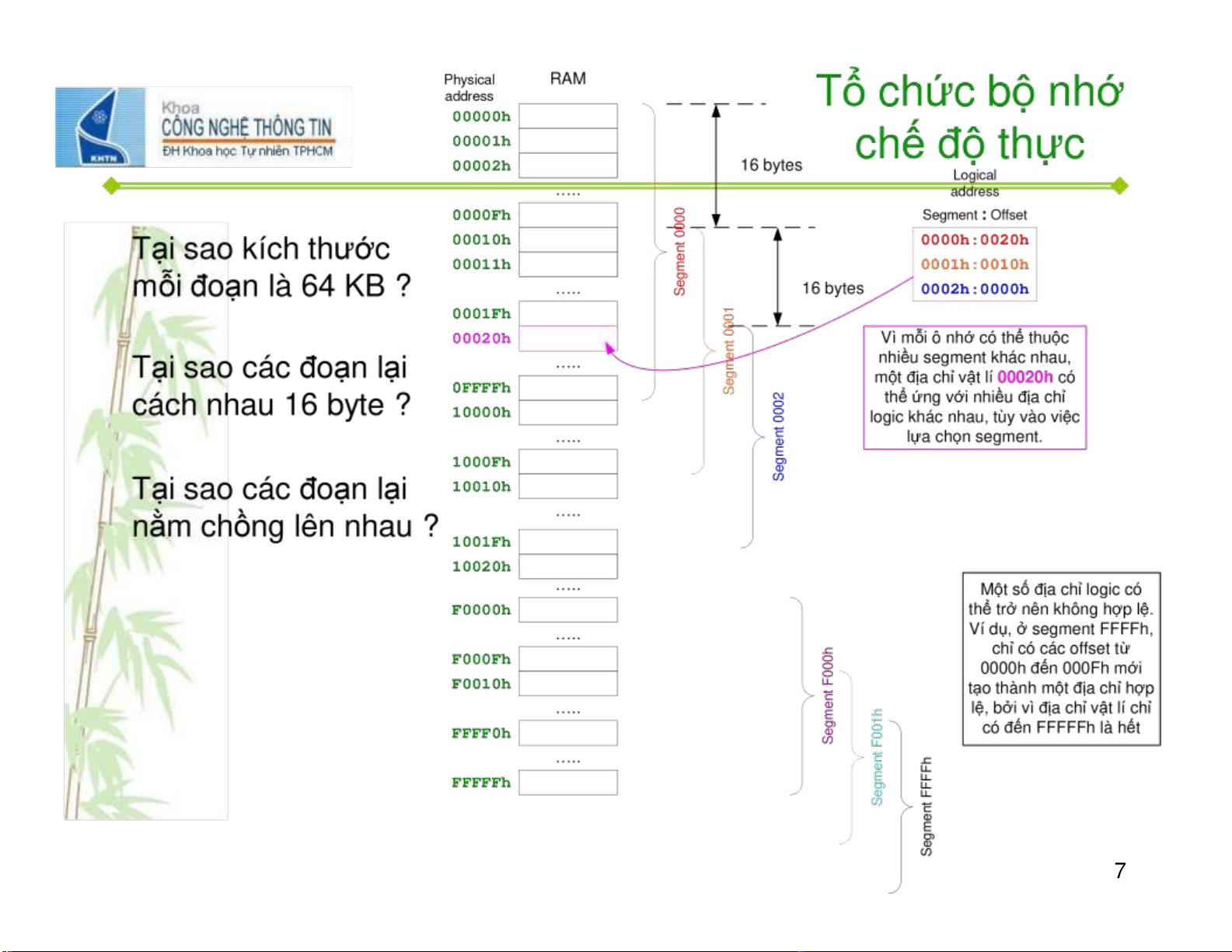

Chuyển đổi địa chỉ ở chế độ thực

• Địa chỉ logic địa chỉ vật lý

– Phy_address = segment * 10h + offset

– Vd: địa chỉ logic 1234h:0005h sẽ ứng với địa chỉ vật lí

1234 h * 10h + 0005h = 12340h + 0005h = 12345h

• Địa chỉ vật lý địa chỉ logic

– Do các đoạn gối đầu nhau nên mỗi ô nhớ có thể thuộc

một vài đoạn khác nhau. Vì vậy, một địa chỉ vật lý có

thể ứng với nhiều địa chỉ logic khác nhau.

– Vd: địa chỉ vật lý 12345h có thể ứng với các địa chỉ logic sau: 1234h:0005h, 1230h:0045 h 1200h:0345h, 1000h:2345 h 8 lOMoAR cPSD| 59994889 1232h:0025h, …

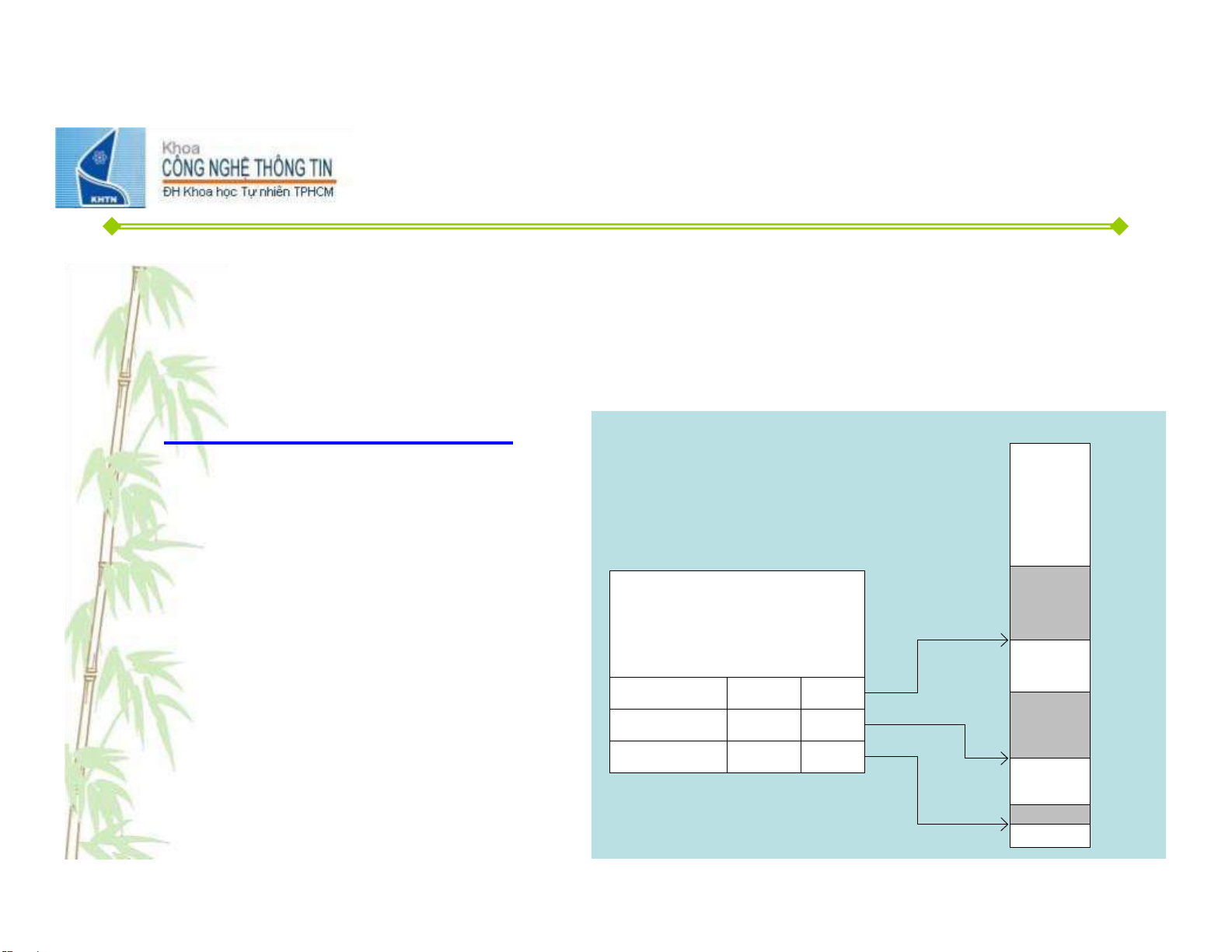

Tổ chức bộ nhớ chế độ bảo vệ

• Bộ nhớ cũng được chia thành các đoạn. Tuy nhiên, kích

thước các đoạn không được định sẵn như chế độ thực.

• Do đó, để định vị một đoạn nào đó thì phải sử dụng một bảng mô tả các đoạn. RAM

• Để truy xuất vào một ô nhớ trong bộ nhớ chính thì cũng phả Local Descriptor Table i thực hiện

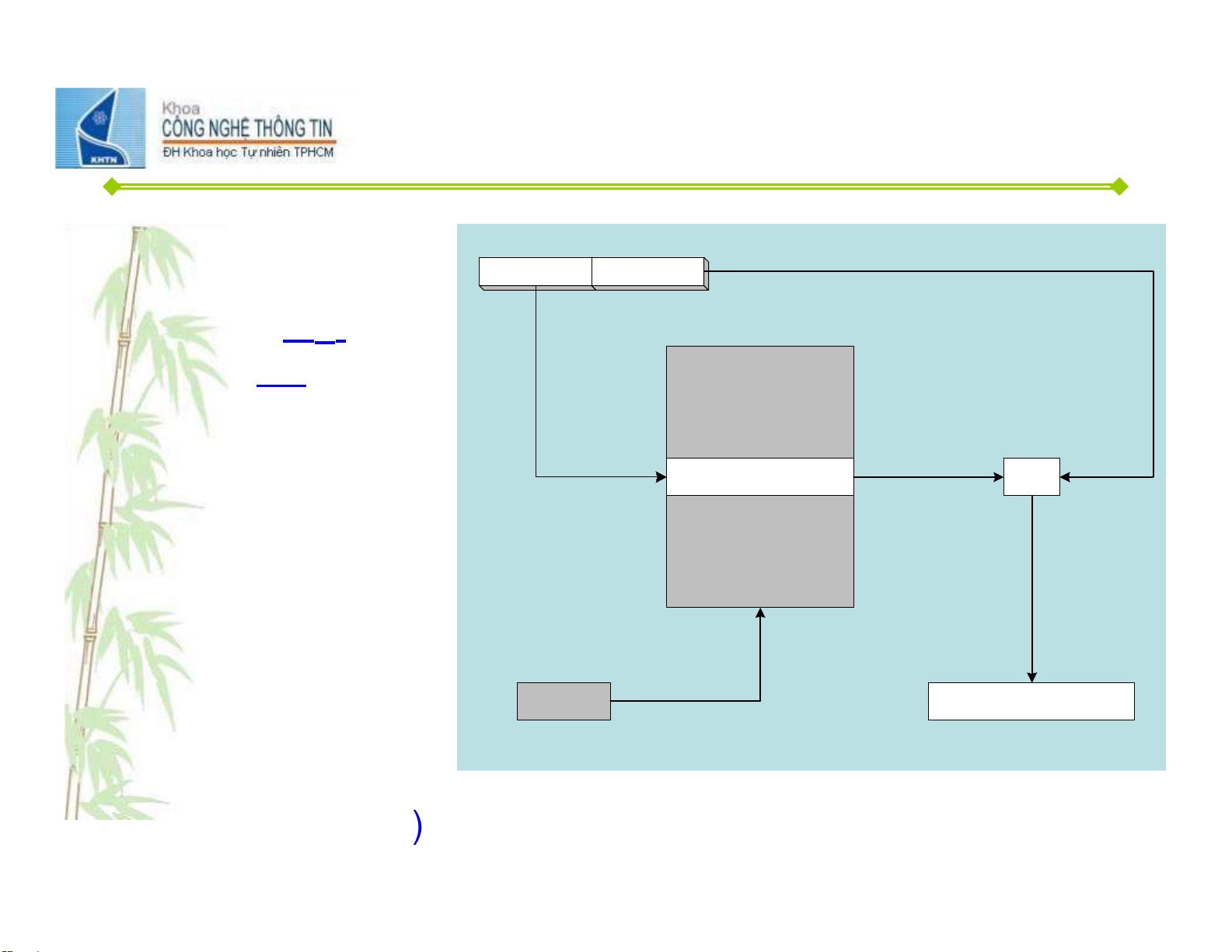

chuyển đổi từ địa chỉ logic (segment, offset) 26000 base limit access thành địa chỉ vật lý 00026000 0010 00008000 000 A 00003000 0002 8000 3000 9 lOMoAR cPSD| 59994889 Chuyể đổ đị ỉ ở ế độ ả ệ n i a ch ch b o v • Th ự c hi ệ n quá Logical address trình chuy Selector Offset ể n đổ i đị a ch ỉ m ộ t b ướ c Descriptor table ho ặ c hai b ướ c để chuy ể n đổ i t ừ đị a ch ỉ logic Segment Descriptor + segment, ( offset) thành đị a ch ỉ v ậ t lý

• B ướ c 1, k ế t h ợ p GDTR/LDTR segment và Linear address offset thành ( contains base address of đị a descriptor table) ch ỉ tuy ế n tính li ( ne ) ar address 10 lOMoAR cPSD| 59994889 Chuyể đổ đị ỉ ở ế độ ả ệ n i a ch ch b o v (tt)

• B ướ c 2, chuy ể n đị a ch ỉ tuy ế n tính thành đị a ch ỉ v ậ t lý ( physical address ) Linear Address 10 10 12 Directory Table Offset Page Frame Page Directory Page Table Physical Address Page-Table Entry Directory Entry CR3 32 11 lOMoAR cPSD| 59994889

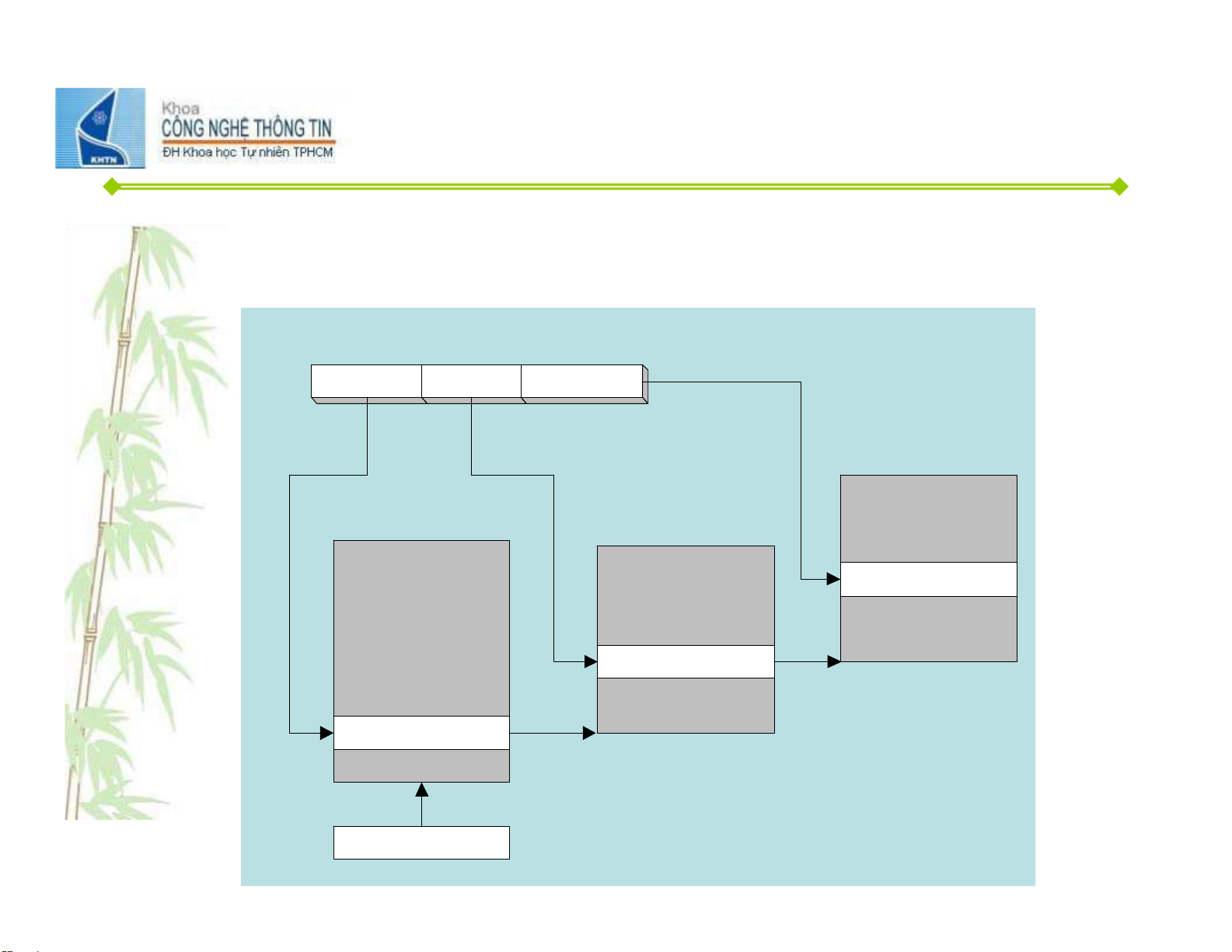

Chương trình chạy trên hệ thống

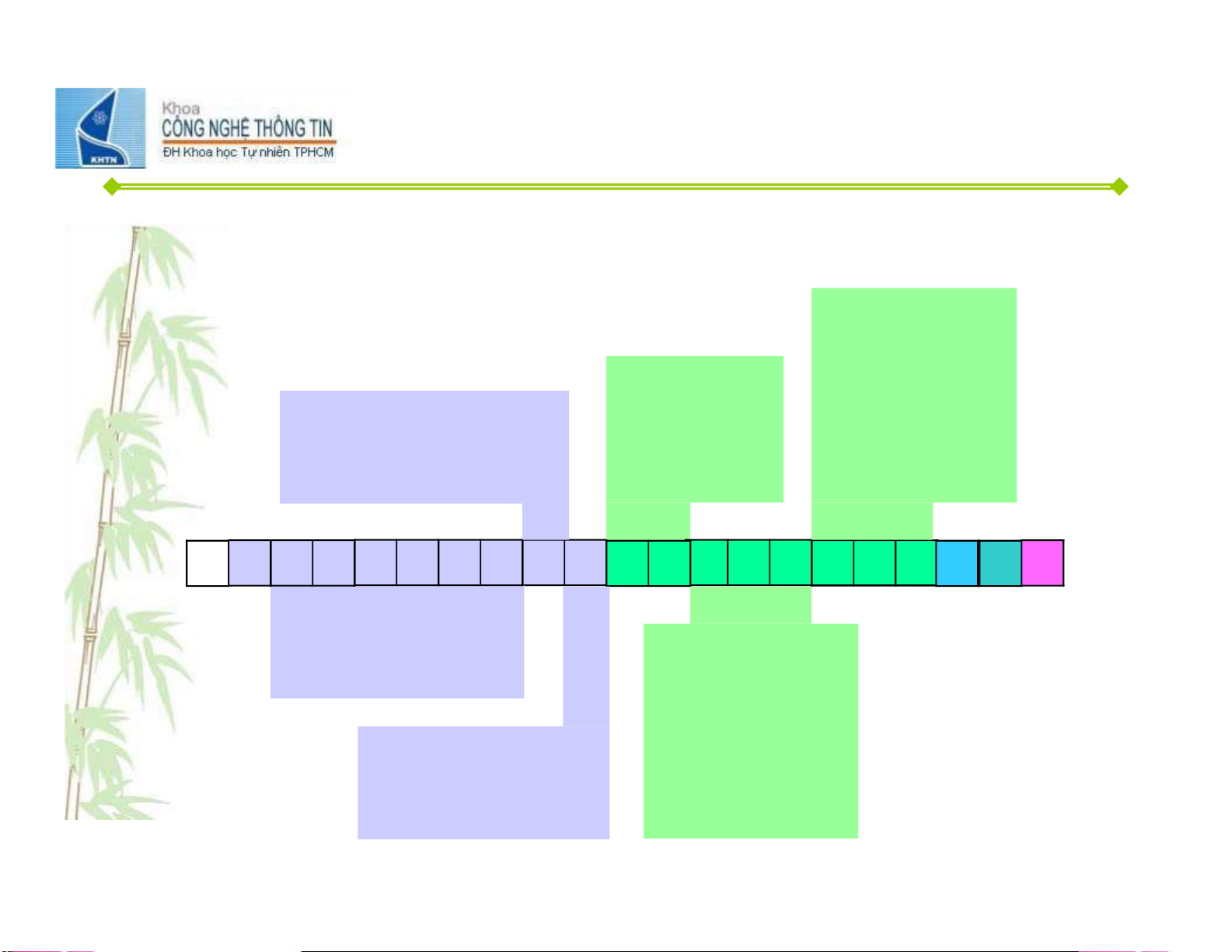

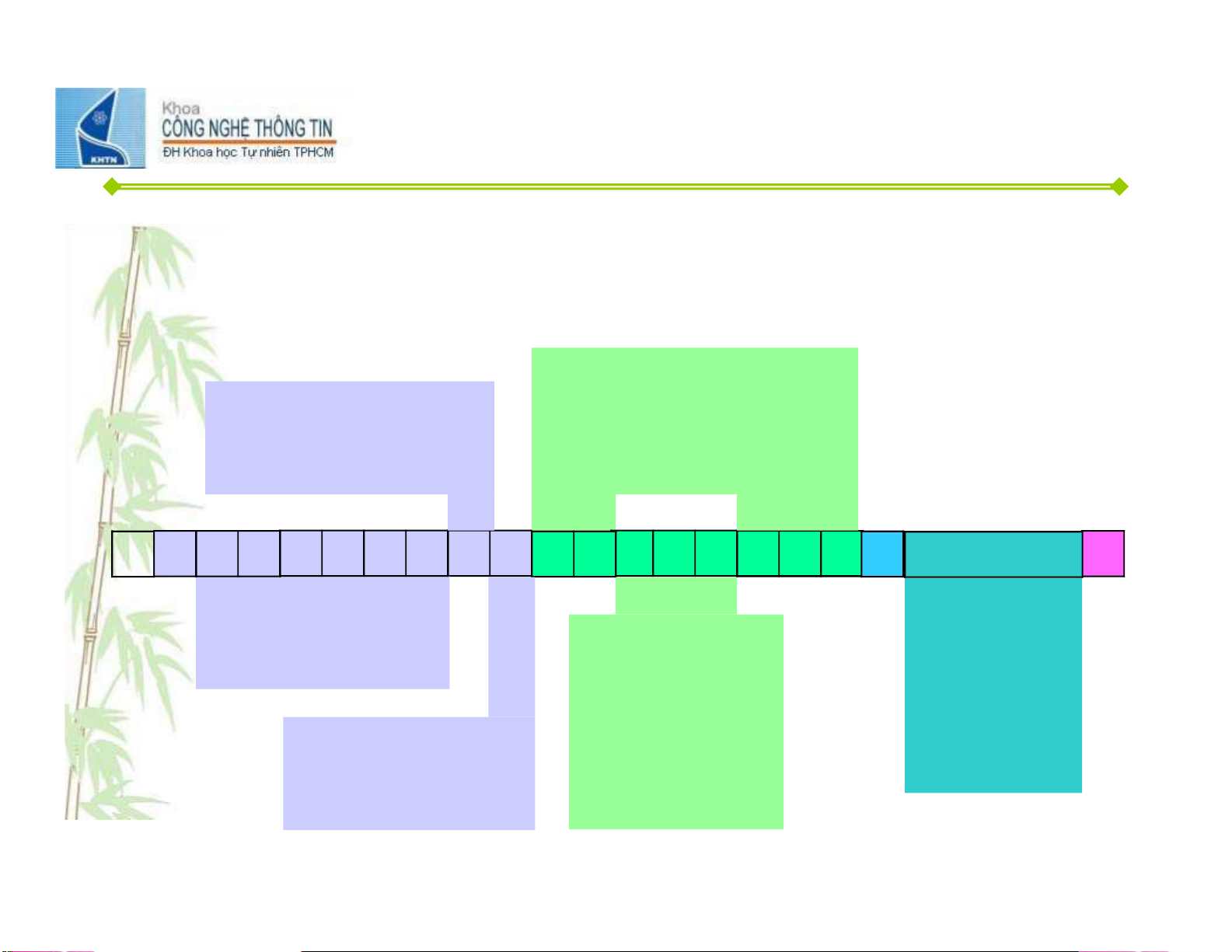

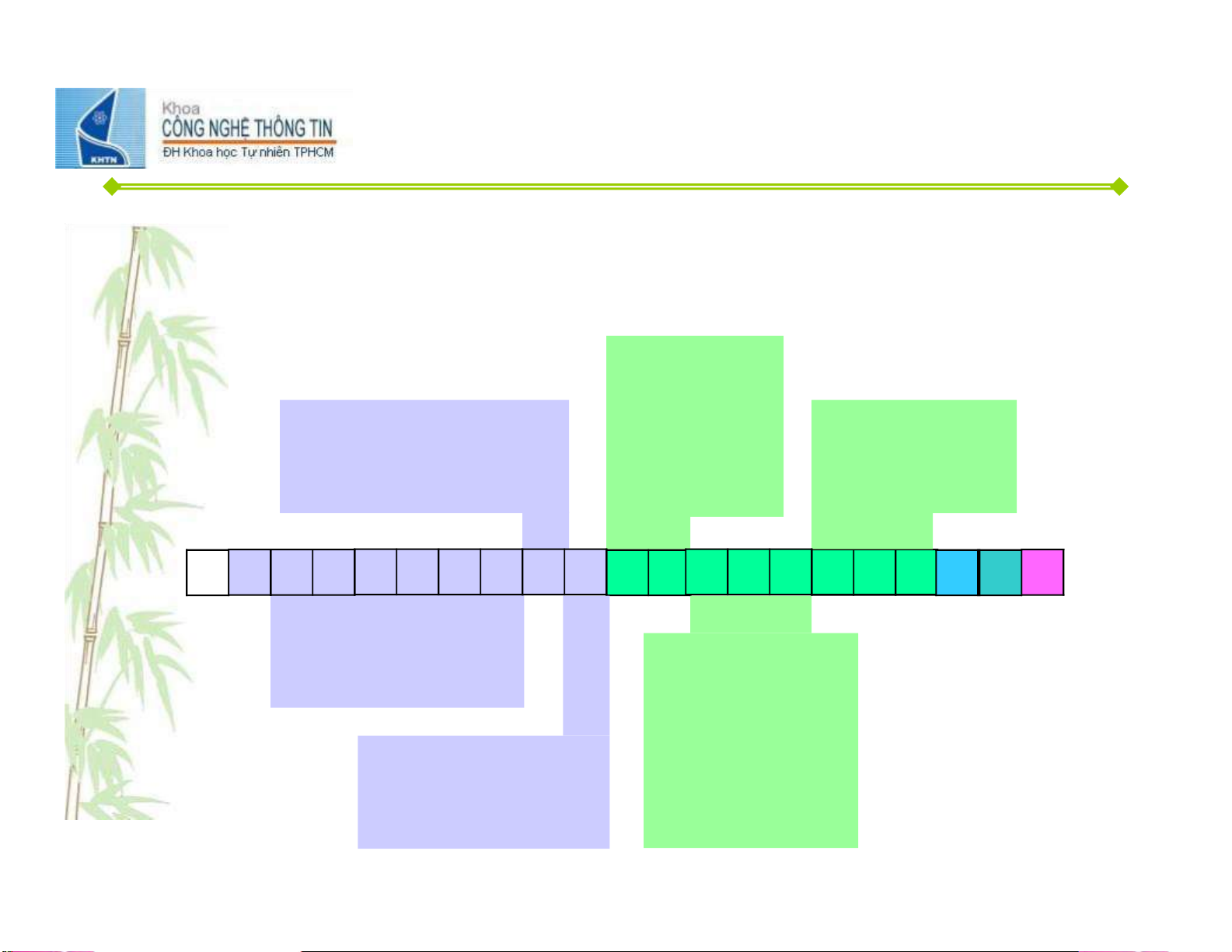

• Chương trình chạy trên hệ thống thông thường chiếm 3 đoạn bộ nhớ

– Một đoạn dành cho mã lệnh (code segment)

– Một đoạn dành cho dữ liệu (data segment)

– Một đoạn ngăn xếp (stack segment) dành để lưu các giá trị trung

gian hoặc các địa chỉ trở về dùng khi gọi hàm

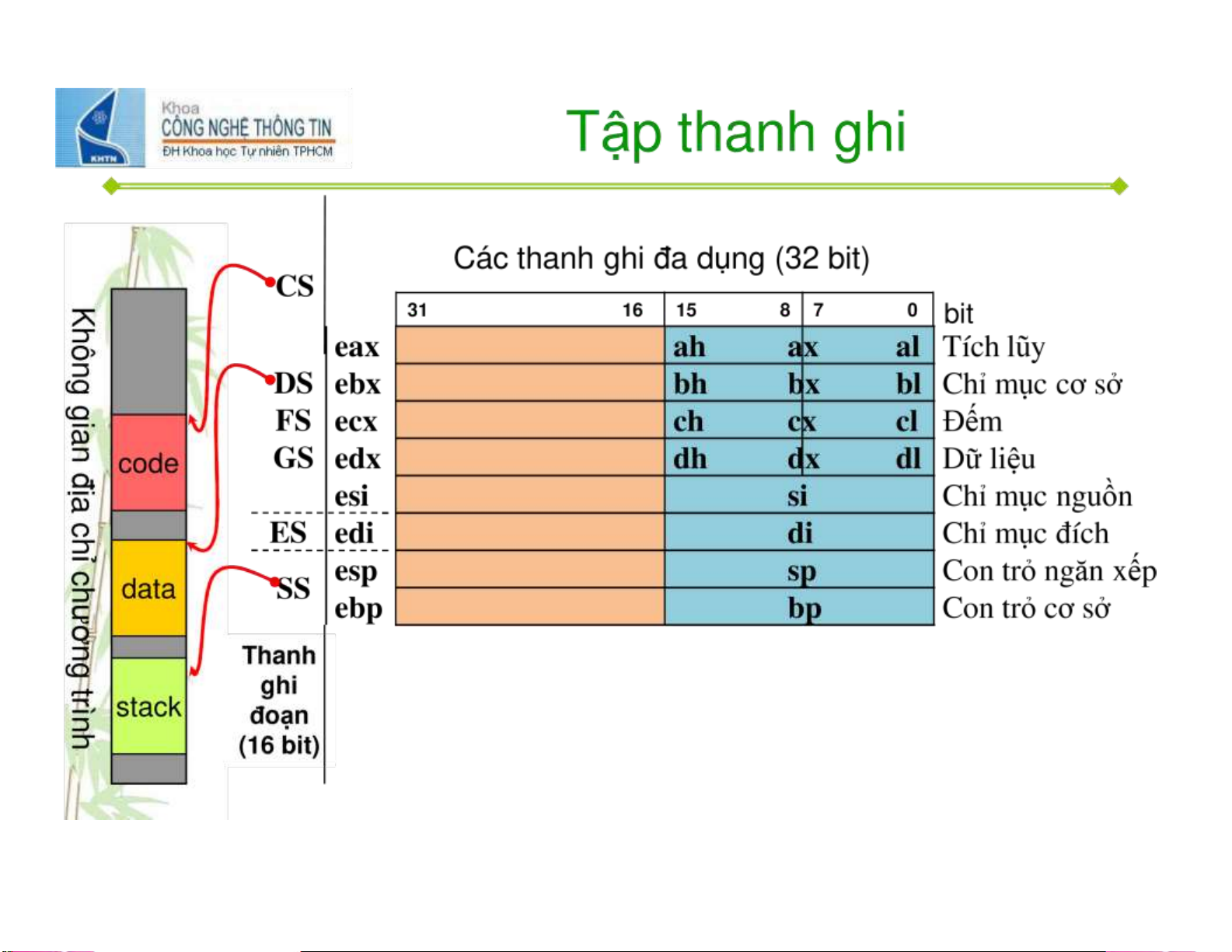

• Trên hệ thống x86, cần có các thanh ghi chứa địa chỉ

đoạn và địa chỉ ô để truy xuất bộ nhớ 12 lOMoAR cPSD| 59994889 13 lOMoAR cPSD| 59994889 Một số thanh ghi khác

• Thanh ghi chứa địa chỉ lệnh (EIP – 32 bit), kết hợp thanh

ghi đoạn CS – 16 bit (CS:EIP )

• Thanh ghi cờ (EFLAGS – 32 bit ) 32 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 ……. VM RF NT IO IO OF DF IF TF SF ZF AF PF CF PL PL

– Carry: cờ tràn không dấu

– Overflow: cờ tràn có dấu – Sign: cờ dấu – Zero: cờ zero

– Auxiliary Carry: cờ nhớ từ bit 3 vào bit 4 – Parity: cờ chẵn lẻ – …

Giá trị của từng cờ được thiết lập sau mỗi lệnh được thực thi 14 lOMoAR cPSD| 59994889

• Một số thanh ghi khác: IDTR (16bit), GDTR (48bit), LDTR (48bit), TR (16bit), ... 15 lOMoAR cPSD| 59994889 16 lOMoAR cPSD| 59994889 ADD CL, AL

• Lệnh này cộng dồn giá trị trong thanh ghi AL vào

thanh ghi CL: CL = CL + AL Giá trị 001 (kết hợp với Giá trị 11 trường d=0) Giá trị

0 cho biết cho biết cho biết toán cộng dồn trường

trường R/M hạng đích là REG vào trường R/M là thanh ghi thanh ghi CL d Kiểu R/M … … 0 0 0 0 0 0 0 0 1 1 0 0 0 0 0 1 … … … Mã thao tác của REG lệnh ADD là s Giá trị 000 (kết 000000 hợp với trường d=0) cho biết Giá trị 0 cho biết toán hạng lệnh

thực hiện nguồn là thanh trên 2 giá trị 8-bit ghi AL 17 lOMoAR cPSD| 59994889 ADD ECX, EAX

• Lệnh này cộng dồn giá trị trong thanh ghi EAX vào thanh ghi ECX trên 2 giá trị 32-bit Giá trị 001 (kết hợp với Giá trị 11 trường d=0) cho

Giá trị 0 cho biết cộng

biết cho biết toán trường R/M dồn trường

hạng đích là là thanh ghi REG vào trường R/M thanh ghi ECX d Kiểu R/M … … 0 0 0 0 0 0 1 1 0 0 0 0 0 1 … … … 0 1 REG Mã thao tác của Giá trị 000 (kết lệnh ADD là s hợp với trường 000000 d=0) cho biết toán hạng Giá trị 1 cho biết nguồn là thanh lệnh thực hiện ghi EAX 18 lOMoAR cPSD| 59994889 ADD EDX, [2000]

• Lệnh này cộng dồn giá trị từ nhớ 4 byte có địa chỉ

bắt đầu là DS:2000 vào thanh ghi EDX

Giá trị 00 kết hợp với

Giá trị 1 cho biết trường R/M=101 cho cộng dồn

trường biết định vị bộ nhớ theo

R/M vào trường REG độ dời d Kiểu R/M

… … 0 0 0 0 0 0 1 1 0 0 0 1 1 1 0 1 … … …

Mã thao tác của REG Sử dụng 4 lệnh ADD là s Giá trị 011 (kết byte của

000000 hợp với trường trường độ d=1) cho biết dời biểu Giá trị 1 cho

biết toán hạng đích diễn giá trị lệnh thực hiện là thanh ghi 2000 trên 2 giá trị 32-bit EDX 19 lOMoAR cPSD| 59994889 ADD EDI, [EBX]

• Lệnh này cộng dồn giá trị từ nhớ 4 byte có địa chỉ

bắt đầu là DS:EBX vào thanh ghi EDI

Giá trị 1 cho biết cộng

cho biết không dùng Giá trị 011 dồn trường

cho trường độ biết định vị bộ R/M vào trường REG dời nhớ [EBX] d Kiểu R/M … … 0 0 0 0 0 0 1 1 0 0 1 1 1 0 1 1 … … … Mã thao tác của REG lệnh ADD là s Giá trị 111 (kết 000000 hợp với trường d=1) cho biết Giá trị 1 cho biết toán hạng đích lệnh thực hiện là thanh ghi trên 2 giá trị 32- EDI bit Giá trị 00 20