Preview text:

MỤC LỤC

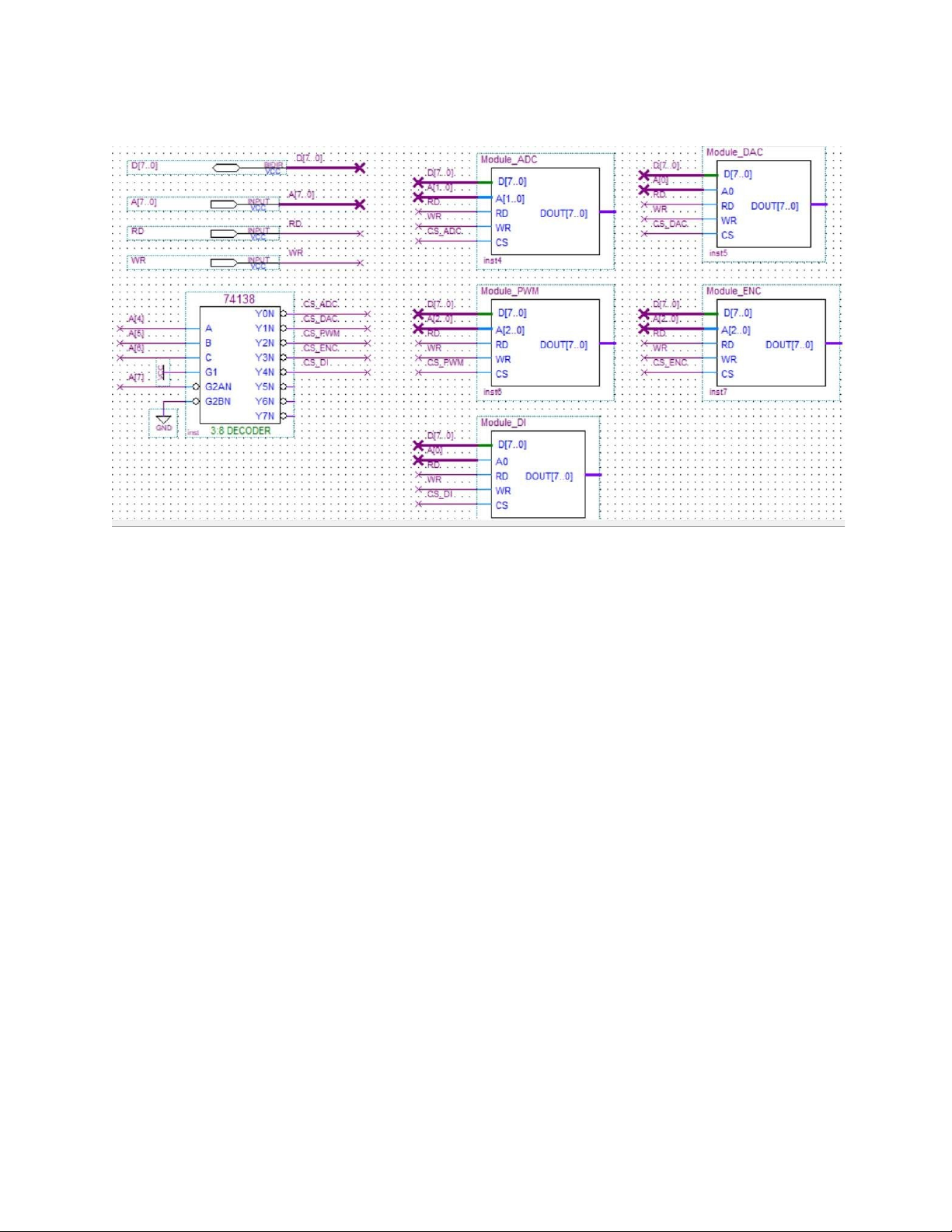

Bài 4: Vẽ lại mạch giải mã ở Slide15 trên Quartus/Block Diagram 9

Bài 5: Vẽ lại mạch giải mã ở Slide19 trên Quartus/Block Diagram 10

2

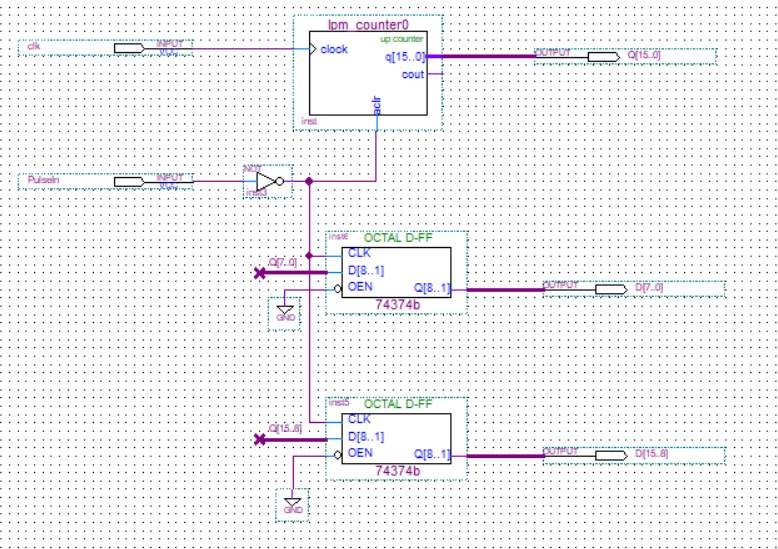

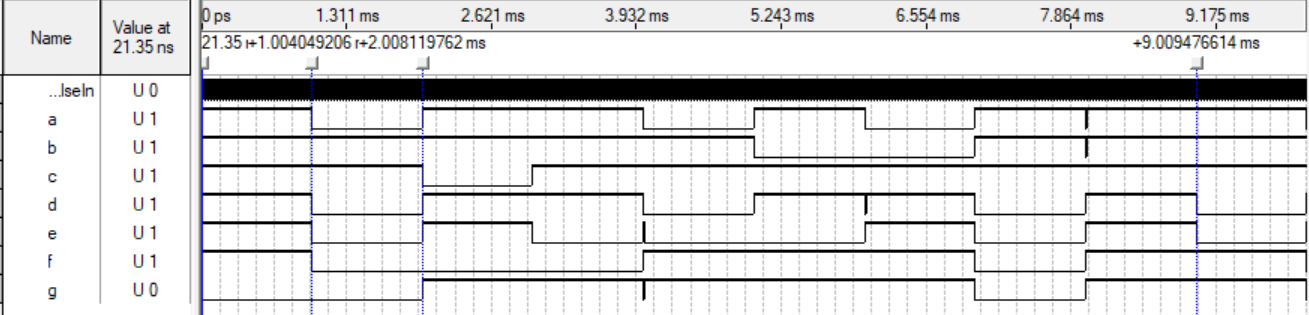

Bài 1: Đo độ rộng xung

- Đầu vào xung PulseIn, clk (us).

- Đầu ra D[15:0] chỉ độ rộng xung PulseIn (đơn vị: us).

- Sử dụng khối lpm_counter trong Megafunctions/Arithmetic

- Chốt được dữ liệu ngõ ra khi PulseIn xuống 0, bắt đầu đo khi PulseIn lên 1

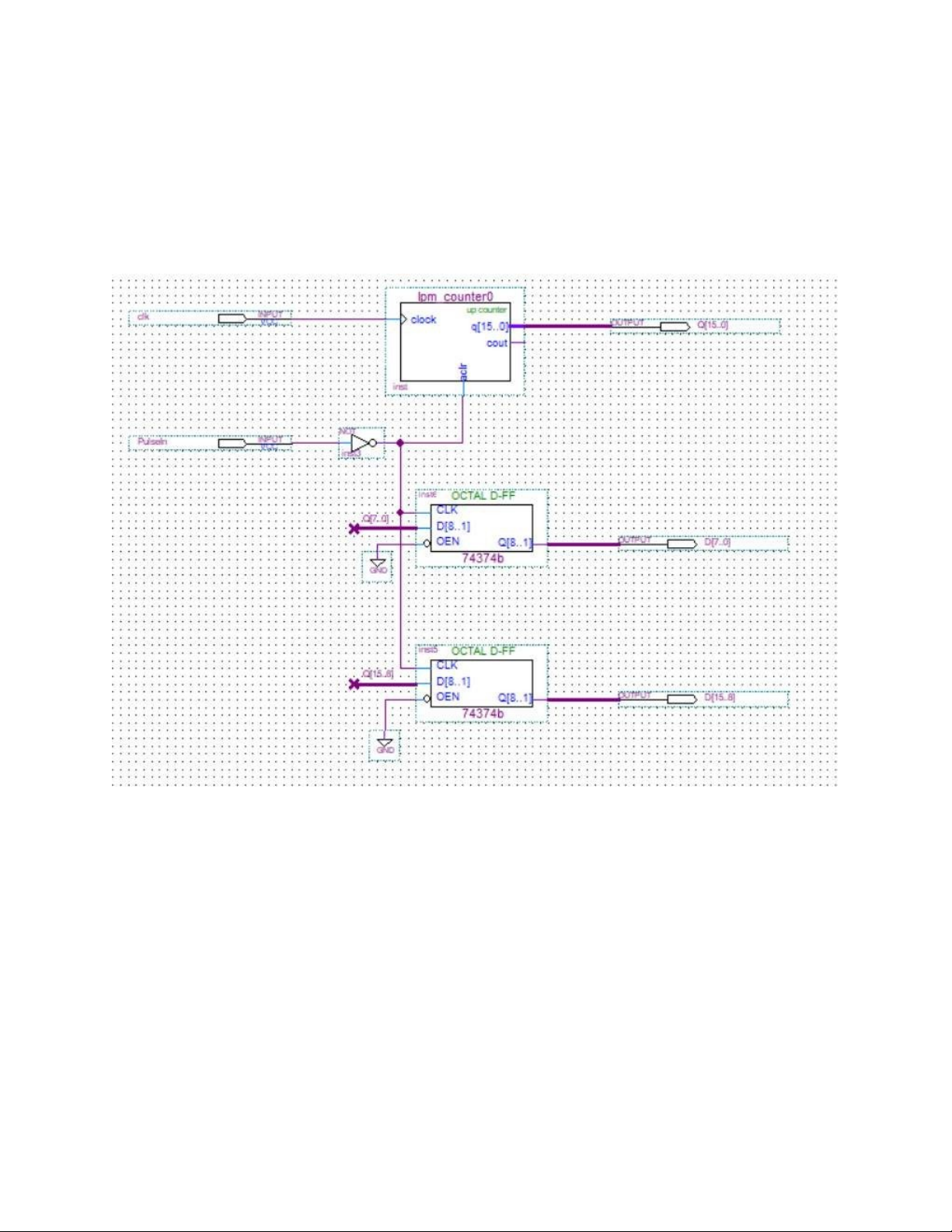

Hình 1: Mạch mô phỏng đo độ rộng xung

Nguyên lý hoạt động:

- Dùng 1 bộ đếm lpm_counter để đếm 16 bit (Q[15:0]), xung clock là xung CLK 1us, xung PulseIn dùng để reset bộ đếm, PulseIn sẽ đi qua cổng NOT để cung cấp tín hiệu cho

chân aclr của khối lpm_counter.

- Khi PulseIn lên 1 thì lpm_counter thực hiện đếm lên, khi xung CLK có cạnh lên thì ngõ ra sẽ tăng một đơn vị.

3

- Khi PulseIn xuống 0 thì 2 khối IC 74374 sẽ thực hiện chốt dữ liệu Q[15..0] ra ngõ ra D[15..0], đồng thời chân aclr được set lên 1 và thực hiện reset bộ đếm.

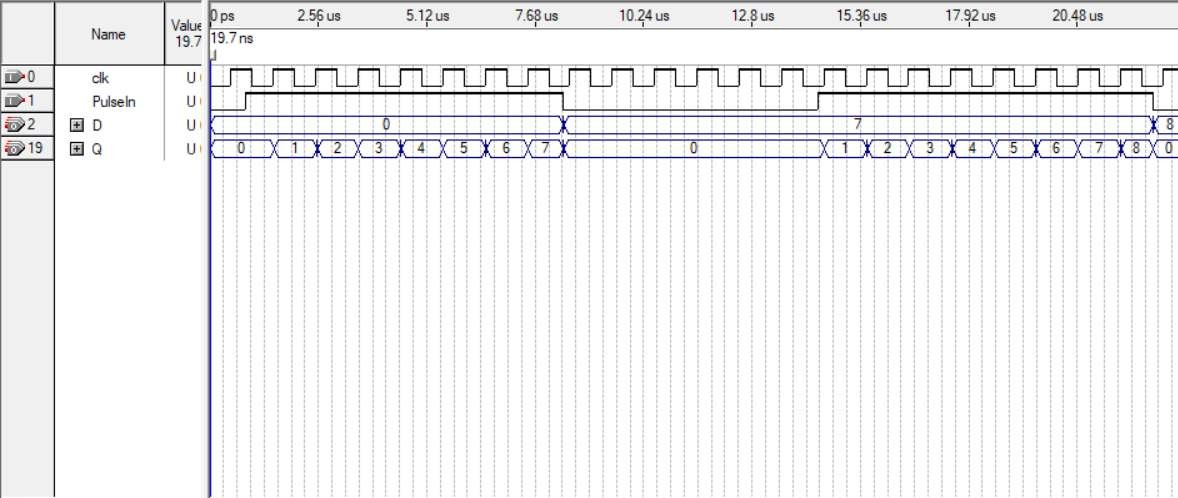

Kết quả mô phỏng:

Nhận xét: kết quả mô phỏng chính xác, tại các cạnh xuống của xung PulseIn thì ngõ ra Q[15..0] của bộ đếm được reset về 0, ngõ ra D[15..0] của các IC chốt sẽ giữ giá trị đếm được của ngõ ra Q.

4

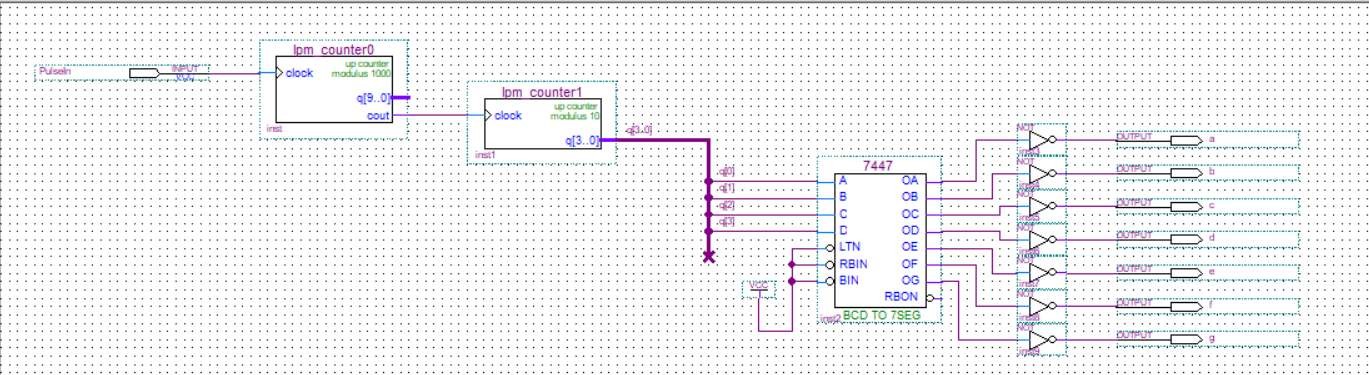

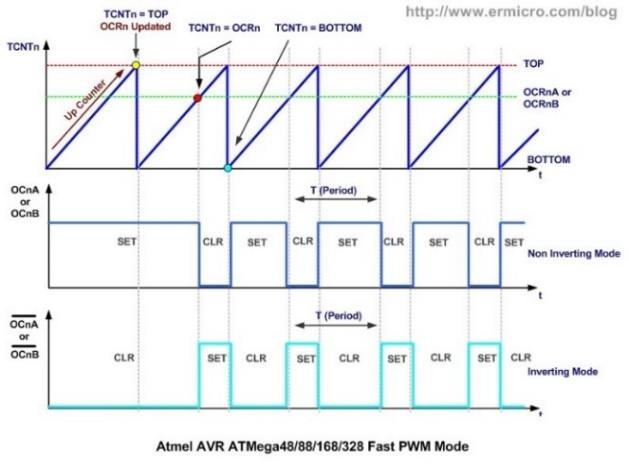

Bài 2: Hiển thị LED 7 đoạn

- Đầu vào xung clk (1us)

- Đầu ra D[6:0]: dữ liệu LED 7 đoạn (cực âm chung)

- Số LED hiển thị : 1

- Hiển thị từ 0ms – 9ms, sau đó lặp lại

- Giải mã LED bằng IC 7447

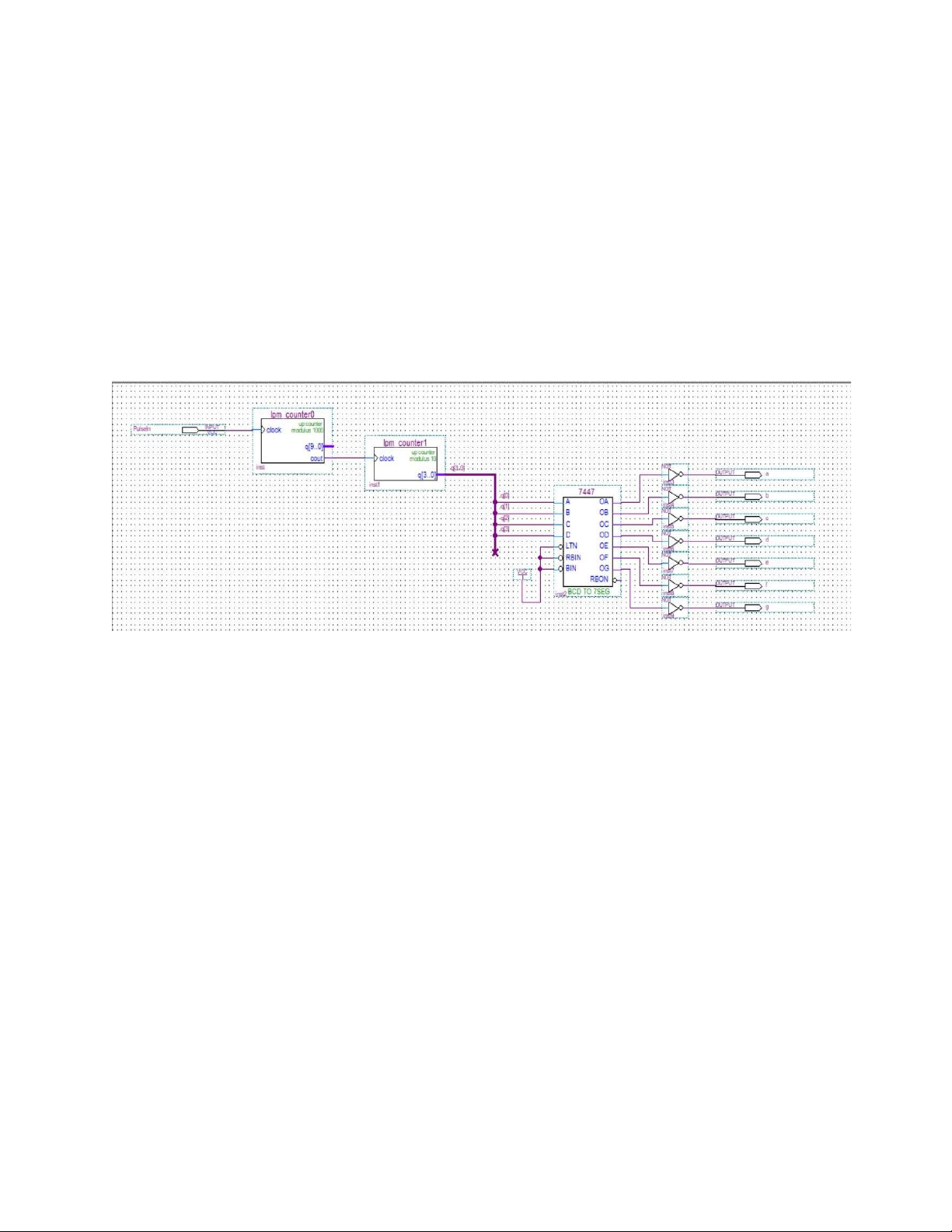

Hình 2: Mạch mô phỏng giải mã LED 7 đoạn

Nguyên lý hoạt động:

- Bộ lpm_counter0 nhận xung đầu vào PulseIn = 1us, ngõ ra Q[0..9] có thể đếm được đến 1000, Modulus = 1000 để xuất ra chân Cout xung clock 1ms.

- Bộ lpm_counter1 lấy xung clock đầu vào là Cout 1ms, Modulus = 10 đếm từ 0-9 rồi lặp lại. Các ngõ ra Q[0..3] đưa vào 7447, ngõ ra 7447 qua cổng NOT để xuất ra LED 7 đoạn.

5

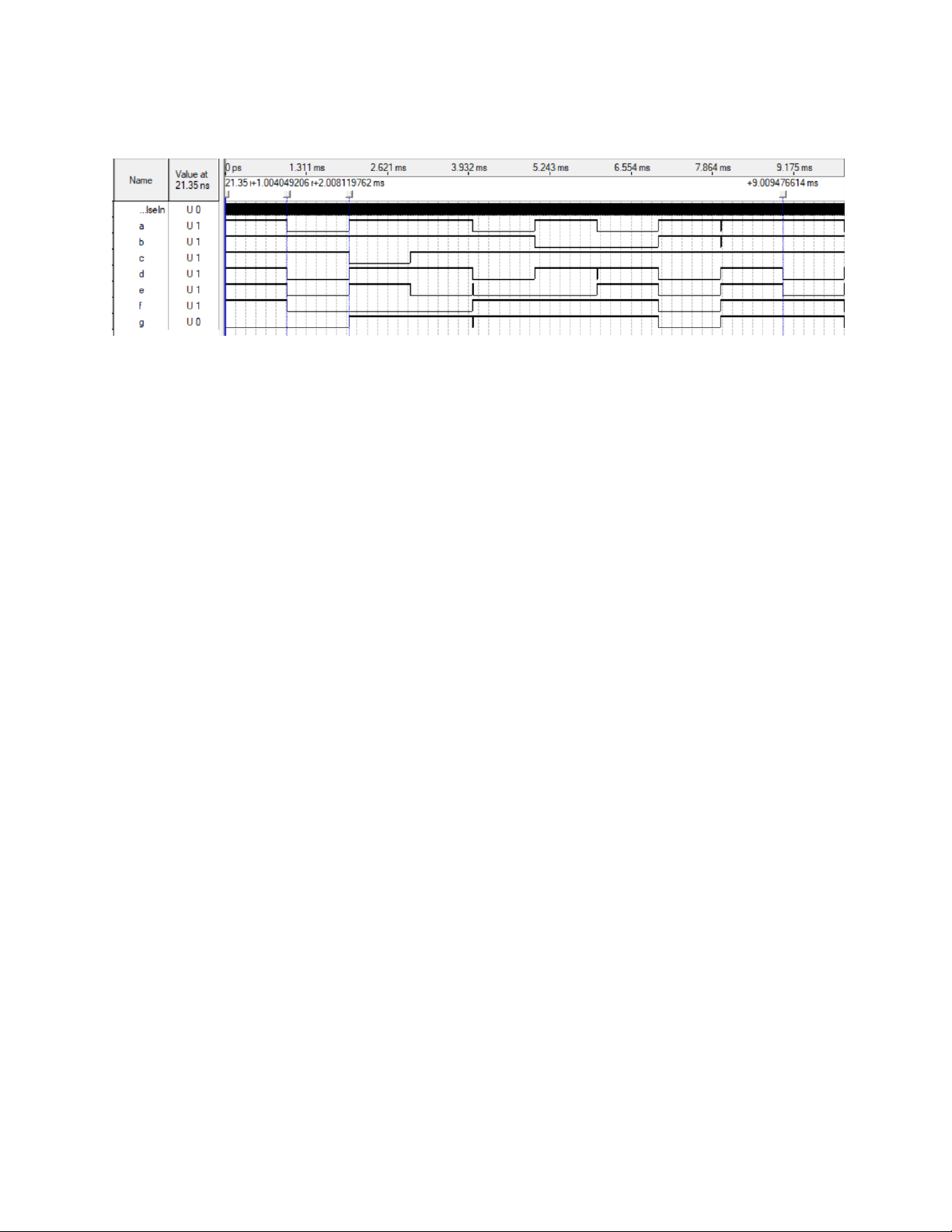

Mô phỏng:

Nhận xét: Mô phỏng phù hợp với yêu cầu đề bài.

6

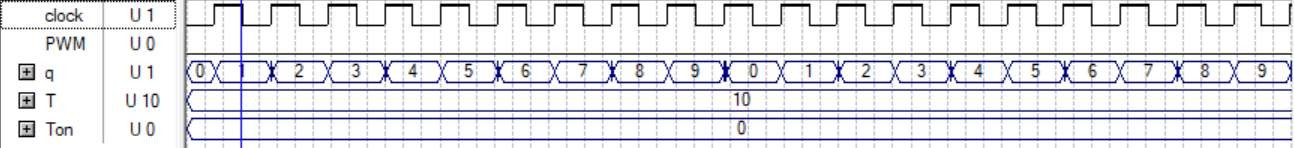

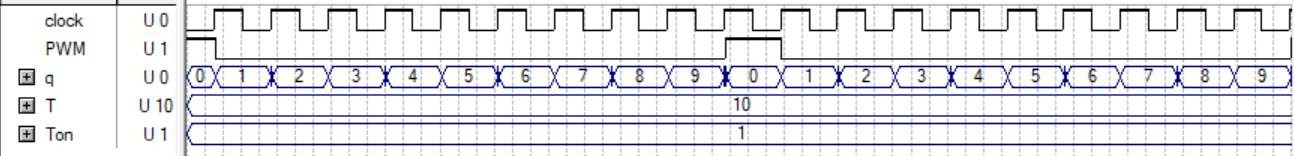

Bài 3: Điều rộng xung

- Đầu vào T (8bit), Ton (8bit), clk (1us).

- Đầu ra PwmOut.

- Độ phân giải 8 bit (255 mức).

- Ton, T chỉ thay đổi 1 lần đầu lúc khởi động, T = 10.

- Sử dụng khối lpm_counter và lpm_cpmpare trong Megafunctions/Arithmetic.

Quy tắc thiết kế: Điều rộng xung dựa trên giá trị T, Ton, clk. Đếm xung clk, khi giá trị

đếm (counter)

Ton

thì PWM =1, khi giá trị đếm vượt quá Ton thì giá trị PWM =0 và khi

giá trị đếm tới T thì reset giá trị đếm về 0. Mạch thiết kế:

Hình 3: Mạch mô phỏng điều rộng xung

- lpm_counter0: đếm số xung của clk chu kỳ 1us với ngõ ra Q[7..0] là giá trị đếm xung.

7

- lpm_compare0: so sánh giá trị đếm của xung với Ton để xuất ra xung PWM.

- lpm_compare1: so sánh giá trị đếm của xung với T, nếu giá trị đếm vượt quá T thì kích clr để reset bộ đếm lpm_counter0.

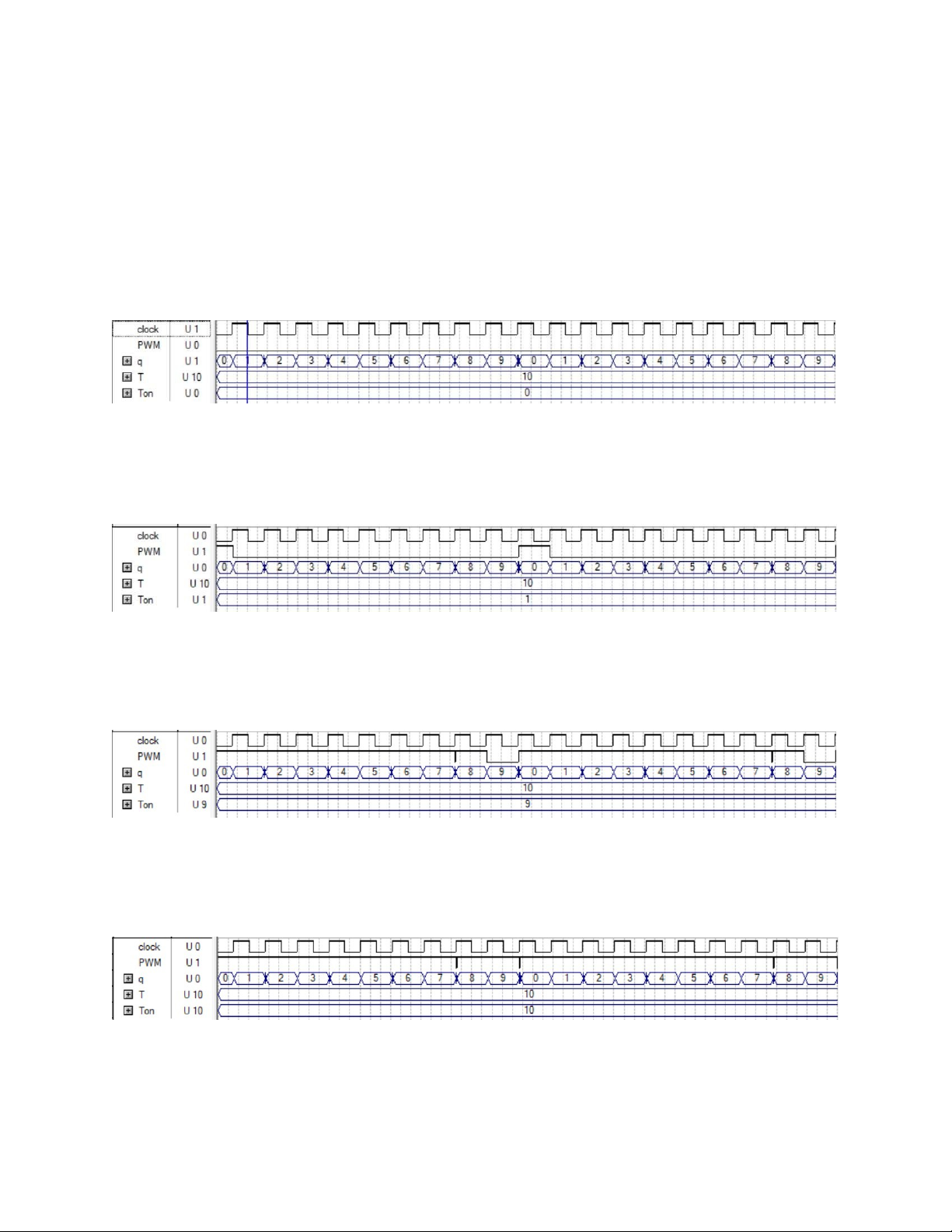

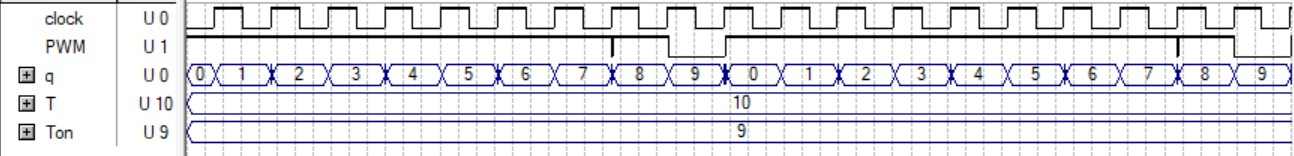

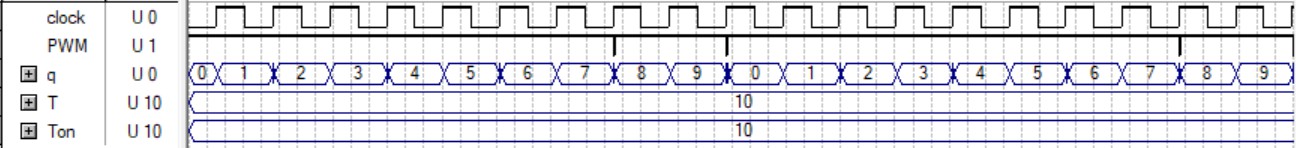

Kết quả mô phỏng:

- T = 10, Ton = 0:

Xung PWM luôn bằng 0 do giá trị đếm counter luôn lớn hơn Ton

- T = 10, Ton = 1:

PWM có xung bằng 1 tới giá trị 1 sau đó hạ xuống về 0.

- T = 10, Ton = 9:

Xung PWM bằng 1 tới khi Q đếm tới 9 sau đó xuống 0 tại 10

- T = 10, Ton = 10:

Ta thấy xung PWM luôn bằng 1 do giá trị counter luôn nhỏ hơn Ton

Từ kết quả mô phỏng ta thấy mạch thiết kế thỏa yêu cầu đề bài.

8

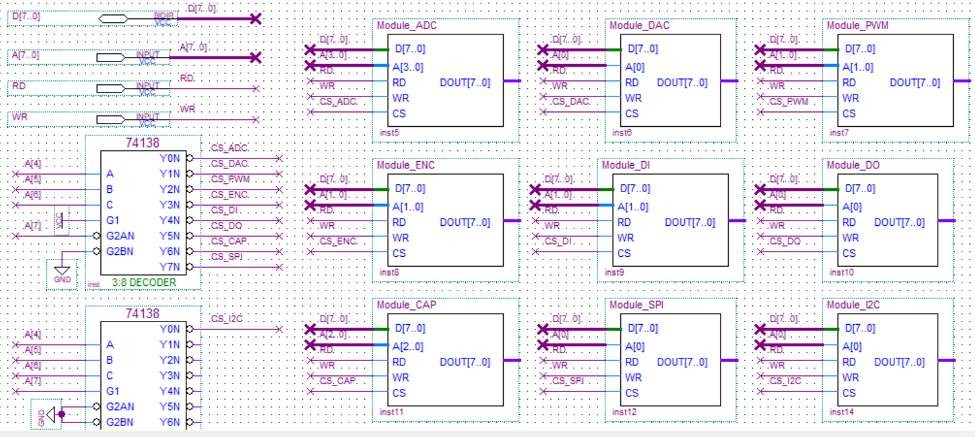

Bài 4: Vẽ lại mạch giải mã ở Slide15 trên Quartus/Block Diagram

Tầm địa chỉ:

CS_ADC: 0x00 – 0x03 CS_DAC: 0x10 – 0x11 CS_PWM: 0x20 – 0x25 CS_ENC: 0x30 – 0x35 CS_DI: 0x40 – 0x41

9

Bài 5: Vẽ lại mạch giải mã ở Slide19 trên Quartus/Block Diagram

Tầm địa chỉ:

CS_ADC: 0x00 – 0x0F CS_DAC: 0x10 – 0x11 CS_PWM: 0x20 – 0x23 CS_ENC: 0x30 – 0x33 CS_DI: 0x40 – 0x43 CS_DO: 0x50 – 0x51 CS_CAP: 0x60 – 0x65 CS_SPI: 0x70

CS_I2C: 0x80

10