Preview text:

Table of Contents

CHƯƠNG 1. DIODE................................................................................................3 1.1.

Mạch phân cực cho diode:.........................................................................3

1.1.2. Mạch phận cực ngược:............................................................................3

1.1.3. Mạch phân cực có hai nguồn dương:......................................................3 1.2.

Mạch chỉnh lưu nửa chu kì:.......................................................................3

1.2.1. Mạch chỉnh lưu nửa chu kỳ không có tụ lọc:..........................................3

1.2.2. Mạch chỉnh lưu nửa chu kỳ có tụ lọc:.....................................................5 1.3.

Mạch chỉnh lưu hai nửa chu kì:.................................................................6

1.3.1 Cấu tạo và nguyên lý hoạt động...............................................................6 1.3.2

Tính toán lý thuyết và đo lường mô phỏng.........................................7 1.4.

Mạch chỉnh lưu cầu:..................................................................................8 1.4.1

Cấu tạo và nguyên lý hoạt động..........................................................8

1.4.2 Tính toán lý thuyết và đo lường mô phỏng..............................................8 1.5.

Mạch ổn áp dùng diode Zener.................................................................10

1.5.1 Cấu tạo và nguyên lý hoạt động.............................................................10

1.5.2 Tính toán lý thuyết và đo lường mô phỏng............................................11 1.6.

Mạch hạn chế: Mạch hạn chế mức dưới dương.......................................11

1.6.1 Cấu tạo và nguyên lý hoạt động.............................................................11

1.6.2 Tính toán lý thuyết và đo lường mô phỏng............................................12 1 DANH MỤC HÌNH ẢNH

Hình 1- 1 Sơ đồ mạch chỉnh lưu nửa chu kỳ.............................................................3

Hình 1- 2 Sơ đồ mạch chỉnh lưu nửa chu kỳ không có tụ lọc...................................3

Hình 1- 3 Kết quả đo mạch chỉnh lưu nửa chu ký không có tụ lọc...........................4

Hình 1- 4 Sơ đồ mạch chỉnh lưu nửa chu kỳ có tụ lọc..............................................5

Hình 1- 5 Kết quả đo mạch chỉnh lưu nửa chu kỳ có tụ lọc......................................5

Hình 1- 6 Sơ đồ mạch chỉnh lưu cả chu kỳ, 2 nguồn................................................6

Hình 1- 7 Kết quả đo mạch chỉnh lưu cả chu kỳ, hai nguồn.....................................7

Hình 1- 8 Sơ đồ mạch chỉnh lưu cầu.........................................................................8

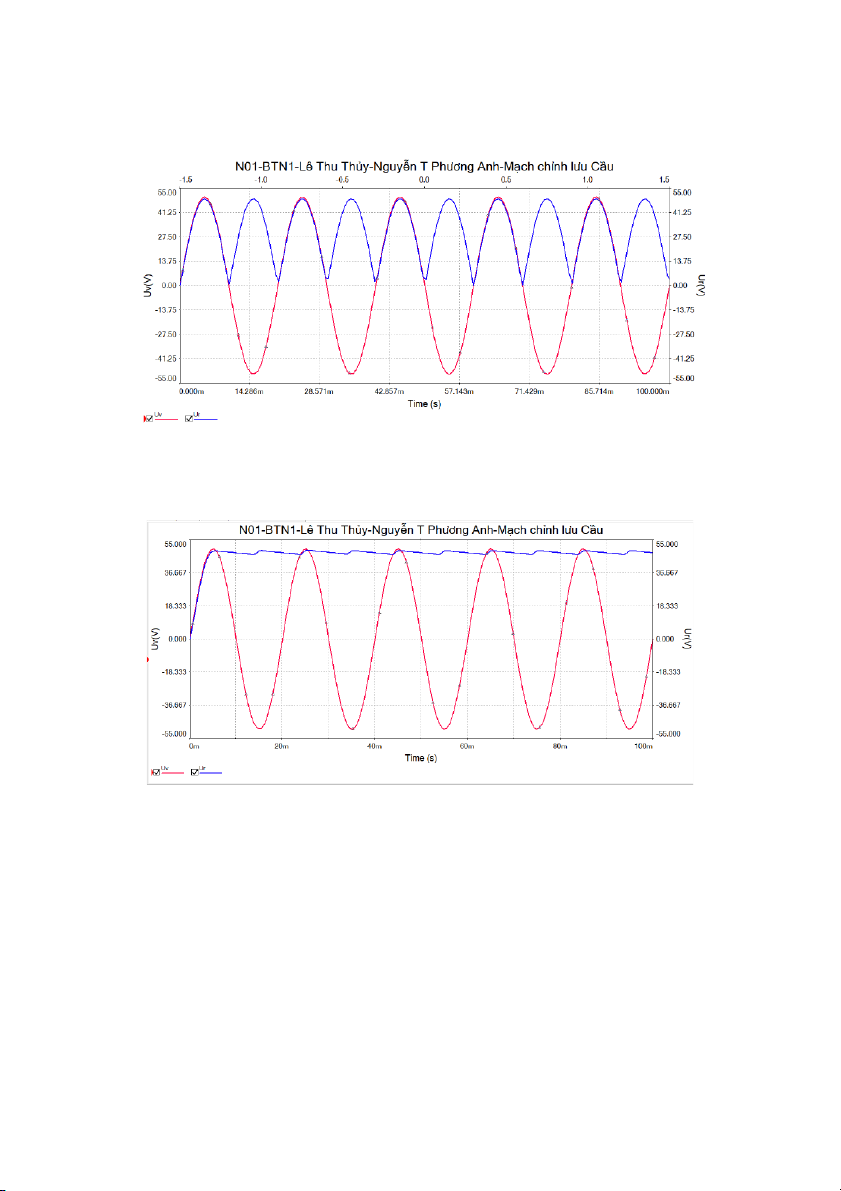

Hình 1- 9 Kết quả đo mô phỏng mạch chỉnh lưu cầu không tụ lọc...........................9

Hình 1- 10 Kết quả đo mô phỏng mạch chỉnh lưu cầu có tụ lọc...............................9

Hình 1- 11 Sơ đồ mạch ổn áp bằng diode zener......................................................10

Hình 1- 12 Sơ đồ mạch hạn chế mức dưới dương...................................................11

Hình 1- 13 Kết quả đo mô phỏng mạch hạn chế mức dưới dương.........................12 DANH MỤC BẢNG BIỂU

Bảng 1- 1 Kết quả đo mô phỏng mạch chỉnh lưu nửa chu kỳ không có tụ lọc........4

Bảng 1- 2 Kết quả đo mô phỏng mạch chỉnh lưu nửa chu kỳ có tụ lọc...................6

Bảng 1- 3 Kết quả đo mạch chỉnh lưu cả chu kỳ, hai nguồn....................................7

Bảng 1- 4 Kết quả đo mô phỏng mạch chỉnh lưu cầu có tụ lọc............................10

Bảng 1- 5 Kết quả lý thuyết và mô phỏng mạch ổn áp dùng diode zener..............11

Bảng 1- 6 Kết quả đo mô phỏng mạch hạn chế mức dưới dương..........................12 2 CHƯƠNG 1. DIODE

Ứng dụng phổ biến của diode: Chỉnh lưu, Ổn áp và Hạn chế 1.1. Mạch phân cực cho diode:

1.1.1. Mạch phân cực thuận:

1.1.2. Mạch phận cực ngược:

1.1.3. Mạch phân cực có hai nguồn dương:

1.2. Mạch chỉnh lưu nửa chu kì:

* Cấu tạo và nguyên lý hoạt động

Mạch chỉnh lưu nửa chu kì gồm một diode chỉnh lưu,

một điện trở hạn chế dòng, một tụ lọc (nếu cần) và nguồn

xoay chiều được ghép nối như hình vẽ.

Hình 1- 1 Sơ đồ mạch chỉnh lưu nửa chu kỳ

Ở nửa chu kì dương, diode phân cực thuận, cho dòng đi qua (Uv>UD)

Ở nửa chu kì âm, diode phân cực ngược, ngăn cản dòng

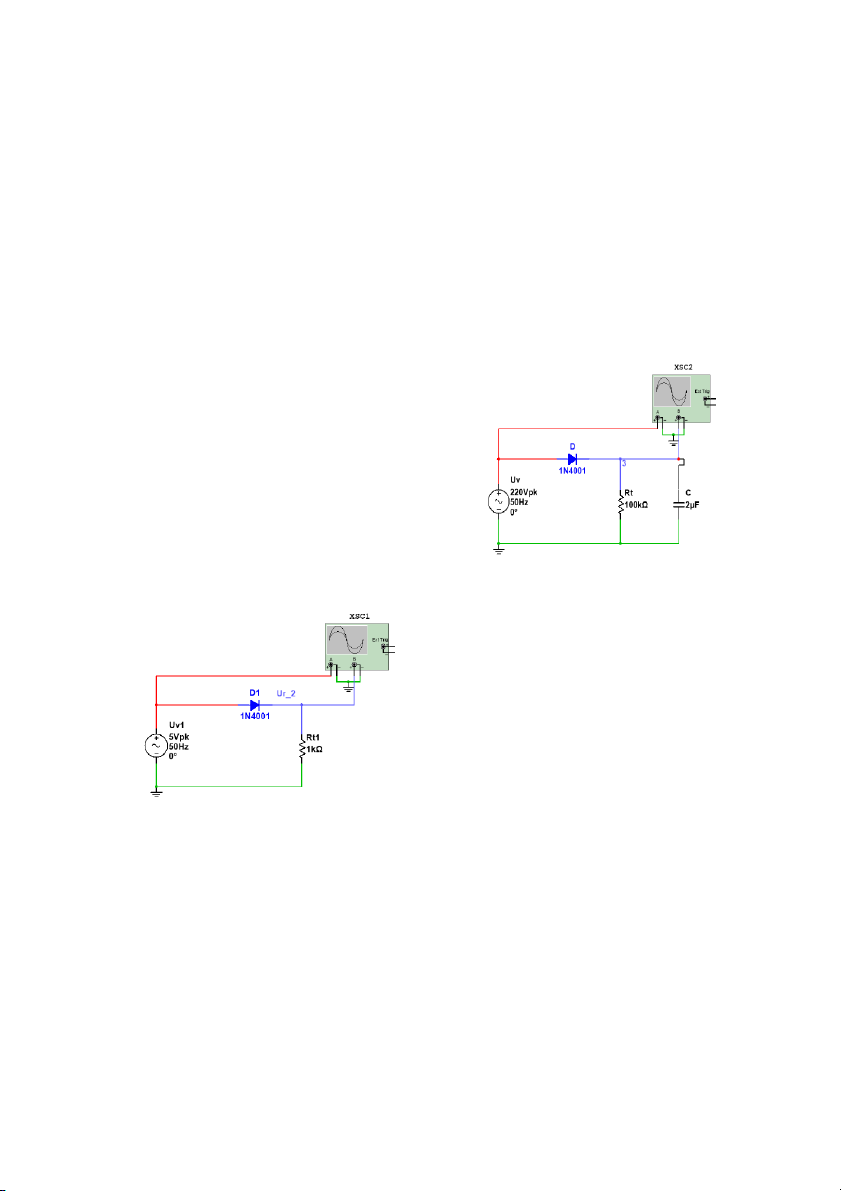

điện (Uv1.2.1. Mạch chỉnh lưu nửa chu kỳ không có tụ lọc: a. Sơ đồ mạch:

Hình 1- 2 Sơ đồ mạch chỉnh lưu nửa chu kỳ không có tụ lọc

Cho số liệu UV=5cos(100πt) V; UD = 0,68 V; rD = 0 Ω

Rt=1kΩ; D : 1N4001– nhóm 1 1 3

Điện áp chỉnh lưu : U = 0,318 (U 0 m -UD0)=1.374 V

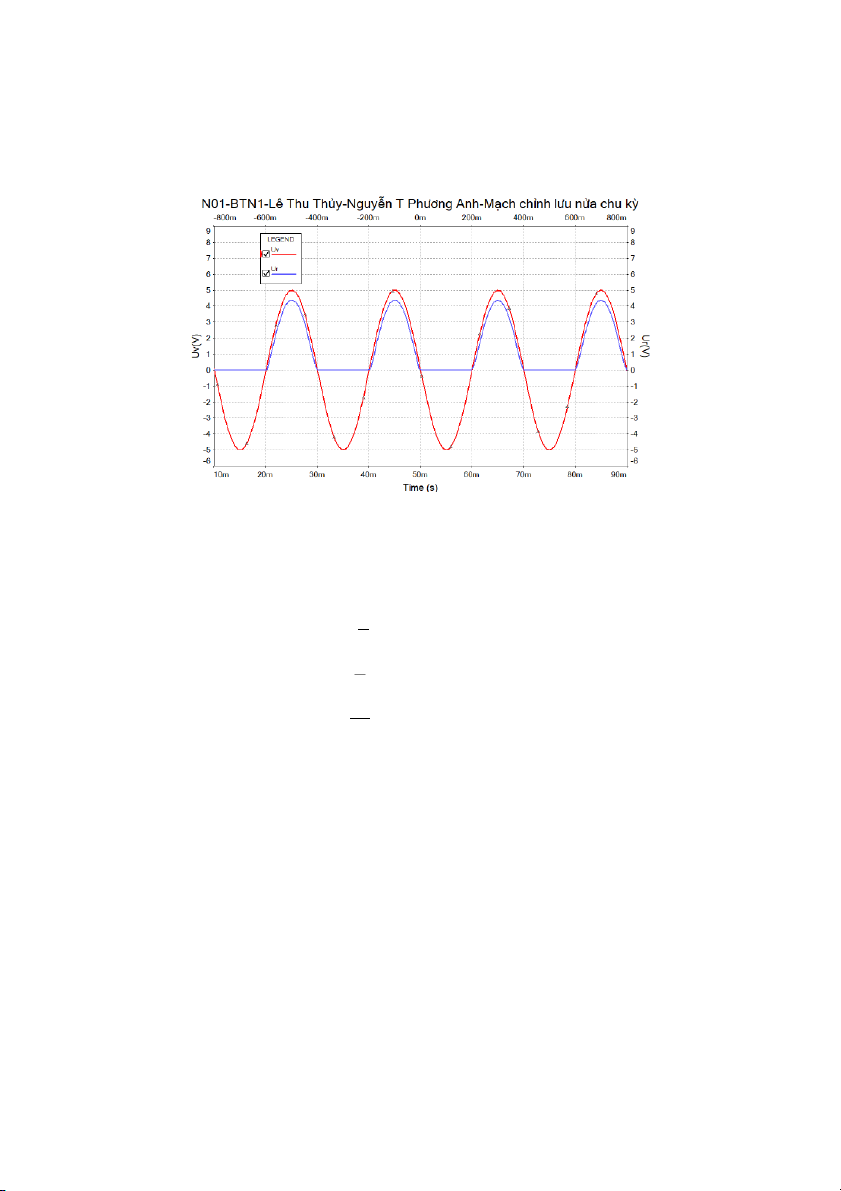

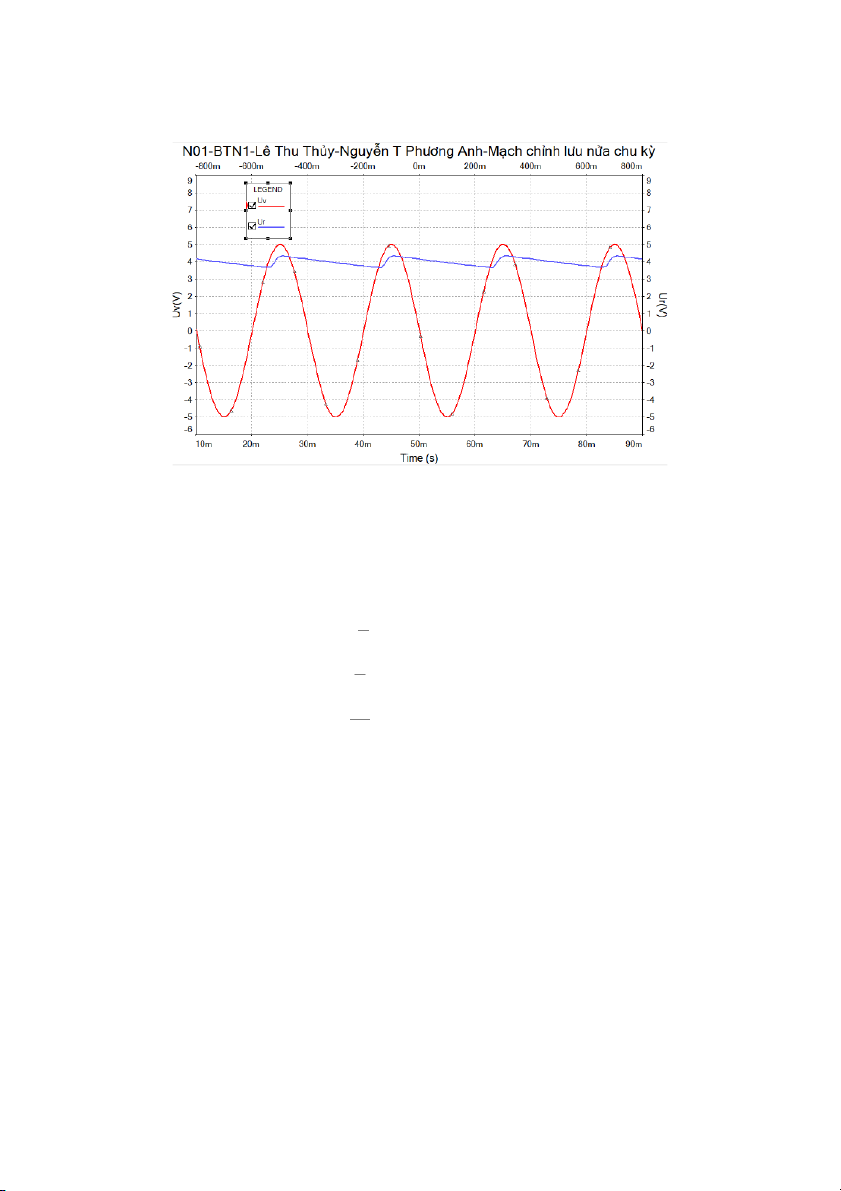

b. Đồ thị Uv(t) và Ur(t):

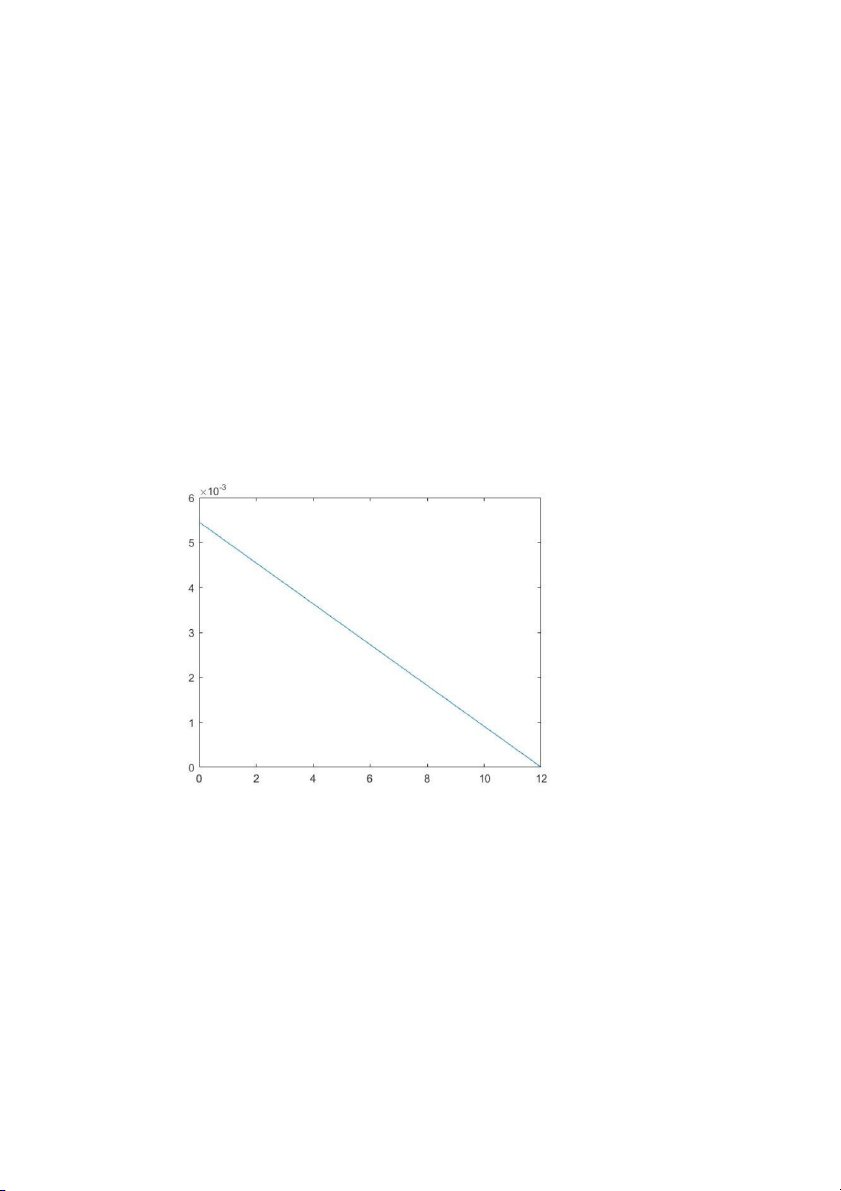

Hình 1- 3 Kết quả đo mạch chỉnh lưu nửa chu ký không có tụ lọc

c. Một số giá trị Uv và Ur tại các mốc thời gian: STT t(ms) Uv(V) Ur(V) 1 0 0 0 2 T=5 4.997 4.385 4 3 T=10 -0.00019 0.014 2 4 3Τ =15 -4.980 -0.00003 4 5 T =20 0.00053 0.00567

Bảng 1- 1 Kết quả đo mô phỏng mạch chỉnh lưu nửa chu kỳ không có tụ lọc

Nhận xét: Kết quả đo mô phỏng và kết quả tính toán lý thuyết tương đối bằng nhau. Ở thời điểm

3T/4, Ura có giá trị âm do qua diode thực tế không chặn hoàn toàn dòng điện mà luôn có một

dòng điện ngược rất rất nhỏ chạy qua khi diode phân cực ngược 4

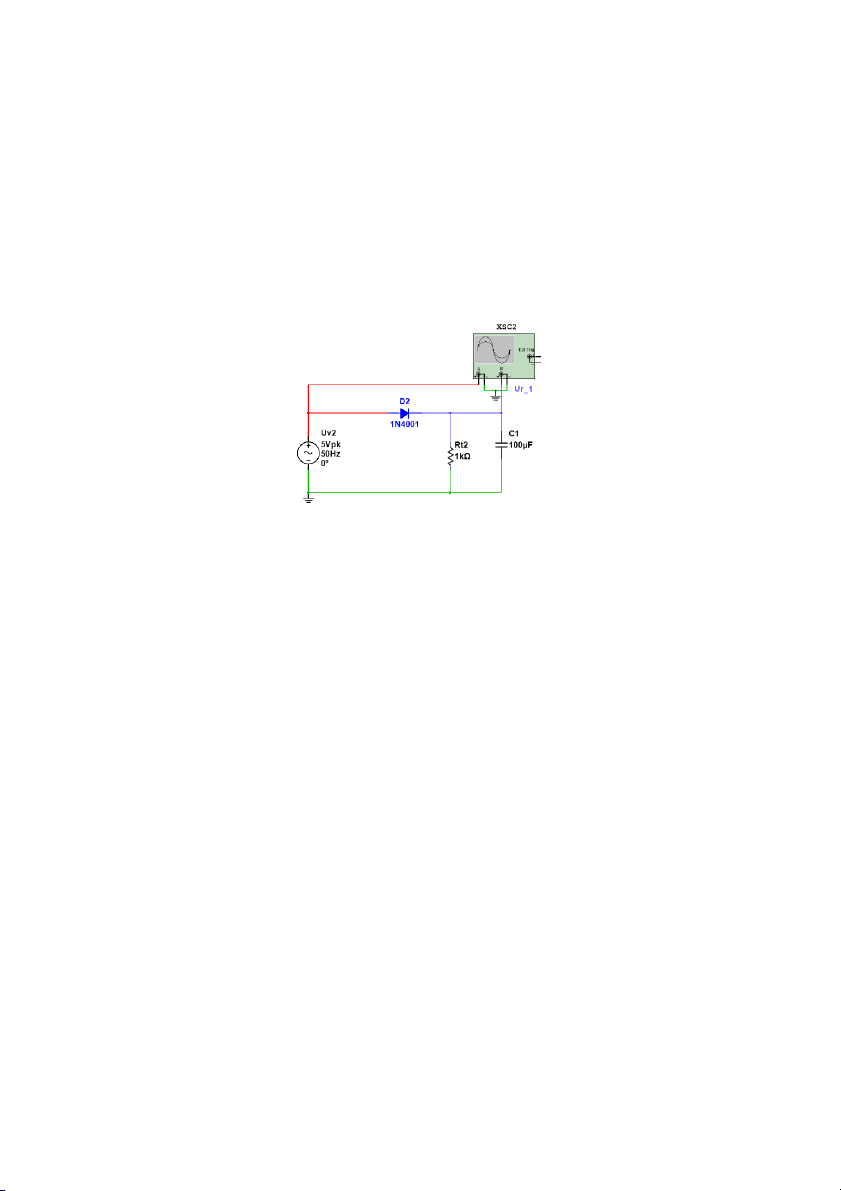

1.2.2. Mạch chỉnh lưu nửa chu kỳ có tụ lọc: a, sơ đồ mạch

Cho số liệu UV=5cos(100πt) V; UD0 = 0,68V; rD = 0 Rt=1kΩ ; rD = 0Ω D : 1N4001 ; C1=100µF 1

Điện áp chỉnh lưu : U0~Um=5V

Hình 1- 4 Sơ đồ mạch chỉnh lưu nửa chu kỳ có tụ lọc

b, Đồ thị Uv(t) và Ur(t) 5

Hình 1- 5 Kết quả đo mạch chỉnh lưu nửa chu kỳ có tụ lọc

c, Một số giá trị Uv và Ur tại các mốc thời gian STT t(ms) Uv(V) Ur(V) 1 0 0 0 2 T=5 4.981 4.311 4 3 T=10 -0.00003 4.164 2 4 3Τ =15 -4.976 3.961 4 5 Τ =20 0.00003 3.767

Bảng 1- 2 Kết quả đo mô phỏng mạch chỉnh lưu nửa chu kỳ có tụ lọc

Nhận xét: Ura được san phẳng nhờ tụ lọc phóng điện bổ xung 1.3.

Mạch chỉnh lưu hai nửa chu kì:

1.3.1 Cấu tạo và nguyên lý hoạt động

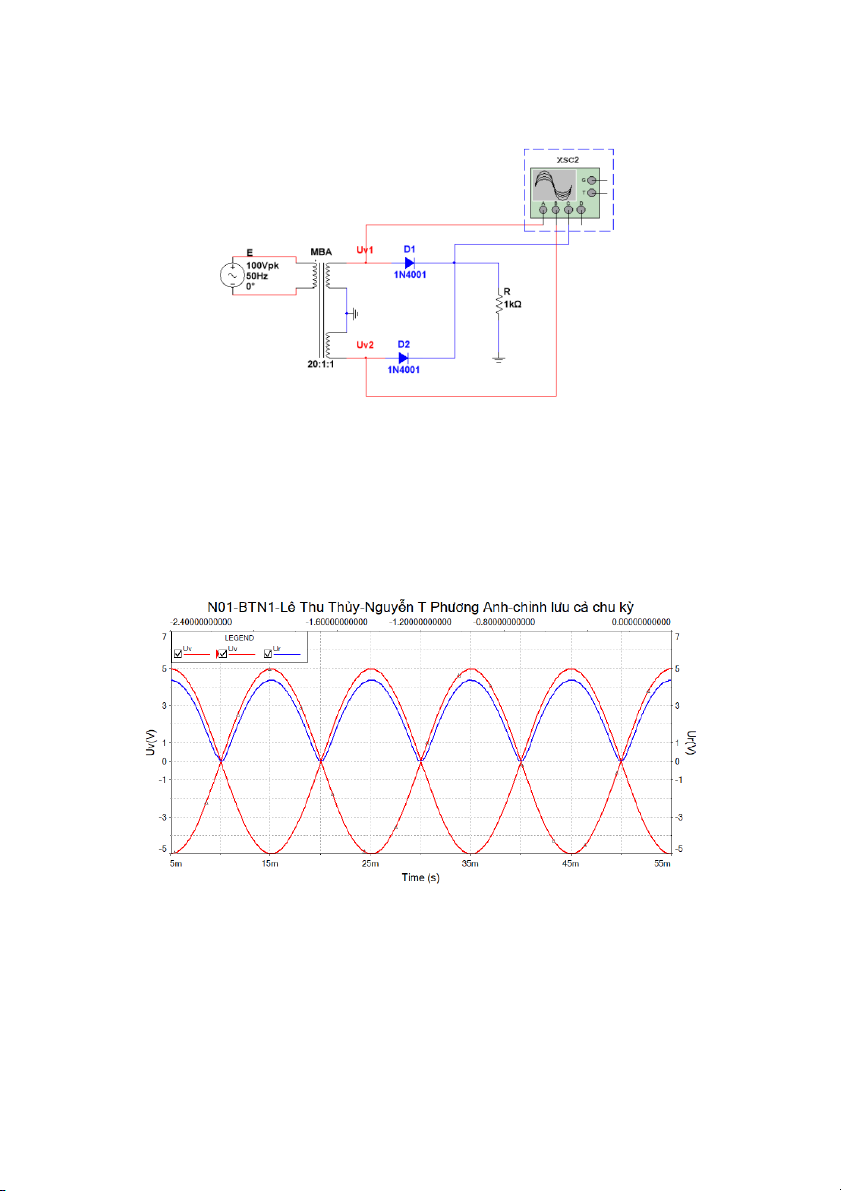

Mạch chỉnh lưu cả chu kỳ, hai nguồn gồm: hai nguồn vào, 2 Diode bán dẫn và 1 điện trở được mô tả như hình vẽ 6

Hình 1- 6 Sơ đồ mạch chỉnh lưu cả chu kỳ, 2 nguồn

1.3.2 Tính toán lý thuyết và đo lường mô phỏng

a, sơ đồ mạch cho như hình trên

Cho số liệu UV1=-UV2=5cos(100πt) V ; UD0 = 0,68V; rD = 0

R=1kΩ ; rD = 0Ω; D1,D : 1N4001 2

b, Đồ thị Uv(t) và Ur(t)

Hình 1- 7 Kết quả đo mạch chỉnh lưu cả chu kỳ, hai nguồn 7 BẢNG SỐ LIỆU STT t(ms) Uv1(V) Uv2(V) Ur(V) 1 0 0 0 0 2 T=5 4.997 -4.997 4.385 4 3 T=10 -0.000196 0.000196 0.01511 2 4 3Τ =15 -4.976 4.976 4.365 4 5 Τ =20 0.000121 -0.000121 0.01937

Bảng 1- 3 Kết quả đo mạch chỉnh lưu cả chu kỳ, hai nguồn 8 1.4. Mạch chỉnh lưu cầu:

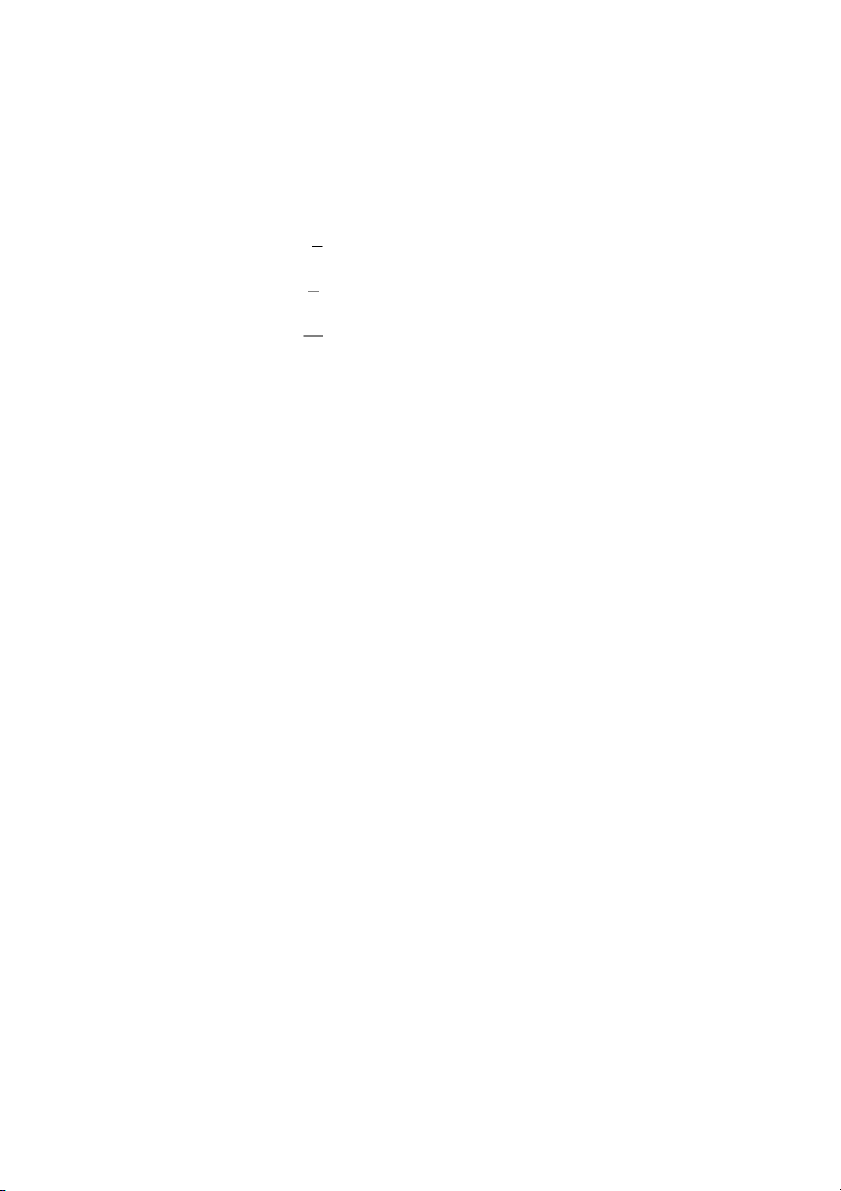

1.4.1 Cấu tạo và nguyên lý hoạt động

Mạch chỉnh lưu cầu gồm 4 diode chỉnh lưu, một điện trở hạn chế dòng, một tụ lọc (nếu cần) và

một nguồn xoay chiều được ghép nối như hình vẽ.

Hình 1- 8 Sơ đồ mạch chỉnh lưu cầu

Ở nửa chu kỳ dương, D2 và D4 mở, còn D1, D3 khóa, dòng điện đi từ dương nguồn qua D2, R, D4 về âm nguồn.

Ở nửa chu kỳ âm, D2 và D4 khóa, còn D1, D3 mở, dòng điện đi từ âm nguồn qua D3, R, D1 về dương nguồn.

1.4.2 Tính toán lý thuyết và đo lường mô phỏng Cho: U = 50cos(100πt) V; U v D = 0,68V

rD = 0; R = 100kΩ; 4Diode 1N4001

● Khi không có tụ lọc:

Điện áp chỉnh lưu: U = 0,636(U 0 m − 2UD) = 30.935V Dòng chỉnh lưu: I = U 0 0 /R = 0.309mA 9

Dưới đây là kết quả đo mô phỏng mạch chỉnh lưu cầu không tụ lọc:

Hình 1- 9 Kết quả đo mô phỏng mạch chỉnh lưu cầu không tụ lọc

● Khi có tụ lọc (nối song song tụ với điện trở R):

Điện áp chỉnh lưu: U = U 0 m − 2UD = 48.64V

Hình 1- 10 Kết quả đo mô phỏng mạch chỉnh lưu cầu có tụ lọc 10 Bảng số liệu: STT t(ms) Uv(V) Ur(V) 1 0 0 0 2 T=5 49.865 48.798 4 3 T=10 0.0025 47.840 2 4 3Τ =15 -49.886 48.837 4 5 Τ =20 0.0043 47.908

Bảng 1- 4 Kết quả đo mô phỏng mạch chỉnh lưu cầu có tụ lọc

Ura biến đổi tuần hoàn theo hàm cos, Uvào ban đầu tăng dần, khi đạt đỉnh thì dữ ổn định ở giá trị

khoảng 48.6V(theo mạch) tùy vào điện dung tụ lọc. 1.5.

Mạch ổn áp dùng diode Zener

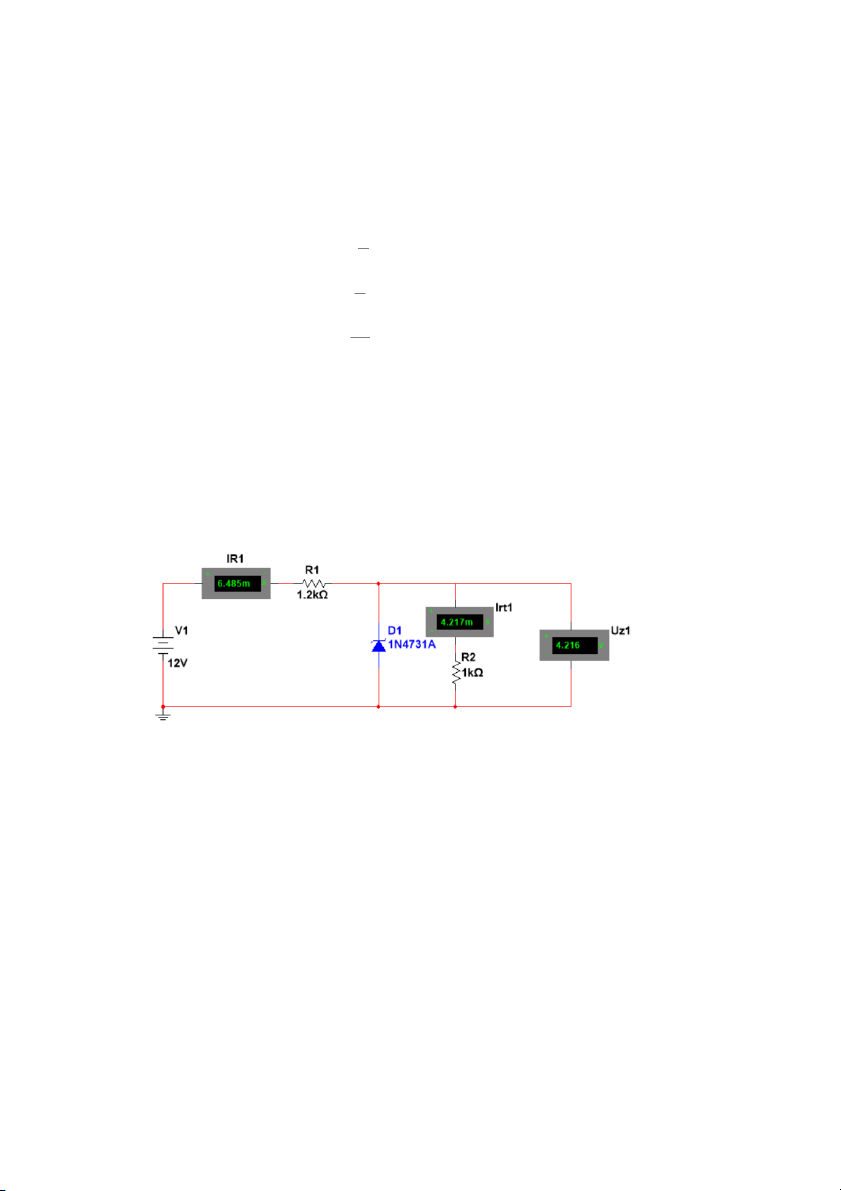

1.5.1 Cấu tạo và nguyên lý hoạt động

Mạch ổn áp bằng diode zener gồm 1 điện trở hạn chế dòng, 1 diode zener, và 1 nguồn một chiều được mắc như Hình

Hình 1- 11 Sơ đồ mạch ổn áp bằng diode zener

Diode zener hoạt động chủ yếu ở chế độ phân cực ngược, lợi dụng tính chất đánh thủng do

điện của diode. Khi điện áp đầu vào nhỏ hơn điện áp đánh thủng của zener, nó sẽ chặn không

cho dòng đi qua. Khi điện áp đầu ra lớn hơn điện áp đánh thủng thủng trên diode zener, nó sẽ ổn

áp sao cho hai đầu diode có điện áp sấp sỉ khoảng 4.3V 11

1.5.2 Tính toán lý thuyết và đo lường mô phỏng

Cho RZ = 0Ω, UZ = 4.3V, EC = 12V, R = 1,2kΩ, R 1 = 1kΩ 2 Ec -U z 12−4,3 Ta có: EC = IR + UZ ↔ I = = =6,417Ma R1 1,2.1 03 4,3 IR2 =Uz= =4,3mA Rz 1.1 03

IZ = I − IR2 = 6,417 – 4,3 = 2,117mA Đại lượng Kết quả lý thuyết Kết quả mô phỏng UZ 5 V 4,216 V I 5,83 mA 6,485 mA IR2 5 mA 4,217 mA

Bảng 1- 5 Kết quả lý thuyết và mô phỏng mạch ổn áp dùng diode zener 1.6.

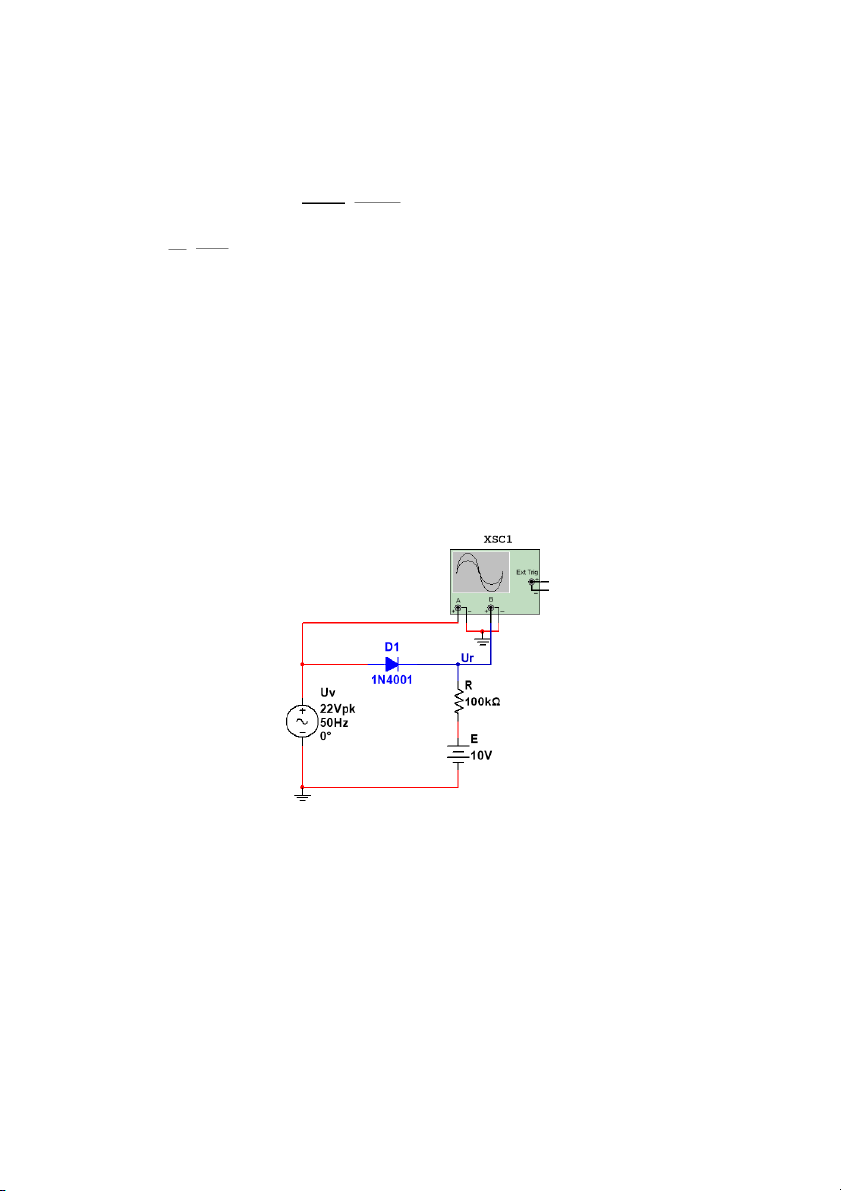

Mạch hạn chế: Mạch hạn chế mức dưới dương

1.6.1 Cấu tạo và nguyên lý hoạt động

Mạch hạn chế mức trên dương gồm 1 diode chỉnh lưu ,1 điện trở hạn chế, 1 nguồn 1 chiều, 1

nguồn xoay chiều được ghép nối như Hình

Hình 1- 12 Sơ đồ mạch hạn chế mức dưới dương 12

1.6.2 Tính toán lý thuyết và đo lường mô phỏng Cho: U = 22cos(100πt) V; U v D = 0,68V; E=10V

rD = 0; R = 100kΩ; Diode 1N4001 nhóm 1 Ở nửa chu kỳ dương:

Khi Uvào > E=>diode phân cực thuận=> Ura ≈ Uvào.

Khi Uvào < E=> diode phân cực ngược=>Ura = E = 10V.

Ở nửa chu kỳ âm: diode luôn phân cực ngược=> Ura=E=10V.

Hình 1- 13 Kết quả đo mô phỏng mạch hạn chế mức dưới dương BẢNG SỐ LIỆU STT t(ms) Uv(V) Ur(V) 1 0 0 0 2 T=5 21.925 21.501 4 3 T=10 -0.001516 9.993 2 4 3Τ =15 -21.987 9.997 4 5 Τ =20 -0.000789 10.004 13

Bảng 1- 6 Kết quả đo mô phỏng mạch hạn chế mức dưới dương CHƯƠNG 2: BIJ

2.1 Mạch phân cực Bazơ ( Phân cực bằng dòng cố định )

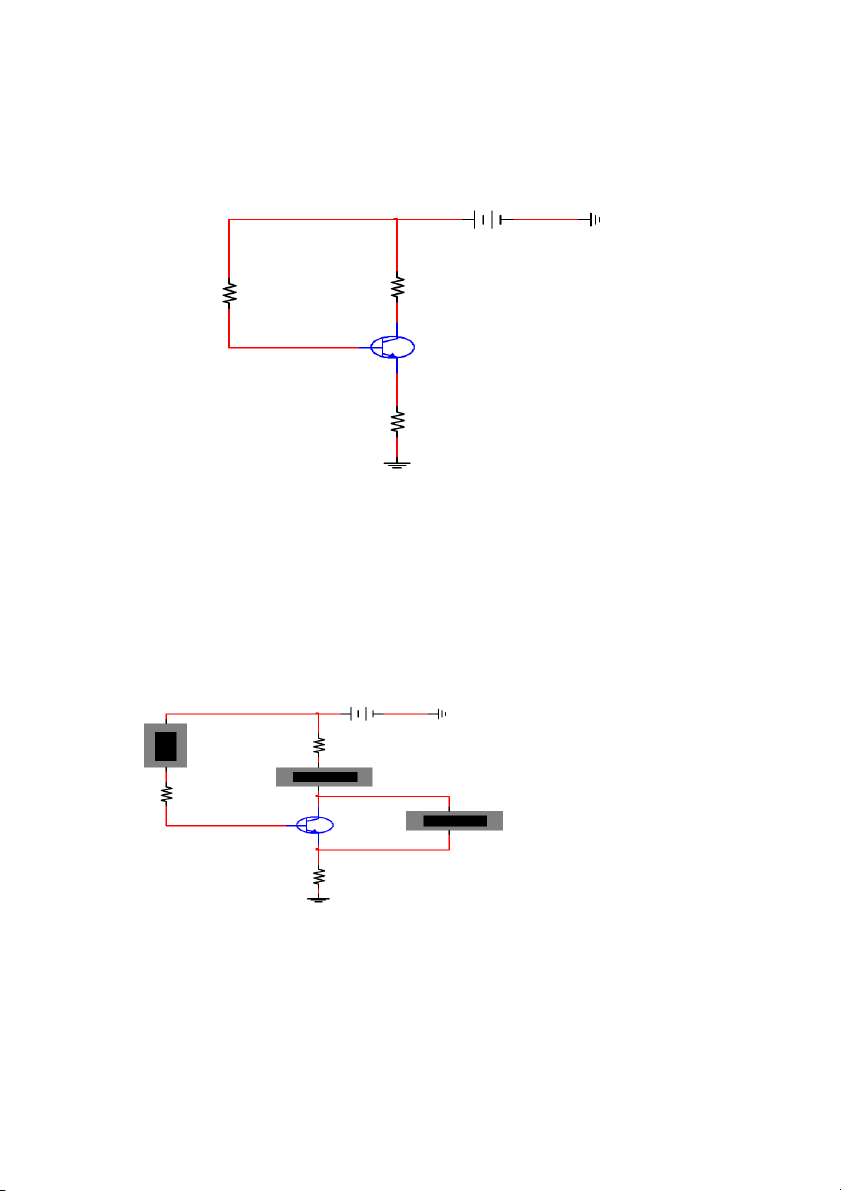

2.1.1 Nguyên lý và cấu tao hoạt động

- Mạch gồm có hai điện trở được mắc ở cực Bazơ và cực Collecter, 1 transistor hai tụ điện và

một nguồn nuôi Ec mắc ở cực Collecter.

- Điện trở RB có giá trị lớn hơn RC để tạo ra điện thế của cực C cao hơn cực B, lớp tiếp giáp

Collecter – Bazơ phân cực ngược. Cực Emiter nối với đất lớp tiếp giáp Emiter – Bazơ phân cực

thuận. Cách mắc đảm bảo cho BIJ làm việc trong vùng khuếch đại. EC 12V IB + IC + 2.94m A DC 1e-009kOhm DC 1e-009Ohm 7.782u A - - RB 1452kΩ RC 2.2kΩ UCE Q1 + 5.534 V 2N3711 DC 10MOhm - + IE 2.947m A DC 1e-009Ohm -

Hình 2.1: Mạch phân cực Bazơ

Transistor 2N3711 dựa theo Datasheet là transistor Si loại NPN UCB = 0.7V , có hệ số khuếch đại

dòng điện nằm trong khoảng 180 ÷ 660. Chọn RC = 2.2 kΩ

Cách chọn R : Để đảm bảo cho BIJ 2N3711 làm việc trong vùng tích cực ( vùng khuếch đại ) thì B điều kiện là U E B C nên ta có: E −I >I >β R C B∗R B C C∗R C ⇔ I B∗RB C∗RC ⇔ RB

Mà hệ số khuếch đại dòng điện phụ thuộc vào dòng I nên chọn R =β R =1452 kΩđể đảm C B max C

bảo lớp tiếp giáp Emitơ – Bazơ phân cực ngược. 14

2.1.2 Sự phụ thuộc của hệ số khuếch đại dòng điên vào dòng IC EC(V ) IC(mA IB(µA) β 2 0.270 0.94 287 4 0.747 2.299 325 6 1.251 3.666 341 8 1.762 5.038 350 10 2.274 6.411 355 12 2.787 7.784 358 14 3.300 9.159 360

Bảng 2.1: Khảo sát hệ số β theo mạch phân cực base

2.1.3 Tính toán lý thuyết:

Dựa theo thông số đo ở bảng 1 chọn E =12V , hệ số khuếch đại dòng điện là C β=358 , U =0.7 CB Xét mạch vào: E

C → R B → U B → U E → GND E −I −U =0 C B∗R B CB I =β I C B

Xét mạch ra: EC → RC → UC → U E → GND U =E −I CE C C∗RC

Theo như đo đạt thực nghiệm tính toán hệ số khuếch đại dòng điện là β=518 Thay số tính toán ta có E −U I = C CB =0.00778 mA B RB I =β∗I =.2785 mA C B U =E −I =5.738 V CE C C∗RC V 15

Theo thông số đo được trên NI và thông số tính toán theo lý thuyết tao có làm việc tĩnh Q: Đại lượng Lý thuyết Đo đạt I (mA) 0.007780 0.007874 B I (mA) 2.785 2.787 C U (V) 5.738 5.868 CE

Bảng 2.2: kết quả đo và lý thuyết mạch phân cực base

2.1.4 Phương trình đường tải E I max ¿ C=5.455(mA) C RC UCE max ¿12(V

Phương trình đường tải :U =E −I CE C C∗RC 16 I C(A)

Hình 2.2: Phương trình đường tải UCE (V ) 17 2.2 Mạch phân cực Emitơ EC 12V RC RB 2.2kΩ 1452kΩ Q1 2N3711 RE 2kΩ

Hình 2.3: Mạch phân cực Emitơ

2.2.1 Cấu tạo và nguyên lý của mạch phân cực Emitơ

Cấu tạo: Mạch gầm một nguồn nuôi E một transistor 2N3711, 3 điện trở R , R , R lắp ở ba cực c c B của transistor.

Nguyên lý: Mạch được mắc như hình vẽ trong đó điện trở được mắc với cực B lớn hơn rất nhiều

so với điện trở lắp với cực C để lớp tiếp giáp Collector và Bazơ phân cực ngược. Lớp tiếp giáp

Emitơ và Bazơ luôn phân cực thuận. BIJ 2N3711 làm việc trong vung khuếch đại 2.2.2 Thông số đo đạt EC + 12V I B R C D C 1e-009Ohm 2.2kΩ 3.553uA - + I C 1.84m A D C 1e-009Ohm - RB 1452kΩ UC E Q1 + 4.258 V DC 10MOhm 2N 3711 - R E 2kΩ 18

Hình 2.4: Mạch phân cực Emitơ

Theo mô phỏng tính toán điểm làm việc tĩnh của transistor là Q(0.00000355, 0.00184, 4.258)

Khi đó hệ số khuếch đại dòng điện là: β=518

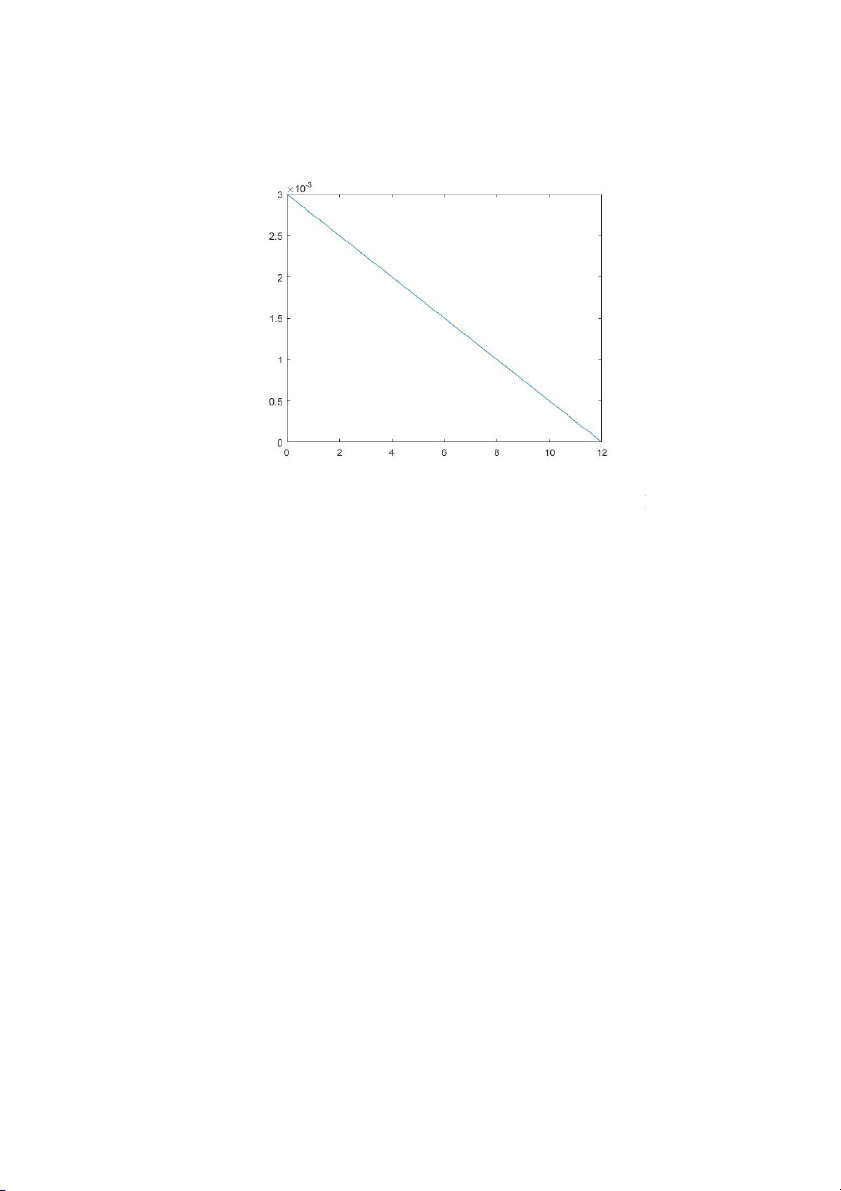

2.2.3 Tính toán theo lý thuyết Cho E =12 V

=1 kΩ, R =1452 kΩ, R =2.2 kΩ c , β=518 , transistor Si, Rc B E . Xét mạch vào: E → R → GND C → R B → U B → U E E E −I −U −I =0 C B∗R B CB E∗R E I =β I C B I =I +I E C B = ( β +1 )∗I B Xét mạch ra: E →

C → RC → U C → U E → R E GND U =E −I −I CE C C∗RC E∗R E

Theo như đo đạt thực nghiệm tính toán hệ số khuếch đại dòng điện là β=518 Thay số tính toán ta có E −U I = C CB =0.00454 mA B (RB+( β +1)∗RC) I =β∗I =2.35172 mA C B U =E −I −I =2.113696V CE C C∗RC E∗R E Q Lý thuyết Đo đạt IB(mA) 0.00454 0.00355 IC(mA 2.35172 1.84 UCE (V ) 2.113696 4.258

Bảng 2.3: Kết quả đo và lý thuyết mạch phân cực emito

2.2.4 Phương trình đường tải E I max ¿ C =2.855(mA) C R R + E∗β +1 C β 19 UCE max ¿12(V I (A) C UCE (V )

2.3 Mạch phân cực hồi tiếp Collector 20 EC 12V RC 2.2KΩ U1 - + RB 7.994u A 1kΩ + IC DC 1e-009Ohm 2.68m A DC 1e-009Ohm - Q1 UCE + 2N3711 0.707 V DC 10MOhm - RE 2KΩ

Hình 2.5: Mạch phân cực hồi tiếp Collector

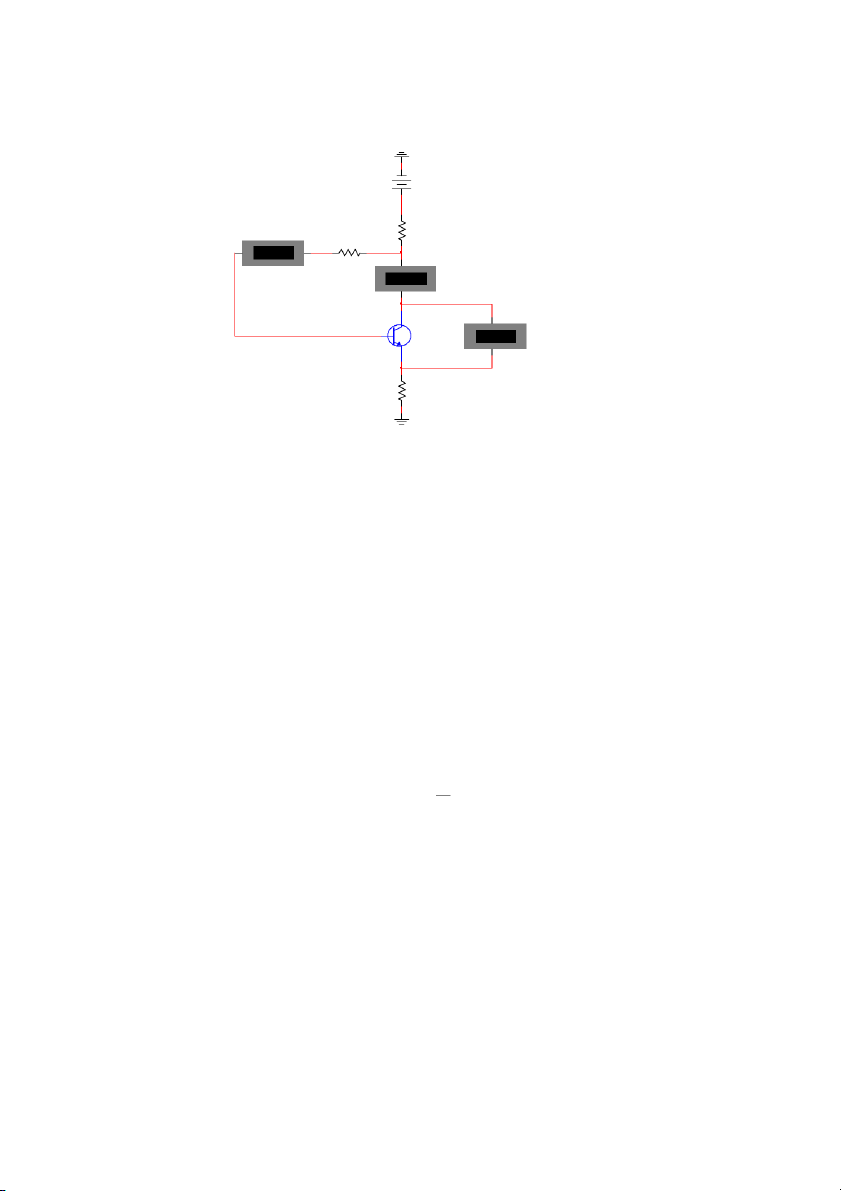

2.3.1 Cấu tạo và nguyên lý hoạt động

Cấu tạo: Mạch gồm ba điện trở 1 transistor được như hình vẽ:

Nguyên lý hoạt động: Phân cực hồi tiếp Collector không yêu cầu R cần lớn hơn nhiều lần so với B

R như phân cực Base hay phân cực Emitơ để đảm bảo phân cực ngược của lớp tiếp giáp C

Collector và Base. Với cách mắc như hình vẽ thì phân cực hồi tiếp Collector luôn đảm bảo

transistor làm việc trong vùng tích cực với mọi giá trị điện trở của R và R . B C 2.3.2 Thông số đo đạt

Với các thông số đầu vào là E =12V

=2.2kΩ , R =1 kΩ, R =2 kΩ C , RC B E transistor 2N3711.

Thông số đo đạt được của điểm làm việc tĩnh Q là: I

I =2.68 ( mA), I =7.994 ( µA) , U =0.707 (V β ¿ C =335 C B CE IB 2.3.3 Tính toán lý thuyết

Với thông số đầu vào là E =12V , R =2.2kΩ , R =1 kΩ, R =2 kΩ transistor 2N3711 và C C B E β=335 21

Xét mạch vào: E → R → R → R C C B → U B → U E E→ GND E −I R −I −U −I =0 C C∗ C B∗RB CB E∗R E I =β I C B I =I C E Xét mạch ra: E

C → RC → U C → U E → R E →GND U =E −I −I CE C C∗RC E∗R E Thay số tính toán ta có E −U I = C CB =0.008 mA B R + β + R ) B ∗(RC B I =β =2.689 mA C ∗I B U =E −I −I =0.7062V CE C C∗RC E∗R E Q Lý thuyết Đo đạt IB(mA) 0.008 0.007994 IC (mA) 2.689 2.680 UCE (V) 0.7062 0.707

Bảng 2.4: Kết quả đo và lý thuyết mạch phân cực hồi tiếp collector 22

2.3.3 Phương trình đường tải U =E −I −I CE C C∗RC E∗R E E I max ¿ C =2.853(mA) C R R + E∗β +1 C β UCE max ¿12(V I C(A) UCE (V ) 23

2.4 Mạch phân cực phân áp

2.4.1 Cấu tạo và nguyên lý hoạt động EC 12V R1 RC 100kΩ 1kΩ + U4 4.538m A DC 1e-009Ohm - U3 + - Q1 U2 + 0.014m A 2N3711 2.911 V DC 10MOhm - R2 DC 1e-009Ohm 100kΩ RE 1kΩ

Hình 2.6: Sơ đồ mạch phân cực phân áp

Cấu tạo: Mạch có cấu tạo như hình vẽ gồm 4 điện trở một transistor 2N3711, một nguồn nuôi EC được mắc như hình.

Nguyên lý hoạt động: Mắc mạch với điện trở R1, R2 lớn hơn nhiều so với điện trở RC để đảm

bảo lớp Je phân cực ngược và BIJ làm việc tròn vùng tích cực. 2.4.2 Thông số đo đạt.

Với các thông số đầu vào E =12V

=1kΩ , R =100 kΩ, R =1 kΩ , R =1 kΩ C , RC 1 2 E transistor 2N3711.

Thông số đo đạt được của điểm làm việc tĩnh Q là:

I =4.538 (mA), I =0.014(mA) , U =2.911(V ) C B CE β=324 24 2.4.3 Tính toán lý thuyết

Biến đổi tương đương mạch phân cực phân áp theo định lý Thevenin ta có: EC 12V RC 1kΩ R th Q1 2N3711 1kΩ RE Eth 1kΩ 6V

Hình 2.7: Sơ đồ chuyển mạch Thevenin Cho U =0.7 V BE , β=324 . R R = 1∗R2 =50 kΩ th R1+ R2 E E = c∗R2 =6 V th R1+R2

Xét mạch vào: E → R → U → U → R → th th B E E Ta có: E = R +U +I th th∗I B BE E∗R E I = ( β+1 ) E ∗I C

Xét mạch ra:E → R → U → U →R →GND. C C C E E Ta có: E =I +I +U C C∗RC E∗RE CE I =β∗I C B Thay số tính toán ta có : IB=0.014(mA) IC=324∗0.014=4.536(mA) U =2.914 V CE 25

Điểm làm việc tĩnh Q theo lý thuyết tính toán và đo đạt Q Lý thuyết Đo đạt I (mA) 0.014 0.014 B IC (mA) 4.536 4.538 U (V) 2.914 2.911 CE

Bảng 2.5: Kết quả đo và lý thuyết mạch phân cực phân áp

2.4.4 Phương trình đường tải: U =E −¿ −I CE C IC∗RC E∗R E E I max ¿ C =5.991(mA) C R R + E∗β +1 C β UCE max ¿12(V 26 I (A) C UCE (V ) 27

2.5 Mạch khuếch đại mắc EC

2.5.1: Sơ đồ cấu tạo mạch EC 12V R2 RC 4kΩ 100K Ω C2 Rt 1µF 1kΩ C1 Q1 2N3711 1µF R3 100KΩ RE 1kΩ Eng 5Vrms 60Hz 0° XSC1 Ex t Tri g + _ A B + _ + _

Bảng 2.5.1: Sơ đồ mạch khuếch đại mắc EC

2.5.2: Tín hiệu vào ra mô phỏng

Với thông số đầu vào E =12V =kΩ, R =1 kΩ , R =1 kΩ C , RC B E ,

R =1 kΩ , R =R =100 kΩ, tín hiệu vào là nguồn AC E =5V transistor 2N371 t 1 2 ng 1 28

Hình 2.5.2: Tín hiệu vào ra của mạch khuếch đại măc EC 29