Preview text:

lOMoARcPSD| 36991220

ĐẠI HỌC QUỐC GIA TP. HỒ CHÍ MINH TRƯỜNG

ĐẠI HỌC BÁCH KHOA

KHOA KHOA HỌC VÀ KỸ THUẬT MÁY TÍNH BÀI THÍ NGHIỆM 1

MÔN HỌC: HỆ THỐNG SỐ

A.Checklist đầu buổi

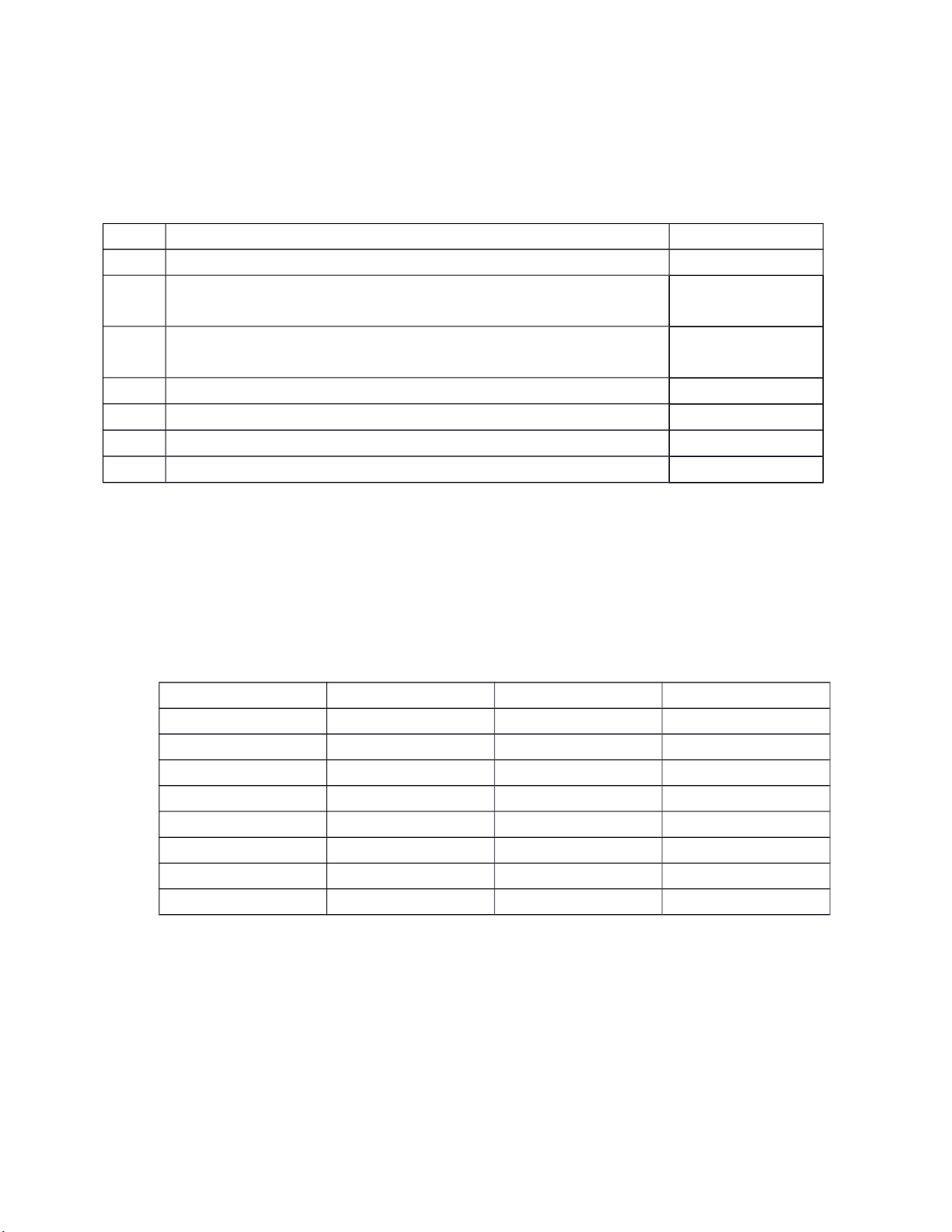

Checklist này cần được hoàn thành vào đầu buổi học ST Nội dung Hoàn thành T 1 Khu vực quanh KIT TN trống trải, gọn gàng X

KIT thí nghiệm đã chạy self-test và xác định không có 2 X dấu hiệu lỗi 3 Các inputs và outputs của KIT hoạt động bình thường 4 Đo hiệu điện thế nguồn lOMoARcPSD| 36991220 VCC của KIT đạt 5V .

B.Checklist cuối buổi

Checklist này cần được hoàn thành vào cuối buổi học STT Nội dung Hoàn thành 1

Tất cả các dây nối đã được gỡ và phân loại X

Tất cả các IC đều đã được nới lỏng trước khi nhấc ra 2 khỏi breadboard

Tất cả các IC đều đã được phân loại và trả lại đúng 3 ngăn đựng 4

Thu dọn và trả KIT thí nghiệm 5 Thu dọn và hoàn trả VOM 6

Thu dọn và hoàn trả oscilloscope (nếu có) 7 Dọn sạch khu vực làm việc Exercise 2.4.2:

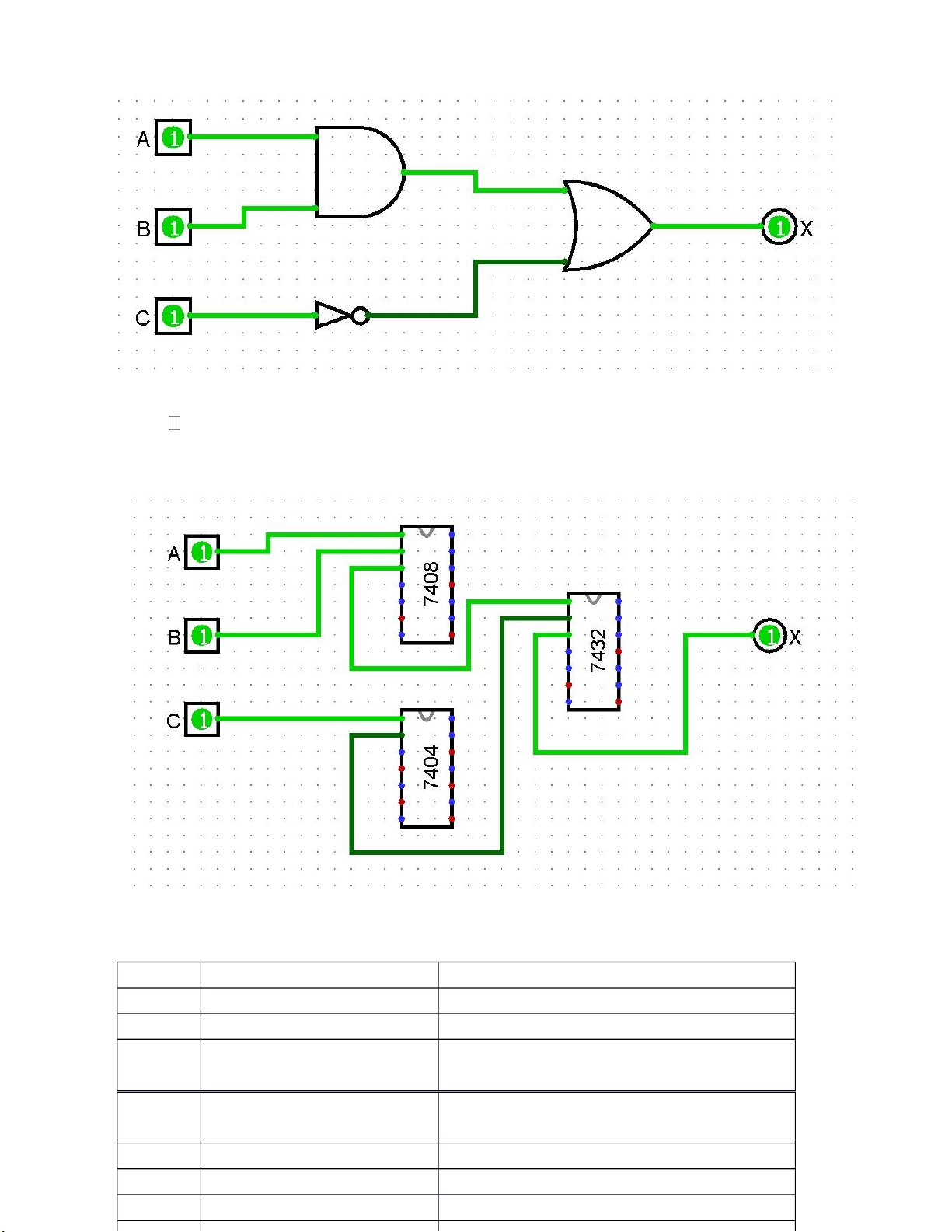

1. Phân tích và giải quyết yêu cầu của đề bài theo lý thuyết: - Inputs: A,B,C - Output: X - Bảng thực trị: A B C X = A.B+C’ 0 0 0 1 0 0 1 0 0 1 0 1 0 1 1 0 1 0 0 1 1 0 1 0 1 1 0 1 1 1 1 1

- Biểu thức logic: X= A.B+C’

2. Mô phỏng kiểm chứng thiết kế: - Sơ đồ nguyên lý: lOMoARcPSD| 36991220

Kết luận: Sơ đồ nguyên lý đúng với bảng thực trị.

3. Vẽ sơ đồ nối dây: 4. Netlist: STT Đầu thứ nhất Đầu còn lại 1 5V KTN Hàng màu đỏ breadboard 2 GND KTN Hàng màu xanh breadboard 3

Hàng màu đỏ Chân 14 của IC 7408, Chân 14 của IC breadboard 7404, Chân 14 của IC 7432 4 Hàng màu xanh

Chân 7 của IC 7408, Chân 7 của IC breadboard 7404, Chân 7 của IC 7432 lOMoARcPSD| 36991220 5 SW0 (A) Chân 1 của IC 7408 6 SW1 (B) Chân 2 của IC 7408 7 SW2 (C) Chân 1 của IC 7404 8

Chân 3 của IC 7408 Chân 1 của IC 7432 9

Chân 2 của IC 7404 Chân 2 của IC 7432 10

Chân 3 của IC 7432 LED0 (X)

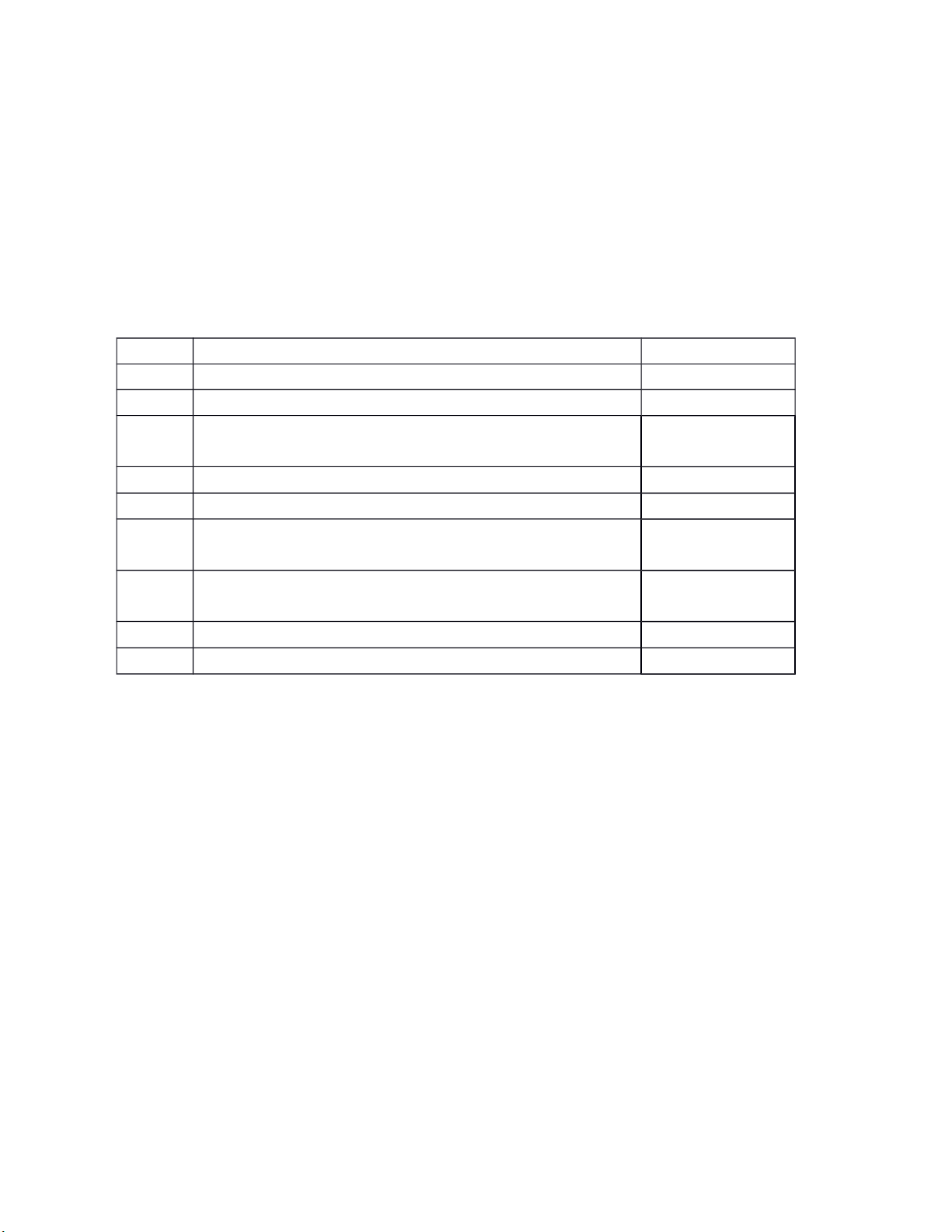

5. Checklist cho từng bài tập STT Nội dung Hoàn thành 1

KIT thí nghiệm đã tắt trước khi cắm IC X 2

Kiểm tra và nắn lại chân IC X

Các chân IC đã được đặt chuẩn xác vị trí vào các 3 lỗtrên breadboard 4

Các chân IC đã được kết nối điện với breadboard 5 Tất

cả các kết nối giữa KIT và chân IC đều tốt

VCC và GND trên KIT không bị chạm nhau 6

(không đoản mạch)

Chân CLK (nếu có dùng) không chập với 7 VCC hoặc GND 8

Hiệu điện thế giữa VCC và GND của IC đạt 5V 9

Đã test và chụp hình đủ các trường hợp