Preview text:

lOMoAR cPSD| 59691467

Phần A. Khảo sát mạch logic tổ hợp

I. Khảo sát IC cổng logic cơ bản:

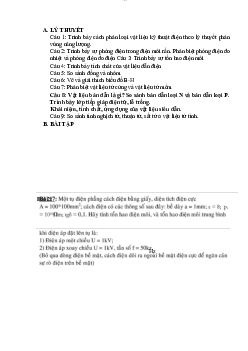

1. IC 7400- IC chứa cổng NAND: Sơ đồ chân: -Sơ đồ lắp ráp: Kết quả thực hành:

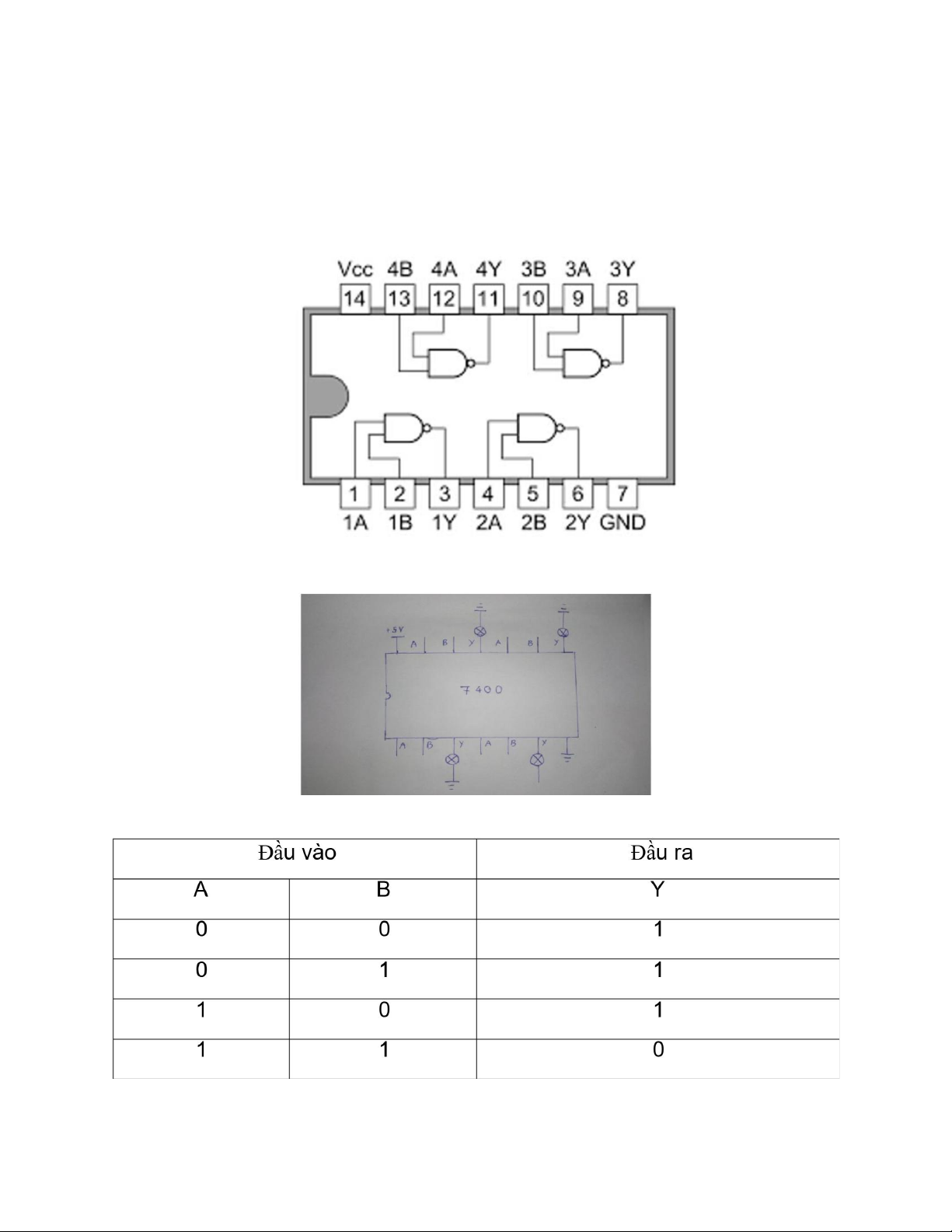

2. IC 7402- IC chứa cổng NOR-Sơ đồ chân: lOMoAR cPSD| 59691467 -Sơ đồ lắp ráp: Kết quả thực hành:

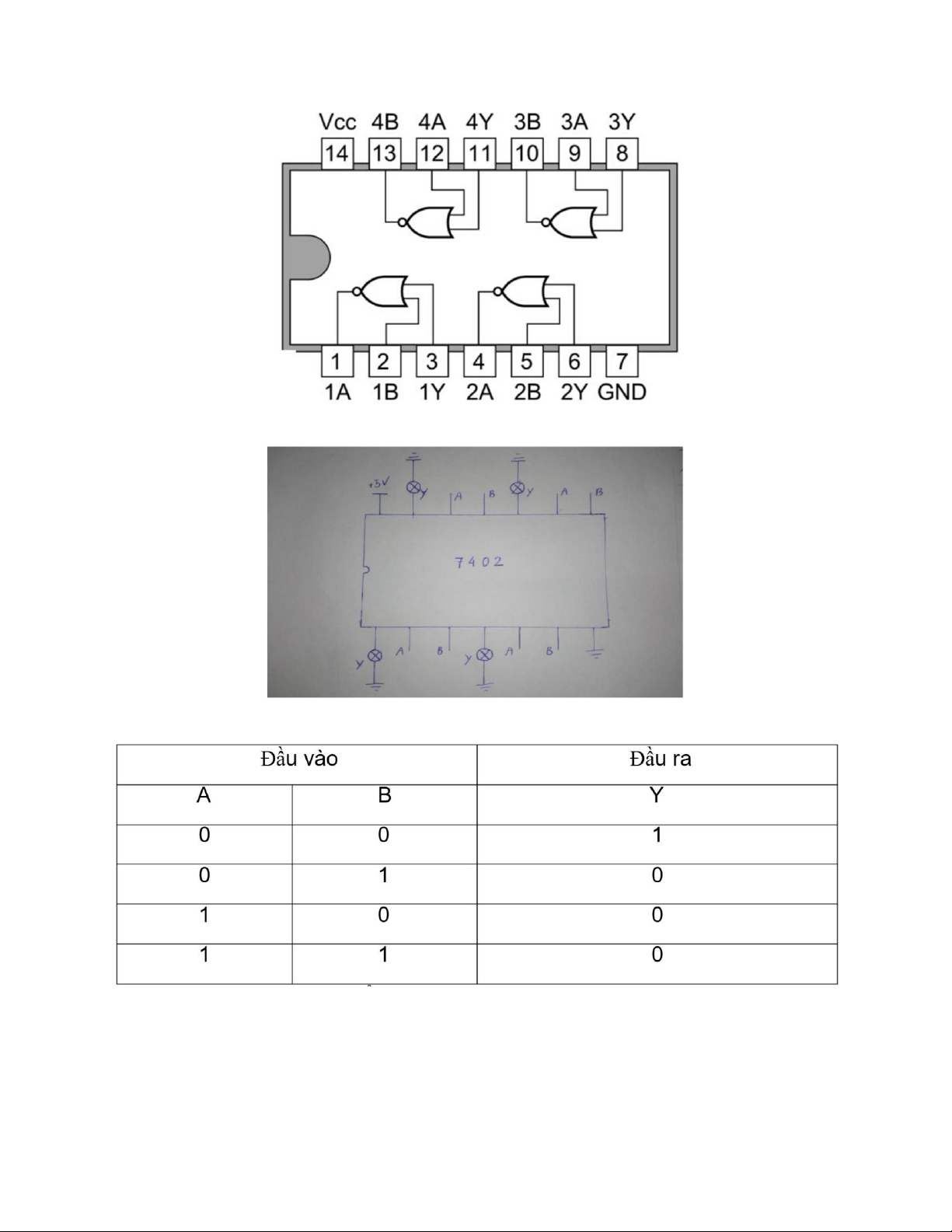

3. IC 7404- IC chứa cổng NOT-Sơ đồ chân: lOMoAR cPSD| 59691467 -Sơ đồ lắp ráp: Kết quả thực hành:

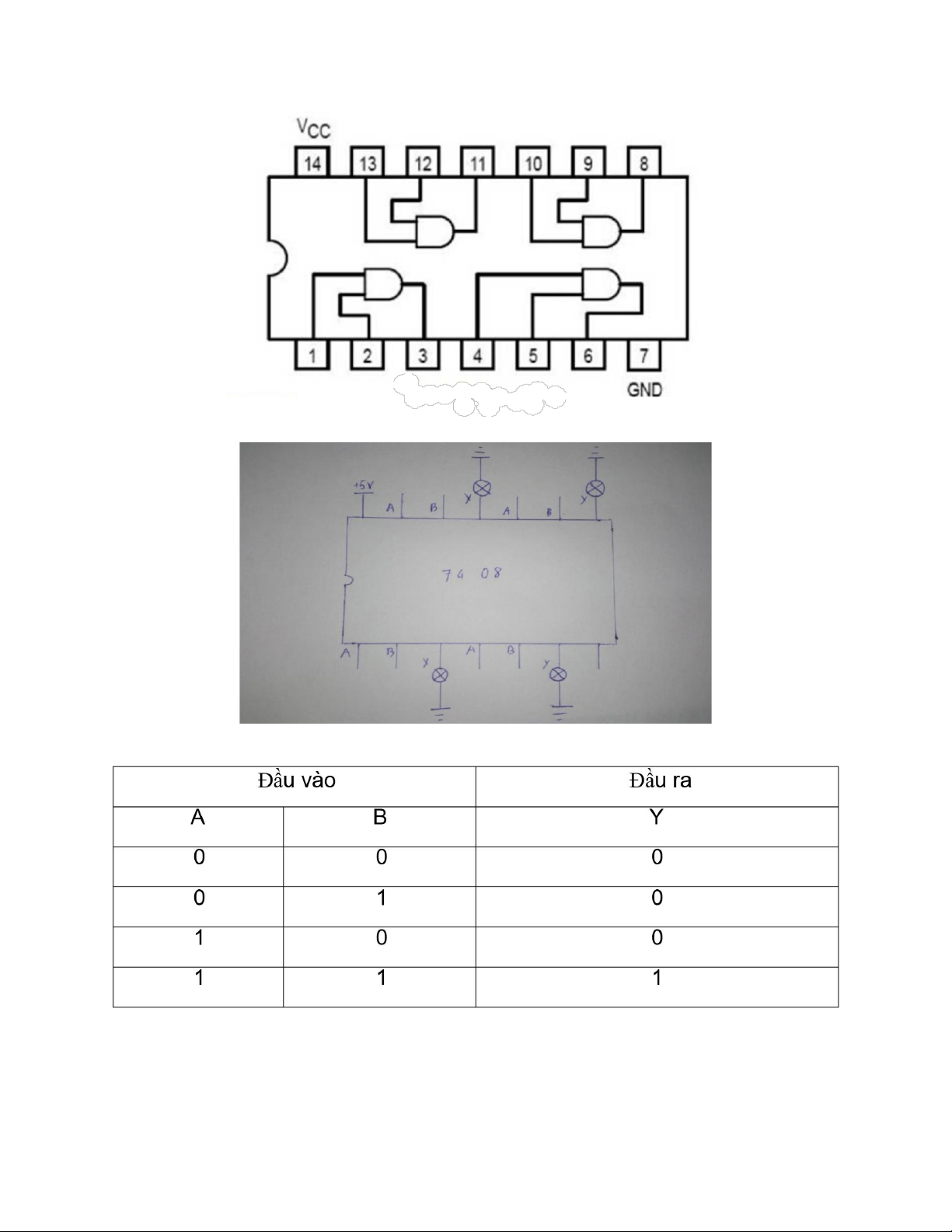

4. IC 7408- IC chứa cổng AND-Sơ đồ chân: lOMoAR cPSD| 59691467 -Sơ đồ lắp ráp: Kết quả thực hành:

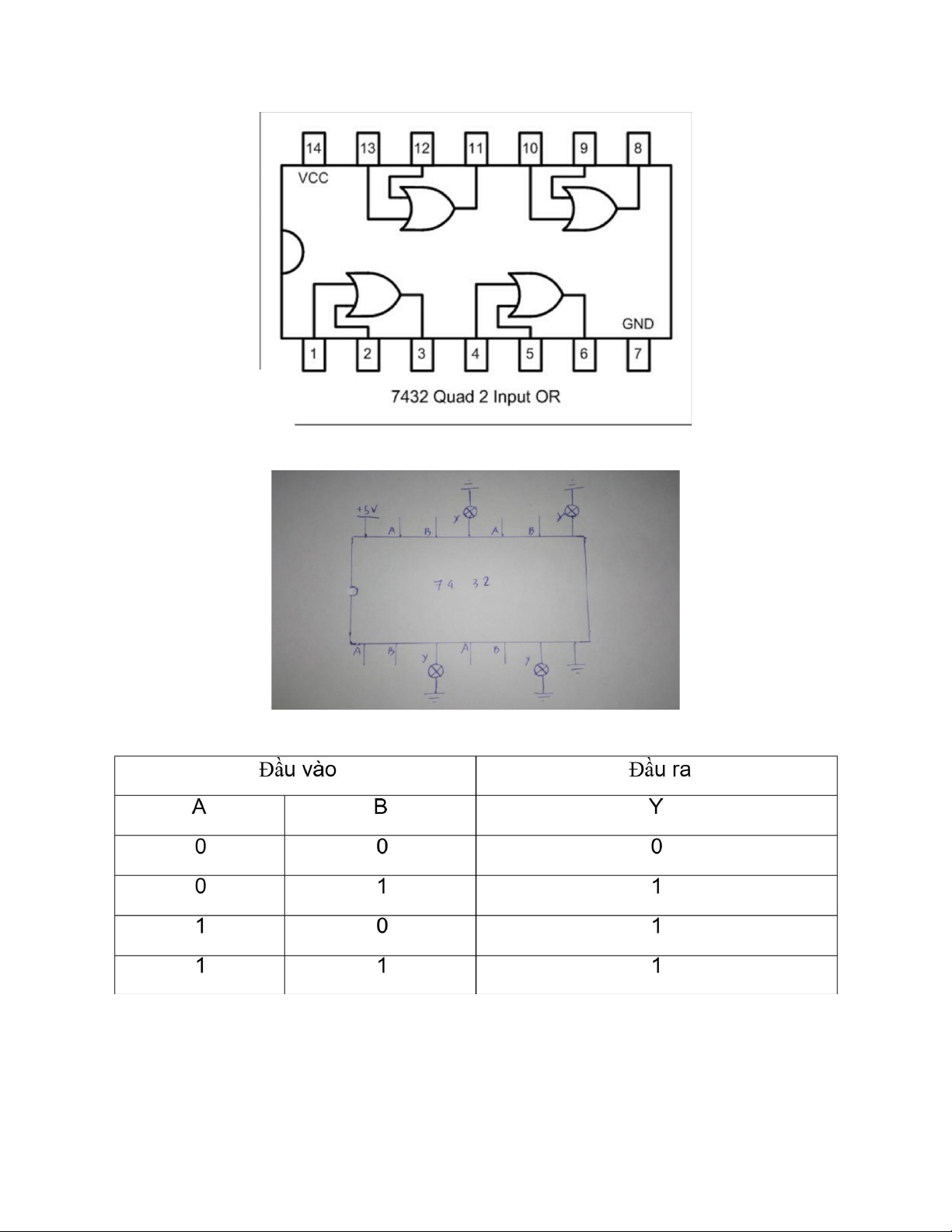

5. IC 7432- IC chứa cổng OR -Sơ đồ chân: lOMoAR cPSD| 59691467 -Sơ đồ lắp ráp: Kết quả thực hành:

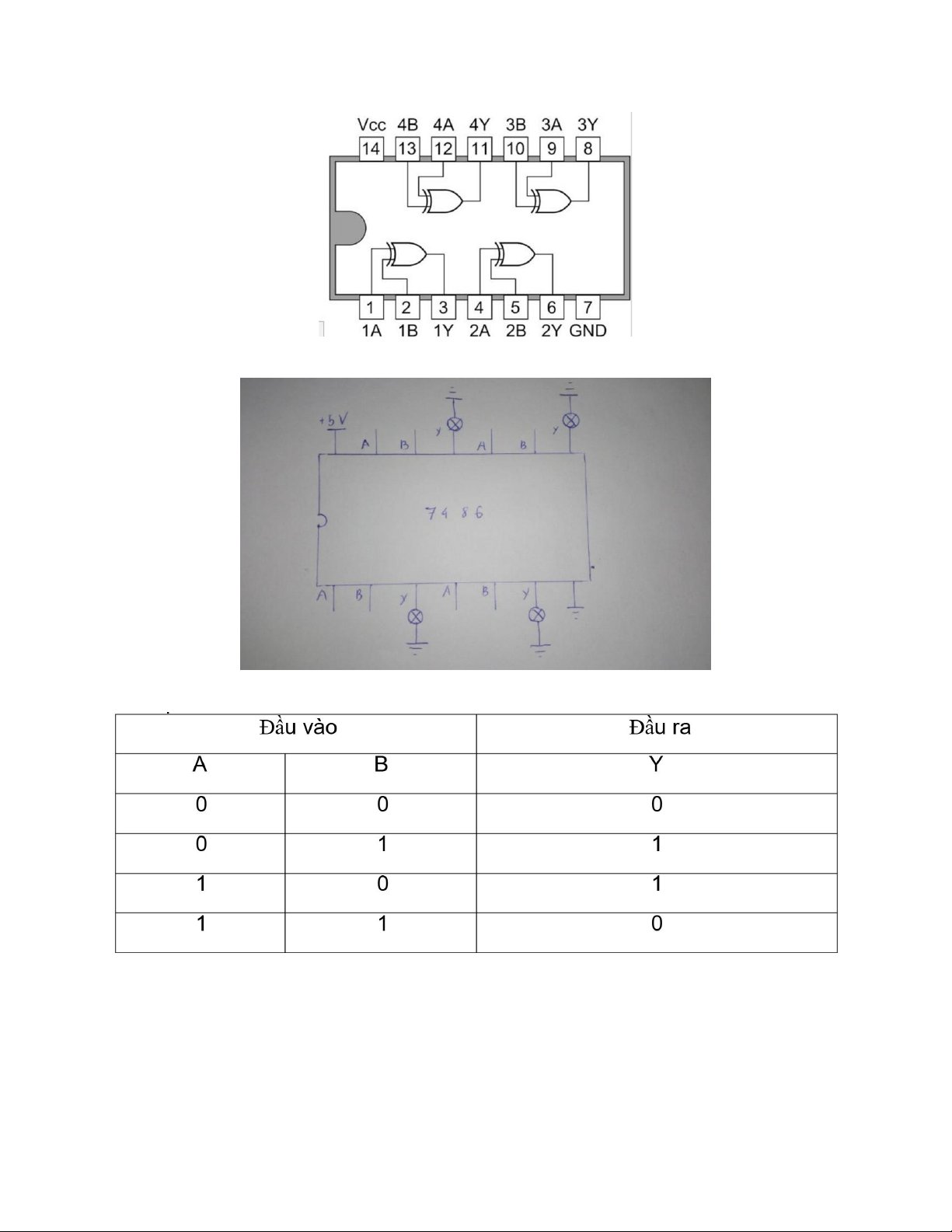

6. IC 7486- IC chứa cổng XOR -Sơ đồ chân: lOMoAR cPSD| 59691467 -Sơ đồ lắp ráp: Kết quả thực hành:

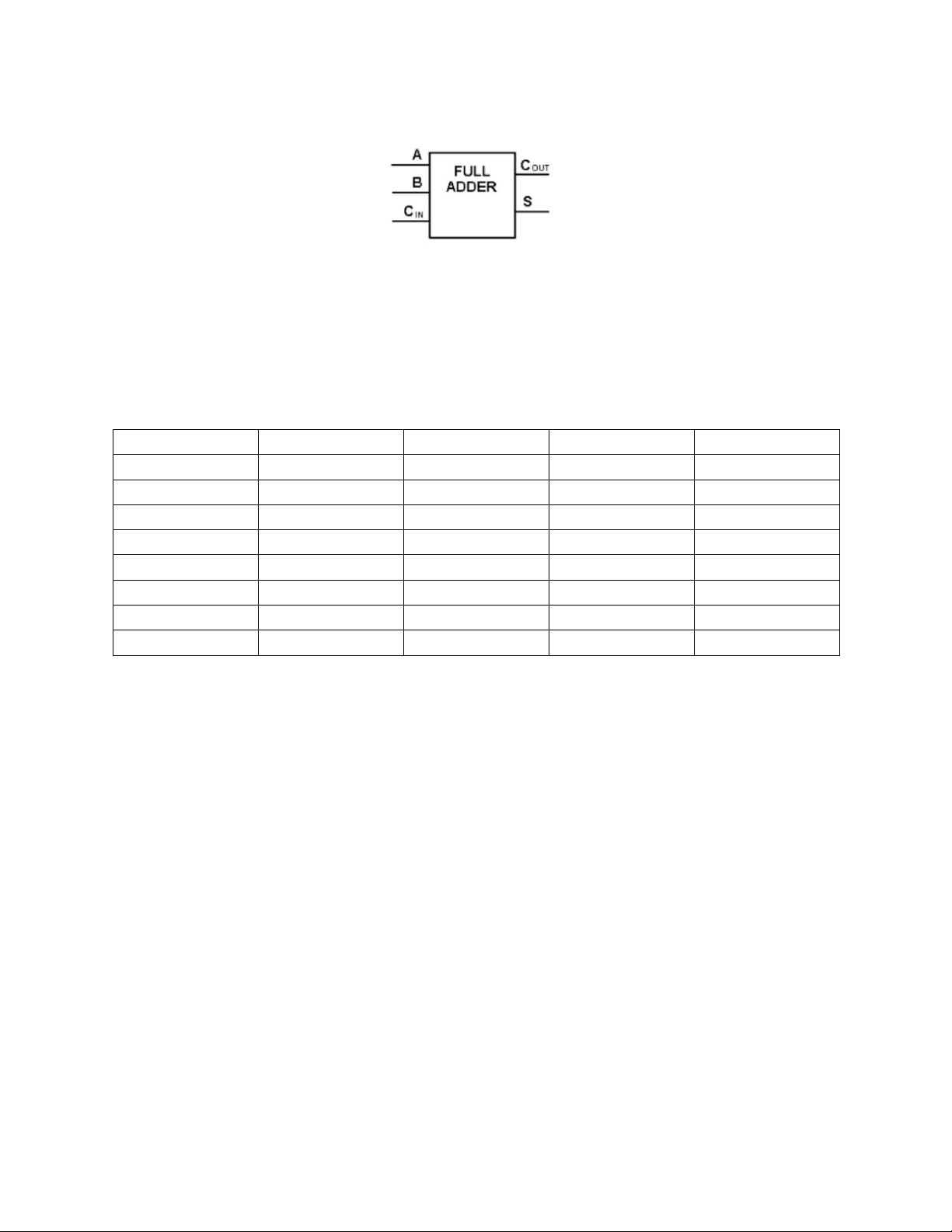

1.2 Thiết kế, lắp ráp, khảo sát mạch cộng, trừ nhị phân một bit 1.2.1 Mạch cộng một bit + Lý thuyết: lOMoAR cPSD| 59691467 Sơ đồ ký hiệu A,B : là đầu vào 1 bit

Cin: là số nhớ của cột có trọng số nhỏ hơn bên cạnh đưa đến.

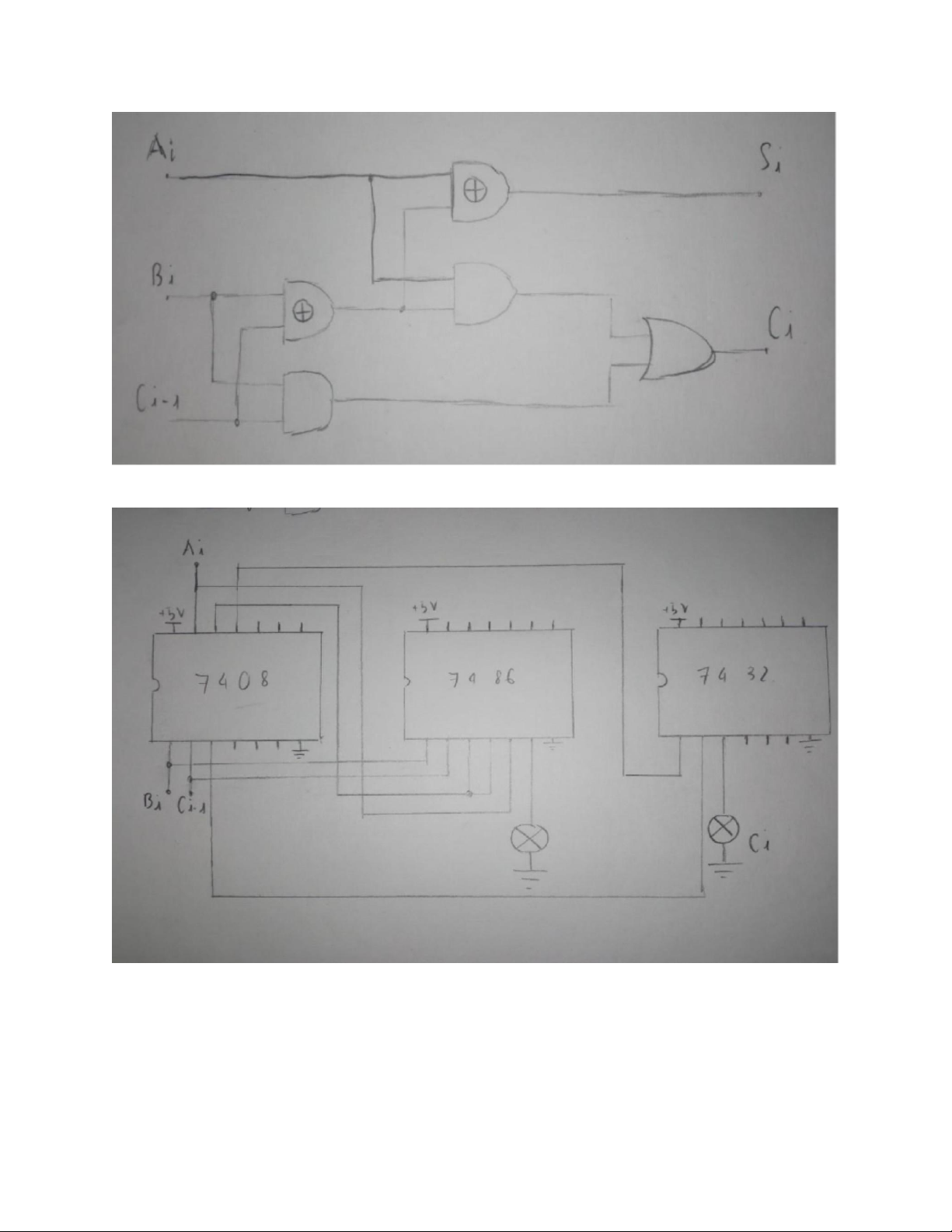

cout: là số nhớ đưa đến cột có trọng số lớn hơn bên cạnh. S: là tổng Bảng trạng thái A B CIN COUT S 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 Ta có: S=A⊕B⊕Cin Cout=AB+ACin+BCin Sơ đồ thiết kế: lOMoAR cPSD| 59691467 Sơ đồ lắp ráp:

Phân tích kết quả thực hành: Sau khi lắp ráp và khảo sát mạch thành công, mạch chạy ổn định

cho ra kết quả hiển thị qua 2 bóng led tùy theo ta thay đổi các bit đầu vào và cho kết quả ra

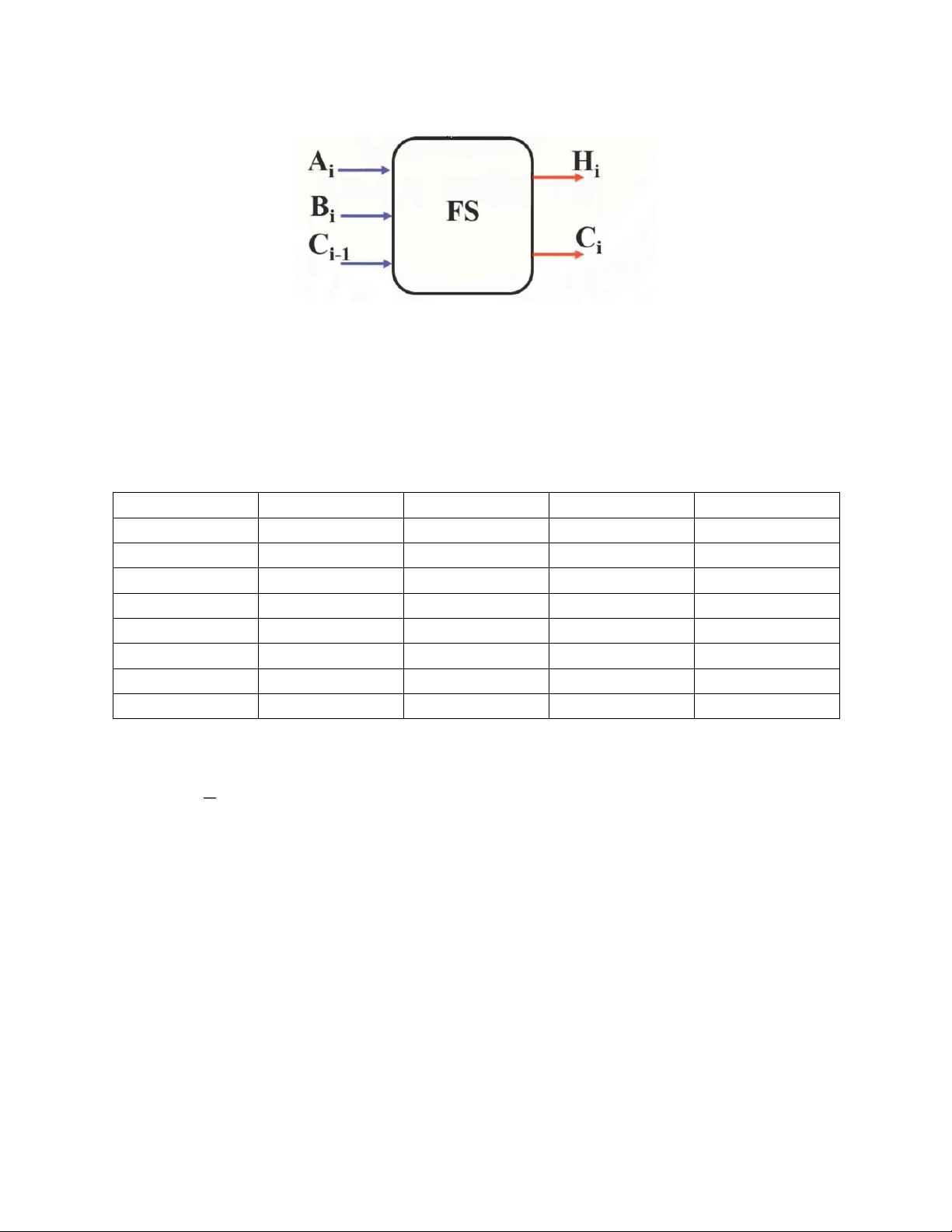

,nếu bít đầu ra là 1 thì led sáng là 0 thí led tắt 1.2.2 Mạch trừ một bit + Lý thuyết: lOMoAR cPSD| 59691467 Sơ đồ ký hiệu Ai,Bi : là đầu vào 1 bit

Ci-1: là số nhớ của cột có trọng số nhỏ hơn bên cạnh đưa đến.

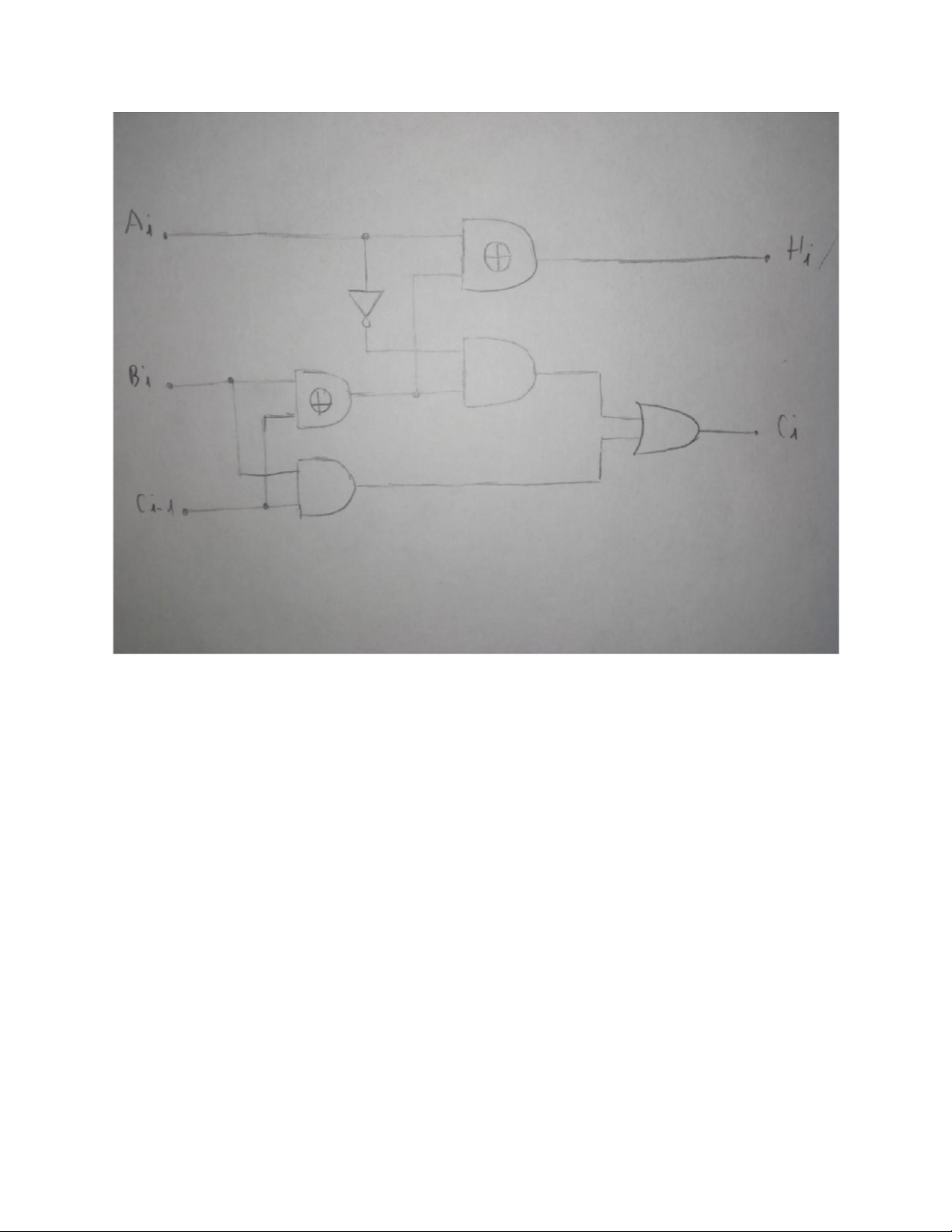

Ci: là số nhớ đưa đến cột có trọng số lớn hơn bên cạnh. H: là hiệu Bảng trạng thái Ai Bi Ci-1 H Ci 0 0 0 0 0 0 0 1 1 1 0 1 0 1 1 0 1 1 0 1 1 0 0 1 0 1 0 1 0 0 1 1 0 0 0 1 1 1 1 1 Ta có H=Ai⊕Bi⊕Ci-1

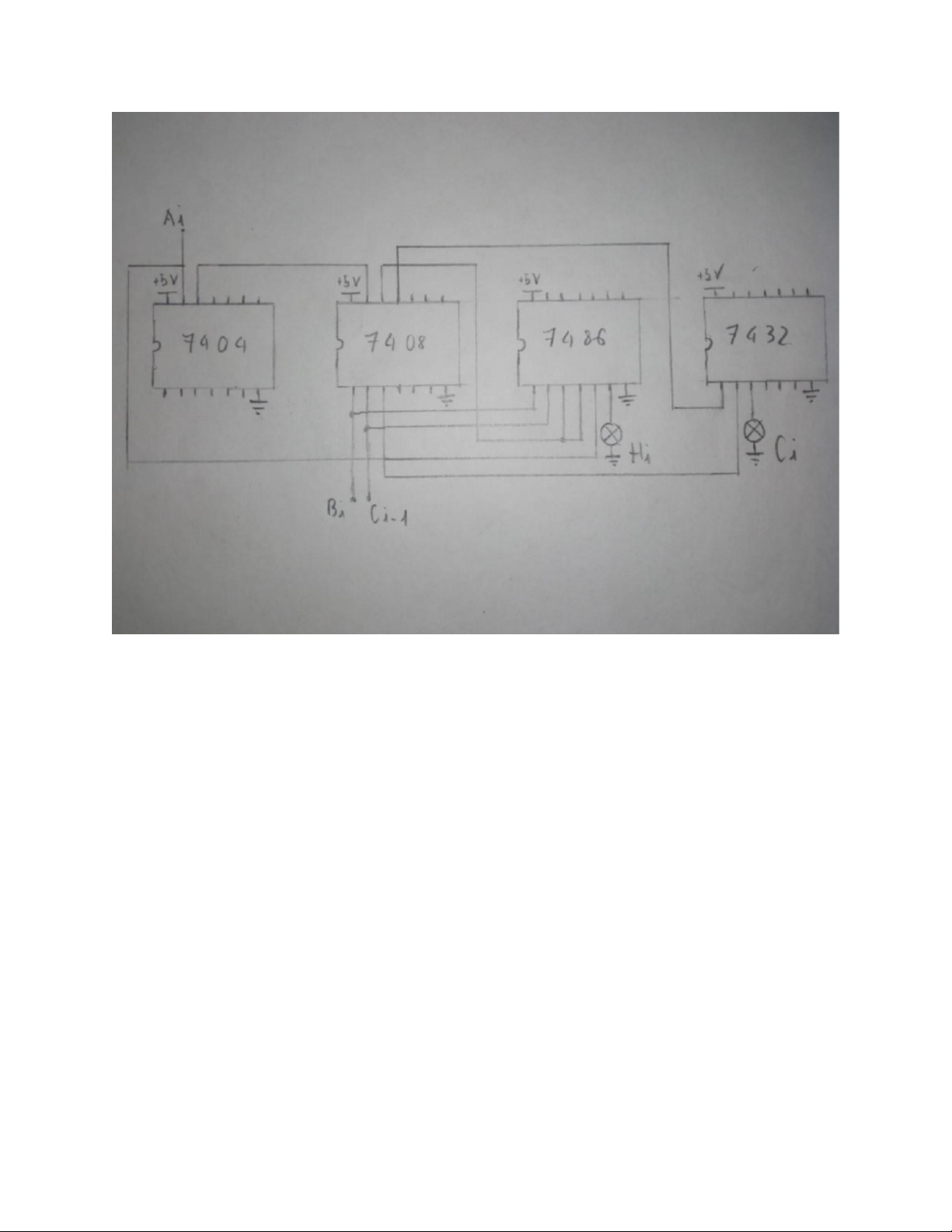

Ci= Bi Ci-1 +Ai (Bi⊕Ci-1 ) Sơ đồ thiết kế: lOMoAR cPSD| 59691467 Sơ đồ lắp ráp: lOMoAR cPSD| 59691467

Phân tích kết quả thực hành: Sau khi lắp ráp và khảo sát mạch thành công, mạch chạy ổn định

cho ra kết quả hiển thị qua 2 bóng led tùy theo ta thay đổi các bit đầu vào và cho kết quả ra

,nếu bít đầu ra là 1 thì led sáng là 0 thí led tắt chạy đúng với lí thuyết đã được học

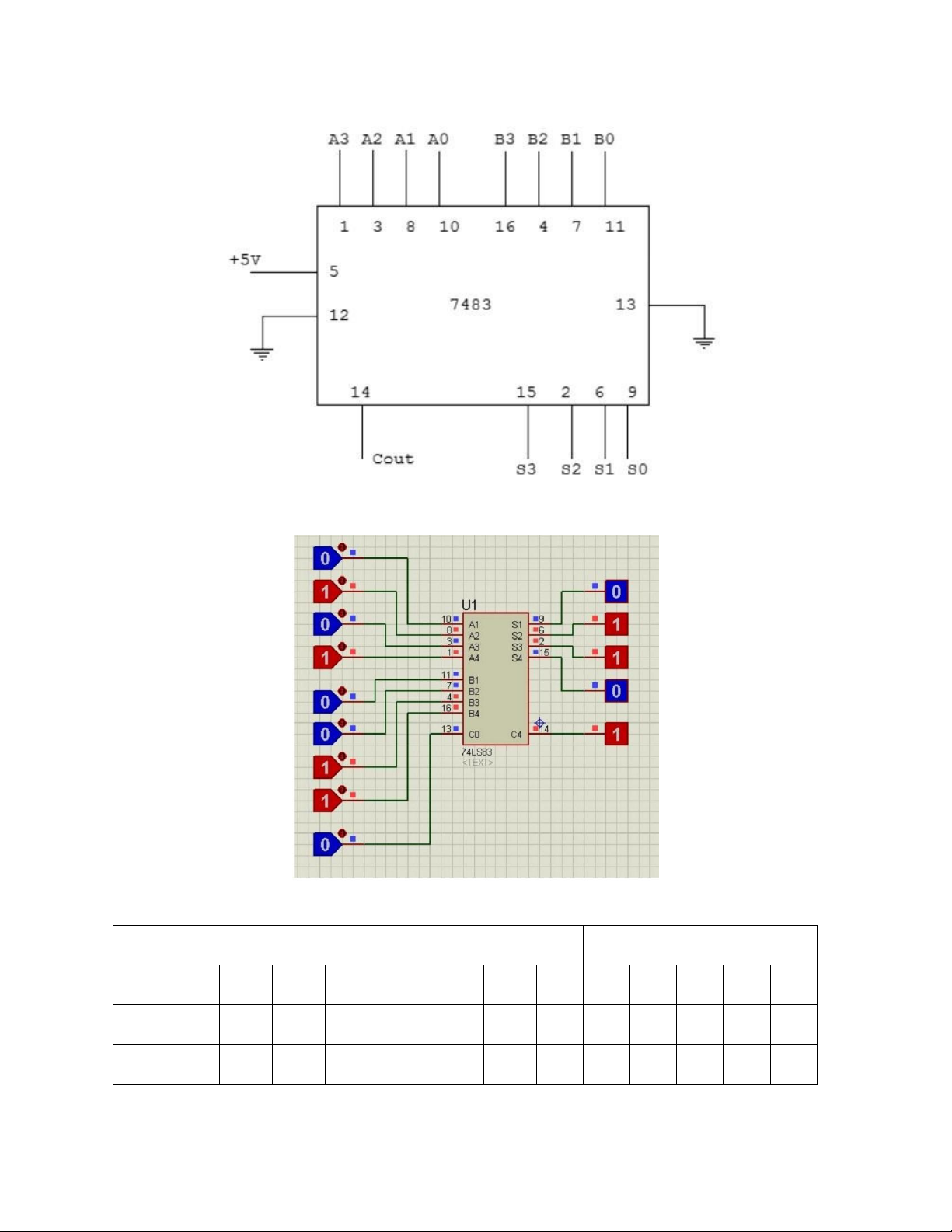

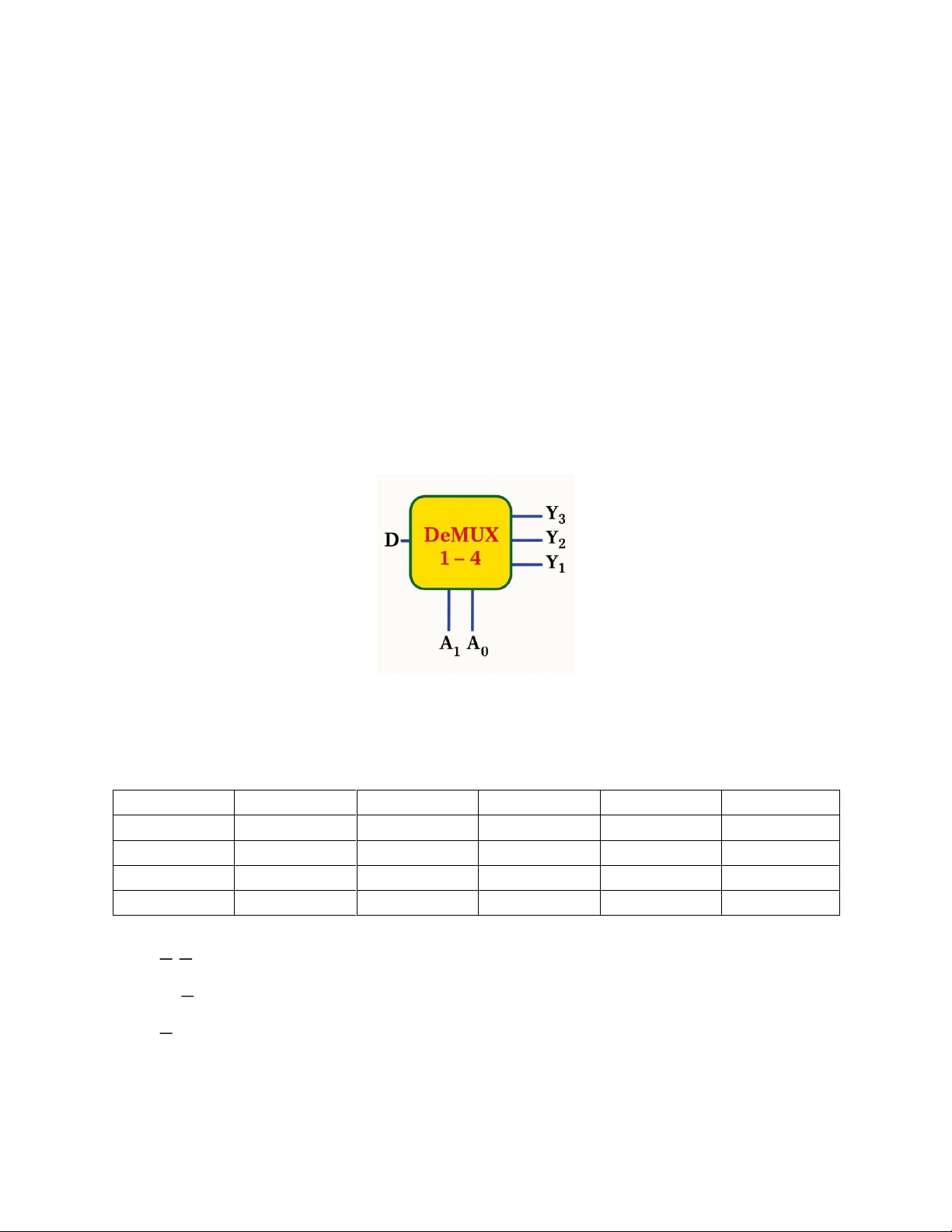

1. Mạch cộng, trừ nhị phân 4 Bit sử dụng IC 7483

1.1. Mạch cộng nhị phân 4 Bit a) Sơ đồ thiết kế lOMoAR cPSD| 59691467 b) Sơ đồ lắp ráp c) Bảng trạng thái Đầu vào Đầu ra A4 A3 A2 A1 B4 B3 B2 B1 C0 S4 S3 S2 S1 C4 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 1 0 0 lOMoAR cPSD| 59691467 0 0 1 0 0 0 0 1 0 0 0 1 1 0 0 1 0 0 0 0 1 1 0 0 1 1 1 0 0 1 1 1 0 0 0 1 0 0 0 0 0 0 1 1 1 1 0 0 0 1 0 0 0 0 0 1 1 0 1 0 0 1 0 1 1 0 0 0 0 1 d) Phương trình Si = Ai ⊕ Bi ⊕ Ci

Ci = (Ai-1.Bi-1) + (Bi-1.Ci-1) + (Ai-1.Ci-1)

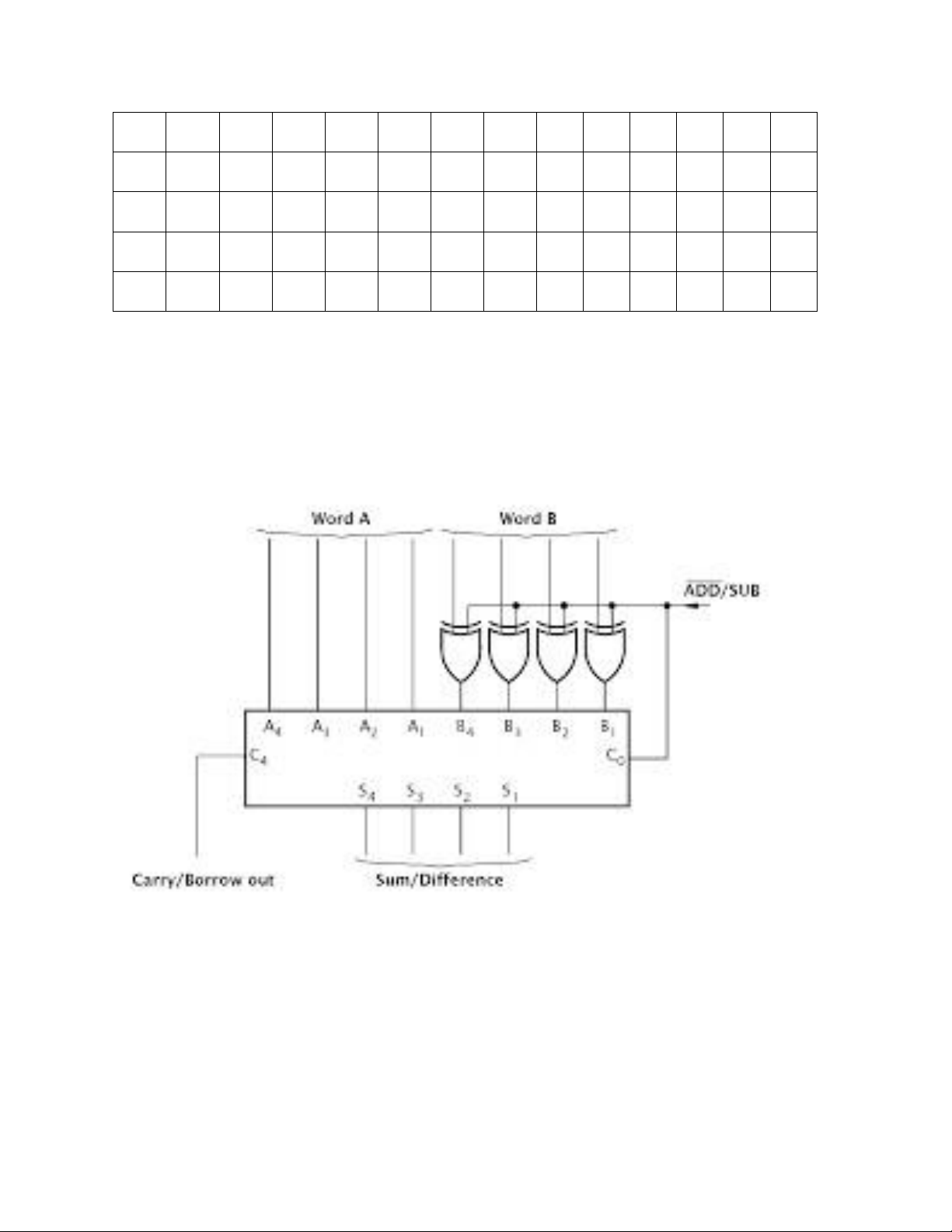

1.2. Mạch trừ nhị phân 4 Bit a) Sơ đồ thiết kế b) Sơ đồ lắp ráp lOMoAR cPSD| 59691467 c) Bảng trạng thái Đầu vào Đầu ra A4 A3 A2 A1 B4 B3 B2 B1 C0 S4 S3 S2 S1 C4 0 0 1 0 0 0 1 1 1 1 1 1 0 0 0 1 1 1 0 1 1 0 1 0 0 0 0 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 0 1 0 1 1 0 0 1 1 1 0 1 0 1 1 1 1 1 0 1 0 1 0 1 0 0 1 d) Phương trình Si = Ai ⊕B ̅ i ⊕ Ci

Ci = (Ai-1.B̅ i-1) + (B̅ i-1.Ci-1) + (Ai-1.Ci-1)

1.3. Phân tích kết quả thực hành

- Một số kết quả không đúng → do tiếp xúc không tốt giữa IC và breadboard.

- LED đầu ra mờ hoặc không sáng → do trở hạn dòng không phù hợp hoặc đứt dây. lOMoAR cPSD| 59691467

- Mạch bộ cộng 4 bit sử dụng IC 7483 hoạt động ổn định và chính xác theo lý thuyết- Có thể

mở rộng để thực hiện phép trừ bằng cách đảo B và đặt C0 = 1.

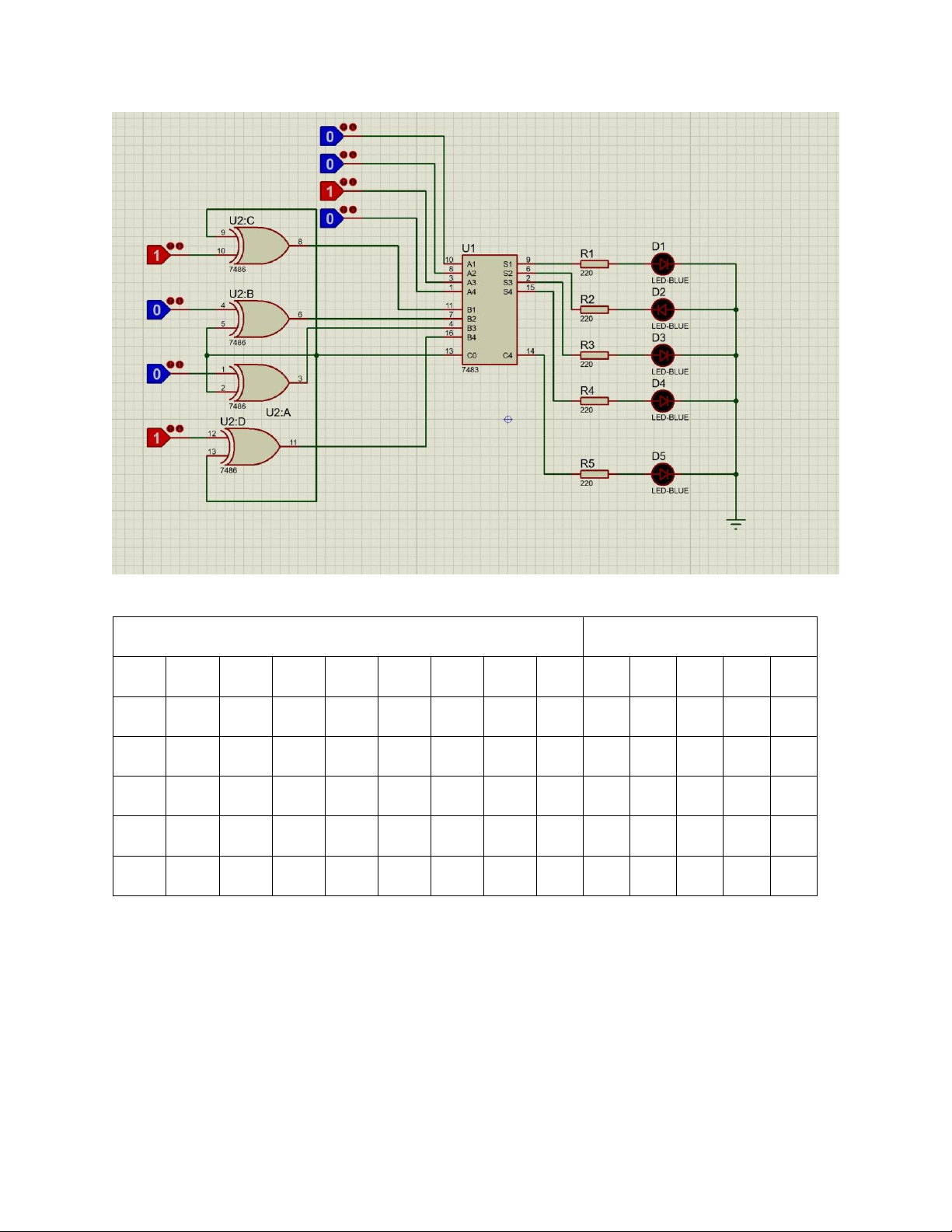

4.Thiết kế, lắp ráp, khảo sát mạch phân kênh (DEMUX 1-4), mạch hợp kênh ,(MUX 4-1) sử

dụng IC cổng logic cơ bản 4.1 Bộ phận kênh( DEMUX1-4) Lí thuyết:

Gọi s là số đâu vào chọn lựa

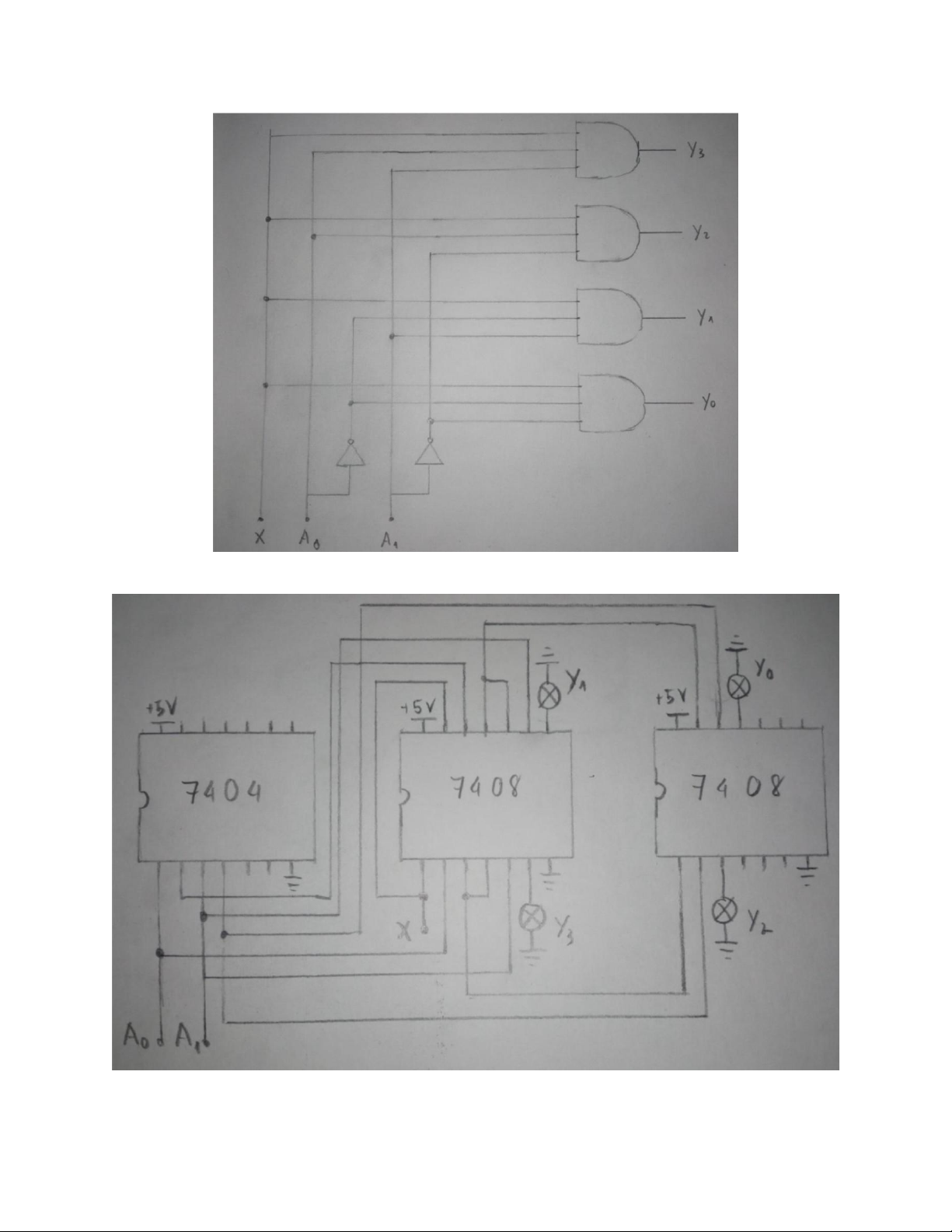

N là số đầu ra kí hiệu s≥log2 (N) DEMUX 1-2n Sơ đồ kí hiệu: Bảng trạng thái: A1 A0 Y3 Y2 Y1 Y0 0 0 X 0 0 0 0 1 0 X 0 0 1 0 0 0 X 0 1 1 0 0 0 X Ta có: Y0=XA0 A1 Y1=X A0 A1 Y2=XA0 A1 Y3=XA0 A1 Sơ đồ thiết kế: lOMoAR cPSD| 59691467 Sơ đồ lắp ráp: lOMoAR cPSD| 59691467

Phân tích kết quả thực hành: Sau khi lắp ráp và khảo sát mạch thành công, mạch chạy ổn định

cho ra kết quả hiển thị qua các bóng led ta thay đổi A0 A1 mạch chạy đúng theo bảng trạng thái

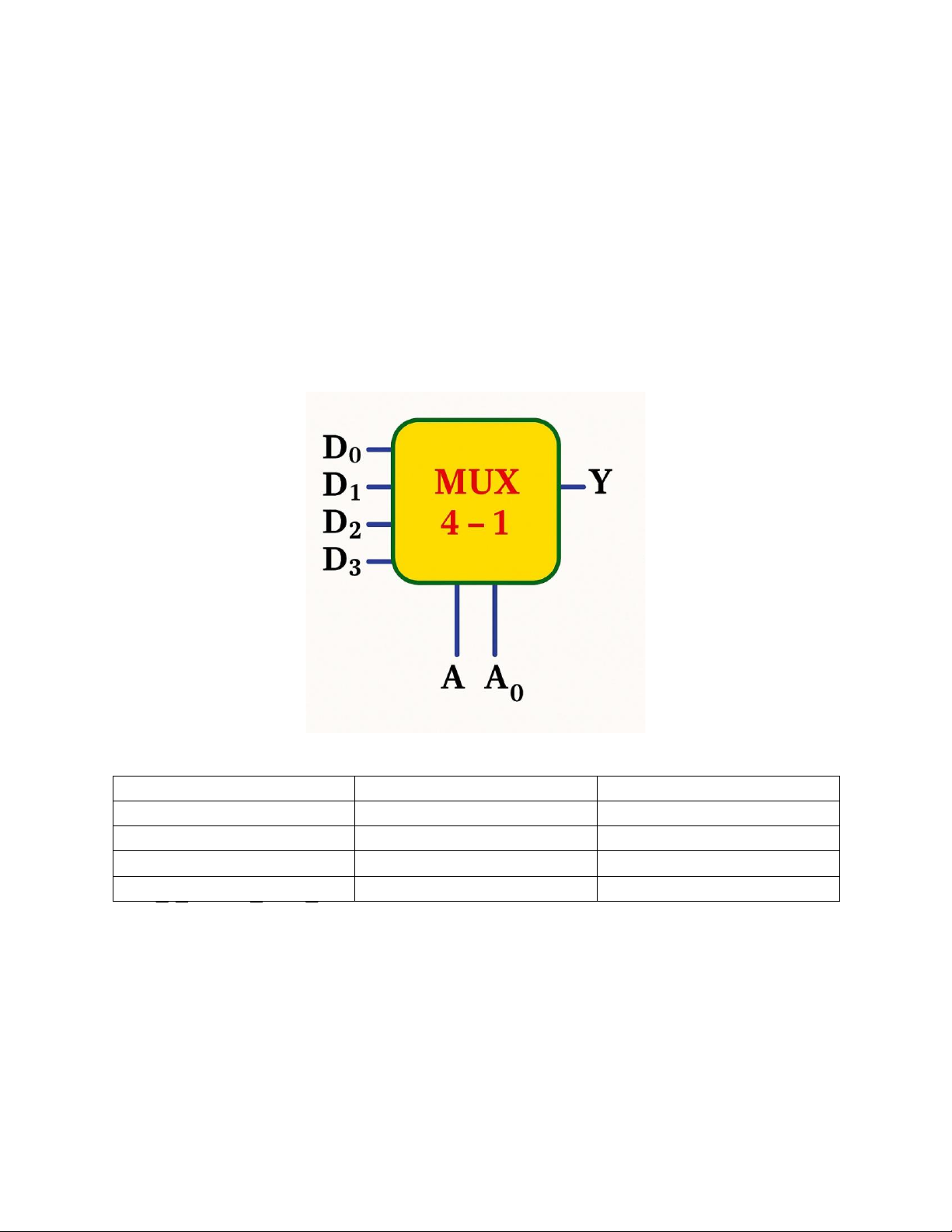

4.2 Bộ mã hóa (MUX 4-1) Lí thuyết:

Gọi s là số đâu vào chọn lựa

N là số đầu ra kí hiệu s≥log2 (N) MUX 2n-1 Sơ đồ kí hiệu: Bảng trạng thái: A1 A0 Y 0 0 X0 0 1 X1 1 0 X2 1 1 X3

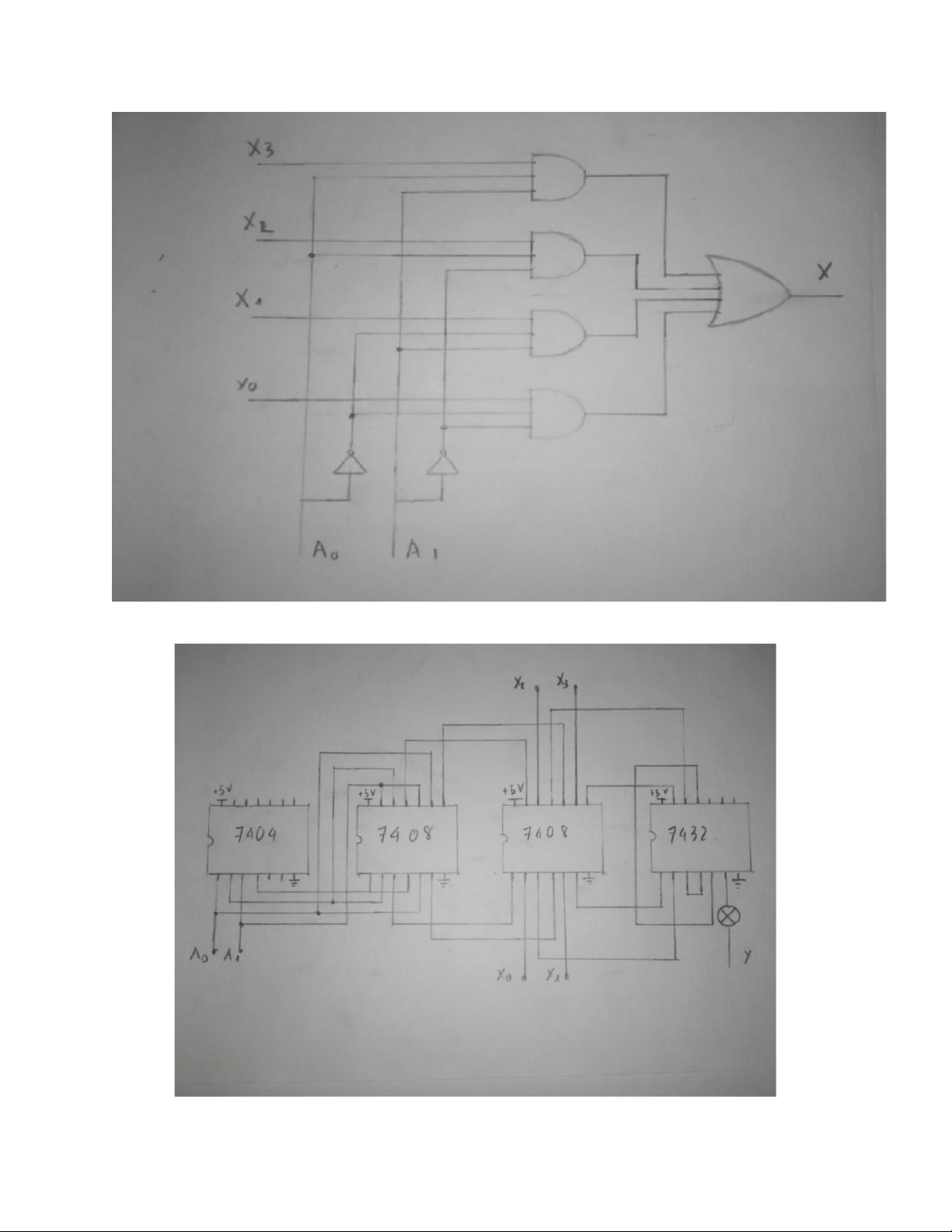

Y=X0 A0 A1 +X1 A0 A1 +X2A0 A1+X3A0 A1 Sơ đồ thiết kế: lOMoAR cPSD| 59691467 Sơ đồ lắp ráp: lOMoAR cPSD| 59691467

Phân tích kết quả thực hành: Sau khi lắp ráp và khảo sát mạch thành công, mạch chạy ổn định

cho ra kết quả hiển thị qua các bóng led ta thay đổi A0 A1 mạch chạy đúng theo bảng trạng thái

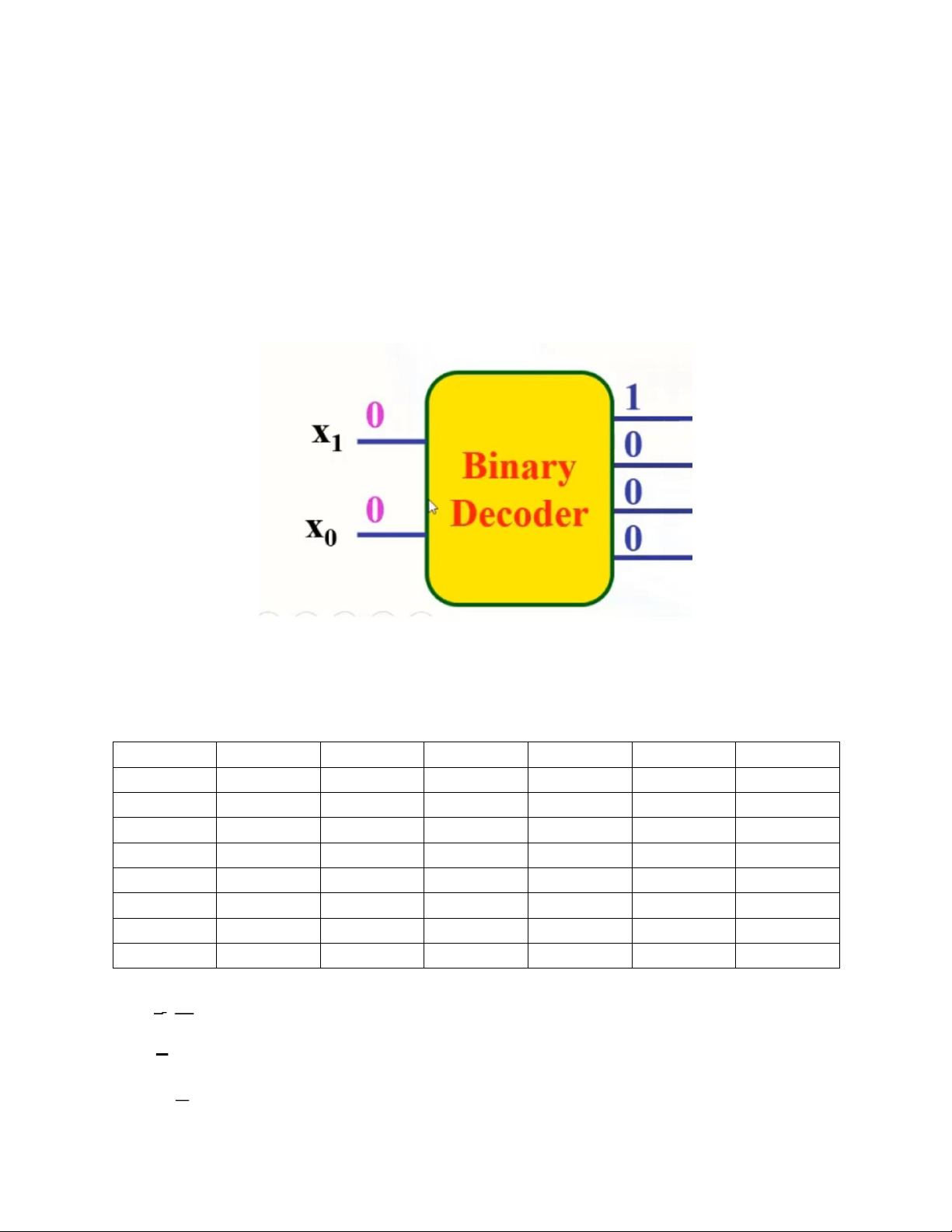

5.Thiết kế, lắp ráp, khảo sát mạch giải mã (DECODER 2-4), mã hóa (ENCODER 4-2) sử dụng IC cổng logic cơ bản.

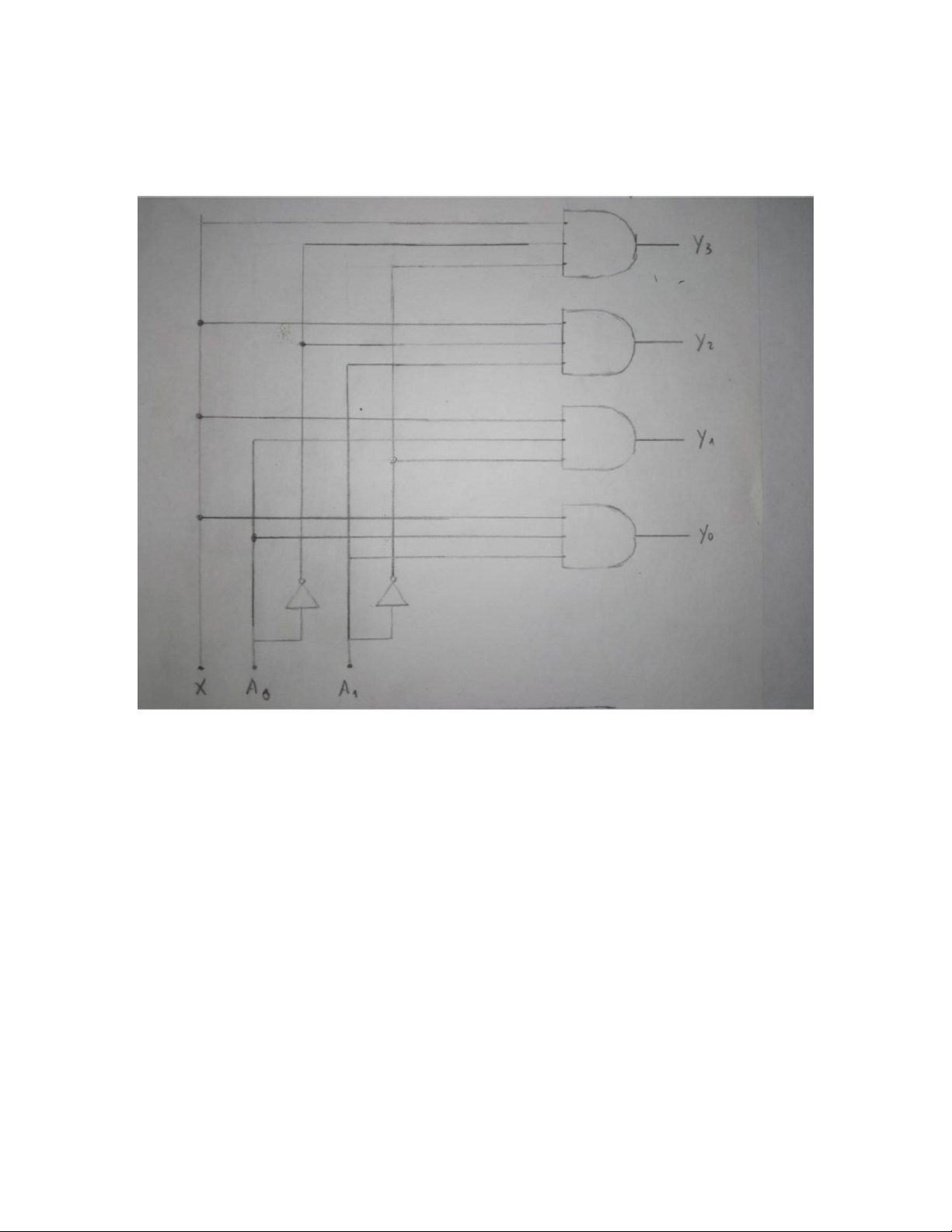

5.1. mạch giải mã (DECODER 2-4) Sơ đồ kí hiệu: Bảng trạng thái: X A0 A1 Y0 Y1 Y2 Y3 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 0 1 1 0 0 0 0 1 0 0 X 0 0 0 1 0 1 0 X 0 0 1 1 0 0 0 X 0 1 1 1 0 0 0 X Ta có: Y0=AA0A1 Y1=AA0A1 lOMoAR cPSD| 59691467 Y2=AA0A1 Y3=AA0A1 Sơ đồ thiết kế: Sơ đồ lắp ráp: