Preview text:

1 Computer Evolution & Designing for Performance CHAPTER 01 2 Contents

An overview of the evolution of computer technology. Von Neuman (IAS) machine.

Understand the key performance issues relating to computer design.

Present an overview of the evolution of the x86 architecture.

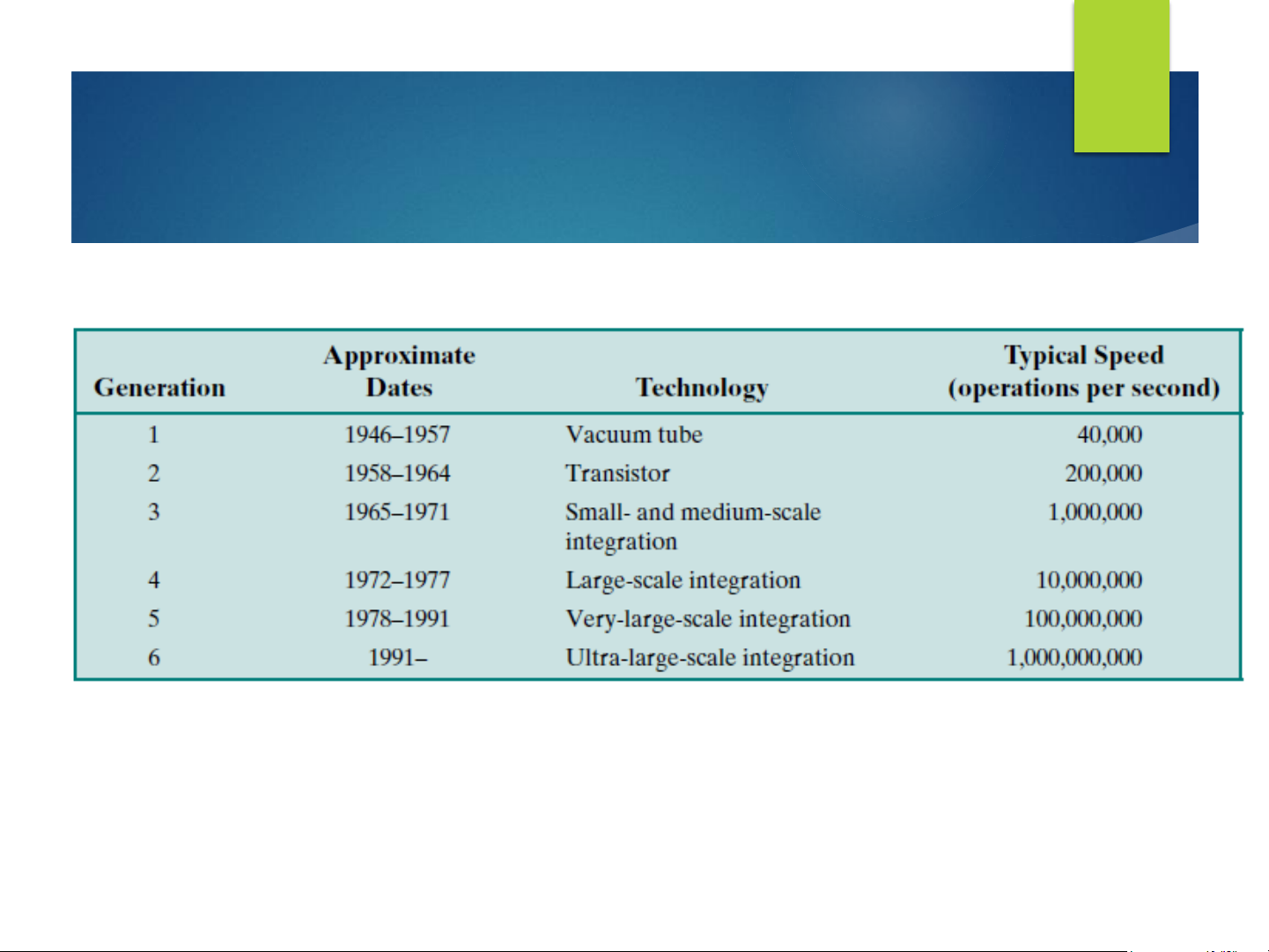

The issues in computer performance assessment. 3 Evolution of • The generations of computer Computer • Evolution of Intel processors Technology 4 The First Generation Vacuum tube

The ENIAC (Electronic Numerical Integrator And Computer),

designed and constructed at the University of Pennsylvania:

The world’s first general purpose electronic digital computer.

Weighing 30 tons, occupying 1500 square feet of floor space,

and containing more than 18,000 vacuum tubes. When

operating, it consumed 140 kilowatts of power. It was capable of 5000 additions per second.

The major drawback of the ENIAC was that it had to be programmed

manually by setting switches, plugging and unplugging cables 5 The First Generation

The VON NEUMANN MACHINE:

In 1946, von Neumann and his colleagues began the design

of a new stored-program computer, referred to as the IAS

computer, at the Princeton Institute for Advanced Studies.

Although not completed until 1952, is the prototype of all

subsequent general-purpose computers. 6 The First Generation

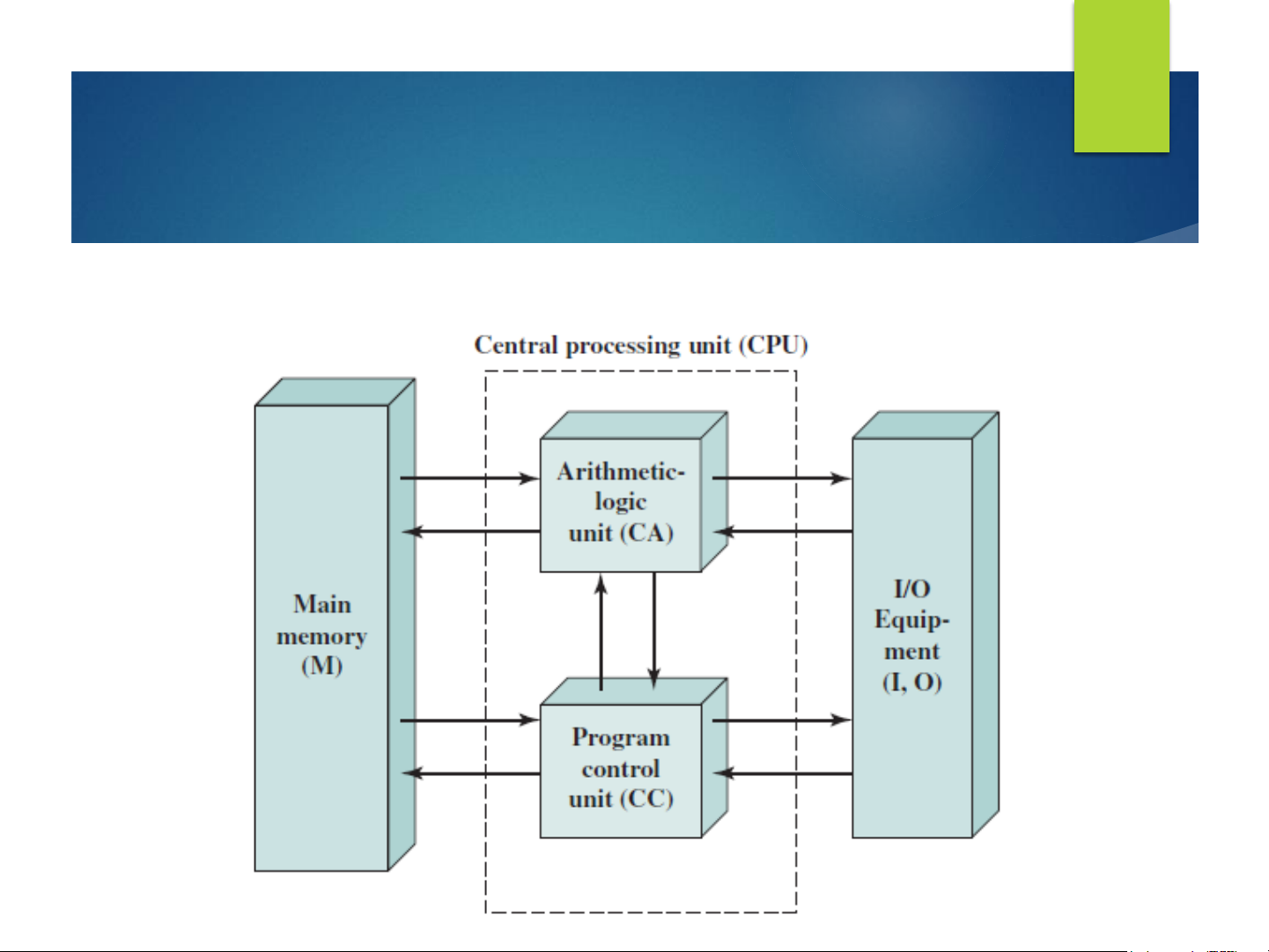

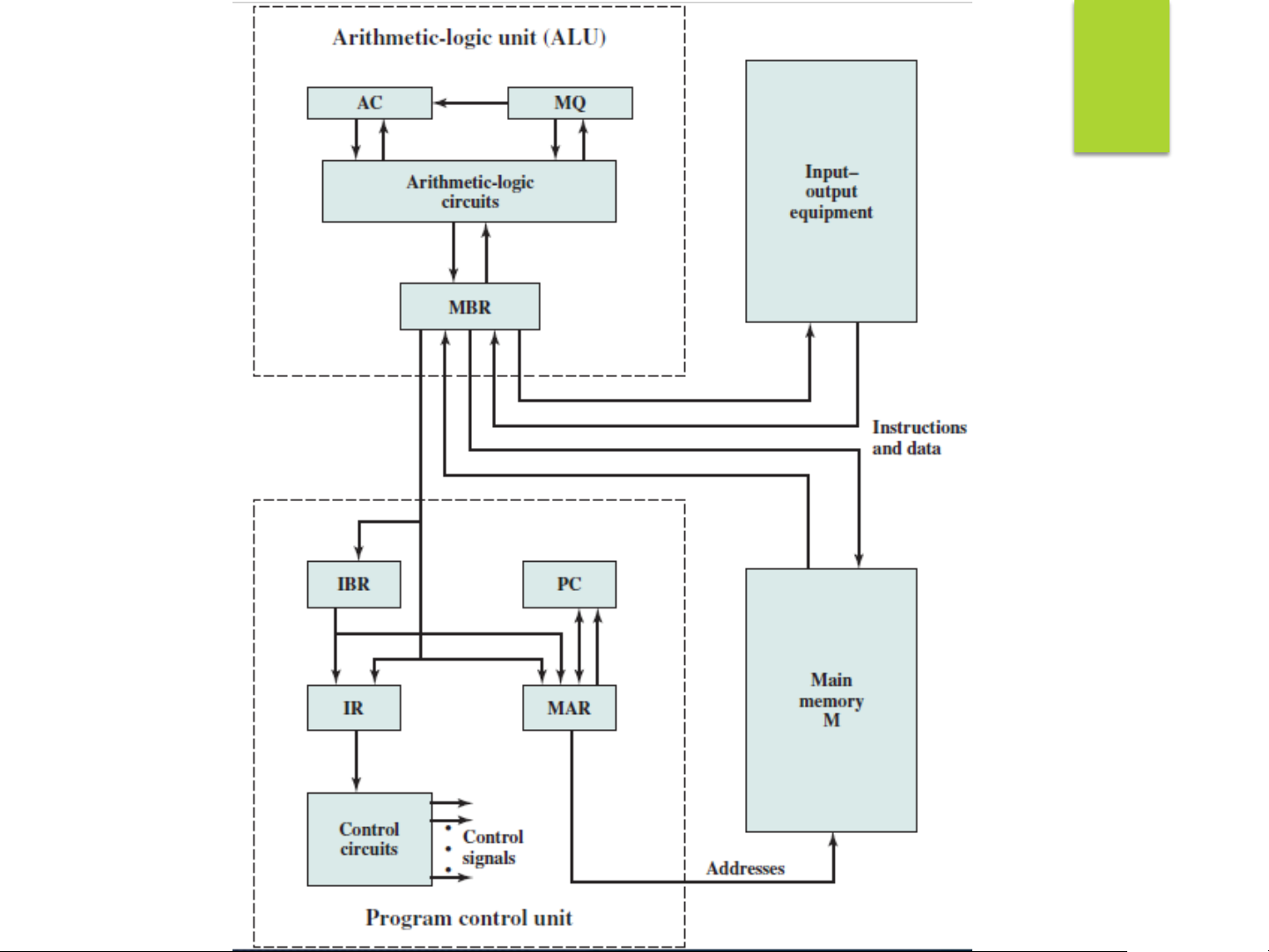

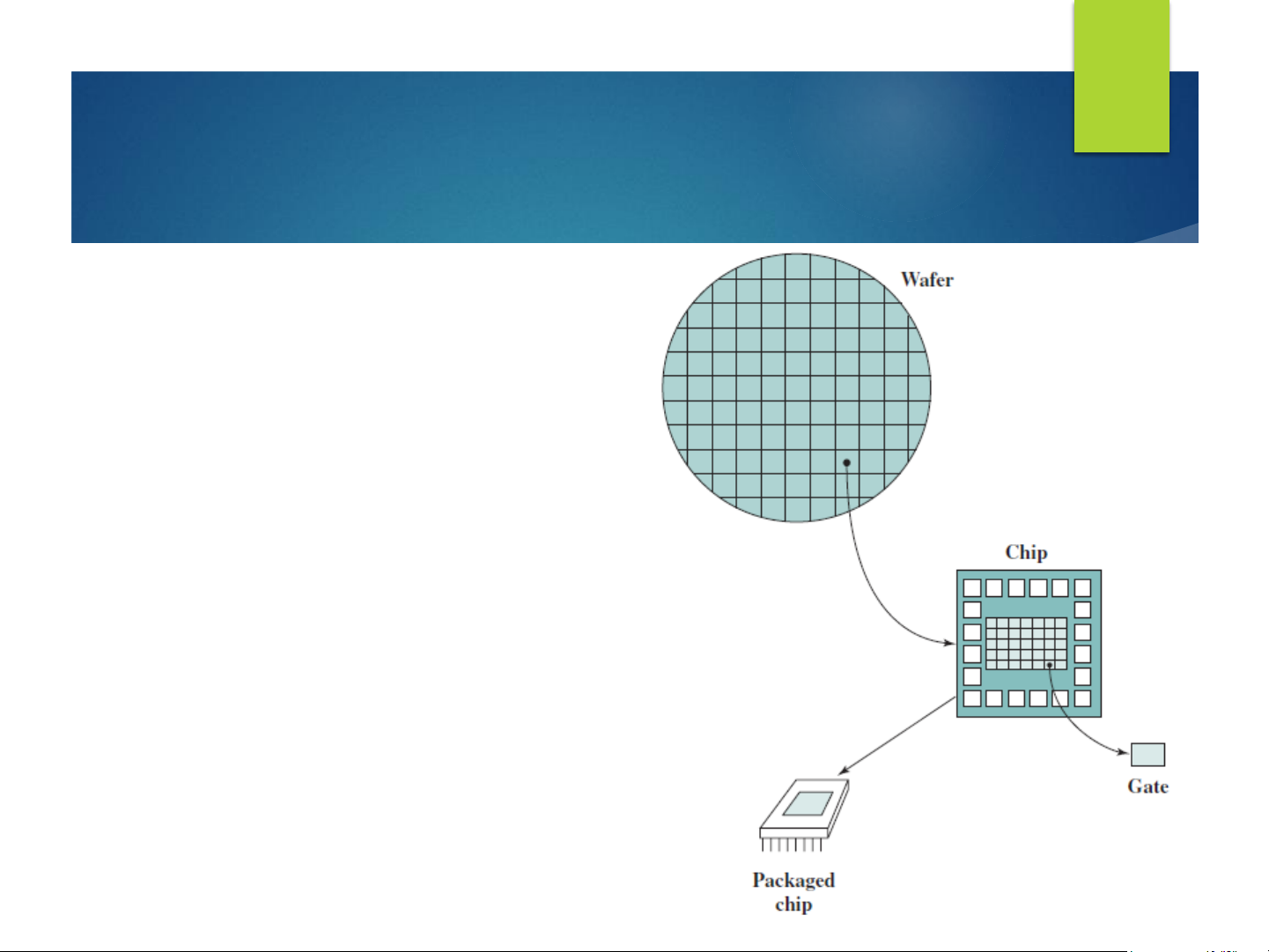

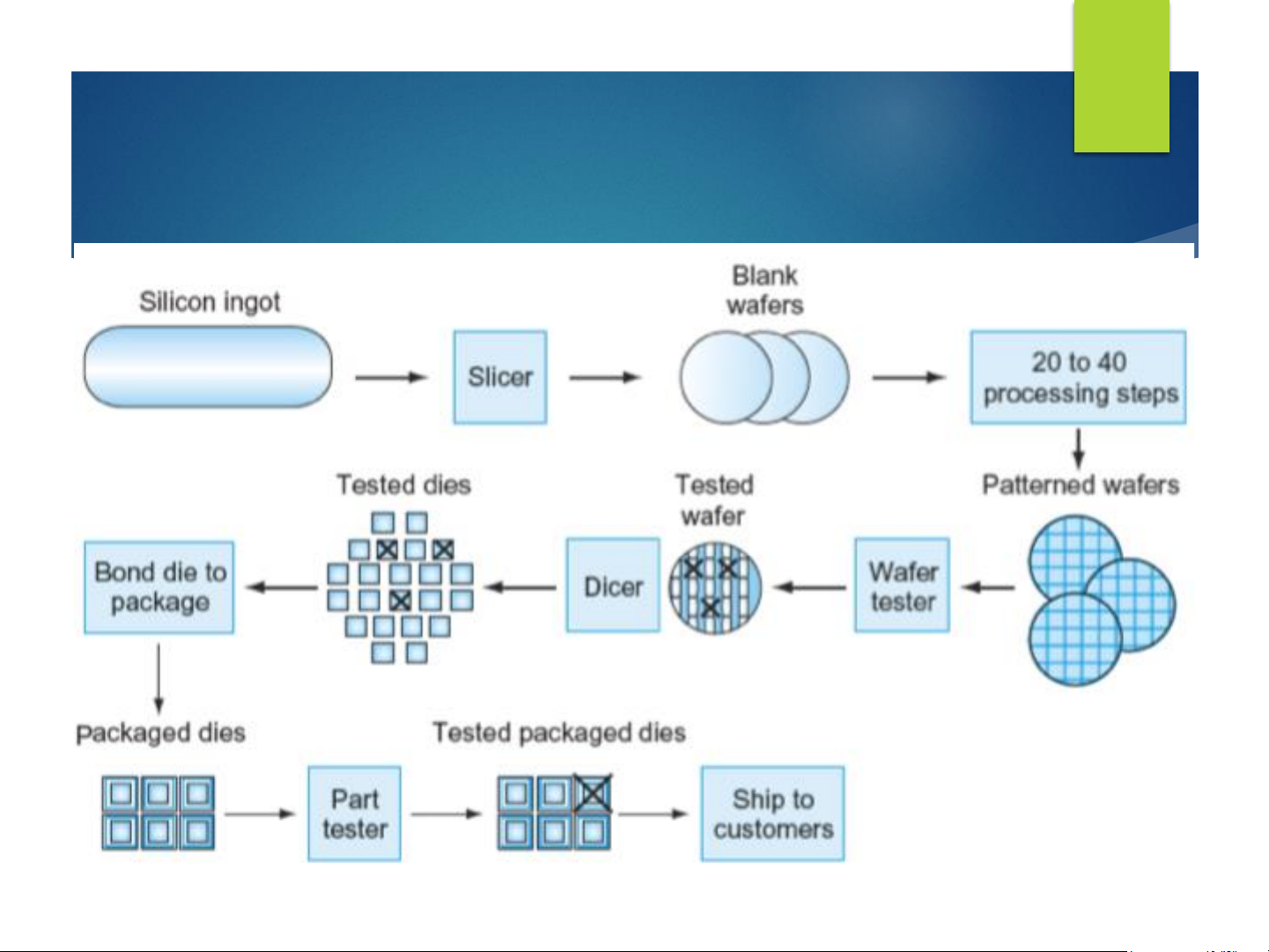

The Structure of IAS computer: 7 The IAS memory structure

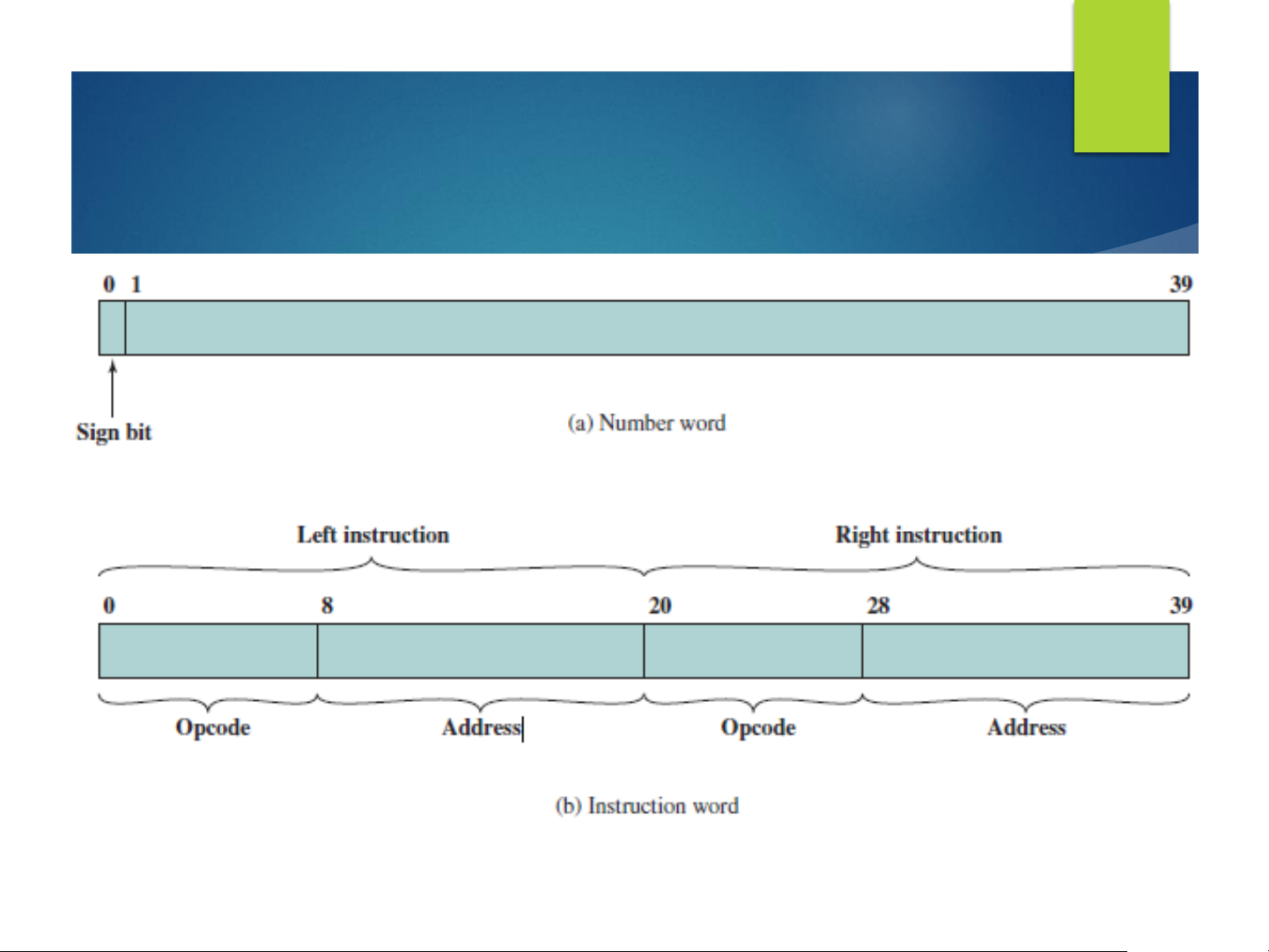

The memory of the IAS consists of 1000 storage locations,

called words (40 bits) each for both data and instructions.

Each instruction is a binary code. Each number is represented

by a sign bit and a 39-bit value.

A word may also contain two 20-bit instructions, with each

instruction consisting of an 8-bit operation code (opcode)

specifying the operation to be performed and a 12-bit

address designating one of the words in memory (numbered from 0 to 999).

The control unit operates the IAS by fetching instructions from

memory and executing them one at a time. 8 9 The IAS memory formats 10 The IAS registers

The control unit operates the IAS by fetching instructions from

memory and executing them one at a time

Both the control unit and the ALU contain storage locations, called registers, 11 The IAS registers

Memory buffer register (MBR): word to be stored in memory or

sent to the I/O unit, or is used to receive a word from memory or from the I/O unit.

Memory address register (MAR): Specifies the address in memory

of the word to be written from or read into the MBR.

Instruction register (IR): Contains the 8-bit opcode instruction being executed.

Instruction buffer register (IBR): Employed to hold temporarily the

right-hand instruction from a word in memory.

Program counter (PC): Contains the address of the next

instruction pair to be fetched from memory.

Accumulator (AC) and multiplier quotient (MQ): 12

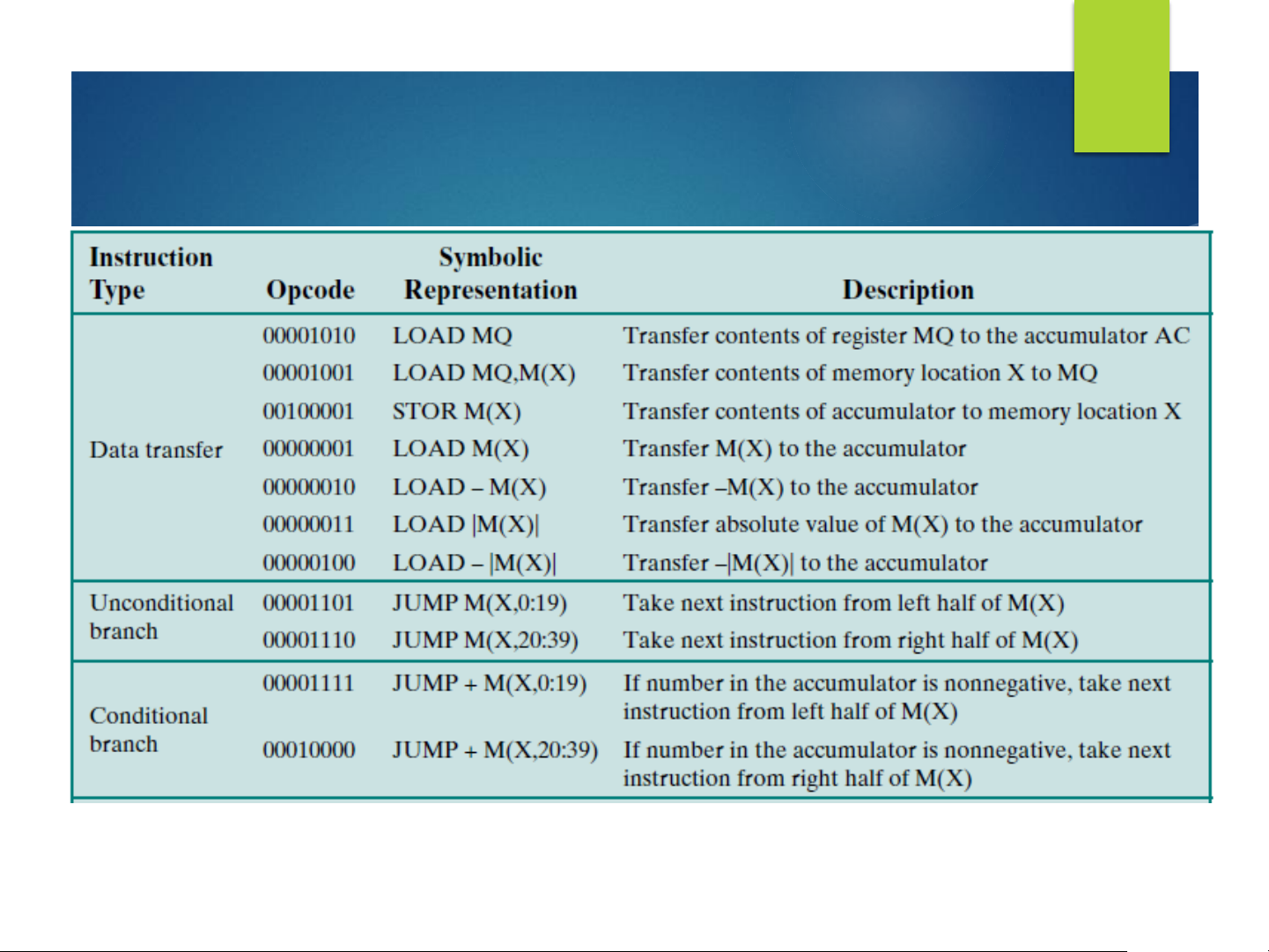

The IAS instruction set example 13 The First Generation

THE COMMERCIAL COMPUTERS

The UNIVAC I (Universal Automatic Computer) (1950) was the first

successful commercial computer. It was intended for both scientific and commercial applications.

The UNIVAC II, which had greater memory capacity and higher

performance than the UNIVAC I, was delivered in the late 1950s.

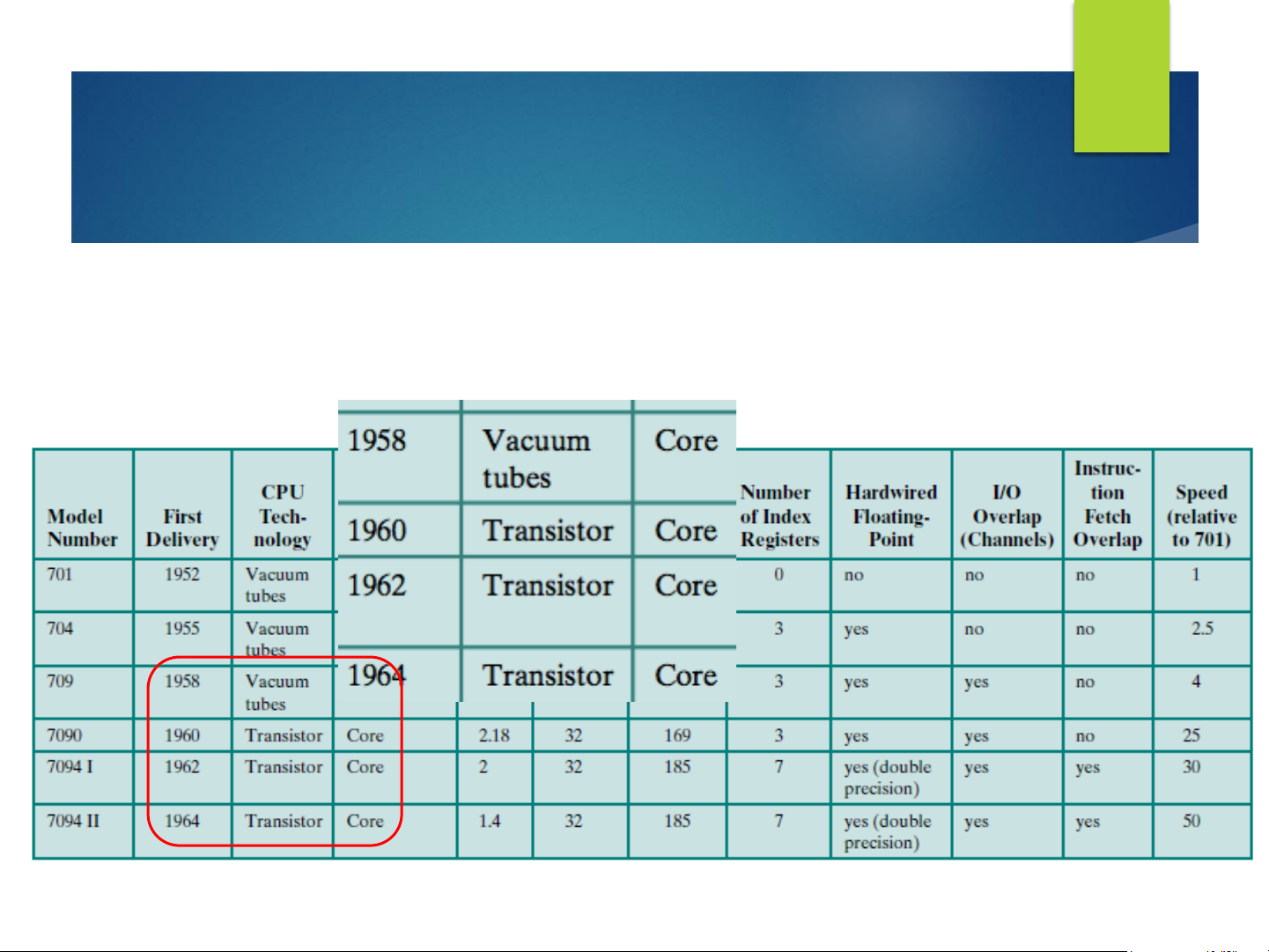

The IBM 701 (1953), which was delivered by IBM - the first electronic

stored-program computer (punched-card processing equipment),

which intended primarily for scientific applications.

The IBM 702 (1955) which had a number of hardware features that

suited it to business applications. 14 The Second Generation TRANSISTORS The second generation:

More complex arithmetic and logic units and control units,

the use of high-level programming languages, and

the provision of system software with the computer. 15 The Second Generation

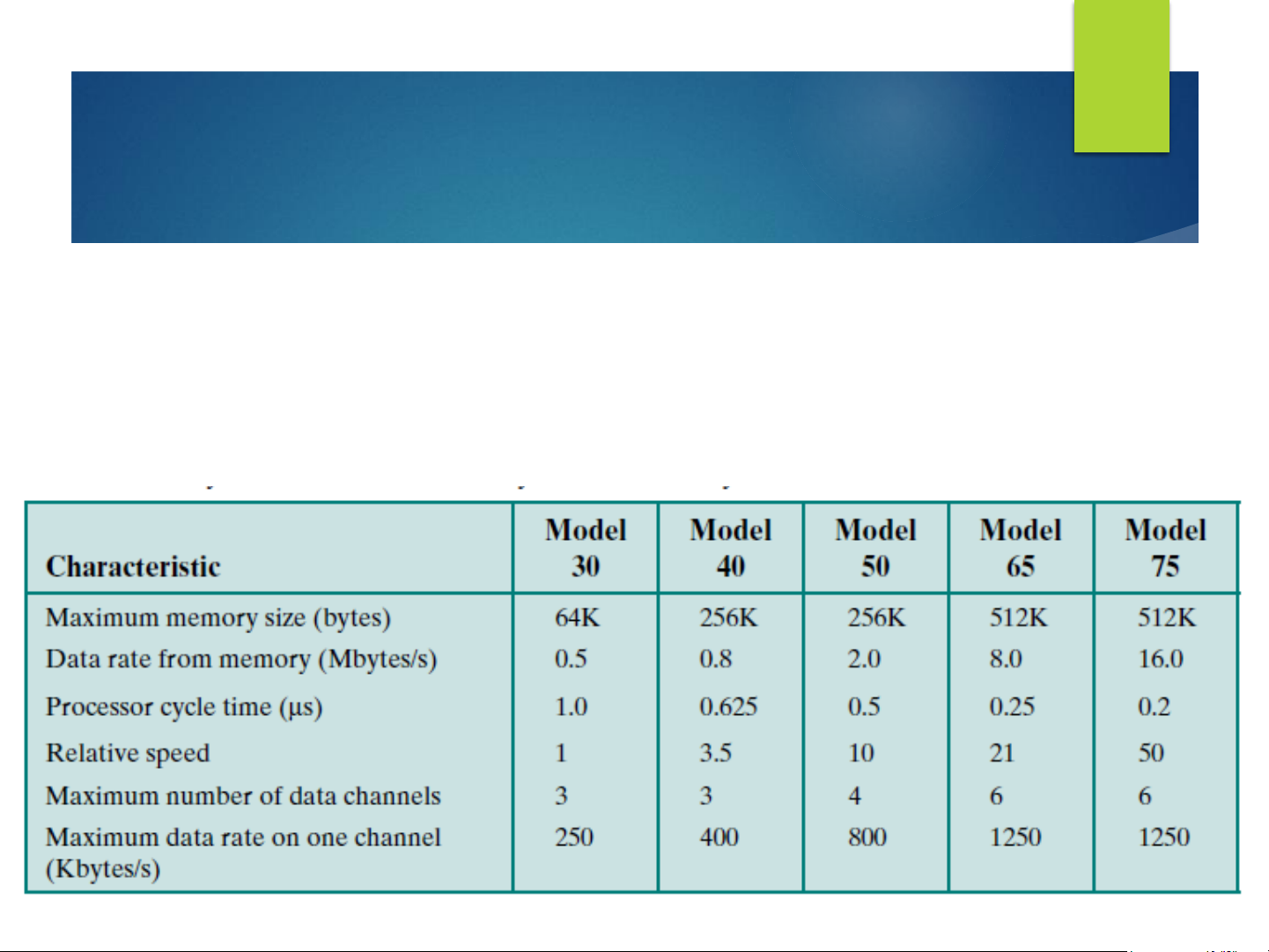

PDP-1 (1957), delivered by DEC IBM 7094 16 The Third Generation

INTEGRATED CIRCUITS (IC) 17 The Third Generation THE IBM SYSTEM/360

The industry’s first planned family of computers which covered a

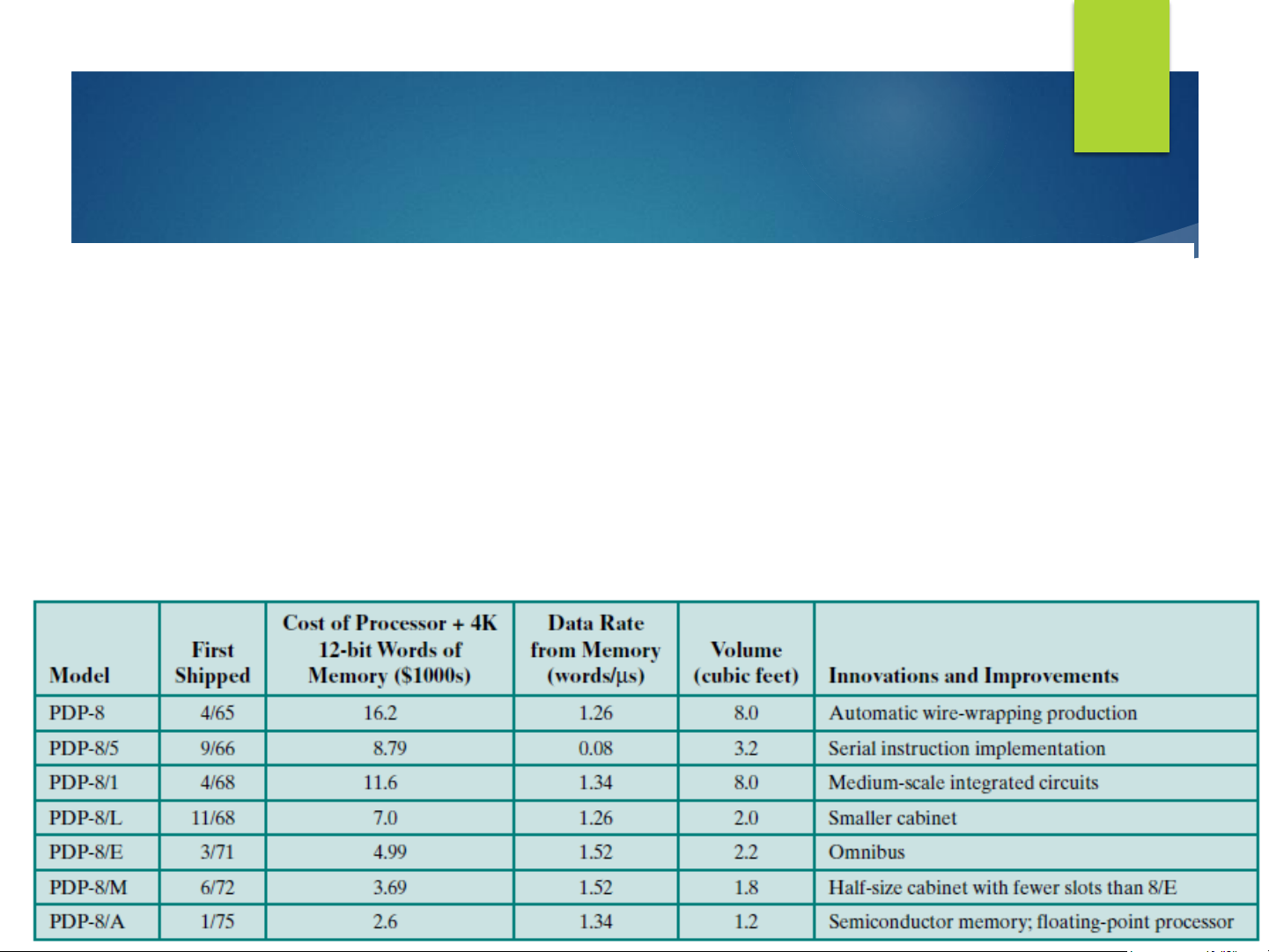

wide range of performance and cost. 18 The Third Generation THE DEC PDP-8

Low cost: $16,000 in comparison with $100,000 of IBM system/360 series,

Small size: Another manufacturer purchase a PDP-8 and

integrate it into a total system for resale 19 Later Generations 20 Processor Fabrication Process