Preview text:

lOMoAR cPSD| 58728417 ĐÁP ÁN CHƯƠNG 3 PHẦN MUX VÀ DEMUX

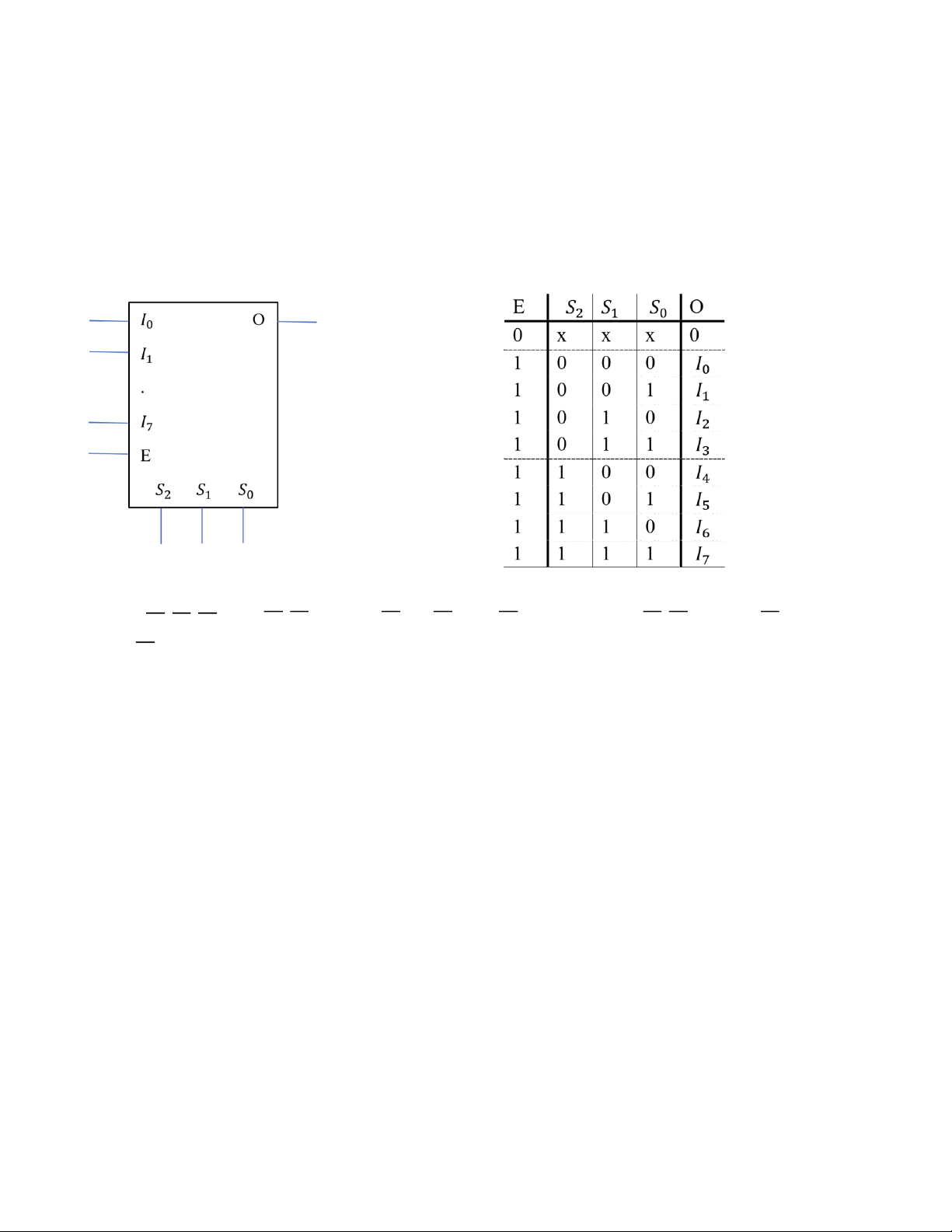

Bài 3.1: Thiết kế mạch đa hợp 8 sang 1 đường, có E tích cực mức cao Mux

8 → 1, E tích cực mức cao BTT:

𝑂𝑂 = 𝐸𝐸(𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0. 𝐼𝐼0 + 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0. 𝐼𝐼1 + 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0. 𝐼𝐼2 + 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0. 𝐼𝐼3 + 𝑆𝑆2. 𝑆𝑆1.

𝑆𝑆0. 𝐼𝐼4 + 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0. 𝐼𝐼5 +

𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0. 𝐼𝐼6 + 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆 ) 0. 𝐼𝐼7

- Vẽ mạch theo hàm ngõ ra

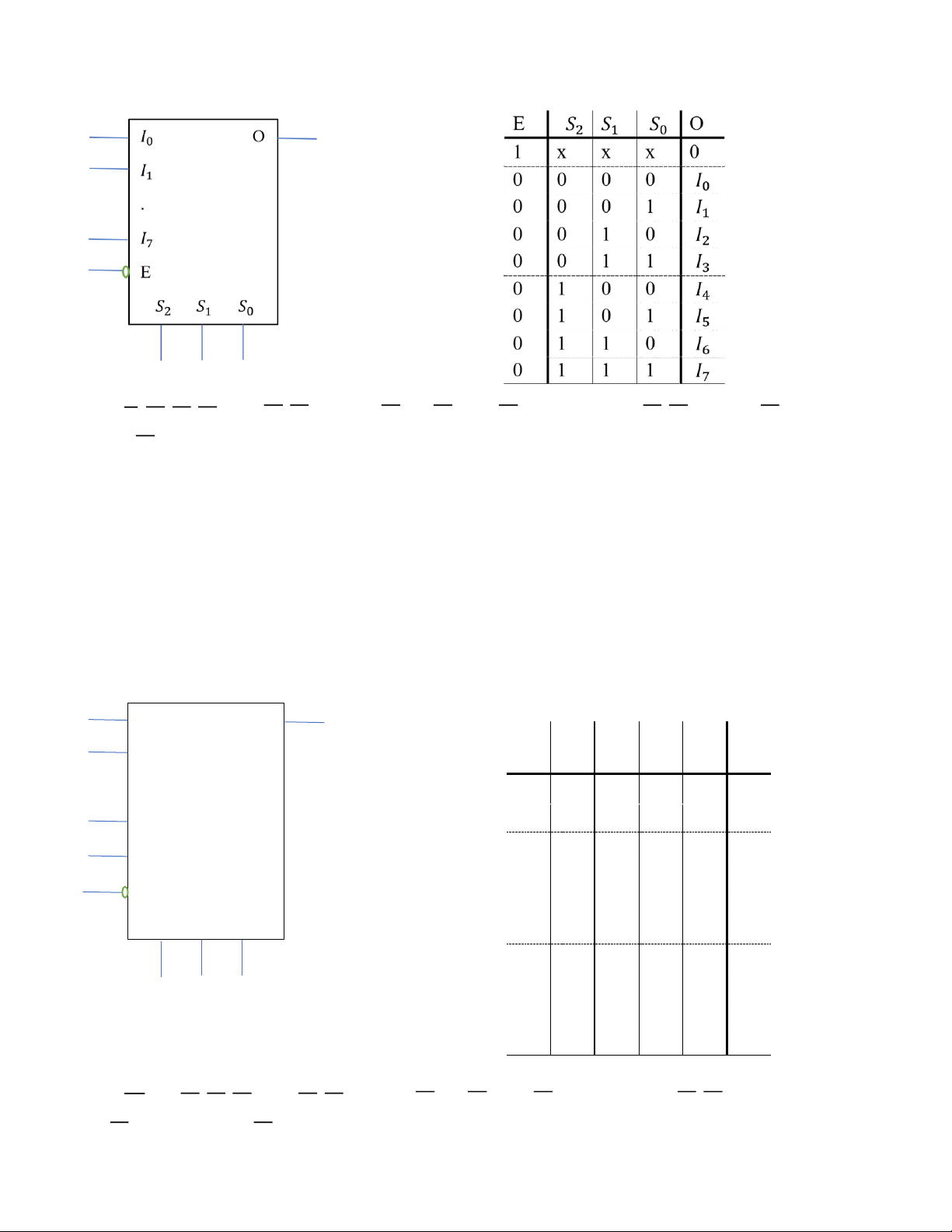

Bài 3.2: Thiết kế mạch đa hợp 8 sang 1 đường, có E tích cực mức thấp Mux

8 → 1, E tích cực mức thấp BTT: lOMoAR cPSD| 58728417

𝑂𝑂 = 𝐸𝐸(𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0. 𝐼𝐼0 + 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0. 𝐼𝐼1 + 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0. 𝐼𝐼2 + 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0. 𝐼𝐼3 + 𝑆𝑆2. 𝑆𝑆1.

𝑆𝑆0. 𝐼𝐼4 + 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0. 𝐼𝐼5 +

𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0. 𝐼𝐼6 + 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆 ) 0. 𝐼𝐼7

- Vẽ mạch theo hàm ngõ ra

Bài 3.3: Thiết kế mạch đa hợp 8 sang 1 đường, có E1 tích cực mức cao và E2 tích cực mức thấp.

Mux 8 → 1, E1 tích cực mức cao và E2 tích cực mức thấp 𝐼 O 0 𝐸𝐸2 𝐸𝐸1 𝑆𝑆1 𝑆𝑆0 O 𝐼 𝐼1 𝑆𝑆2 𝐼 . 1 x x x x 0 x 0 x x x 0 𝐼7 𝐼 0 1 0 0 0 𝐼𝐼0 𝐸 1 0 1 0 0 1 𝐼𝐼1 𝐸 𝐸 2 0 1 0 1 0 𝐼𝐼2 𝐸 𝑆 2 𝑆1 𝑆0 0 1 0 1 1 𝐼𝐼3 𝑆 𝑆 𝑆 0 1 1 0 0 𝐼𝐼 BTT: 4 0 1 1 0 1 𝐼𝐼5 0 1 1 1 0 𝐼𝐼6 0 1 1 1 1 𝐼𝐼7

𝑂𝑂 = 𝐸𝐸2. 𝐸𝐸1(𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0. 𝐼𝐼0 + 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0. 𝐼𝐼1 + 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0. 𝐼𝐼2 + 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0. 𝐼𝐼3 +

𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0. 𝐼𝐼4 + lOMoAR cPSD| 58728417

𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0. 𝐼𝐼5 + 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0. 𝐼𝐼6 + 𝑆𝑆2.

𝑆𝑆1. 𝑆𝑆0. 𝐼𝐼7)

- Vẽ mạch theo hàm ngõ ra

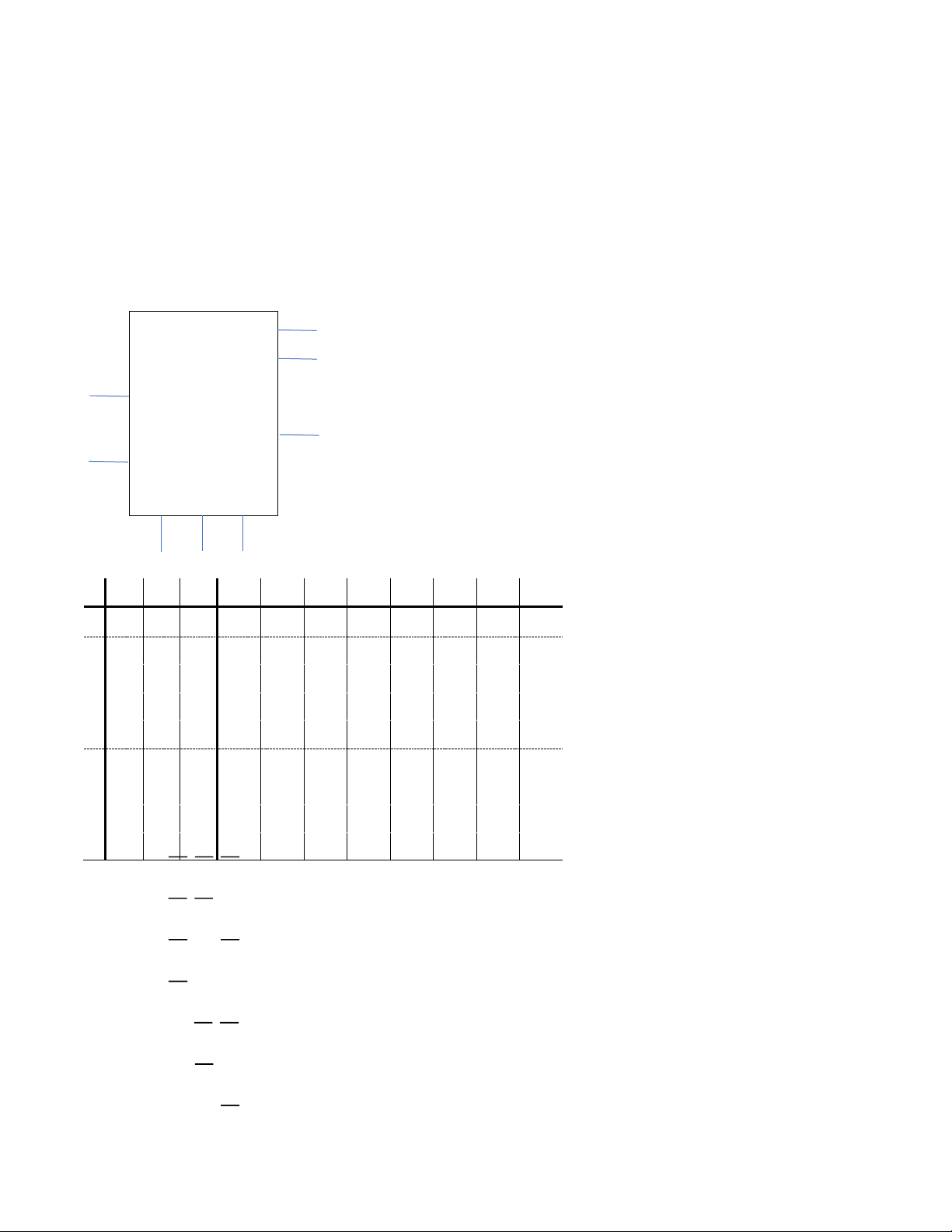

Bài 3.4: Thiết kế mạch giải đa hợp 1 sang 8 đường, có E tích cực mức cao.

Demux 1 → 8, E tích cực mức cao 𝑂0 𝑂 𝑂1 𝑂 I 𝑂 7 𝑂 E 𝑆 2 𝑆1 𝑆0 𝑆 𝑆 𝑆 BTT:

E 𝑆𝑆2 𝑆𝑆1 𝑆𝑆0 𝑂𝑂7 𝑂𝑂6 𝑂𝑂5 𝑂𝑂4 𝑂𝑂3 𝑂𝑂2 𝑂𝑂1 𝑂𝑂0 0 x x x 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 I 1 0 0 1 0 0 0 0 0 0 I 0 1 0 1 0 0 0 0 0 0 I 0 0 1 0 1 1 0 0 0 0 I 0 0 0 1 1 0 0 0 0 0 I 0 0 0 0 0 1 1 0 1 0 0 I 0 0 0 0 1 1 1 0 0 I 0 0 0 0 0 0 1 1 1 1 I 0 0 0 0 0 0 0

𝑂𝑂0 = 𝐼𝐼. 𝐸𝐸. 𝑆𝑆2. 𝑆𝑆1.

𝑆𝑆0 𝑂𝑂1 = 𝐼𝐼. 𝐸𝐸.

𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0

𝑂𝑂2 = 𝐼𝐼. 𝐸𝐸. 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0

𝑂𝑂3 = 𝐼𝐼. 𝐸𝐸. 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0

𝑂𝑂4 = 𝐼𝐼. 𝐸𝐸. 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0 lOMoAR cPSD| 58728417

𝑂𝑂5 = 𝐼𝐼. 𝐸𝐸. 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0

𝑂𝑂6 = 𝐼𝐼. 𝐸𝐸. 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0

𝑂𝑂7 = 𝐼𝐼. 𝐸𝐸. 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0

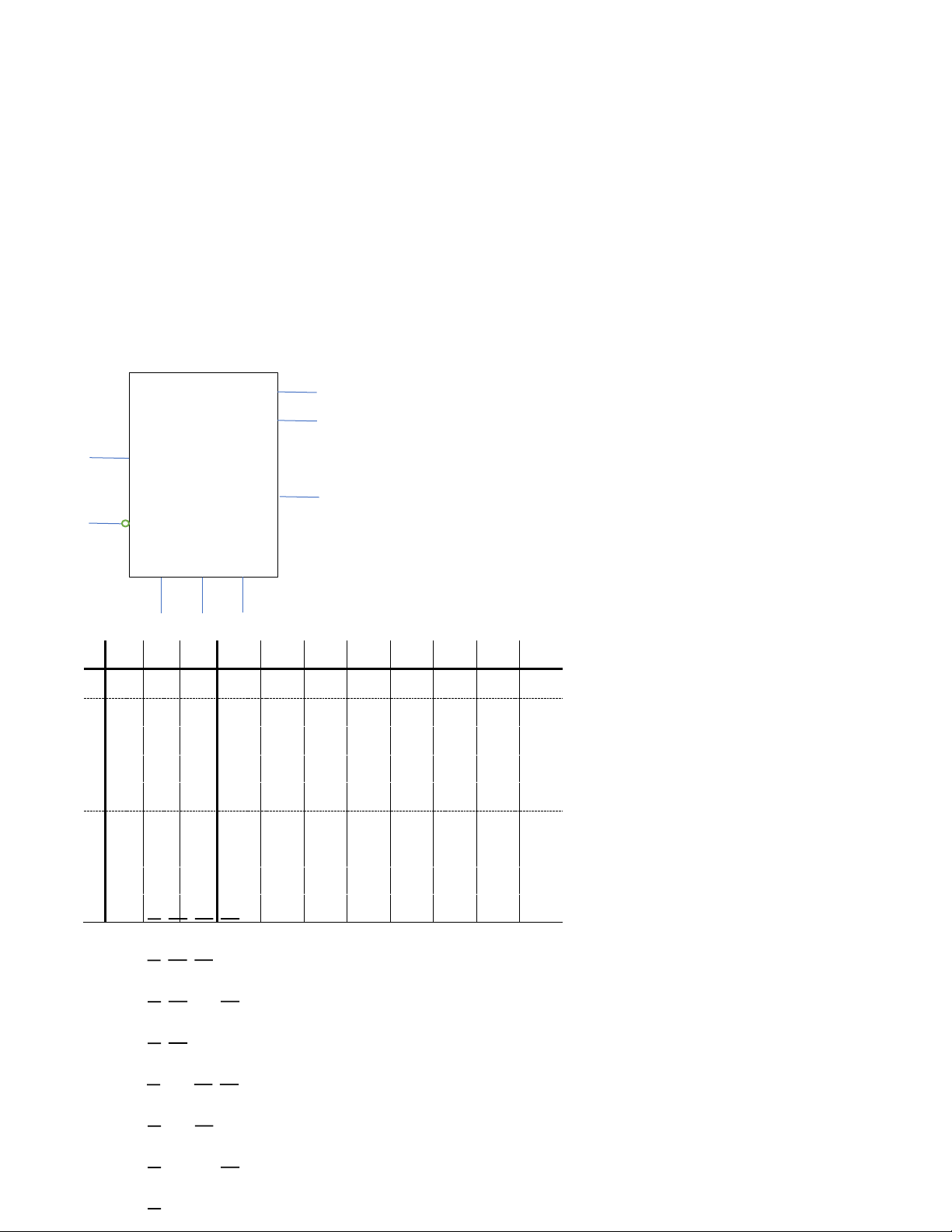

Bài 3.5: Thiết kế mạch giải đa hợp 1 sang 8 đường, có E tích cực mức thấp. Demux

1 → 8, E tích cực mức thấp 𝑂0 𝑂 𝑂1 𝑂 I 𝑂 7 𝑂 E 𝑆 2 𝑆1 𝑆0 𝑆 𝑆 𝑆 BTT:

E 𝑆𝑆2 𝑆𝑆1 𝑆𝑆0 𝑂𝑂7 𝑂𝑂6 𝑂𝑂5 𝑂𝑂4 𝑂𝑂3 𝑂𝑂2 𝑂𝑂1 𝑂𝑂0 1 x x x 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 I 0 0 0 1 0 0 0 0 0 0 I 0 0 0 1 0 0 0 0 0 0 I 0 0 0 0 1 1 0 0 0 0 I 0 0 0 0 1 0 0 0 0 0 I 0 0 0 0 0 0 1 0 1 0 0 I 0 0 0 0 0 1 1 0 0 I 0 0 0 0 0 0 0 1 1 1 I 0 0 0 0 0 0 0

𝑂𝑂0 = 𝐼𝐼. 𝐸𝐸. 𝑆𝑆2. 𝑆𝑆1.

𝑆𝑆0 𝑂𝑂1 = 𝐼𝐼. 𝐸𝐸.

𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0

𝑂𝑂2 = 𝐼𝐼. 𝐸𝐸. 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0

𝑂𝑂3 = 𝐼𝐼. 𝐸𝐸. 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0 lOMoAR cPSD| 58728417

𝑂𝑂4 = 𝐼𝐼. 𝐸𝐸. 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0

𝑂𝑂5 = 𝐼𝐼. 𝐸𝐸. 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0

𝑂𝑂6 = 𝐼𝐼. 𝐸𝐸. 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0

𝑂𝑂7 = 𝐼𝐼. 𝐸𝐸. 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0

Bài 3.6: Thiết kế mạch giải đa hợp 1 sang 8 đường, có E1 tích cực mức cao và E2 tích cực mức thấp.

Demux 1 → 8, E tích cực mức thấp 𝑂0 𝑂 𝑂1 𝑂 I 𝑂 7 𝑂 𝐸1 𝐸 𝐸2 𝐸 𝑆 2 𝑆1 𝑆0 𝑆 𝑆 𝑆

𝐸𝐸2 𝐸𝐸1 𝑆𝑆2 𝑆𝑆1

𝑆𝑆0 𝑂𝑂7 𝑂𝑂6 𝑂𝑂5 𝑂𝑂4 𝑂𝑂3 𝑂𝑂2 𝑂𝑂1 𝑂𝑂0 1 x x x x 0 0 0 0 0 0 0 0 x 0 x x x 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 I 0 1 0 0 1 0 0 0 0 0 0 I I 0 0 1 0 1 0 0 0 0 0 0 0 0 0 1 0 1 1 0 0 0 0 I 0 0 0 0 1 1 0 0 0 0 0 I 0 0 0 0 0 1 1 0 1 0 0 I 0 0 0 0 0 0 1 1 1 0 0 I 0 0 0 0 0 0 0 1 1 1 1 I 0 0 0 0 0 0 0

𝑂𝑂0 = 𝐼𝐼. 𝐸𝐸2. 𝐸𝐸1. 𝑆𝑆2.

𝑆𝑆1. 𝑆𝑆0 𝑂𝑂1 = 𝐼𝐼. 𝐸𝐸2.

𝐸𝐸1. 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0 lOMoAR cPSD| 58728417

𝑂𝑂2 = 𝐼𝐼. 𝐸𝐸2. 𝐸𝐸1. 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0

𝑂𝑂3 = 𝐼𝐼. 𝐸𝐸2. 𝐸𝐸1. 𝑆𝑆2.

𝑆𝑆1. 𝑆𝑆0 𝑂𝑂4 = 𝐼𝐼. 𝐸𝐸2.

𝐸𝐸1. 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0

𝑂𝑂5 = 𝐼𝐼. 𝐸𝐸2. 𝐸𝐸1. 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0

𝑂𝑂6 = 𝐼𝐼. 𝐸𝐸2. 𝐸𝐸1. 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0

𝑂𝑂7 = 𝐼𝐼. 𝐸𝐸2. 𝐸𝐸1. 𝑆𝑆2. 𝑆𝑆1. 𝑆𝑆0

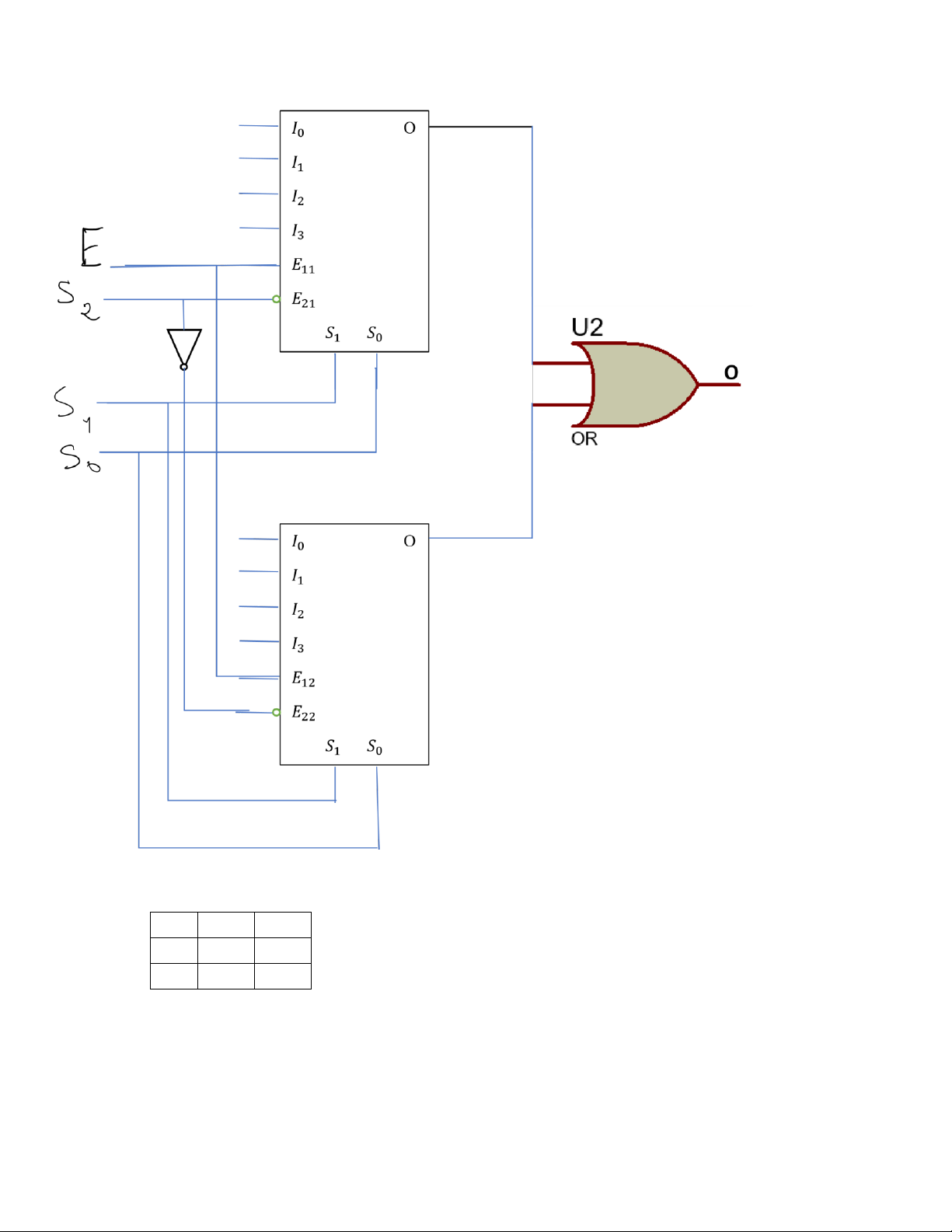

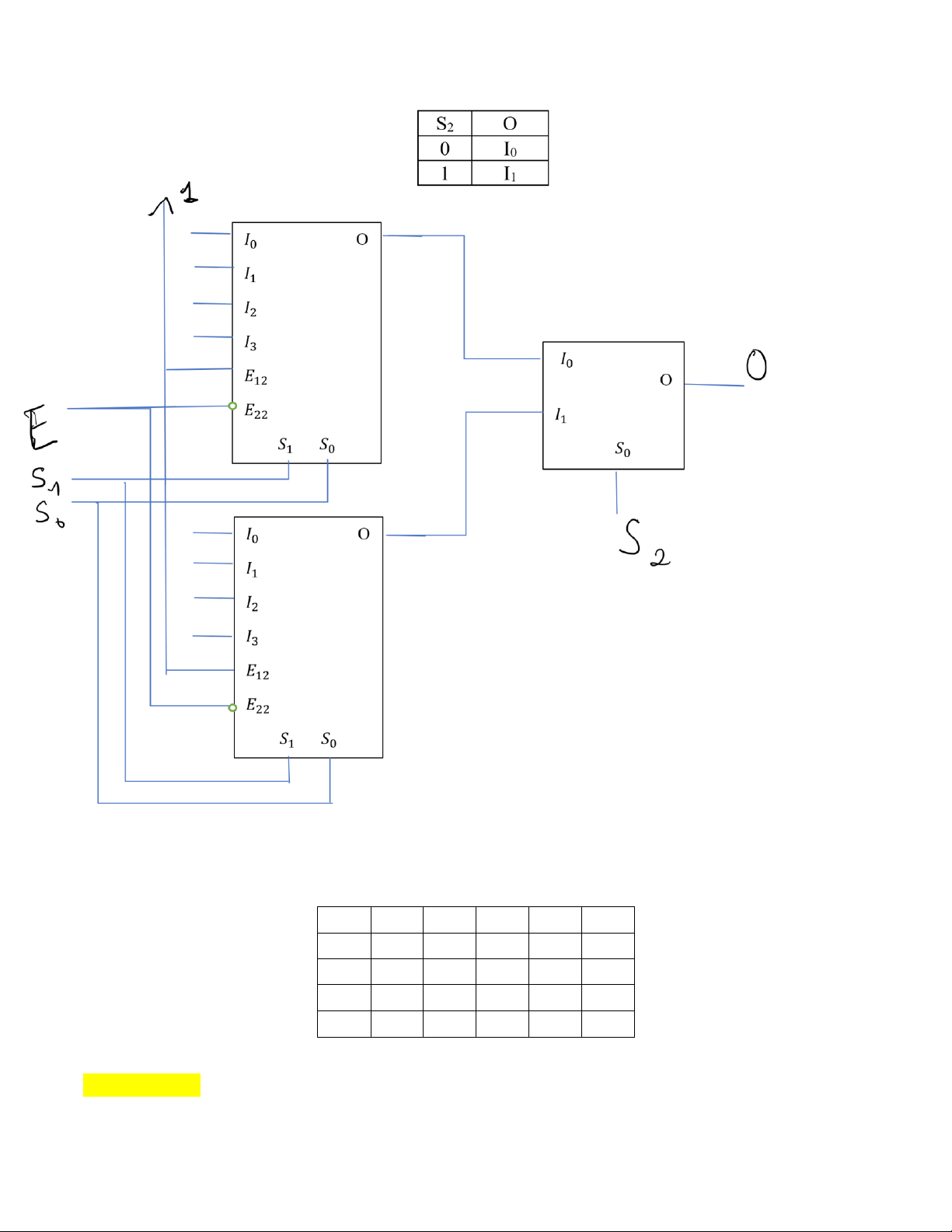

Bài 3.7. Cho mạch đa hợp 4 sang 1 đường, có E1 tích cực mức cao và E2 tích cực mức thấp

a) Ghép các mạch trên thành 8 sang 1 có E tích cực mức cao Thiếu S2 Dư E21 E22 S2 E22 E21 0 1 0 1 0 1 E21= S2; E22 = 𝑆𝑆2 lOMoAR cPSD| 58728417

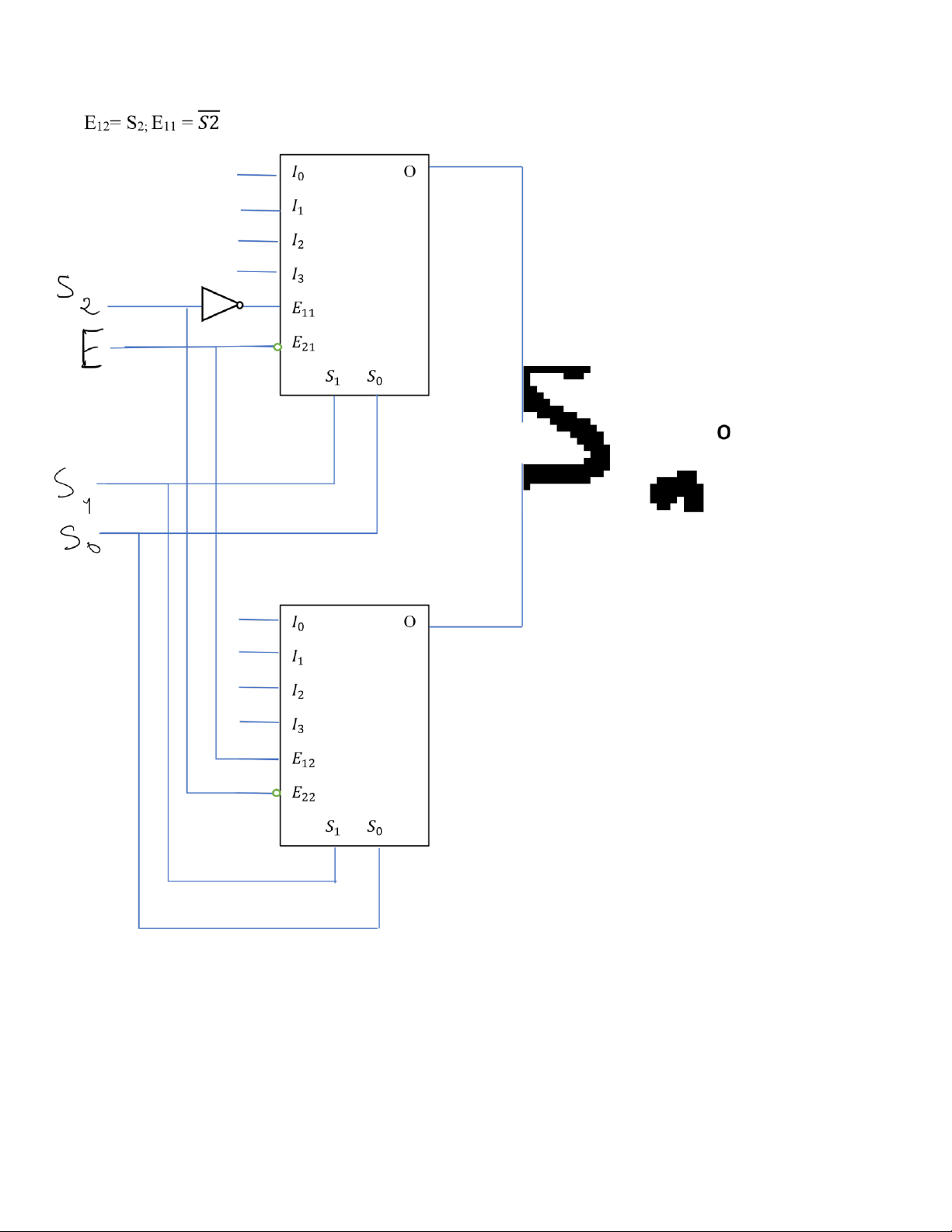

b) Ghép các mạch trên thành 8 sang 1 có E tích cực mức thấp. Thiếu S2 Dư E11 E12 S2 E12 E11 0 0 1 1 1 0 lOMoAR cPSD| 58728417

c) Ghép các mạch trên thành 8 sang 1 có E tích cực mức thấp, không sử dụng cổng Logic lOMoAR cPSD| 58728417

d) Ghép các mạch trên thành 16 sang 1. S3 S2 E4 E3 E2 E1 0 0 CP 0 1 CP 1 0 CP 1 1 CP Vẽ mạch logic lOMoAR cPSD| 58728417

PHẦN ENCODER và DECODER

Bài 3.9: Thiết kế mạch mã hóa từ 8 sang 3 đường ngõ vào tác động mức thấp

Encoder 8 → 3, ngõ vào tích cực mức thấp 𝐼 0 𝑂0 𝐼 𝑂 𝐼1 𝑂1 𝐼 𝑂 . 𝑂 2 𝑂 𝐼 7 𝐼 𝑆 𝑆 𝑆 2 1 0 𝑆 𝑆 𝑆 BTT:

𝐼𝐼7 𝐼𝐼6 𝐼𝐼5 𝐼𝐼4 𝐼𝐼3 𝐼𝐼2 𝐼𝐼1 𝐼𝐼0 𝑂𝑂2 𝑂𝑂1 𝑂𝑂0 1

1 1 1 1 1 1 0 0 0 0 1 1 1 1 1 1 0 1 0 0 1 1 1 1 1 1 0 1 1 0 1 0 1 1 1 1 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0 0 1 1 0 1 1 1 1 1 1 0 1 1 0 1 1 1 1 1 1 1 1 0 0 1 1 1 1 1 1 1 1 1 1

𝑂𝑂0 = 𝐼𝐼1 + 𝐼𝐼3 + 𝐼𝐼5 + 𝐼𝐼7 = 𝐼𝐼1. 𝐼𝐼3. 𝐼𝐼5. 𝐼𝐼7

𝑂𝑂1 = 𝐼𝐼2 + 𝐼𝐼3 + 𝐼𝐼6 + 𝐼𝐼7 = 𝐼𝐼2. 𝐼𝐼3. 𝐼𝐼6. 𝐼𝐼7

𝑂𝑂2 = 𝐼𝐼4 + 𝐼𝐼5 + 𝐼𝐼6 + 𝐼𝐼7 = 𝐼𝐼4. 𝐼𝐼5. 𝐼𝐼6. 𝐼𝐼7

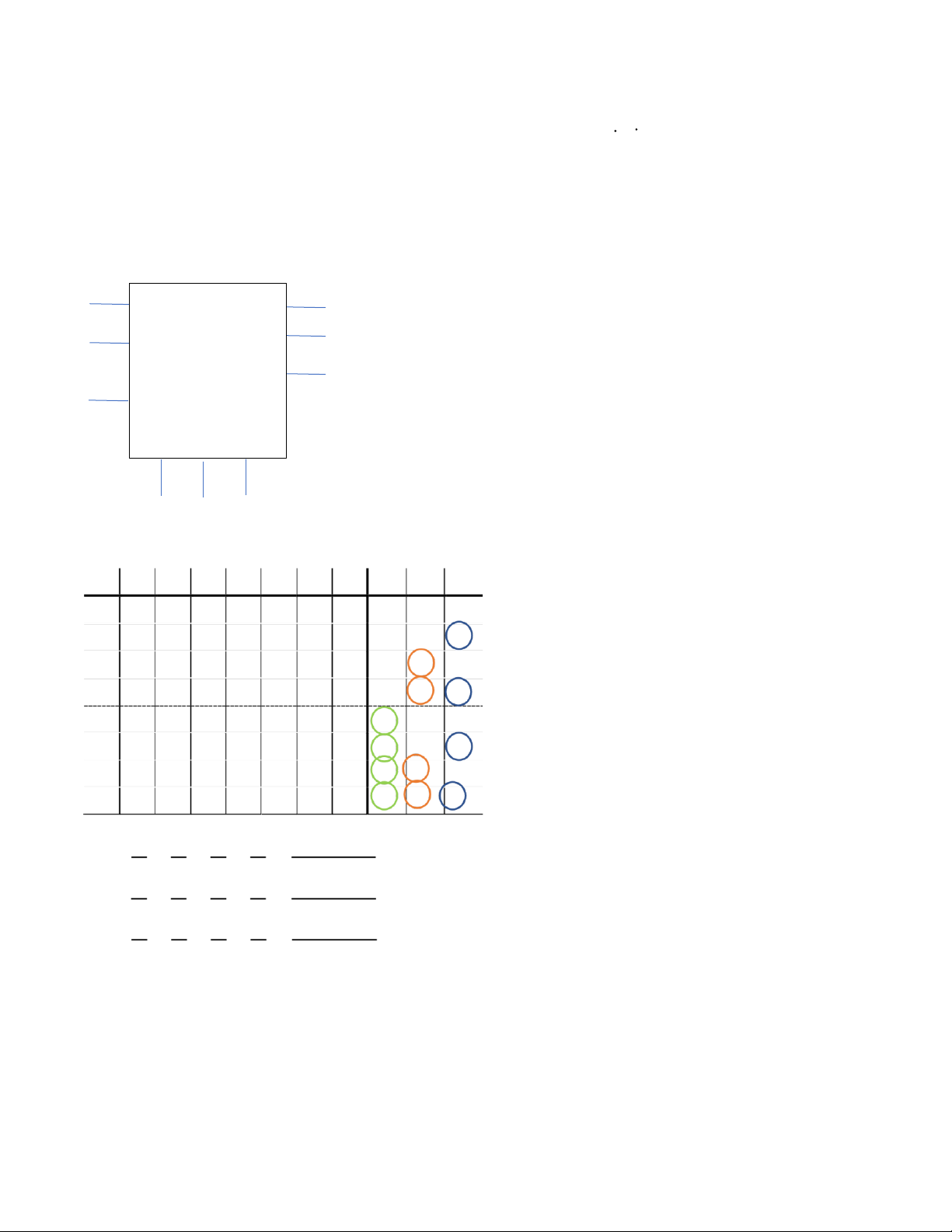

Bài 3.11 Mạch mã hóa ghép bằng 4 mạch 4 sang 2 ngõ vào mức cao

- Bảng sự thật: Các bạn tự viết

- Các ngõ ra O0 = I1 + I3 + I5 + I7 + I9 + I11 + I13 + I15

O1 = I2+ I3 + I6 + I7 + I10 + I11 + I14 + I15 lOMoAR cPSD| 58728417

O3 = I4 + I5 + I6 + I7 + I12 + I13 + I14 + I15

O4 = I8 + I9 + I10 + I11 + I12 + I13 + I14 + I15

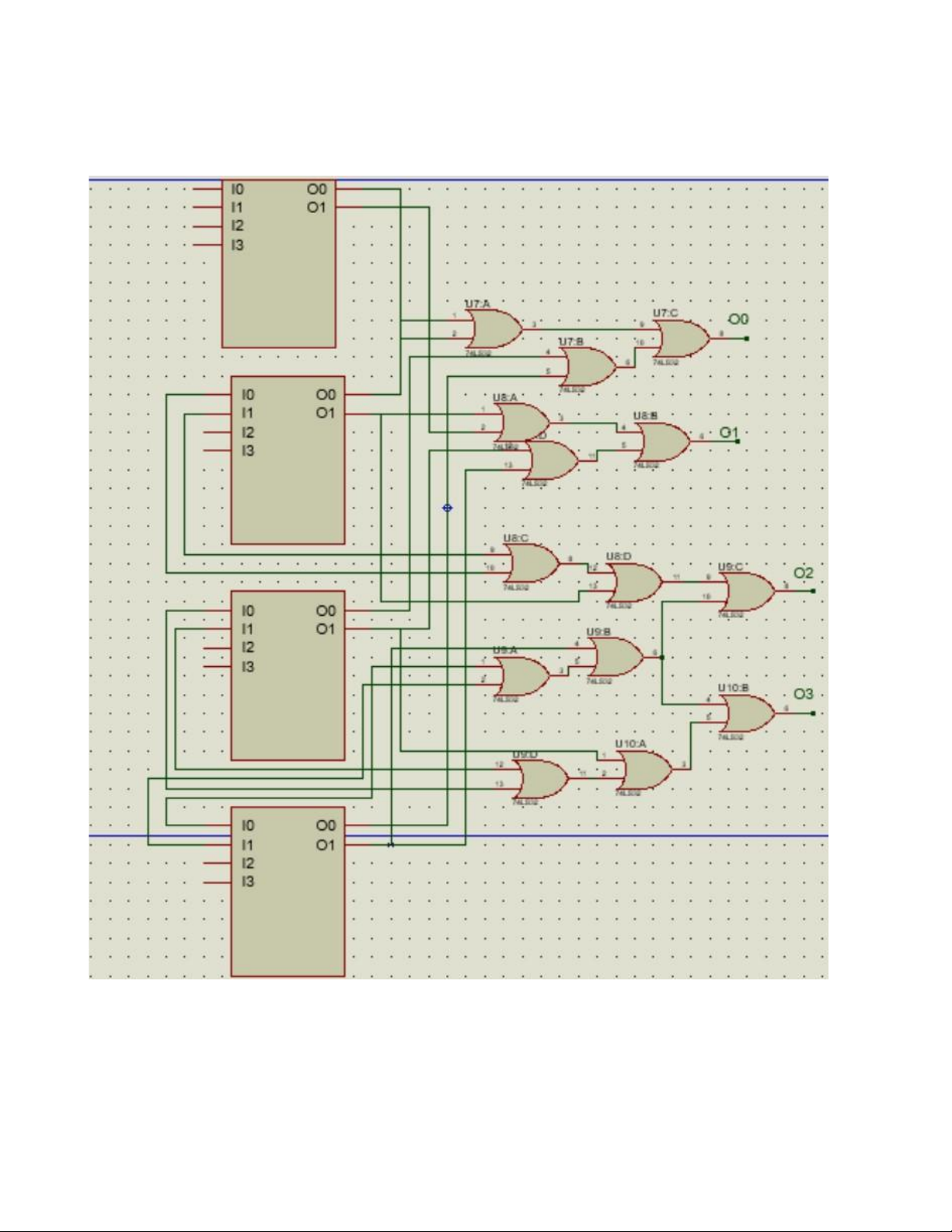

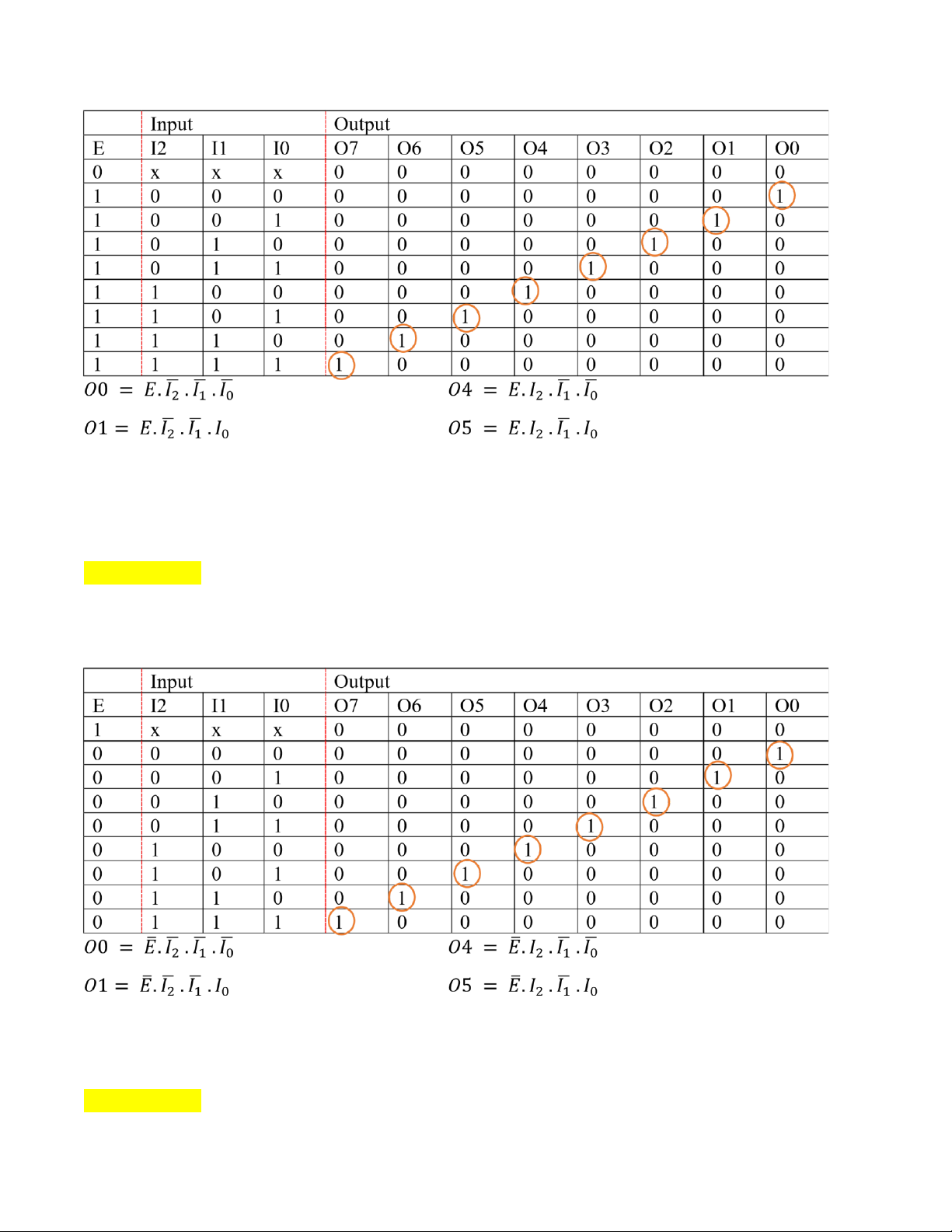

Bài 3.12 Thiết kế mạch giải mã từ 3 sang 8 đường ngõ ra mức cao, có E mức cao Bảng trạng thái: lOMoAR cPSD| 58728417

𝑂𝑂2 = 𝐸𝐸. 𝐼𝐼2 . 𝐼𝐼1 . 𝐼𝐼0

𝑂𝑂6 = 𝐸𝐸. 𝐼𝐼2 . 𝐼𝐼1 . 𝐼𝐼0 𝑂𝑂3 = 𝐸𝐸. 𝐼𝐼 𝑂𝑂7 = 𝐸𝐸. 𝐼𝐼 2 . 𝐼𝐼1 . 𝐼𝐼0 2 . 𝐼𝐼1 . 𝐼𝐼0 Vẽ mạch logic

Bài 3.13 Thiết kế mạch giải mã từ 3 sang 8 đường ngõ ra mức cao, có E mức thấp Bảng trạng thái

𝑂𝑂2 = 𝐸𝐸. 𝐼𝐼2 . 𝐼𝐼1 . 𝐼𝐼0

𝑂𝑂6 = 𝐸𝐸. 𝐼𝐼2 . 𝐼𝐼1 . 𝐼𝐼0

𝑂𝑂3 = 𝐸𝐸. 𝐼𝐼2 . 𝐼𝐼1 . 𝐼𝐼0

𝑂𝑂7 = 𝐸𝐸. 𝐼𝐼2 . 𝐼𝐼1 . 𝐼𝐼 Vẽ mạch logic 0 lOMoAR cPSD| 58728417

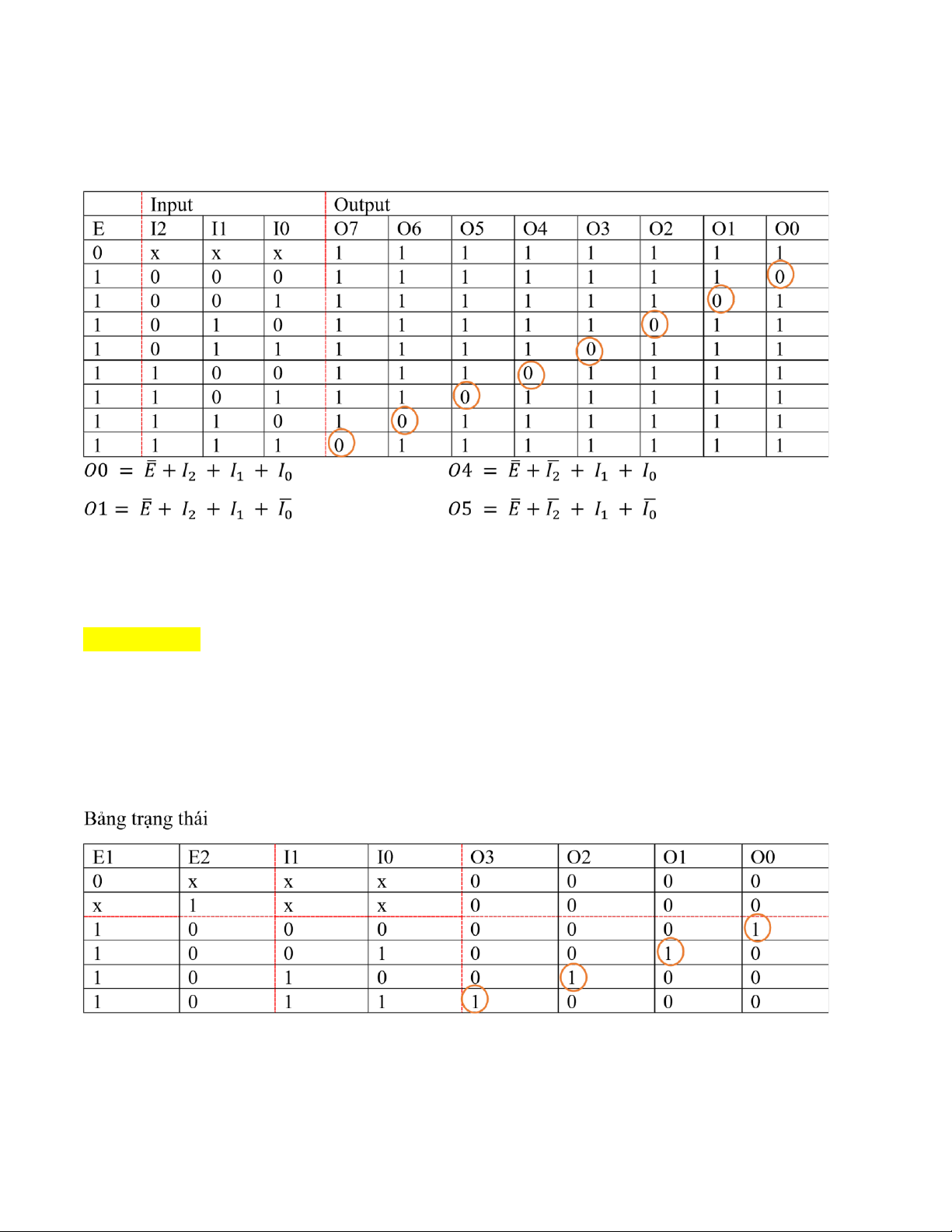

Bài 3.14 Thiết kế mạch giải mã từ 3 sang 8 đường ngõ ra mức thấp, có E mức cao. Bảng trạng thái

𝑂𝑂2 = 𝐸𝐸 + 𝐼𝐼2 + 𝐼𝐼1 + 𝐼𝐼0

𝑂𝑂6 = 𝐸𝐸 + 𝐼𝐼2 + 𝐼𝐼1 + 𝐼𝐼0

𝑂𝑂3 = 𝐸𝐸 + 𝐼𝐼2 + 𝐼𝐼1 + 𝐼𝐼0

𝑂𝑂7 = 𝐸𝐸 + 𝐼𝐼2 + 𝐼𝐼1 + 𝐼𝐼0 Vẽ mạch logic

Bài 3.15: tương tự 3.14 thay E’ thành E

Bài 3.16 Thiết kế mạch giải mã từ 2 sang 4 đường ngõ ra mức cao, có E1 mức cao và E2 mức thấp

𝑂𝑂0 = 𝐸𝐸2. 𝐸𝐸1. 𝐼𝐼1 . 𝐼𝐼0

𝑂𝑂2 = 𝐸𝐸2. 𝐸𝐸1 . 𝐼𝐼1 . 𝐼𝐼0 lOMoAR cPSD| 58728417 𝑂𝑂1 = 𝐸𝐸 𝑂𝑂3 = 𝐸𝐸

2. 𝐸𝐸1 . 𝐼𝐼1 . 𝐼𝐼0 2. 𝐸𝐸1 . 𝐼𝐼1 . 𝐼𝐼0 Vẽ mạch logic

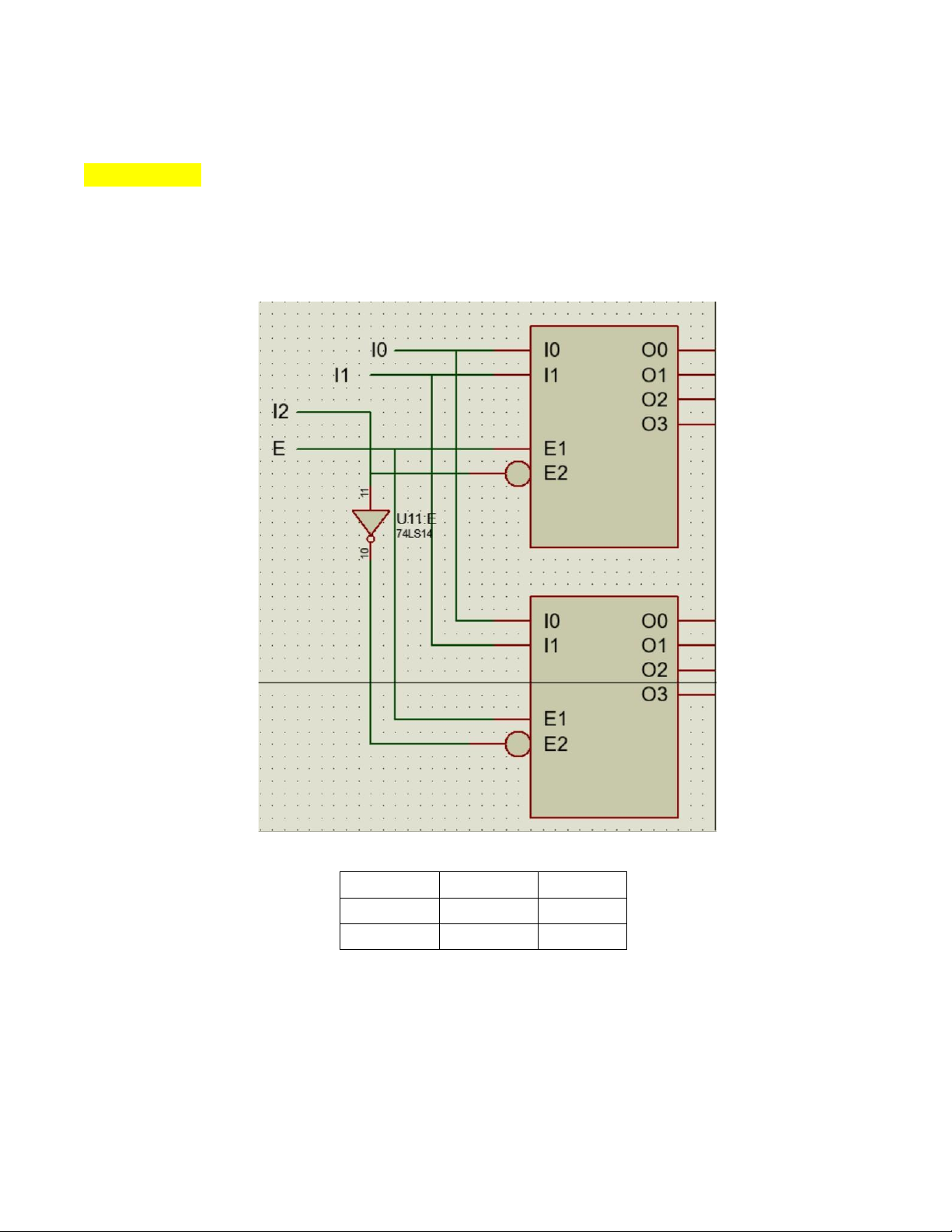

Bài 3.17 Ghép các mạch giải mã trong Bài 3.16 thành mạch giải mã 3 sang 8 có E mức cao. Thiếu I2, dư E21 E22 I2 E21 E22 0 0 1 1 1 0 𝐸𝐸21 = 𝐼𝐼2 𝐸𝐸22 = 𝐼𝐼2

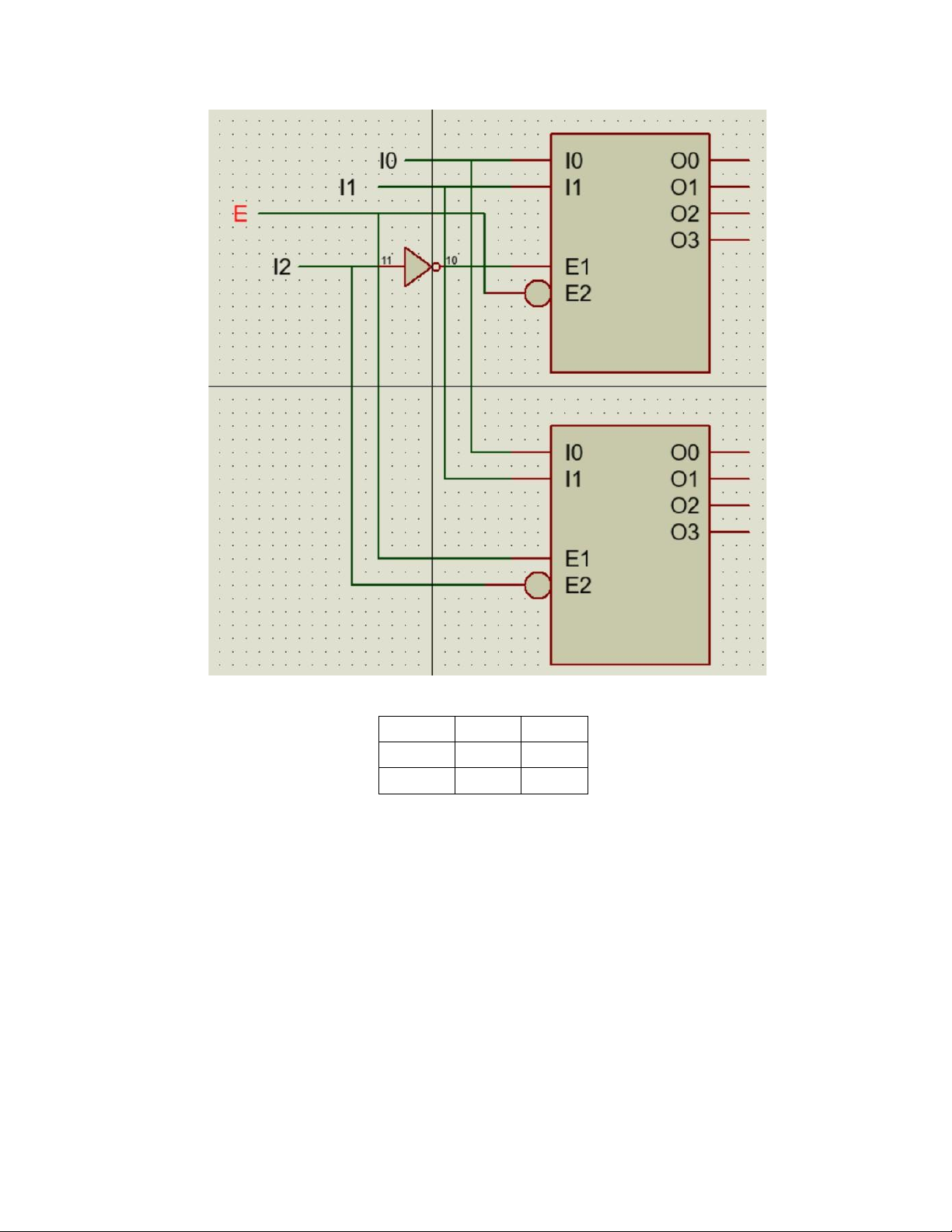

Bài 3.18 Ghép các mạch giải mã trong Bài 3.16 thành mạch giải mã 3 sang 8 có E mức thấp lOMoAR cPSD| 58728417 Thiếu I2, dư E11 E12 I2 E11 E12 0 1 0 1 0 1 𝐸𝐸21 = 𝐼𝐼2 𝐸𝐸22 = 𝐼𝐼2