Preview text:

Ôn cấu trúc máy tính và vi xử lí 1. Hệ thống máy tính

- Thành phần cơ bản của máy tính:

o Bộ xử lí trung tâm (CPU): điều kiển các hoạt động của máy tính và xử lý dữ liệu.

▪ Bộ xử lí (Control unit): điều kiển hoạt động của CPU và máy tính.

▪ Bộ số học và logic (ALU): thực hiện các phép tính toán và logic.

▪ Các thanh ghi(registers): cung cấp khả năng lưu trữ nội bộ cho CPU.

▪ CPU interconection: cung cấp liên lạc giữa control unit, ALU, registers.

o Bộ nhớ chính: lưu trữ dữ liệu.

o I/O: truyền dữ liệu giữa máy tính và môi trường bên ngoài.

o System interconection: cung cấp liên lạc giữa CPU, bộ nhớ chính và I/O.

- Lịch sử của máy tính:

o Thế hệ đầu tiên - Ống chân không(vacuum tubes):

▪ Máy tính đầu tiên: ENIAC

▪ Von Neumann Architecture: khái niệm lưu trữ chương trình.

o Thế hệ thứ hai – Bóng bán dẫn(transistors):

▪ Nhỏ hơn, rẻ hơn, tản nhiệt ít hơn.

▪ Các bộ số học, logic, điều kiển phức tạp hơn.

▪ Ngôn ngữ lập trình câp cao.

o Thế hệ thứ ba – Mạch tích hợp(integrated circuits):

▪ Chế tạo toàn bộ mạch điện trong một miếng slicon nhỏ.

▪ Moore’s law: số lượng transistors gấp đôi mỗi năm.

▪ M Law từ 1970’s: số lượng transistors gấp đôi mỗi 2 năm.

▪ Giá thành của một con chip gần như không thay đổi.

▪ Mật độ cao hơn, hiệu suất cao hơn. ▪ Máy tính nhỏ hơn. ▪ Giảm điện năng. o Bộ nhớ bán dẫn:

▪ Ứng dụng mạch tích hợp để xây dựng bộ nhớ.

▪ Chứa được nhiều dung lượng hơn. ▪ Đọc không phá hủy. ▪ Nhanh hơn.

- Đánh giá hiệu suất:

o Tốc độ thực hiện lệnh:

▪ MIPS= Ic = f

Ts × 106 CPI × 106

▪ MIPS: triệu câu lệnh mỗi giây

▪ Ic: số lượng câu lệnh.

▪ Ts: thời gian thực hiện chương trình.

▪ CPI: số chu kì mỗi câu lệnh. ▪ f: xung nhịp. ▪ T: tần số. ▪ f = 1 T

▪ Ts=CPI ×T × Ic

2. Hệ thống số đếm

- Các hệ thống số đếm: thập phân, nhị phân, thập lục phân, bát phân.

- Chuyển đổi giữa các hệ cơ số:

o Phần nguyên, chia cho x lấy dư cho đến khi bằng 0.

o Phần thập phân, nhân cho x lấy nguyên cho đến khi bằng

0 hoặc đạt độ chính xác yêu cầu.

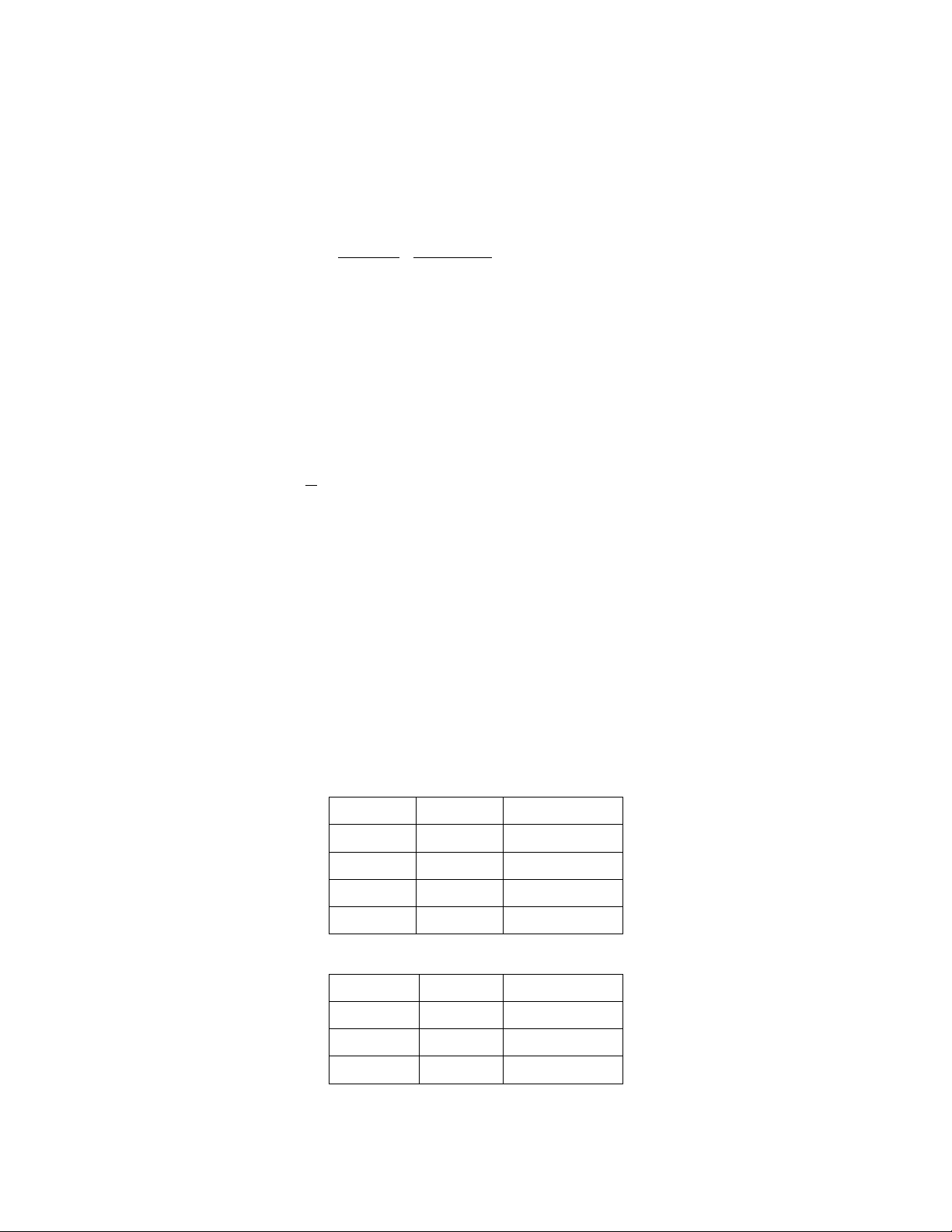

- Các phép toán số học: o Phép cộng nhị phân: A B A + B 0 0 0 0 1 1 1 0 1 1 1 0(nhớ 1) o Phép trừ nhị phân: A B A – B 0 0 0 0 1 1(Mượn 1) 1 0 1 1 1 0 o Phép nhân nhị phân A B A × B 0 0 0 0 1 0 1 0 0 1 1 1 o Phép chia nhị phân

- Số nhị phân có dấu – Bù hai:

o Số bù hai: đảo bit cộng 1.

▪ Bit có trọng số lớn nhất quy ước dấu: 0(+), 1(-).

▪ Tìm giá trị của số âm:

1) Khai triển như số dương nhưng bit có trọng số lớn nhất nhân thêm với -1.

2) Lấy bù hai của nó được số dương có cùng biên độ.

▪ Phạm vi biểu diễn: −2n−1 đến 2n−1−1.

o Cộng trừ hai số bù hai: thực hiện như số không dấu.

▪ Thực hiện trên toán hạng có cùng chiều dài.

▪ Kết quả đúng nếu nằm trong phạm vi biểu diễn. o Số dấu phẩy tĩnh:

▪ Định dạng số dấu phẩy tĩnh n bit với m bit dùng cho phần lẻ thập phân. o Số dấu phẩy động:

▪ Số thực N thường được biểu diễn dưới dạng số dấu phẩy động:

N =±M ×X E(1 ≤ M ∈ X) ▪ Trong đó:

• M là phần định trị. • X là cơ số. • E là phần lũy thừa. - Chuẩn IEEE 754:

o Số dấu động kiểu đơn(32 bit): 1 bit 8 bit 32 bit S e m o Trong đó: ▪ S là bit dấu. ▪ e = E + 127.

▪ m là phần lẻ của phần định trị M (M = 1.m)

o Công thức xác định giá trị số thực:

X =(−1)S ×1. m× 2e−127 3. Các phép toán logic

- Đại số boole:

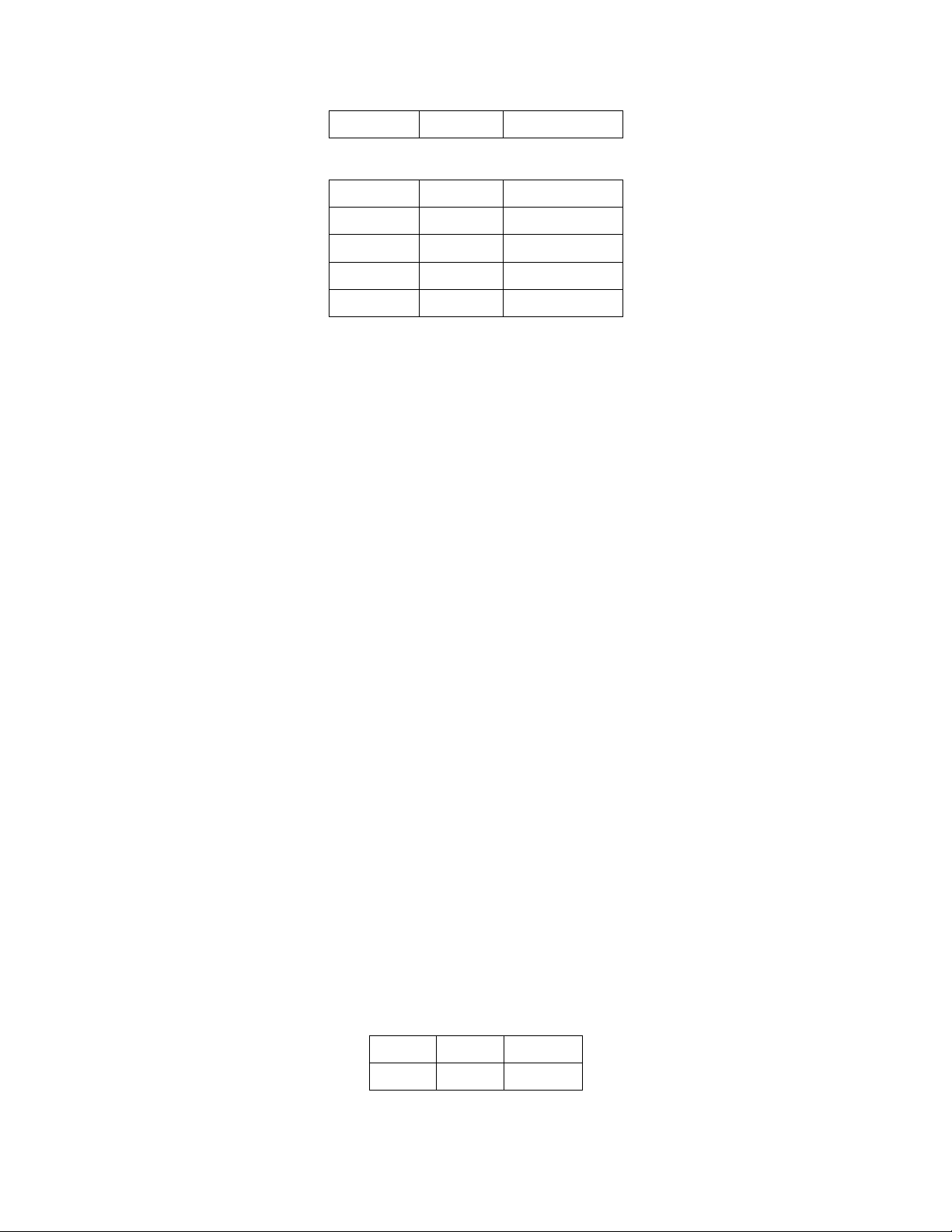

o Gồm 3 toán tử là (AND), (OR) và (NOT). AND OR NOR X Y X × Y X Y X + Y X X 0 0 0 0 0 0 0 1 0 1 0 0 1 1 1 0 1 0 0 1 0 1 1 1 1 1 1 1 - Các tiên đề: o Tính giao hoán:

➢ x + y= y + x

➢ x× y= y ×x o Tính kết hợp:

➢ (x + y )+ z =x+( y + z)

➢ (x× y)×z =x×( y× z) o Tính phân phối:

➢ x×( y + z )=x× y + x×z

➢ x +( y ×z )=(x+ y )×( x + z ) o Phần tử đồng nhất: ➢ x +1=1 ➢ x +0=x ➢ x× 1=x ➢ x× 0=0 o Phần tử bù: ➢ x + x=1 ➢ x× x=0

- Các định lý cơ bản: ➢ ´x=x

➢ x + x=x ➢ x× x=x

➢ x + y=x × y

➢ x× y=x + y

- Cách định lý hấp thụ:

➢ x + x× y=x

➢ x× ( x+ y )=x

➢ x +( x× y )=x+ y

➢ x× ( x+ y )=x× y

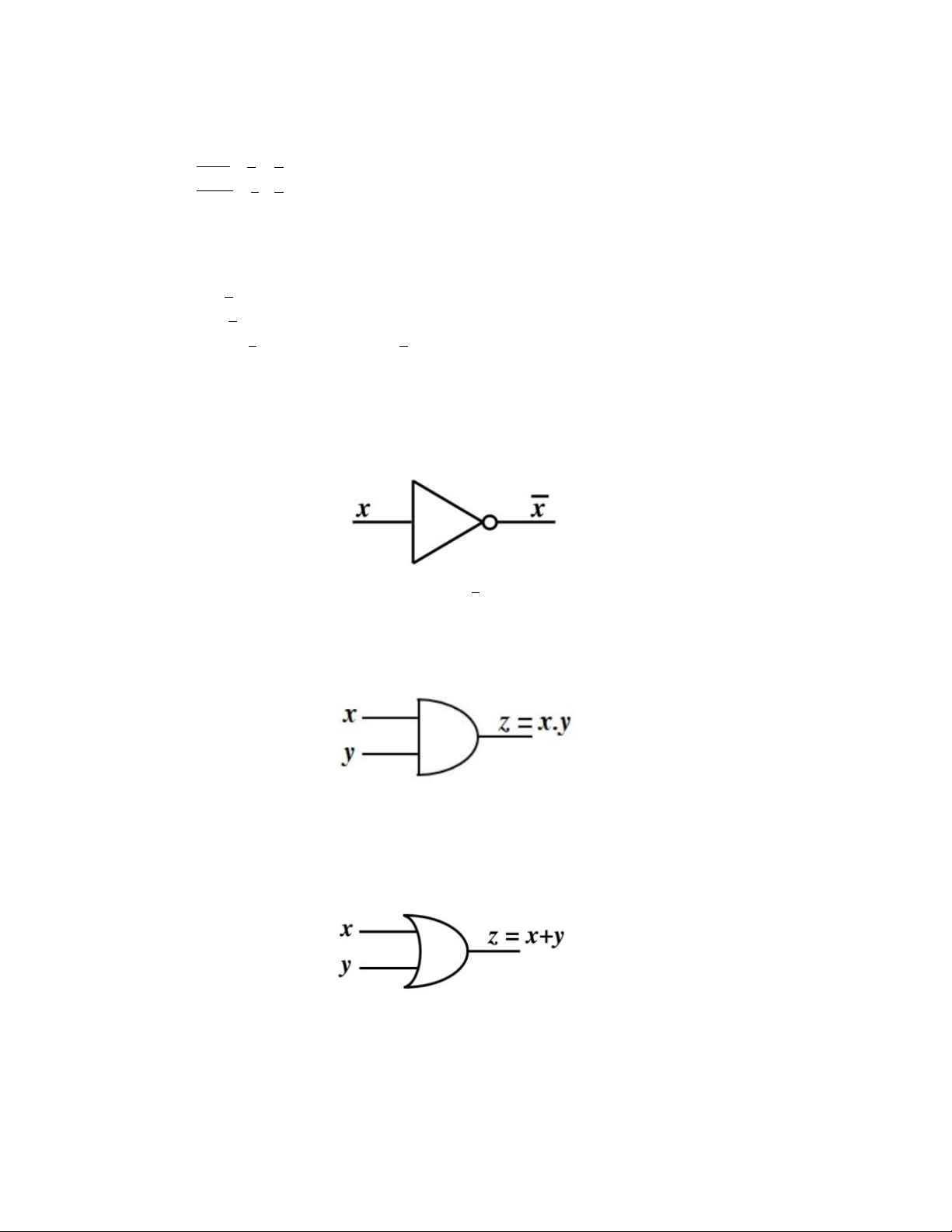

➢ x× y + x×z + y ×z=x × y + x ×z 4. Cổng logic - Cổng đảo (NOT): o Ký hiệu:

o Phương trình logic: y=x - Cổng (AND): o Ký hiệu:

o Phương trình logic: z=x × y - Cổng (OR): o Ký hiệu:

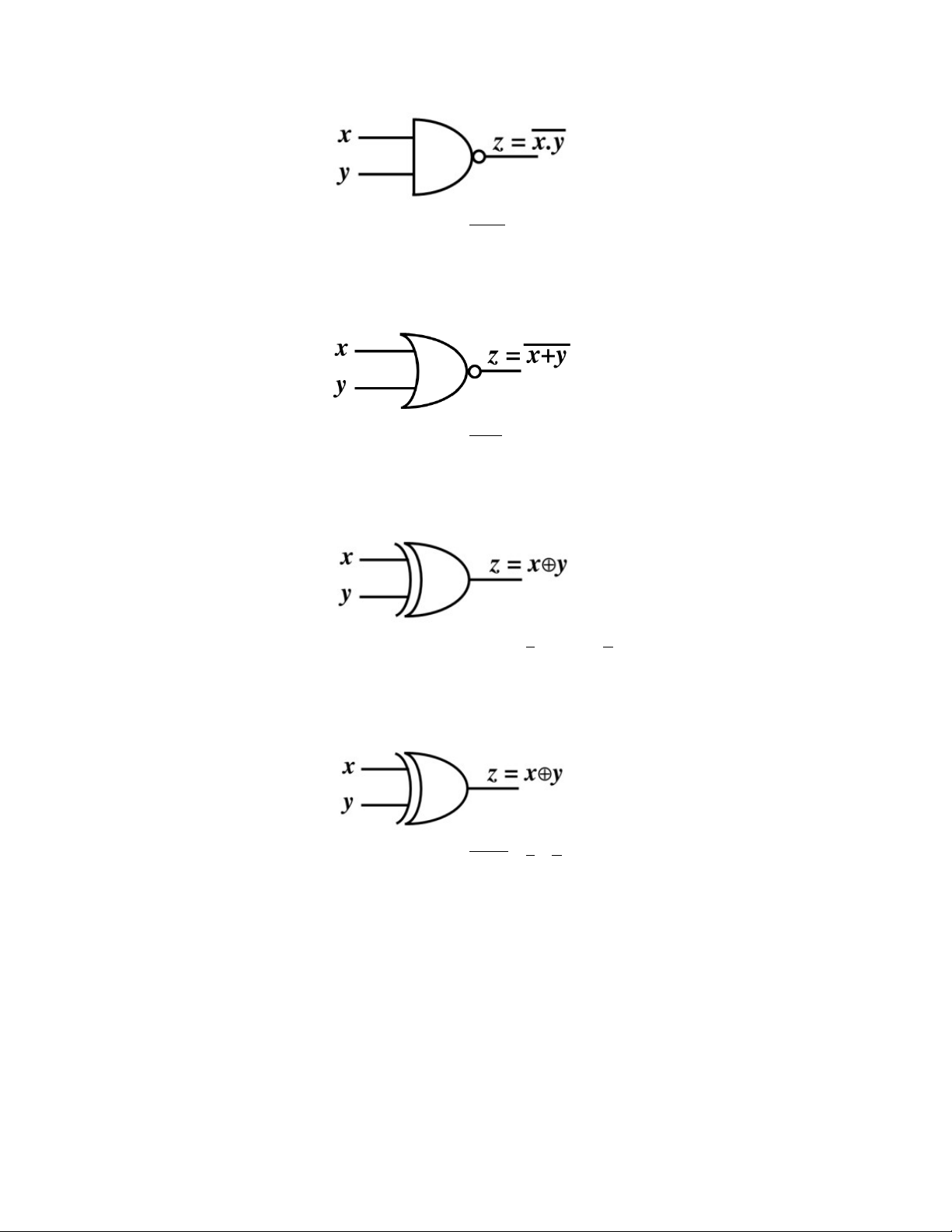

o Phương trình logic: z=x + y - Cổng (NAND): o Ký hiệu:

o Phương trình logic: z=x × y - Cổng (NOR): o Ký hiệu:

o Phương trình logic: z=x + y - Cổng XOR: o Ký hiệu:

o Phương trình logic: z=x ⊕ y=x× y + x× y - Cổng XNOR: o Ký hiệu:

o Phương trình logic: z=x ⊕ y=x× y + x× y

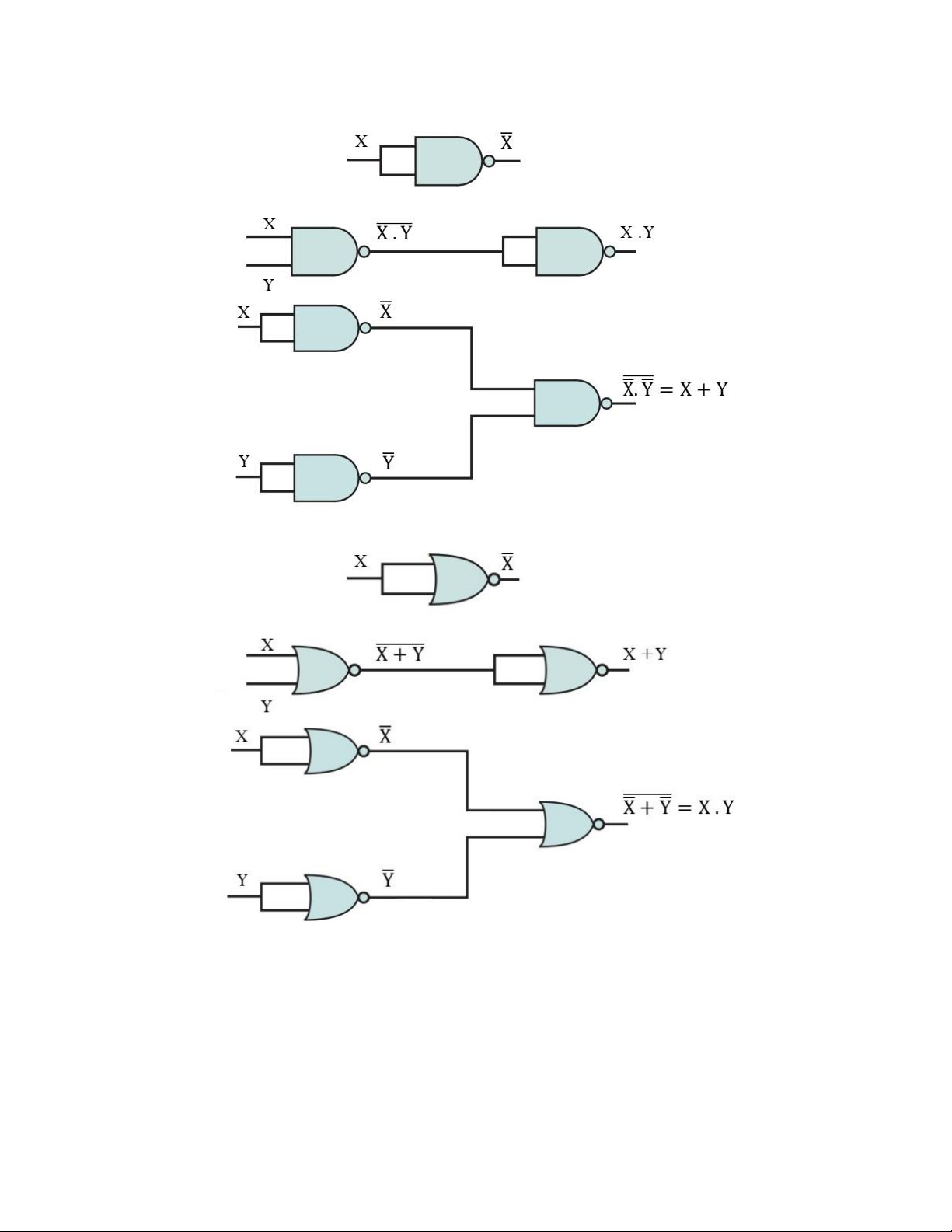

- Chuyển đổi giữa các cổng logic:

5. Chức năng của máy tính:

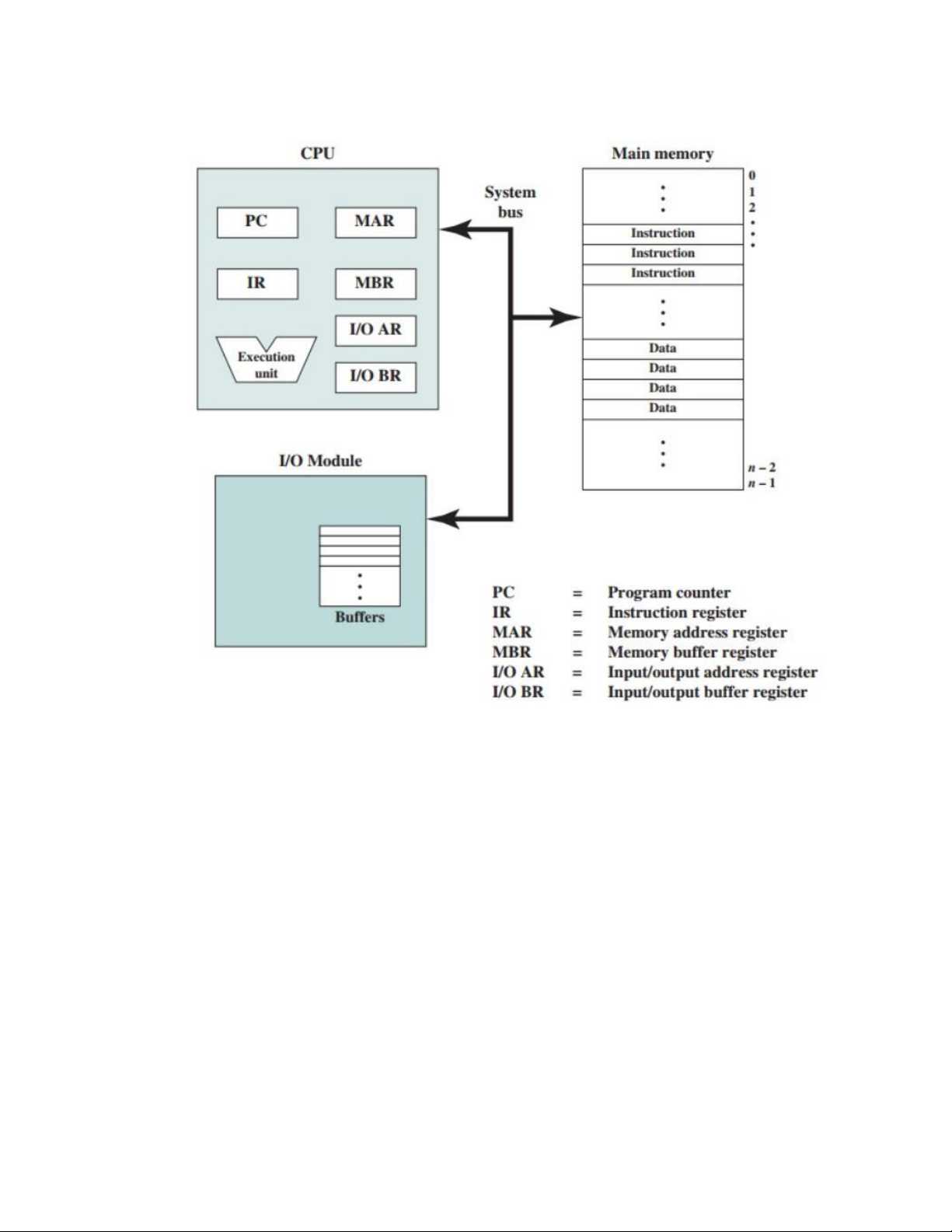

- Các thanh ghi(registers):

o PC: địa chỉ của câu lệnh tiếp theo.

o IR: địa chỉ của câu lệnh đang được thực thi.

o MAR: địa chỉ ô nhớ đang được truy cập trong bộ nhớ.

o MBR: nội dung của ô nhớ đang được truy cập trong bộ nhớ. o IO AR: địa chỉ I/O. o IO BR: nội dung I/O.

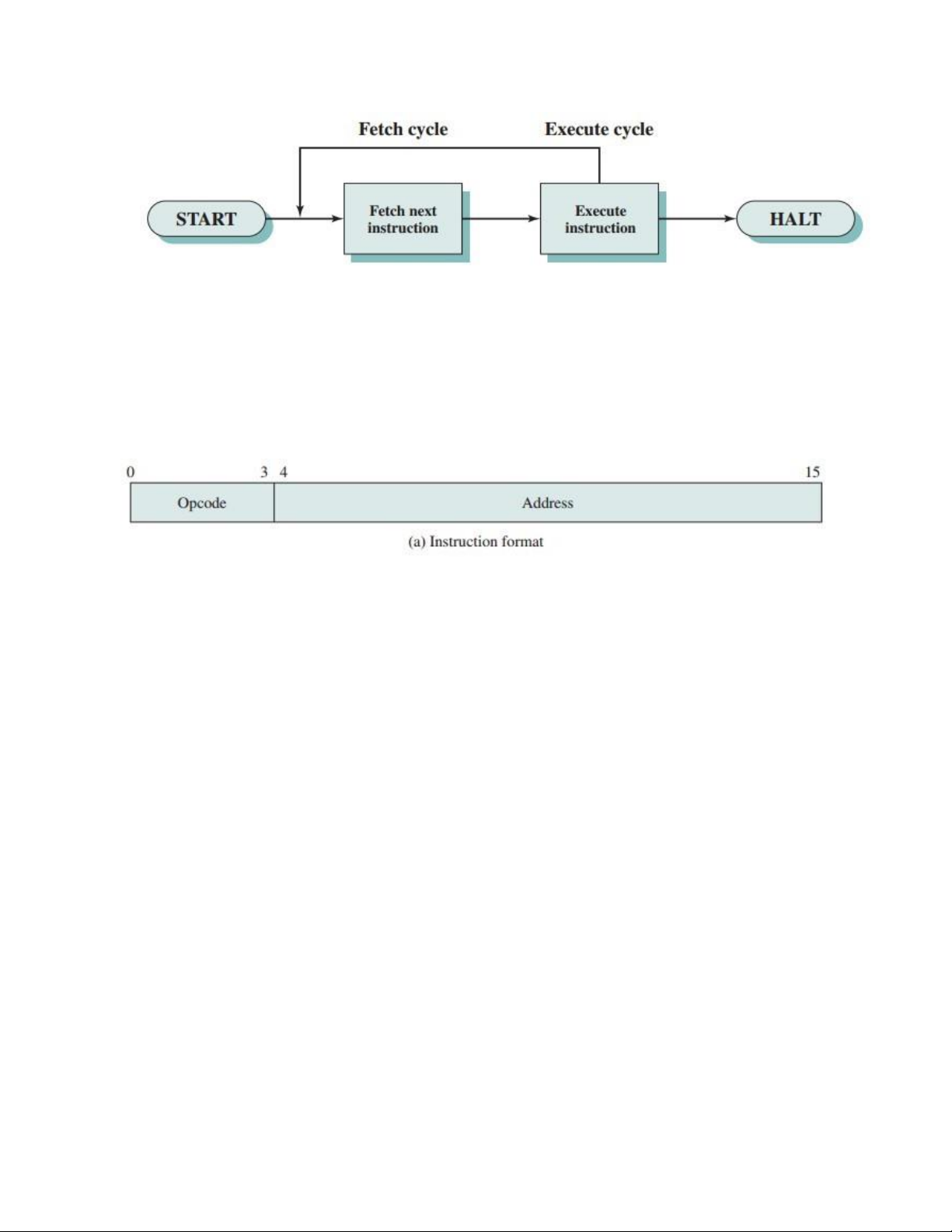

- Chức năng cơ bản là thực thi chương trình, tức là thực thi lệnh(instruction).

- Xử lí lệnh: đọc lệnh từ bộ nhớ và thực hiện từng lệnh.

- 4 loại câu lệnh:

o Truyền dữ liệu giữa bộ nhớ và bộ xử lí.

o Truyền dữ liệu giữa I/O và bộ xử lí.

o Thực hiện phép toán số học hoặc logic trên dữ liệu. o Lệnh điều kiển. - Một số opcode:

o 0001(1): lấy AC từ bộ nhớ.

o 0010(2): lưu AC vào bộ nhớ.

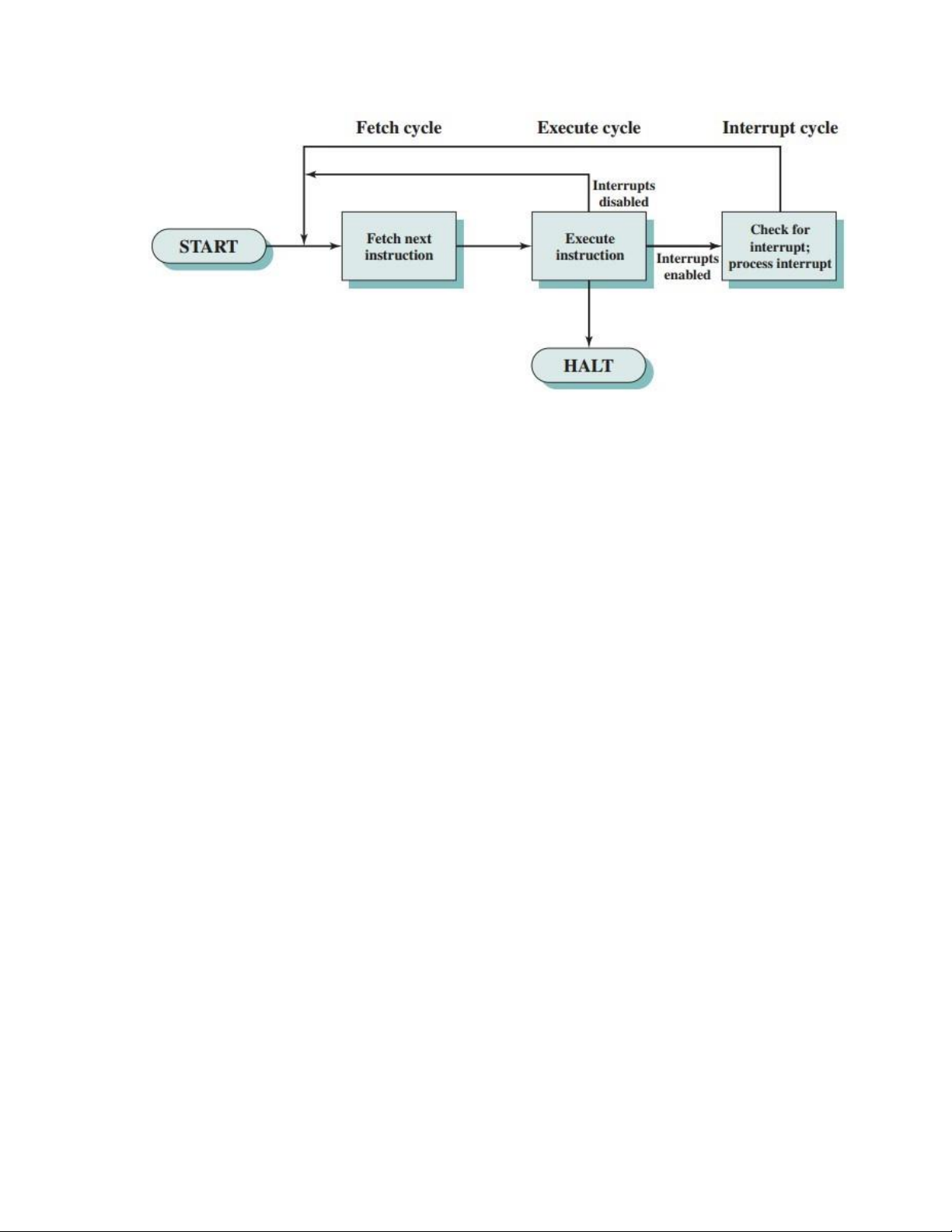

o 0101(5): thêm vào AC từ bộ nhớ. - Chu kì lệnh:

o Tính toán địa chỉ câu lệnh. o Lấy lệnh. o Giải mã lệnh.

o Tính toán địa chỉ toán hạng. o Lấy toán hạng. o Thao tác dữ liệu. o Lưu trữ toán hạng. 6. Ngắt(interrupts):

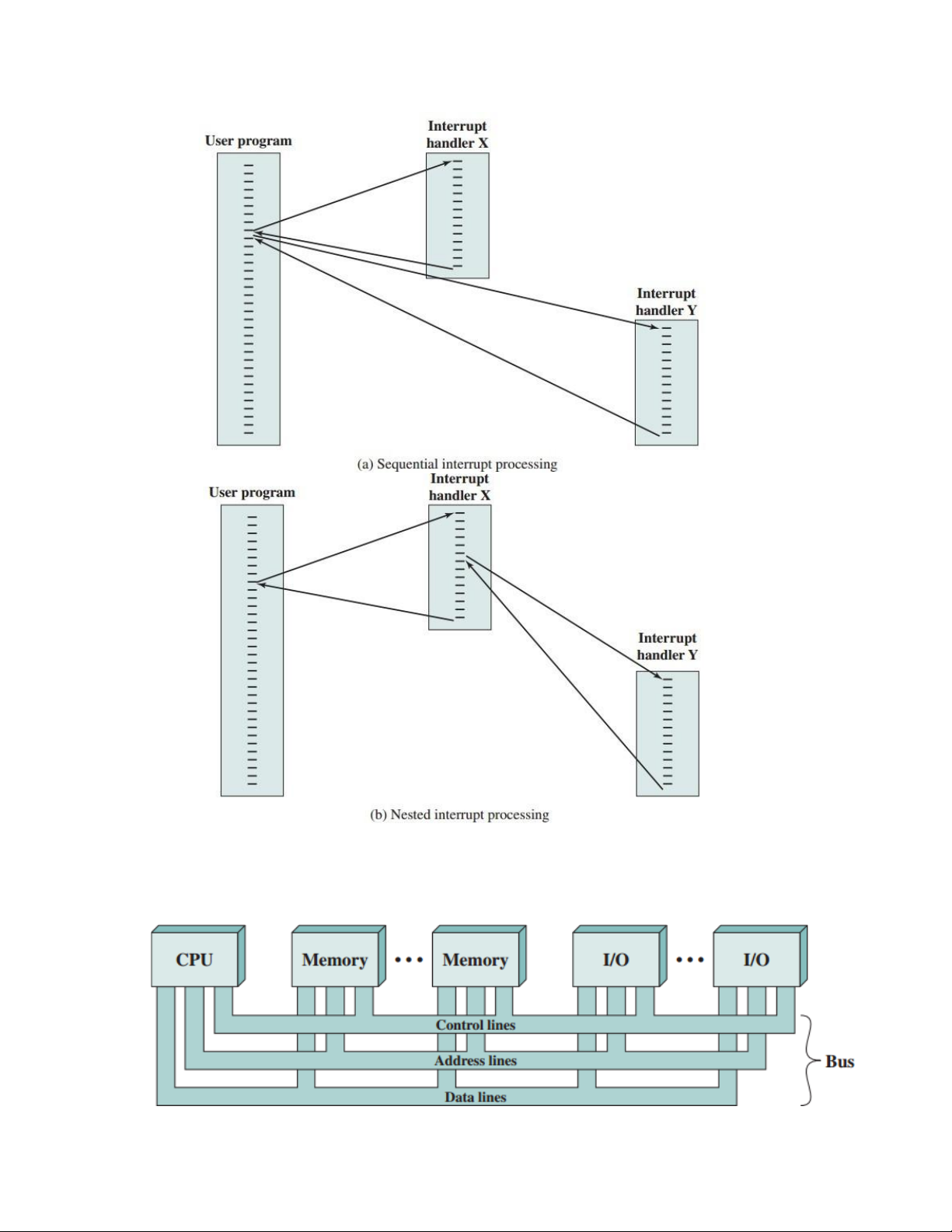

- Là một cơ chế mà các module khác(I/O, bộ nhớ) có thể

làm gián đoạn quá trình xử lí bình thường của bộ nhớ.

- Nhiều lệnh ngắt: 7. Bus interconnection:

- Đường kết nối các thành phần khác nhau của máy tính. - Dedicated bus:

o Dây dẫn riêng cho dữ liệu và địa chỉ.

o Có thể đưa địa chỉ và dữ liệu trên bus cùng lúc.

o Thông lượng cao, ít tranh chấp.

o Tăng kích thước và chi phí. - Multiplexed bus:

o Một đường có thể sử dụng ở thời điểm khác nhau

để chứa dữ liệu hoặc địa chỉ. o Ít đường bus hơn. o Mạch phức tạp hơn.

o Khả năng giảm hiệu suất.

8. Các loại địa chỉ:

- Immediate: operand là một giá trị cụ thể.

- Direct: operand là giá trị của một biến.

- Indirect: địa chỉ của operand được lưu trong một biến.

- Register: operand là một thanh ghi.

- Register indirect: địa chỉ của operand được lưu trong thanh ghi.

- Displacement: thay thế giá trị của biến bằng một biểu thức.

- Implicit: operand được lưu trong một stack register.

9. Cấu trúc và chức năng của bộ xử lí:

- Yêu cầu của bộ xử lí: o Tìm nạp lệnh. o Giải mã lệnh. o Tìm nạp dữ liệu. o Xử lí dữ liệu. o Ghi dữ liệu. - Thanh ghi:

o Thanh ghi hoặc tập hợp thanh ghi chứa các thông tin trạng thái.

o Các trường và cờ thông thường:

▪ Sign, zero, carry, equal, overflow, interrupt enable/ disable, supervisor.

o Các thông tin trạng thái để đưa ra quyết định rẽ nhánh.

- Chiến lược pipelining:

o Công thức speedup: n×k f 2 × f 1 n+k −1 o Trong đó:

▪ f1: tần số khi không thực hiện pipelining.

▪ f2: tần số khi thực hiện pipelining. ▪ n: số câu lệnh.

▪ k: số phần pipelining. - Pipelining hazards: o Resource hazard. o Data hazard. o Control hazard.

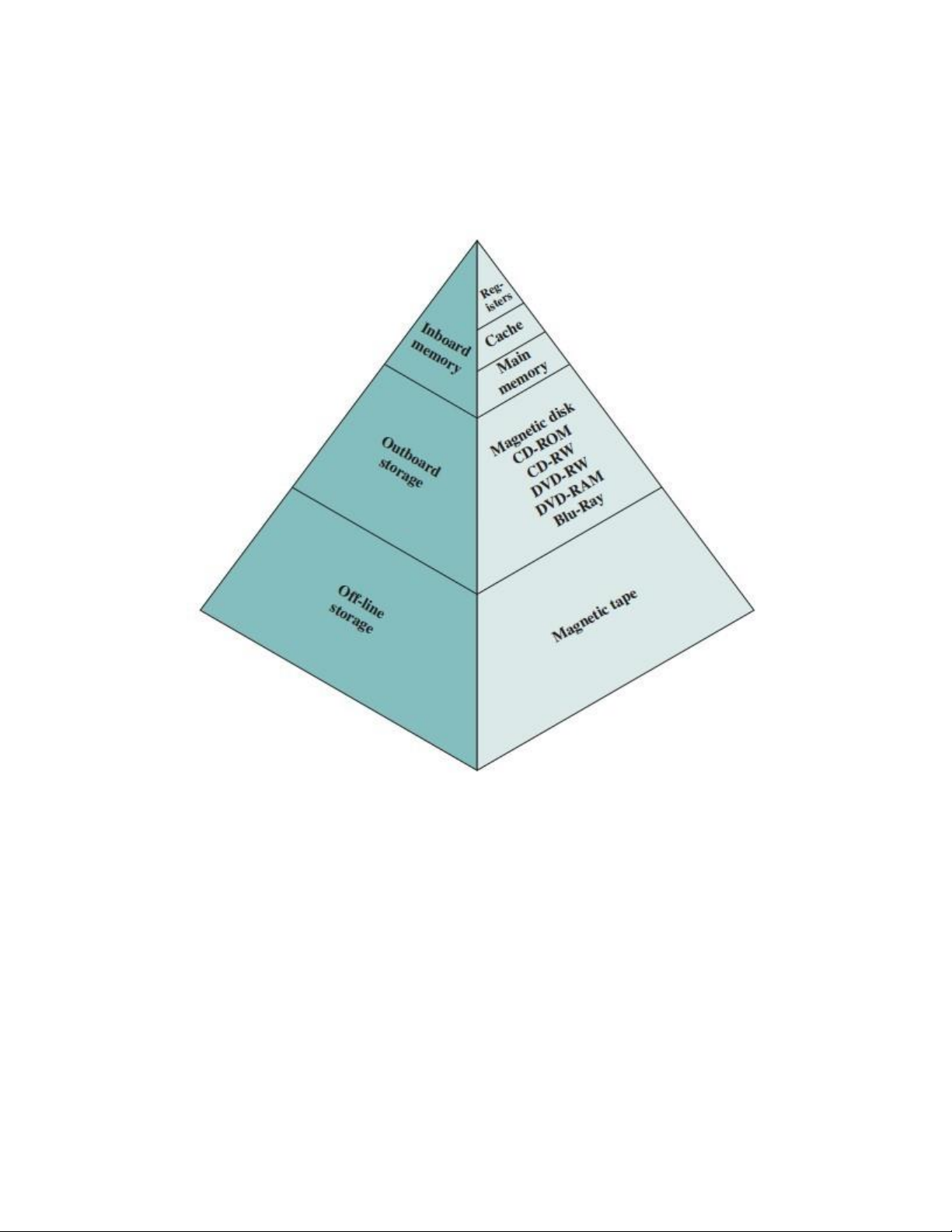

10. Hệ thống bộ nhớ máy tính:

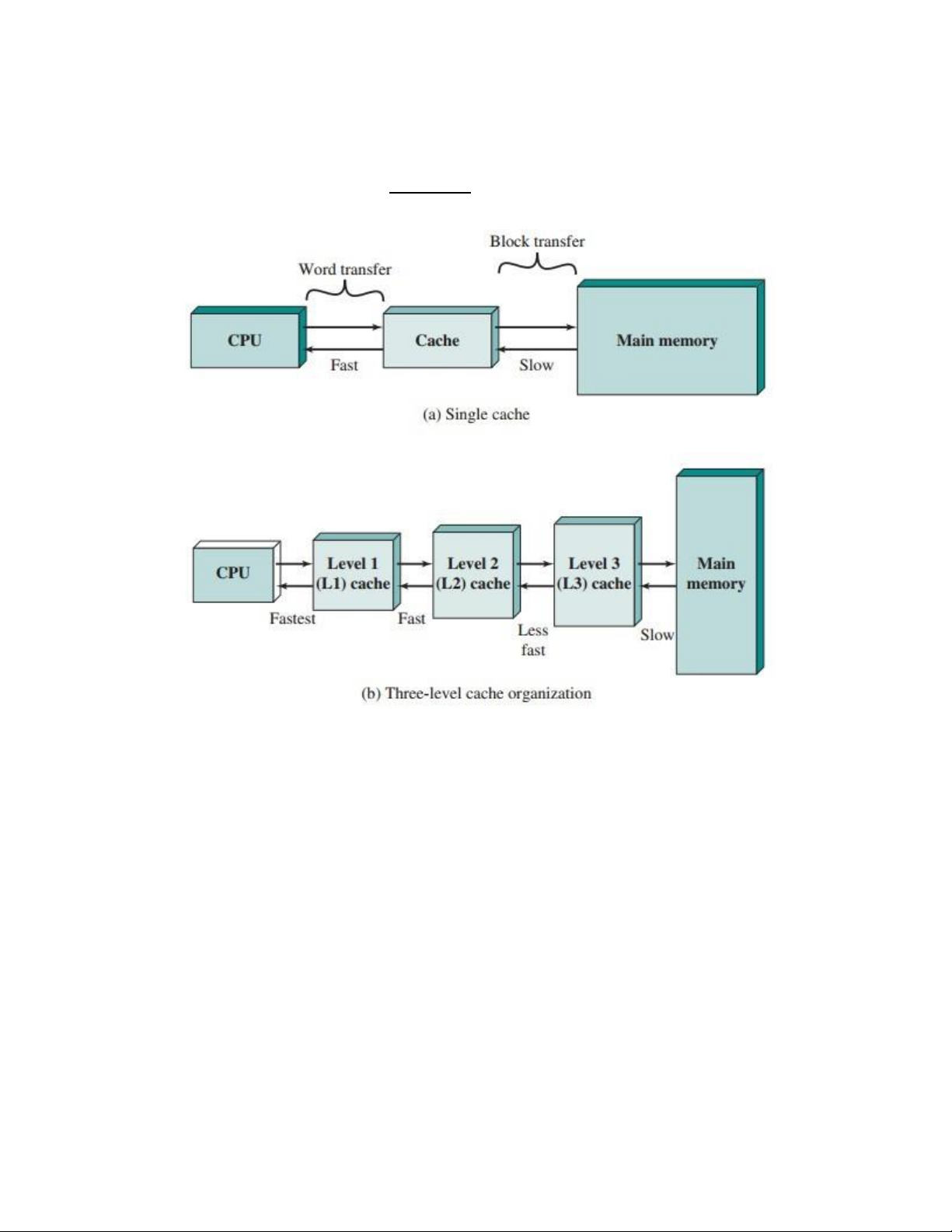

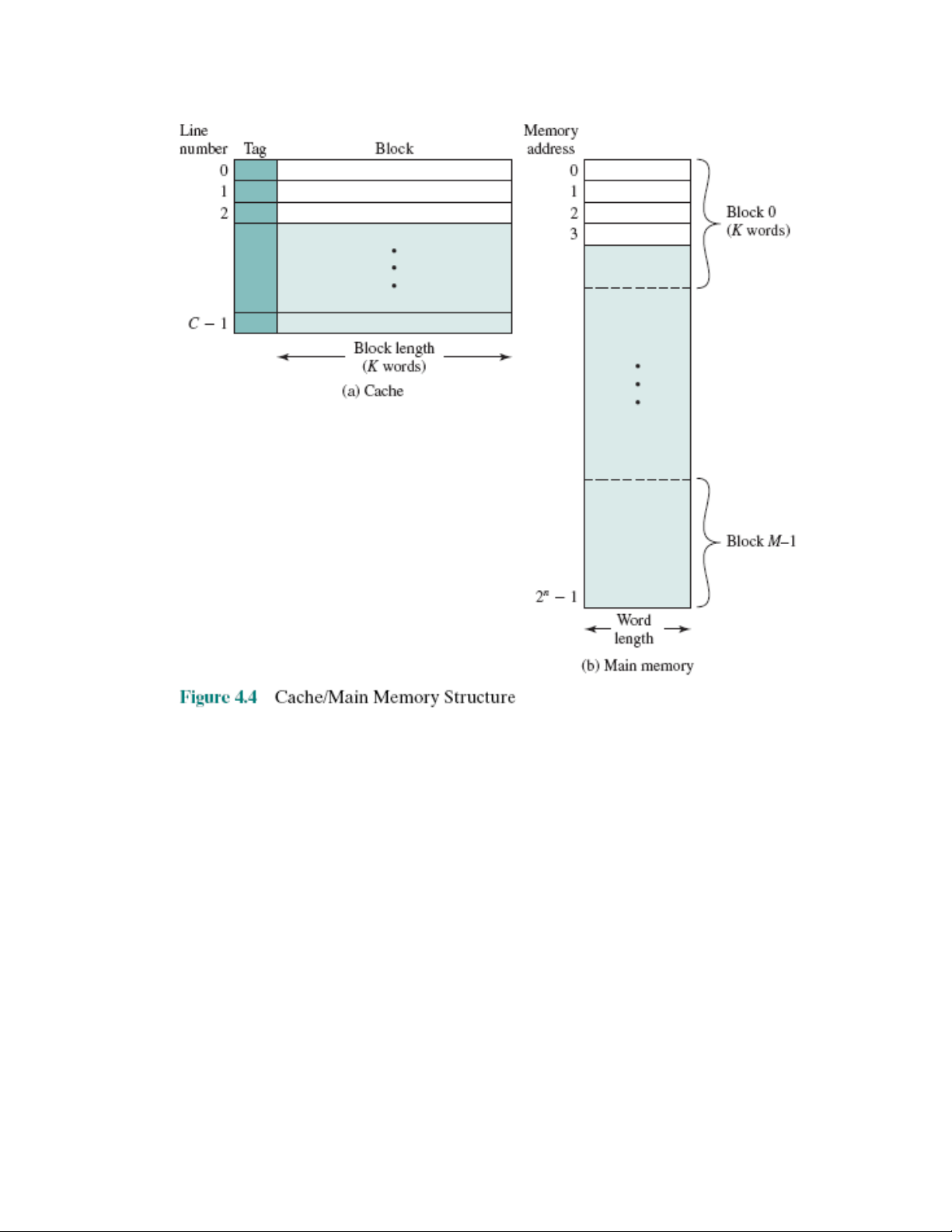

- Bộ nhớ đệm(cache):

o Là bộ nhớ tốc độ cao nằm giữa CPU và bộ nhớ chính

và giữ 1 bản sao của dữ liệu được sử dụng thường xuyên.

o Khi CPU muốn một giá trị dữ liệu từ bộ nhớ, nó sẽ tìm trong cache trước.

o Nếu dữ liệu nằm trong cache nó sẽ sử dụng dữ liệu đó.

o Nếu dữ liệu không nằm trong cache, nó sẽ sao chép

một dòng dữ liệu từ bộ nhớ vào trong cache và cung

cấp cho CPU những gì nó muốn.

o Cache hit: dữ liệu cần đã có trong cache.

o Cache miss: dữ liệu cần chưa có trong cache.

o Tỉ lệ hit: hit ratio= Hit Hit + Miss - Dòng cache: - Kích cỡ Cache: o Càng lớn càng tốt.

o Kích cỡ bị giới hạn bởi:

▪ Không gian trên chip xử lí. ▪ Hạn chế sản xuất. ▪ Trị giá. - Mapping:

o Thuật toán ánh xạ bộ nhớ chính vào dòng bộ nhớ đệm. o Direct mapping:

▪ Khối j trong bộ nhớ chính sẽ được tải vào dòng

i= jmod m (m là số line trong cache). ▪ Địa chỉ bộ nhớ: Tag Line Word

Độ dài bit Số khối của Số line của Số từ của 1 dòng cache một khối o Fully associative mapping:

▪ Một khối có thể tải vào bất cứ dòng nào trong cache. ▪ Địa chỉ bộ nhớ: Tag Word

Độ dài bit Số khối trong bộ nhớ Số từ của một khối o Set associative mapping:

▪ Mỗi cache gồm m set và mỗi set gồm k line. Một

khối có thể tải vào bất kì dòng nào trong 1 set nhất định. ▪ Địa chỉ bộ nhớ: Tag Set Word

Độ dài bit Số khối ứng Số set trong Số từ của với 1 set cache một khối - Replacement policy:

o Khi xảy ra miss cache, dữ liệu sẽ được sao chép vào 1

vị trí nào đó trong bộ nhớ đệm.

o Với set associative và fully associative, hệ thống phải

quyết định vị trí đặt dữ liệu và giá trị nào được thay thế. o Thuật toán thay thế:

▪ Nhập trước xuất trước.

▪ Ít sử dụng gần đây nhất.

▪ Ít sử dụng thường xuyên nhất. ▪ Ngẫu nhiên. - Các bộ nhớ bán dẫn: Bộ nhớ Loại Random - access memory Read – write memory (RAM) Read – only memory (ROM) Read only memory Programmable ROM (PROM) Read only memory Erasable PROM (EPROM) Read mostly memory Electrically erasable PROM Read mostly memory (EEPROM) Flash memory Read mostly memory - DRAM và SRAM: DRAM SRAM

Tạo ra từ các ô, lưu trữ dữ

Thiết bị kĩ thuật số sử dụng

liệu bằng cách sạc tụ điện

các phần tử logic như bộ xử lí

Sự hiện diện hay vắng mặt

Các giá trị nhị phân được lưu

của điện tích trong tụ được

trữ bằng cách sử dụng cấu

hiểu là bit nhị phân 1 hoặc 0 hình cổng logic flip-flop

Yêu cầu sạc làm mới định kì

Lưu trữ dữ liệu miễn là có

để duy trì lưu dữ liệu nguồn cung cấp cho nó Nhỏ, rẻ hơn, chậm hơn

Lớn, đắt hơn, nhanh hơn

Thường sử dụng cho bộ nhớ Thường sử dụng cho bộ nhớ chính cache

- Dung lượng và tổ chức:

o Dung lượng thường biểu thị bằng bit.

o Tổ chức thường biểu thị bằng word ×acess width

o Hai thiết bị có thể có cùng dung lượng, nhưng khác nhau về tổ chức.

▪ 1 Mb (256 K× 4 ) – 256K từ, mỗi từ 4 bit.

▪ 1 Mb(128 K ×8) – 128K từ, mỗi từ 8 bit. - Note: 1 byte = 8 bits.

- Kích thước RAM được đo bằng đơn vị nhị phân, trong khi

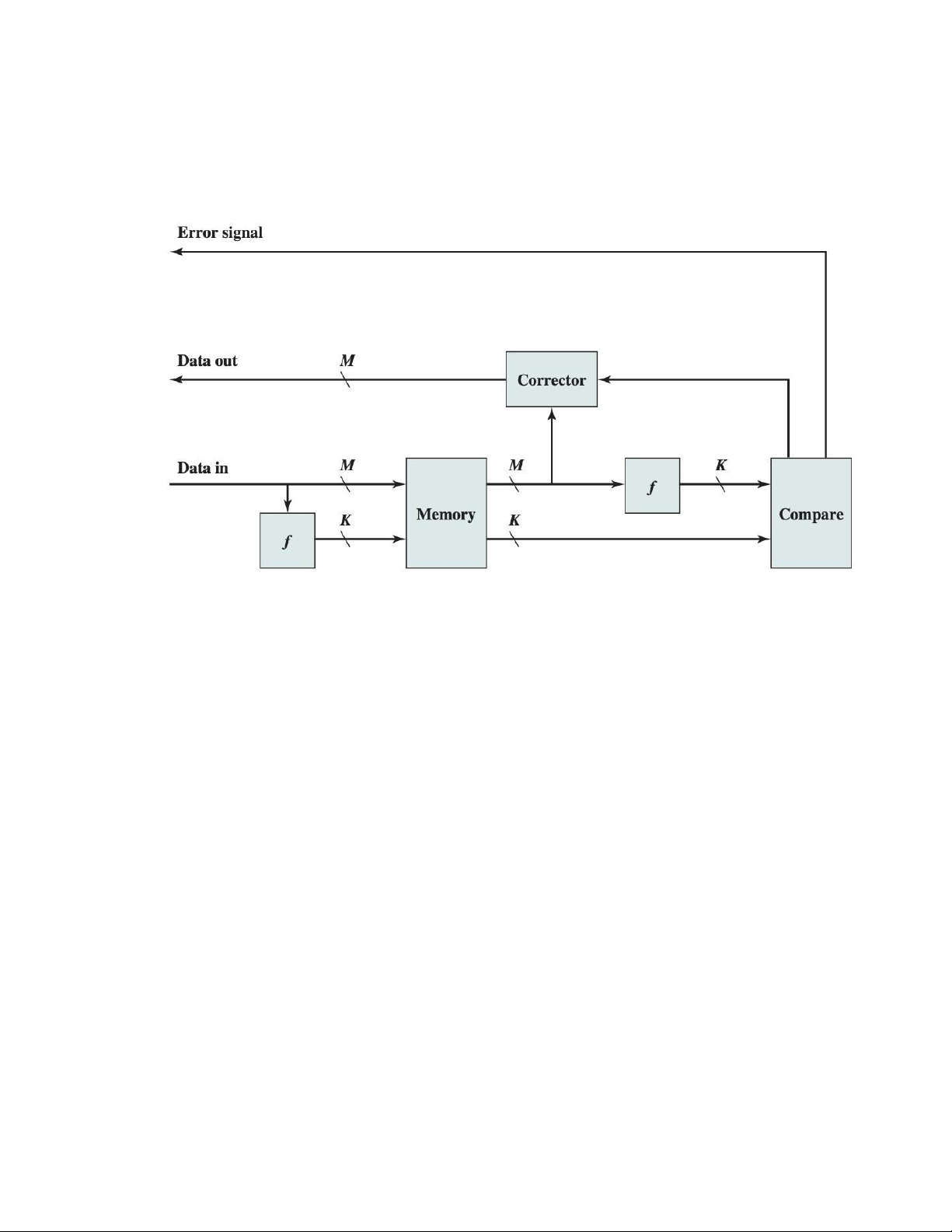

kích thước ổ cứng được đo bằng đơn vị thập phân. - Sửa lỗi:

- Mã sửa lỗi hamming: