Preview text:

ECE 485/585 Microprocessor System Design Portland State University Mark G. Faust Module: Introduction 2 Topics Course Introduction Technology Trends Units 3 Part of Two Quarter Sequence

• ECE 485/585 Microprocessor System Design – System Issues • Memory

Not a course on microprocessors (ECE 371) • Caches

Not a course on interfacing (ECE 372) • Virtual Memory

Assumes familiarity with at least one microprocessor • Buses

Comfortable with (generic) assembly language • I/O Devices: Disks • Reliability

• ECE 486/586 Computer Architecture – Processor Oriented • CPU Datapath and Control • Computer Arithmetic • Pipelining • Branch Prediction • Performance Measurement 4 Quick Survey

• Taken an operating systems course?

• Which microprocessor family are you familiar with? – Intel x86 – ARM – MIPS – Other • C/C++ Programming • Verilog? VHDL?

• Have you heard of, can you define/explain…

– Two way set associative cache

– Demand paged virtual memory – Vectored interrupt – TLB 5 Are Caches Desirable?

Computer architecture doesn’t arise in a vacuum. It’s a consequence of the

constraints imposed by the real world technology and components (e.g.

microprocessors, memory, disk, I/O devices) that are available (e.g. memory)

or demanded by the market (e.g. wireless, graphics). For example, if you had

terabytes of persistent storage with access times of 1ns you’d have little need

for L1, L2 caches, swapping, etc.

Just like building architecture, we’re dealing with the materials (components,

subsystems) . The pyramids weren’t made of timber. So, you’ll find

architectural decisions from past designs that wouldn’t necessarily be made the same way today. 6

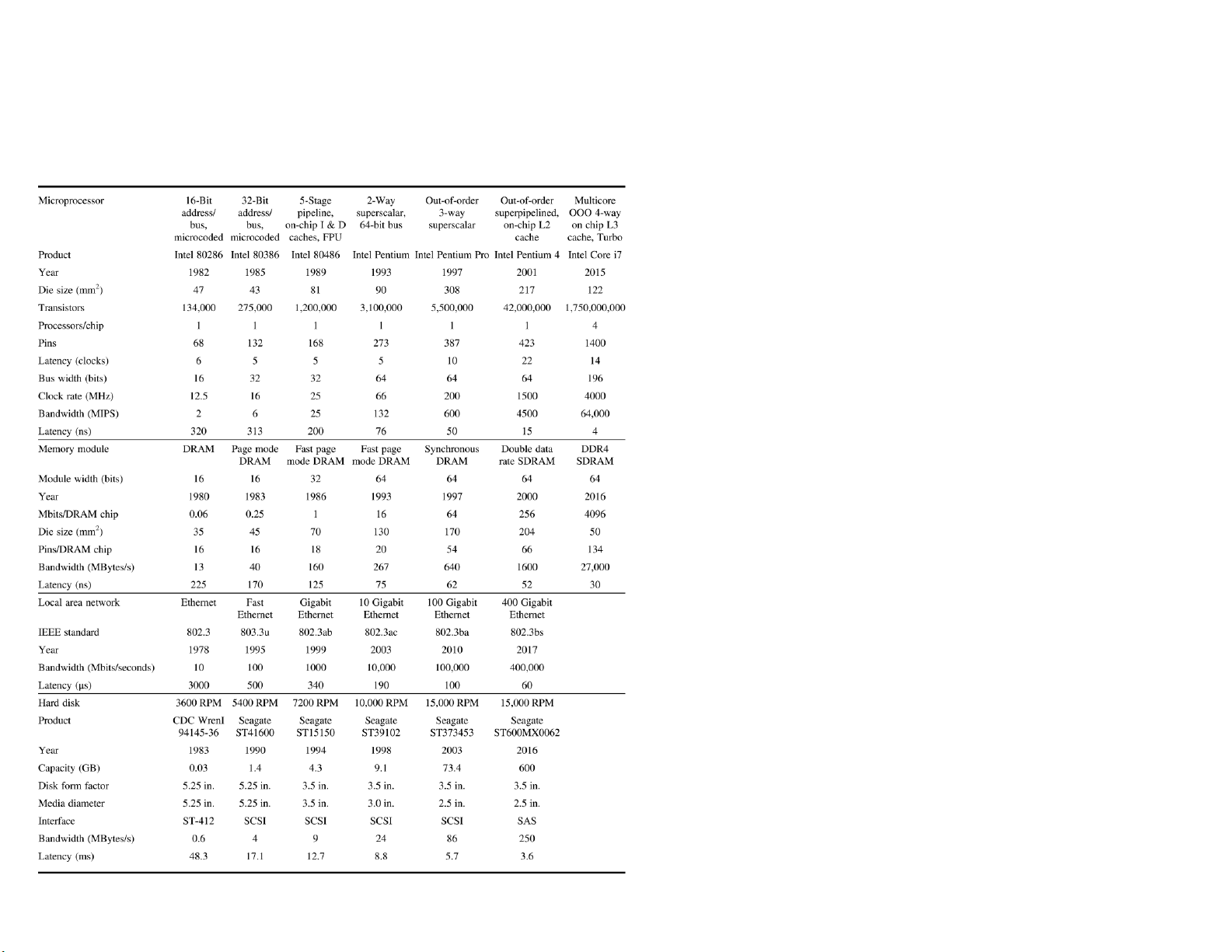

Computer Engineers must be aware of technology trends Process technology

• Transistor density increases by ~ 35%/year

• Die size increasing by ~10-20%/year

• Wafer size increasing (step : 8” 12”) DRAM density

• ~40-60% density increase per year

• Cycle time reduced by 1/3 every 10 years

• Bandwidth increases at 2x rate of latency decreasing

• Evidence rate of capacity increase slowing Magnetic disk technology

• >100% density increase annually since 1990

• Access time reduced 30% in 10 years Networking technology

• Bandwidth and latency (bandwidth primary focus)

• Accelerated in recent years (1Gb Ethernet vs 100 Mb availability) 7

Revised from Patterson, “Latency lags bandwidth”, CACM 47:10, October, 2004

Exponential Growth Doesn't Go Forever Moore's law

doubling of transistors every 1-2 years Dennard scaling

power density constant as transistor size decreases Areal density in HDDs 30% - 100% improvement/year 8 This Course • No textbook

– No single book or even half dozen books covers the content

– Some content is so current no textbooks cover the material yet

• Trade-off between timely publication and accuracy • Will rely on – Lecture slides

– Links to articles, websites, datasheets

• Lots of real world examples – Latest technology – Not always

• Concepts sometimes more easily introduced and understood in context of older, simpler systems

• Same techniques often used in more recent systems

• In some cases the functionality is preserved intact

• Studying both older and newer systems allows us to see the evolution of

features over time and understand the reasons for that evolution 9

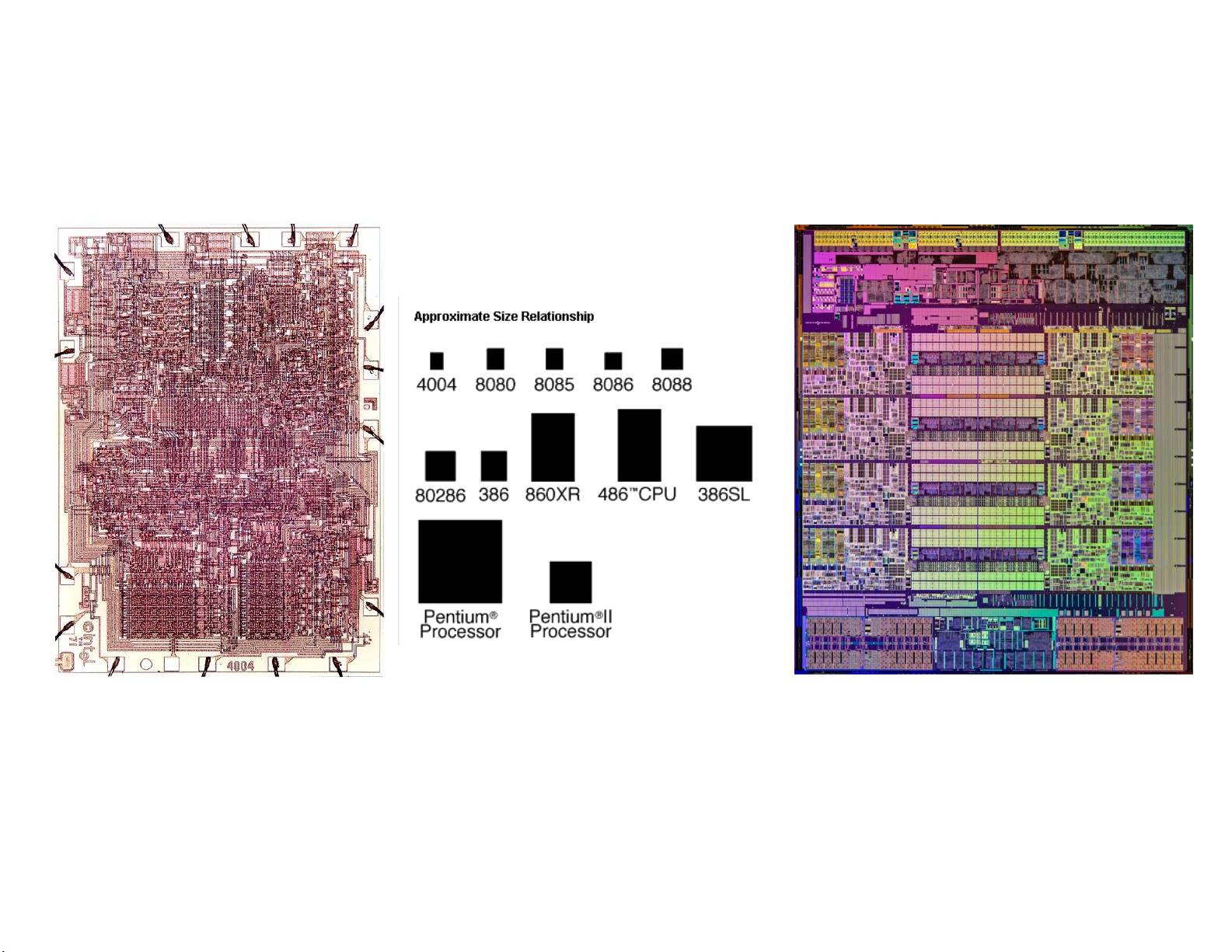

Evolution of Intel Microprocessors Intel 4004 (November 1971) Intel Core i7-5960X [2,300 transistors] 8086: 29,000 [2,600,000,000 transistors] Xeon: 286,000,000 10 Units B – bytes

What is the size of a memory described as 2GB? b – bits

Size of memory is described in powers of 2. 2GB = 230 bytes B/s – bytes/second Why? bps – bits per second

If we use n address lines (bits) then we naturally have 2n addressable locations

What is the bandwidth of a bus described as transferring 8GB/s?

Speed of bus is described in powers of 10. 8GB/s = 8 x 109 bytes/second Why?

Bandwidth is frequency x data path width. 1 MHZ = 106 Hz. 1 byte/period = 1MB/s

What is the capacity of a disk drive described as 4TB?

Disk drives are/were often described in powers of 10 (!). 4TB = 4 x 1012 bytes Why?

Hard disk drives (HDDs) and flash-based solid state drives (SSDs) are weird (marketing

won). Though "addresses" are n bits and thus there are 2n blocks (locations), expressing

this as a power of 10 yields what appears to be a bigger number. A 4TB (4 x 1012 byte)

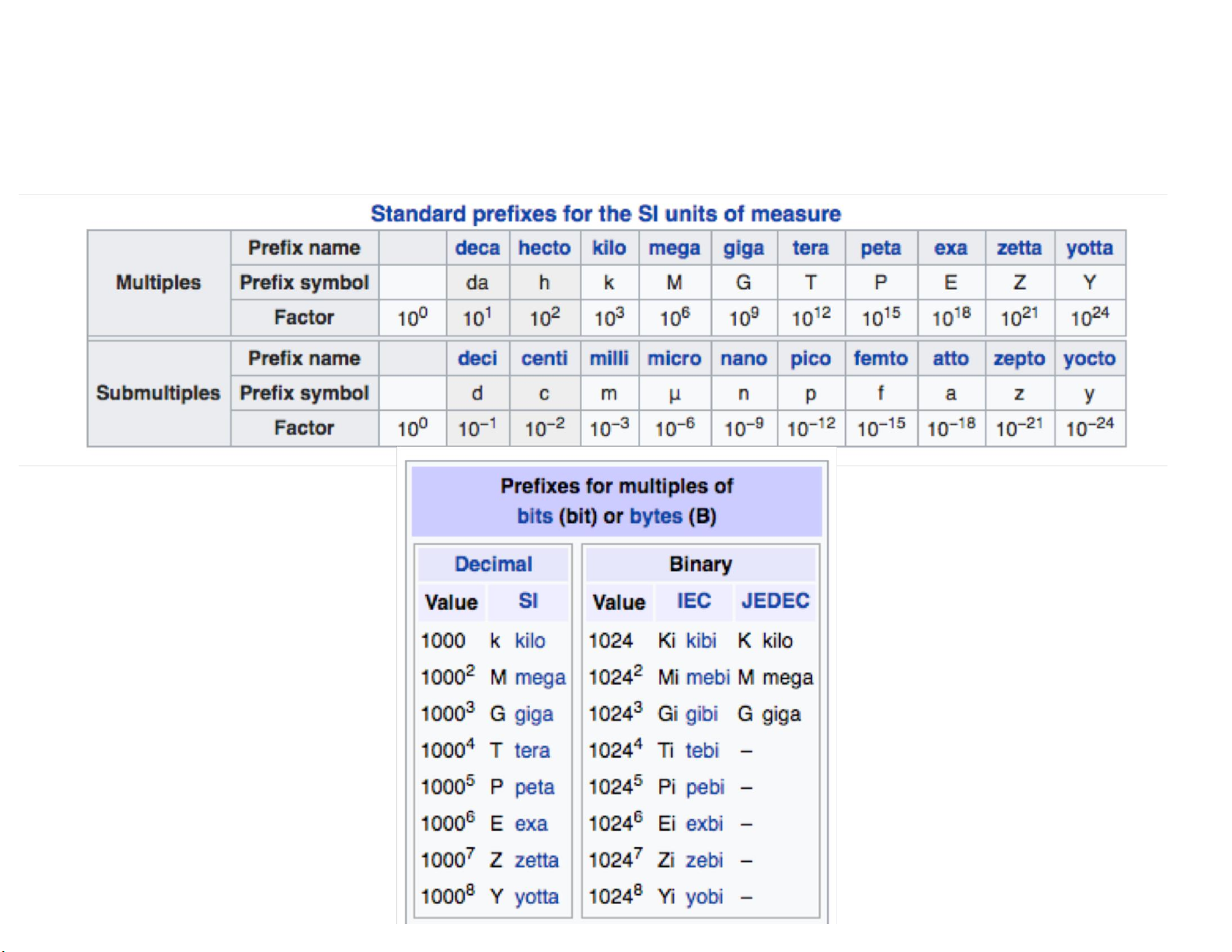

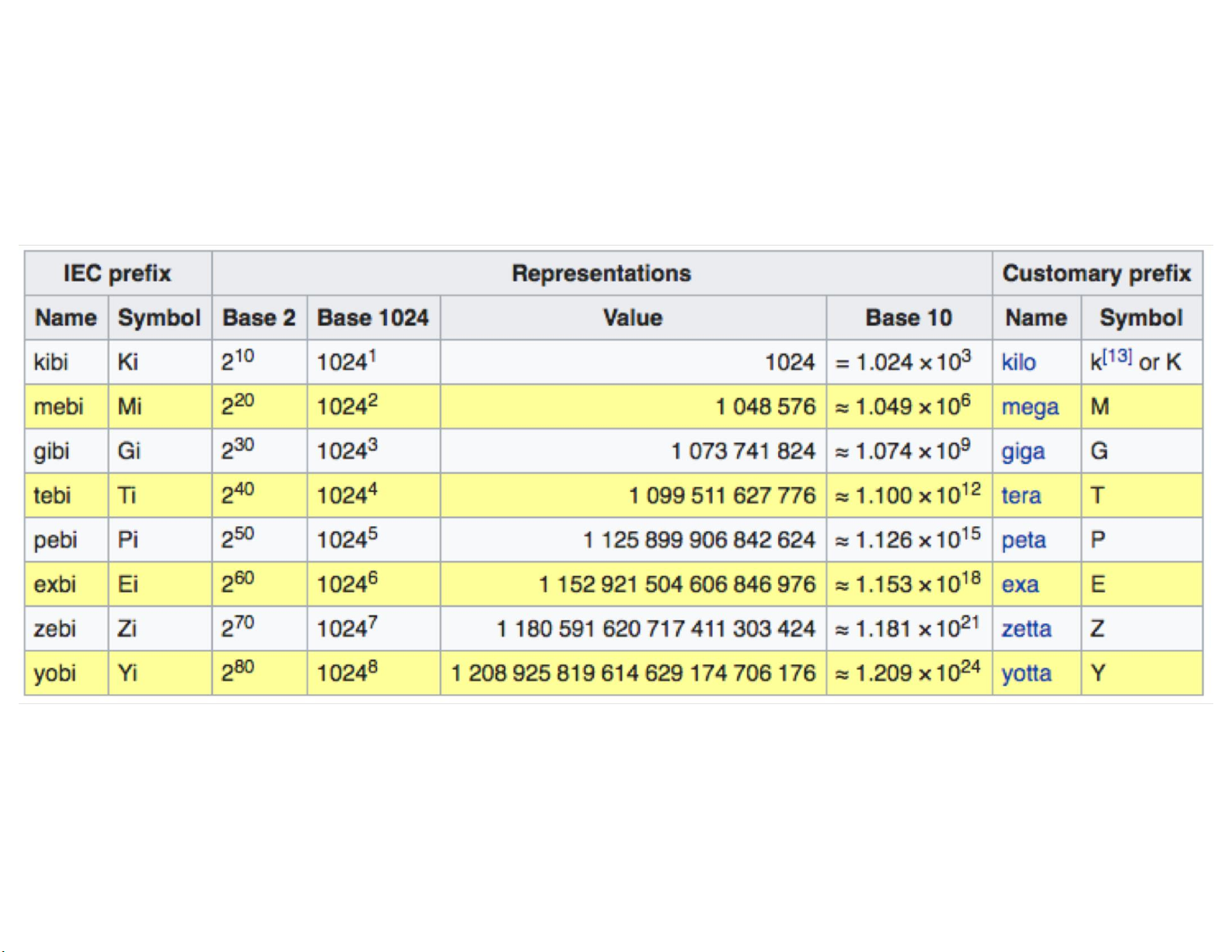

drive has "only" ~3.64 x 2040 bytes (3.64 TB binary). 4TB sounds bigger than 3.64TB. 11 SI and IEC Units 12 IEC Units 13 Units Exceptions

• Seagate now seems to express disk drive data transfer rates in both SI and IEC units

• Optical Compact Discs (CDs) use IEC units: MB = 10242 (220) bytes

• Optical DVDs (like HDDs and SSDs) use SI units: GB = 10003 (109) bytes 14