Preview text:

Nguyễn Trọng Luật – BM Điện Tử - Khoa Điện-Điện Tử - ĐH Bách Khoa TP. HCM

BÀI TẬP CÓ LỜI GIẢI – PHẦN 2

MÔN KỸ THUẬT SỐ Bộ môn Điện tử

Đại Học Bách Khoa TP.HCM Bài 1

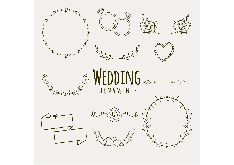

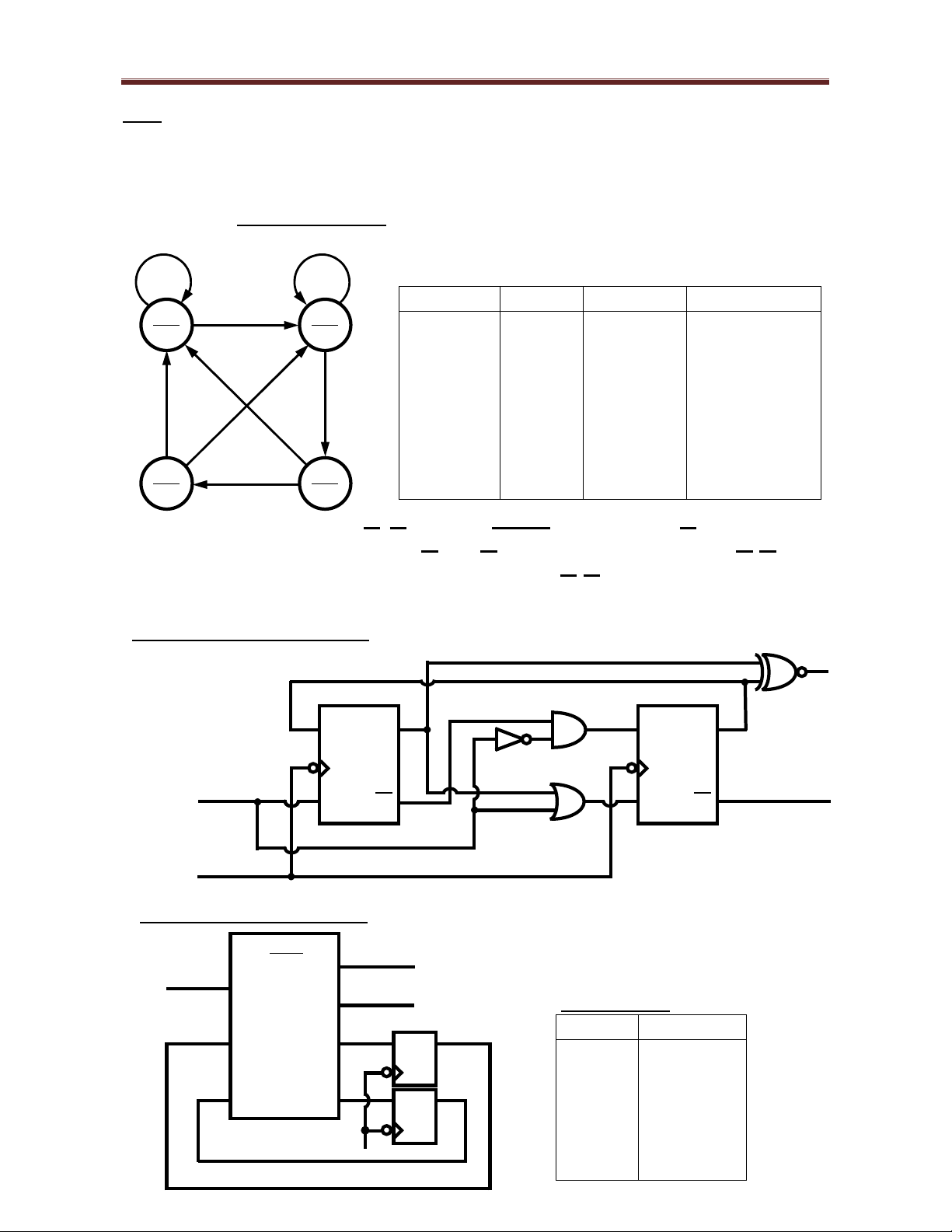

Cho maïch logic nhö hình veõ. Khaûo saùt daïng tín hieäu Y, Z, T theo tín hieäu A, B, C. Bieát

raèng giaù trò ban ñaàu ngoõ ra Q cuûa choát D vaø Flip Flop D ñeàu baèng 1. D Q Y A EN Q Z B D Q T CK Q C

T = Z ⊕ C = Z ⊕ C A B C Y Z T 1

Nguyễn Trọng Luật – BM Điện Tử - Khoa Điện-Điện Tử - ĐH Bách Khoa TP. HCM Bài 2

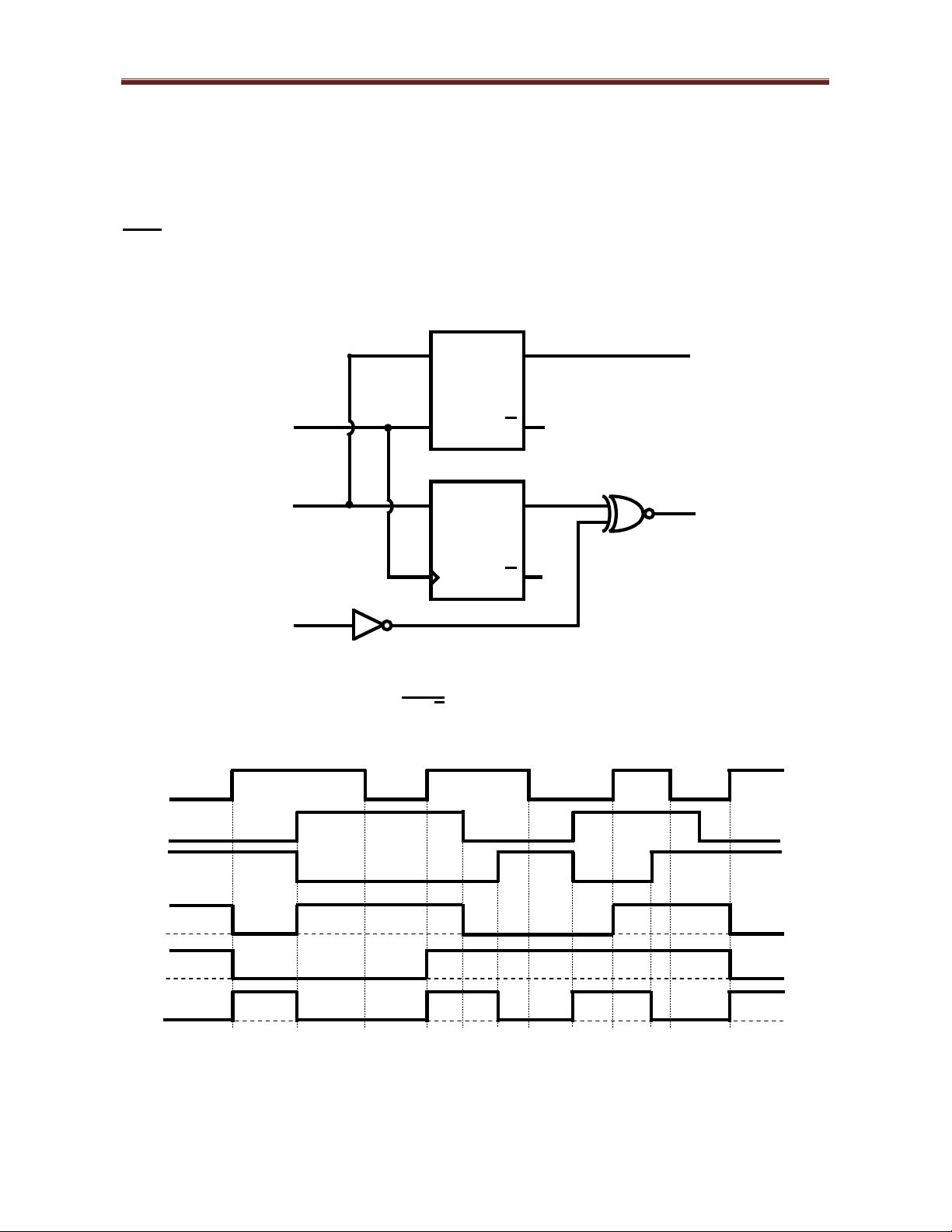

Söû duïng JK.FF coù xung clock kích theo caïnh leân, ngoõ vaøo Preset vaø Clear tích cöïc logic

0 (tích cöïc thaáp), thieát keá bộ ñếm noái tieáp (boä ñeám baát ñoàng boä) 3 bit QAQBQC (QC laø LSB) coù

giaûn ñoà traïng thaùi nhö hình veõ. QAQBQC 111 QA QB QC 1 0 1 1 1 0 110 000 1 1 1 0 0 0 0 0 1 001 101 0 1 0 Z = QA QB = QA + QB (Tích cöïc thaáp)

Töø giaûn ñoà traïng thaùi ta coù ñaây laø boä ñeám leân coù daõy ñeám tuaàn hoaøn: 101, 110, 111, 000, 001 QC QB QA (msb) 1 Pr Pr Pr 1 J Q 1 J Q 1 J Q CK CK CK 1 K Q 1 K Q 1 K Q Cl Cl Cl 1 1 Bài 3

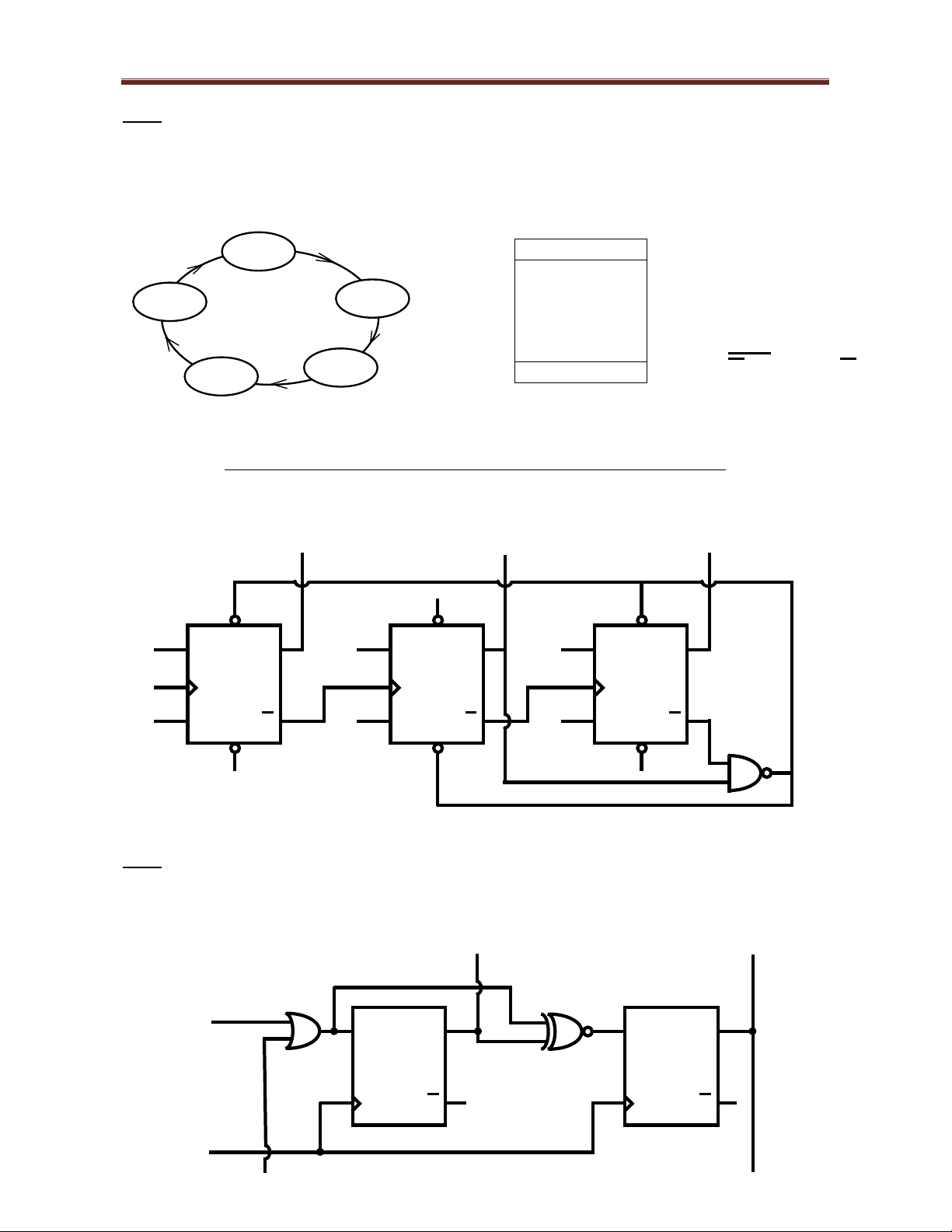

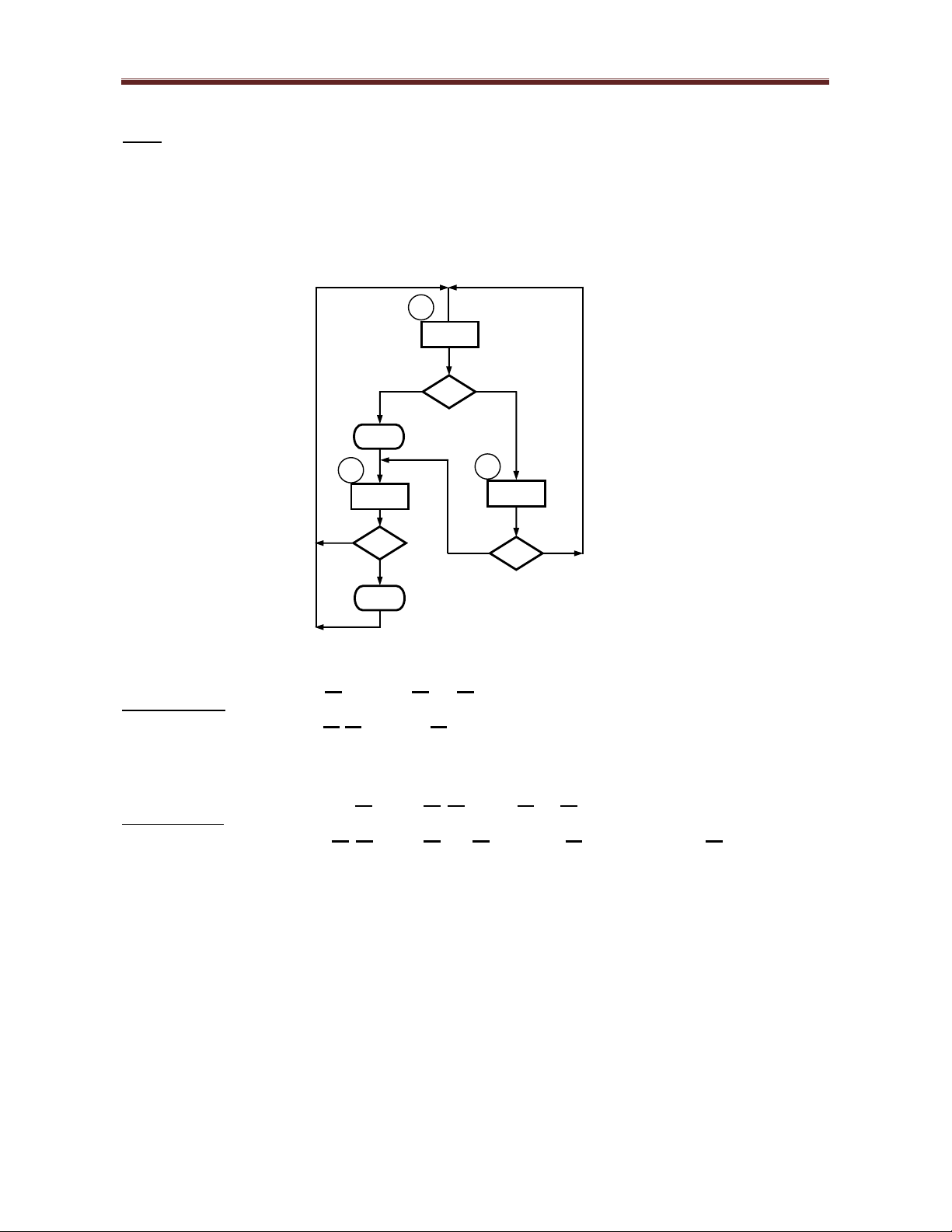

Xaùc ñònh giaûn ñoà traïng thaùi cuûa heä tuaàn töï goàm 1 ngoõ vaøo X vaø 2 T-FF Q1, Q0 nhö hình veõ Q0 Q1 X T Q T Q CK Q CK Q CK 2

Nguyễn Trọng Luật – BM Điện Tử - Khoa Điện-Điện Tử - ĐH Bách Khoa TP. HCM

Töø sô ñoà ta coù: T0 = X + Q1 vaø T1 = (X + Q1) ⊕ Q0

Laäp baûng chuyeån traïng thaùi: X Q1 Q0 T1 T0 Q+1 Q+0 0 0 0 1 0 1 0 0 0 1 0 0 0 1 0 1 0 0 1 1 1 0 1 1 1 1 0 0 1 0 0 0 1 0 1 1 0 1 1 1 1 0 1 1 0 0 1 1 1 1 1 1 1 1 0 0

Ta coù giaûn ñoà traïng thaùi: Q1Q0 Q0Q1 00 X = 0 10 Hoặc 00 X = 0 01 1 0, 1 1 0, 1 1 1 0, 1 0, 1 01 11 10 11 0 0 Bài 4

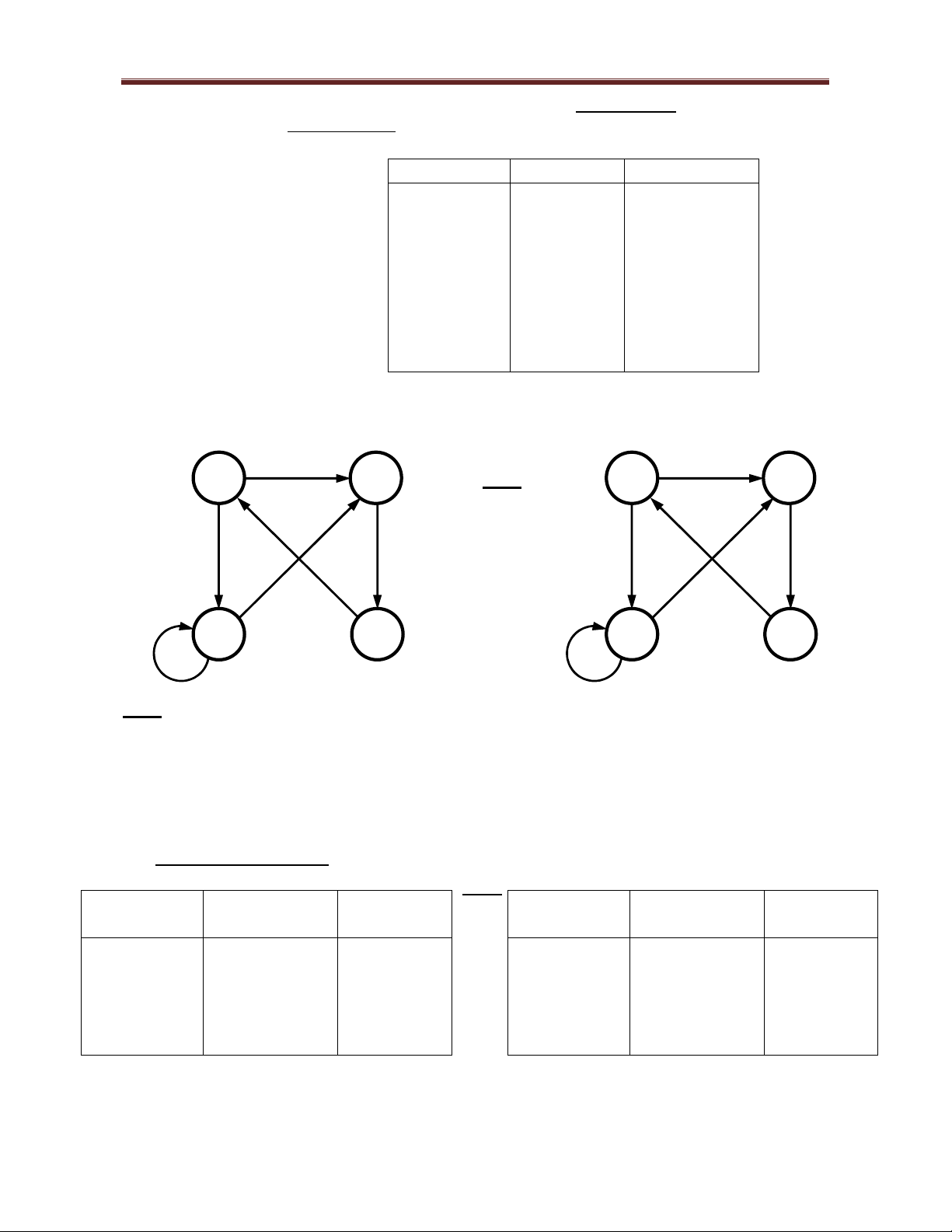

Thaønh laäp baûng chuyeån traïng thaùi hoaëc giaûn ñoà traïng thaùi cuûa heä tuaàn töï kieåu MOORE

coù 1 ngoõ vaøo X vaø 1 ngoõ ra Z. Ngoõ ra Z chæ baèng 1 khi ngoõ vaøo X nhaän ñöôïc chuoãi lieân tuïc

1, 1, 0, 1. Haõy ruùt goïn baûng traïng thaùi.

Baûng traïng thaùi ruùt goïn: Hoặc TTHT TTKT Ngoõ ra TTHT TTKT Ngoõ ra X = 0 X = 1 X = 0 X = 1 (reset) A A B 0 (reset) S0 S0 S1 0 ( 1 ) B A C 0 ( 1 ) S1 S0 S2 0 ( 1, 1 ) C D C 0 ( 1, 1 ) S2 S3 S2 0 (1, 1, 0) D A E 0 (1, 1, 0) S3 S0 S4 0 (1, 1, 0, 1) E A C 1 (1, 1, 0, 1) S4 S0 S2 1 3

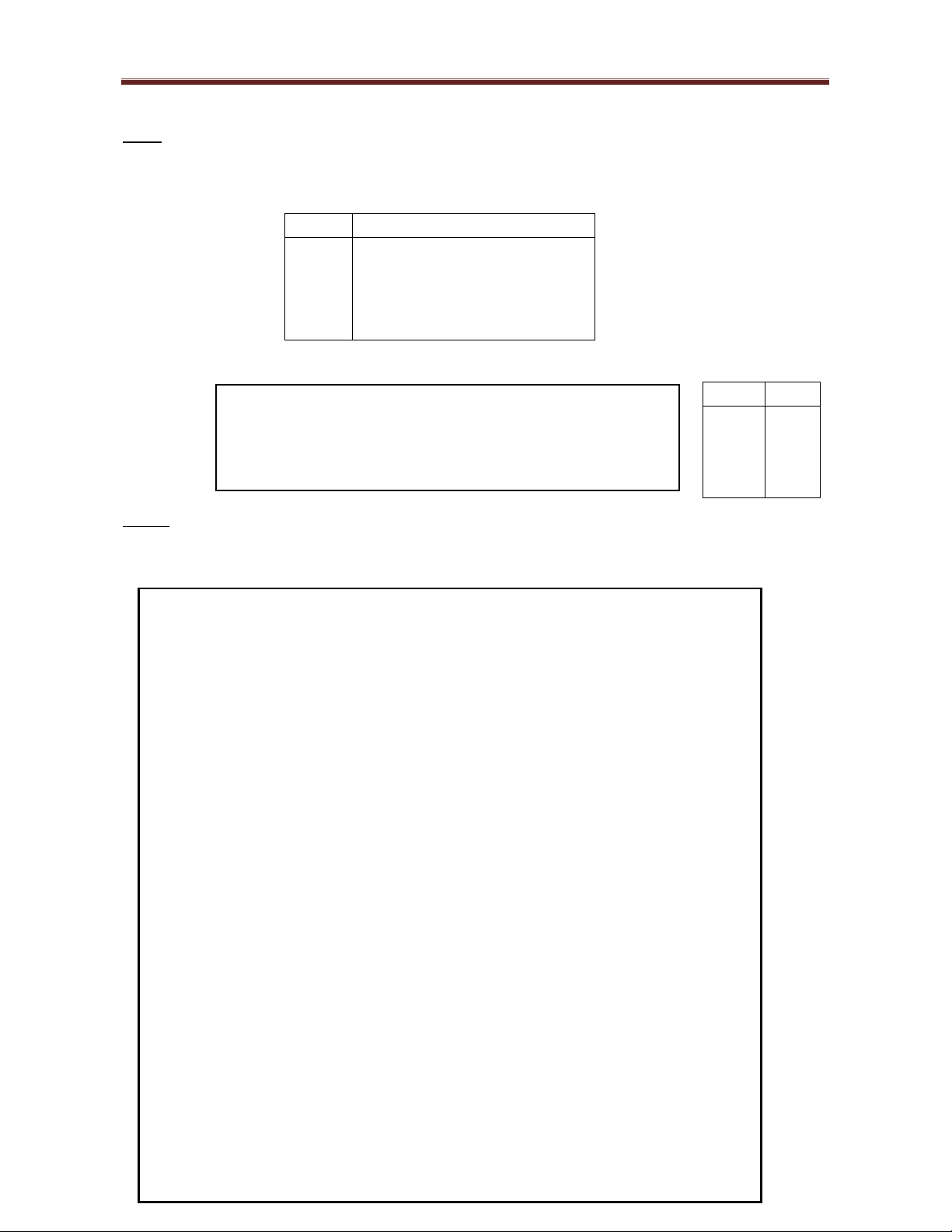

Nguyễn Trọng Luật – BM Điện Tử - Khoa Điện-Điện Tử - ĐH Bách Khoa TP. HCM Bài 5

Cho heä tuaàn töï coù 1 ngoõ vaøo X vaø 2 ngoõ ra Z1, Z2. Heä coù 4 traïng thaùi A, B, C vaø D coù

giaûn ñoà traïng thaùi nhö hình veõ. Vôùi pheùp gaùn traïng thaùi (maõ hoùa traïng thaùi) A: Q1Q2 = 10,

B: Q1Q2 = 00, C: Q1Q2 = 01 vaø D: Q1Q2 = 11. Haõy thieát keá heä baèng JK_FF vaø coång logic hoaëc

D_FF vaø PLA (chæ choïn 1 trong 2). Bieát raèng khi xung clock vaøo coù caïnh xuoáng heä seõ chuyeån traïng thaùi. 0 1 X Q1 Q2 Z1 Z2 Q+1 Q+2 J1 K1 J2 K2 A X = 1 B 0 0 0 1 1 0 1 0 X 1 X 01 11 0 0 1 0 0 1 1 1 X X 0 0 1 0 0 1 1 0 X 0 0 X 0 0 1 1 1 0 1 0 X 0 X 1 1 0 0 1 1 0 0 0 X 0 X 0 1 1 1 0 1 0 0 1 0 1 X X 1 1 1 0 0 1 0 0 X 1 0 X D 0 C 1 1 1 1 0 0 0 X 1 X 1 10 00

Duøng bìa K, ta coù: Z1 = Q1 Q2 + Q1 Q2 = Q2 ⊕ Q2 Z2 = Q2 D1 = Q+1 = X Q1 + Q1 Q2 D2 = Q+2 = X Q1 J1 = Q2 K1 = X J2 = X Q1 K2 = X + Q1 * Thi

ết kế bằng JK-FF và cổng: Z 1 J1 Q1 J2 Q2 CK CK X K1 Q1 K2 Q2 Z2 CK * Thi

ết kế bằng D-FF và PLA: PLA Z1 X Z2

Bảng nạp PLA X Q1 Q2 Z1 Z2 D1 D2 Q1 D1 D Q - 0 0 1 0 0 0 - 1 1 1 0 0 0 Q2 D2 D Q - - 0 0 1 0 0 0 1 - 0 0 1 0 CK - 0 1 0 0 1 0 0 0 - 0 0 0 1 4

Nguyễn Trọng Luật – BM Điện Tử - Khoa Điện-Điện Tử - ĐH Bách Khoa TP. HCM Bài 6

Cho heä tuaàn töï coù löu ñoà maùy traïng thaùi (löu ñoà SM, giaûn ñoà traïng thaùi nhö hình veõ). Xaùc

ñònh phöông trình (haøm) traïng thaùi keá cuûa caùc bieán traïng thaùi Q+1, Q+2 vaø phöông trình (haøm) ngoõ ra Z1, Z2.

S0 01 = Q 1Q2 Z1 X 0 1 Z2

S2 10

S1 11 Z1, Z2 1 X 0 1 X 0 Z1 11 P/trình ngoõ ra: Z1 = Q1 Q2 + Q1 Q2 + X Q1 Q2 Z2 = X Q1 Q2 + Q1 Q2 P/trình TTKT:

Q+1 = X Q1 Q2 + X Q1 Q2 + X Q1 Q2

Q+2 = X Q1 Q2 + X Q1 Q2 + X Q1 Q2 + X Q1 Q2 + X Q1 Q2 5

Nguyễn Trọng Luật – BM Điện Tử - Khoa Điện-Điện Tử - ĐH Bách Khoa TP. HCM Bài 7

Moät heä toå hôïp coù ngoõ ra Z laø soá nhò phaân 4 bit (z3 z2 z1 z0); coù chöùc naêng choïn 1 trong

4 maõ nhò phaân 4 bit ở ngoõ vaøo: M, N, P hoaëc Q phuï thuoäc 2 ngoõ vaøo ñieàu khieån x1 vaø x0. x1 x0 Z = z3 z2 z1 z0 0 0 M = m3 m2 m1 m0 0 1 N = n3 n2 n1 n0 1 0 P = p3 p2 p1 p0 1 1 Q = q3 q2 q1 q0

Vieát maõ VHDL thöïc hieän maïch naøy söû duïng component MUX 4 1 coù khai baùo ENTITY: ENTITY MUX4 IS s1 s0 y

PORT (d0, d1, d2, d3: IN STD_LOGIC; 0 0 d0 s1, s0: IN STD_LOGIC; 0 1 d1 y: OUT STD_LOGIC); 1 0 d2 END MUX4; 1 1 d3

Gôïi yù: - Moãi ngoõ ra zi choïn 1 trong 4 ngoõ vaøo mi, ni, pi, qi.

- Caùc ngoõ vaøo vaø M, N, P, Q vaø ngoõ ra Z khai baùo kieåu STD_LOGIC_VECTOR. LIBRARY ieee;

USE ieee.std_logic_1164.all; ENTITY cau7 IS

PORT (m, n, p, q: IN std_logic_vector(3 downto 0); x1, x0: IN std_logic;

z: OUT std_logic_vector(3 downto 0)); END cau7;

ARCHITECTURE structure OF cau7 IS

COMPONENT MUX4 IS

PORT (d0, d1, d2, d3: IN STD_LOGIC; s1, s0: IN STD_LOGIC; y: OUT STD_LOGIC); END COMPONENT; BEGIN

U0: MUX4 PORT MAP(m(0),n(0),p(0),q(0),x1,x0,z(0));

U1: MUX4 PORT MAP(m(1),n(1),p(1),q(1),x1,x0,z(1));

U2: MUX4 PORT MAP(m(2),n(2),p(2),q(2),x1,x0,z(2));

U3: MUX4 PORT MAP(m(3),n(3),p(3),q(3),x1,x0,z(3)); END structure; 6

Nguyễn Trọng Luật – BM Điện Tử - Khoa Điện-Điện Tử - ĐH Bách Khoa TP. HCM Bài 8

Moät maïch hoaùn ñoåi maïng 2 daây (2-input permutation network): coù 2 ngoõ vaøo a, b; ngoõ

vaøo ñieàu khieån c vaø 2 ngoõ ra x, y. Maïch coù hoaït ñoäng nhö sau:

- Khi c = 0 thì x = a vaø y = b.

- Khi c = 1 thì x = b vaø y = a.

Haõy vieát maõ VHDL (söû duïng phaùt bieåu Process) moâ taû hoaït ñoäng cuûa maïch. LIBRARY ieee;

USE ieee.std_logic_1164.all; ENTITY cau8 IS

PORT (a, b, c: IN std_logic;

x, y : OUT std_logic); END cau8;

ARCHITECTURE behavior OF cau8 IS BEGIN PROCESS (a, b, c) BEGIN

IF c = ’0’ THEN x <= a; y <= b; ELSE x <= b; y <= a; END IF; END PROCESS; END behavior; 7