Preview text:

lOMoARcPSD| 10435767

CHƯƠNG 6 – GIAO TIẾP TƯƠNG TỰ LT3

6.1 GIỚI THIỆU CHUNG GIAO TIẾP TÍN HIỆU TƯƠNG TỰ

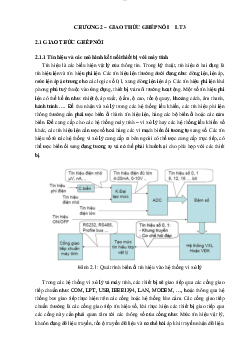

Trong kỹ thuật, hầu hết các tín hiệu ều dưới dạng tín hiệu tương tự, trong khi các hệ

thống vi xử lý thực hiện các chương trình, cho phép iều khiển tự ộng các hệ thống kỹ thuật

lại là các hệ thống số. Hình 6.1 mô tả việc giao tiếp giữa các hệ thống vi xử lý và các quy

trình ối tượng kỹ thuật, các quy trình công nghệ trong thực tế. Trên hình vẽ, ể thu thập thông

tin tương tự từ bên ngoài, hệ thống vi xử lý cần các bộ giao tiếp chuyển ổi tương tự sang số

(ADC – Analog to Digital Converter). Và ể cung cấp các tín hiệu iều khiển dưới dạng tương

tự hệ thống sử dụng các giao tiếp biến ổi số sang tương tự (DAC – Digital to Analog Converter).

Hình 6.1: Mô hình giao tiếp các tín hiệu tương tự trong các hệ thống vi xử lý

6.2 MẠCH ĐIỆN TỬ TƯƠNG TỰ ỨNG DỤNG 6.2.1

Mạch ứng dụng khuếch ại thuật toán

Khuếch ại thuật toán là một trong số những linh kiện iện tử thường gặp nhất trong kỹ

thuật tương tự, vì thế trong kỹ thuật o lường và iều khiển công nghiệp, khuếch ại thuật toán

cũng có mặt trong rất nhiều thiết bị và hệ thống. Khả năng sử dụng của các bộ khuếch ại

thuật toán là rất vạn năng, chúng ược áp dụng trong nhiều lĩnh vực như các bộ khuếch ại

một chiều, các bộ khuếch ại xoay chiều, bộ lọc tích cực, bộ dao ộng, bộ biến ổi trở kháng,

bộ vi phân, bộ tích phân...

Ðể làm nổi bật tính chất của một bộ khuếch ại thuật toán, hãy xét tính năng của một bộ

khuếch ại thuật toán lý tưởng:

Hệ số khuếch ại khi không có phản hồi âm lớn vô cùng. lOMoARcPSD| 10435767

Ðiện trở lối vào lớn vô cùng.

Ðộ rộng dải thông lớn vô cùng.

Hệ số nén ồng pha CMRR lớn vô cùng.

Ðiện trở lối ra bằng không

Thời gian áp ứng bằng không.

Trên thực tế, không có bộ khuếch ại thuật toán lý tưởng mà chỉ tồn tại những khuếch ại

thuật toán thực có tính chất gần với những tiêu chuẩn ã nêu. Các tham số và các mạch ứng

dụng của bộ khuếch ại thuật toán rất nhiều, không thể nêu hết trong phần này mà ở ây, chỉ

nêu lên những tham số cơ bản, cách tính toán và các mạch ã ược áp dụng trong hệ thống iều khiển.

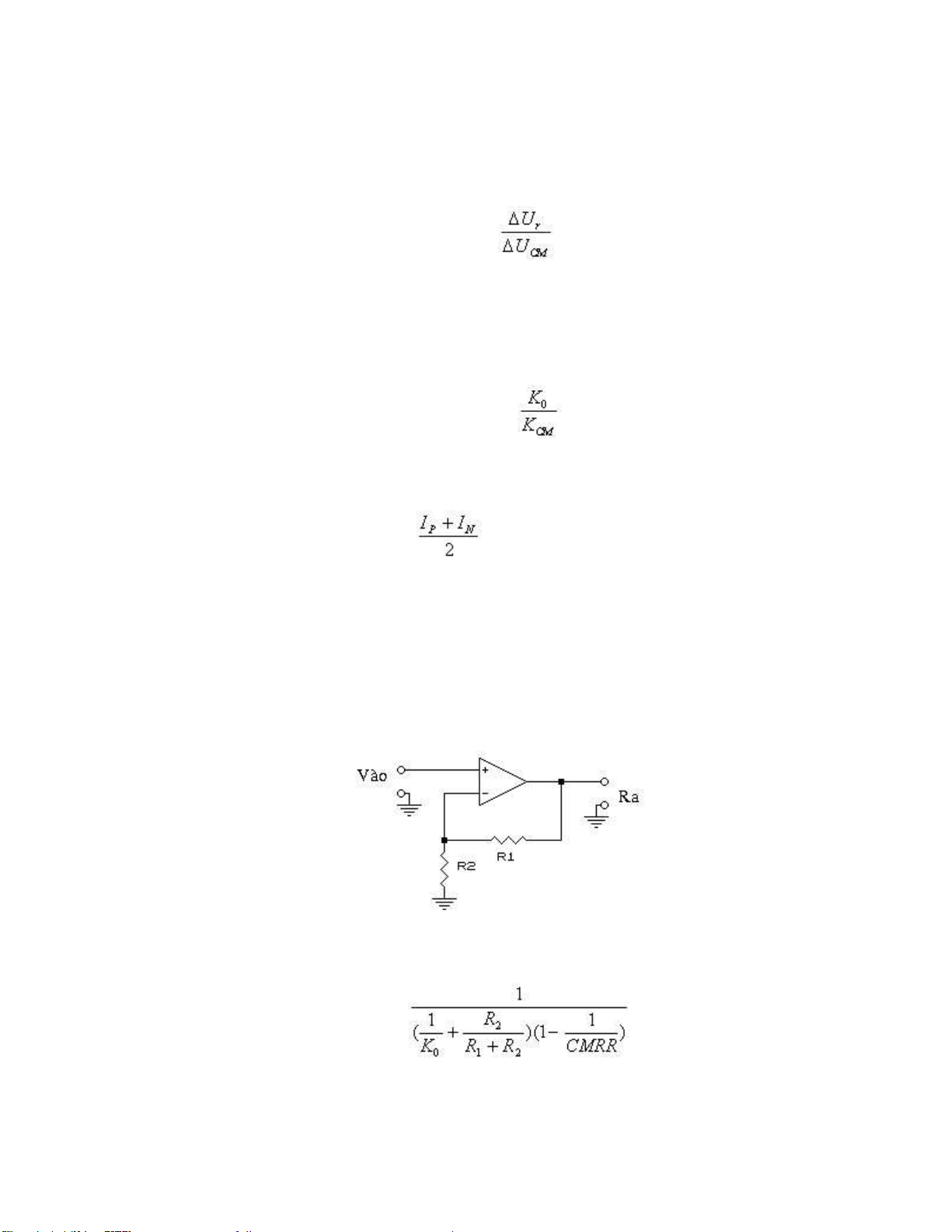

Các tham số cơ bản của mạch khuếch ại thuật toán

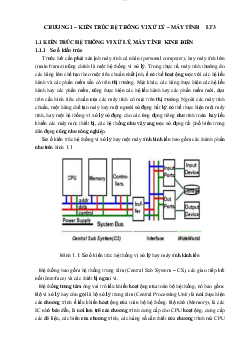

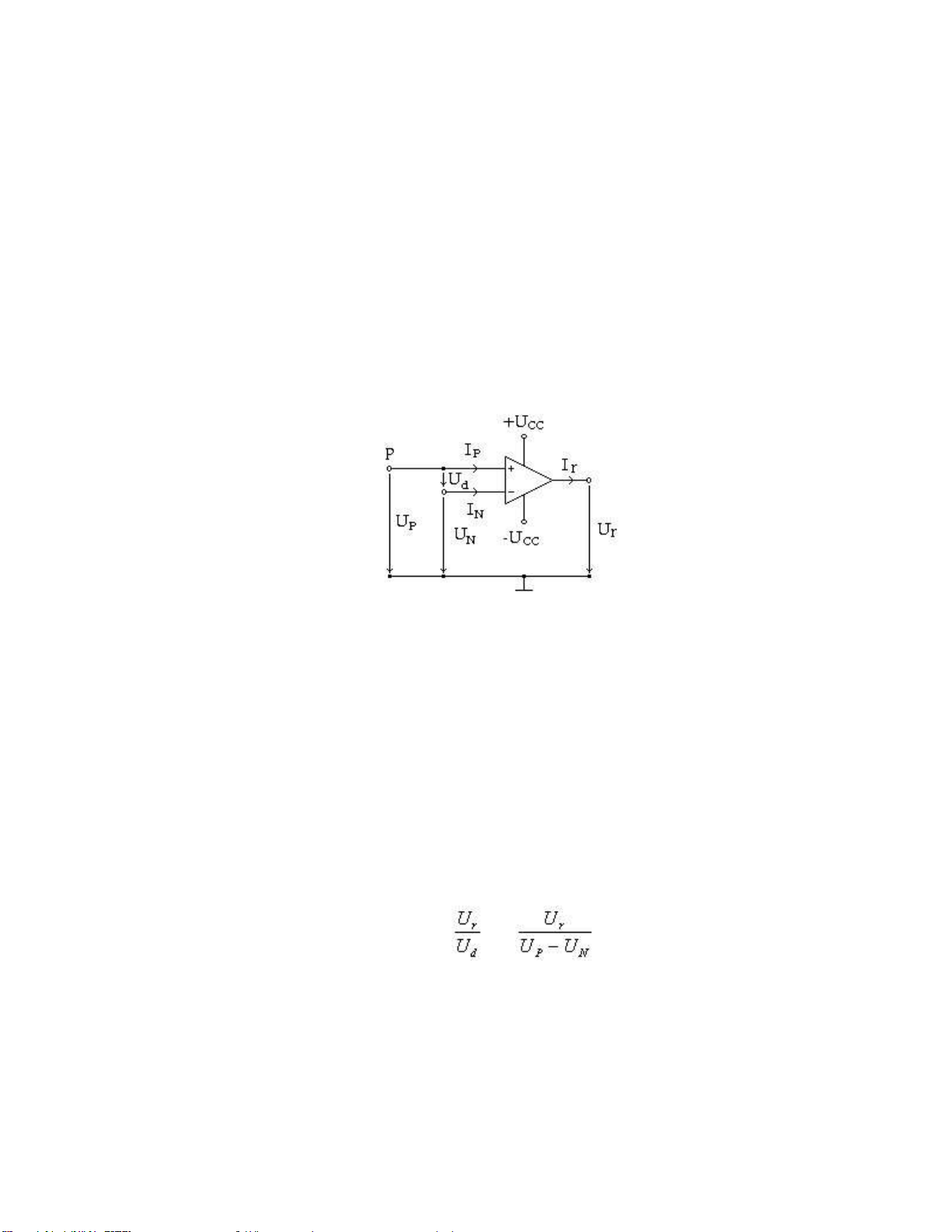

Hình 6.2: Bộ khuếch ại thuật toán. Ud iện áp vào hiệu

UP , IP iện áp vào và dòng iện vào cửa thuận.

UN , IN iện áp vào và dòng iện vào cửa ảo.

Ur , Ir iện áp ra và dòng iện ra.

Bộ khuếch ại thuật toán khuếch ại hiệu iện áp Ud = UP - UN với hệ số khuếch ại K0 khác 0. Do ó iện áp ra:

Ur = K0. Ud = K0(UP - UN)

Hệ số khuếch ại hiệu K0

Khi không tải ược xác ịnh theo biểu thức sau K = 0 =

Hệ số khuếch ại ồng pha KCM

Nếu ặt vào cửa thuận và cửa ảo của bộ khuếch ại thuật toán các iện áp bằng nhau, nghĩa là: lOMoARcPSD| 10435767

UP = UN = UCM ≠ 0

thì Ud = 0. Gọi UCM là iện áp vào ồng pha. Theo biểu thức trên ta có Ur=0. Tuy nhiên, thực

tế không phải như vậy, giữa iện áp ra và iện áp vào ồng pha có quan hệ tỷ lệ là hệ số khuếch ại ồng pha KCM : KCM =

KCM nói chung phụ thuộc vào mức iện áp vào ồng pha.

Hệ số nén ồng pha CMRR

Dùng ể ánh giá khả năng làm việc của bộ khuếch ại thực so với bộ khuếch ại lý tưởng (KCM=0) CMRR =

Dòng vào tĩnh

Là trị trung bình của dòng vào cửa thuận và dòng vào cửa ảo: It =

với UP = UN = 0

Dòng vào lệch không là hiệu các dòng vào tĩnh ở hai cửa của bộ khuếch ại thuật toán I0

= IP - IN với UP = UN = 0

Thông thường I0 = 0,1IP. Trị số của dòng vào lệch không thay ổi theo nhiệt ộ. Hiện

tượng này gọi là hiện tượng trôi dòng lệch không. Các sơ ồ cơ bản của bộ khuếch ại thuật toán

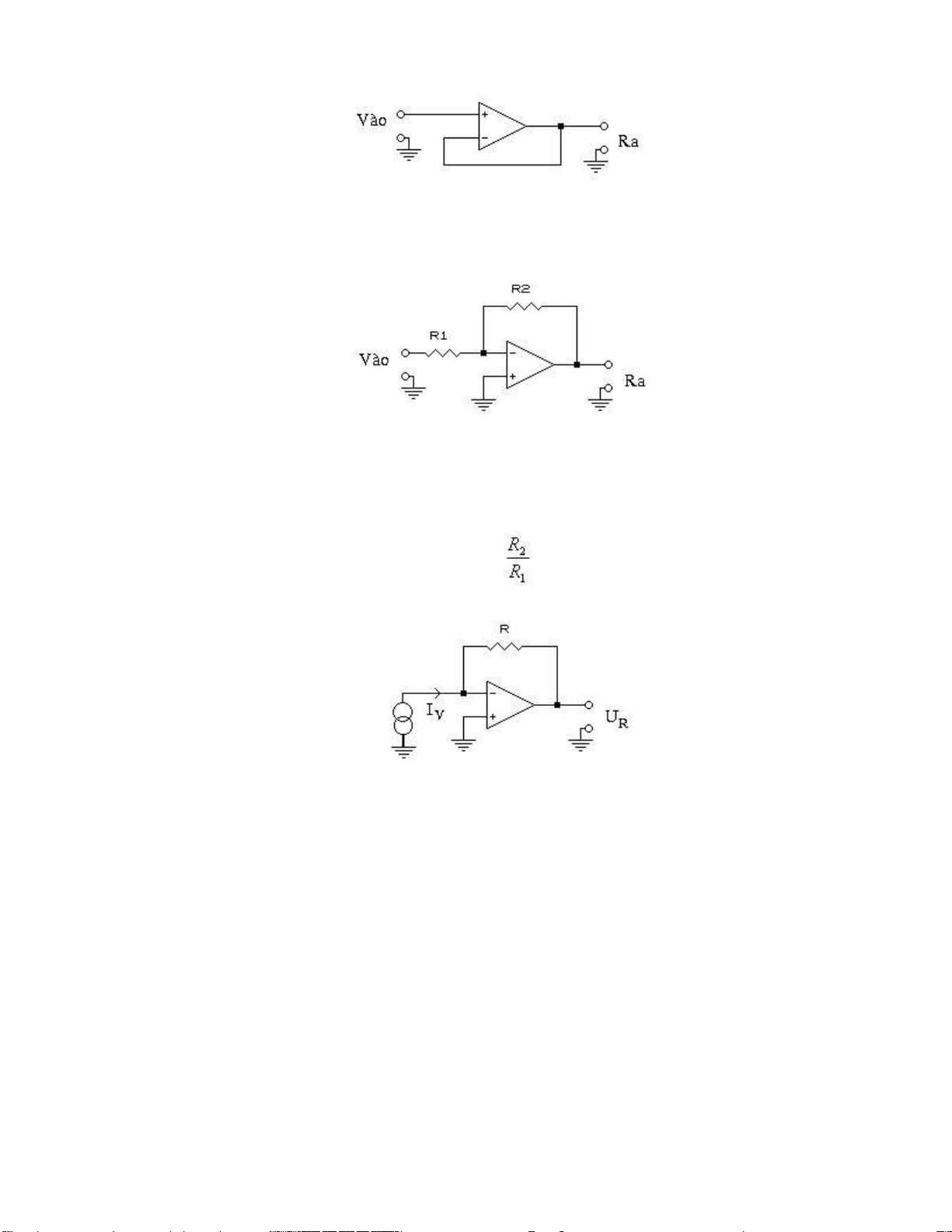

Sơ ồ khuếch ại không ảo

Hình 6.3: Sơ ồ khuếch ại không ảo Hệ số

khuếch ại của mạch: K =

Mạch ệm

Ðây là trường hợp ặc biệt của mạch khuếch ại không ảo lOMoARcPSD| 10435767

Hình 6.4: Sơ ồ mạch ệm

Mạch có hệ số khuếch ại bằng 1 và dùng ể phối hợp trở kháng.

Mạch khuếch ại ảo

Hình 6.5: Sơ ồ mạch khuếch ại ảo Hệ số khuếch ại của mạch: K =

Sơ ồ biến ổi dòng iện - iện áp

Hình 6.6: Sơ ồ biến ổi dòng iện - iện áp

Ðiện áp ra ược tính theo biểu thức: UR = - R.IV lOMoARcPSD| 10435767

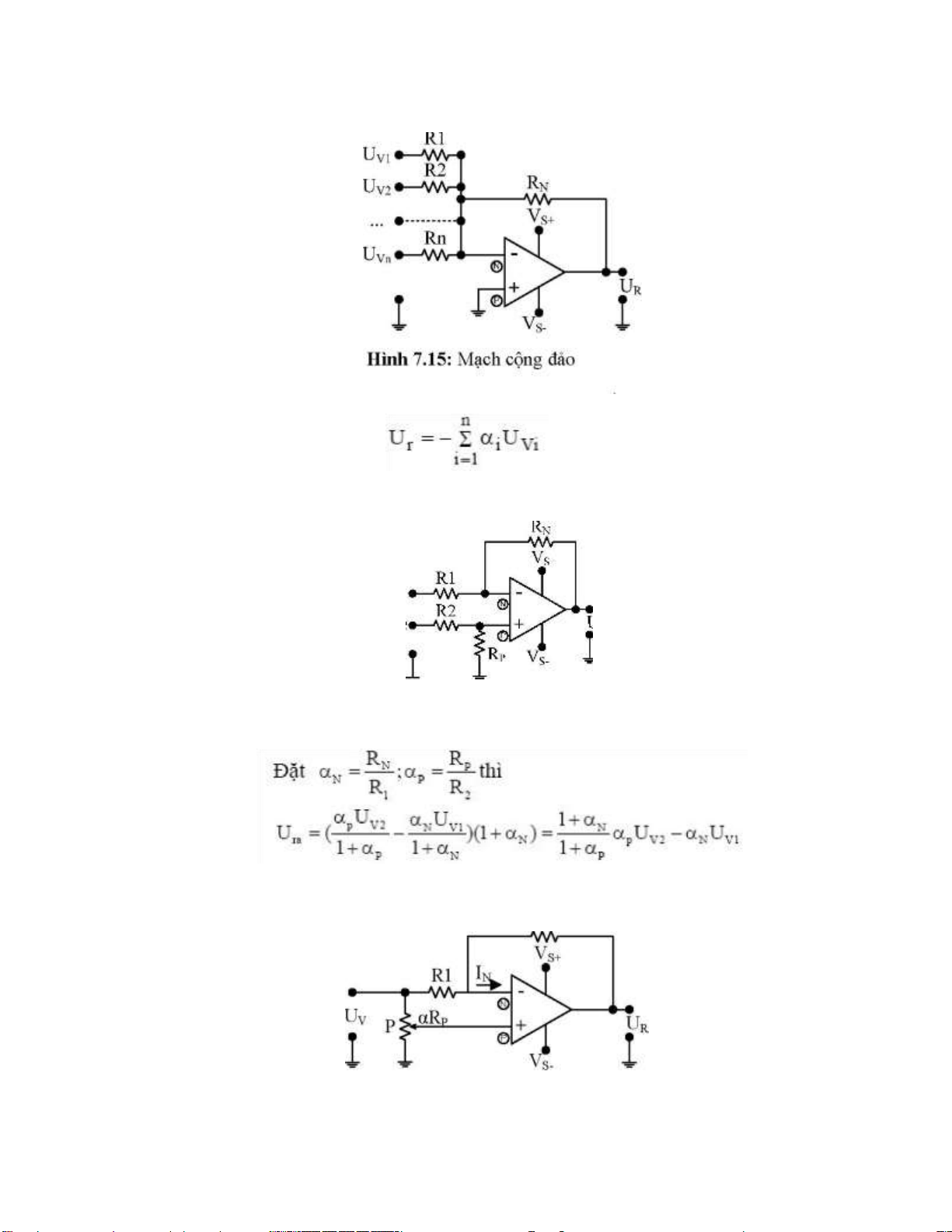

Mạch cộng ảo

Hình 6.7: Mạ ch c ộng ả o Điện áp ngõ ra: Mạch trừ: Hình 6.8: Mạch trừ

Mạch cho phép thay ổi cục tính iện áp ra:

Hình 6.9: Mạch cho phép thay ổi cục tính iện áp ra lOMoARcPSD| 10435767

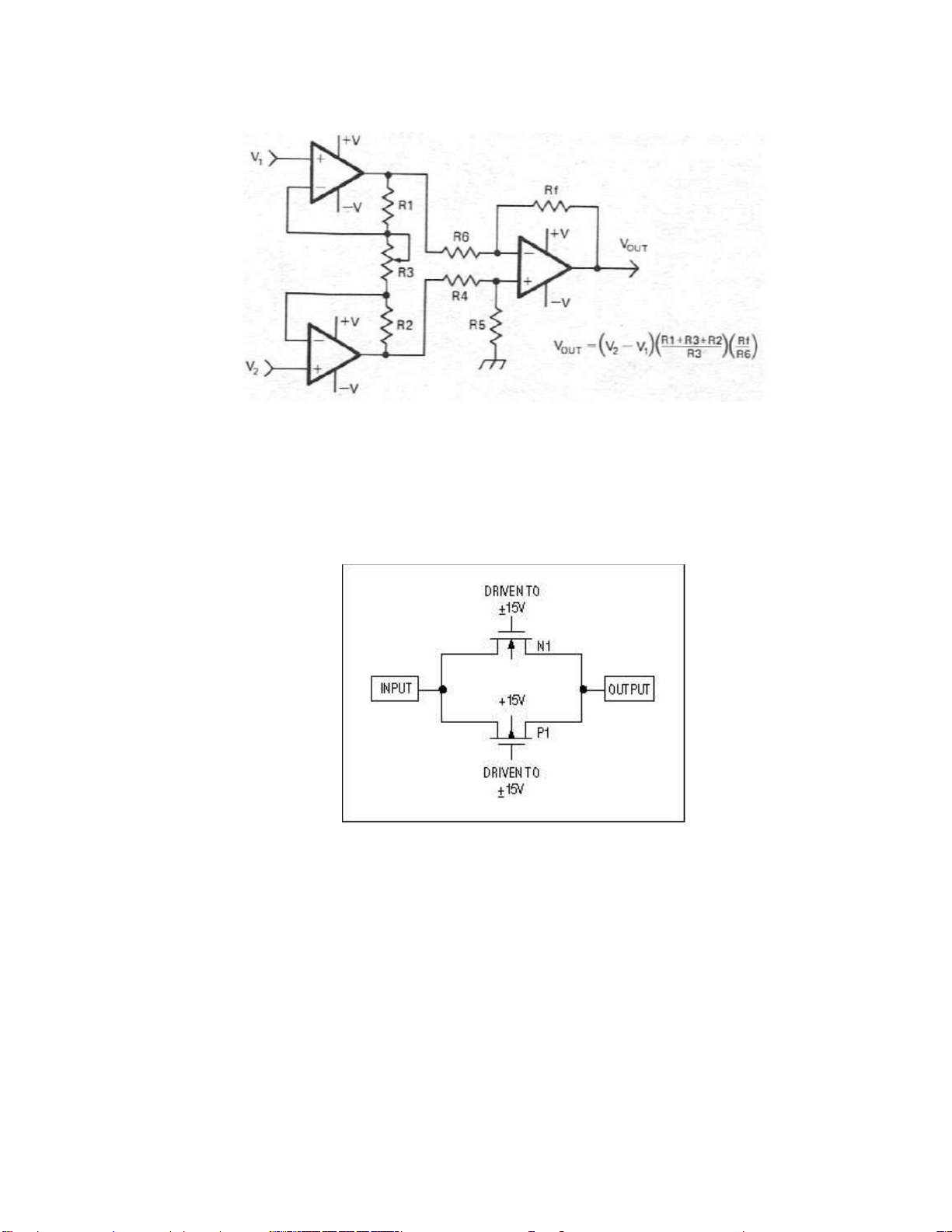

Mạch khuếch ại o lường:

Hình 6.10: Mạch khuếch ại o lường 6.2.2

Mạch ghép kênh và chuyển mạch tương tự

Khi có nhiều kênh tương tự ngõ vào ra cần giao tiếp với hệ thống vi xử lý iều khiển, ể

tránh phải sử dụng nhiều bộ biến ổi A/D, D/A, người ta thường sử dụng các chuyển mạch

tương tự ể chọn một kênh tại một thời iểm.

Hình 6.11: Cấu tạo chuy ển mạch tương tự

Giống như một công tắc cơ khí các chuyển mạch tương tự có nhiệm vụ cách ly hoặc cho

phép tín hiệu ngõ vào chuyển tới ngõ ra. Khác với các công tắc cơ khí sử dụng các tiếp iểm

kim loại, ược iều khiển óng ngắt bằng tay hoặc bằng iện (như relay), các chuyển mạch iện

tử thực hiện bằng các MOFET. Hình 6.11 mô tả cầu trúc của một chuyển mạch tương tự,

chuyển mạch sử dụng 2 MOSFET kênh N và P mắc song song và ược iều khiển trực tiếp từ

bên ngoài. Các cực cổng N1 và P1 ược kích lệch pha 180o, khi N1 =15V thì P=-15V và ngược lại. lOMoARcPSD| 10435767

Khi sử dụng các chuyển mạch tương tự cần chú ý các ặc tính của tín hiệu cần chuyển

mạch như: biên ộ tín hiệu cần chuyển mạch, ộ méo dạng tín hiệu …. Sau ây là một số ặc

tính cần xem xét khi lựa chọn các chuyển mạch tương tự.

V+: xác ịnh biên ộ tín hiệu tương tự có thể i qua chuyển mạch tương tự mà không bị

xén ỉnh. Các mạch MOSFET bên trong cần ược phân cực ể cho phép toàn dải biên ộ của tín

hiệu ngõ vào. Một số chuyển mạch tương tự có nguồn phân cực ối xứng cho phép chuyển

mạch các tín hiệu ối xứng.

VIH/VIL: là tín hiệu iều khiển óng mở chuyển mạch tương tự. Hầu hết các chuyển

mạch tương tự ều cho phép óng mở bằng các tín hiệu iều khiển số. Do ó cần xem xét mức

tín hiệu iều khiển này sử dụng các cổng số thích hợp cho việc iều khiển.

Ron (On State Resistance): Ron sẽ ảnh hưởng tới việc mất và suy giảm tín hiệu chuyển

mạch. Các chuyển mạch tương tự có Ron nhỏ cần sử dụng các transistor có kích thước lớn.

Tuy nhiên khi sử dụng các transistor lớn và ế bán dẫn có kích thước lớn sẽ làm tăng iện

dung vào ra CI/O. Các iện dung này sẽ ảnh hưởng rất lớn tới tần số áp ứng của chuyển mạch

tương tự. Khi chuyển mạch các tín hiệu với tần số lớn cần sử dụng các chuyển mạch có Ron và CI/O nhỏ.

Ron(flat) – Dải iện trở ộng: là khoảng từ nhỏ nhất ến lớn nhất của iện trở ộng chuyển

mạch tương tự. Thông số này thường thay ổi theo nhiệt ộ.

CON/COFF – Điện dung ON/OFF: thông số này cần ược xem xét vì nó ảnh hưởng tới

áp ứng thời gian, thời gian ổn ịnh và khả năng ghép nối ngõ ra (fanout) của chuyển mạch tương tự.

Tần số áp ứng: hầu hết các chuyển mạch CMOS ều có giới hạn trên cho tần số tín hiệu

chuyển mạch khá thấp. Người ta có thể thực hiện các chuyển mạch với Ron và CI/O thấp,

tuy nhiên vẫn có các bộ lọc thông thấp ký sinh ở các ngõ ra làm giảm tần số áp ứng của các chuyển mạch tương tự.

THD - Độ méo dạng sóng sin hoặc tổng hài méo dạng: thông số này xác ịnh ộ tuyến

tính của chuyển mạch. Sự áp ứng không tuyến tính của linh kiện có thể xảy ra do nhiều

nguyên nhân (như do thiết kế, do tính chất linh kiện …). Nhưng ảnh hưởng nhiều nhất là

do sự thay ổi của RON khi tín hiệu vào thay ổi. Chuyển mạch có RON nhỏ là rất quan trọng,

nhưng thông số RON(flat) cũng quan trọng không kém. Các MOSFET kênh N có ặc tính

RON(flat) khá tốt khi 0 < VI/O < V+ - 2V), tuy nhiên nó sẽ tăng rất nhanh khi VI/O tiến gần tới

V+ hoặc VGS giảm. Vì vậy nên chọn các chuyển mạch tương tự sao cho ảm bảo iều kiện 0 < VI/O < V+. lOMoARcPSD| 10435767

Nhiễu xuyên kênh (Crosstalk): Có hai loại xuyên kênh trong chuyển mạch tương tự cần ược xem xét là: -

Xuyên kênh giữa tín hiệu iều khiển và tín hiệu ngõ ra: do ặc tính tụ ký sinh trong quá

trình thực hiện các MOSFET, nên sự thay ổi của tín hiệu iều khiển có thể gây ra nhiễu trên tín hiệu ngõ ra. -

Xuyên kênh giữa các chuyển mạch chế tạo trên cùng ế bán dẫn: cũng do các tụ ký sinh

khi chế tạo, tín hiệu chuyển mạch ở chuyển mạch này có thể ảnh hưởng tới tín hiệu

chuyển mạch ở một kênh khác.

Cách ly ở trạng thái óng: tương ứng với trở kháng ở trạng thái cách ly tín hiệu chuyển

mạch, nó thường ược o theo ơn vị DB ở tần số áp ứng của chuyển mạch.

Khả năng chặn tín hiệu tần số cao: Thông số này liên quan ến khả năng chặn tín hiệu

khi tắt của chuyển mạch. Giống như nhiễu xuyên kênh, các tụ ký sinh có thể nối các tín

hiệu tần số cao từ ngõ vào tới ngõ ra khi chuyển mạch ở trạng thái tắt.

Để chọn biến ổi một trong nhiều tín hiệu tương tự ngõ vào, người ta sẽ sữ dụng các bộ

dồn kênh tín hiệu tương tự. Các bộ dồn kênh này sẽ có cấu trúc bao gồm nhiều chuyển mạch

tương tự nối chung ngõ ra. Một trong các chuyển mạch sẽ ược chọn thông tín hiệu ngõ vào

bằng một bộ giải mã ịa chỉ giống như một bộ dồn kênh số. 6.2.3

Mạch tạo iện áp chuẩn

Điện áp chuẩn ảnh hưởng trực tiếp tới ộ chính xác của các quá trình biến ổi tương tự –

số. Thông thường trong các bộ biến ổi A/D, D/A tích hợp sẵn các khối tạo iện áp chuẩn, ở

các vi mạch không tích hợp sẵn có thể sử dụng các IC tạo áp chuẩn chuyên dụng. Các vi

mạch này sẽ tạo ra iện áp ngõ ra không thay ổi theo thời gian, nhiệt ộ hay theo iện áp cung

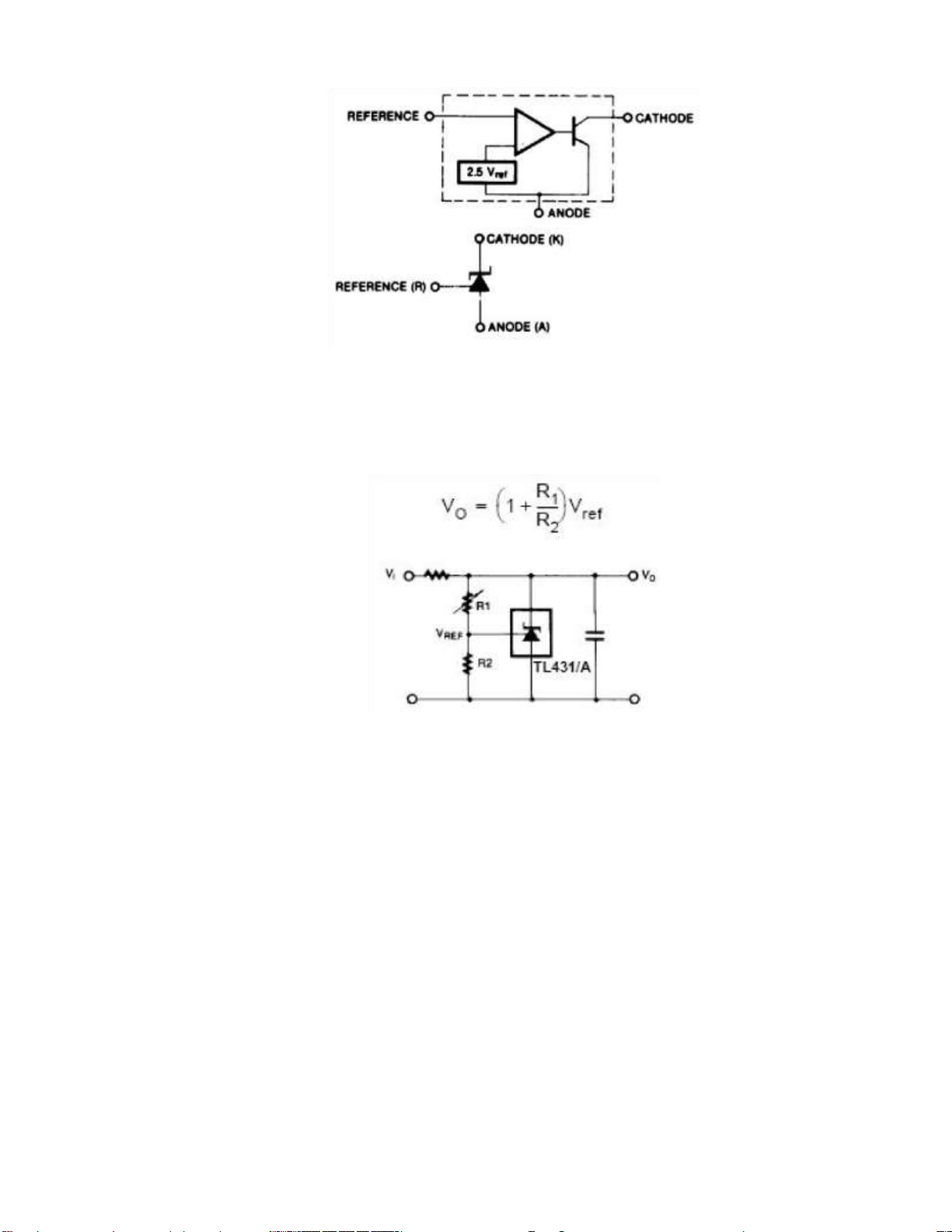

cấp cho nó. Hình 6.12 mô tả cấu tạo và ký hiệu của vi mạch tạo áp chuẩn TL431A, tín hiệu

iện áp ưa vào chân REFERENCE sẽ ược so sánh với iện áp chuẩn 2.5 V bên trong, khuếc

ại qua OP – AMP ể iều khiển transitor dẫn giữ một iện áp không ổi giữa Anode và Kathode. lOMoARcPSD| 10435767

Hình 6.12: Cấu tạo vi mạch tạo áp chuẩn TL431A

Hình 6.13 mô tả một mạch tạo áp chuẩn iển hình sử dụng TL431A, giá trị iện áp chuẩn

ngõ ra của mạch sẽ thay ổi khi thay ổi giá trị biến trở R1.

Hình 6.13: Mạch tạo áp chuẩn sử dụng TL431A 6.2.4

Lấy mẫu và giữ mẫu (Sample & Hold)

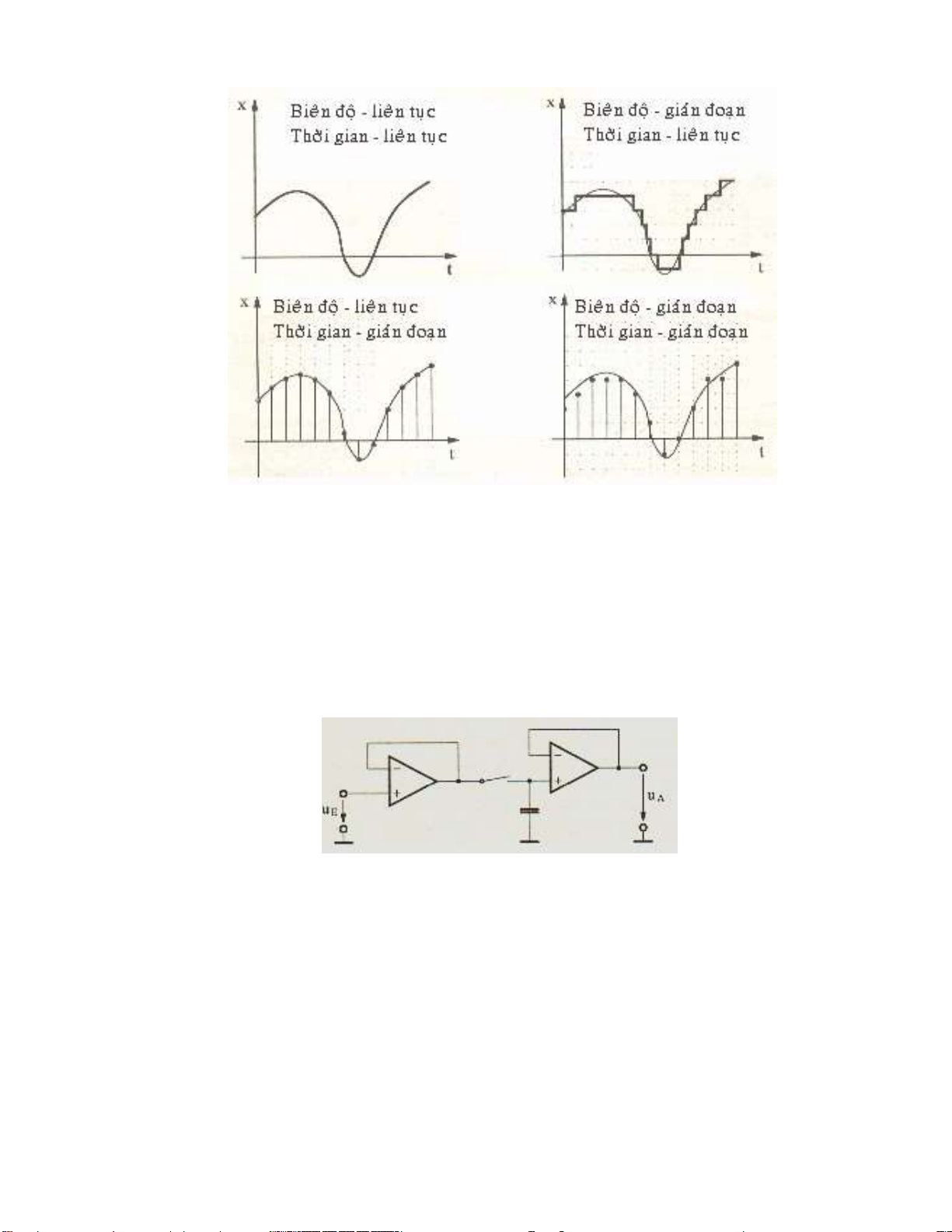

Quá trình lấy mẫu (Sampling) là bước ầu tiên trong chuyển ổi tương tự – số là rời rạc

hoá theo thời gian tín hiệu ầu vào ban ầu. Việc lấy mẫu như vậy ược bộ phận lấy mẫu và

giữ – Sample & Hold Circuit (S&H) thực hiện. lOMoARcPSD| 10435767

Hình 6.14: Lấy mẫu tín hiệu tương tự

Bước tiếp theo, bộ chuyển ổi tương tự – số A/D chuyển ổi các mẫu nghiệm liên tục

theo giá trị và ã ươc rời rạc hoá theo thời gian ó thành tín hiệu lượng tử hoá theo giá trị và

biểu diễn dưới dạng số nhị phân.

Phải chọn tần số lấy mẫu sao cho các trị lấy mẫu có thể ặc trưng cho tín hiệu ban ầu

(fsample ≥ 2 fmax), và có thể phục hồi lại tín hiệu ban ầu từ các mẫu này.

Hình 6.15: Mạch lấy mẫu và giữ (Track & Hold)

Mạch lấy mẫu và dừng S&H: Trong kỹ thuật chuyển ổi tương tự – số, tín hiệu tương

tự biến thiên liên tục theo thời gian u(t) ược lấy mẫu ở những thời iểm nhất ịnh, và giá trị

tín hiệu nhận ược sẽ ược lưu giữ trong một khoảng thời gian ịnh trước.

Trong nhiều bộ chuyển ổi A/D, tín hiệu phải ược giữ không ổi trong suốt thời gian chuyển

ổi. Để thực hiện việc ó, dùng mạch Track-and-Hold – T&H. Cấu trúc cơ bản của mạch T&H trên hình 6.15. lOMoARcPSD| 10435767

Sau mỗi lần mở chuyển mạch, tụ iện nạp ến giá trị iện áp ầu vào uvao(t) và lưu giữ giá

trị tức thời của iện áp ầu vào trước thời iểm mở chuyển mạch. Cả hai bộ khuếch ại thuật

toán làm bộ ệm buffer cho ầu vào cũng như ầu ra.

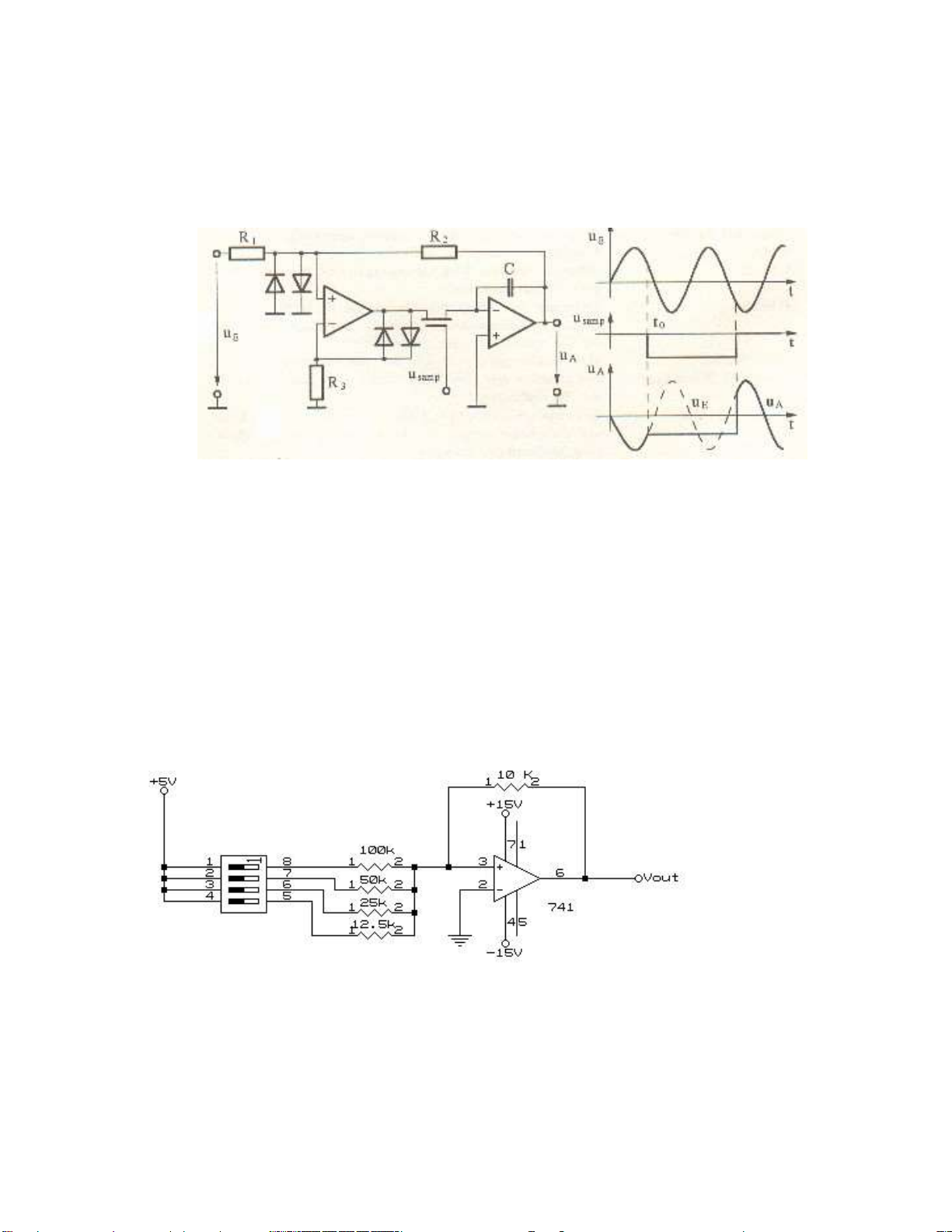

Một mạch T&H khác ược mô tả trên hình 6.16.

Hình 6.16: Mạch lấy mẫu và gi ữ (Track & Hold) dùng FET

Một transistor trường FET cực cổng cách ly (Isolated – Gate – FET) ược mắc giữa

KĐTT ảo pha và KĐTT tích phân. Khi usamp = 0, transistor FET sẽ dẫn và iện áp ầu ầu ra

uA tương ứng iện áp ầu vào, giả thiết hằng số thời gian tích phân của KĐTT ( ược xác ịnh

bởi dòng iện ầu ra cực ại của KĐTT là ủ nhỏ). Vào thời iểm t=t0, transistor trường khóa

,như vậy việc nạp tụ không ổi, iện áp ầu ra UA ược giữ lại ở mức giá trị UA(t)=UA(t0), cho

ến khi transistor trường ược iều khiển mở mạch. Khi FET óng, các diode sẽ dẫn và nhờ ó

mà tránh ược hiện tượng KĐTT bị quá iều khiển. Hình 6.17: Ví dụ về DAC 4 bit lOMoARcPSD| 10435767 6.2.5

Các bộ biến ổi tương tự – số, số - tương tự (ADC/DAC)

6.2.5.1 Biến ổi số – Tương tự (DAC – Digital to Analog Converter)

Mục ích của bộ biến ổi DA, là biến ổi tín hiệu nhị phân n bit thành dòng hay áp tương

ứng. Hình 6.17 mô tả một bộ biến ổi DA 4 bit ơn giản. Về nguyên tắc bộ chuyển ổi số-

tương tự tiếp nhận một mã số n bit song song hoặc nối tiếp ở lối vào và biến ổi ra dòng iện

hoặc iện áp tương ứng ở lối ra. Dòng iện hay iện áp ở lối ra là hàm biến thiên phù hợp theo mã số ở lối vào.

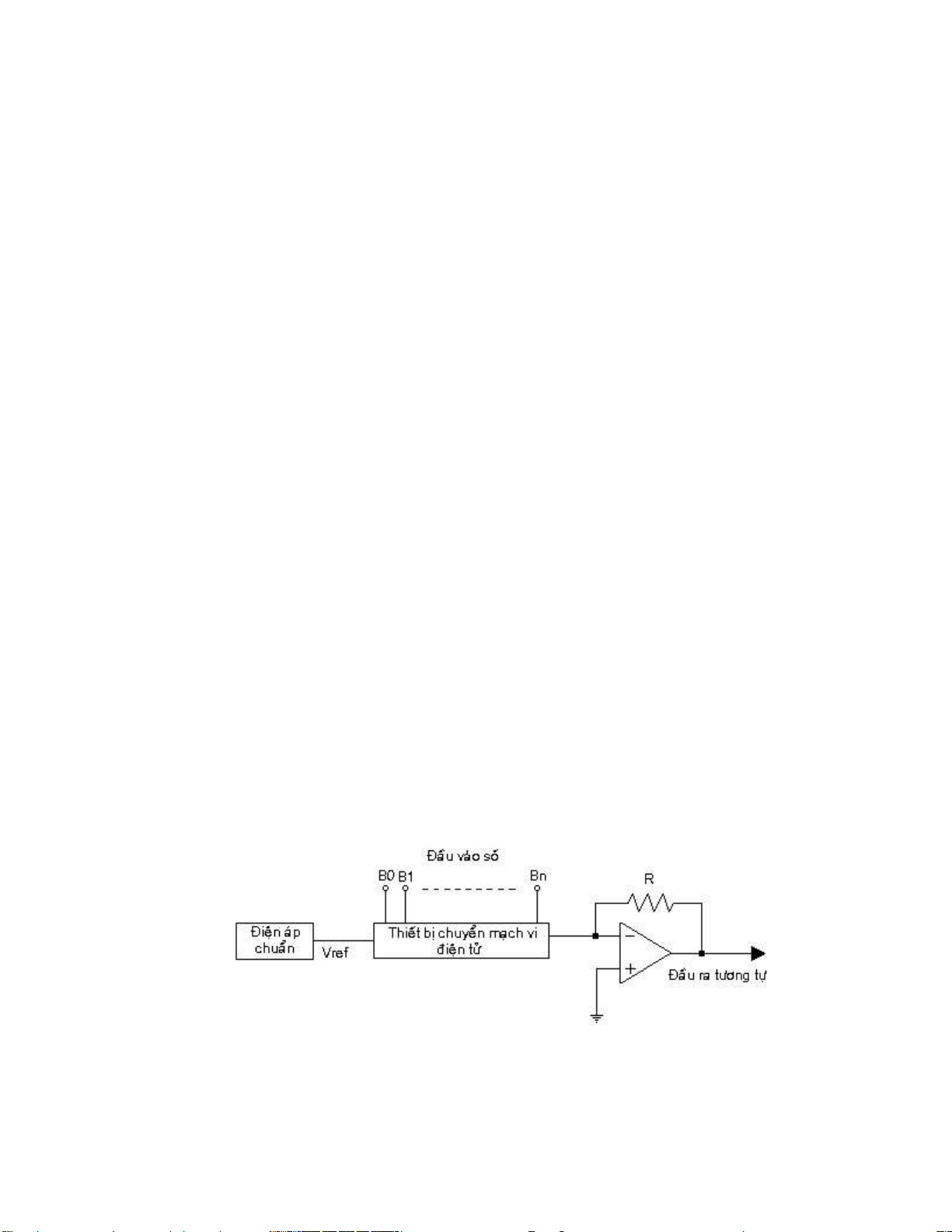

Sơ ồ khối một bộ DAC hoàn chỉnh hình 6.18 bao gồm ba phần tử cơ bản:

Ðiện áp quy chiếu ổn ịnh bên ngoài (Vref) DAC cơ sở

Khuếch ại thuật toán

Như vậy iện áp ầu ra của bộ biến ổi V0 sẽ phụ thuộc vào mã nhị phân ầu vào theo công thức sau:

V0 = Vref (B020 + B121 + ... + Bn2n)

Trong ó B0 là bit thấp nhất và Bn là bit cao nhất của mã nhị phân ầu vào, Vref là iện áp quy chiếu.

DAC cơ sở cấu tạo bằng những chuyển mạch tương tự ược iều khiển bởi mã số ầu vào

và các iện trở chính xác. Các chuyển mạch tương tự iều chỉnh dòng iện hay iện áp trích ra

từ iện áp quy chiếu và tạo nên dòng iện hay iện áp ở ầu ra tương ứng với mã số ầu vào.

Mạch khuếch ại thuật toán dùng ở ây ể chuyển ổi dòng thành áp ồng thời có chức năng tầng ệm.

Bộ biến ổi DAC có ặc iểm là ại lượng ra tương tự không liên tục, ộ rời rạc của ầu ra phụ

thuộc vào số bit của bộ biến ổi, những DAC có số bit ầu vào lớn thì tổng số nấc iện áp ra

càng lớn và khoảng cách giữa các nấc càng nhỏ.

Hình 6.18: Sơ ồ khối DAC lOMoARcPSD| 10435767

Các tham số của bộ chuyển ổi DA:

Ðộ phân giải (Solution): Liên quan ến số bit của một DAC. Nếu số bit là n thì số trạng

thái của tín hiệu nhị phân là 2n nghĩa là sẽ có 2n mức iện thế (hoặc dòng iện) khác nhau,

do ó có ộ phân giải là 1/2n. Ðộ phân giải càng bé thì iện thế (hoặc dòng iện ầu ra) càng

có dạng liên tục, càng gần với thực tế và ngược lại.

Ðộ chính xác (Accuracy): Có thể ánh giá chất lượng của một DAC bằng sai số của nó.

Ðại lượng biểu diễn sai số là ộ lệch tối a giữa ại lượng ra và một ường thẳng nối iểm 0

với iểm FS (Full Scale) trên ặc tuyến chuyển ổi DA.

Ðộ tuyến tính (Linearity): Ðộ tuyến tính của DAC cho biết ộ lệch iện áp so với một

ường thẳng i qua những iểm nút của ặc tuyến chuyển ổi. Ðó là ặc tính thường gặp nhất

với DAC. Ðường cong ặc tuyến là ơn iệu nếu sự thay ổi ộ lệch trên là không ổi dấu. Ðể

có một DAC ơn iệu, ộ lệch này phải lớn hơn 0 cho mỗi nấc thang. Ngoài ra mức ộ tuyến

tính của DAC phải nhỏ hơn hoặc bằng 1/2 LSB ể nó trở nên ơn iệu. Như vậy 1/2

LSB là ặc trưng về giới hạn ơn iệu của một DAC.

Phi tuyến vi sai: là ại lượng cho biết ộ lệch giữa giá trị thực tế và lý tưởng cho một nấc

iện áp ra ứng với mỗi thay ổi của mã số vào. Ðại lượng này cho biết về ộ nhẵn của ường

cong ặc tuyến ối với DAC.

Thời gian thiết lập: ối với một DAC là thời gian cần thiết ể iện áp ra ạt tới giá trị tới

hạn sai số xung quanh giá trị ổn ịnh. Giới hạn này thường là 1/2 LSB hoặc biểu diễn

bằng giá trị FS. Thời gian thiết lập trước hết phụ thuộc vào kiểu chuyển mạch, kiểu iện

trở và kiểu khuếch ại dùng ể xây dựng bộ DAC. Thông thường nó ược ịnh nghĩa bằng

thời gian từ khi iện áp bắt ầu thay ổi cho tới khi ạt tới vùng giới hạn sai số cho trước.

Nó không bao gồm thời gian trễ tính từ khi có sự thay ổi mã số ở ầu vào cho tới khi iện áp ra bắt ầu áp ứng.

Các mạch DAC iển hình

Các DAC có thể ược xây dựng theo một trong những kiểu mạch sau:

Chuyển ổi DA theo kiểu iện trở trọng lượng

Chuyển ổi DA theo kiểu mạch R-2R

Chuyển ổi DA theo phương pháp mã hoá Shannon-Rack

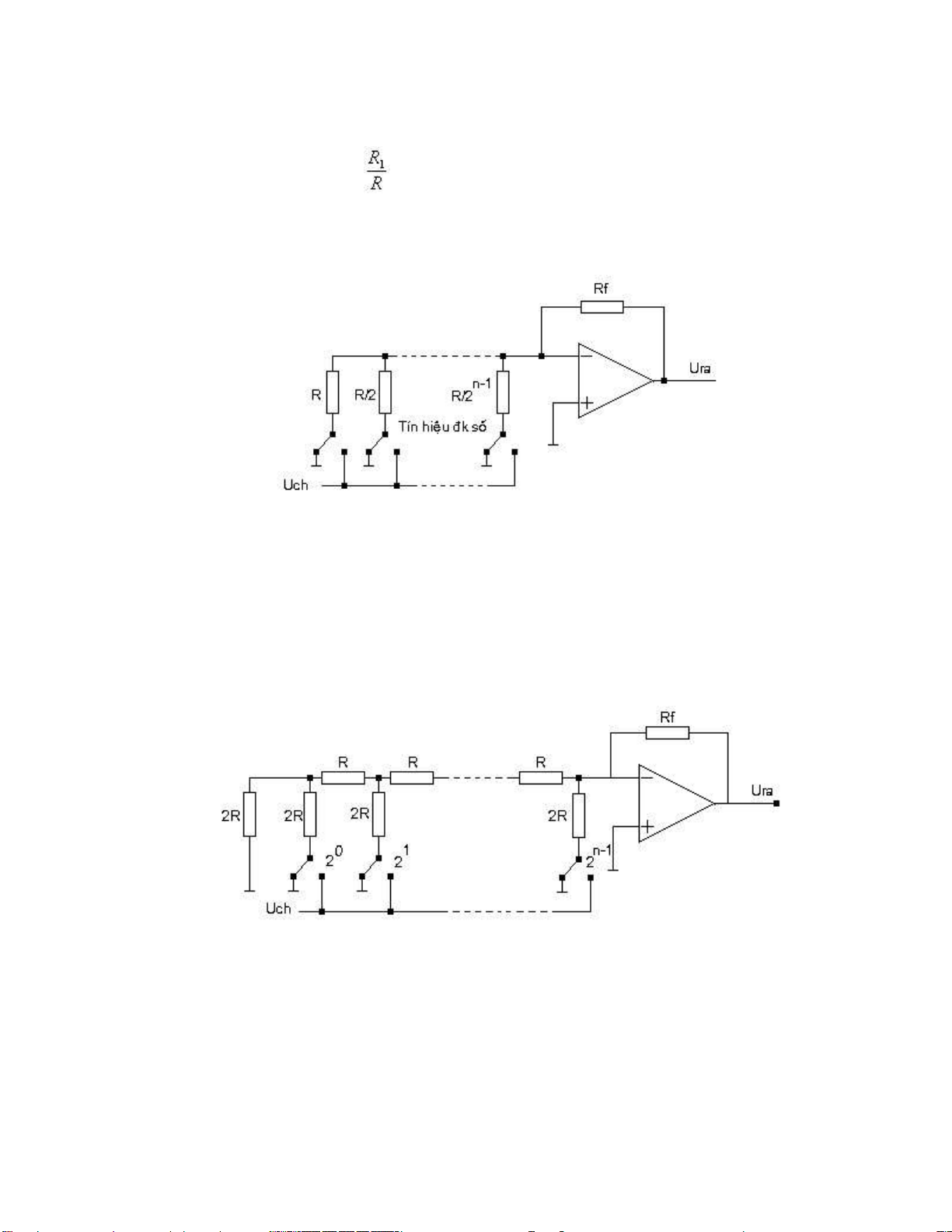

Bộ chuyển ổi DA theo kiểu iện trở trọng lượng (Weighted resistor DAC)

Mạch gồm một nguồn iện áp chuẩn Uch, các chuyển mạch, các iện trở có giá trị lần lượt

là R, R/2, R/4, ... , R/2n-1 và các mạch khuếch ại thuật toán (hình 6.19). Với mạch iện này,

khi một khoá iện nào ược nối với nguồn iện thế chuẩn thì sẽ cung cấp cho bộ KÐTT dòng

iện. Dòng iện này ộc lập với các khoá còn lại. Như vậy có thể thấy ngay rằng biên ộ iện áp

ra phụ thuộc vào các vị trí ược óng hay mở khoá nghĩa là ược nối với iện áp chuẩn Uch hay lOMoARcPSD| 10435767

nói cách khác phụ thuộc vào giá trị các bit tương ứng trong tín hiệu số ưa vào mạch chuyển

ổi. Một cách tổng quát, với một DAC có n bit thì tín hiệu ra ược tính theo công thức: Ura = -Uch

(2n-1.Bn-1 + 2n-2.Bn-2 + ... + 21.B1 + 20.B0)

Trong ó B0 - Bn-1 có giá trị "0" hoặc "1".

Hình 6.19: DAC theo phương pháp iện trở trọng lượng

Mạch có ưu iểm là ơn giản, nhưng nhược iểm là ộ chính xác và tính ổn ịnh của kết quả

phụ thuộc nhiều vào trị số tuyệt ối của các iện trở và sự ổn ịnh của chúng trong các môi

trường khác nhau. Ngoài ra còn phụ thuộc vào tính ổn ịnh và ộ chính xác của nguồn iện áp chuẩn.

Bộ chuyển ổi DA theo kiểu thang iện trở R-2R (R-2R ladder)

Hình 6.20: DAC theo phương pháp mạch R-2R

DAC với thang iện trở R-2R (hình 6.20) khắc phục ược một số nhược iểm của DAC iện trở

trọng lượng. Mạch chỉ gồm hai iện trở R và 2R mắc theo hình thang với nhiều khoá iện

(mỗi khoá iện cho một bit) và một nguồn iện áp chuẩn Uch. Ðại lượng cần tìm là dòng Ith

chảy vào mạch KÐTT khi có một số khoá iện ược nối với Uch. Theo mạch iện ta có: lOMoARcPSD| 10435767 Ura = -Ith.Rf

Xét tại chuyển mạch tương ứng với bit thứ i, nút tương ứng trên mạch hình thang là 2i.

Sử dụng ịnh lý Thevenin, khi óng chuyển mạch vào Uch thì iện thế tương ương Thevenin

tại nút 2i sẽ là Uch/2 và nguồn tương có nội trở là R, như vậy tại nút 2i+1 (tiến về phía mạch

KÐTT) ta có nguồn tương ương Thevenin có trị số là Uch/4 và nội trở là R.

Từ những kết quả trên suy ra rằng khi di chuyển về phía mạch KÐTT thì trị số iện thế

Thevenin tại mỗi nút bằng một nửa trị số tại nút kề cận bên trái nó, và tại nút 2n-1 do ặc tính

của bộ KÐTT iện thế ược coi bằng 0V.

Một cách tổng quát, ta có công thức ể tính iện áp ra của một DAC n bit với iện trở hình thang R-2R như sau:

Trong ó B0 - Bn-1 có giá trị "0" hoặc "1".

Các DAC theo thang iện trở phải dùng số iện trở khá lớn, ví dụ nếu một DAC n bit thì

cần dùng 2(n-1) iện trở trong khi phương pháp iện trở trọng lượng chỉ phải dùng n thôi.

Nhưng bù lại ộ chính xác và tính ổn ịnh của tín hiệu ra ược ảm bảo tốt hơn.

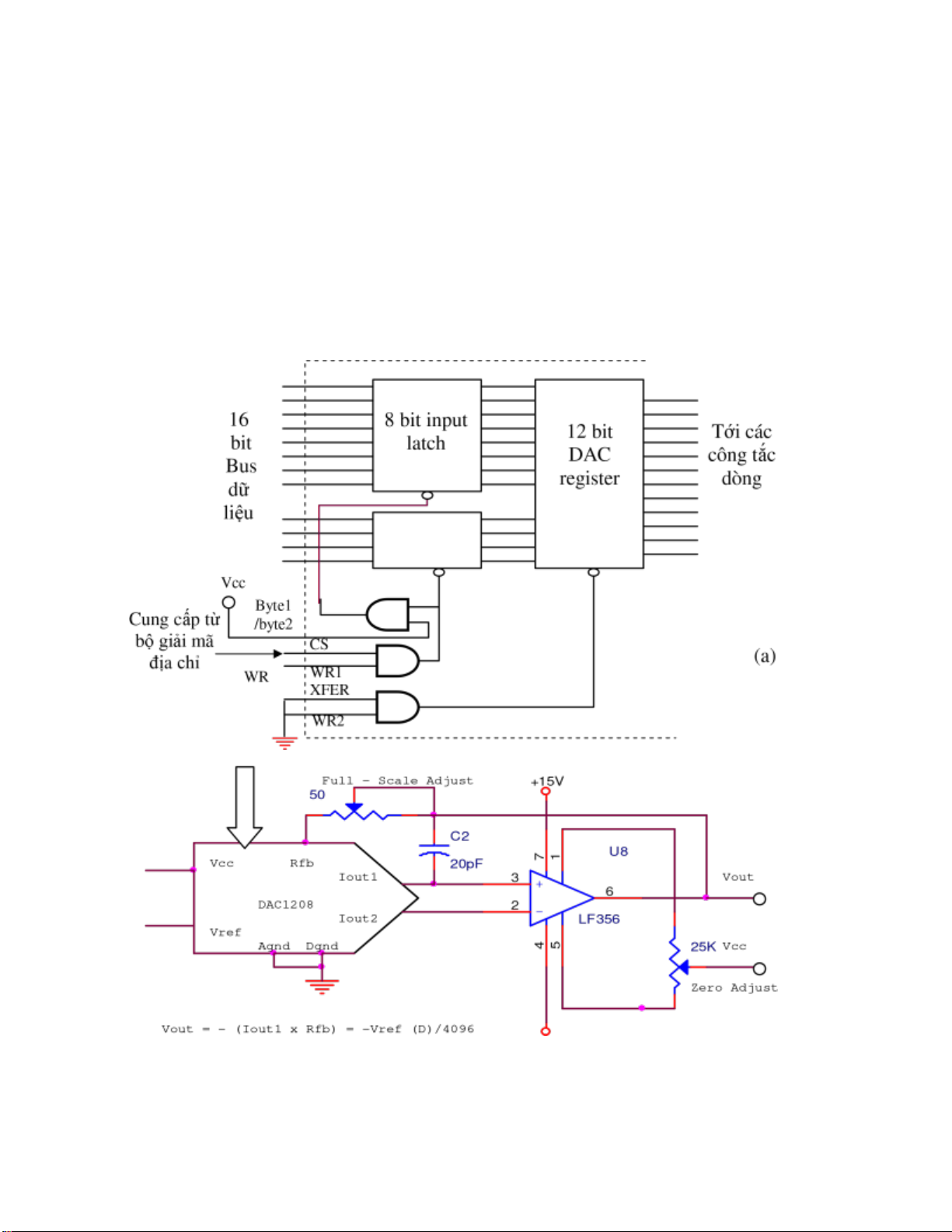

Ghép nối DAC với hệ VXL

Khi sử dụng một DAC 8 bit trong một hệ thống vi xử lý, một cách ơn giản có thể nối

các ngõ vào của chúng tới một cổng ngõ ra, hoặc một số bộ DAC còn cho phép nối trực

tiếp các ngõ vào của chúng tới Bus dữ liệu như ối với một cổng vào ra thông thường.

Còn ối với các ứng dụng yêu cầu ộ phân giải 12 bit, cần phải sử dụng các DAC 12 bit.

Nhưng nếu hệ thống sử dụng vi xử lý 8 bit, trước hết phải nối 8 bit thấp của DAC tới một

cổng vào ra, còn 4 bit cao của nó phải nối tới một cổng vào ra khác. Trong chương trình

cần phải chuyển 8 bit thấp tới bằng một lệnh ghi, và 4 bit cao bằng một lệnh ghi khác.

Nhưng khi sử dụng hai lần ghi như vậy, ngõ ra sẽ bị ột biến, trước khi ạt ược giá trị ổn ịnh

như mong muốn. Ví dụ khi muốn biến ổi giá trị của 1 DAC 12 bit từ 0000 1111 1111 thành

0001 0000 0000. Khi ghi 8 bit thấp tới DAC, ngõ ra của nó sẽ thay ổi giá trị từ 0000 1111

1111 thành 0000 0000 0000, sau ó ghi tới 4 bit cao ngõ ra với trở về giá trị mong muốn là

0001 0000 0000. Như vậy trong khoảng thời gian giữa hai lần ghi sẽ là giá trị không mong

muốn. Trong nhiều hệ thống vấn ề trên sẽ gây ra hoạt ộng không ổn ịnh. Để tránh ược nhược

iểm này có thể sử dụng các bộ cài tại ngõ vào DAC. Bộ cài sẽ ược nạp giá trị hai lần sau ó

chuyển ồng thời 12 bit tới DAC. Rất nhiều bộ DAC hiện nay cho phép thực hiện công việc

trên một cách dễ dàng. Hình 5.36a trình bày cấu trúc ngõ vào của DAC1230 và DAC08 của

hãng national, chúng có bộ cài 4 bit thấp vì thế có thể ghi tới 12 bit ngõ vào bằng hai lệnh lOMoARcPSD| 10435767

ghi từ các cổng vào ra 8 bit, hoặc trực tiếp từ Bus dữ liệu. Cũng có thể nối các ngõ vào của

DAC này tới các ường dữ liệu của các hệ thống 16 bit như trên hình 6.21.

Các bộ DAC yêu cầu iện áp chuẩn chính xác, mạch hình 5.36b sử dụng iện áp chuẩn –

10,000V. Các DAC cung cấp dòng ngõ ra, vì vậy cần nối thêm một mạch Op Amp ở ngõ

ra ể biến ổi thành iện áp tương ứng. Thông thường sử dụng các bộ khuếch ại có ngõ vào

FET, vì dòng phân cực ngõ vào của các bộ khuếch ại lưỡng cực có thể ảnh hưởng tới ộ

chính xác của ngõ ra. Chú ý trong mạch sử dụng masse số và masse tương tự riêng nhau, ể

tránh nhiễu cho tín hiệu số gây ra bởi sự méo dạng của tín hiệu tương tự. +15 V Vref -15V (b) lOMoARcPSD| 10435767

Hình 6.21: (a) Cấu trúc cài bên trong của DAC1208.

(b) Mạch kết nối tương tự.

6.2.5.2 Biến ổi tương tự – số (ADC – Analog to Digital Converter)

Trong phần trước chúng ta ã bàn ến việc thu nhận các tín hiệu thông qua các sensor

nhiệt, áp suất ... và các mạch khuếch ại thuật toán dùng ể khuếch ại và lọc các tín hiệu iện

này. Bước tiếp theo là bộ biến ổi AD biến ổi tín hiệu tương tự sang dạng số ể có thể làm việc ược với CPU.

Trong một bộ ADC, tín hiệu tương tự sau khi qua xử lý ược ưa vào mạch lấy mẫu. Mạch

lấy mẫu sẽ Lấy mẫu tín hiệu tương tự tại các thời iểm khác nhau và cách ều nhau, nói cách

khác ây là quá trình rời rạc hoá tín hiệu về mặt thời gian.

Sau khi lấy mẫu, các mẫu iện áp sẽ ược lượng tử hoá và mã hoá. Quá trình lượng tử hoá

về bản chất là quá trình làm tròn số ược thực hiện theo nguyên tắc so sánh, tín hiệu cần

chuyển ổi ược so sánh với một ơn vị chuẩn. Còn mã hoá là quá trình xắp xếp lại kết quả ã

lượng tử theo một quy luật nhất ịnh tuỳ thuộc vào loại mã yêu cầu ở ầu ra bộ biến ổi.

Các tham số cơ bản của bộ chuyển ổi gồm có:

Dải biến ổi của iện áp tương tự ầu vào là khoảng iện áp mà ADC có thể thực hiện

chuyển ổi ược. Khoảng iện áp này có thể lấy giá trị từ 0 ến một giá trị âm hay dương,

hoặc cũng có thể là iện áp hai cực tính -UAM tới + UAM.

Ðộ chính xác của ADC: Tham số ặc trưng cho ộ chính xác của ADC là ộ phân giải

(Resolution). Tín hiệu ở ầu ra của một ADC là các giá trị số ược xắp xếp theo một quy

luật nào ó. Số các số hạng ở mã ầu ra (số bit trong từ mã nhị phân) tương ứng với dải

biến ổi iện áp vào cho biết mức chính xác của phép biến ổi.

Ví dụ một bộ biến ổi AD có số bit ầu ra là N=12 thì sẽ phân biệt ược 212=2096 mức

trong dải biến ổi iện áp ầu vào của nó - UAM chẳng hạn. Như vậy mỗi mức ADC phân

biệt ược ở ầu vào là UAM/2096. Trong thực tế người ta dùng số bit N ể ặc trưng cho ộ

chính xác của một ADC khi dải biến ổi iện áp ầu vào là không ổi.

Liên quan ến ộ chính xác của một ADC còn có các tham số như: méo phi tuyến, sai số

khuếch ại, sai số lệch không, sai số ơn iệu, sai số lượng tử hoá ...

Tốc ộ chuyển ổi cho biết số kết quả chuyển ổi trong một giây, còn ược gọi là tần số

chuyển ổi fc. Cũng có thể dùng tham số thời gian chuyển ổi Tc ể ặc trưng cho tốc ộ

chuyển ổi (Tc = 1/fc). Tốc ộ chuyển ổi càng cao thì ộ chính xác càng giảm và ngược lại.

Các phương pháp chuyển ổi AD

Có nhiều cách ể phân loại các bộ biến ổi AD, hay dùng hơn cả là phương pháp phân loại

về mặt thời gian. Phương pháp này có ưu iểm là cho phép phán oán một cách tổng quát về tốc ộ chuyển ổi. lOMoARcPSD| 10435767

Chuyển ổi song song (Parallel Comparator ADC): Tín hiệu cần chuyển ổi ược so sánh

cùng một lúc với nhiều giá trị chuẩn, vì vậy các bit ược xác ịnh ồng thời và ưa ến ầu ra.

Chuyển ổi nối tiếp theo mã ếm: Quá trình so sánh ược thực hiện từng bước theo quy

luật mã ếm. Kết quả chuyển ổi ược xác ịnh bằng cách ếm số lượng giá trị tín hiệu tương tự cần chuyển ổi.

Chuyển ổi nối tiếp theo mã nhị phân: Quá trình so sánh ược thực hiện từng bước theo

quy luật của mã nhị phân. Các ơn vị chuẩn dùng ể so sánh lấy các giá trị giảm dần theo

mã nhị phân, do ó các bit ược xác ịnh lần lượt từ bit có ý nghĩa nhất MSB (Most

Significant Bit) ến bit có ít ý nghĩa nhất LSB (Least Significant Bit).

Chuyển ổi song song - nối tiếp kết hợp: Trong phương pháp này qua mỗi bước so sánh

có thể xác ịnh ược tối thiểu là 2 bit ồng thời.

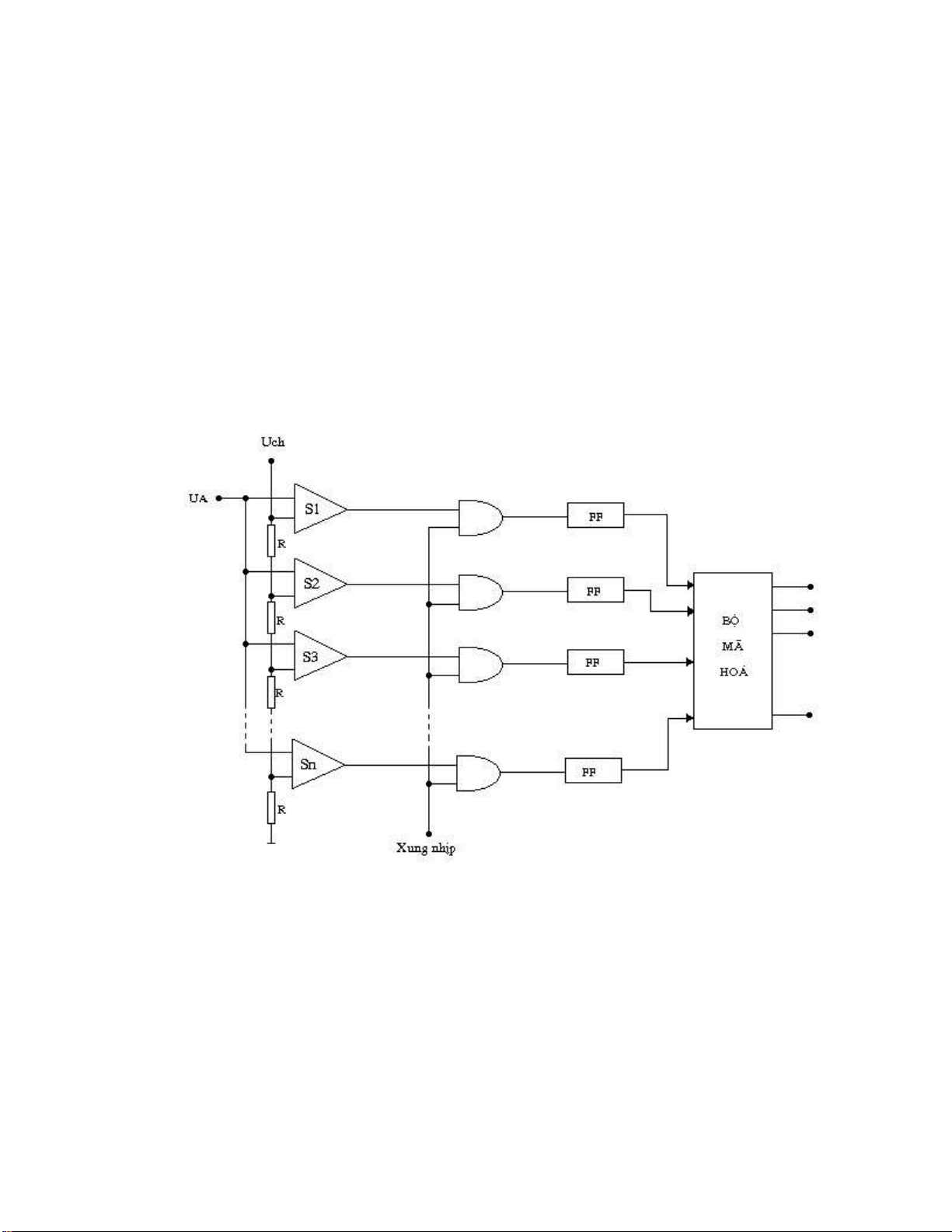

Chuyển ổi theo phương pháp song song

Hình 6.22: Sơ ồ nguyên lý bộ chuyển ổi AD theo phương pháp song song

Nguyên tắc của bộ chuyển ổi:

Tín hiệu tương tự UA ược ồng thời ưa ến các bộ so sánh từ S1 - Sm. Ðiện áp chuẩn Uch

ược ưa ến ầu vào thứ hai của bộ so sánh qua thang iện trở R. Do ó các iện áp chuẩn ặt vào

bộ so sánh lân cận khác nhau một lượng không ổi và giảm dần từ S1 - Sm. Ðầu ra của các

bộ so sánh có iện áp chuẩn lấy trên thang iện trở thì có mức logic "1", còn ngược lại có mức logic "0". lOMoARcPSD| 10435767

Các ầu ra của mạch ược nối với một mạch "AND", ầu còn lại của mạch "AND" nối với

xung nhịp. Chỉ khi xuất hiện xung nhịp ở ầu vào mạch "AND" thì xung ra của bộ so sánh

ược vào mạch nhớ Flip - Flop (FF). Như vậy xung nhịp óng vai trò ảm bảo cho quá trình so

sánh và ưa tín hiệu vào bộ nhớ, sau ó bộ mã hoá sẽ biến ổi tín hiệu vào dưới dạng mã ếm

thành mã nhị phân (có thể là dạng khác).

Mạch biến ổi song song có ưu iểm là tốc ộ chuyển ổi nhanh, nhưng kết cấu mạch khá phức

tạp nếu ta tăng ộ phân giải của phép biến ổi AD (resolution). Thực vậy, ể thiết lập một bộ

biến ổi có ộ phân giải n bit thì cần phải có (2n -1) bộ so sánh, do vậy phương pháp này chỉ

dùng cho các bộ ADC tốc ộ cao và ộ phân giải thấp.

Chuyển ổi AD theo phương pháp ếm

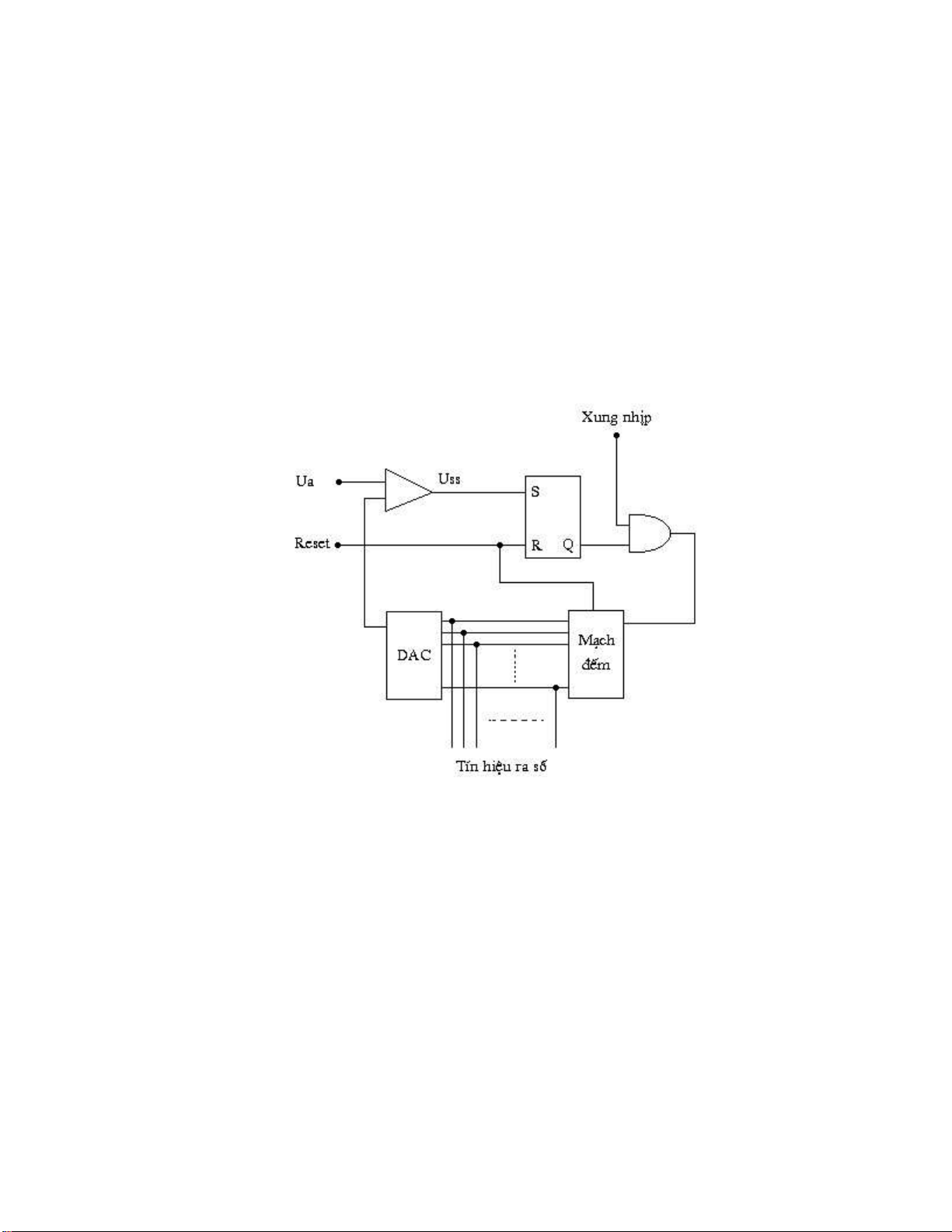

Hình 6.23: Sơ ồ khối mạch ADC kiểu ếm

Mạch bao gồm các phần tử: Bộ so sánh, RS Flip-Flop, cổng "AND" dùng ể óng mở

xung nhịp, bộ ếm n bit và một DAC n bit. Các phần tử ược mắc thành mạch hồi tiếp.

Hoạt ộng của mạch: Lúc ầu mạch Flip-Flop và mạch ếm ược Reset, lối ra Q của FF ở

mức logic "0", bộ ếm cũng xoá về 0, do ó iện áp ra UDAC của DAC là 0V. Cổng AND mở ể

cho các xung nhịp vào mạch ếm. Lúc này iện áp vào Ua lớn hơn UADC nên Uss ở trị thấp.

UDAC tăng dần theo hình bậc thang vì mạch ếm liên tục ổi trạng thái từ thấp lên cao, khi

UDAC ủ lớn hơn Ua thì Uss chuyển lên cao làm cho lối ra Q của FF chuyển lên mức logic "0"

làm cổng AND óng lại. Lúc này nội dung bộ ếm là tín hiệu số n bit tương ứng với tín hiệu

tương tự Ua cần chuyển ổi. lOMoARcPSD| 10435767

Như vậy thời gian chuyển ổi của ADC kiểu ếm phụ thuộc vào ộ lớn của tín hiệu tương

tự Ua và tần số xung nhịp. Nếu Ua càng lớn thì thời gian chuyển ổi càng dài, nếu xung

nhịp cao thì thời gian chuyển ổi ngắn.

Ngoài ra ADC kiểu ếm còn có một ặc iểm là thời gian chuyển ổi của mạch sẽ hạn chế

tần số biến thiên cao nhất của tín hiệu tương tự ầu vào Ua.

Chuyển ổi AD theo phương pháp xấp xỉ liên tiếp

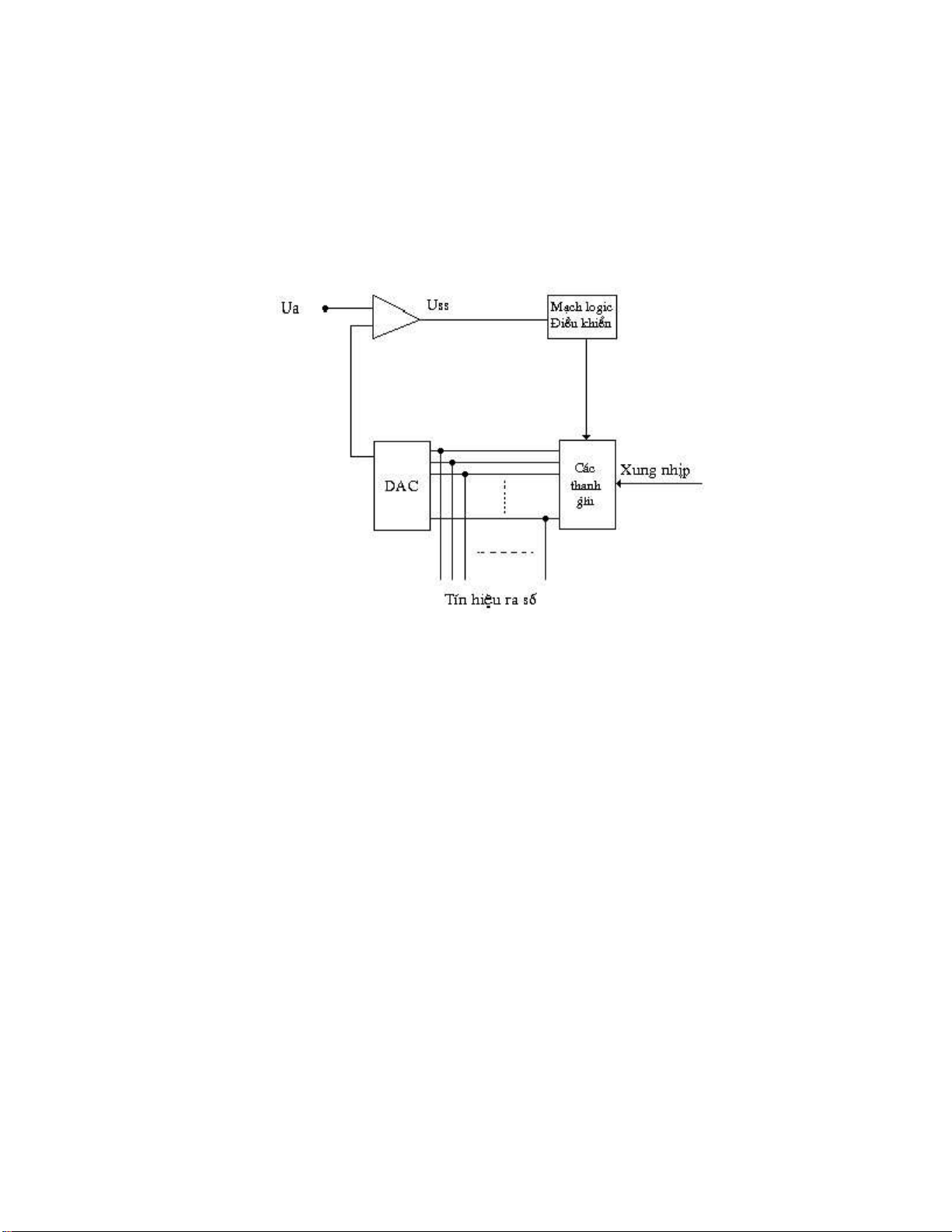

Hình 6.24: Sơ ồ khối mạch ADC xấp xỉ liên tiếp

Chuyển ổi AD theo phương pháp xấp xỉ liên tiếp có ưu iểm lớn là thời gian chuyển ổi

tỷ lệ thuận với số bit của mã số và thời gian thiết lập của mạch ghi chứ không phụ thuộc

vào ộ lớn của tín hiệu chuyển ổi.

Khởi ầu mạch ghi ở trạng thái Reset, sau ó mạch iều khiển kích thích ể bit lớn nhất xuất

hiện. Khi ó sẽ xảy ra một trong hai trường hợp:

Nếu UDAC > Ua thì bit này ược bỏ qua (vẫn thiết lập "0")

Nếu UADC < Ua thì bit này ược duy trì (thiết lập "1")

Sau ó lại kích thích ể bit kế tiếp xuất hiện, và công việc so sánh cứ tiếp tục ến khi

UDAC = Ua thì quá trình chuyển ổi kết thúc.

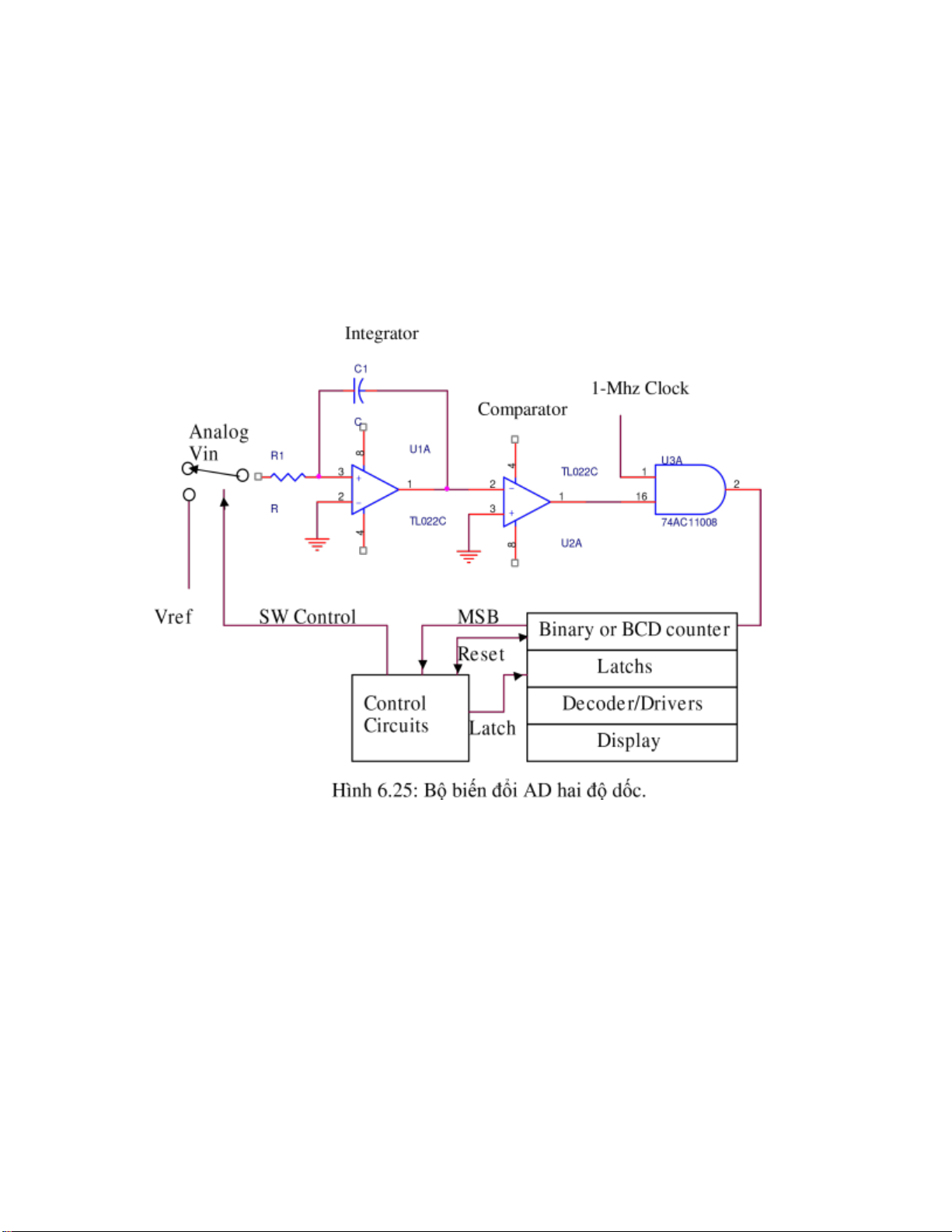

Chuyển ổi AD theo phương pháp tích phân hai ộ dốc.

Hình 6.25 trình bày sơ ồ các khối chức năng của một bộ ADC hai ộ dốc. Loại ADC này

thường sử dụng trong các volt kế số vì có số bit phân giải cao với giá thành hạ.

Khi bắt ầu biến ổi mạch iều khiển sẽ xoá bộ ếm về 0 và nối ngõ vào của mạch tích phân

tới tín hiệu iện áp cần biến ổi. Khi iện áp cần biến ổi dương, ngõ ra mạch tích phân sẽ là lOMoARcPSD| 10435767

một iện áp âm. Khi ngõ ra mạch so sánh có iện áp âm khoảng vài microvolt, ngõ ra bộ so

sánh vẫn ở mức cao, lúc này cổng AND cho phép xung 1 Mhz ưa vào bộ ếm. Sau một giá

trị ếm xác ịnh nào ó (thường là 1000), mạch iều khiển sẽ chuyển ngõ vào của mạch tích

phân tới iện áp chuẩn âm và xoá bộ ếm. Với iện áp ngõ vào âm, iện áp ngõ ra của mạch tích

phân sẽ tăng dần về 0. Khi ngõ ra mạch tích phân ạt tới 0 volt, ngõ ra mạch so sánh sẽ

chuyển trạng thái về mức thấp cắt xung clock cung cấp tới bộ ếm. Giá trị ếm ược trong bộ

ếm cho tới khi ngõ ra mạch tích phân ạt tới 0 volt sẽ tương ứng với giá trị iện áp vào.

Ghép nối ADC với hệ VXL

Giao tiếp với ADC so sánh song song.

Trong hầu hết các ứng dụng sử dụng các bộ ADC biến ổi song song, các bộ ADC này sẽ

cung cấp dữ liệu ngõ ra thông thường rất nhanh so với yêu cầu. Vì vậy hoàn toàn có thể sử

dụng một mạch thâm nhập trực tiếp bộ nhớ ể nạp trực tiếp các dữ liệu của ADC vào bộ nhớ

mà không cần sự iều khiển của vi xử lý. Bộ vi xử lý sau ó có thể xử lý các dữ liệu ã ược lấy vào bộ nhớ.

Giao tiếp với ADC hai ộ dốc và ếm liên tiếp. lOMoARcPSD| 10435767

Với các bộ ADC hai ộ dốc và ếm liên tiếp, thời gian biến ổi là khá chậm so với tốc ộ hoạt

ộng của CPU. Để ọc ược dữ liệu úng, cần kiểm tra trạng thái của tín hiệu chốt dữ liệu cung

cấp từ mạch iều khiển trong ADC. Khi tín hiệu này tác ộng mức cao, vi xử lý có thể ọc ược

một mã dữ liệu ể ghi vào bộ nhớ.

Giao tiếp với ADC xấp xỉ liên tiếp.

Đọc dữ liệu trong các bộ ADC xấp xỉ liên tiếp cần thực hiện theo sự iều khiển của chương

trình. Trước hết cần cung cấp tín hiệu khởi ộng quá trình biến ổi SC (Start Converter) từ vi

xử lý tới ADC. Tiếp theo kiểm tra ngõ ra EOC của ADC ể biết ược thời iểm quá trình biến

ổi kết thúc. Khi EOC tác ộng, vi xử lý có thể ọc ược một dữ liệu hợp lệ cung cấp từ ADC.

Với các bộ ADC có nhiều kênh vào, thông thường chúng sẽ có các ường ịa chỉ và tín hiệu

cài ịa chỉ ể chọn kênh. Công việc này ược thực hiện dễ dàng bằng phần mềm.