Preview text:

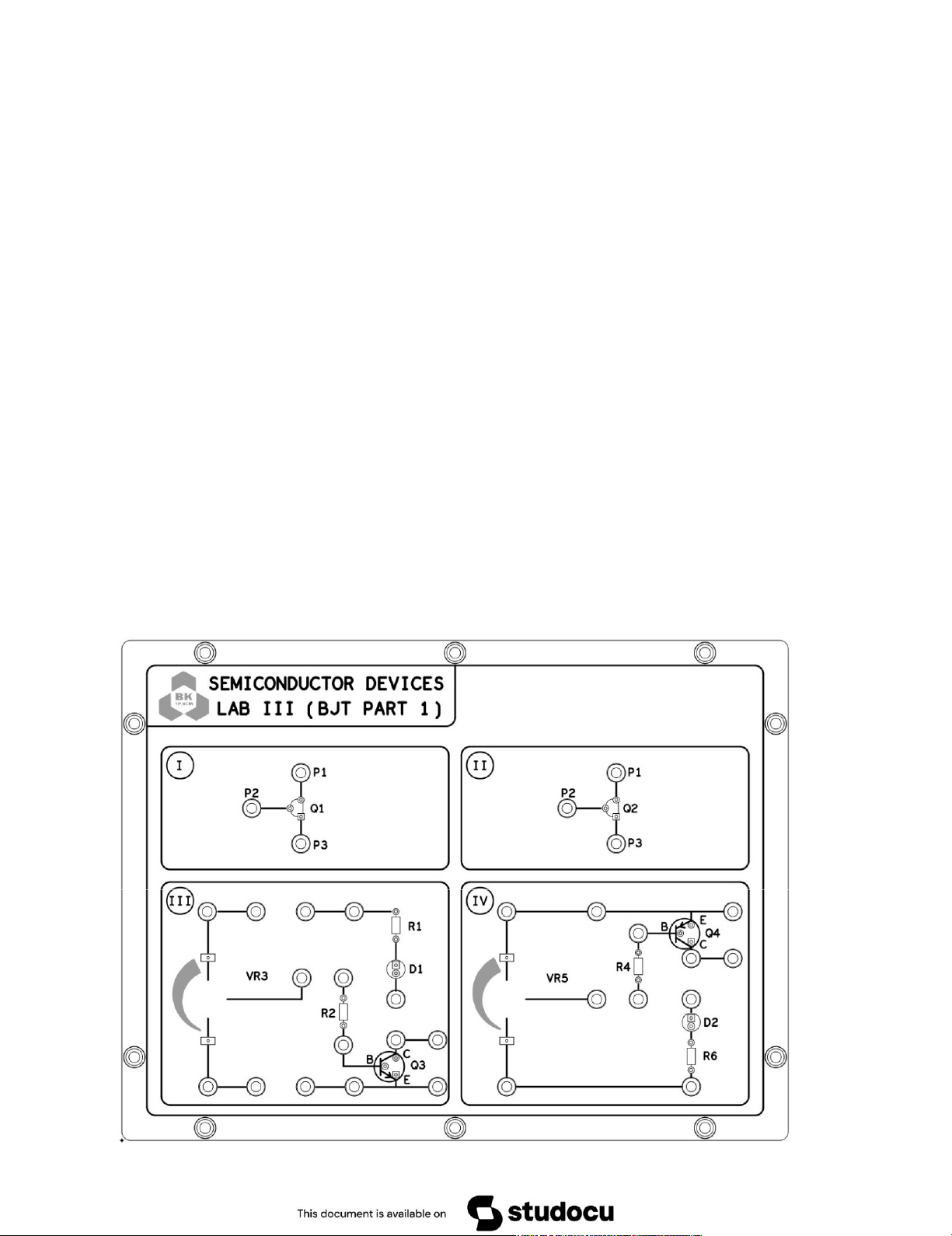

lOMoARcPSD|46958826 lOMoARcPSD|46958826 BÀI TN 4 KHẢO SÁT BJT Nhóm 09 – L07 Thành viên MSSV Nguyễn Việt Tiến 2114993 Nguyễn Hoàng Đạt 2111011 Thiên Hải Lâm 2113888 MỤC TIÊU:

Nắm được cách sử dụng kit thí nghiệm, dụng cụ đo.

Nắm được đặc tính các linh kiện BJT loại npn, pnp Khảo

sát mạch khuếch đại, mạch đóng/ngắt dùng BJT CHUẨN BỊ: Chuẩn bị bài prelab

Xem lại cách sử dụng các công cụ đo VOM, DVM và Oscilloscope. lOMoARcPSD|46958826 2 THÍ NGHIỆM 1 Mục tiêu

Đo và kiểm tra BJT. Yêu cầu

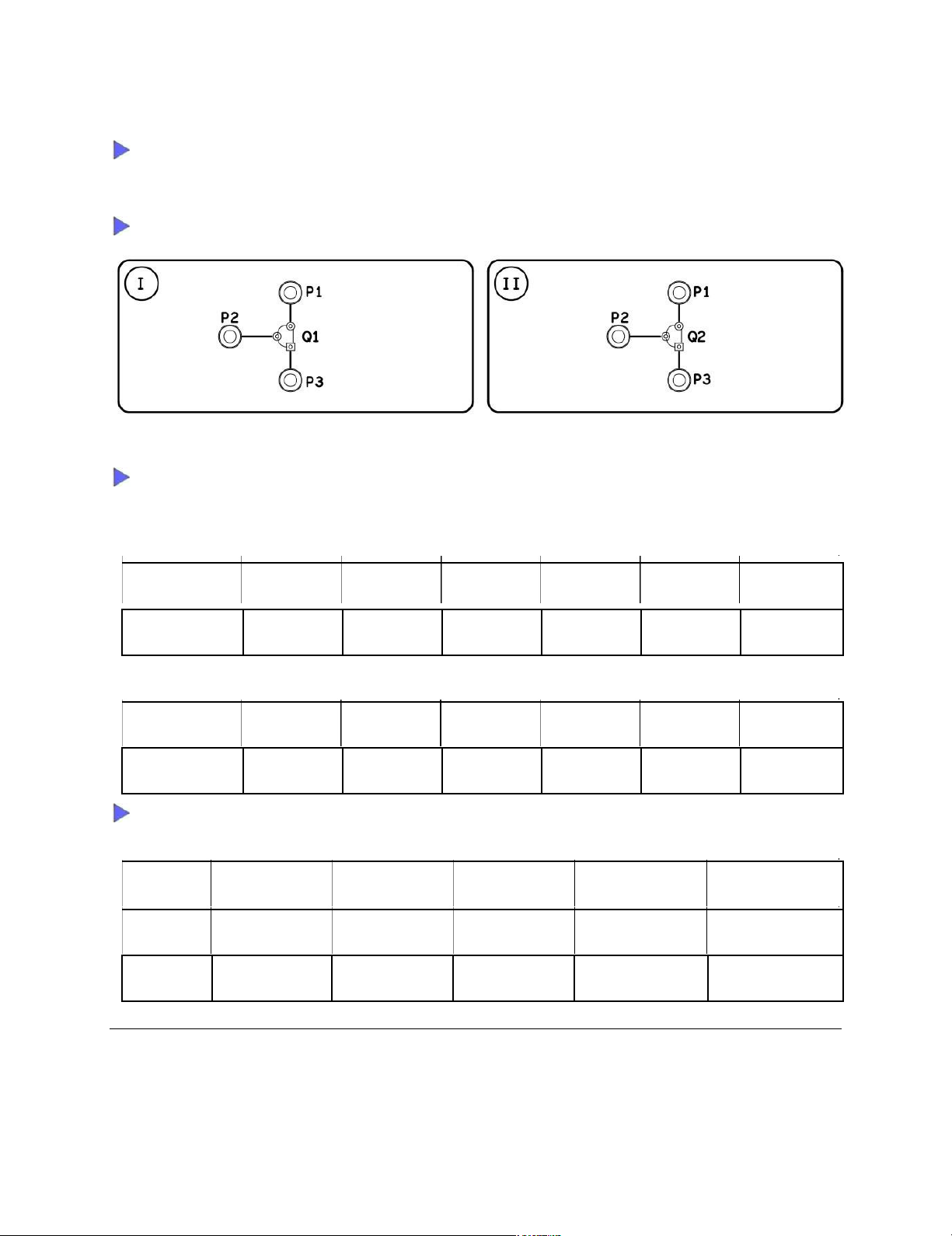

Dùng VOM đo và kiểm tra BJT ở module 1 và 2, phần BJT Kiểm tra

Đưa VOM về chế độ đo diode. Đo điện áp giữa các chân của BJT trong khối I và

II và ghi nhận vào bảng sau Transistor Q1 Điểm đo P1–P2 P2–P1 P1–P3 P3–P1 P2–P3 P3–P2 Giá trị (V) 0,671 0,000 0,663 0,000 0,000 0,000 Transistor Q2: Điểm đo P1–P2 P2–P1 P1–P3 P3–P1 P2–P3 P3–P2 Giá trị (V) 0,657 0,000 0,000 0,000 0,000 0,670

Xác định xem transistor loại gì và các chân P1-P2-P3 là chân gì,

BJT còn tốt hay không. Giải thích. P1 P2 P3 Loại BJT Chất lượng Q1 Base Collector Emitter N-P-N Tốt Q2 Collector Base Emitter P-N-P Tốt

Lab Material for “Semiconductor device

experiment lab” Nhóm 09 – L07 lOMoARcPSD|46958826 3 Giải thích: + Với Q1: V 0,671 V P1 P2: p n 12

Q1 là loại N-P-N với P1 là cực Base V13 0,663 V P1 P3: p n + Với Q2: V 0,657 V P1 P2: p n 12

Q2 là loại P-N-P với P2 là cực Base V 32 0,670 V P3 P2: p n

Lab Material for “Semiconductor device

experiment lab” Nhóm 09 – L07 lOMoARcPSD|46958826 4 THÍ NGHIỆM 2 Mục tiêu

Khảo sát các miền hoạt động tắt/khuếch đại/bão hòa của BJT npn Chuẩn bị

Đọc xem điện trở R1 có giá trị là bao nhiêu và kiểm chứng lại bằng VOM.

R1 = 1000 Ω (giá trị đọc)

R1 = 988 Ω (giá trị đo)

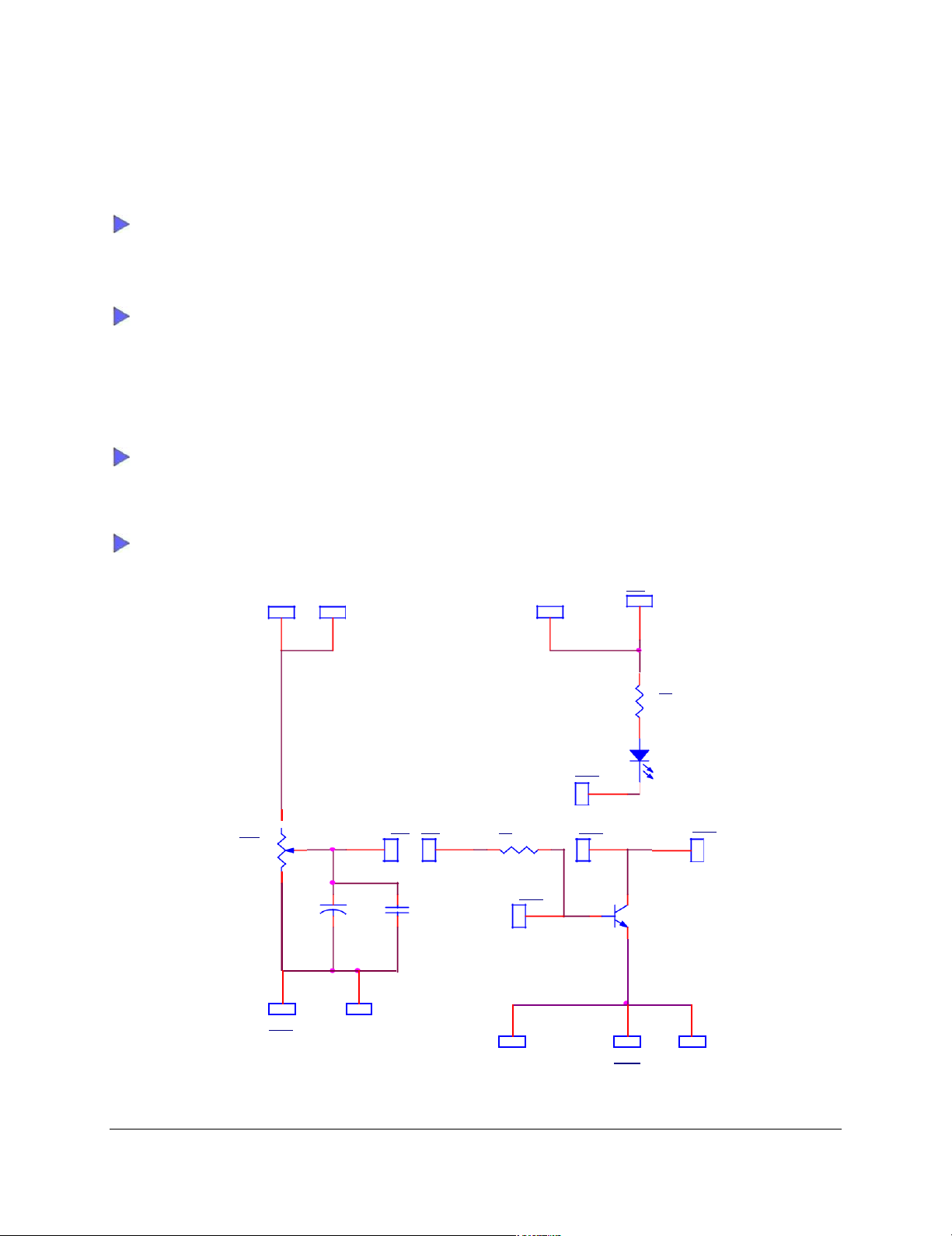

Chỉnh nguồn điện về 12V và kết nối mạch như Hình 2. Một VOM đo dòng

điện Ib ở tầm uA, một VOM đo dòng Ic ở tầm mA, và 1 VOM đo điện áp Vce.

Vặn biến trở VR3 về mức nhỏ nhất. TP7 TP30 TP31 TP29 1 1 1 1 R1 1K D1 LED TP11 1 VR3 TP8 TP9 R2 TP12 TP13 10K 1 1 1 1 50K TP10 C6 C8 1 Q3 10uF/50V 0.1u/50V C1815 1 1 TP14 TP28 1 1 1 TP32 TP15 TP27

Hình 1: Sơ đồ phần III

Lab Material for “Semiconductor device

experiment lab” Nhóm 09 – L07

Downloaded by Pham Huyen (21073258@vnu.edu.vn) lOMoARcPSD|46958826 5

Hình 2: Layout thực tế trên module thí nghiệm Tiến hành

Bật nguồn. Chỉnh biến trở để thay đổi dòng điện Ib, quan sát giá trị

Ic và Vce và điền vào bảng sau: Ib

10uA 15uA 20uA 25uA 30uA 35uA 40uA 45uA 50uA Ic (mA) 3,22 4,78 6,34 7,77 9,05 9,24 9,28 9,29 9,30 Vce (V) 6,25 4,69 3,11 1,34

0,384 0,205 0,187 0,163 0,152

Với Ib trong khoảng nào thì transistor dẫn khuếch đại? Khi đó hfe là bao nhiêu?

Với Ib trong khoảng 10÷30 thì transistor dẫn khuếch đại.

Khi đó, hfe khoảng 302.

Lab Material for “Semiconductor device

experiment lab” Nhóm 09 – L07

Downloaded by Pham Huyen (21073258@vnu.edu.vn) lOMoARcPSD|46958826 6

Khi dùng transistor làm nhiệm vụ đóng/ngắt, ta đưa transistor vào chế độ nào? Vì sao?

– Khi dùng transistor làm nhiệm vụ đóng/ngắt, ta đưa transistor vào

chế độ bão hòa/tắt. – Vì:

+ Khi ở chế độ bão hòa, transistor cho dòng điện đi qua và có Vce

rất nhỏ, mạch như ngắn mạch, thực hiện chức hiện đóng.

+ Khi ở chế độ tắt, transistor không cho dòng điện đi qua, hoạt động

như mạch hở, thực hiện chức năng ngắt.

Lab Material for “Semiconductor device

experiment lab” Nhóm 09 – L07

Downloaded by Pham Huyen (21073258@vnu.edu.vn) lOMoARcPSD|46958826 7 THÍ NGHIỆM 3 Mục tiêu

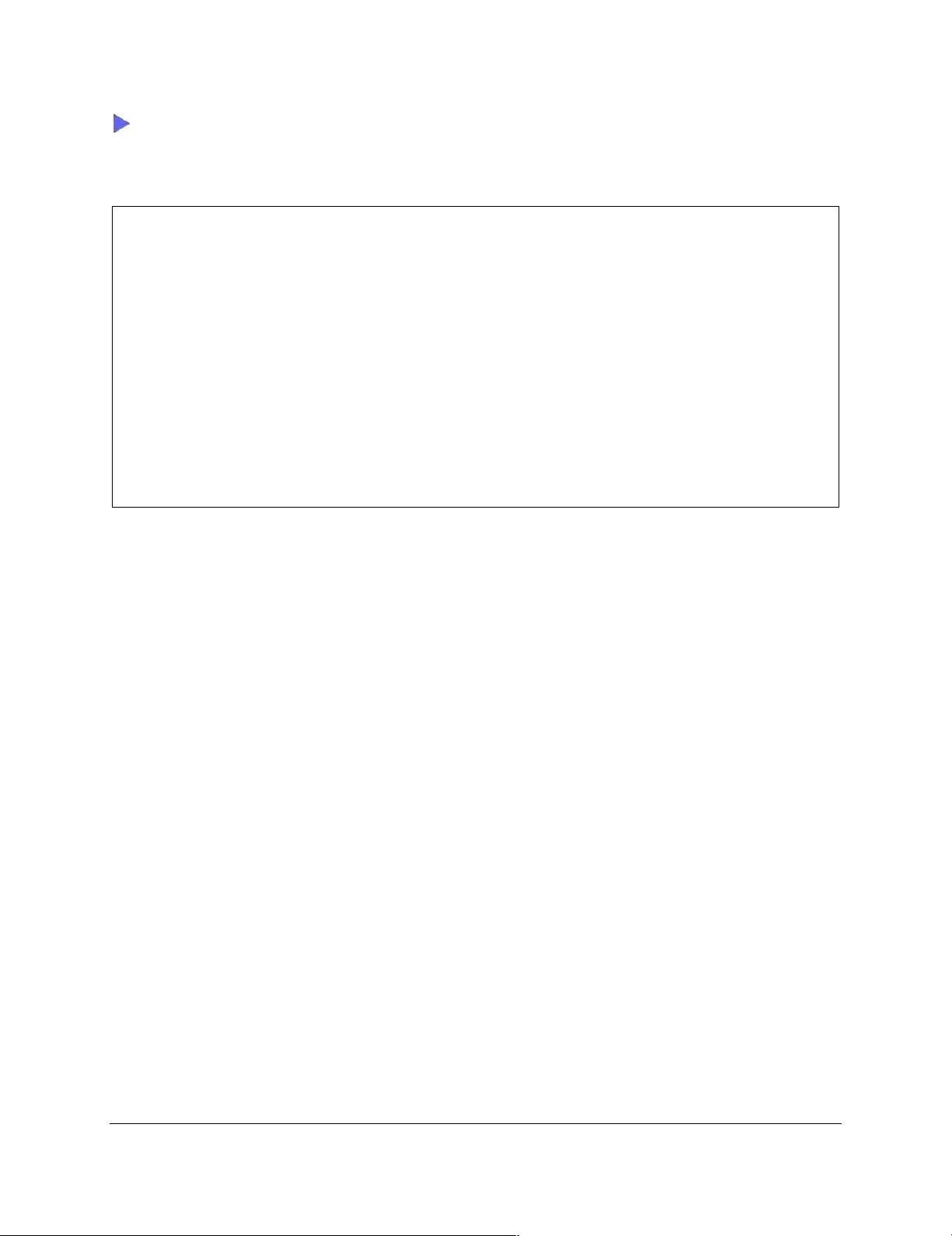

Khảo sát các miền hoạt động tắt/khuếch đại/bão hòa của BJT pnp Chuẩn bị

Đọc xem điện trở R6 có giá trị là bao nhiêu và kiểm chứng lại bằng VOM.

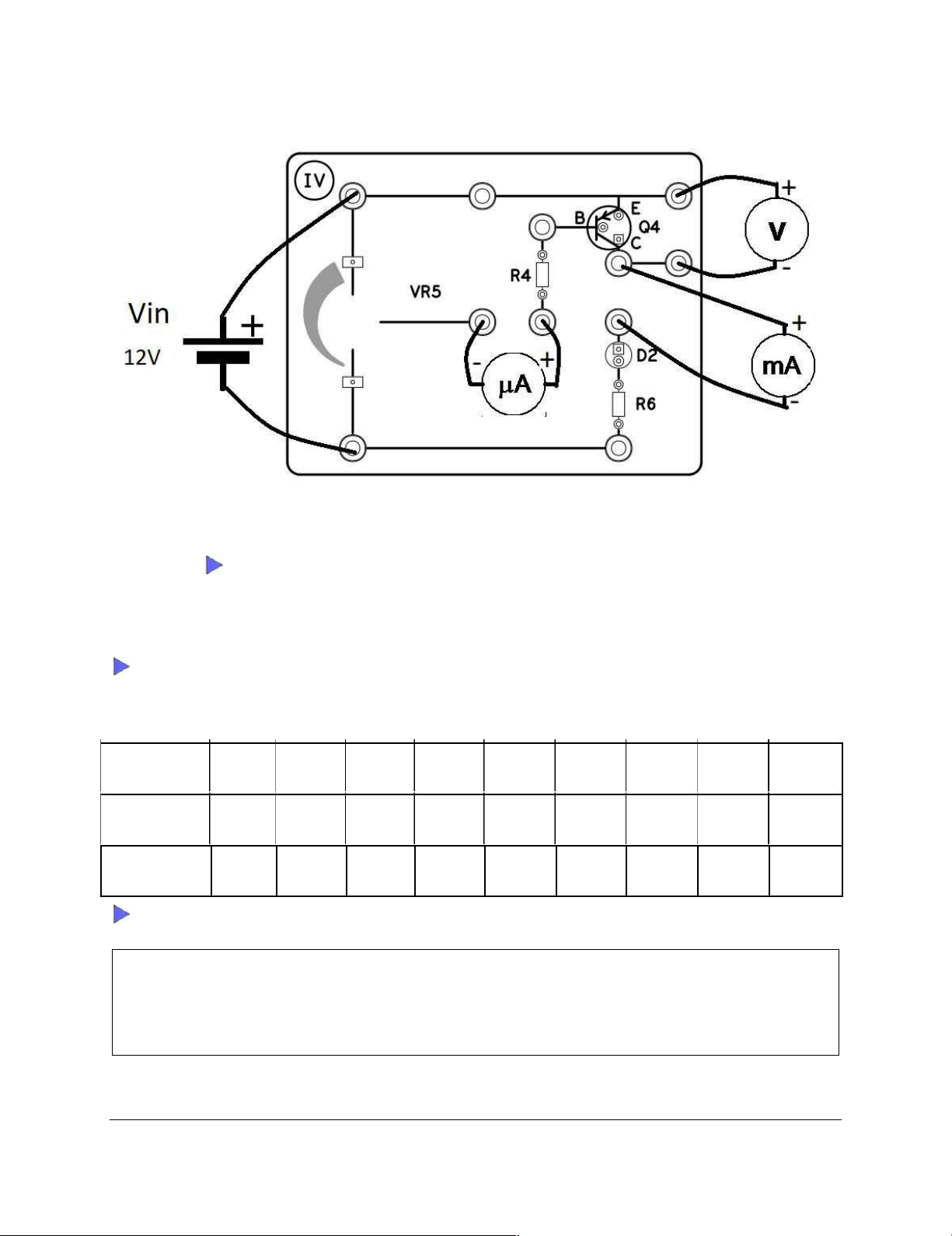

Chỉnh nguồn điện về 12V và kết nối mạch như Hình 4. Một VOM đo dòng

điện Ib ở tầm uA, một VOM đo dòng Ic ở tầm mA, và 1 VOM đo điện áp Vce. TP17 TP16 1 1 TP18 1 Q4 TP21 TP22 1 1 TP23 2N3906 1 TP24 VR5 TP19 TP20 R4 1 10K 1 1 D2 50K LED C7 C1 0.1u/50V 10uF/50V R6 1K 1 1 TP25 TP26

Hình 3: Sơ đồ khối BJT pnp

Lab Material for “Semiconductor device

experiment lab” Nhóm 09 – L07

Downloaded by Pham Huyen (21073258@vnu.edu.vn) lOMoARcPSD|46958826 8

Hình 4: Sơ đồ kết nối trên module thí nghiệm phần

BJT pnp Vặn biến trở VR3 về mức lớn nhất. Tiến hành

Bật nguồn. Chỉnh biến trở để thay đổi dòng điện Ib, quan sát giá trị

Ic và Vce và điền vào bảng sau: Ib

10uA 15uA 20uA 25uA 30uA 35uA 40uA 45uA 50uA Ic (mA) 2,54 3,72 4,75 5,72 6,66 7,46 8,25 8,95 9,15 Vce (V) 6,94 5,68 3,75 3,20 2,71 1,62 0,83 0,30 0,21

Với Ib trong khoảng nào thì transistor dẫn khuếch đại? Khi đó hfe là bao nhiêu?

Với Ib nằm trong khoảng 10÷30 thì transistor dẫn khuếch đại.

Khi đó, hfe khoảng 222.

Lab Material for “Semiconductor device

experiment lab” Nhóm 09 – L07

Downloaded by Pham Huyen (21073258@vnu.edu.vn) lOMoARcPSD|46958826 9

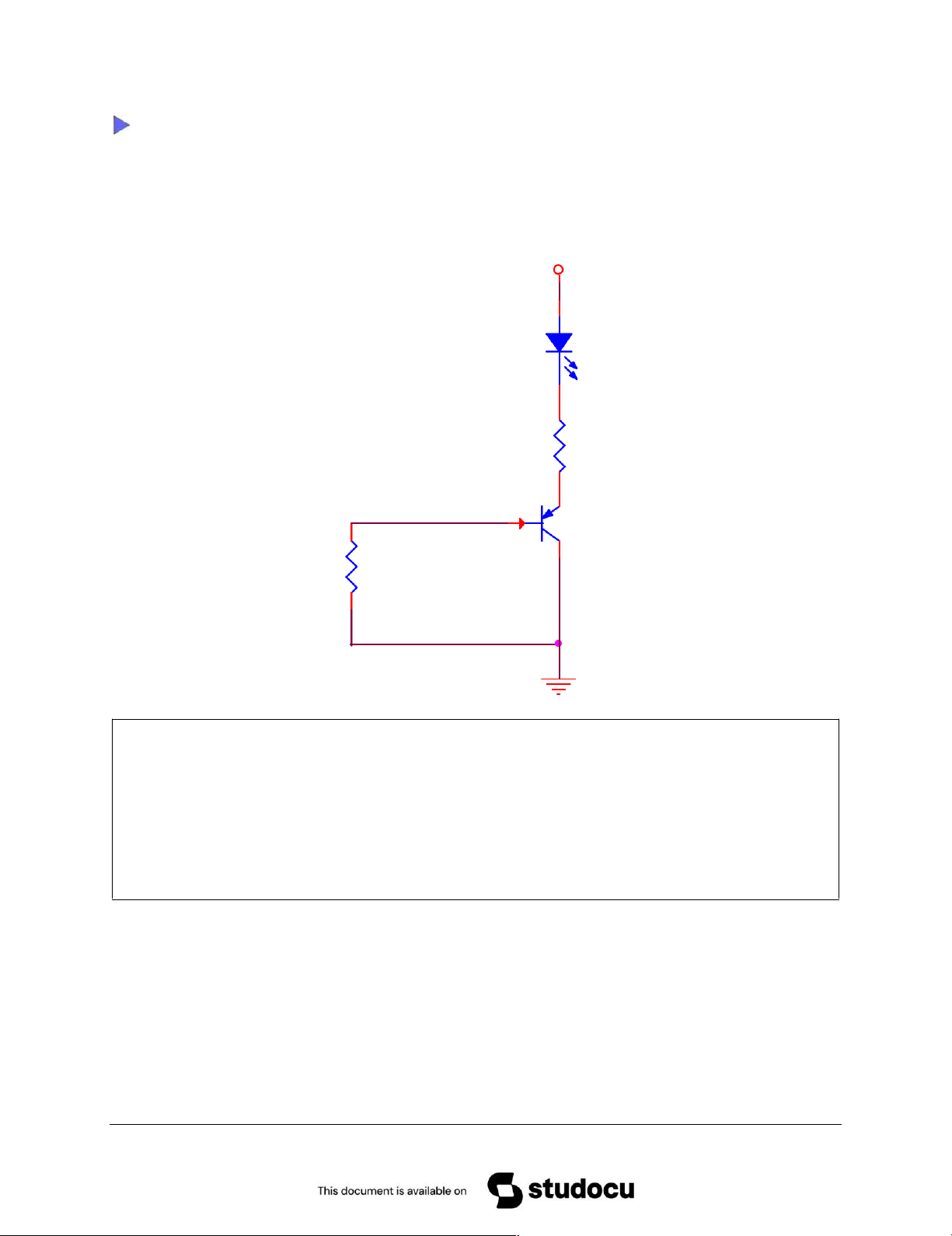

Nếu thay vì đặt tải (điện trở + led) ở cực C, ta đặt ờ cực E như hình

sau. Khi đó BJT có bão hòa được không? Vì sao? (Câu hỏi này trả lời

khi nộp báo cáo, không cần trả lời lúc tiến hành thí nghiệm). VCC D1 LED R1 220 Q1 R2 10K

Phần trả lời: BJT không thể bão hòa được.

Vì khi transistor P-N-P hoạt động ở vùng bão hòa thì hai thành phần E-

B và C-B đều hoạt động ở miền phân cực thuận, nghĩa là VE VB và VC

VB , từ đó suy ra VEC < VEB. Mà ta lại có VEC VEB VE 0 (VE VB ) VB 0

Lab Material for “Semiconductor device

experiment lab” Nhóm 09 – L07

Downloaded by Pham Huyen (21073258@vnu.edu.vn) lOMoARcPSD|46958826 10 THÍ NGHIỆM 4 Mục tiêu

Khảo sát đặc tuyến vào của BJT npn. Chuẩn bị

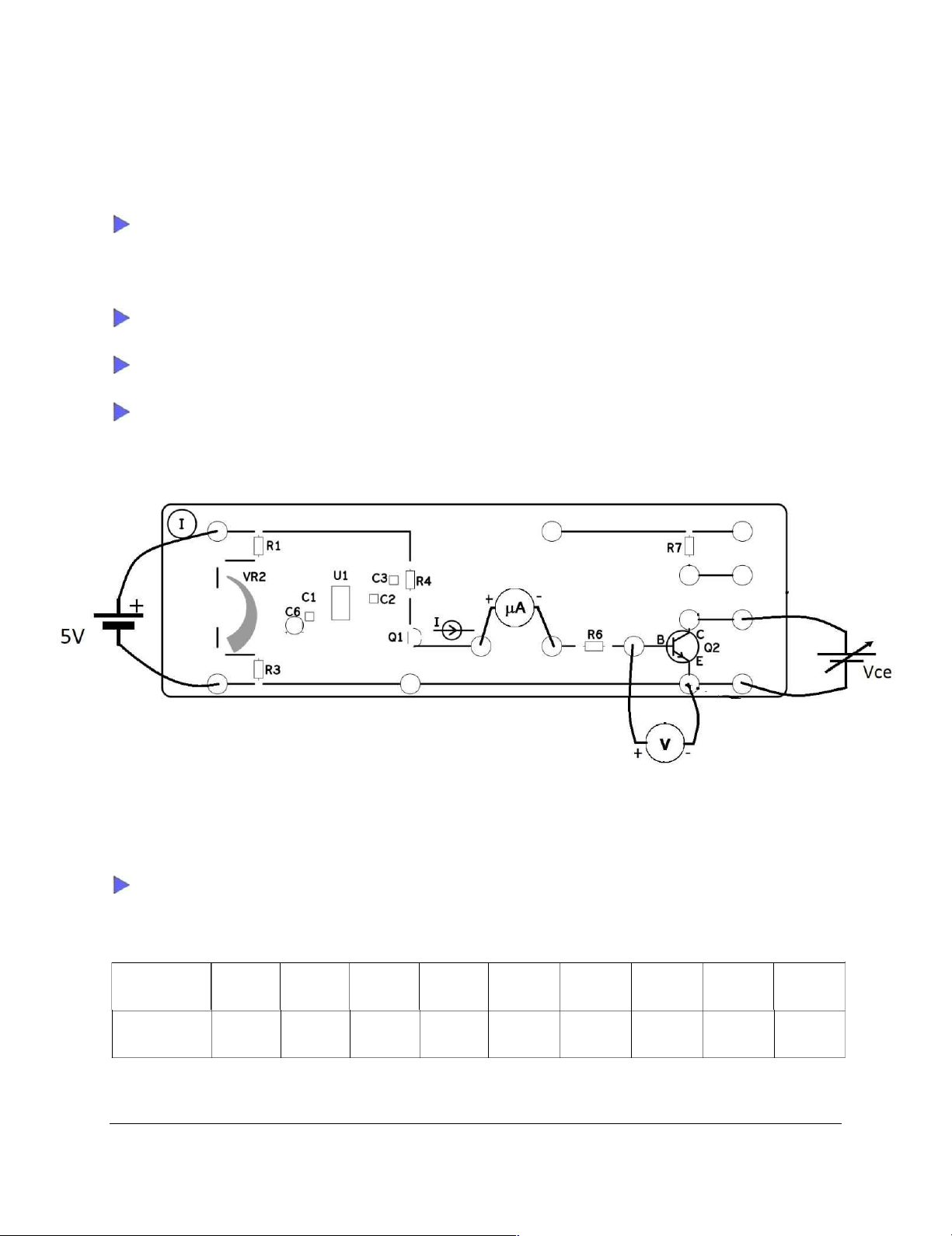

Chỉnh nguồn biến đổi 0-5V về nhỏ nhất (0V).

Chỉnh biến trở VR2 về vị trí nhỏ nhất.

Kết nối nguồn điện 5V vào mạch cấp nguồn dòng, nguồn điện thay

đổi 0-5V vào hai cực C-E của Q2. Các VOM kết nối như hình vẽ.

Hình 5: Kết nối mạch đo đặc tuyến vào của BJT Tiến hành

Bật nguồn. Chỉnh điện áp VCE cố định là 2V, chỉnh biến trở R2 để thay đổi dòng

IB và ghi vào bảng sau. Trong quá trình thí nghiệm lưu ý giữ VCE cố định là 2V. IB

10uA 15uA 20uA 25uA 30uA 35uA 40uA 45uA 50uA

VBE (V) 0,507 0,558 0,591 0,608 0,625 0,640 0,653 0,669 0,673

Lab Material for “Semiconductor device

experiment lab” Nhóm 09 – L07

Downloaded by Pham Huyen (21073258@vnu.edu.vn) lOMoARcPSD|46958826 11

Chỉnh điện áp VCE cố định là 4V, chỉnh biến trở R2 để thay đổi dòng IB

và ghi vào bảng sau. Trong quá trình thí nghiệm lưu ý giữ VCE cố định là 4V. IB

10uA 15uA 20uA 25uA 30uA 35uA 40uA 45uA 50uA VBE (V)

0,448 0,540 0,556 0,577 0,595 0,608 0,620 0,634 0,645

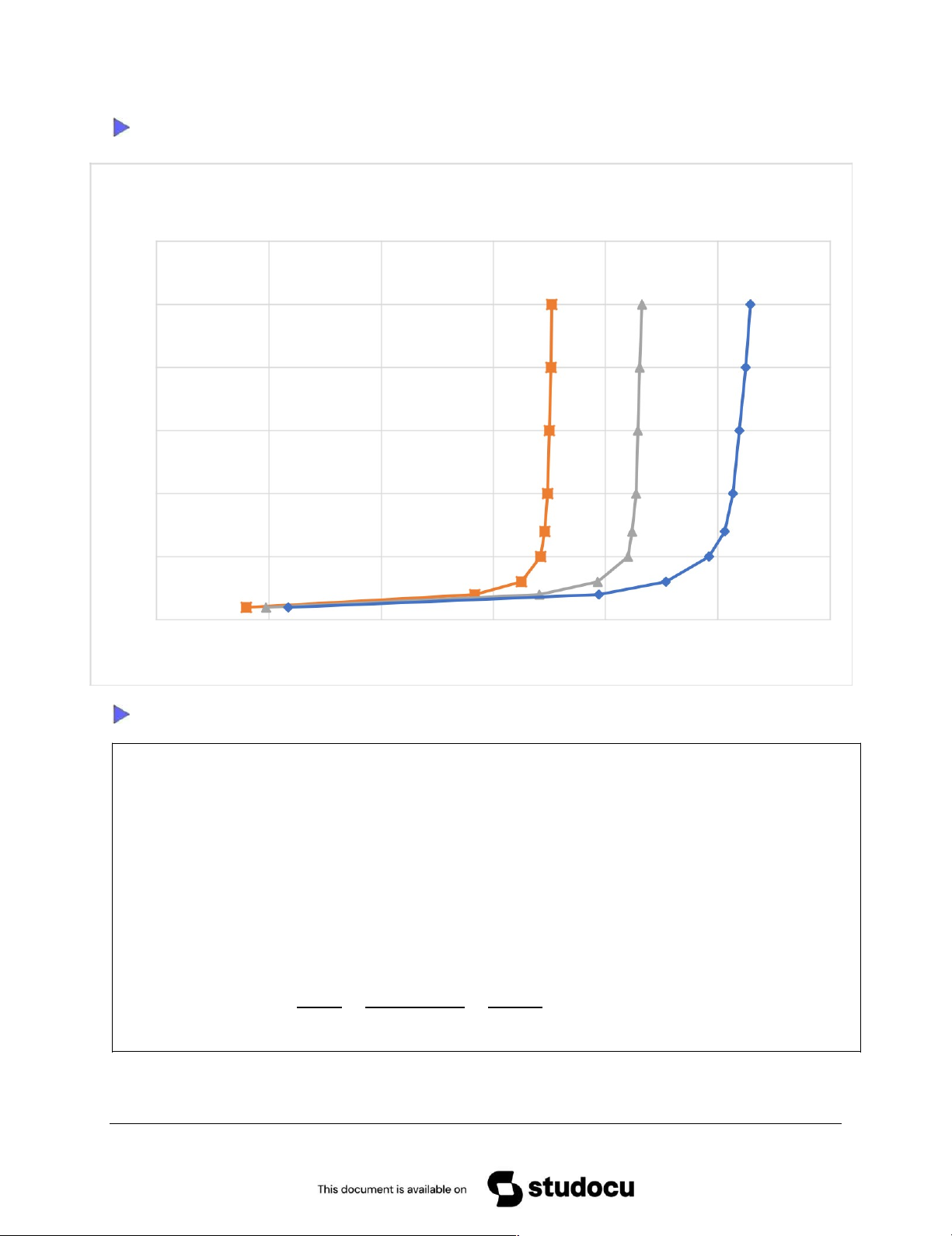

Vẽ đặc tuyến vào IB - VBE ứng với hai trường hợp VCE = 2V và VCE = 4V. Đặc tuyến IB - VBE 60 50 50 45 40 40 35 IB 30 30 25 20 20 15 10 10 0 0 0,1 0,2 0,3 0,4 0,5 0,6 0,7 0,8 VBE khi:

Nút hình vuông: VCE = 4

Nút hình thoi: VCE = 2

Nhận xét đặc tuyến đã vẽ. Nhận xét:

Đặc tuyến giống với dạng của Diode.

Đặc tuyến ứng với VCE = 4V dịch về bên trái hơn đặc tuyến ứng với VCE = 2V

chứng tỏ khi ở cùng VBE thì mức VCE = 4V cho giá trị IB cao hơn VCE = 2V.

Lab Material for “Semiconductor device

experiment lab” Nhóm 09 – L07

Downloaded by Pham Huyen (21073258@vnu.edu.vn) lOMoARcPSD|46958826 12 THÍ NGHIỆM 5

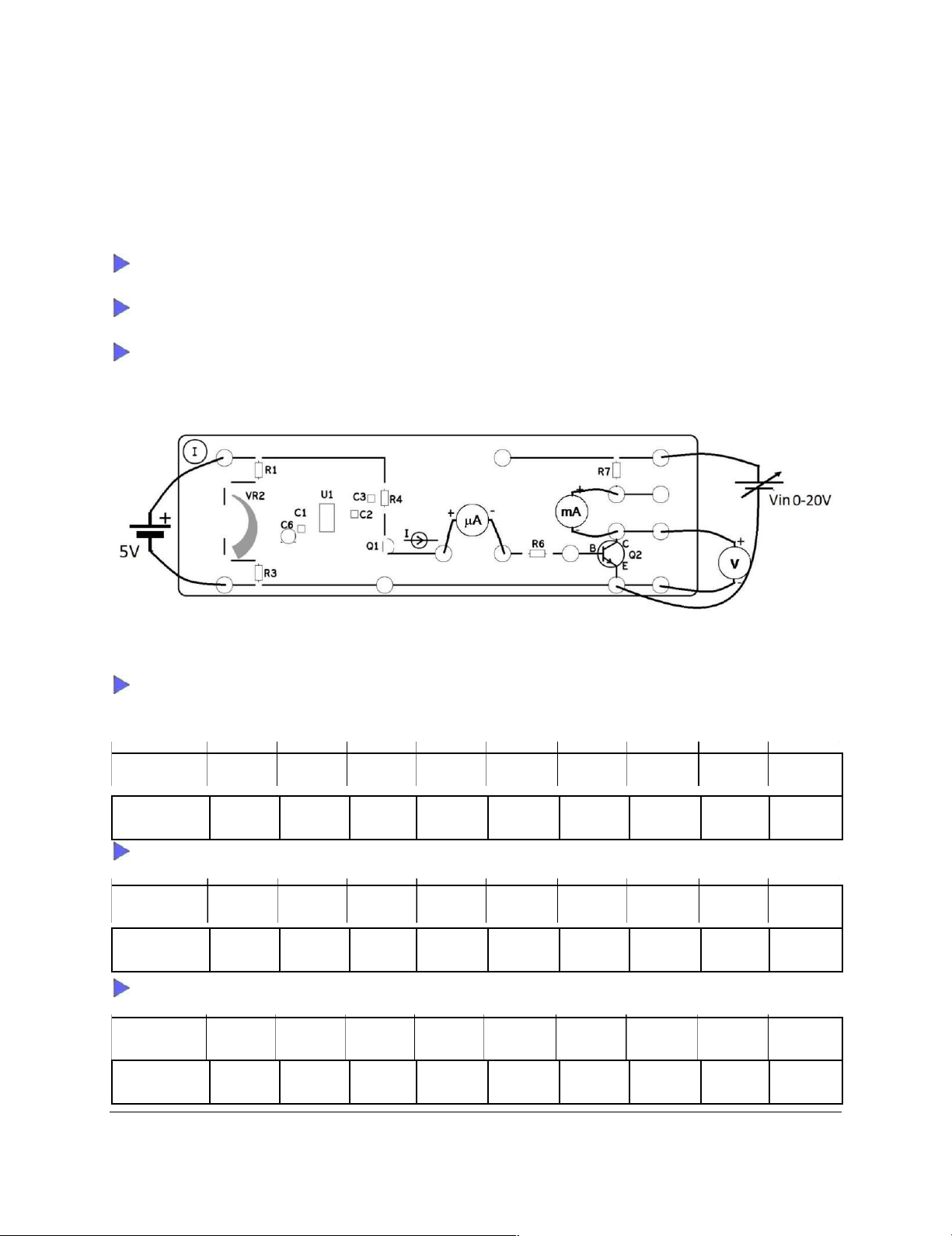

Mục tiêu: Khảo sát đặc tuyến ngõ ra của BJT npn. Chuẩn bị

Chỉnh nguồn biến đổi 0-20V về nhỏ nhất (0V).

Chỉnh biến trở VR2 về vị trí nhỏ nhất.

Kết nối nguồn điện 5V vào mạch cấp nguồn dòng, nguồn điện thay

đổi 0-20V vào mạch. Các VOM kết nối như hình vẽ. Tiến hành

Bật nguồn. Chỉnh dòng điện IB cố định là 20uA, thay đổi Vin để có được

các giá trị VCE theo bảng sau. Điền các giá trị tương ứng của dòng IC. VCE 0.1V 0.2V 0.3V 0.5V 0.7V 1V 1.5V 2V 2.5V Ic (mA) 1,60 5,67 6,50 6,84 6,92 6,97 7,00 7,03 7,04

Lặp lại thí nghiệm với IB = 25uA. VCE 0.1V 0.2V 0.3V 0.5V 0.7V 1V 1.5V 2V 2.5V Ic (mA) 1,95 6,82 7,86 8,40 8,47 8,54 8,57 8,61 8,65

Lặp lại thí nghiệm với IB = 30uA VCE 0.1V 0.2V 0.3V 0.5V 0.7V 1V 1.5V 2V 2.5V Ic (mA) 2,35 7,88 9,08 9,84

10,12 10,27 10,38 10,50 10,58

Lab Material for “Semiconductor device

experiment lab” Nhóm 09 – L07

Downloaded by Pham Huyen (21073258@vnu.edu.vn) lOMoARcPSD|46958826 13

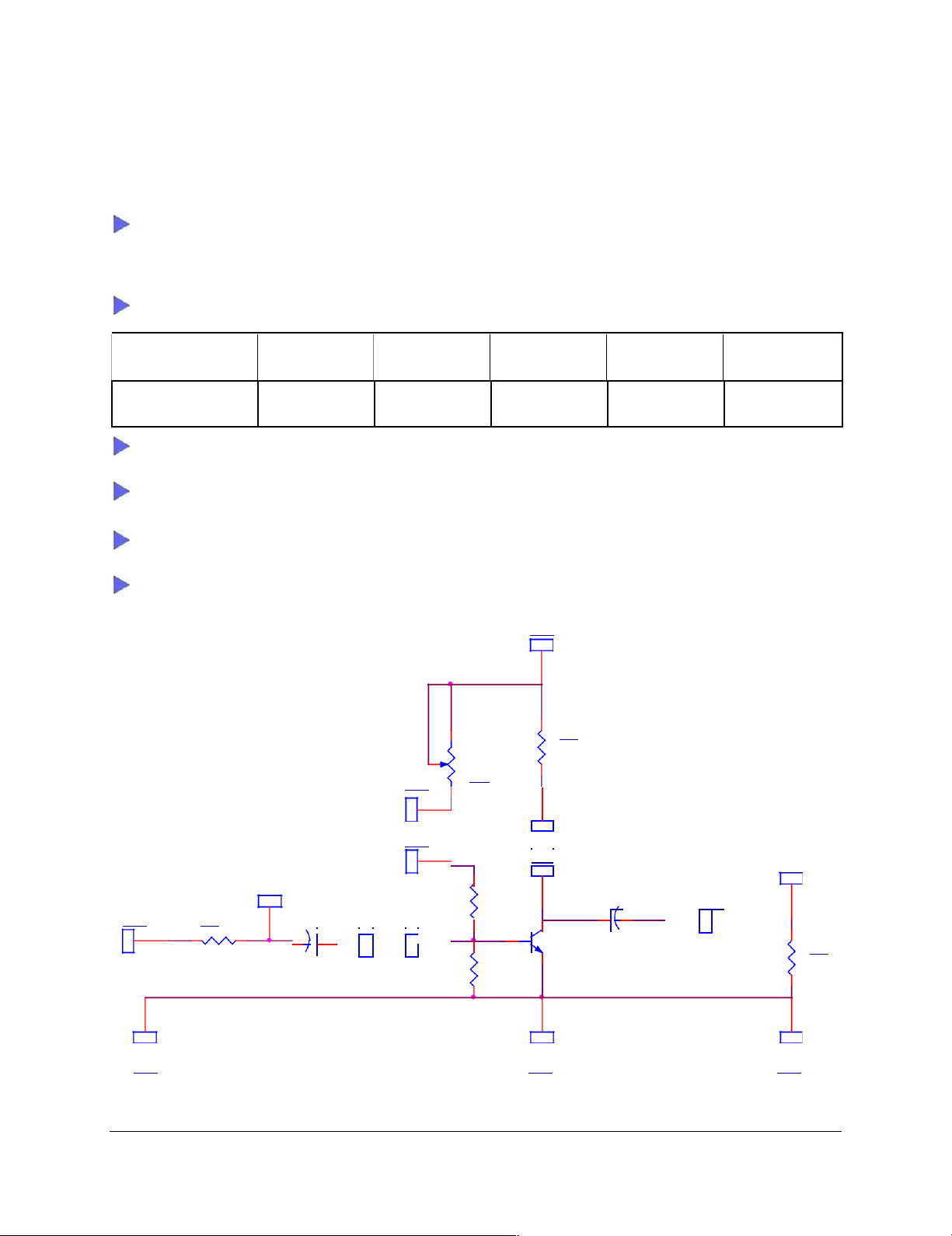

Vẽ đặc tuyến ngõ ra IC -VCE ứng với 3 trường hợp trên. ĐẶC TUYẾN IC - VCE 3 2,5 2 C E V 1,5 1 0,5 Ic khi:

Nút hình vuông: Ib = 30 uA

Nút hình tam giác: Ib =25 uA 0

Nút hình thoi: Ib = 20 uA 0 2 4 6 8 10 12

Nhận xét tương quan giữa 3 đặc tuyến. Ước tính điện áp Early. Nhận xét:

+ Khi VCE thấp (Khoảng < 0,2V) thì đặc tuyến gần như nằm ngang (Ic tăng rất nhanh).

+ Khi VCE cao (Khoảng > 0,2V) thì đặc tuyến rất dốc, IC tăng chậm dần và bão hòa.

Lấy số liệu từ bảng I = 20 A, lấy 2 điểm (VCE; IC) lần lượt là (0,7; 6,92) và (1; 6,97), μ

ta có độ dốc của đặcBtuyến và từ đó tìm ra điện áp Early (VA): dIC 6,97 6,92 6,97 V 40V A dVCE 1 0,7 VA 1

Lab Material for “Semiconductor device

experiment lab” Nhóm 09 – L07

Downloaded by Pham Huyen (21073258@vnu.edu.vn) lOMoARcPSD|46958826 14 THÍ NGHIỆM 6 Mục tiêu

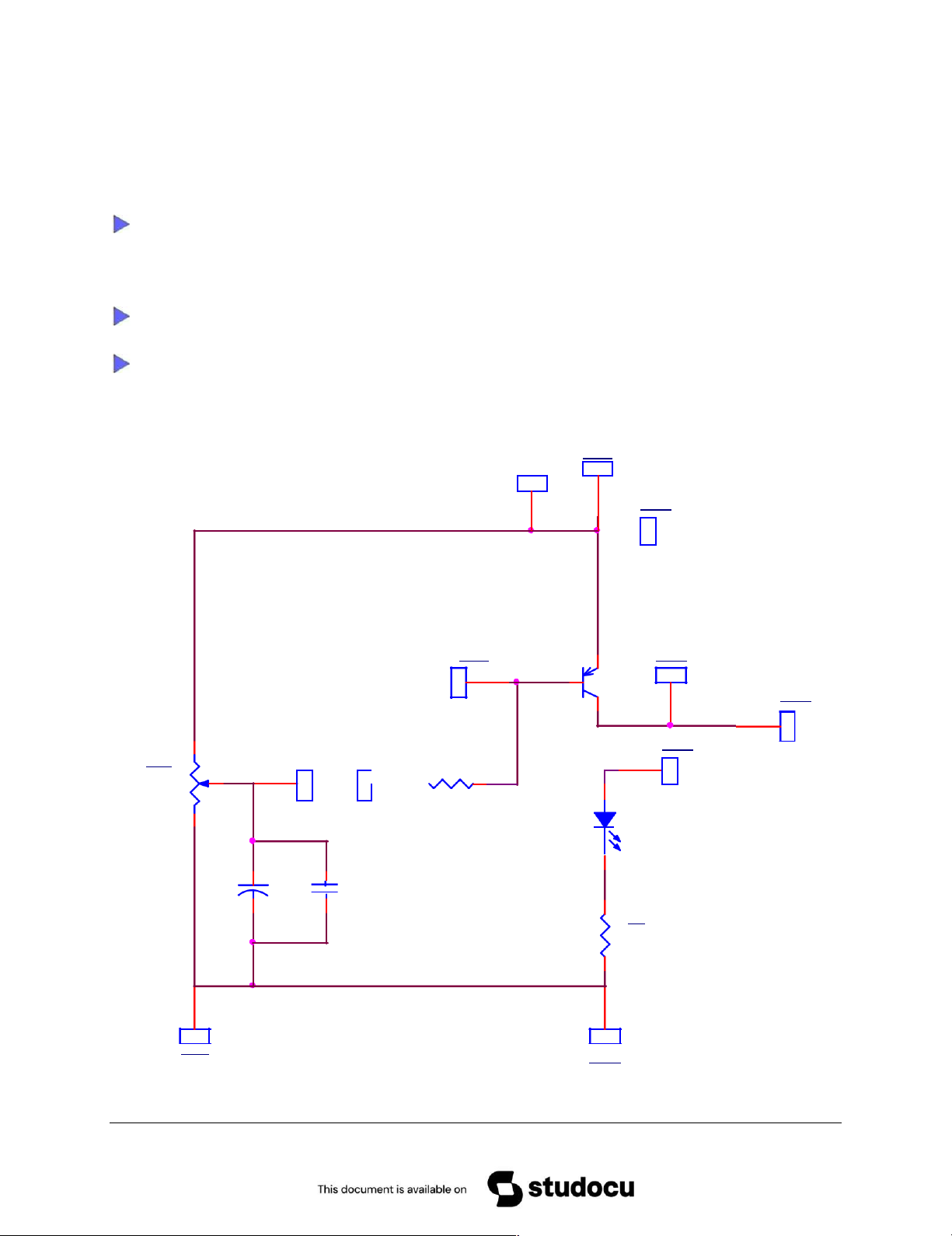

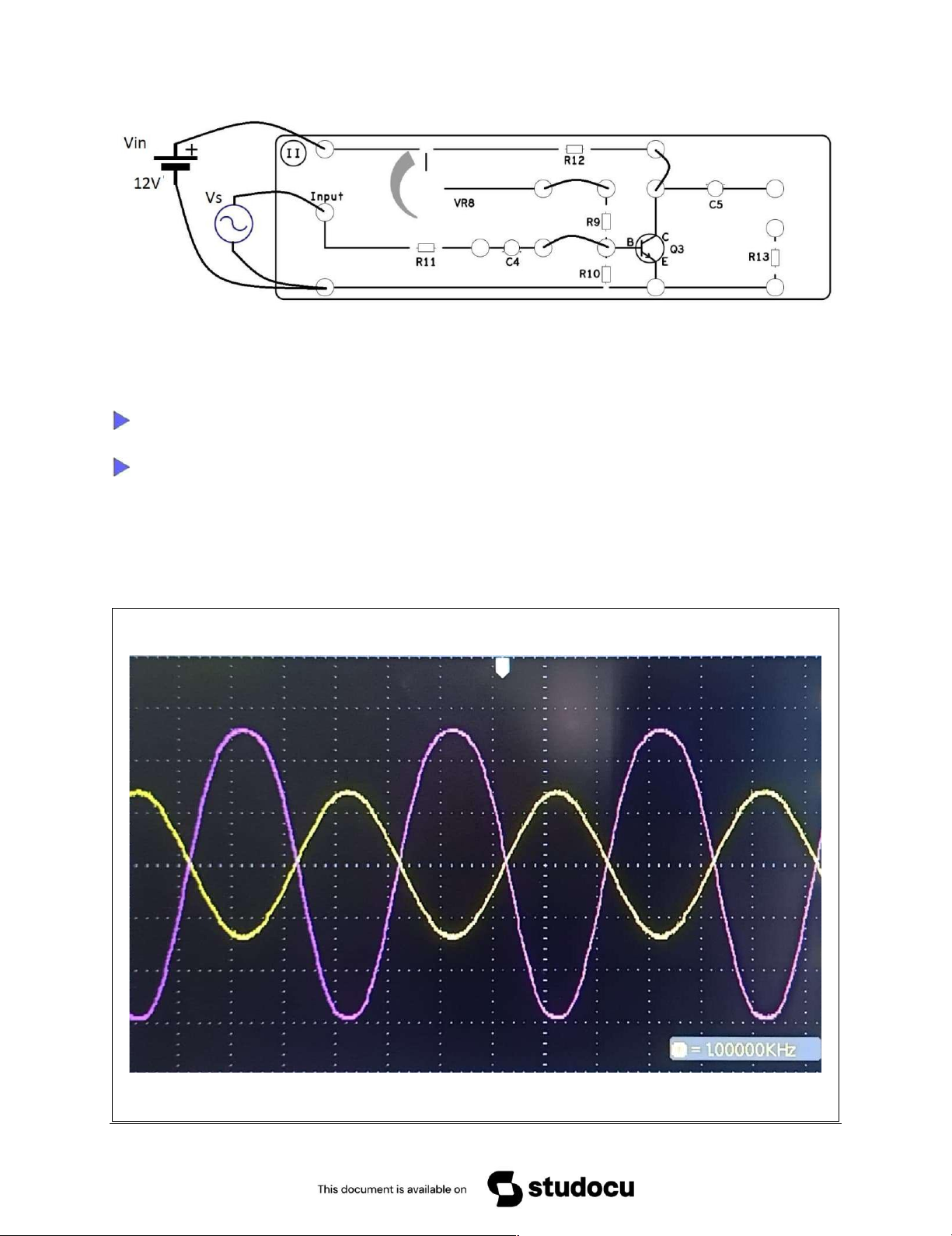

Khảo sát mạch khuếch đại ghép E chung. Chuẩn bị

Đọc và dùng VOM xác định lại giá trị các điện trở Điện trở R9 R10 R11 R12 R13 Giá trị (kΩ) 96,1 9,86 9,92 0,981 9,85

Kết nối mạch như Hình 7. Nguồn cấp Vin là 12V

Chỉnh nguồn tín hiệu Vs có biên độ 1V, tần số 1Khz. Rồi giảm biên độ Vs về 0V.

Dùng 1 VOM đo điện áp giữa cực C và E của Q3.

Dùng kênh 1 dao động ký đo dạng sóng Vs, kênh 2 dạng sóng tại cực C của Q3. TP16 1 R12 1K 47K VR8 TP17 1 1 TP18 TP23 1 TP24 TP26 TP21 1 R9 120K C5 TP25 1 1 TP22 R11 1 C4 TP20 TP19 1 1 1 Q3 C1815 10uF R13 R10 10K 10uF 10K 10K 1 1 1 TP27 TP28 TP29

Hình 6: Sơ đồ mạch khuếch đại E chung

Lab Material for “Semiconductor device

experiment lab” Nhóm 09 – L07

Downloaded by Pham Huyen (21073258@vnu.edu.vn) lOMoARcPSD|46958826 15

Hình 7: Sơ đồ kết nối mạch khuếch đại E chung Tiến hành

Bật nguồn. Chỉnh biến trở VR8 để VCE = 6V.

Tăng dần biên độ Vs. Xác định biên độ tối đa của Vs để ngõ ra

không bị méo dạng (max swing). Nếu dạng sóng ngõ ra bị méo dạng

ở 1 đầu hình sine, chỉnh biến trở R8 để thay đổi phân cực sao cho đạt

max swing. Vẽ dạng sóng vs và vce trên cùng hệ tọa độ.

+ Vs trước khi bị biến dạng (chưa đạt max swing): (Vs = 0,568V)

Lab Material for “Semiconductor device

experiment lab” Nhóm 09 – L07

Downloaded by Pham Huyen (21073258@vnu.edu.vn) lOMoARcPSD|46958826 16

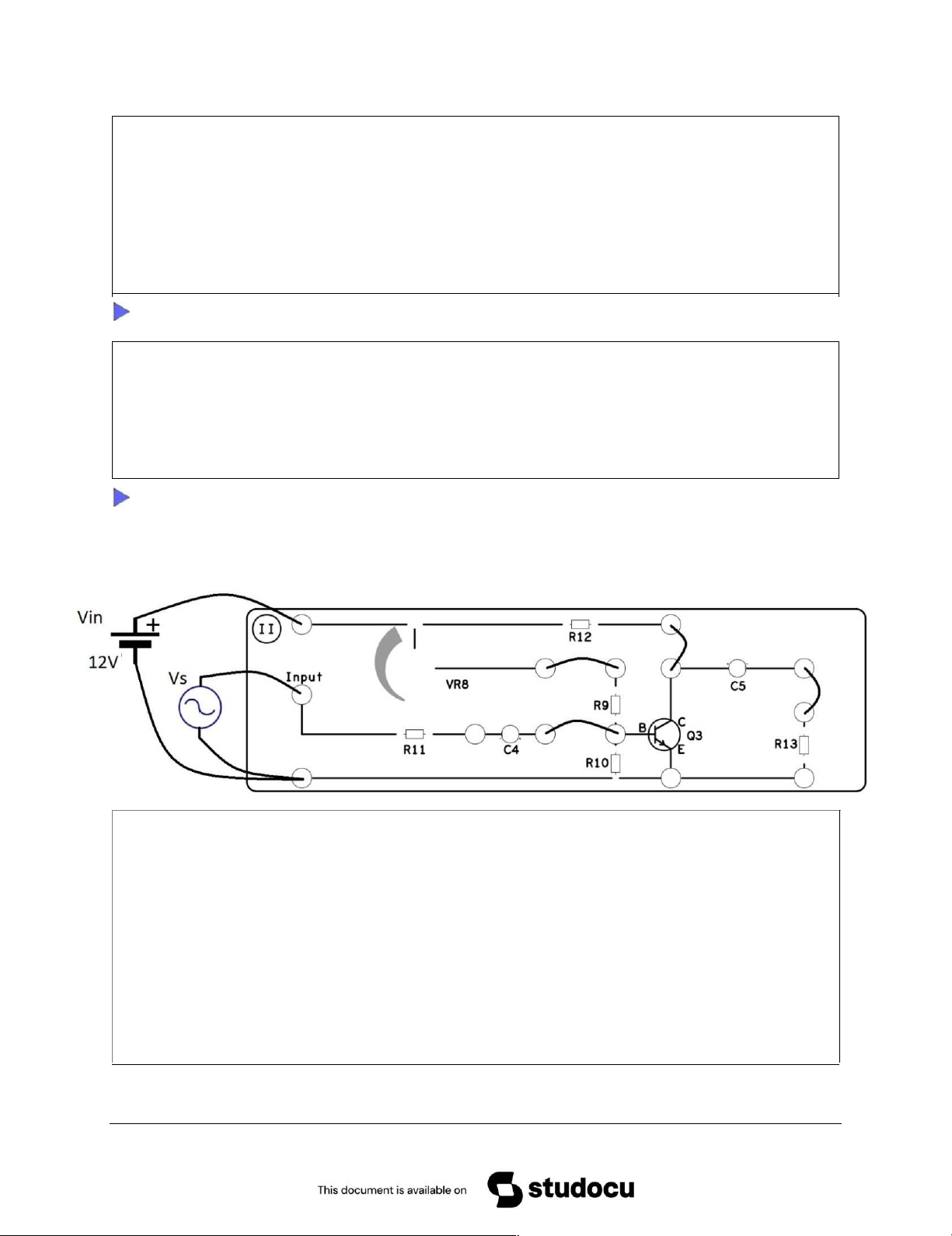

+ Vs sau khi bị biến dạng (đã đạt max swing):

+ Biên độ tối đa để Vs không bị biến dạng là khoảng 0,568 V (trong

hình trên là đã ở khoảng 0,63 V), đồng thời thì Vce khoảng 11,04 V.

Xác định độ lợi của mạch khuếch đại ở max-swing. Kiểm chứng lại so với lý thuyết. V Độ lợi: ce 11,04 19,44 V 0,568 s R in Theo lý thuyết: g m R12 / /r0 R R in 11 I 26mV C

Với: Rin rpi / / R10 ; rpi ; g m ; R12 / /r0 R12 I C 26mV Do không đo được nên ta không

thể tính chính xác độ lợi theo lý thuyết.

Vì vậy, ta chỉ dự đoán xem kết quả đo

theo thực nghiệm có hợp lý hay không.

Lab Material for “Semiconductor device

experiment lab” Nhóm 09 – L07

Downloaded by Pham Huyen (21073258@vnu.edu.vn) lOMoARcPSD|46958826 17

+ Đầu tiên, theo lý thuyết thì có giá trị âm, phù hợp với kết quả đo

được phù hợp khi Vin và Vout ngược pha.

+ Tiếp theo, vế g m R12 / /r0 thường có giá trị khoảng 100 300 . Mà Rin <

R11 nên giá trị 19,44 là có cơ sở. Lúc này, Rin nhỏ hơn R11 rất nhiều lần.

Tắt nguồn, đo giá trị VR8 tại max swing và kiểm chứng lại so với lý thuyết.

- Giá trị VR8 đo được tại max swing: VR 8 52 k , tăng so với ban đầu.

- Nguyên nhân: Khi BJT vào vùng bão hòa, sóng bị méo dạng, ta

điều chỉnh tăng VR8 để giảm IC làm tăng giới hạn bão hòa của BJT.

Kết nối tải R13 vào mạch. Chuyển kênh 2 của dao động ký sang đo

dạng sóng ngõ ra trên R3. Nhận xét.

- Sau khi kết nối tải R13 vào mạch, dạng sóng ngõ ra trên R3 không

đổi, tuy nhiên biên độ Vout giảm nhưng không nhiều.

- Nguyên nhân: Khi nối tải, theo lý thuyết thì độ lợi thay đổi theo công thức: R 13 10 ' 0 19,44 17,67 R 13 R12 11

Kết quả trên phù hợp theo lý thuyết.

Lab Material for “Semiconductor device

experiment lab” Nhóm 09 – L07

Downloaded by Pham Huyen (21073258@vnu.edu.vn) lOMoARcPSD|46958826 18

Chỉnh lại Vs sao cho đạt max swing trong trường hợp có tải R13.

Xác định độ lợi và Vs tại Max Swing. Kiểm chứng lại so với lý thuyết

Tại max swing: Vs = 0,624 V; Vout = 11,84 V. V 11,84 Độ lợi: out 19 Vs 0,624

Nhận xét: Như dự đoán, Vs tăng so với khi không có tải. Kết quả độ

lợi cũng khá gần với độ lợi theo lý thuyết đã tính ở trên.

Giải thích: Khi có tải, độ lợi giảm làm tăng giới hạn của Vs.

Lab Material for “Semiconductor device

experiment lab” Nhóm 09 – L07

Downloaded by Pham Huyen (21073258@vnu.edu.vn)