Preview text:

Bài tập lớn Kiến trúc máy tính MỤC LỤC

DANH MỤC CÁC HÌNH VẼ..................................................................................II

DANH MỤC CÁC BẢNG BIỂU.............................................................................II

MỞ ĐẦU...................................................................................................................1

CHƯƠNG 1 TỔNG QUAN KIẾN TRÚC MÁY TÍNH............................................2

1.1 Chức năng.......................................................................................................2

1.2 Cấu trúc........................................................................................................... 3

CHƯƠNG 2 RAM.....................................................................................................8

2.1 Hoạt động của bộ nhớ.....................................................................................8

2.2 RAM.............................................................................................................10

2.2.1 Cấu trúc DRAM và SRAM....................................................................10

2.3 Tổ chức của bộ nhớ.......................................................................................15

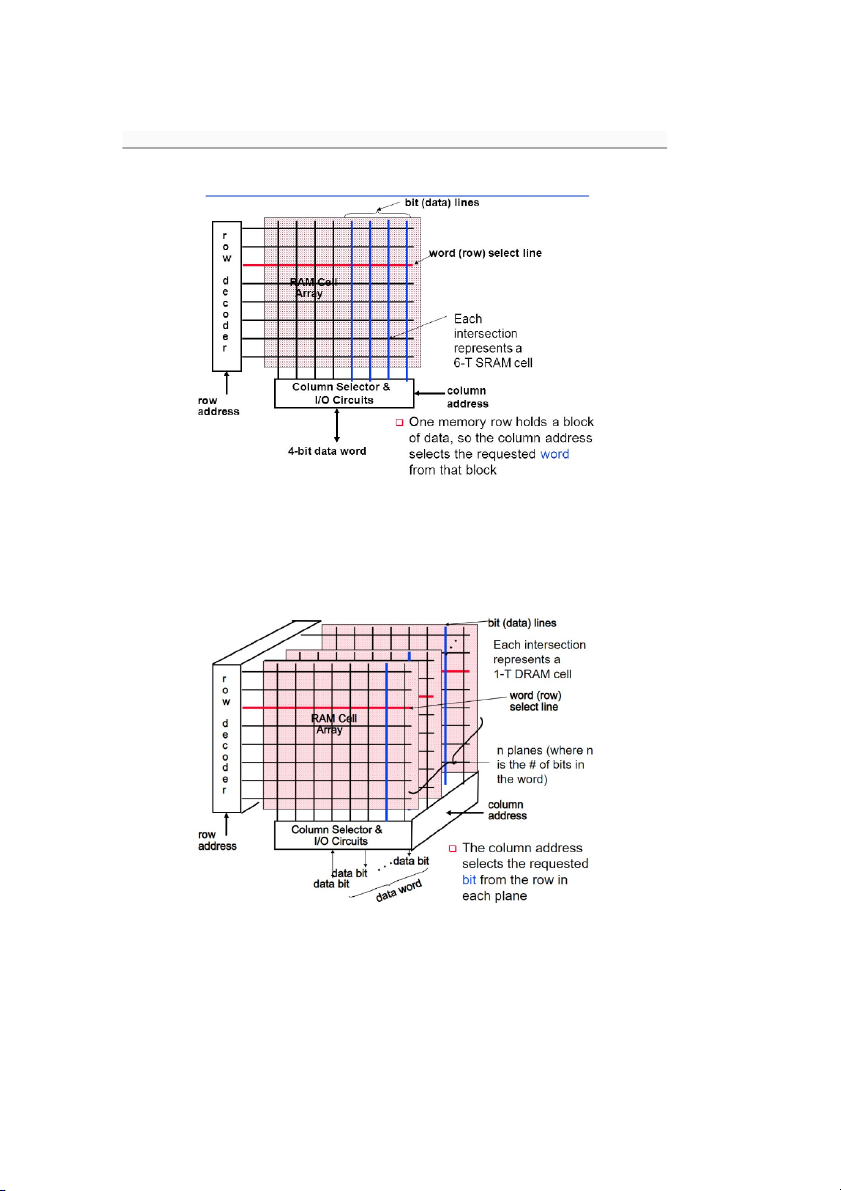

Tổ chức bộ nhớ SRAM...................................................................................16

Tổ chức bộ nhớ DRAM..................................................................................16

Tổ chức DRAM nâng cao...............................................................................17

SDRAM..........................................................................................................17

DDR SDRAM.................................................................................................19

TÀI LIỆU THAM KHẢO.......................................................................................22 Nguyễn Thái Châu I Lớp DCCTCLC66A1 (2121050525)

Bài tập lớn Kiến trúc máy tính

DANH MỤC CÁC HÌNH VẼ

Hình 1-1 Máy tính: Cấu trúc cấp cao nhất.................................................................3

Hình 1-2 Các yếu tố chính của một máy tính đa lõi...................................................5

Hình 1-3 Bộ xử lý zEnterprise EC12 (PU) Sơ đồ chip..............................................6

Hình 1-4 zEnterprise EC12 Bố cục cốt lõi.................................................................6

Hình 2-1 Hoạt động của ô nhớ..................................................................................8

Hình 2-2 Phần tử nhớ DRAM 1 bit..........................................................................11

Hình 2-3 Phần tử nhớ DRAM 1 bit.........................................................................13

Hình 2-4 Đặc tính và giá thành của SRAM và DRAM............................................14

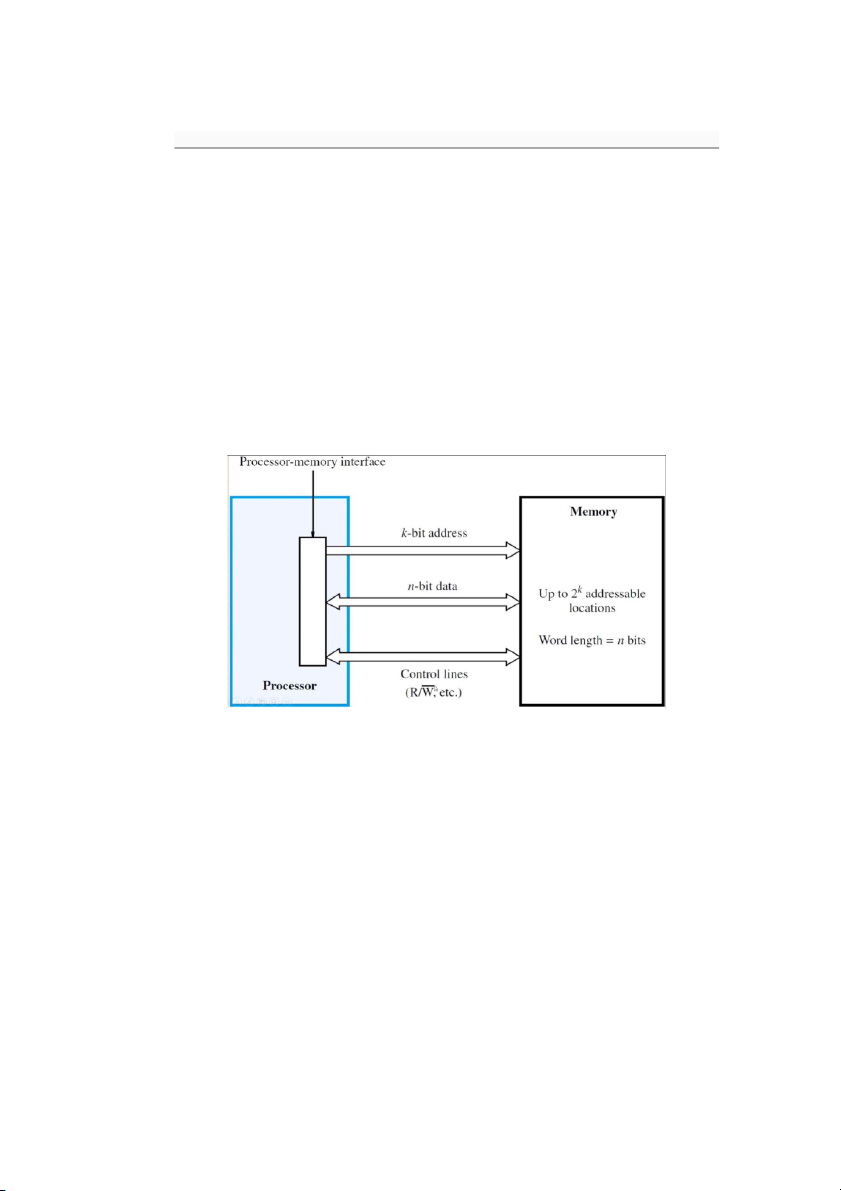

Hình 2-5 Giao tiếp giữa bộ xử lý và bộ nhớ............................................................15

Hình 2-6 Tổ chức bộ nhớ SRAM............................................................................16

Hình 2-7 Tổ chức bộ nhớ DRAM............................................................................16

Hình 2-8 RAM động đồng bộ 256Mb.....................................................................17

Hình 2-9 Thời gian đọc SDRAM (Độ dài liên tục = 4, độ trễ = 2)..........................19

Hình 2-10 các thế hệ DDR......................................................................................20

DANH MỤC CÁC BẢNG BIỂU

Bảng 2-1 Các loại bộ nhớ bán dẫn.............................................................................9

Bảng 2-2 Giải thích thuật ngữ RAM động đồng bộ (Hình 2-8)...............................18

Bảng 2-3 Đặc điểm DDR.........................................................................................20 Nguyễn Thái Châu II Lớp DCCTCLC66A1 (2121050525)

Bài tập lớn Kiến trúc máy tính Nguyễn Thái Châu III Lớp DCCTCLC66A1 (2121050525)

Bài tập lớn Kiến trúc máy tính MỞ ĐẦU

Kiến trúc máy tính đề cập đến những thuộc tính của một hệ thống mà một lập

trình viên có thể nhìn thấy được hay nói cách khác là những thuộc tính có tác động

trực tiếp đến việc thực thi logic của một chương trình. Một thuật ngữ thường được

sử dụng thay thế cho kiến trúc máy tính là kiến trúc tập lệnh (ISA). ISA xác định

các định dạng hướng dẫn, mã lệnh, thanh ghi, lệnh và bộ nhớ dữ liệu; ảnh hưởng

của các lệnh được thực thi trên thanh ghi và bộ nhớ; và một thuật toán để kiểm soát

việc thực thi lệnh. Tổ chức máy tính đề cập đến các đơn vị hoạt động và các kết nối

của chúng để thực hiện các đặc điểm kiến trúc. Ví dụ về các thuộc tính kiến trúc bao

gồm tập lệnh, số lượng bit được sử dụng để biểu diễn các kiểu dữ liệu khác nhau (ví

dụ: số, ký tự), cơ chế I / O và kỹ thuật định địa chỉ bộ nhớ. Các thuộc tính của tổ

chức bao gồm các chi tiết phần cứng trong suốt đối với người lập trình, chẳng hạn

như các tín hiệu điều khiển; giao diện giữa máy tính và thiết bị ngoại vi; và công

nghệ bộ nhớ được sử dụng.

Trong lịch sử, và cho đến ngày nay, sự khác biệt giữa kiến trúc và tổ chức là

một điều quan trọng. Nhiều nhà sản xuất máy tính cung cấp một nhóm mô hình máy

tính, tất cả đều có cùng kiến trúc nhưng có sự khác biệt về tổ chức. Do đó, các mô

hình khác nhau trong gia đình có giá cả và đặc điểm hiệu suất khác nhau. Hơn nữa,

một kiến trúc cụ thể có thể kéo dài nhiều năm và bao gồm một số mô hình máy tính

khác nhau, tổ chức của nó thay đổi theo công nghệ thay đổi. Một ví dụ nổi bật của

cả hai hiện tượng này là kiến trúc Hệ thống IBM / 370. Kiến trúc này được giới

thiệu lần đầu tiên vào năm 1970 và bao gồm một số mô hình. Khách hàng có yêu

cầu khiêm tốn có thể mua một mô hình rẻ hơn, chậm hơn và, nếu nhu cầu tăng lên,

sau đó nâng cấp lên một mô hình đắt hơn, nhanh hơn mà không cần phải từ bỏ phần

mềm đã được phát triển. Trong những năm qua, IBM đã giới thiệu nhiều mô hình

mới với công nghệ cải tiến để thay thế các mô hình cũ hơn, mang đến cho khách

hàng tốc độ cao hơn, chi phí thấp hơn hoặc cả hai. Các mô hình mới hơn này vẫn

giữ nguyên kiến trúc để khoản đầu tư vào phần mềm của khách hàng được bảo vệ.

Đáng chú ý, kiến trúc System / 370, với một vài cải tiến, đã tồn tại cho đến ngày

nay như là kiến trúc của dòng sản phẩm máy tính lớn của IBM.

Bài tập lớn Kiến trúc máy tính

CHƯƠNG 1 TỔNG QUAN KIẾN TRÚC MÁY TÍNH

Máy tính là một hệ thống phức tạp; máy tính đương đại chứa hàng triệu linh

kiện điện tử cơ bản. Điều quan trọng là nhận ra bản chất phân cấp của hầu hết các

hệ thống phức tạp, bao gồm cả máy tính [SIMO96]. Hệ thống phân cấp là một tập

hợp các hệ thống con có liên quan với nhau, mỗi hệ thống sau này lần lượt phân cấp

theo cấu trúc cho đến khi chúng ta đạt đến mức thấp nhất của hệ thống con cơ bản. [ CITATION NXB09 \l 1033 ]

Bản chất phân cấp của các hệ thống phức tạp là điều cần thiết cho cả thiết kế

và mô tả của chúng. Người thiết kế chỉ cần xử lý một mức cụ thể của hệ thống tại

một thời điểm. Ở mỗi cấp độ, hệ thống bao gồm một tập hợp các thành phần và mối

quan hệ giữa chúng với nhau. Hành vi ở mỗi cấp chỉ phụ thuộc vào đặc tính được

đơn giản hóa, trừu tượng hóa của hệ thống ở cấp thấp hơn tiếp theo. Ở mỗi cấp độ,

người thiết kế quan tâm đến cấu trúc và chức năng. 1.1 Chức năng

Về bản chất, cả cấu trúc và hoạt động của một máy tính đều đơn giản. Nói

chung, chỉ có bốn chức năng cơ bản mà máy tính có thể thực hiện:

Xử lý dữ liệu: Dữ liệu có thể có nhiều dạng khác nhau và phạm vi yêu cầu

xử lý cũng rộng. Tuy nhiên, chúng ta sẽ thấy rằng chỉ có một số phương pháp

hoặc kiểu xử lý dữ liệu cơ bản.

Lưu trữ dữ liệu: Ngay cả khi máy tính đang xử lý dữ liệu đang bay (tức là dữ

liệu đến và được xử lý, và kết quả sẽ xuất hiện ngay lập tức), máy tính phải

tạm thời lưu trữ ít nhất những dữ liệu đó. phần dữ liệu đang được xử lý tại

bất kỳ thời điểm nào. Như vậy, có ít nhất một chức năng lưu trữ dữ liệu ngắn

hạn. Một điều quan trọng không kém, máy tính thực hiện chức năng lưu trữ

dữ liệu lâu dài. Các tập tin dữ liệu được lưu trữ trên máy tính để phục vụ cho

việc truy xuất và cập nhật sau này.

Di chuyển dữ liệu: Môi trường hoạt động của máy tính bao gồm các thiết bị

đóng vai trò là nguồn hoặc đích của dữ liệu. Khi dữ liệu được nhận hoặc gửi

đến một thiết bị được kết nối trực tiếp với máy tính, quá trình này được gọi

là đầu vào - đầu ra (I / O) và thiết bị được coi là thiết bị ngoại vi. Khi dữ liệu

được di chuyển trong khoảng cách xa hơn, đến hoặc từ một thiết bị từ xa, quá

trình này được gọi là truyền thông dữ liệu.

Bài tập lớn Kiến trúc máy tính

Điều khiển: Trong máy tính, bộ điều khiển quản lý tài nguyên của máy tính

và điều phối hoạt động của các bộ phận chức năng của nó theo hướng dẫn. 1.2 Cấu trúc

MÁY TÍNH MỘT BỘ XỬ LÝ ĐƠN GIẢN

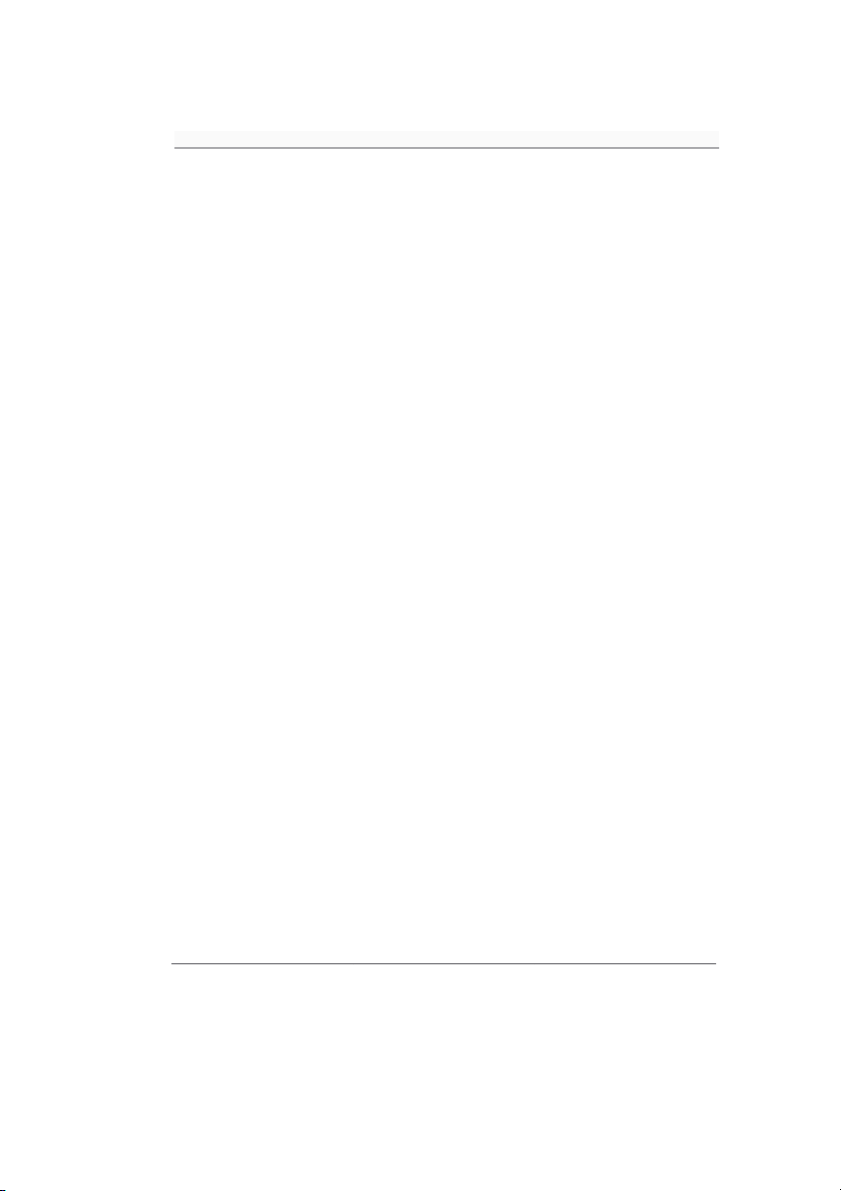

Hình 1-1 Máy tính: Cấu trúc cấp cao nhất

Hình 1-1 cung cấp một cái nhìn phân cấp về cấu trúc bên trong của một máy tính bộ

xử lý đơn truyền thống. Có bốn thành phần cấu trúc chính:

Khối xử lý trung tâm (CPU): Điều khiển hoạt động của máy tính và thực

hiện các chức năng xử lý dữ liệu của nó; thường được gọi đơn giản là bộ xử lý.

Bộ nhớ chính: Lưu trữ dữ liệu.

I/O: Di chuyển dữ liệu giữa máy tính và môi trường bên ngoài.

Bài tập lớn Kiến trúc máy tính

Kết nối hệ thống: Một số cơ chế cung cấp giao tiếp giữa CPU, bộ nhớ chính

và I / O. Một ví dụ phổ biến về kết nối hệ thống là bằng một bus hệ thống,

bao gồm một số dây dẫn mà tất cả các thành phần khác gắn vào.

Khối điều khiển: Điều khiển hoạt động của CPU và do đó là máy tính.

Đơn vị số học và logic (ALU): Thực hiện các chức năng xử lý dữ liệu của máy tính.

Thanh ghi: Cung cấp bộ nhớ trong cho CPU.

Kết nối CPU: Một số cơ chế cung cấp giao tiếp giữa đơn vị điều khiển, ALU và thanh ghi.

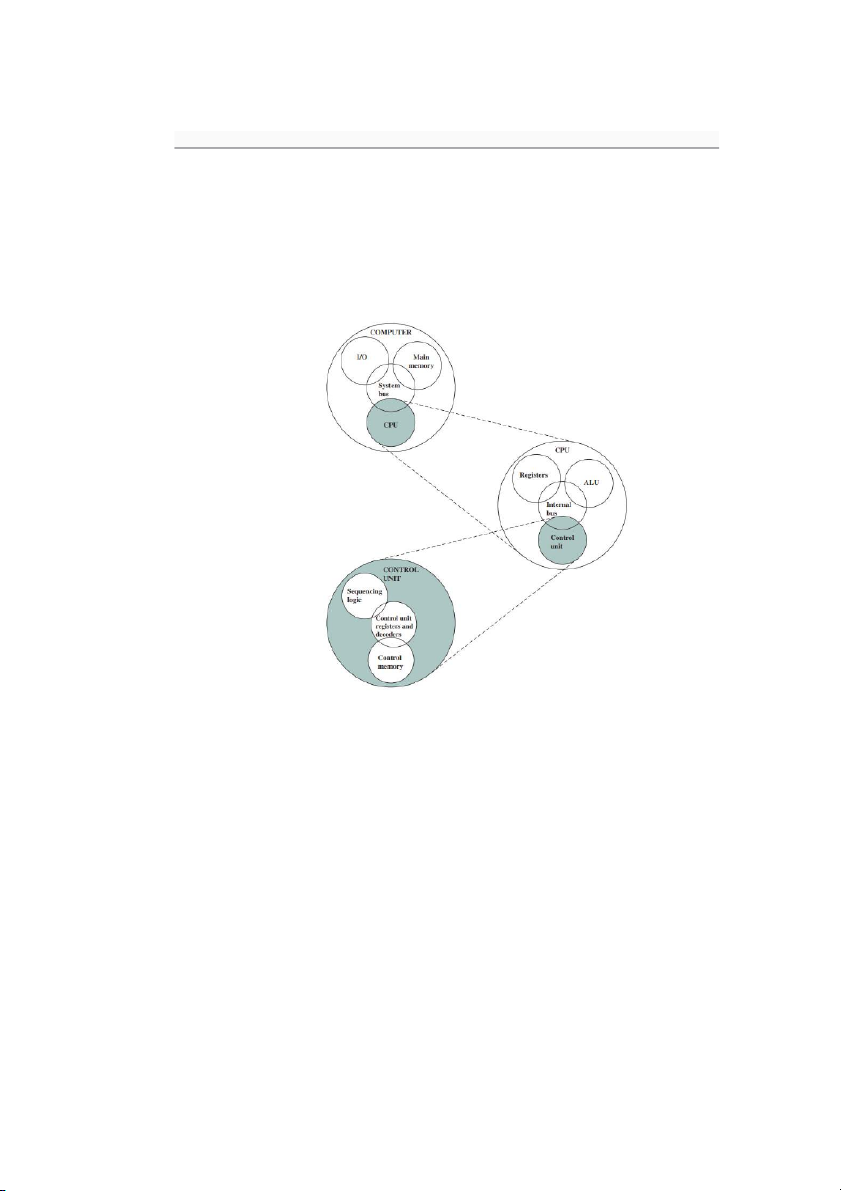

CẤU TRÚC MÁY TÍNH ĐA LÕI

Đơn vị xử lý trung tâm (CPU): Phần máy tính tìm nạp và thực thi các

lệnh. Nó bao gồm một ALU, một đơn vị điều khiển và các thanh ghi. Một

hệ thống với một đơn vị xử lý duy nhất thường được gọi đơn giản là một bộ xử lý.

Core: Một đơn vị xử lý riêng lẻ trên chip xử lý. Một lõi có thể có chức

năng tương đương với một CPU trên hệ thống một CPU. Các đơn vị xử lý

chuyên biệt khác, chẳng hạn như một đơn vị được tối ưu hóa cho các hoạt

động vectơ và ma trận, cũng được gọi là lõi.

Bộ xử lý: Một miếng silicon vật lý chứa một hoặc nhiều lõi. Bộ xử lý là

thành phần máy tính thông dịch và thực hiện các lệnh. Nếu một bộ xử lý

chứa nhiều lõi, nó được gọi là bộ xử lý đa lõi.

Bài tập lớn Kiến trúc máy tính

Hình 1-2 Các yếu tố chính của một máy tính đa lõi

Logic lệnh: Điều này bao gồm các nhiệm vụ liên quan đến việc tìm nạp các

lệnh và giải mã từng lệnh để xác định thao tác lệnh và vị trí bộ nhớ của bất kỳ toán hạng nào.

Đơn vị số học và logic (ALU): Thực hiện hoạt động được chỉ định bởi một lệnh.

Logic tải / lưu trữ: Quản lý việc truyền dữ liệu đến và đi từ bộ nhớ chính thông qua bộ nhớ đệm.

Bài tập lớn Kiến trúc máy tính

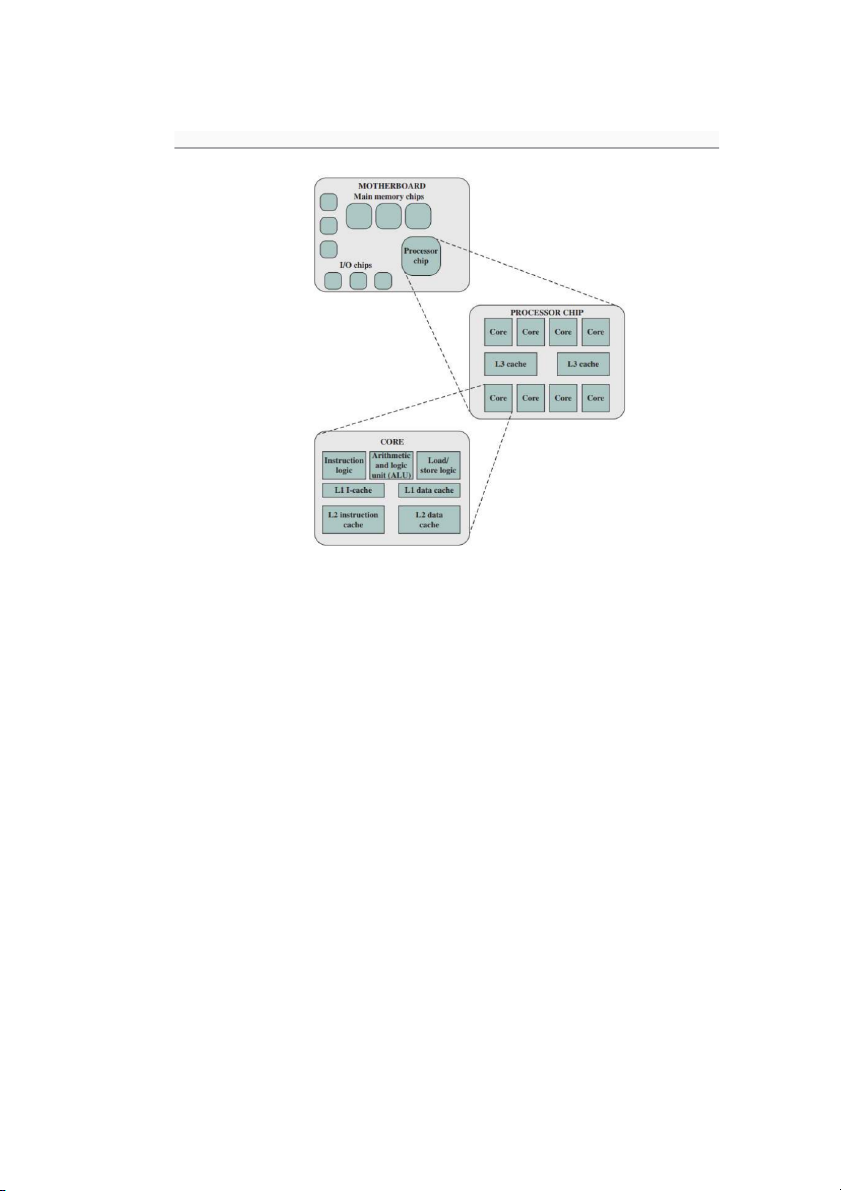

Hình 1-3 Bộ xử lý zEnterprise EC12 (PU) Sơ đồ chip

Hình 1-4 zEnterprise EC12 Bố cục cốt lõi

IDU (đơn vị giải mã lệnh): IDU được cấp từ bộ đệm IFU và chịu trách nhiệm

phân tích và giải mã tất cả các mã hoạt động z / Architecture.

LSU (bộ lưu trữ tải): LSU chứa bộ đệm dữ liệu 96-kB L1, 1 và quản lý lưu

lượng dữ liệu giữa bộ đệm dữ liệu L2 và các đơn vị thực thi chức năng. Nó

chịu trách nhiệm xử lý tất cả các kiểu truy cập toán hạng ở mọi độ dài, chế

độ và định dạng như được định nghĩa trong z / Architecture.

XU (đơn vị dịch): Đơn vị này dịch các địa chỉ logic từ các lệnh thành địa chỉ

vật lý trong bộ nhớ chính. XU cũng chứa một bộ đệm nhìn sang một bên bản

Bài tập lớn Kiến trúc máy tính

dịch (TLB) được sử dụng để tăng tốc độ truy cập bộ nhớ. TLB được thảo luận trong Chương 8.

FXU (đơn vị điểm cố định): FXU thực hiện các phép toán số học điểm cố định.

BFU (đơn vị dấu phẩy động nhị phân): BFU xử lý tất cả các phép toán dấu

phẩy động nhị phân và thập lục phân, cũng như các phép toán nhân điểm cố định.

DFU (đơn vị dấu phẩy động thập phân): DFU xử lý cả hoạt động dấu phẩy

động và dấu phẩy cố định trên các số được lưu trữ dưới dạng chữ số thập phân.

RU (bộ khôi phục): RU giữ một bản sao của trạng thái hoàn chỉnh của hệ

thống bao gồm tất cả các thanh ghi, thu thập các tín hiệu lỗi phần cứng và

quản lý các hành động khôi phục phần cứng.

COP (bộ đồng xử lý chuyên dụng): COP chịu trách nhiệm nén và mã hóa dữ liệu cho mỗi lõi.

I-cache: Đây là bộ đệm lệnh L1 64-kB, cho phép IFU tìm nạp trước các lệnh

trước khi chúng cần thiết.

Điều khiển L2: Đây là logic điều khiển quản lý lưu lượng thông qua hai bộ đệm L2.

Data-L2: Bộ nhớ đệm dữ liệu L2 1 MB cho tất cả lưu lượng bộ nhớ khác với lệnh.

Hướng dẫn L2: Bộ nhớ đệm lệnh L2 1 MB

Bài tập lớn Kiến trúc máy tính CHƯƠNG 2 RAM

2.1 Hoạt động của bộ nhớ

Phần tử cơ bản của bộ nhớ bán dẫn là ô nhớ. Mặc dù nhiều công nghệ điện tử

được sử dụng, tất cả các ô nhớ bán dẫn đều có chung một số thuộc tính:

Chúng thể hiện hai trạng thái ổn định, có thể được sử dụng để biểu diễn nhị phân 1 và 0

Chúng có khả năng được viết thành (ít nhất một lần), để thiết lập trạng thái.

Chúng có khả năng được đọc để cảm nhận trạng thái.

Hình 2-5 Hoạt động của ô nhớ

Hình 2-1 mô tả hoạt động của một ô nhớ. Thông thường nhất, tế bào có ba thiết bị

đầu cuối chức năng có khả năng mang tín hiệu điện. . Như tên cho thấy, đầu cuối

chọn sẽ chọn một ô nhớ cho thao tác đọc hoặc ghi. Đầu cuối điều khiển cho biết đọc

hoặc ghi. Để ghi, đầu cuối kia cung cấp tín hiệu điện đặt trạng thái của ô thành 1

hoặc 0. Để đọc, đầu cuối đó được sử dụng cho đầu ra của trạng thái ô.

Thông thường ta ta sẽ phân ra làm 2 hoạt động chính là:

Hoạt động ghi dữ liệu.

Hoạt động đọc dữ liệu.

Giữa ghi (write) và đọc (read) chúng ta có một đường chung là chọn (select)

nhưng khác nhau là dữ liệu trong (data in) và cảm nhận (sense).

Cảm nhận (sense) sẽ cảm nhận thông tin được ghi trên ô nhớ này mức 0 hay

mức 1 và từ sense này ta đưa ra các trạng thái logic và đưa vào phần cứng

khác hoặc đưa vào bộ xử lý,...

Bài tập lớn Kiến trúc máy tính

Dữ liệu trong (Data in): Là khi ta muốn ghi vào ô nhớ ở trạng thái mức cao

hay mức thấp, Mức 0 hay mức 1.

Chọn (Select): Ta có một mảng các bộ nhớ (Memory array) chứa nhiều các

cell. Để truy cập vào trong các cell này, ta phải có 1 đường dữ liệu chọn

(select) để chọn những vùng nhớ đó, ô nhớ đó để bắt đầu thao tác là ghi dữ liệu.

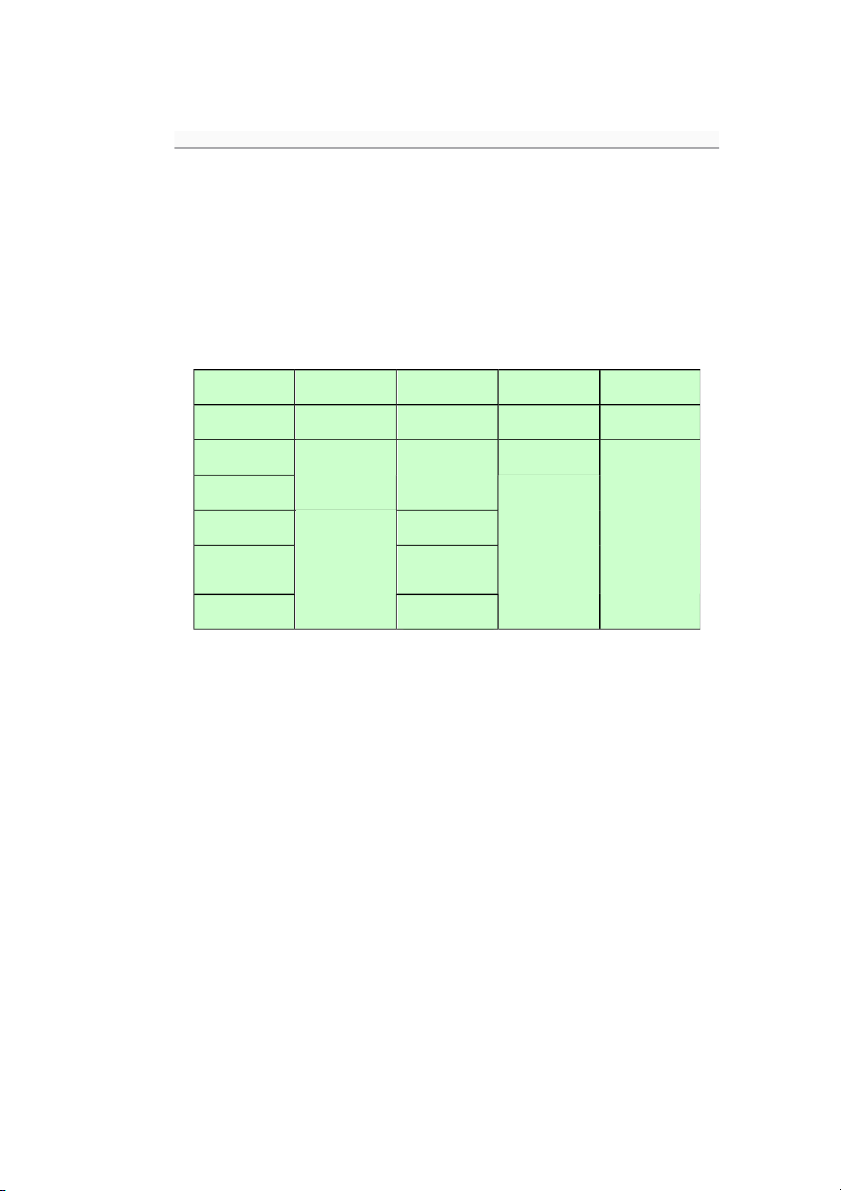

Điều khiển (Control): Điều khiển hoạt động 1 là đọc 2 là ghi. Memory Type Category Erasure Write Volatility Mechanism Random-access Read-write Electrically, Electrically Volatile memory (RAM) memory byte-level Read-only Masks memory (ROM) Read-only Not possible Programmable memory ROM (PROM) Erasable PROM UV light, chip- (EPROM) level Nonvolatile Electrically Electrically Read-mostly Electrically, Erasable PROM memory byte-level (EEPROM) Flash memory Electrically, block-level

Bảng 2-1 Các loại bộ nhớ bán dẫn

Bảng 2.1 Liệt kê các loại bộ nhớ bán dẫn chính. Phổ biến nhất được gọi là bộ

nhớ truy xuất ngẫu nhiên (Random-access memory) hay còn được gọi là RAM. Và

một số bộ nhớ đọc để lưu chương trình (read-only memory) hay còn được gọi là ROM

Điểm giống và khác biệt giữa RAM và phần còn lại là:

RAM là bộ nhớ có khả năng vừa ghi vừa

đọc (Read-write memory)

khác với phần còn lại bộ nhớ chỉ đọc (Read-only memory) và bộ nhớ

chủ yếu là đọc (Read-mostly memory)

Erasure (Dọn dẹp): RAM có thể xoá được nội dung của bộ nhớ này (Electrically, byte-level).

Cơ chế của RAM là ghi bằng điện.

Bài tập lớn Kiến trúc máy tính

Đặc tính là bay hơi (Volatility): dữ liệu ghi trên bộ nhớ này sẽ bị mất đi,

không còn lưu trữ được nếu như nguồn cung cấp cho bộ nhớ này bị

ngắt quãng. Trái ngược với bộ nhớ RAM, thì bộ nhớ ROM có thể lưu

trữ được dữ liệu kể cả khi nguồn cung cấp không còn nữa (Nonvolatile).

Và điểm chung nhất giữa RAM và phần còn lại: đều là bộ nhớ bán dẫn,

và có chức năng là lưu trữ dữ liệu và lệnh. 2.2 RAM

Công nghệ RAM được chia thành hai công nghệ:

RAM động (Dynamic RAM) hay còn được gọi là DRAM

RAM tĩnh (Static RAM) hay còn được gọi là SRAM.

2.2.1 Cấu trúc DRAM và SRAM

Cấu trúc RAM động (DRAM-Dynamic RAM)

Yếu tố lưu trữ dữ liệu cơ chế là dùng tụ điện để lưu trữ trạng thái nạp.

Nếu như trạng thái của tụ điện mà nó được nạp thì dữ liệu trên nó ở mức 1.

Còn nếu như tụ điện trên DRAM này ko được nạp (rỗng) thì nó ở mức 0. Sự

hiện diện hoặc không có điện tích trong tụ điện được hiểu là một hệ nhị phân 1 hoặc 0

Vì điện tích trên tụ điện sẽ bị rò, vì thế chúng ta phải có một cơ chế nào đó

để duy trì thông tin được nạp trên tụ điện này. Thì cơ chế đó là charge

refreshing trên tụ điện (capacitors).

Thuật ngữ động lực học (Dynamic) đề cập đến xu hướng điện tích được lưu

trữ bị rò rỉ ra ngoài, ngay cả khi nguồn điện được cấp liên tục.

Bài tập lớn Kiến trúc máy tính

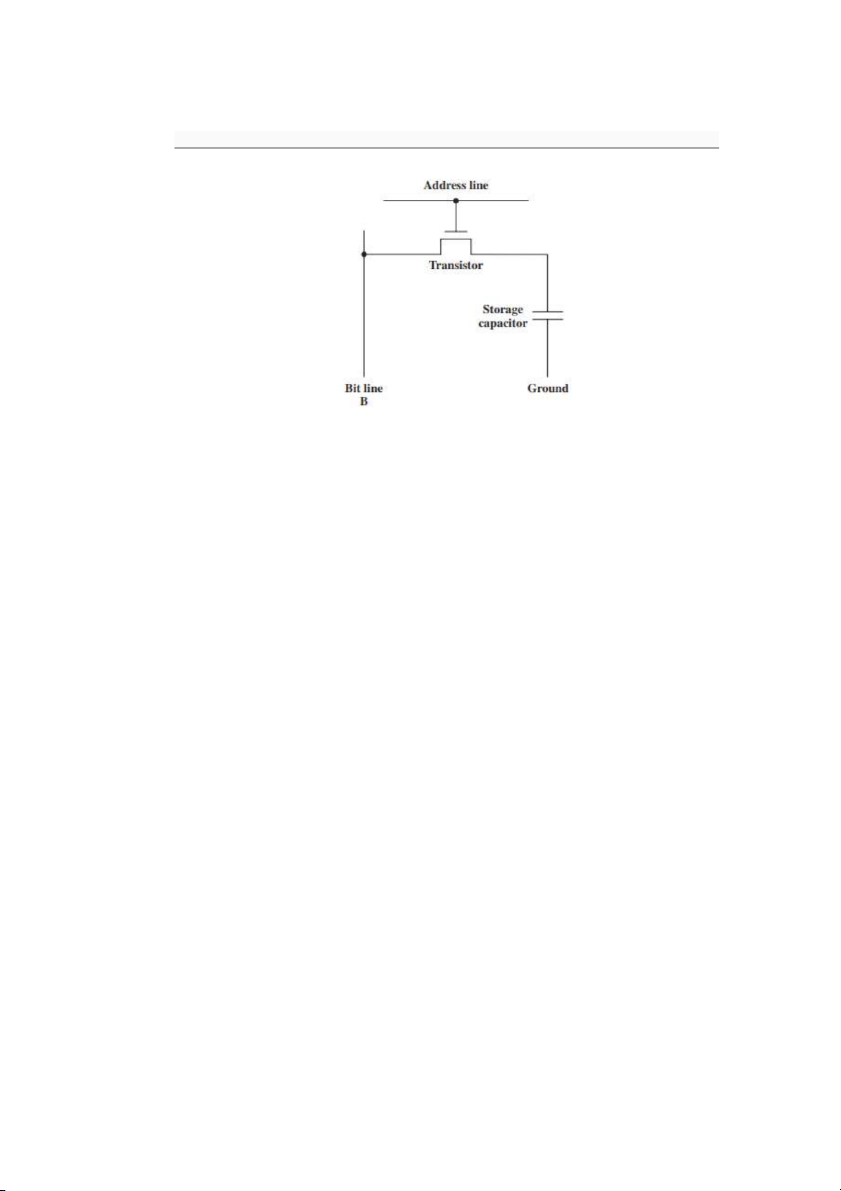

Hình 2-6 Phần tử nhớ DRAM 1 bit

Hình 2-2 là cấu trúc DRAM điển hình cho một ô riêng lẻ lưu trữ một bit.

Bộ nhớ DRAM được tổ chức thành một ma trận nhớ (thường là ma trận

vuông), trong đường địa chỉ (Adress line) là một trong các dây hàng của ma trận,

còn đường bit (Bit Line) là một trong các dây cột. Phần tử nhớ được đặt ở giao điểm

của các dây hàng và cột.

Phần tử nhớ được đặt ở giao điểm của dây hàng và cột. Transistor hoạt động

như là một khoá điện tử. Transistor có 3 cực là cực cổng G (Gate) nằm phía về phía

đường địa chỉ (Adress line), cực máng D (Drain) nằm về phía đường Bit (Bit line)

và cực nguồn S (Source) nằm về phía tụ của điện. Trong đó cực G (Gate) là cực

điều khiển, D sẽ được nối với S khi G có mức điện áp cao (1) so với S, ngược lại thì

điện trở giữa D và S sẽ rất lớn. Việc ghi (Write)

Khi đường địa chỉ có mức tích cực (1), T ở trạng thái mở, nối tụ điện C với

đường bit bit. Nếu thao tác là ghi thì giá trị cần phải đặt trên đường bit. Nếu giá

trị đó là 1 thì tụ C sẽ được nạp tới điện áp ứng với giá trị 1 trên đường bit, còn

nếu giá trị đó là 0 thì tụ C sẽ bị phóng hết điện tích, tức là có giá trị 0. Việc đọc (Read)

Việc đọc phức tạp hơn ghi một chút do tụ điện tích trên tụ C ứng với giá trị

cần đọc rất nhỏ. Trước khi đặt đường địa chỉ lên mức tích cực, cần phải đặt lên

Bài tập lớn Kiến trúc máy tính

đường bit điện áp bằng 1/2 mức chênh lệch giữa điện áp ứng với mức 0 và điện

áp ứng với mức 1. Điện áp trên tụ sẽ làm cho điện áp trên đường bit thay đổi

một chút theo chiều hướng tăng hoặc giảm, tuỳ thuộc vào việc nó đang nhớ giá

trị (high) hay 0 (low). Sự thay đổi nhỏ của điện áp trên đường bit sẽ được truyền

tới đầu vào của một bộ khuếch đại nhạy, tại đầu ra của nó ta nhận được điện áp

ứng với giá trị của bit chứa trên tụ C. Làm tươi (Refresh)

Vì mọi tụ điện đều có một điện trở rò và transistor T mắc nối tiếp với

nó dù ở trạng thái cấm cũng có một điện trở nhất định, cho nên khi được nạp,

điện tích trên tụ C liên tục bị phóng, sau một khoảng thời gian nhất định sẽ

làm mất thông tin mất thông tin mà C chứa. Chính vì vậy cần phải nạp điện

lại cho tụ C trước khi điện áp trên tụ giảm thấp hơn một ngưỡng nào đó, việc

này còn được gọi là “làm tươi” (refresh). Để làm tươi ô nhớ DRAM, cần

phải đọc nội dung của nó rồi viết trở lại. Việc làm tươi phải được tiến hành

đều đặn theo một chu kỳ nhất định, gọi là chu kỳ làm tươi; Tên gọi RAM

động (Dynamic RAM) xuất phát từ hoạt động này.

Cấu trúc RAM tĩnh (SRAM-Static RAM)

Ngược lại, RAM tĩnh (SRAM) là một thiết bị kỹ thuật số sử dụng cùng các phần

tử logic được sử dụng trong bộ xử lý.

Trong SRAM, các giá trị nhị phân được lưu trữ bằng cách sử dụng cấu hình

cổng logic flip-flop truyền thống.

RAM tĩnh sẽ giữ dữ liệu của nó miễn là nguồn được cung cấp cho nó.

Khi phần tử nhớ đã được thiết lập giá trị thì nó nhớ mãi cho đến khi chúng ta

thiết lập cho nó một giá trị mới.

Vì thế người ta gọi nó là phần tử nhớ RAM tĩnh (Static Random Access

Memory). Bộ nhớ được xây dựng từ các phần tử 1 bit như vậy được gọi là bộ nhớ RAM tĩnh.

Bài tập lớn Kiến trúc máy tính

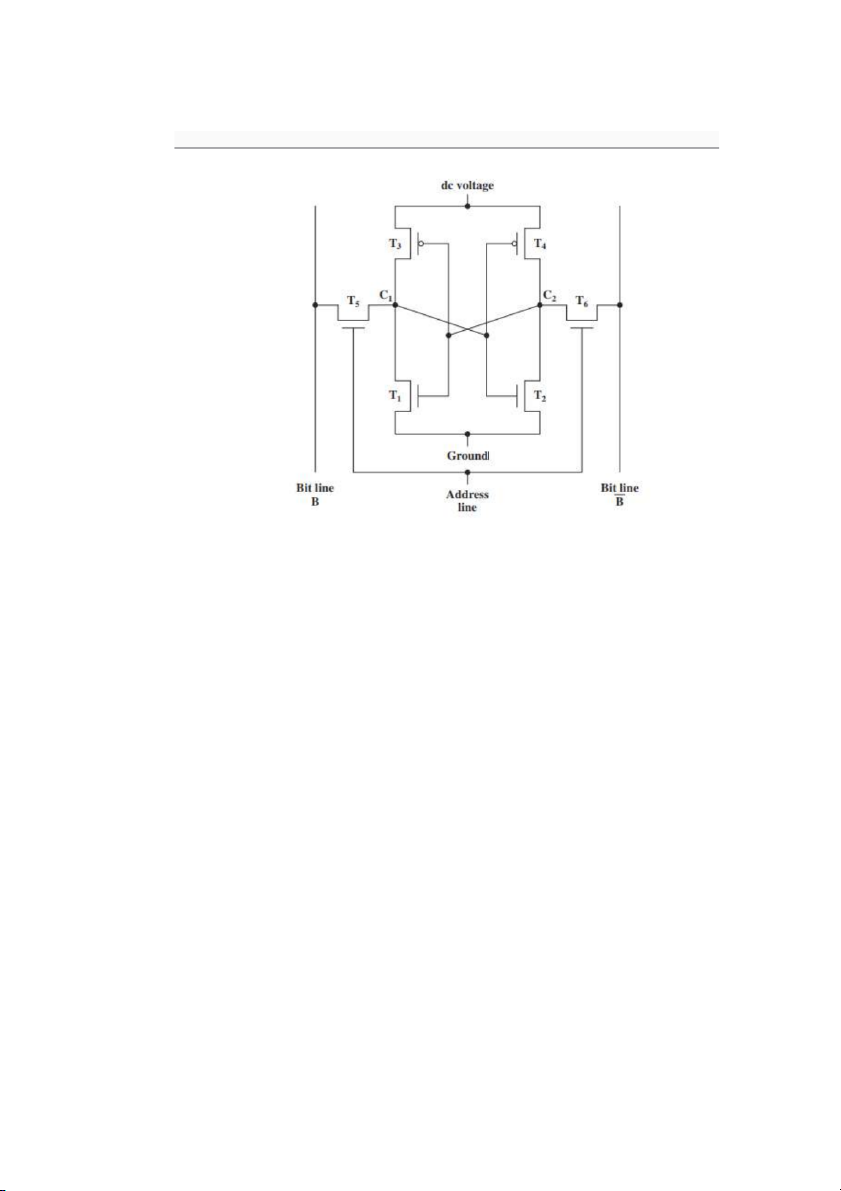

Hình 2-7 Phần tử nhớ DRAM 1 bit

Hình 2-3 thể hiện cấu trúc của 1 bit nhớ SRAM, được sử dụng 6 Transistor

được kí hiệu từ T1 đến T6. Trong đó có 4 Transistor NPN là T1 đến T4 và 2

Transistor PNP là T5 và T6 hoạt động như 2 công tắc điện tử để kết nối đường Bit

line và đường C1 cũng như là đường Bit line và đường C2.

Ở trạng thái logic 1, điểm C1 cao (1) và điểm C2 thấp (0); ở trạng thái này,

T1 và T4 tắt và T2 và T3 đang bật.1 Ở trạng thái logic 0, điểm C1 ở mức thấp (0) và

điểm C2 ở mức cao (1); ở trạng thái này, T1 và T4 đang bật và T2 và T3 tắt. Cả hai

trạng thái đều ổn định miễn là đặt điện áp dòng điện một chiều (một chiều). Không

giống như DRAM, không cần làm mới để giữ lại dữ liệu.

Như trong DRAM, dòng địa chỉ SRAM được sử dụng để mở hoặc đóng một

công tắc. Dòng địa chỉ điều khiển hai bóng bán dẫn (T5 và T6). Khi một tín hiệu

được áp dụng cho đường này, hai bóng bán dẫn được bật, cho phép hoạt động đọc

hoặc ghi. Đối với hoạt động ghi, giá trị bit mong muốn được áp dụng cho dòng B,

trong khi phần bù của nó được áp dụng cho dòng B. Điều này buộc bốn bóng bán

dẫn (T1, T2, T3, T4) ở trạng thái thích hợp. Đối với thao tác đọc, giá trị bit được đọc từ dòng B.

Bài tập lớn Kiến trúc máy tính

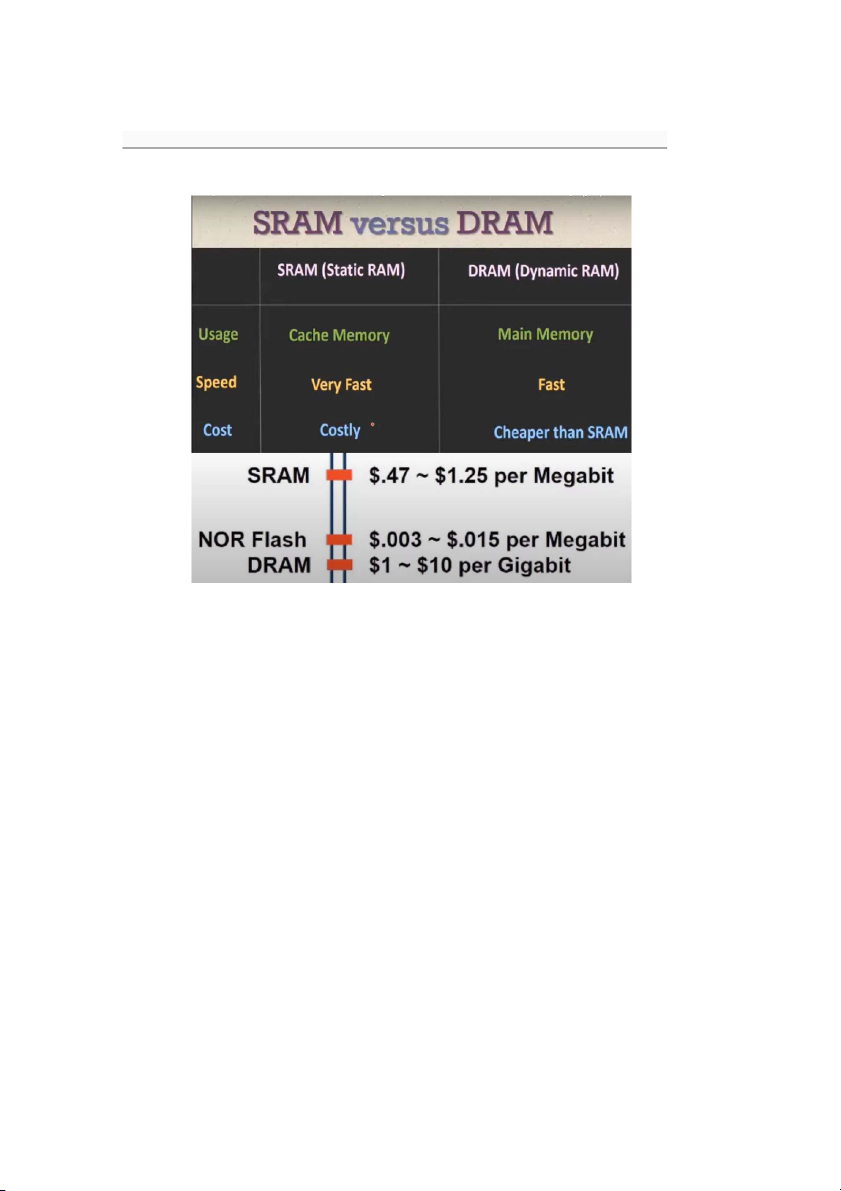

So sánh bộ nhớ SRAM và bộ nhớ DRAM

Hình 2-8 Đặc tính và giá thành của SRAM và DRAM

Hình 2-4 cho ta thấy được khác nhau về đặc tính và giá thành giữa SRAM và DRAM.

Điểm giống nhau giữa SRAM và DRAM:

Cả SRAM và DRAM đều dễ bay hơi; nghĩa là, nguồn điện phải được cung cấp liên

tục cho bộ nhớ để bảo toàn các giá trị bit.

Điểm khác nhau giữa SRAM và DRAM: RAM Động

Đơn giản hơn để xây dựng, nhỏ hơn

Mật độ tích hợp dày hơn (ô nhỏ hơn => nhiều ô hơn trên một đơn vị diện tích) Ít tốn kém hơn

Bài tập lớn Kiến trúc máy tính

Yêu cầu mạch làm tươi (refresh circuitry) dùng để tránh bị rò trên những con

tụ và vì thế nó cũng là một điểm hạn chế của DRAM làm cho tốc độ truy

xuất của bộ nhớ DRAM này chậm hơn so với SRAM

Có xu hướng được ưa chuộng cho lớn cho các yêu cầu bộ nhớ

Được sử dụng cho bộ nhớ chính. RAM Tĩnh

Vì bộ nhớ RAM Tĩnh không yêu cầu về mặt làm tươi (refresh) cho nên tốc

độ của SRAM nhanh hơn so với DRAM

Do những đặc điểm tương đối này, SRAM được sử dụng cho bộ nhớ đệm (cả chip bật và tắt)

2.3 Tổ chức của bộ nhớ

Hình 2-9 Giao tiếp giữa bộ xử lý và bộ nhớ

Hình 2-5 mô tả quá trình giao tiếp giữa bộ xử lý và bộ nhớ, phần bên trái là

bộ xử lý (Processor) và bên phải là bộ nhớ (Memory). Các đường tín hiệu giao tiếp

giữa bộ xử lý và bộ nhớ bao gồm các đường địa chỉ (address) và đường dữ liệu

(data). Bên cạnh đó ta có tín hiệu điều khiển (Control lines) như là R/W ( Read và Write).

Bài tập lớn Kiến trúc máy tính

Tổ chức bộ nhớ SRAM

Hình 2-10 Tổ chức bộ nhớ SRAM

Hình 2-6 minh hoạ cho tổ chức bộ nhớ SRAM, đầu vào là các đường địa chỉ theo

hàng (row address) và cột (column address). Và mỗi giao điểm của row address và

column address đại diện cho 1 bit nhớ SRAM

Tổ chức bộ nhớ DRAM

Hình 2-11 Tổ chức bộ nhớ DRAM

Hình 2-7 mô tả tổ chức của bộ nhớ DRAM, mỗi bit nhớ (Giao điểm của hàng

và cột) được cấu tạo bởi 1-T DRAM Cell.

Bài tập lớn Kiến trúc máy tính

Tổ chức DRAM nâng cao

Một trong những điểm nghẽn hệ thống quan trọng nhất khi sử dụng bộ vi xử

lý hiệu suất cao là giao diện với bộ nhớ chính bên trong.

Chip DRAM truyền thống bị hạn chế bởi cả kiến trúc bên trong và giao diện

của nó với bus bộ nhớ của bộ xử lý.

Một số cải tiến đối với kiến trúc DRAM cơ bản đã được khám phá và hiện

đang thống trị thị trường là RAM động đồng bộ (Synchronous dynamic

random access - SDRAM) và RAM động đồng bộ gấp đôi (Double Data Rate SDRAM - DDR-DRAM) SDRAM

Không giống như DRAM truyền thống, không đồng bộ, SDRAM trao đổi dữ

liệu với bộ xử lý được đồng bộ hóa với tín hiệu xung nhịp bên ngoài và chạy ở tốc

độ tối đa của bộ xử lý / bus bộ nhớ mà không áp đặt trạng thái chờ. Tốc độ SDRAM

đạt từ 66-133MHz (thời gian thâm nhập bộ nhớ từ 75ns150ns).

Hình 2-8 minh hoạ sơ đồ khối của RAM đồng bộ (SDRAM) 256Mb

Hình 2-12 RAM động đồng bộ 256Mb