Preview text:

lOMoARcPSD| 36991220

TRƯỜNG ĐẠI HỌC SƯ PHẠM KỸ THUẬT TP. HCM

KHOA ĐÀO TẠO CHẤT LƯỢNG CAO MÔN HỌC:

INTEGRATED CIRCUITS AND SYSTEMS DESIGN BÁO CÁO CUỐI KỲ

ĐỀ TÀI: TÌM HIỂU GIAO TIẾP SPI lOMoAR cPSD| 36991220 MỤC LỤC

NHẬN XÉT CỦA GIẢNG VIÊN..................................................................................I

MỤC LỤC......................................................................................................................

II MỤC LỤC HÌNH ẢNH.........................................V

CHƯƠNG 1: TỔNG QUAN......................1

1. Đặt vấn đề..............................................................................1

2. Mục tiêu đề tài.................................................................1

3. Nội dung nghiên cứu..............................................................................................1

4. Bố cục......................................................1

5. Giới hạn đề tài........................................................ 2

CHƯƠNG 2: CƠ SỞ LÝ THUYẾT............................................................................. 3

2.1. Giới thiệu giao diện SPI......................................................................................3

2.2. Chuẩn truyền thông SPI...................................................................................... 3 2.2.1. Cấu trúc

SPI..................................................................................................3

2.2.2. SPI truyền thông như thế nào?.....................................................................5

2.2.3. Các kiểu kết nối SPI.....................................................................................9

CHƯƠNG 3: THIẾT KẾ.............................................................................................13

3.1. Sơ ồ khối thiết kế.............................................................................................13

3.1.1. Mô hình giao tiếp SPI................................................................................ 13 3.1.2. Sơ ồ khối thiết mạch giao tiếp

SPI...........................................................13 3.1.3. Sơ ồ SCK Clock

Logic.............................................................................14

3.2. Mô tả thanh ghi..................................................................................................15

3.2.1. Thanh ghi của giao tiếp bên trong vi iều

khiển....................................... 15

3.2.2. Thanh ghi của giao tiếp SPI.......................................................................16

3.3. Sơ ồ thuật toán thiết kế....................................................................................18 lOMoARcPSD| 36991220

CHƯƠNG 4: ĐÁNH GIÁ QUA TESTBENCH........................................................20

4.1. Thiết kế chương trình........................................................................................20

4.2. Chương trình testbench tổng quát.....................................................................22

4.3. Mô tả các trường hợp test..................................................................................25 4.4. Kết

quả...............................................................................................................26

4.5. Nhận xét và ánh giá.........................................................................................26 CHƯƠNG 5: KẾT

LUẬN............................................................................................28 5.1. Những ưu iểm của

SPI.................................................................................... 28 5.2. Những nhược iểm của

SPI.............................................................................. 28 TÀI LIỆU THAM

KHẢO........................................................................................... 29 lOMoARcPSD| 36991220

MỤC LỤC HÌNH ẢNH

Hình 1: Giao diện SPI ..................................................................................................... 4

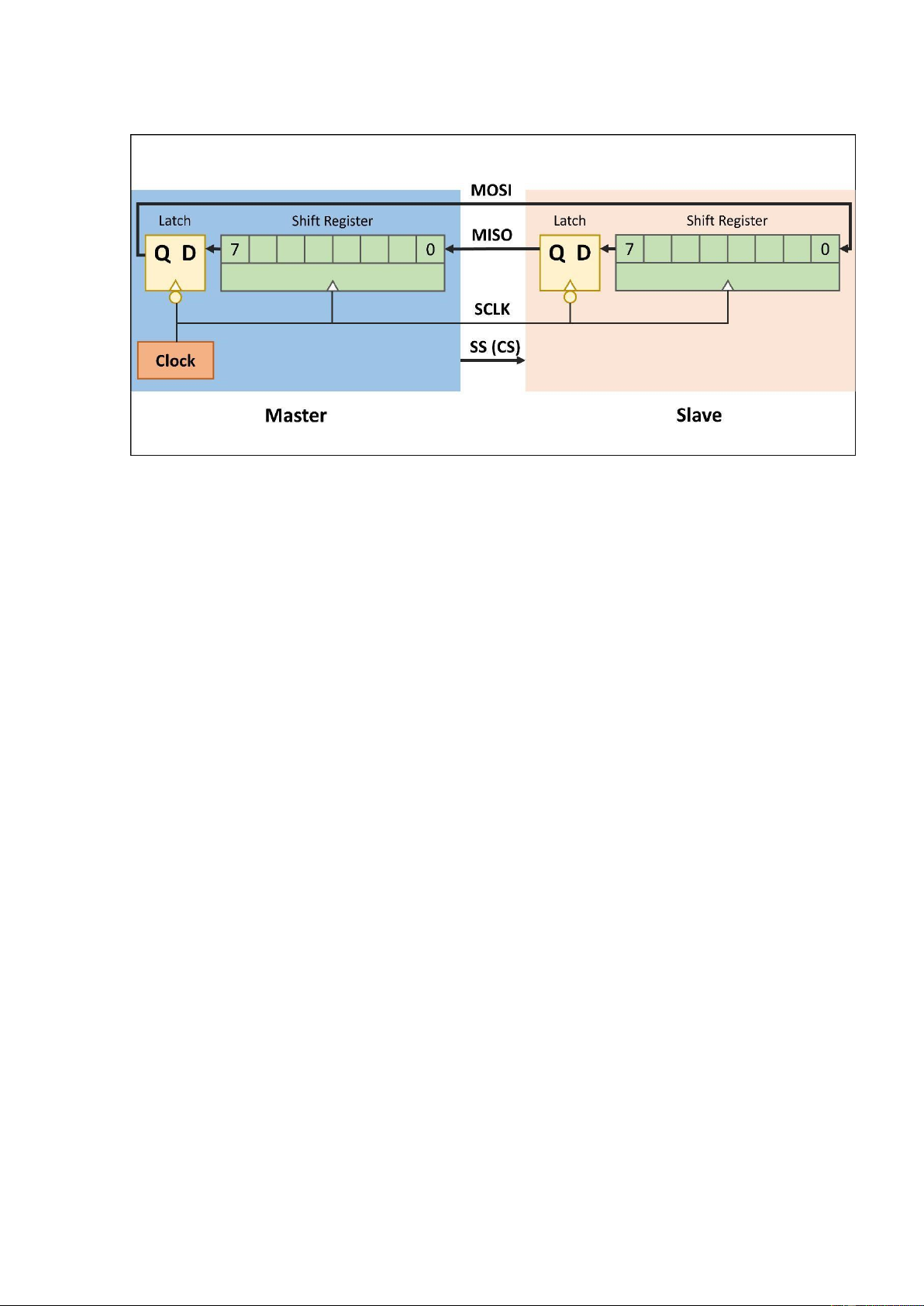

Hình 2: Truyền dữ liệu SPI ............................................................................................. 5

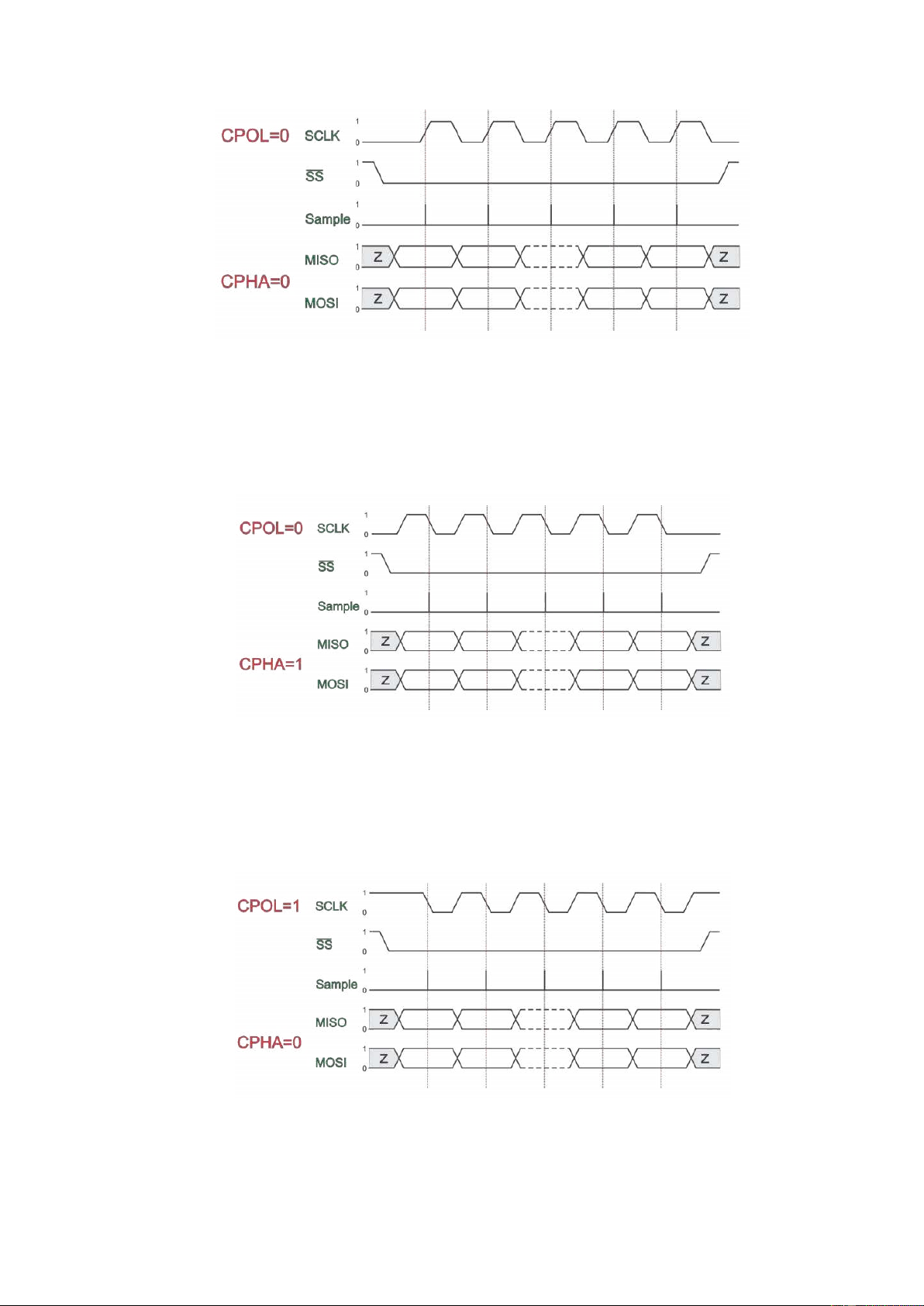

Hình 3: Giản ồ timing của giao tiếp SPI theo Motorola ................................................. 6

Hình 4: Giản ồ thời gian của SPI ở Mode 0 .................................................................... 8

Hình 5: Giản ồ thời gian của SPI ở Mode 1 .................................................................... 8

Hình 6: Giản ồ thời gian của SPI ở Mode 2 .................................................................... 8

Hình 7: Giản ồ thời gian của SPI ở Mode 3 .................................................................... 9

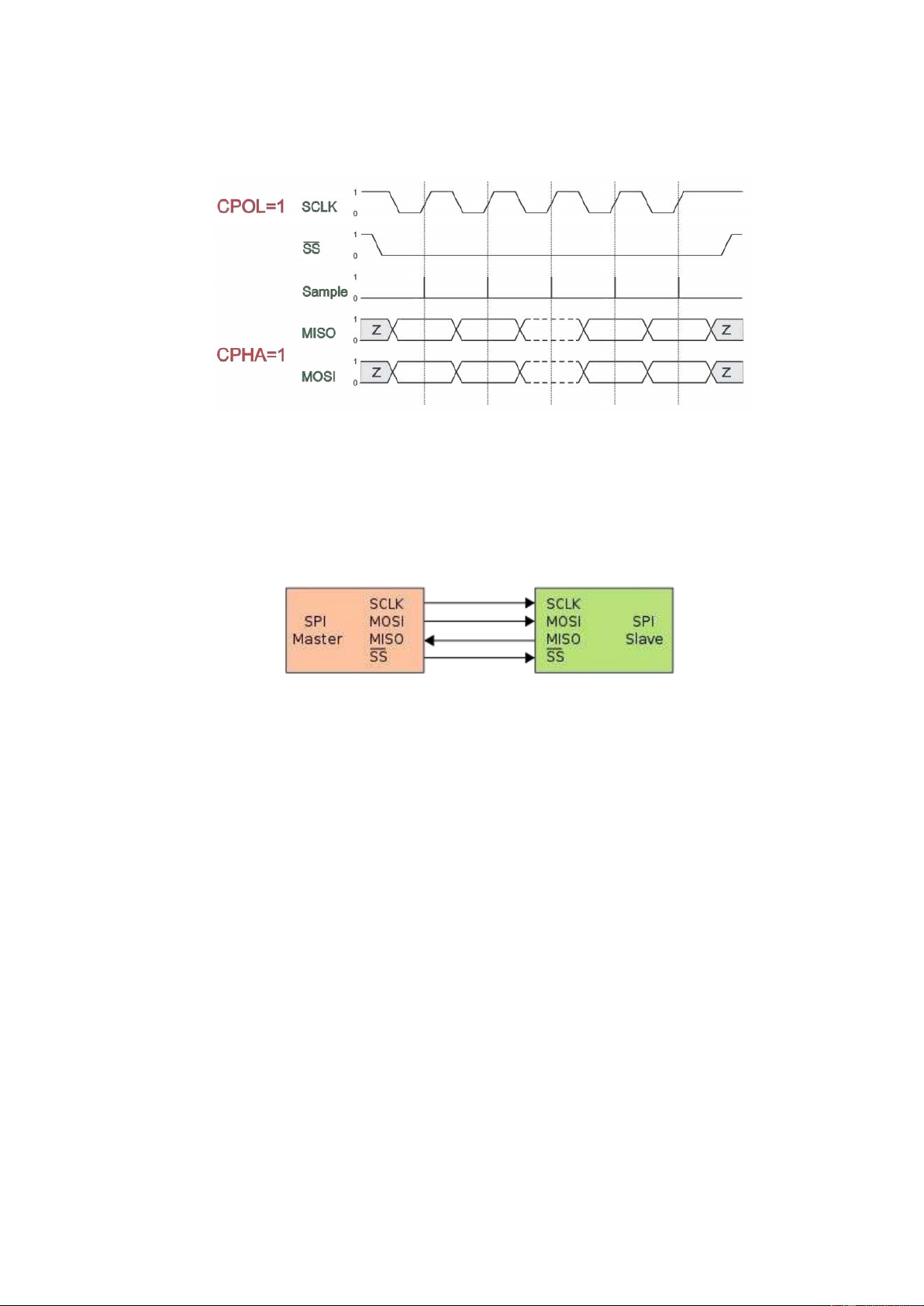

Hình 8: Kết nối point-to-point, một master nối với một slave ........................................ 9

Hình 9: Kết nối nhiều slave song song .......................................................................... 10

Hình 10: Kết nối nối tiếp (Daisy-Chained) ................................................................... 11

Hình 11: Kết nối hai master song song ến một slave .................................................... 11

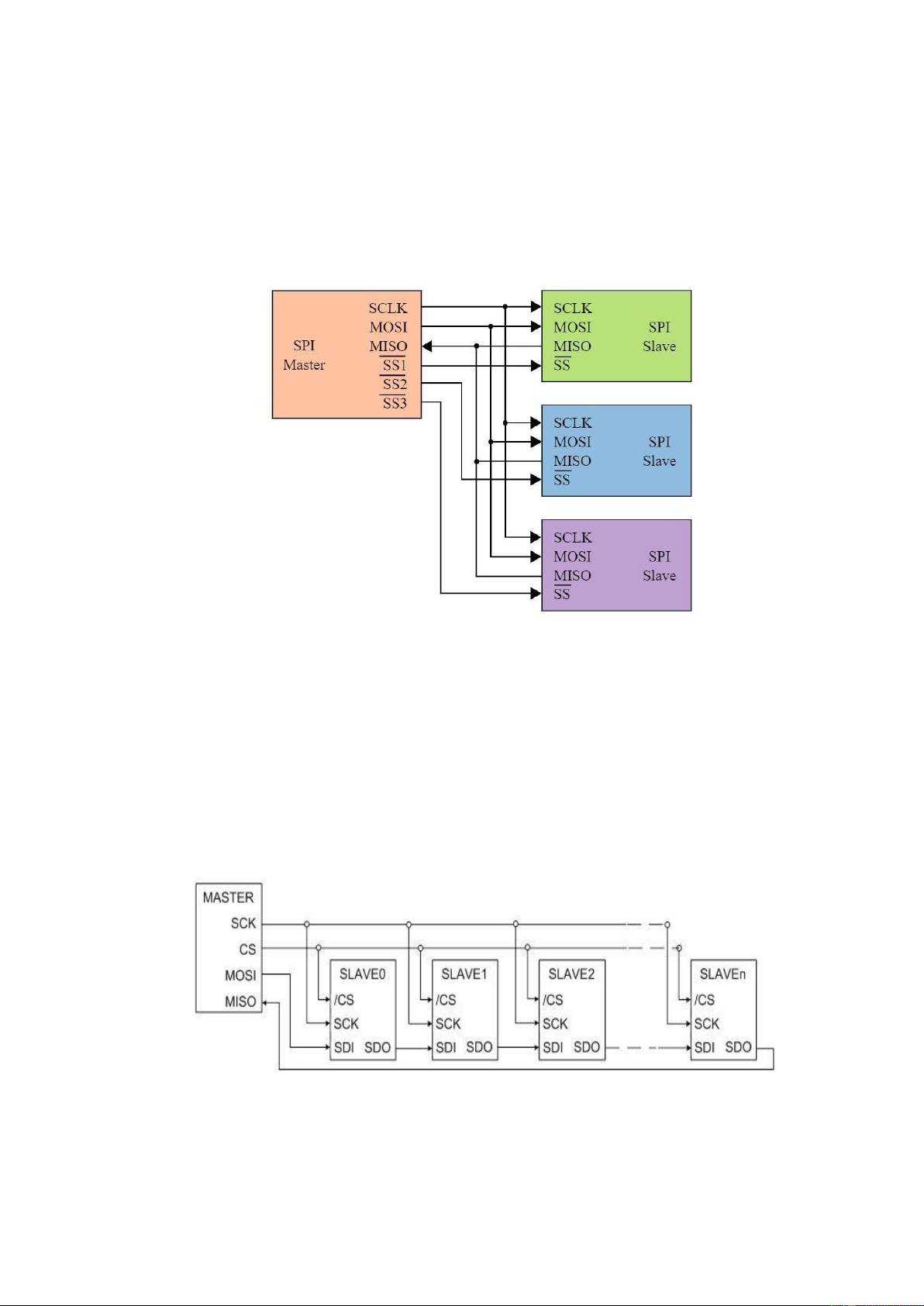

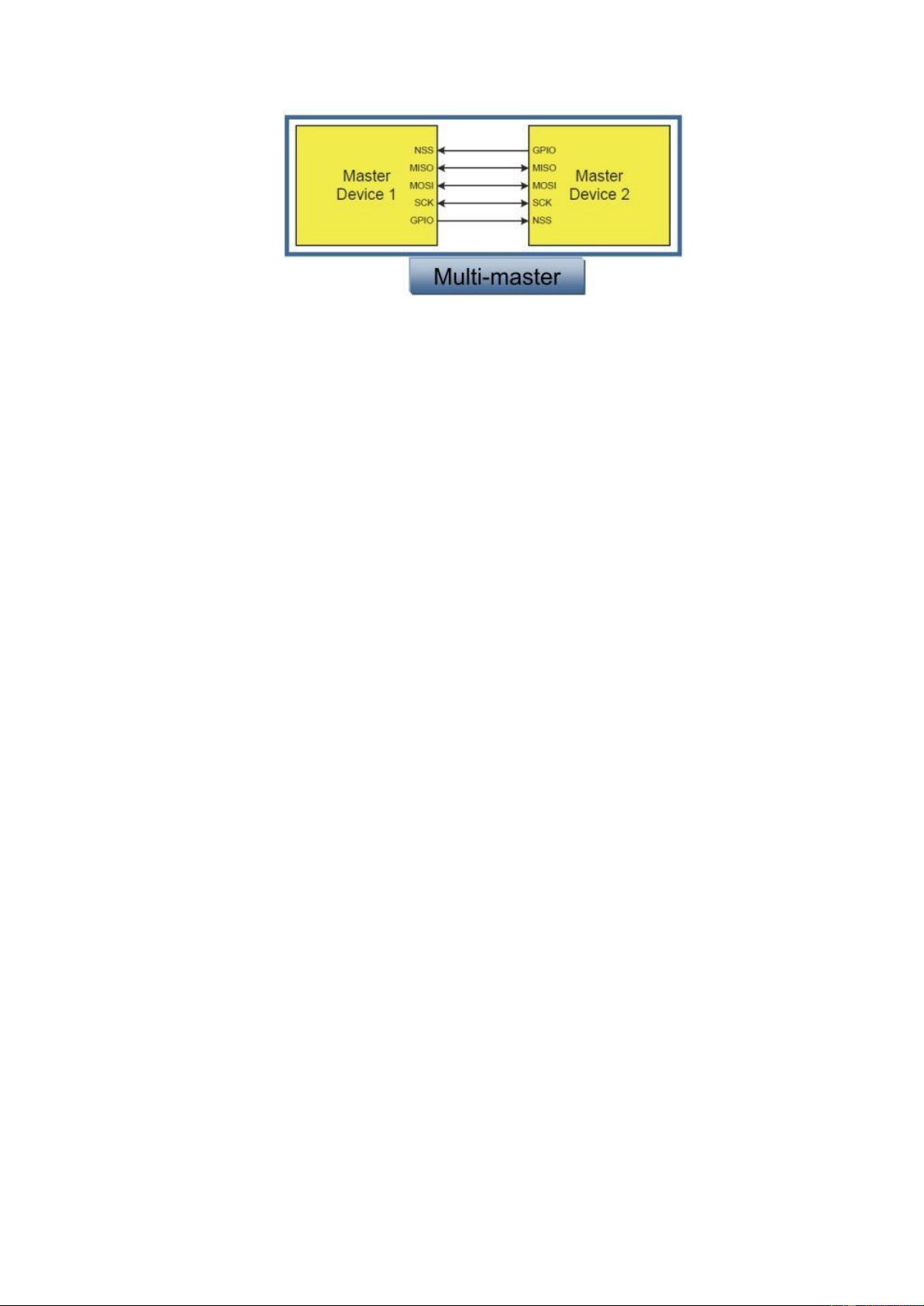

Hình 12: Kết nối hai master với nhau ........................................................................... 12

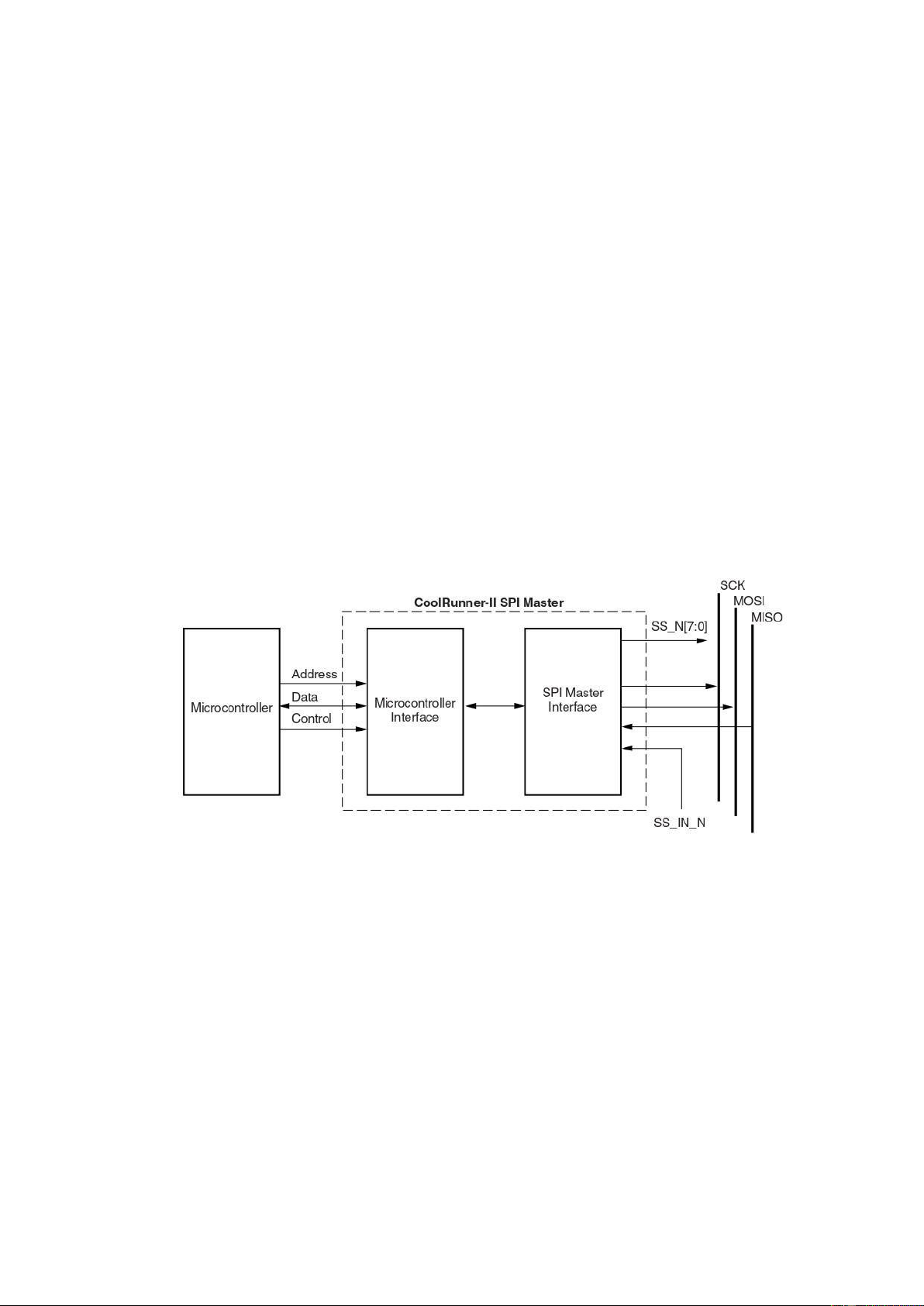

Hình 13: CoolRunner-II SPI Master ............................................................................. 13

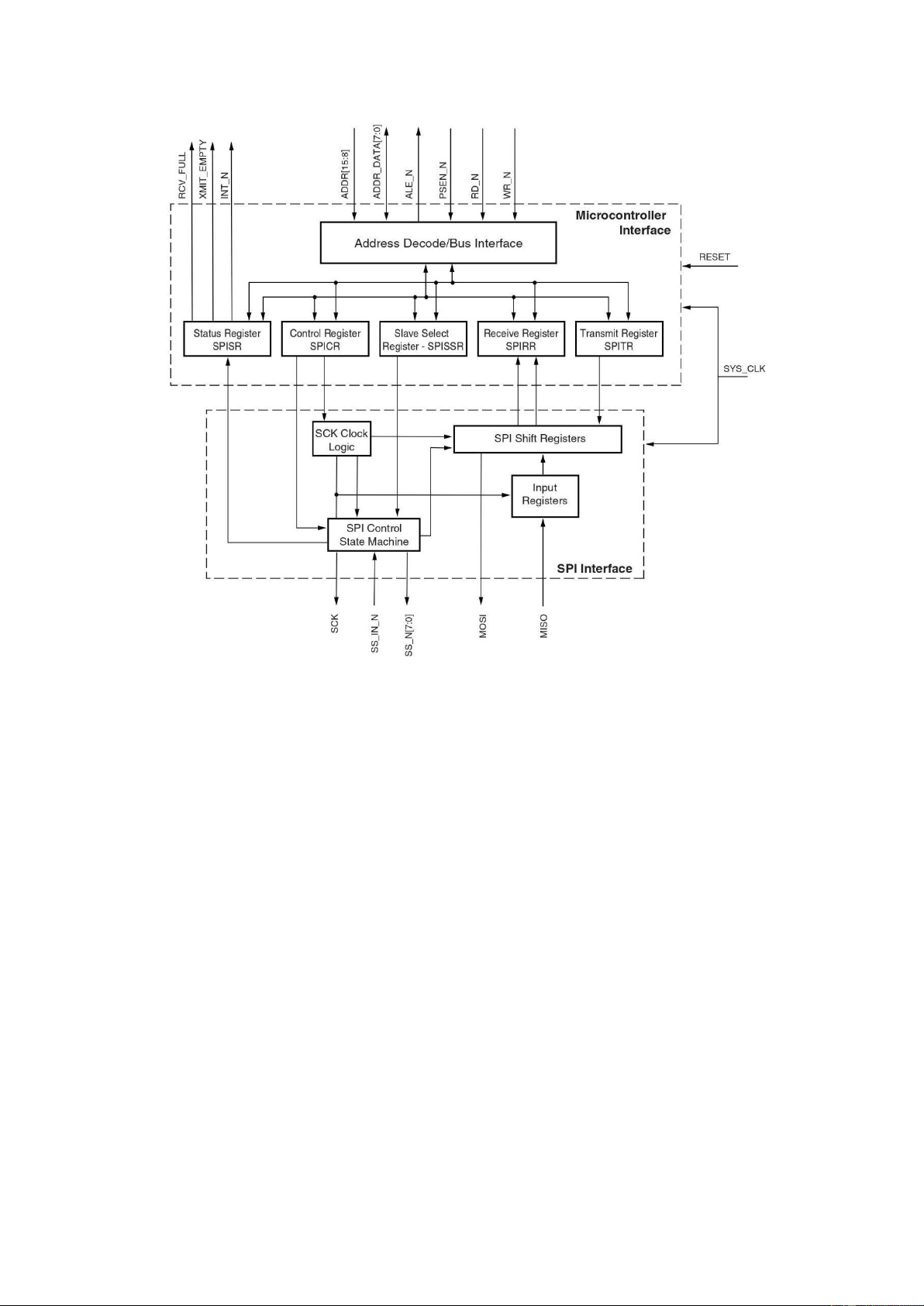

Hình 14: SPI Master Block Diagram ............................................................................ 14

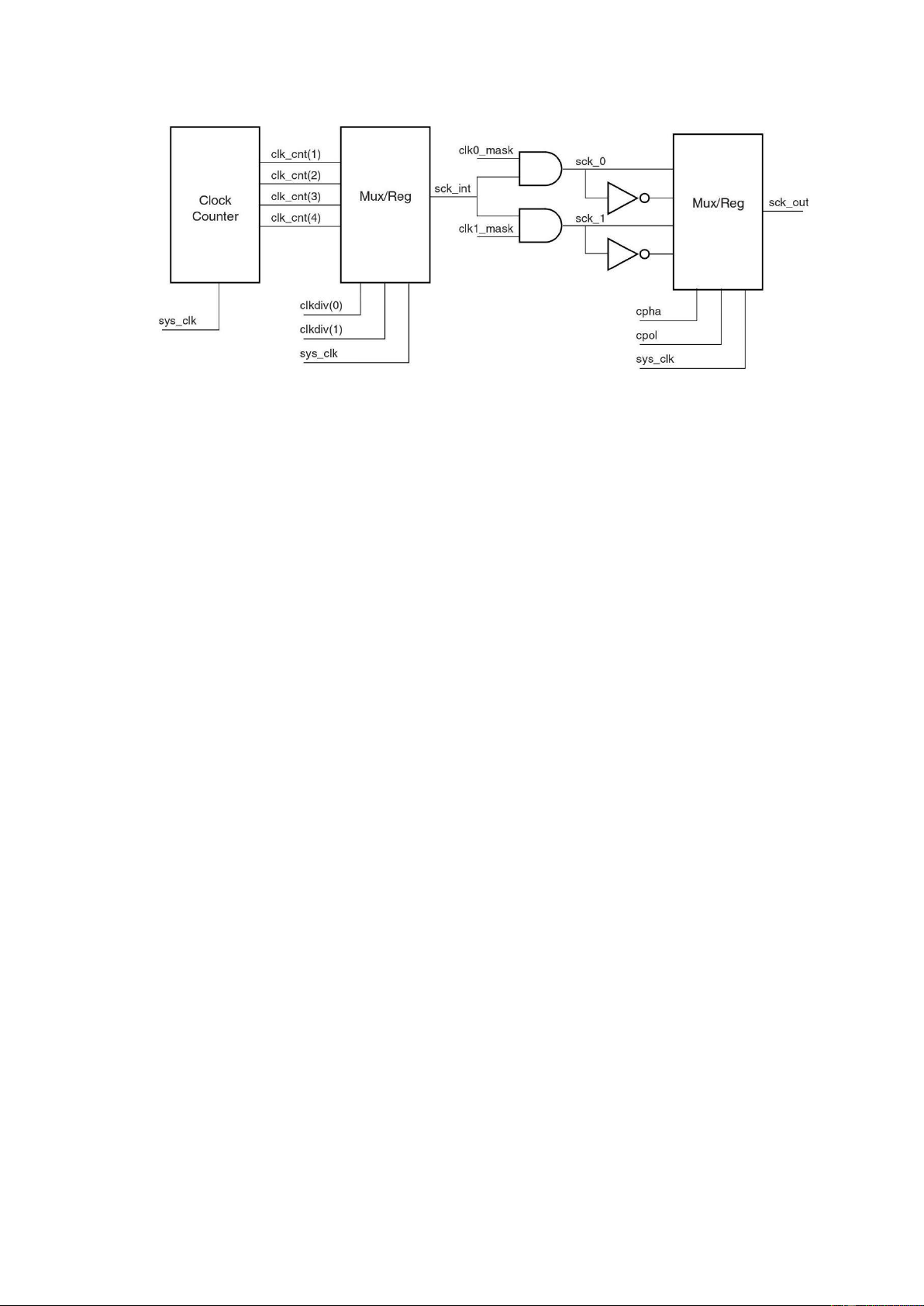

Hình 15: SCK Clock Generation Logic ........................................................................ 15

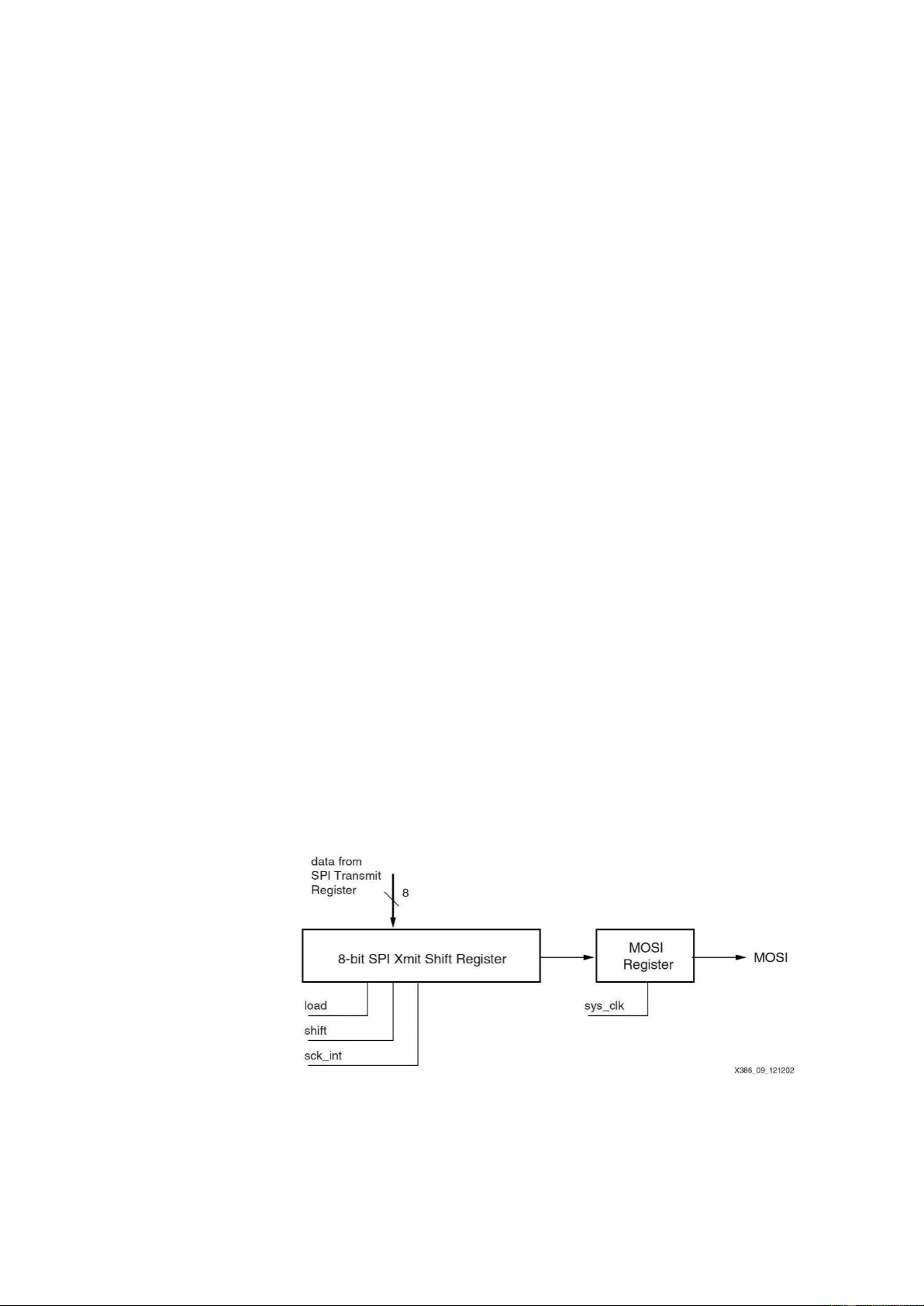

Hình 16: SPI Transmit Shift Register ........................................................................... 17

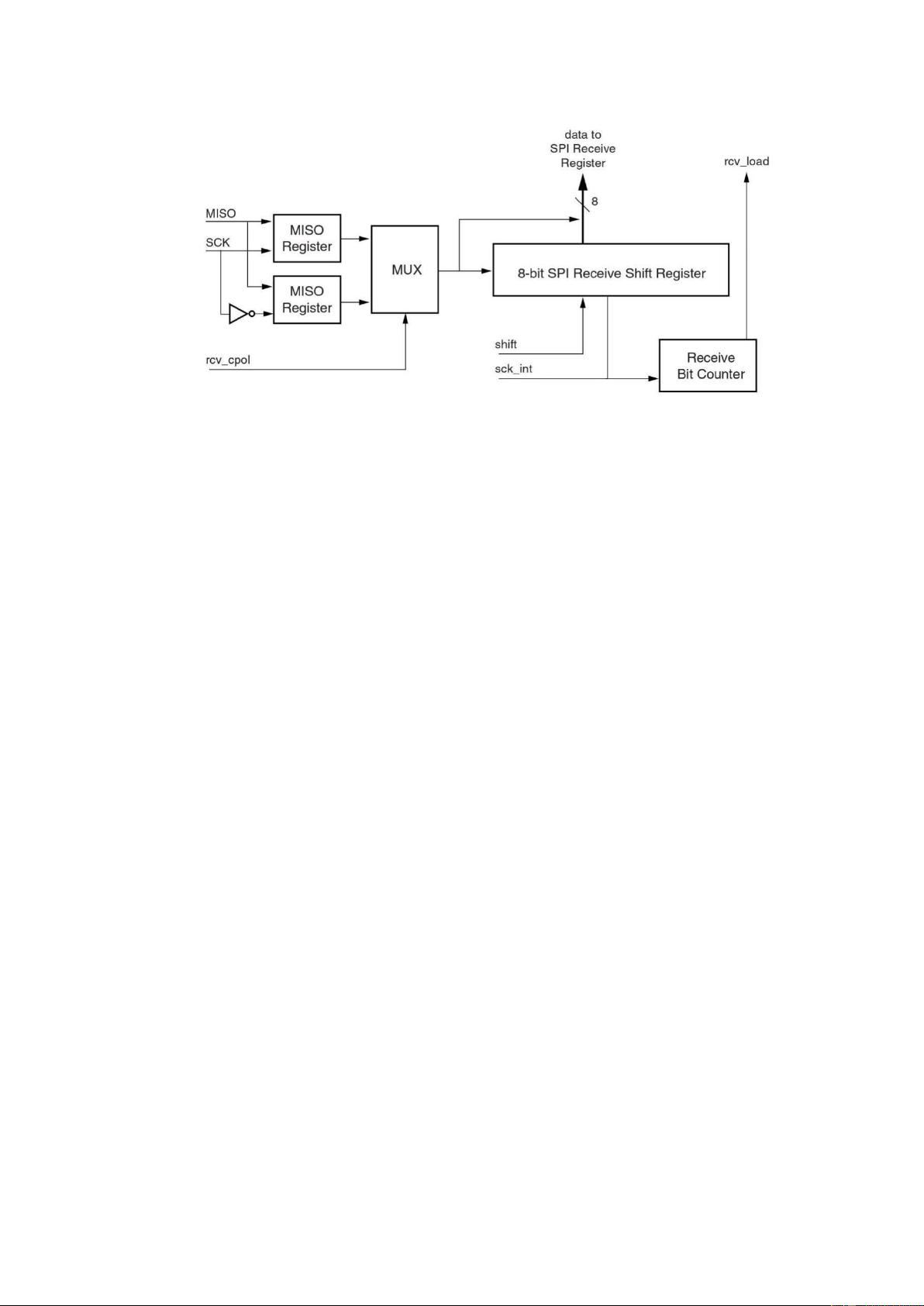

Hình 17: SPI Receive Shift Register and MISO Input Data Registers ......................... 18

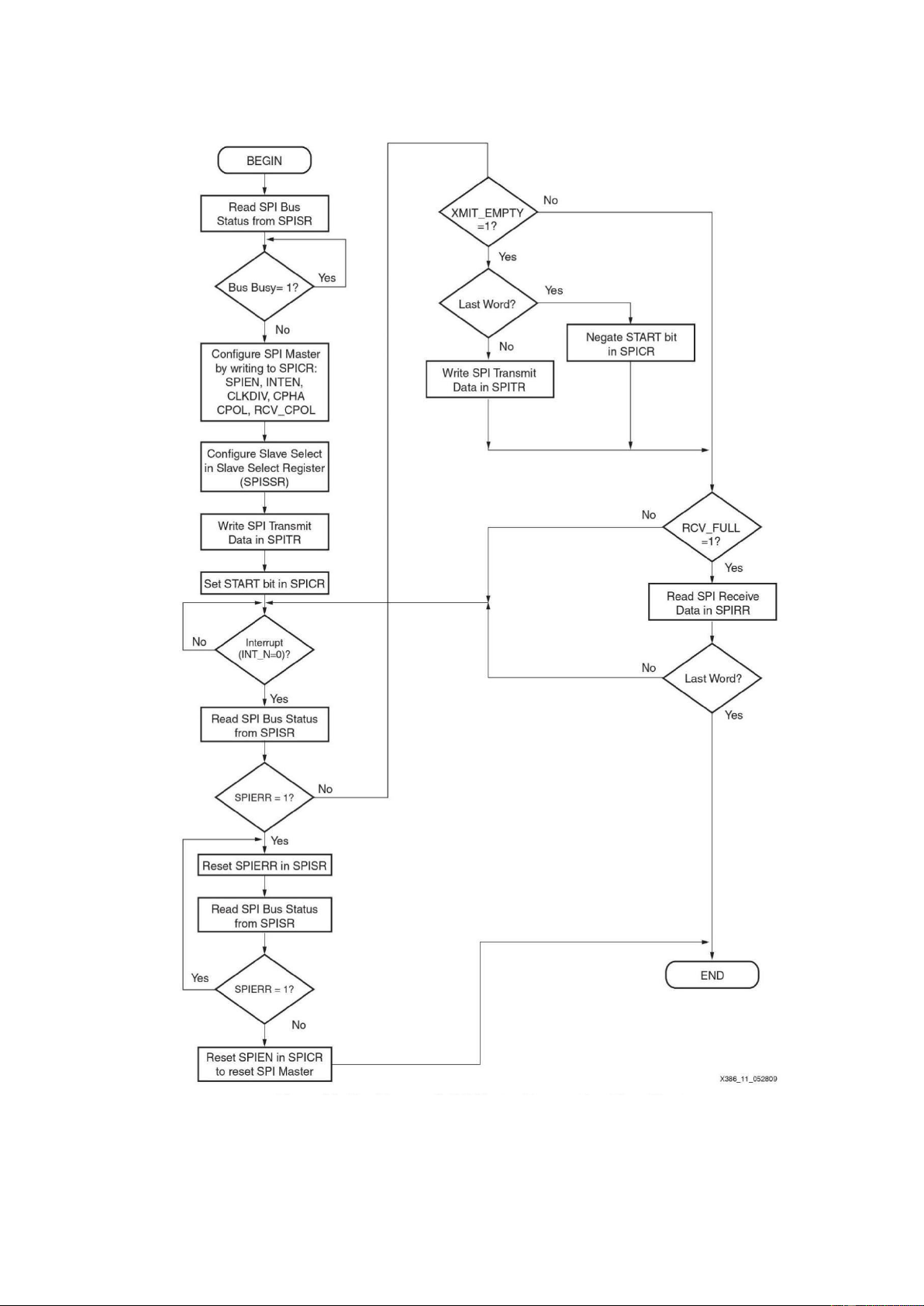

Hình 18: SPI Master Transaction Flow Chart ............................................................... 19

Hình 19: Hệ thống sử dụng giao tiếp SPI ...................................................................... 20 Hình 20: Kết

quả.............................................................................................................26 MỤC LỤC BẢNG

Bảng 1: Các tín hiệu của giao diện SPI............................................................................5

Bảng 2: Các chế ộ truyền thông trong giao thức SPI.....................................................7 lOMoARcPSD| 36991220

CHƯƠNG 1: TỔNG QUAN 1. Đặt vấn ề

Hiện nay, các vi xử lý hay vi iều khiển ang ược sử dụng rộng rãi trong nhiều lĩnh vực

như: iều khiển, tự ộng hóa, o ạc, truyền thông... So với các phương pháp iều khiển, o ạc

truyền thống (cơ khí, iện tử tương tự... ) thì sử dụng vi xử lý có các ưu iểm như: nhỏ gọn,

ít tốn năng lượng, thời gian áp ứng nhanh, có thể lập trình ược.

Giao tiếp và truyền nhận dữ liệu là một nhu cầu không thể thiếu trong hệ thống

nhúng.Trong ó giao thức ngoại vi nối tiếp (Serial Peripheral Interface) là một loại giao

tiếp truyền thông nối tiếp ồng bộ ược sử dụng cho giao tiếp khoảng cách ngắn, chủ yếu

trong các hệ thống nhúng. Giao diện ược phát triển bởi Motorola vào giữa những năm

1980 và ã trở thành một tiêu chuẩn thực tế. Các ứng dụng iển hình bao gồm thẻ từ và

màn hình tinh thể lỏng. Cùng với ó giao diện SPI ngày càng ược sử dụng rộng rãi trong

ngành công nghiệp cơ iện tử. Nhận thức ược tầm quan trọng của giao diện SPI trong lập

trình nhúng ây là cơ sở ể chúng em chọn ề tài bài tập lớn “Tìm hiểu giao diện SPI” ể kết thúc môn học.

2. Mục tiêu ề tài

- Hiểu ược chuẩn nối tiếp truyền thông.

- Nắm ược kiến thức về chuẩn giao tiếp SPI. - Phân tích ược ưu,

ược iểm của giao tiếp SPI.

- Thiết kế ứng dụng sử dụng giao tiếp SPI

- Nhận xét và ánh giá qua việc mô phỏng bằng phần mềm

3. Nội dung nghiên cứu

- Tổng quan về vấn ề sử dụng giao diện SPI trong truyền nhận dữ liệu.

- Giới thiệu về chuẩn giao tiếp SPI

- Đặc iểm và nguyên lý hoạt ộng của SPI

- Thiết kế phần cứng và giải thuật sử dụng SPI - Mô phỏng và ánh giá qua phần mềm - Tóm tắt và kết luận 4. Bố cục

Nội dung chính của ề tài gồm 6 chương: lOMoARcPSD| 36991220

CHƯƠNG 1: TỔNG QUAN CHƯƠNG 2: CƠ SỞ LÝ THUYẾT CHƯƠNG 3:

THIẾT KẾ CHƯƠNG 4: ĐÁNH GIÁ QUA TESTBENCH CHƯƠNG 5: KẾT

LUẬN VÀ HƯỚNG PHÁT TRIỂN

5. Giới hạn ề tài

Đề tài chỉ ề cập ến nghiên cứu về mặt lý thuyết chuẩn giao tiếp SPI, nguyên lý hoạt

ộng và ưu nhược iểm của SPI, viết một chương trình ứng dụng của SPI, mô phỏng trên

phần mềm và hướng phát triển công nghệ trong tương lai. lOMoARcPSD| 36991220

CHƯƠNG 2: CƠ SỞ LÝ THUYẾT

2.1. Giới thiệu giao diện SPI

SPI (Serial Peripheral Interface – Giao diện Ngoại vi Nối tiếp) là một chuẩn ồng bộ

nối tiếp ể truyền dữ liệu ở chế ộ song công toàn phần (full-duplex), do công ty Motorola

thiết kế nhắm ảm bảo sự liên hợp giữa các vi iều khiền và thiết bị ngoại vi một cách ơn giản.

Đây là kiểu truyền thông Master-Slave, trong ó có 1 chip Master iều phối quá trình

truyền thông và các chip Slaves ược iều khiển bởi Master vì thế truyền thông chỉ xảy ra giữa Master và Slave.

SPI cung cấp một giao diện nối tiếp ơn giản giữa vi xử lý và thiết bị ngoại vi. Giống

với các Bus nối tiếp khác như I2C, CAN hoặc USB. Chuẩn giao tiếp SPI ngày càng ược

sử dụng rộng rãi trong lĩnh vực iện tử, ặc biệt là trong giao tiếp trao ổi dữ liệu với các thiết bị ngoại vi.

Giao diện SPI ược sử dụng tích hợp trong một số loại thiết bị như: - Các bộ chuyển ổi (ADC và DAC)

- Các loại bộ nhớ (EEPROM và FLASH)

- Các loại IC thời gian thực

- Các loại cảm biến (nhiệt ộ, áp suất...)

- Và một số loại thiết bị khác như: bộ trộn tín hiệu analog, LCD, Graphic LCD...

2.2. Chuẩn truyền thông SPI 2.2.1. Cấu trúc SPI

Giao diện SPI ược thực hiện thông qua Bus 4 dây MISO, MOSI, SCK và SS nên ôi

khi SPI còn ược gọi là “giao diện 4 dây”.

a. MISO – Master Input/ Slave Output

Chân MISO dùng ể truyền dữ liệu ra khỏi SPI khi ặt cấu hình là Slave và nhận dữ

liệu khi ặt cấu hình là Master. MISO của Master và các Slaves ược nối trực tiếp với nhau.

b. MOSI – Master Output/ Slave Input

Chân MOSI dùng ể truyền dữ liệu ra khỏi SPI khi ặt cấu hình là Master và nhận dữ

liệu khi ặt cấu hình là Slave. MISO của Master và các Slaves ược nối trực tiếp với nhau. lOMoARcPSD| 36991220

c. SCK – Serial Clock

Xung giữ nhịp cho giao tiếp SPI, vì SPI là chuẩn truyền thông ồng bộ nên cần một

ường giữ nhịp, mỗi nhịp trên chân SCK báo 1 bit dữ liệu ến hoặc i. Sự tồn tại của chân

SCK giúp quá trình truyền ít bị lỗi và vì thế tốc ộ truyền của SPI có thể ạt hiệu quả cao.

Xung nhịp chỉ ược tạo ra bởi chip Master. d. SS – Slave Select

SS là ường chọn Slave cần giao tiếp, trên các chip Slave ường SS sẽ ở mức cao khi

không làm việc. Nếu chip Master kéo ường SS của một Slave nào ó xuống mức thấp thì

việc giao tiếp sẽ xảy ra giữa Master và Slave ó.

Chỉ có một ường SS trên mỗi Slave nhưng có thể có nhiều ường iều khiển trên Master

tùy thuộc vào thiết kế của người dùng.

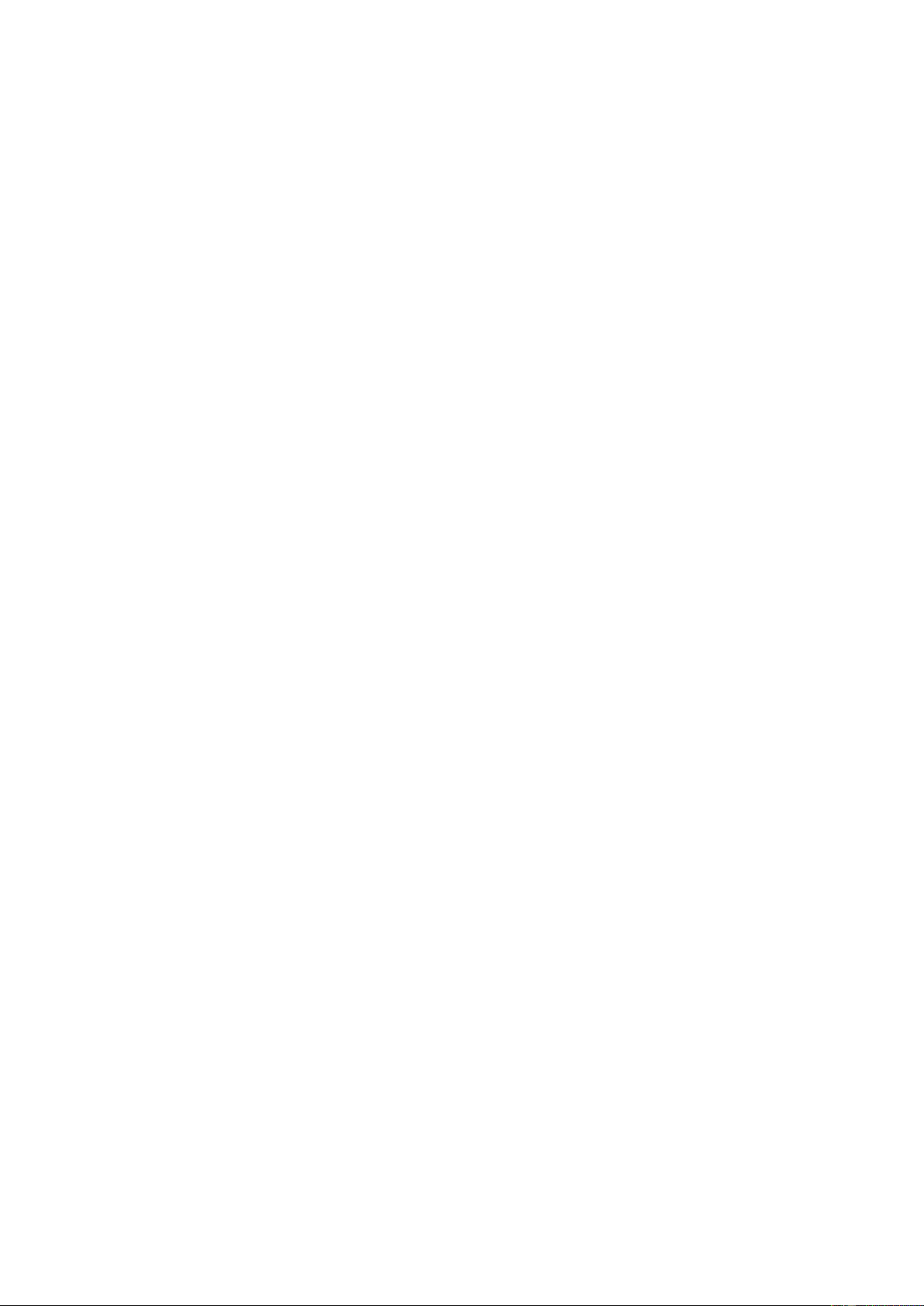

Hình 1: Giao diện SPI

Có thể mô tả tóm tắt các tín hiệu của giao diện SPI bằng bảng sau: Tên tín hiệu Chiều Mô tả SCK Master: ầu ra

Clock ồng bộ truyền/nhận dữ liệu luôn

ược cung cấp bởi Master Slave: ầu vào lOMoARcPSD| 36991220 SS Master: ầu ra

Tín hiệu kết nối với Slave. Master kích

hoạt tín hiệu này nếu muốn truyền/nhận Slave: ầu vào dữ liệu với Slave. Master: MOSI Đầu ra

Đầu ra dữ liệu nối tiếp Slave: SDO hoặc SO

- Với Master tín hiệu có tên Master Out Slave In

- Với Slave tín hiệu có tên Slave Data Out Master: MISO Đầu vào

Đầu vào dữ liệu nối tiếp Slave: SDI hoặc SI

- Với Master tín hiệu có tên Master In Slave Out

- Với Slave tín hiệu có tên Slave Data In

Bảng 1: Các tín hiệu của giao diện SPI

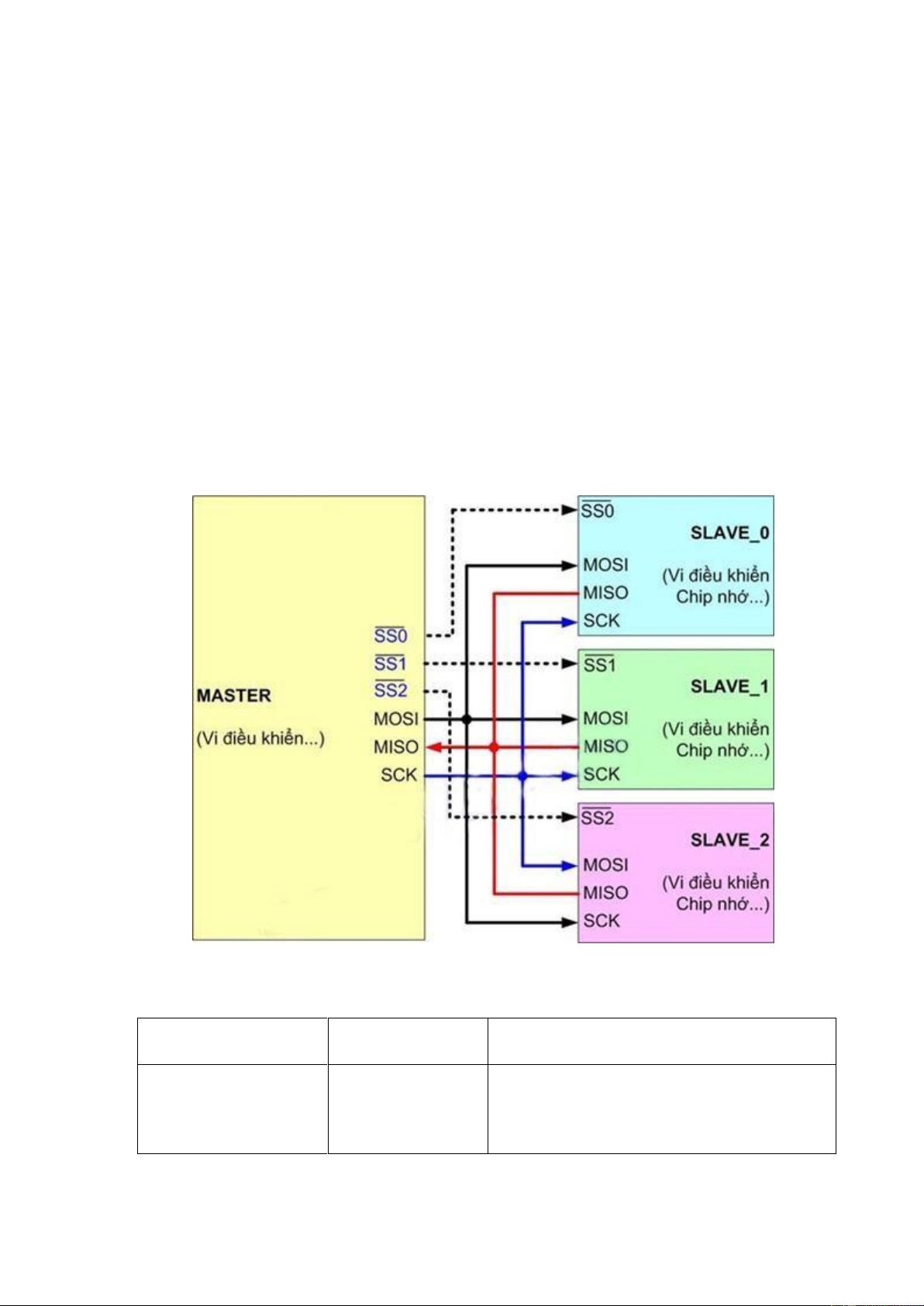

2.2.2. SPI truyền thông như thế nào? a. Mô tả cơ chế

Hình dưới ây mô tả quá trình truyền một gói dữ liệu thực hiện bởi module SPI trong

AVR, bên trái là chip Master và bên phải là Slave.

Hình 2: Truyền dữ liệu SPI

b. Giản ồ ịnh thời giao tiếp SPI – Motorola

Khi Master muốn truyền/nhận dữ liệu, nó kéo tín hiệu chọn chip SS xuống mức thấp.

Sau ó, Master cung cấp Clock ồng bộ việc truyền/nhận dữ liệu trên ường SCK.

Vị trí lấy mẫu dữ liệu và dịch dữ liệu theo xung SCK phụ thuộc vào hai thông số lOMoARcPSD| 36991220

cấu hình ược quy ịnh bởi chuẩn SPI là pha của Clock (CPHS – Clock Phase) và cực của

Clock (CPOL – Clock Polarity).

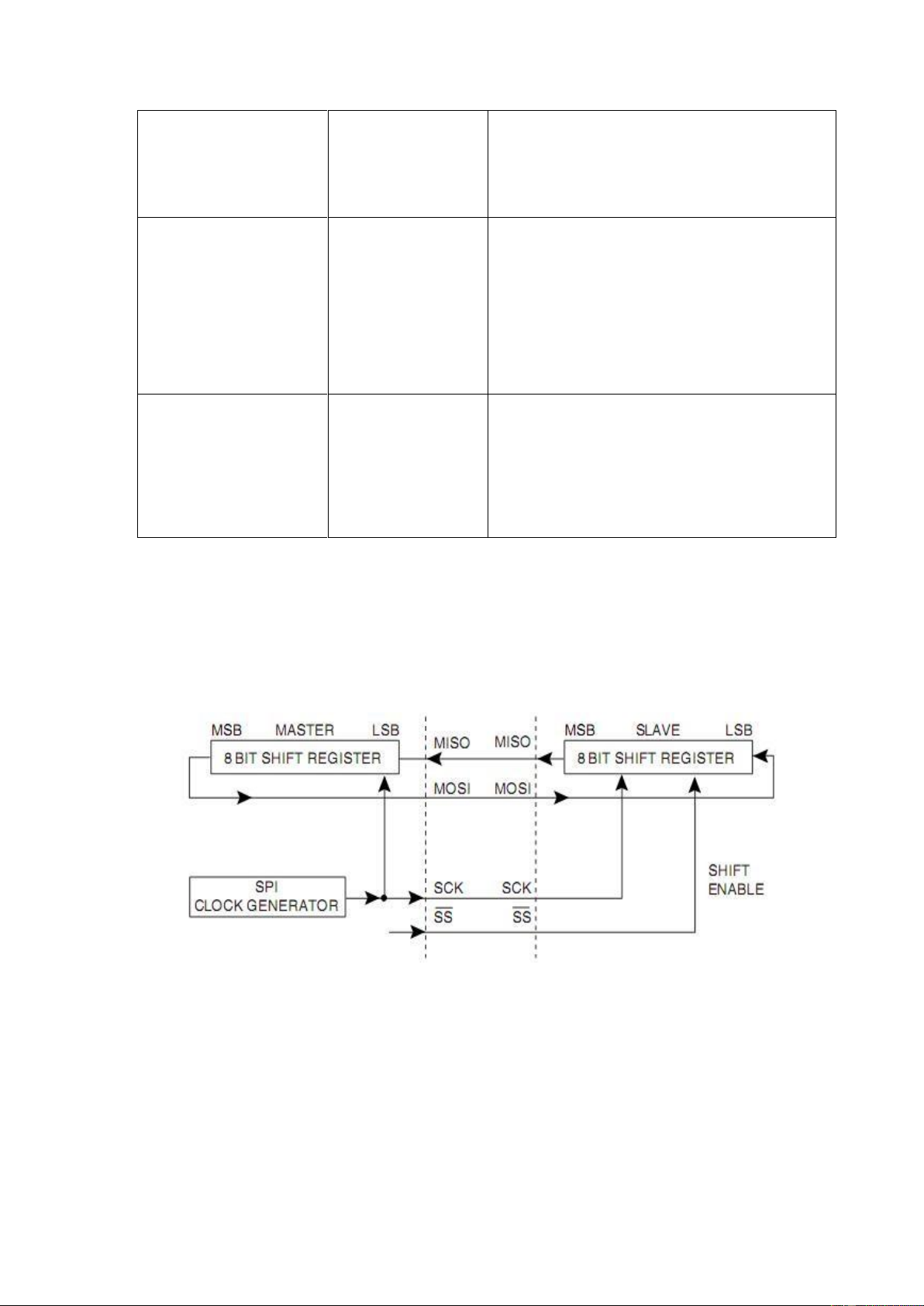

Hình 3: Giản ồ timing của giao tiếp SPI theo Motorola

Cực của Clock quyết ịnh trạng thái rảnh (idle) của tín hiệu SCK. Nếu CPOL = 0 thì

mức logic khi idle của SCK là mức 0. Nếu CPOL = 1 thì ngược lại.

Dựa vào pha của Clock chúng ta sẽ biết lấy iểm mẫu ở âu: -

Nếu pha Clock bằng 0 thì dữ liệu ược lấy mẫu khi SCK chuyển từ trạng thái idle

sang active, có thể là cạnh lên hoặc cạnh xuống tùy vào giá trị CPOL. -

Nếu pha Clock bằng 1 thì dữ liệu ược lấy mẫu khi SCK chuyển từ trạng thái active sang idle.

c. SPI là giao thức ồng bộ

Module SPI cho phép giao tiếp nối tiếp ồng bộ kép giữa vi xử lý với thiết bị ngoại vi:

- Tín hiệu SCK ược cung cấp bởi Master nhằm tạo xung ồng bộ cho phép dữ liệu ược

truyền i hoặc khi ọc dữ liệu nhận ược.

- Khi tín hiệu SCK ược phát ra thì tín hiệu này có thể thay ổi nhưng không làm hỏng dữ

liệu. Lí do là trong giao thức SPI, tốc ộ của dữ liệu truyền i sẽ thay ổi theo sự thay ổi

của SCK. Điều này rất có lợi nếu như vi xử lý bị cấp xung ồng hồ không chính xác (Ví dụ: bộ dao ộng RC).

d. SPI là giao thức trao ổi dữ liệu

Dữ liệu lúc nào cũng ược truyền qua lại giữa các thiết bị SPI. Thật ra, không có khái

niệm thiết bị phát hay thiết bị nhận trong giao thức SPI mà mỗi thiết bị có 2 ường dữ

liệu, một ường dữ liệu vào và một ường dữ liệu ra. lOMoARcPSD| 36991220

Dữ liệu truyền i ược iều khiển bởi xung SCK từ Master.

Khi ược truyền i, dữ liệu vào cần phải ược ọc ngay nếu không sẽ bị mất i và khi ó,

giao thức SPI có thể sẽ ngưng hoạt ộng. Để tránh tình trạng này, lúc nào ta cũng phải ọc

dữ liệu về ngay sau khi truyền i cho dù dữ liệu ó không thực sự cần thiết.

Thường thì một tín hiệu chọn Slave sẽ tác ộng mức thấp ể chỉ ra Slave nào ược truy

cập. Tín hiệu này phải ược sử dụng khi có nhiều hơn một Slave trong cùng hệ thống và

thường không sử dụng ến khi trong mạch chỉ có một Slave. Tuy nhiên, theo nguyên tắc

thì ta nên sử dụng tín hiệu này trong cả hai trường hợp trên.

Tín hiệu SS sẽ chỉ ra Slave nào mà Master muốn bắt ầu một quá trình trao ổi dữ liệu

bằng giao thức SPI giữa thiết bị Slave ó và chính nó. Nếu tín hiệu trên ường SS là 0 thì

chứng tỏ giao thức SPI ang hoạt ộng. Ngược lại là mức 1 thì giao thức SPI sẽ không hoạt ộng.

Một ặc iểm khá quan trọng của tín hiệu SS là nó có tác dụng làm tăng cường khả

năng miễn nhiễm cho hệ thống. Lí do là SS sẽ Reset Slave ể nó có thể nhận Byte dữ liệu tiếp theo.

SPI có 4 mode hoạt ộng, phụ thuộc vào cực tính và pha của xung ồng hồ. Trong

trường hợp cực âm của xung ồng hồ, tín hiệu SCK sẽ ở mức thấp trong quá trình nghỉ và

chuyển sang mức cao trong quá trình truyền dữ liệu. Ngược lại, ối với trường hợp cực

dương của xung ồng hồ, tín hiệu SCK ở mức cao trong quá trình nghỉ và chuyển sang

mức thấp khi truyền dữ liệu: SPI Mode CPOL CPHS 0 0 0 1 0 1 2 1 0 3 1 1

Bảng 2: Các chế ộ truyền thông trong giao thức SPI SPI Mode 0:

Mô tả: Xung dương, dữ liệu ược chốt trước khi dịch Giản ồ thời gian: lOMoARcPSD| 36991220

Hình 4: Giản ồ thời gian của SPI ở Mode 0 SPI Mode 1:

Mô tả: Xung dương, dữ liệu ược dịch i trước khi chốt Giản ồ thời gian:

Hình 5: Giản ồ thời gian của SPI ở Mode 1 SPI Mode 2:

Mô tả: Xung âm, dữ liệu

ược chốt lại trước khi dịch Giản ồ thời gian:

Hình 6: Giản ồ thời gian của SPI ở Mode 2 SPI Mode 3: lOMoARcPSD| 36991220

Mô tả: Xung âm, dữ liệu bị dịch i trước khi chốt lại Giản ồ thời gian:

Hình 7: Giản ồ thời gian của SPI ở Mode 3

2.2.3. Các kiểu kết nối SPI

a. Kết nối iểm – iểm ( point-to-point )

Đây là kiểu kết nối cơ bản nhất của giao thức SPI là một master kết nối với một slave.

Hình 8: Kết nối point-to-point, một master nối với một slave

Cả Master và Slave ều có thanh ghi dịch nối tiếp (thanh ghi dữ liệu 8 bits) ở bên

trong. Thiết bị Master bắt ầu việc trao ổi dữ liệu bằng cách truyền i một bit vào thanh ghi

dịch của nó, sau ó bit dữ liệu sẽ ược ưa sang Slave theo ường tín hiệu MOSI (SDI), Slave

sẽ truyền dữ liệu nằm trong thanh ghi dịch của chính nó ngược trở về Master thông qua

ường tín hiệu MISO (SDO). Bằng cách này, dữ liệu của hai thanh ghi sẽ ược trao ổi với

nhau. Việc ọc và ghi dữ liệu vào Slave diễn ra cùng một lúc nên tốc ộ trao ổi dữ liệu diễn

ra rất nhanh. Do ó, giao thức SPI là một giao thức rất có hiệu quả.

Trong kiểu kết nối này, chỉ có thiết bị Master mới có thể iều khiển (phát ra) xung

SCK. Dữ liệu sẽ không ược truyền i nếu như Master không cung cấp xung SCK và tất cả

các thiết bị Slave ều ược iều khiển bởi xung nhịp phát ra từ Master trong khi ó, Slave lại

không có khả năng phát xung. lOMoARcPSD| 36991220

b. Kết nối Multi-slave

Kết nối nhiều slave ộc lập (Independent slaves) hay kết nối song song:

Trong cách kết nối này, tín hiệu SCK và SDO từ Master ược cung cấp ến từng Slave.

Đường tín hiệu SDO của các Slave nối chung lại với nhau và truyền về Master. Lúc này,

Master sẽ lựa chọn Slave nào ể trao ổi dữ liệu thông qua các chân SS riêng lẻ.

Hình 9: Kết nối nhiều slave song song

c. Kết nối nối tiếp hay kết nối Daisy-Chained

Trong kết nối này, chân SS và SCK của master nối song song ến tất cả các slave.

Chân SDO của slave trước nối ến SDI của slave sau. Chân MOSI của master nối ến SDI

của slave ầu tiên trong chuỗi và MISO ược nối ến SDO của slave cuối cùng trong chuỗi.

Việc truyền dữ liệu từ master ến các slave và dữ liệu master nhận từ slave cuối cùng

ược minh họa với các slave như sau: lOMoARcPSD| 36991220

Hình 10: Kết nối nối tiếp (Daisy-Chained)

d. Kết nối Multi-master

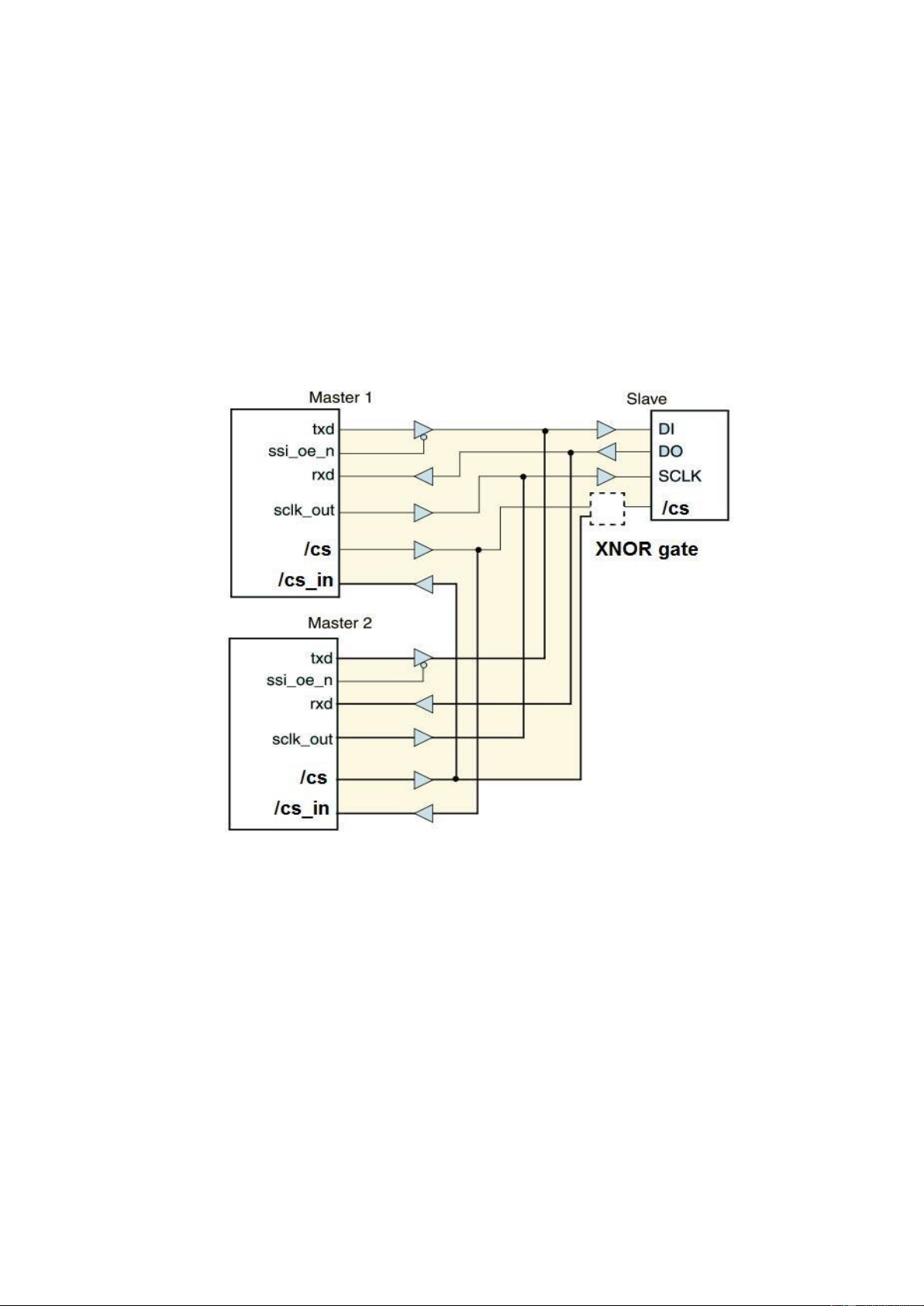

Kết nối nhiều master ộc lập (Independent masters hay Multi-master). Đối với kiểu

kết nối này có nhiều cách kết nối và nhiều vấn ề hơn. e. Kết nối nhiều master song song ến một slave

Với cách kết nối này, phần cứng ngoại vi phải hỗ trợ thêm các tín hiệu iều khiển khác

ể tránh xung ột khi hai master cùng truy xuất ến slave. Ví dụ một trong các cách hỗ trợ

multi-master như trong hình sau:

Hình 11: Kết nối hai master song song ến một slave

Giải pháp ở ây là ngoài các tín hiệu SPI thông thường, phần cứng của hai master SPI

hỗ trợ thêm tín hiệu SS_IN ể master này biết master kia có ang chọn slave hay không.

Đồng thời tín hiệu SS nối ến slave ược mắc qua một cổng XNOR ể nếu hai master cùng

chọn thì tín hiệu SS của slave vẫn không tích cực. Bên cạnh ó, trong mạch trên, ngoài

TXD (chính là tín hiệu MOSI) thì ường SCK cũng phải Hi-Z khi master không chọn slave.

f. Kết nối hai master với nhau

Đây là một dạng khác của multi-master. Trong ó hai master nối trực tiếp với nhau, giao tiếp qua 5 ường. lOMoARcPSD| 36991220

Hình 12: Kết nối hai master với nhau lOMoARcPSD| 36991220

CHƯƠNG 3: THIẾT KẾ

3.1. Sơ ồ khối thiết kế

3.1.1. Mô hình giao tiếp SPI

Serial Peripheral Interface (SPI) là một liên kết dữ liệu nối tiếp, ồng bộ, song công,

là liên kết tiêu chuẩn trên nhiều bộ vi xử lý, vi iều khiển và thiết bị ngoại vi. Nó cho phép

giao tiếp giữa bộ vi xử lý và thiết bị ngoại vi và giao tiếp giữa các bộ xử lý. Hệ thống

SPI ủ linh hoạt ể giao tiếp trực tiếp với nhiều thiết bị ngoại vi có sẵn trên thị trường

Thiết kế SPI Master ã ược thực hiện trong CoolRunner-II CPLD. Thiết kế

CoolRunner-II SPI Master có thể ược sử dụng ể cung cấp bộ iều khiển SPI cho các bộ vi

iều khiển hoặc bộ vi xử lý không chứa giao diện SPI. Sơ ồ khối mức cao ược thể hiện

trong “Hình 13” Giao diện vi iều khiển (microcontroller) ược chọn trong triển khai SPI

Master này dựa trên chu kỳ bus vi iều khiển 8051 phổ biến, nhưng có thể dễ dàng sửa ổi

thành các giao diện vi iều khiển khác

Hình 13: CoolRunner-II SPI Master

3.1.2. Sơ ồ khối thiết mạch giao tiếp SPI

Sơ ồ khối của CoolRunner-II CPLD SPI Master, thể hiện trong “Hình 14” ược chia

thành hai khối chính, giao diện vi iều khiển và giao diện SPI. lOMoARcPSD| 36991220

Hình 14: SPI Master Block Diagram

3.1.3. Sơ ồ SCK Clock Logic

Quá trình này tạo ra ầu ra SCK dựa trên cài ặt CLKDIV, CPHA và CPOL trong thanh

ghi iều khiển SPI. Tần số xung nhịp của tín hiệu SCK ược xác ịnh bằng cách chia nhỏ

xung nhịp ầu vào dựa trên các mục trong thanh ghi iều khiển. Tín hiệu, SCK_INT là

SCK bên trong ược sử dụng ể ồng bộ dữ liệu nối tiếp ra khỏi thiết bị và ược tạo ra liên

tục. Máy trạng thái SPI Control ược ồng bộ hóa với tín hiệu nội bộ này. Tín hiệu SCK_1

ại diện cho SCK khi CPHA = 1 và tín hiệu SCK_0 ại diện cho SCK khi CPHA = 0. Máy

trạng thái iều khiển SPI tạo mặt nạ cho các xung này (CLK0_MASK, CLK1_MASK) ể

SCK ầu ra có mối quan hệ pha chính xác với dữ liệu và ược giữ ở trạng thái không hoạt

ộng khi không có dữ liệu ược chuyển.

Biểu diễn logic cần thiết ể tạo ầu ra tín hiệu SCK tới bus SPI ược thể hiện trong “Hình 15”. lOMoARcPSD| 36991220

Hình 15: SCK Clock Generation Logic

3.2. Mô tả thanh ghi

3.2.1. Thanh ghi của giao tiếp bên trong vi iều khiển

a. SPI Status Register (SPISR)

Thanh ghi này chứa trạng thái của bộ iều khiển SPI. Thanh ghi trạng thái này là chỉ

ọc ngoại trừ một số bit nhất ịnh có thể xóa ược bằng phần mềm. b. SPI Slave Select Register (SPISSR)

Thanh ghi này chứa các bit cho biết dòng chọn phụ nào sẽ ược xác nhận. "1" ở một

vị trí bit chỉ ra rằng bit tương ứng trong bus ầu ra lựa chọn phụ ược xác nhận theo các

thông số kỹ thuật ịnh thời SPI. "0" ở một vị trí bit chỉ ra rằng bit tương ứng trong bus ầu

ra lựa chọn Slave vẫn bị phủ ịnh. Điều này cho phép vi iều khiển chỉ ịnh dòng chọn phụ

nào ược xác nhận trong quá trình truyền dữ liệu SPI.

Lưu ý rằng chỉ có thể xác nhận một dòng chọn phụ trong quá trình truyền dữ liệu

SPI. Điều này phải ược tuân thủ bởi vi iều khiển, việc triển khai phần cứng của thông số

kỹ thuật này không thực thi yêu cầu này. Nói cách khác, nếu vi iều khiển ặt nhiều bit

trong thanh ghi này, nhiều dòng chọn phụ sẽ ược xác nhận cho quá trình truyền SPI.

c. SPI Transfer Data Register (SPITR)

Thanh ghi này chứa dữ liệu ược truyền trên bus SPI trên chân MOSI. Dữ liệu ược

ghi vào thanh ghi này ược xuất trên bus SPI khi bit START trong thanh ghi iều khiển

(SPICR) ã ược xác nhận. Miễn là bit START trong SPICR ược xác nhận, các byte dữ

liệu bổ sung trong thanh ghi này sẽ tiếp tục ược truyền trên bus SPI. lOMoARcPSD| 36991220

Sau khi dữ liệu này ược tải vào thanh ghi dịch chuyển truyền SPI, XMIT_EMPTY

xác nhận và vi iều khiển có thể ặt byte dữ liệu tiếp theo ể truyền trên bus SPI vào thanh

ghi này. Việc ghi dữ liệu vào thanh ghi này sẽ ặt lại cờ XMIT_EMPTY.

XMIT_EMPTY phải ược phủ ịnh và START phải ược xác nhận trước khi máy trạng

thái SPI bắt ầu truyền dữ liệu trên bus SPI. d. SPI Receive Data Register (SPIRR)

Thanh ghi này chứa dữ liệu nhận ược từ bus SPI trên chân MISO. Khi một byte dữ

liệu ã ược nhận từ bus SPI và ược chuyển ến SPIRR, cờ RCV_FULL xác nhận. Sau ó vi

iều khiển ọc dữ liệu từ SPIRR ặt lại cờ RCV_FULL. Bởi vì dữ liệu ược tải từ thanh ghi

dịch chuyển nhận SPI ến SPIRR, vi iều khiển có toàn bộ quá trình truyền SPI 8 bit ể ọc dữ liệu từ SPIRR.

3.2.2. Thanh ghi của giao tiếp SPI

SPI Shift Registers bao gồm SPI Transmit Shift Register và SPI Receive Shift Register

a. SPI Transmit Shift Register

Thanh ghi dịch chuyển truyền SPI là một thanh ghi dịch chuyển có thể tải ược 8 bit

chứa dữ liệu SPI. Thanh ghi dịch chuyển này ược tải từ Thanh ghi truyền SPI (SPITR)

thông qua tín hiệu tải do máy trạng thái iều khiển SPI tạo ra và ược tạo xung nhịp bởi

cạnh lên của SCK_INT. Dữ liệu chuyển ra ngoài là dữ liệu MOSI.

SCK_OUT là một SYS_CLK trễ từ SCK_INT. Do ó, cần phải trì hoãn dữ liệu ược

chuyển ra khỏi thanh ghi dịch chuyển truyền SPI bởi một SYS_CLK cũng như ể duy trì

mối quan hệ giữa MOSI và SCK_OUT. lOMoARcPSD| 36991220

Hình 16: SPI Transmit Shift Register

b. SPI Receive Shift Register

Một thanh ghi dịch chuyển riêng biệt ược sử dụng ể nhận dữ liệu MISO vì pha xung

và cực tính của ầu ra SCK có thể thay ổi dựa trên mỗi giao dịch. Thanh ghi dịch chuyển

nhận SPI ược ặt xung nhịp trên cạnh lên của SCK bên ngoài. Bộ bit RCV_CPOL trong

thanh ghi iều khiển cho phép vi iều khiển chỉ ịnh cạnh nào của dữ liệu MISO ến SCK

bên ngoài ược lấy mẫu. Điều này cho phép sự linh hoạt trong việc xử lý tất cả các loại

thiết bị SPI Slave khác nhau vì một số SPI Slave sẽ ồng bộ dữ liệu ở cạnh lên của SCK

trong khi còn lại sẽ ồng bộ dữ liệu ở cạnh xuống của SCK. Nếu một phụ xung nhịp dữ

liệu trên cạnh xuống của SCK, thì RCV_CPOL phải ược ặt thành "1" ể CoolRunner-II

SPI Master sẽ ồng bộ dữ liệu trên cạnh lên của SCK. Nếu một bộ phận phụ xử lý dữ liệu

trên cạnh lên của SCK, thì RCV_CPOL phải ược ặt thành "0" ể CoolRunner-II SPI

Master ồng bộ hóa dữ liệu trên cạnh xuống

của SCK. Điều này giúp loại bỏ mọi vấn ề về thời gian thiết lập và lưu giữ.

Nếu Slave hoạt ộng theo ặc iểm kỹ thuật SPI cho CPHA và CPOL, RCV_CPOL sẽ

bằng "1" bất cứ khi nào CPHA và CPOL bằng nhau và "0" nếu không.

Trong quá trình triển khai thực tế, hai thanh ghi ầu vào ược sử dụng ể lấy mẫu MISO,

một thanh ghi có xung nhịp ở cạnh lên của SCK, thanh ghi còn lại có xung nhịp ở cạnh

xuống của SCK. Đầu ra của hai thanh ghi này sau ó ược ghép với bit RCV_CPOL ược

sử dụng làm dòng chọn. Đầu ra của bộ ghép kênh này sau ó sẽ trở thành ầu vào cho thanh

ghi dịch chuyển nhận SPI ược ặt xung nhịp trên cạnh lên của SCK bên ngoài. Sử dụng

phương pháp triển khai này loại bỏ clock ghép kênh bên trong CPLD. Xung clock ghép

kênh trong CPLD ặt thời gian trễ giữa SCK và dữ liệu ầu vào thực tế vào thanh ghi dịch

chuyển. Sự chậm trễ này trên SCK có thể ặt ra yêu cầu về thời gian lưu trữ dữ liệu bổ

sung trên thiết bị phụ mà không mong muốn. Do ó, thay vào ó, người ta ã quyết ịnh ghép

kênh dữ liệu, do ó loại bỏ sự cần thiết phải chỉ ịnh yêu cầu thời gian lưu giữ trên thiết bị phụ. lOMoARcPSD| 36991220

Hình 17: SPI Receive Shift Register and MISO Input Data Registers

3.3. Sơ ồ thuật toán thiết kế

FlowChart ể cấu hình và thực hiện giao dịch SPI cho CoolRunner-II SPI Master ược

thể hiện trong “Hình 18”. Vì SPI là một giao thức truyền thông song công nên dữ liệu

ược nhận trong khi dữ liệu ược truyền i.

Lưu ý rằng nếu lỗi SPI xảy ra cho thấy rằng một Master khác ã chiếm quyền iều

khiển bus, thì hoạt ộng của hệ thống phải ược xác minh. Lưu ồ hiển thị liên tục thăm dò

PIERR (SPI Error Bit) trong thanh ghi trạng thái ể xác ịnh thời iểm lỗi SPI ã ược sửa

chữa. Vì lỗi SPI cũng xác nhận một ngắt (nếu ngắt ã ược bật), một giải pháp thay thế cho

việc thăm dò thanh ghi trạng thái SPI (SPISR) là phục vụ ngắt ể xác ịnh xem lỗi SPI ã

ược sửa hay chưa. Một trong hai luồng này có thể không phải là luồng hoạt ộng mà hệ

thống yêu cầu khi xảy ra lỗi SPI; nhà thiết kế nên xác ịnh các hoạt ộng chính xác ể thực

thi khi lỗi SPI xảy ra dựa trên các yêu cầu hệ thống. lOMoARcPSD| 36991220

Hình 18: SPI Master Transaction Flow Chart

CHƯƠNG 4: ĐÁNH GIÁ QUA TESTBENCH lOMoARcPSD| 36991220

4.1. Thiết kế chương trình

Hình 19: Hệ thống sử dụng giao tiếp SPI

Chương trình giao tiếp bên trong hệ thống sử dụng giao tiếp SPI theo sơ ồ trên hình

vẽ, kèm với các khối chương trình khác có nhiệm vụ tạo xung sclk và xử lí các tín hiệu liên tục.

a. Khối khai báo tín trong hệ thống module SPI_Master ( output reg [7:0] out_data, output mosi, output miso, output sclk, output [7:0] mastershift, output [7:0] slaveshift, input clk, input cs, input wr, input rd, input [7:0] in_data, input [1:0] div );

b. Khối khai báo các reg và wire sử dụng trong hệ thống reg busy =0; reg sclk =0; reg [4:0] sclk_cnt=0; reg [4:0] div_cnt=4'b0001; reg [7:0] mastershift; reg [7:0]

slaveshift; reg out; reg miso = lOMoARcPSD| 36991220

0; reg mosi = 0; wire mosi_buf;

wire miso_buf; wire [4:0]clk_div;

assign mosi_buf = mastershift[7];

assign miso_buf = slaveshift[7]; c.

Khối tạo xung sclk, chứa bộ chia xung ể tạo ra xung sclk từ xung clk ban ầu always @(posedge clk) begin if (!busy) begin if (cs && wr) begin mastershift <= in_data; slaveshift <= 8'b0; busy<=1; out <=0; end else if (cs && rd) begin busy<=1; out <=1; end end else begin if (!out) out_data <=

8'bxxxxxxxx; div_cnt<=div_cnt+1;

if (div_cnt>=clk_div) begin

div_cnt<=1; sclk<=!sclk; if

(!sclk) sclk_cnt<=sclk_cnt+1; if (sclk_cnt==8) begin

busy<=0; sclk_cnt<=0; if (out)

out_data<=mastershift; end end lOMoARcPSD| 36991220 end end endmodule

d. Khối giao tiếp SPI always @(posedge sclk)

begin mosi = mosi_buf; miso = miso_buf;

mastershift = (mastershift<<1) | miso;

slaveshift = (slaveshift<<1) | mosi;

end assign mosi_buf = mastershift[7];

assign miso_buf = slaveshift[7];

4.2. Chương trình testbench tổng quát `timescale 1ns / 1ps module SPIMaster_Test; wire [7:0] out_data; wire mosi; wire miso; wire sclk; wire [7:0] mastershift; wire [7:0] slaveshift; reg clk; reg cs; reg wr; reg rd; reg [7:0] in_data; reg [1:0] div;

// Instantiate the Unit Under Test (UUT)

SPI_Master uut ( out_data, mosi, miso,

sclk, mastershift, slaveshift, clk, cs, wr, rd, in_data, div ); initial begin clk=0; forever #10 clk=!clk; end initial begin rd=0; cs=0; wr=0; div=0; in_data= 8'b11001010; lOMoARcPSD| 36991220 cs=1; wr=1; #20; cs=0; wr=0; #1000; in_data= 8'b01010001; cs=1; wr=1; #20; cs=0; wr=0; #1000; cs=1; rd=1; #20; cs=0; rd=0; #1000; in_data= 8'b01010001; cs=1; wr=1; #20; cs=0; wr=0; end endmodule

4.3. Mô tả các trường hợp test a.

Testcase 1: Ghi dữ liệu từ in_data = 8’b11001010 ra Slave

in_data= 8'b11001010; cs=1; wr=1; #20; cs=0; wr=0; #1000; b.

Testcase 2: Ghi dữ liệu ra từ in_data = 8’b01010001 ra

Slave in_data= 8'b01010001; cs=1; wr=1; #20; cs=0; wr=0; #1000; c.

Testcase 3: Đọc dữ liệu từ thanh ghi Slave và xuất ra

out_data cs=1; rd=1; #20; cs=0; rd=0; #1000;

d. Testcase 4: Ghi dữ liệu từ in_data = 8’b01010001 ra Slave

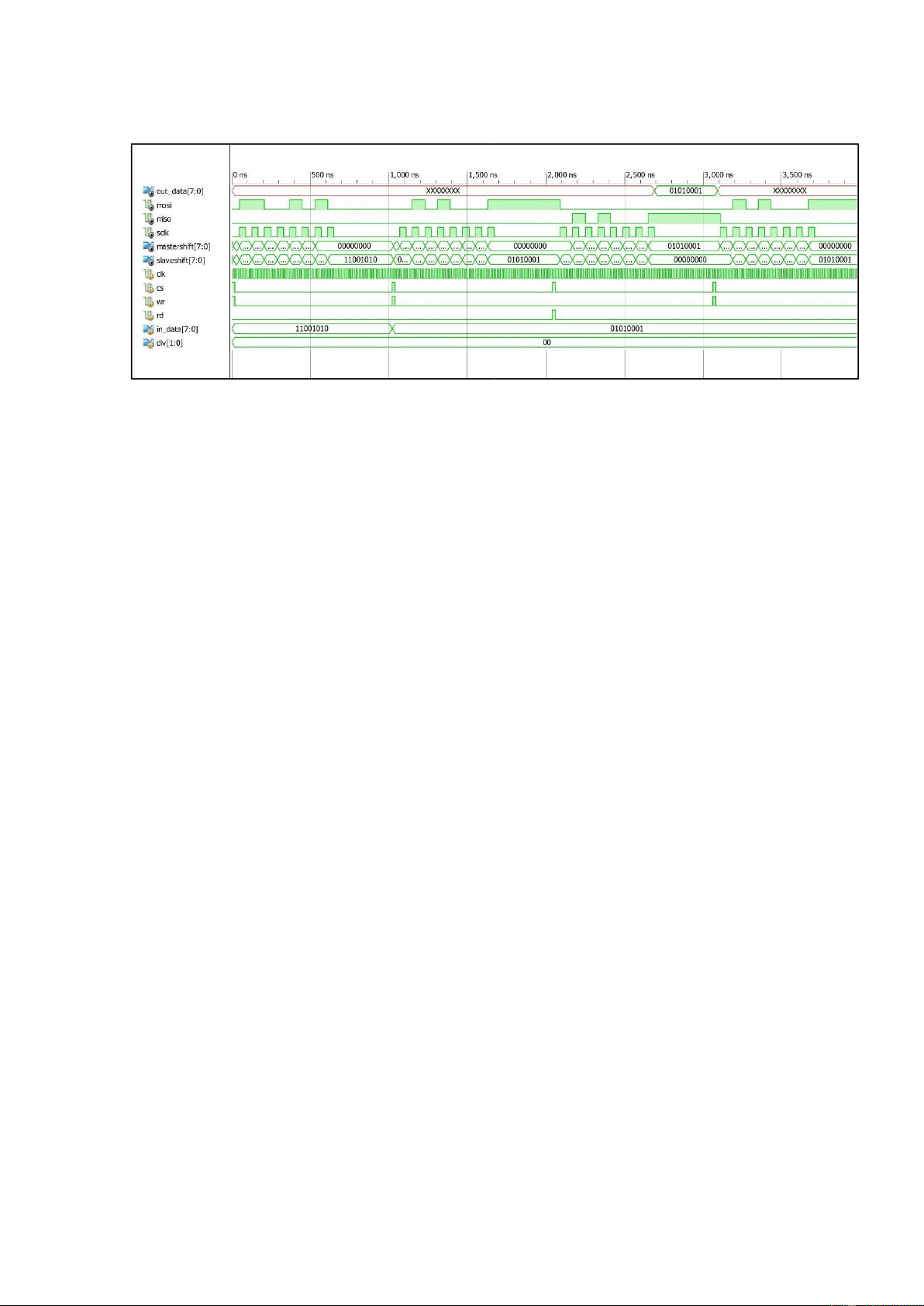

in_data= 8'b01010001; cs=1; wr=1; #20; cs=0; wr=0; lOMoARcPSD| 36991220 4.4 .Kếtquả Hình20:Kếtquả

4.5. Nhận xét và ánh giá

a. Nhận xét Testbench:

Các tín hiệu ngõ vào và ngõ ra của mô hình thiết kế gồm có: clk, cs, wr, rd, div,

in_data, out_data, miso, mosi, sclk, mastershift, slaveshift.

Testcase 1: in_data = 8’b11001010, khi có xung lên cs và wr mastershift nhận giá trị

từ in_data, chương trình tạo 8 xung sclk theo tương ứng gấp 4 lần xung clk ban ầu, và

xung sclk ầu tiên bắt ầu ở vị trí clk ầu tiên sau khi cs xuống lại mức thấp. Với mỗi xung

lên sclk, miso thay ổi trạng thái bằng mastershift[7], mosi luôn bằng 0, slaveshift nhận

miso vào bit cuối cùng. Kết quả ở slaveshift bằng in_data 11001010.

Testcase 2: in_data = 8’b01010001, khi có xung lên cs và wr mastershift nhận giá trị

từ in_data, chương trình tạo 8 xung sclk theo tương ứng gấp 4 lần xung clk ban ầu, và

xung sclk ầu tiên bắt ầu ở vị trí clk ầu tiên sau khi cs xuống lại mức thấp. Với mỗi xung

lên sclk, miso thay ổi trạng thái bằng mastershift[7], mosi luôn bằng 0, slaveshift nhận

miso vào bit cuối cùng. Kết quả ở slaveshift bằng in_data 01010001.

Testcase 3: Khi có xung lên cs và rd, chương trình tạo 8 xung sclk theo tương ứng

gấp 4 lần xung clk ban ầu, và xung sclk ầu tiên bắt ầu ở vị trí clk ầu tiên sau khi cs xuống

lại mức thấp. Với mỗi xung lên sclk, mosi thay ổi trạng thái bằng slaveshift[7], miso luôn

bằng 0, mastershift nhận mosi vào bit cuối cùng. Kết quả ở mastershift = 01010001, out_data = 01010001.

Testcase 4: in_data = 8’b01010001, khi có xung lên cs và wr mastershift nhận giá trị

từ in_data, chương trình tạo 8 xung sclk theo tương ứng gấp 4 lần xung clk ban ầu, và lOMoARcPSD| 36991220

xung sclk ầu tiên bắt ầu ở vị trí clk ầu tiên sau khi cs xuống lại mức thấp. Với mỗi xung

lên sclk, miso thay ổi trạng thái bằng mastershift[7], mosi luôn bằng 0, slaveshift nhận

miso vào bit cuối cùng. Kết quả ở slaveshift bằng in_data 01010001. b. Đánh giá qua Testbench Ưu iểm:

- SPI có cấu tạo phần cứng ơn giản, truyền dữ liệu thông dịch chuyển dữ liệu.

- Slave dùng chung bộ xung truyền dữ liệu của Master, do ó không cần quan tâm ến ộ

chính xác của bộ dao ộng. Nhược iểm:

- Không có chức năng kiểm tra nếu dữ liệu truyền bị lỗi.

- Chỉ kết nối với từng Slave ộc lập. lOMoARcPSD| 36991220

CHƯƠNG 5: KẾT LUẬN 5.1. Những ưu iểm của

SPI - Truyền thông song công. - Lượng dữ liệu

ưa vào cao hơn giao thức I2C.

- Không giới hạn ở 8-bit word trong trường hợp truyền bit.

- Tùy ý lựa chọn size thông tin nội dung và mục ích. - Giao tiếp phần cứng ơn giản.

- Yêu cầu nguồn tiêu chuẩn thấp hơn I2C mạch ít cồng kềnh. - Không có sự iều chỉnh hay các chế

ộ truyền thất bại liên quan.

- Slave sử dụng clock của master và không cần ộ chính xác của bộ dạo ộng (oscillator).

- Không cần thiết bộ truyền nhận.

- Nhiều nhất là một dây tín hiệu bus duy nhất trên thiết bị (CS), tất cả dây khác ược chia sẻ.

5.2. Những nhược iểm của SPI

- Yêu cầu nhiều dây trên IC hơn I2C. - Không ấn ịnh

ịa chỉ, tín hiệu chip select ược yêu cầu trên bus ược chia sẻ. - Không có luồng iều khiển phần cứng. - Không có chế ộ nhận biết slave.

- Các bus multi-master thì ít và bất tiện, thường sử dụng giới hạn slave ơn.

- Không có một tiêu chuẩn chính thức, không có sự phê duyệt phù hợp.

- Chỉ làm việc ở khoảng cách ngắn hơn so với Rs232, Rs485 hay CAN.

TÀI LIỆU THAM KHẢO

1. https://en.wikipedia.org/wiki/Serial_Peripheral_Interface 2. Datasheet: CoolRunner-II Serial Peripheral Interface Master,

https://www.xilinx.com/support/documentation/application_notes/xapp386.pdf

3. Giao tiếp SPI, https://deviot.vn/blog/giao-tiep-spi.74706311 4. Introduction to SPI

Interface, https://www.analog.com/en/analog-dialogue/articles/introduction-to-spi- interface.html

5. SPI: Serial Port Interface,https://wiki.analog.com/resources/eval/sdp/sdp- b/peripherals/spi lOMoARcPSD| 36991220

6. SPI, https://www.fpgakey.com/wiki/details/13