Preview text:

lOMoARcPSD| 40651217 MoARc PSD| 40651217 I. Lý thuyết

1. Chương 1. Hệ đếm, tổng quan về máy tính

- Khái niệm hệ đếm, phân biệt hệ đếm có vị trí và hệ đếm không vị trí

- Khái niệm: cơ số, trọng số, tính giá trị của số với các hệ đếm khác nhau

- Chuyển đổi hệ đếm: hệ 16, hệ 2, hệ 10

- Khái niệm kiến trúc máy tính, tổ chức máy tính, cấu trúc và chức năng của máy tính

- Các thành phần của máy tính và ý nghĩa của chúng

- Các thành phần của CPU và ý nghĩa của chúng

2. Chương 2. Lịch sử máy tính

- Khái quát các giai đoạn phát triển của máy tính: bao nhiêu thế hệ, cơ sở để chia các thế

hệ khác nhau, công nghệ phần cứng của mỗi thế hệ, định luật Moore.

- Nêu đặc điểm nổi bật của mỗi thế hệ máy tính.

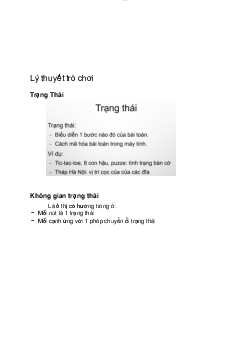

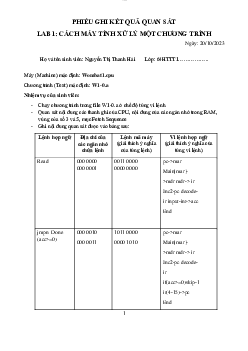

3. Chương 3. Hoạt động của máy tính – Hệ thống bus

a. Hoạt động của máy tính:

- Nêu các thành phần cơ bản của máy tính

- Hoạt động chính của máy tính: chu kỳ lệnh, các bộ phận tham gia vào quá trình truy

xuất và thực thi lệnh: CPU, RAM, thanh ghi, bus. Các bước trong chu kỳ lệnh - Các loại lệnh khác nhau.

- Các thanh ghi và ý nghĩa của mỗi thanh ghi tham gia vào hoạt động của máy tínhb. Hệ

thống kết nối trong máy tính

- Hệ thống kết nối cần đáp ứng những kết nối nào trong máy tính? Các loại tín hiệu

ra/vào mỗi module và ý nghĩa.

- Hệ thống bus, nguyên lý, cấu trúc. Ý nghĩa từng loại bus. Nhược điểm của bus.

- Các đặc tính của bus: chuyên dụng/ghép kênh, định thời đồng bộ/không đồng bộ, hệ

thống bus phân cấp, phân xử bus, … lOMoARcPSD| 40651217

4. Chương 4. Bộ nhớ cache

a. Hệ thống nhớ trong máy tính

- Phân cấp bộ nhớ trong máy tính, các phương pháp truy cập, các công nghệ bộ nhớ, các

phương pháp đánh giá hiệu năng b. Bộ nhớ cache

- Nguyên lý, cấu trúc, phương pháp truy cập.

- Đặc tính của bộ nhớ cache: kích thước cache, kích thước khối, các phương pháp ánh

xạ,thuật toán thay thế, cache thống nhất/phân chia, chính sách ghi, cache nhiều cấp, …

- Tính toán các phương pháp ánh xạ

5. Chương 5. Bộ nhớ trong

- Các công nghệ bộ nhớ trong: DRAM/SRAM, ROM, đặc điểm BN trong- Các loại bộ

nhớ ROM: ROM, PROM,… Phân biệt và ứng dụng của mỗi loại - Tổ chức chip nhớ:

- Các loại công nghệ bộ nhớ RAM: DRAM, SDRAM, DDR-SDRAM.

- Nguyên lý phát hiện sửa lỗi Hamming SEC, SEC-DED

6. Chương 6. Bộ nhớ ngoài

- Nguyên lý đĩa cứng, thành phần đĩa cứng: platter, đầu đọc

- Tổ chức đĩa cứng: track, sector, nội dung sector, phương pháp bố trí đĩa, cylinder

- Đặc tính đĩa cứng: đĩa có đầu cố định/di chuyển, đĩa cố định/đĩa tháo được, đĩa 2 mặt,

đặc tính đầu đọc/ghi, …

- Nguyên lý bộ nhớ SSD, công nghệ, đặc tính, ưu điểm so với HDD

- Tổ chức SSD, phương pháp đọc/ghi dữ liệu

- Hai vấn đề cần khắc phục của SSD 7. Chương 9. Khối ALU

- Mã hóa số nguyên trong máy tính: không dấu, bù 2, dấu-độ lớn. Miền giá trị của các

dạng biểu diễn, cách tính giá trị, nguyên tắc mở rộng phạm vi.

- Các phép toán với số nguyên: cộng, trừ, nhân, chia. Nguyên tắc phát hiện tràn, nguyên

tắc đổi dấu trong phép nhân và phép chia

- Mã hóa số thực: số dấu chấm động 32b, 64b, 128b. Một số mã đặc biệt. 8. Chương 10. Tập lệnh lOMoARcPSD| 40651217

- Khái niệm lệnh, hoạt động, tập lệnh, toán hạng, …

- Cấu trúc lệnh máy: mã lệnh và trường địa chỉ. Đặc điểm của tập lệnh 1 địa chỉ, 2 địa

chỉ, 3 địa chỉ và ưu điểm, nhược điểm. - Các loại lệnh máy, các toán hạng 9. Chương

11. Chế độ định địa chỉ

- Các chế độ định địa chỉ, ưu điểm và nhược điểm 10. Chương 12. CPU

- Cấu trúc CPU, các loại thanh ghi và ý nghĩa

- Kỹ thuật đường ống, các loại xung đột trong kỹ thuật đường ống II. Bài tập

Chương 1. Bài tập chuyển đổi hệ đếm

1. Biểu diễn số thập phân sang nhị phân a. 10.25 b. 25.125 c. 124.75

2. Biểu diễn số nhị phân sang thập phân a. 100101.011 b. 100011111.01 c. 110110.1 d. 1101.101

3. Biểu diễn số thập phân sang thập lục phân a. 54.123 b. 142.5 c. 101.25

4. Biểu diễn số thập lục phân sang thập phân a. AB.C b. 10D.E lOMoARcPSD| 40651217 c. A98.03

5. Biểu diễn số nhị phân sang thập lục phân a. 1001001.0010 b. 11110000.11 c. 101101100.001

6. Biểu diễn số thập lục phân sang nhị phân a. AB.C12 b. 14D.E c. A78.03

8. Chuyển các số sau sang hệ thập phân a. 111102 b. 11010102 c. 5438 d. A12316 e. 101101.0112 f. 4E1B.2C16

9. Chuyển đổi các số sau sang hệ nhị phân a. 84310 b. 84316 c. 34.62510 d. 541. A116 e. 12.2510

f. A4 B3C2.2916

10. Chuyển đổi các số hệ nhị phân sau thành số hệ thập lục phân a. 1100101.0112 b. 11001.112 c. 1100000101.010012 d. 1101.012

Chương 3. Hoạt động của máy tính – Hệ thống bus

1. Bus địa chỉ có số đường là 22 đường. Dung lượng tối đa của bộ nhớ là bao nhiêu

nếu kích thước mỗi ngăn nhớ là 16 bit?

2. Bus địa chỉ có số đường là 26 đường. Xác định dung lượng bộ nhớ tối đa CPU có

thể quản lý được biết kích thước ngăn nhớ là 32b? lOMoARcPSD| 40651217

Chương 4. Bài tập ánh xạ

1. BN Chính dung lượng 8GB, cache 16MB, sử dụng ánh xạ trực tiếp. Kích thước từ

(ngăn nhớ) 8B (64b). Khối = 128 từ.

- Xác định số khối trong bn chính

- Xác định số đường trong bn cache

- Khối 60840 sẽ được ánh xạ vào đường nào trong bộ nhớ cache

- Xác định kích thước địa chỉ bộ nhớ, số bít của các trường trong địa chỉ từ

2. Xét bộ nhớ cache 16KB, sử dụng ánh xạ trực tiếp với kích thước khối là 256B.

Dung lượng BN chính là 128KB. Xác định định dạng địa chỉ bộ nhớ (số bít địa chỉ,

được chia thành bao nhiêu trường và kích thước các trường). Biết mỗi ngăn nhớ có kích thước 1B

3. Xét bộ nhớ chính dung lượng 4 GB, chia thành các khối kích thước 32B. Biết rằng

kích thước ngăn nhớ (từ) là 2B. Giả sử bộ nhớ cache ánh xạ trực tiếp có 512 đường. a.

Xác định dung lượng bộ nhớ cache

b. Xác định các trường của địa chỉ bộ nhớ và kích thước mỗi trường.

4. Cho máy tính có dung lượng bộ nhớ chính: 32GB; Cache: 32KB; Line: 128B; kích

thước ngăn nhớ: 4B. Hãy tính số bit của các trường địa chỉ bộ nhớ trong các trường hợp sau: a. Ánh xạ trực tiếp b. Ánh xạ kết hợp

c. Ánh xạ tập kết hợp 4 đường.

5. Cho bộ nhớ cache 128 đường, sử dụng ánh xạ trực tiếp. Khối 345 được ánh xạ vào đường nào?

6. Cho bộ nhớ cache 256 đường, sử dụng ánh xạ kết hợp. Khối 345 được ánh xạ vào đường nào?

7. Cho bộ nhớ cache 512 đường, sử dụng ánh xạ tập kết hợp 4 đường. Khối 1103 được

ánh xạ vào đường nào?

Chương 5. Bài tập BN RAM, mã sửa lỗi

1. Cho chip nhớ có 15 chân địa chỉ, 8 chân dữ liệu. Tính dung lượng chip nhớ. lOMoARcPSD| 40651217

2. Cho chip nhớ DRAM: 20 chân địa chỉ, 4 chân dữ liệu. Tính kích thước ngăn nhớ và dung lượng chip nhớ.

3. Bộ nhớ RAM gồm 8 chip nhớ mắc đan xen, mỗi chip có 8 chân dữ liệu và 32 chân địa

chỉ. Tính dung lượng bộ nhớ

4. Cho dữ liệu 1110 0010, xác định mã Hamming SEC của dữ liệu đó, viết từ lưu trữ.

5. Cho dữ liệu 1010 1101, xác định mã Hamming SEC của dữ liệu đó, viết từ lưu trữ.

6. Cho từ lưu trữ được đọc ra từ bộ nhớ như sau: 0101 1011 0110. Xác định xem từ này

có bị lỗi không, sửa lỗi nếu có thể?

7. Cho từ lưu trữ được đọc ra từ bộ nhớ như sau: 1011 0000 1111. Xác định xem từ này

có bị lỗi không, sửa lỗi nếu có thể? Chương 6. Bài tập

1. Cho đĩa cứng HDD có các thông số sau: - Dung lượng: 500GB - Số track/cylinder = 50 - Số cylinder = 5000 - Sector = 2048B

Xác định số sector/track của đĩa cứng trên

2. Cho ổ cứng HDD sử dụng công nghệ đĩa 2 mặt. Ổ cứng có các thông số sau: - Dung lượng: 1TB - Số cylinder = 32.768 - Sector = 512B

Xác định số đĩa cứng của ổ cứng trên.

3. Cho ổ cứng HDD gồm 4 đĩa hai mặt, xác định số track trong một cylinder.

4. Tính dung lượng ổ cứng HDD gồm 2 đĩa 2 mặt, 65536 cylinder, mỗi track có 64 sector, mỗi sector có 512B

5. Ổ cứng gồm 10 track trong một cylinder. Tính số lượng đĩa của ổ biết ổ dùng công nghệ đĩa hai mặt

6. Ổ cứng gồm 10 track trong một cylinder. Tính số lượng đầu đọc/ghi của ổ. lOMoARcPSD| 40651217 Chương 9.

1. Biểu diễn các số thập phân sau sang dạng bù 2 8b và dấu-độ lớn 8b a. 123 b. -110 c. 12 e. -127 d. -129 f. 62

2. Xác định miền giá trị của các dạng biểu diễn sau:

a. dấu-độ lớn 8b (tổng quát dấu-độ lớn n bit)

b. bù hai 8b (tổng quát bù hai n bit)

c. số nguyên ko dấu 8b (tổng quát số nguyên ko dấu n bit) 3. Tính toán giá trị của các

số biểu diễn dạng bù 2 8b sau a. 1000 0000 b. 1000 1000 c. 0110 1000 d. 1001 1110

4. Tính toán giá trị của các số biểu diễn dạng dấu độ lớn-8b sau a. 1000 0000 b. 1000 1000 c. 0110 1000 d. 1001 1110

5. Thực hiện phép toán sau biết các số biểu diễn dưới dạng số bù 2 8b (chú ý kiểm tra tràn) a. 1000 1001 + 0100 1000 b. 1111 0000 – 0111 0001 c. 0100 1111 + 0100 0000

6. Nêu nguyên tắc tràn của các phép toán với số nguyên bù 2

7. Biểu diễn các số thập phân sau sang dạng số thực dấu chấm động 32ba. 10.125 b. -112.375 lOMoARcPSD| 40651217 c. 25.5

8. Cho các số biểu diễn trong máy tính với định dạng số thực dấu chấm động 32b như

sau. Xác định giá trị thập phân tương ứng của số đó a. 1100 0011 1110 1000 0000 0000 0000 0000

b. 0011 1110 1110 1100 0000 0000 0000 0000