Preview text:

lOMoAR cPSD| 59285474

ĐẠI HỌC QUỐC GIA THÀNH PHỐ HỒ CHÍ MINH

TRƯỜNG ĐẠI HỌC CÔNG NGHỆ THÔNG TIN KHOA

KỸ THUẬT MÁY TÍNH

BÁO CÁO BÀI THỰC HÀNH LAB1 THIẾT KẾ HỆ THỐNG SoC

Sinh viên thực hiện

NGUYỄN THƯỜNG QUÂN – 21522498

Giảng viên hướng dẫn Phạm Thanh Hùng

Tp. Hồ Chí Minh, ngày 13 tháng 4 năm 2024 Ojectives:

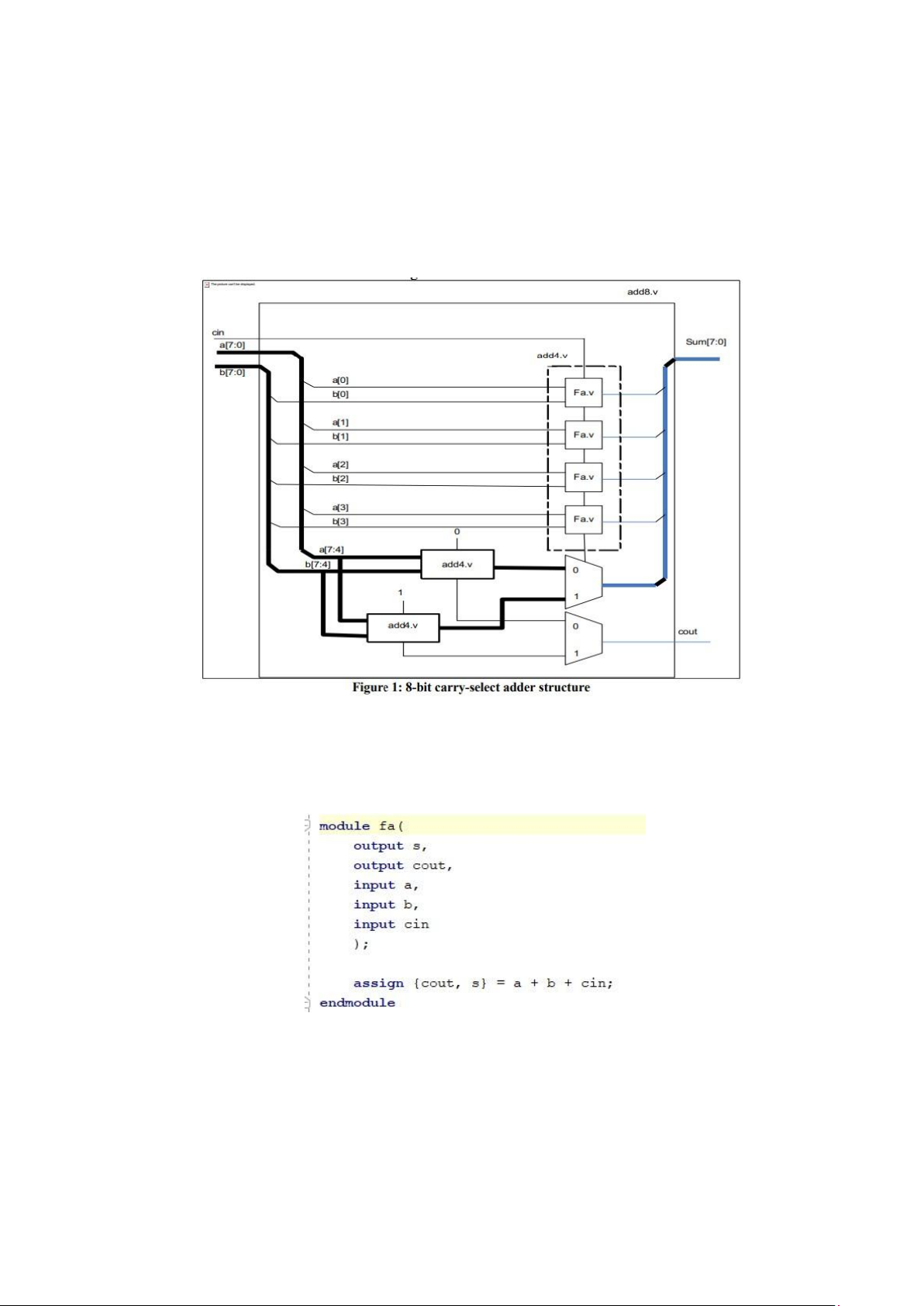

- Designing and testing an 8-bit carry-select adder using Verilog. lOMoAR cPSD| 59285474

- Simulate the operation of the adder design by executing the simulation on Vivado. - Design a FIFO.

- Simulate and debug the FIFP design using Vivado. I.

Design an 8-bit carry-select adder using Verilog

We have 3 module design: fa.v, add4.v, add8.v 1. Module fa – fulladder

Design a module fulladder 1 bit using behavioral model:

2. Module add4 – 4 fulladder lOMoAR cPSD| 59285474 3. Module add8

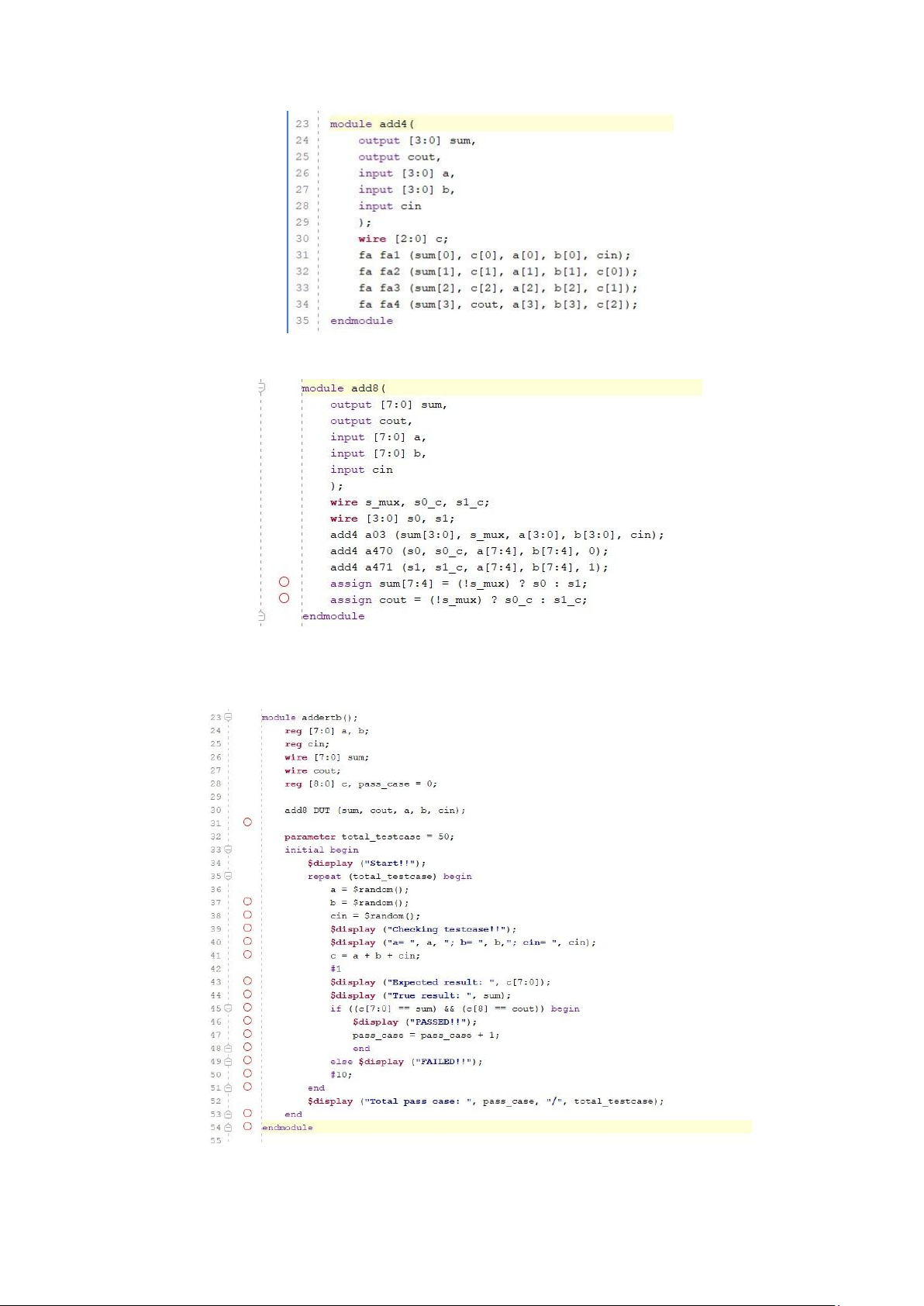

This also the top-level module of design 4. Testbench – addertb

In this testbench, we will drive 3 input a, b, cin with random value. We'll compare the

result from module with variable c = a + b + cin. If equal, print "PASSED" to console. lOMoAR cPSD| 59285474

Unless print "FAILED". Variable pass_case is used to check total pass case of total test case we have. II. Simulation adder

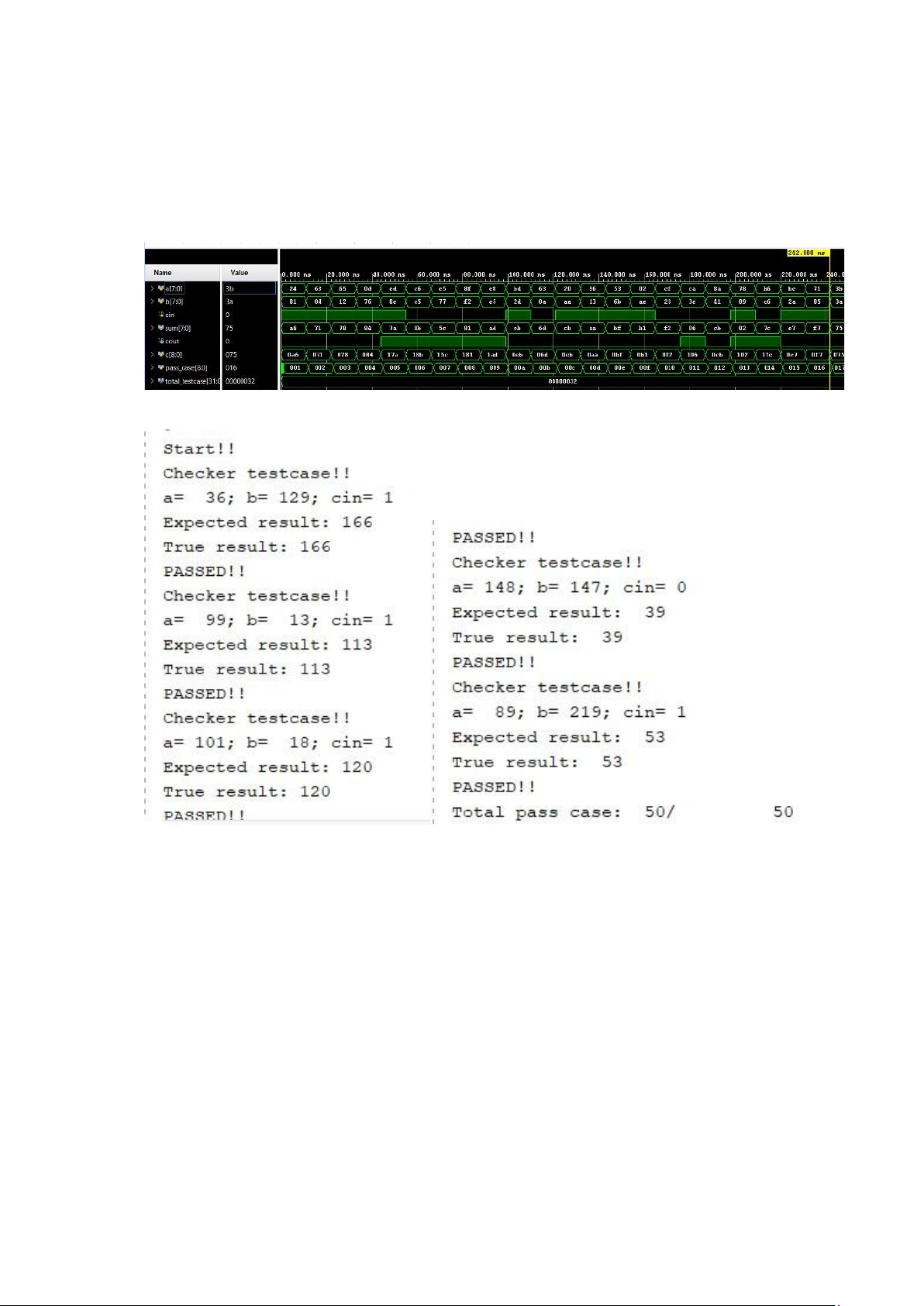

Run simulation the adder design, we have waveform result:

With checker in module testbench, we will check the result in Tcl console: III. Design FIFO

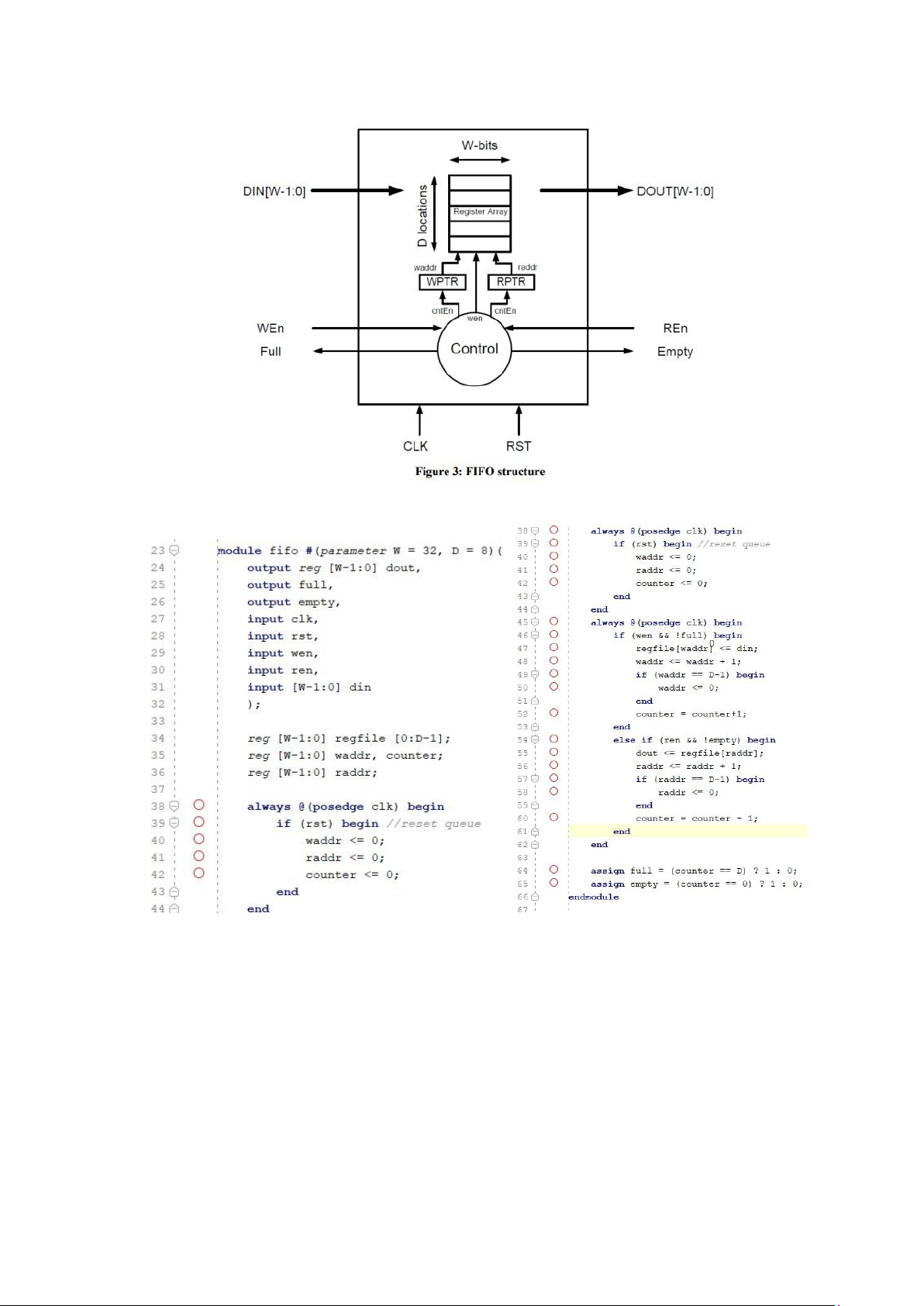

FIFO (First In – First Out) is a queue that the first data to be written is the first data will be read out.

In this lab, we will desgin a generic DxW-bit FIFO. - D (depth) = 8 - W (width) = 32 lOMoAR cPSD| 59285474

We will design the FIFO in only one module:

When reset signal = 1 (synchronous active-high), write and read pointer (waddr and raddr) reset to zero, counter = 0.

Waddr and raddr is the pointer of this FIFO. Imagine, raddr is the head of queue and waddr is the tail of queue.

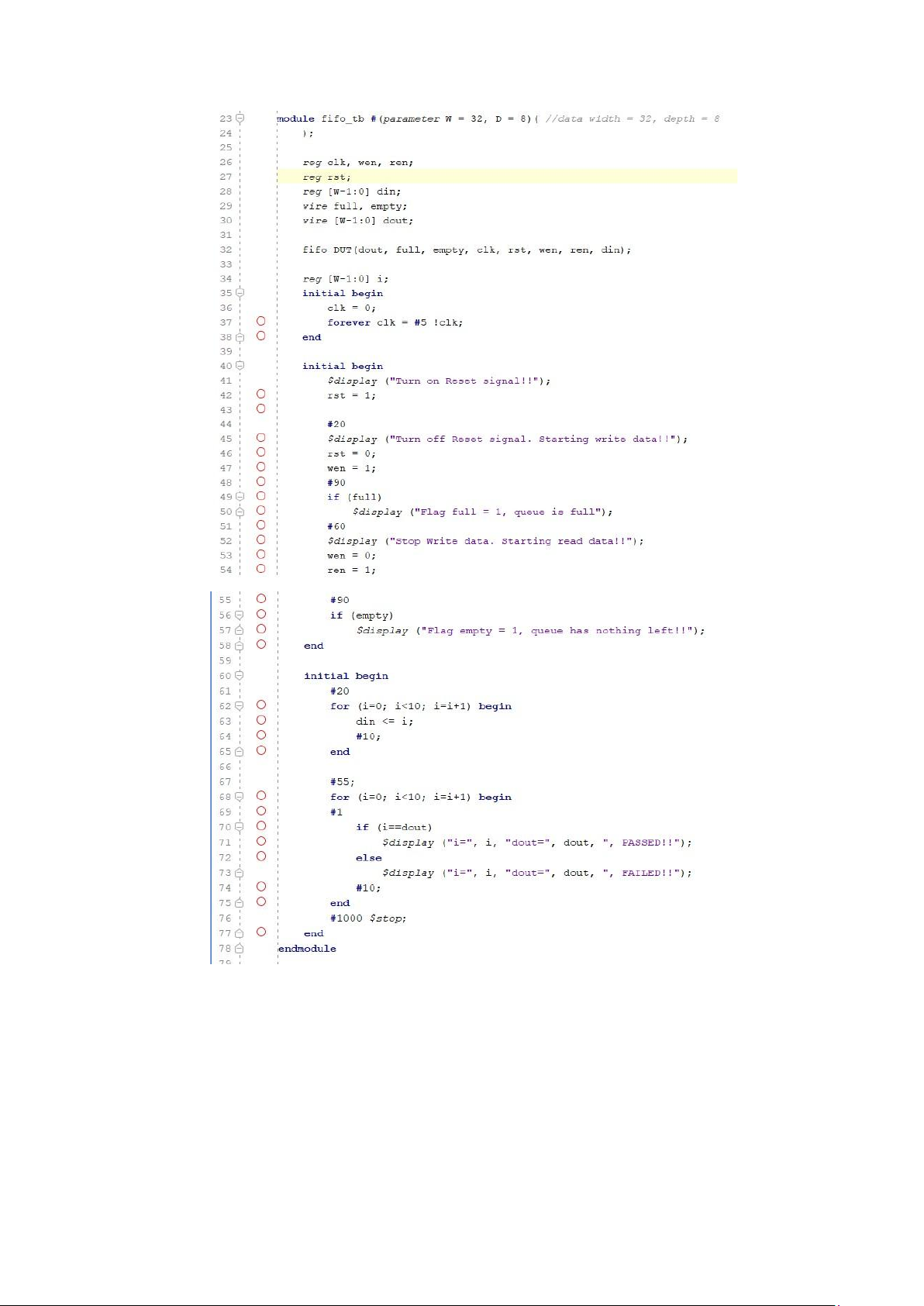

The full flag is on when the counter reaches Depth, the empty flag is on when the counter downs to Zero. Testbench: lOMoAR cPSD| 59285474

In this testbench, we will drive input "din" with the value from 0 to 10. We set the fit time

delay to rise and fall these signals.

When reading data (dout rising), we will compare that with the same value of input. If

equal, print PASSED to console. Unless print FAILED. IV. Simulation FIFO

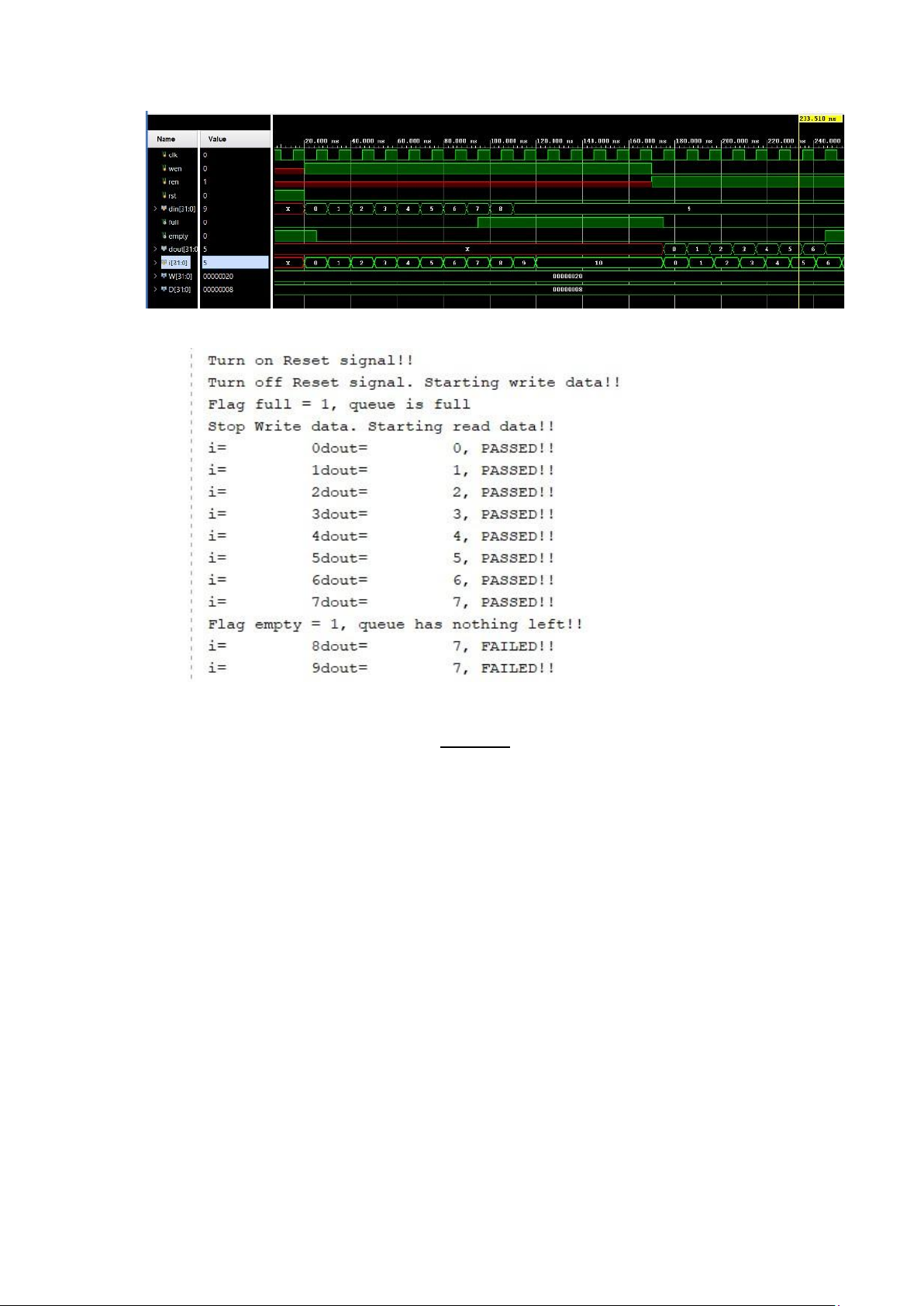

Run simulation the FIFO design, we have the result: lOMoAR cPSD| 59285474

With self-checker in testbench, we'll check the result in Tcl console:

As we see, the Tcl console result is the same to we expected. The end!