Preview text:

lOMoARcPSD| 10435767

CHƯƠNG 3 – CÁC PHƯƠNG PHÁP TRAO ĐỔI THÔNG TIN LT3 3.1 GIỚI THIỆU

Như ã biết hệ thống CPU bao gồm 3 phần chính : CPU, bộ nhớ và vào ra. Trong ó

CPU óng vai trò iều khiển hoạt ộng của hệ thống. Đối với bộ nhớ chúng có tốc ộ hoạt

ộng khá nhanh, có thể áp ứng gần như tức thời khi CPU truy cập, mặt khác bộ nhớ sử

dụng lưu trữ các hằng và biến nên khi cần chúng sẽ ược truy xuất bằng một lệnh truyền

dữ liệu, khi ó bộ nhớ sẽ luôn sẵn sàng truyền dữ liệu, mà không phải chờ bất cú một tác

ộng nào từ bên ngoài. Còn ối với vào ra thông thường có tốc ộ áp ứng chậm, mặt khác

ôi khi chúng còn phải chờ tác ộng từ bên ngoài (ví dụ như khi ọc bàn phím CPU phải

chờ cho người sử dụng nhấn phím …), vì vậy các vào ra cần phải có cơ chế iều khiển

hoạt ộng khác với bộ nhớ. Trong các hệ thống vi xử lý, các thiết bị vào ra thường ược

iều khiển bằng ba giải phương pháp sau:

- Vào ra dữ liệu bằng phương pháp thăm dò (polling).

- Vào ra dữ liệu bằng ngắt (interrupt).

- Vào ra dữ liệu bằng phương pháp thâm nhập trực tiếp bộ nhớ ( DMA -Direct Memory Access).

Với phương pháp thăm dò, CPU sẽ hoạt ộng theo chế ộ phân chia thời gian, nó sẽ

kiểm tra lần lượt từng thiết bị và thực hiện chương trình phục vụ khi thiết bị hoạt ộng.

Ở phương pháp ngắt thiết bị hoạt ộng sẽ thông báo ể CPU biết bằng một tín hiệu yêu

cầu, CPU sẽ tạm ngừng (ngắt) công việc hiện hành ể phục vụ nó. Còn với phương pháp

vào ra bằng DMA, CPU sẽ ược yêu cầu ngưng hoạt ộng ể thiết bị vào ra (thường là ổ ĩa)

truyền dữ liệu theo từng khối với bộ nhớ, dưới sự iều khiển của bộ iều khiển DMA (DMAC).

Mỗi phương pháp iều khiển vào ra dữ liệu nêu trên có các ặc iểm khác nhau và sẽ

ược ứng dụng trong các trường hợp khác nhau, chúng sẽ ược mô tả cụ thể trong các

mục kế tiếp của chương.

3.2 PHƯƠNG PHÁP THĂM DÒ (POLLING)

Các hệ thống vi xử lý hoặc máy tính, luôn quản lý nhiều thiết bị vào ra với các nguyên

tắc hoạt ộng khác nhau, nên cần các chương trình iều khiển khác nhau. Để iều khiển ược

tất cả các thiết bị trong hệ thống, CPU có thể thực hiện các chương trình làm việc với

lần lượt từng thiết bị mà nó quản lý.

Một số thiết bị luôn sẵn sàng hoạt ộng tại bất cứ thời iểm nào, CPU có thể truyền dữ

liệu lập tức tới các cổng vào ra của nó. Tức là CPU sẽ mở cửa vào ra ể ọc dữ liệu, hoặc

ghi dữ liệu tới thiết bị khi chúng tới vòng phục vụ. Lúc này các bộ vào ra chỉ óng vai trò lOMoARcPSD| 10435767

là các cổng ngăn cách giữa Bus hệ thống và thiết bị, ể các hoạt ộng của thiết bị không

ảnh hưởng tới hệ thống trong khi CPU phục vụ các thiết bị khác.

Ví dụ như trong hệ thống o nhiệt ộ và hiển thị lên LED 7 oạn, giá trị nhiệt ộ luôn ược

cảm biến biến ổi, qua khuếch ại tới ADC sẵn sàng ể CPU ọc tại bất cứ thời iển nào. Do

ó, cứ tới vòng phục vụ CPU sẽ ọc ược giá trị số tương ứng với nhiệt ộ ầu dò luôn sẵn

sàng tại ngõ ra bộ biến ổi A/D, và sau ó sẽ cung cấp ra LED 7 oạn ể hiển thị. Và nếu

vòng phục vụ ủ ngắn, sẽ luôn thấy nhiệt ộ cần o hiển thị trên LED trong khi các thiết bị

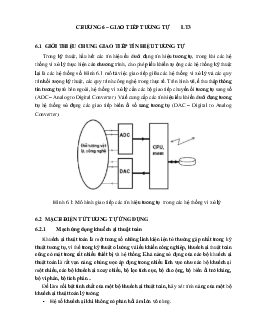

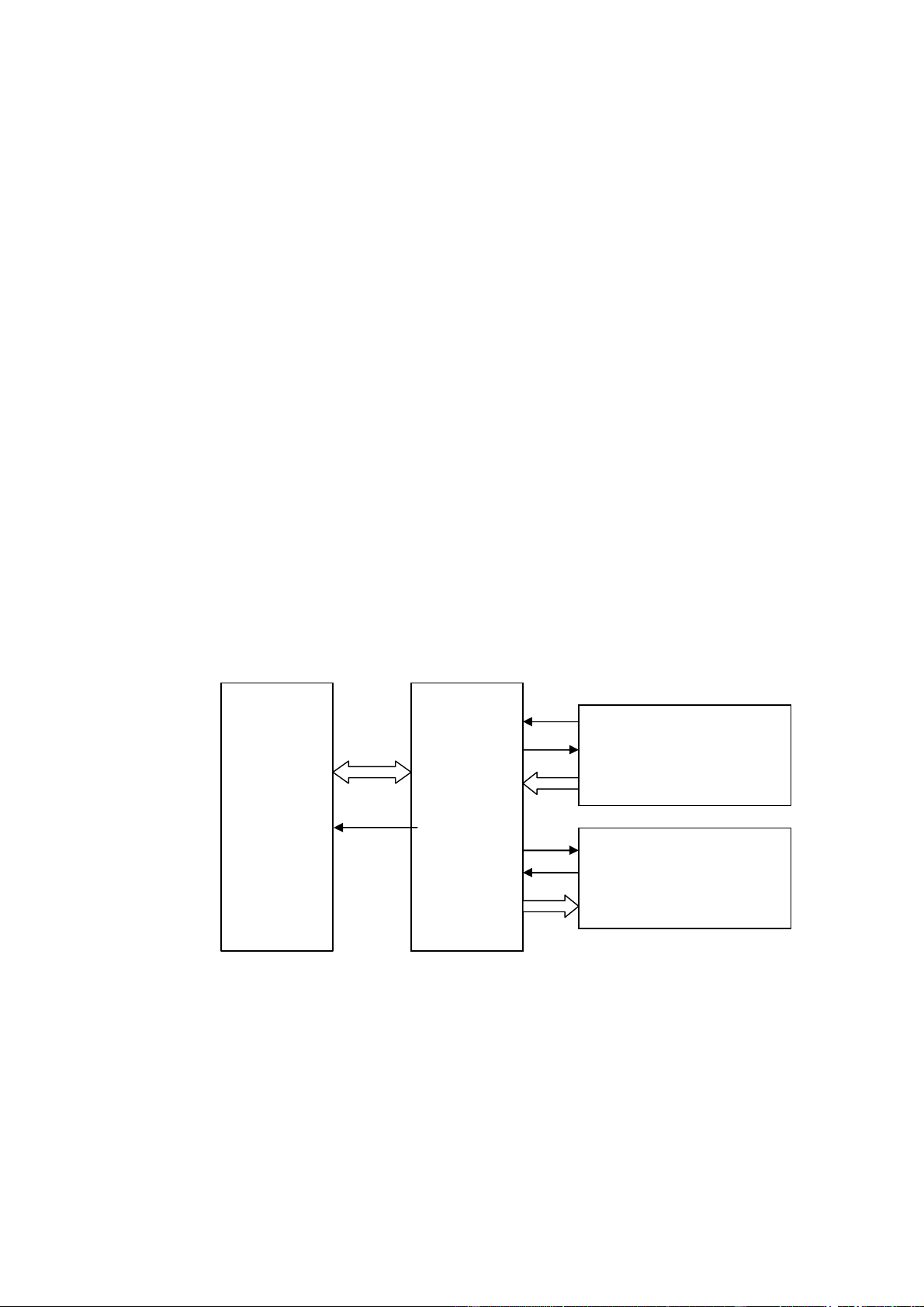

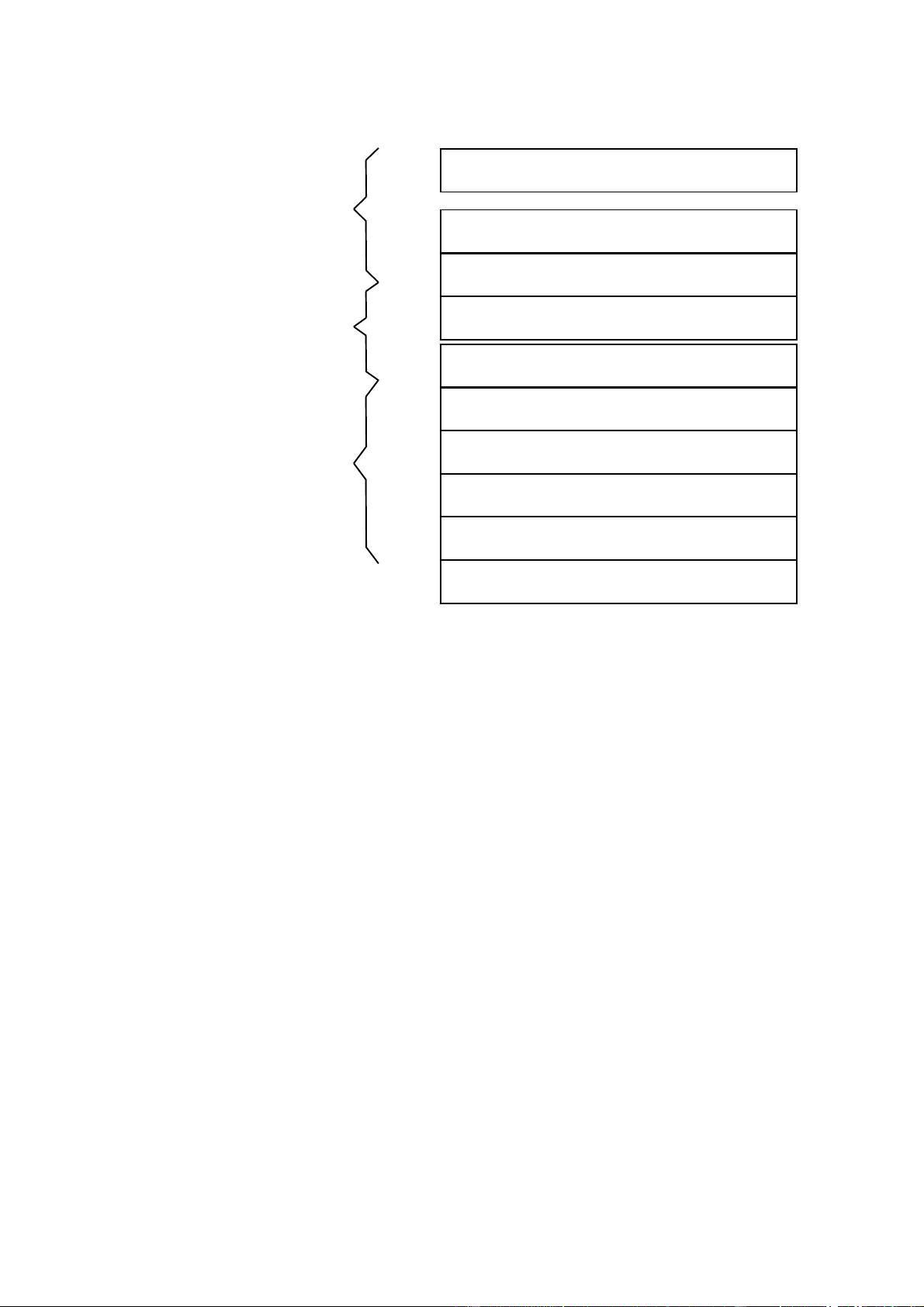

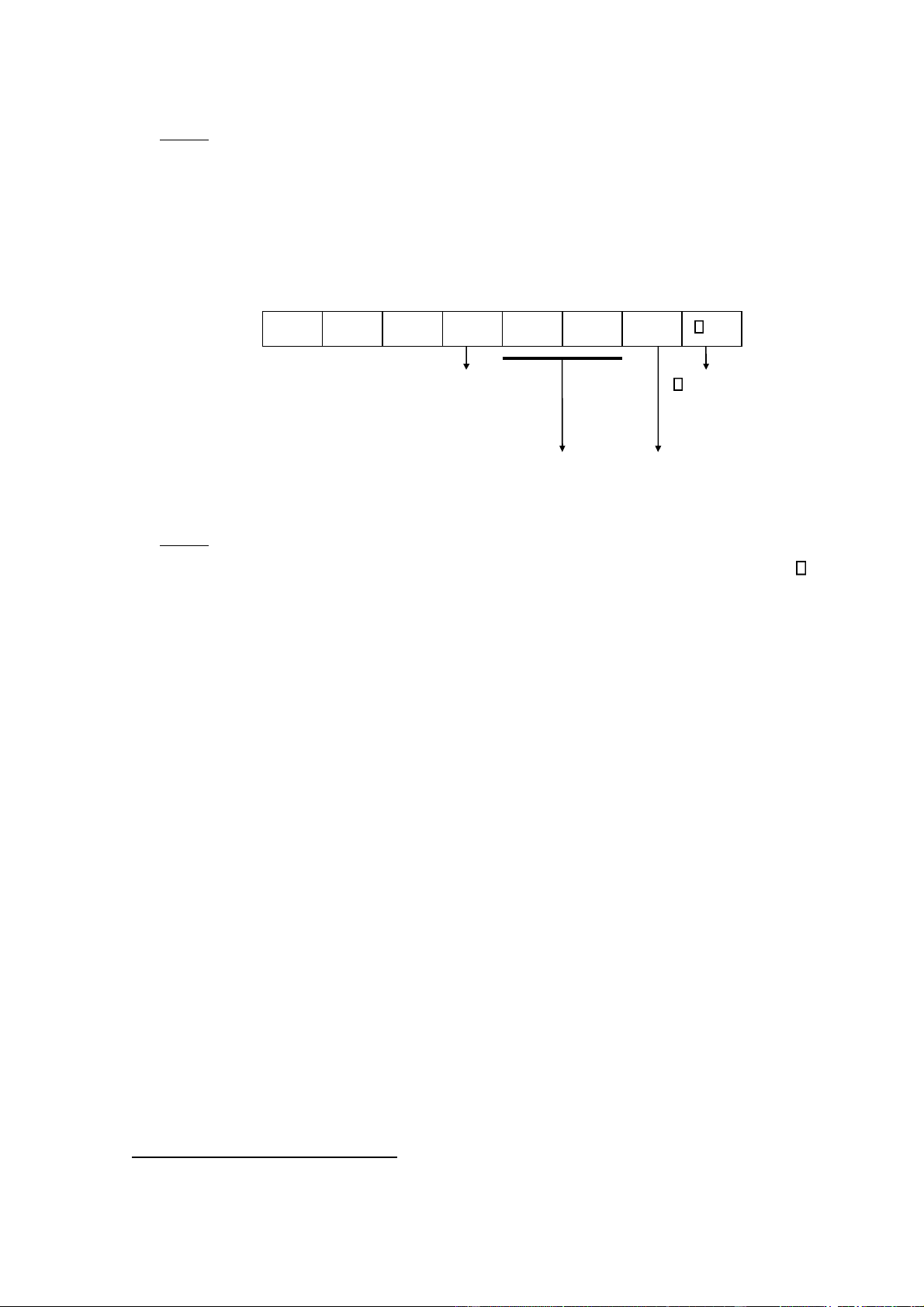

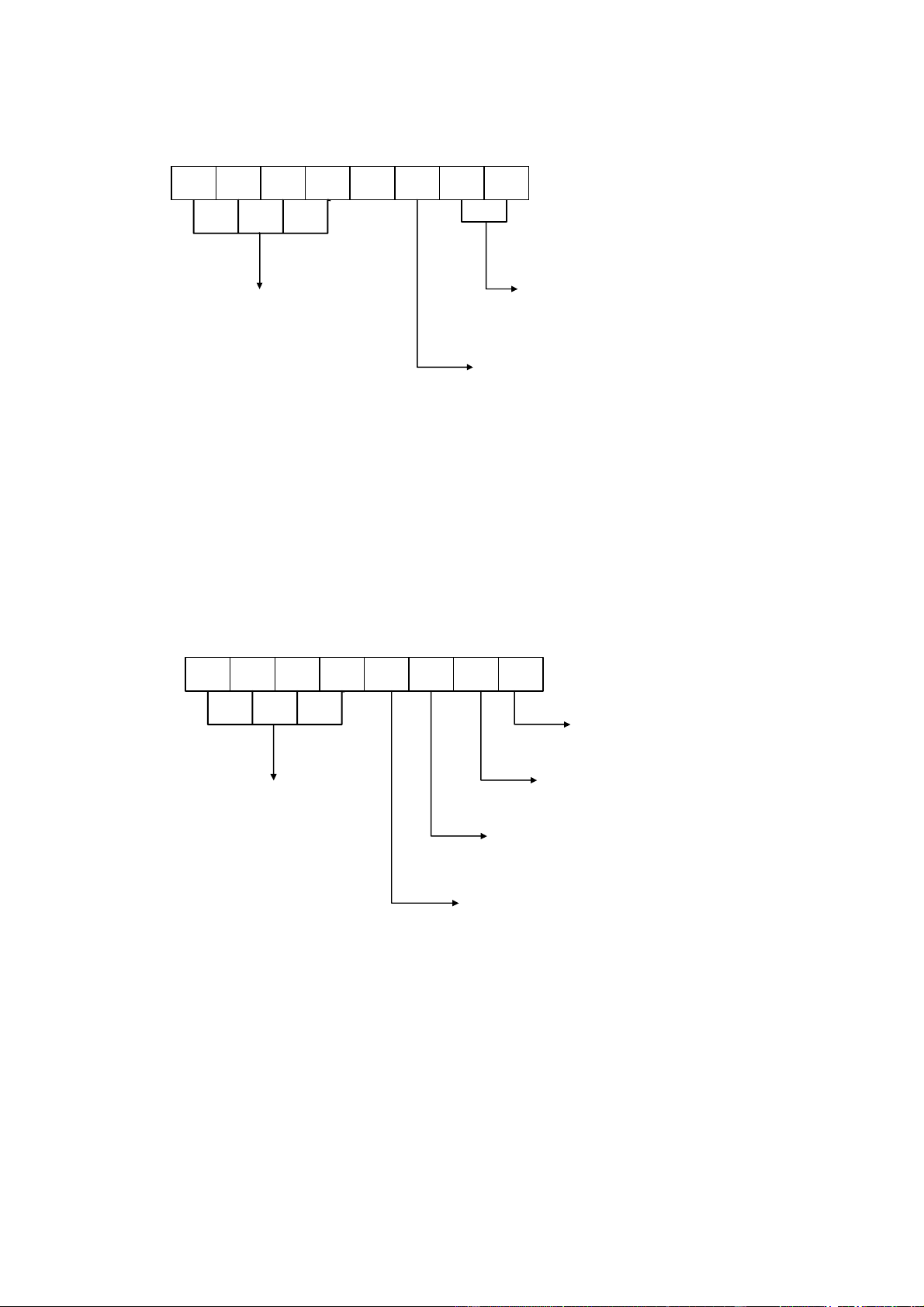

khác của hệ thống vẫn ược phục vụ. Mạ ch Mạ ch cài Thi ế t bị Data Bus ệ m vào D 0 –D 7 OC G STB CS1 V +5 pr Data Bus Q D D 0 clk clr CS0 CS1

Hình 3.1: Mạch giao tiếp vào có bắt tay.

Tuy nhiên trong thực tế không phải tất cả các thiết bị làm việc với CPU ều luôn ở

trạng thái sẵn sàng như trên, có thể tới vòng phục vụ mà thiết bị chưa sẵn sàng truyền

dữ liệu với CPU. Ví dụ bàn phím khi CPU ọc vẫn chưa có phím nào ược nhấn, máy in

chưa in xong dữ liệu ã truyền cho nó trong lần trước ó …. Như vậy, ể iều khiển hoạt ộng

của thiết bị, CPU cần kiểm tra trạng thái của thiết bị trước khi truyền dữ liệu với nó. Và

như vậy một thiết bị cần phải có tín hiệu hoặc cổng vào ể thông báo trạng thái cho CPU,

ví dụ bàn phím cung cấp một mã ặc biệt khi không có phím nhấn, máy in cung cấp tín

hiệu sẵn sàng khi có thể nhận dữ liệu ể in. Hình 3.1 trình bày mạch giao tiếp của một

cổng vào có bắt tay giữa một thiết bị và CPU. Trên hình vẽ, khi thiết bị vào có dữ liệu

truyền cho CPU, nó cung cấp tín hiệu STB ể cài dữ liệu vào bộ cài ồng thời kích cho

mạch lật tạo tín hiệu sẵn sàng làm việc mức 1. Khi tới vòng phục vụ của thiết bị này,

trước hết CPU ọc cổng trạng thái (CS0 = 0), nếu ọc ược dữ liệu có bit D0 = 1, nó hiểu

rằng thiết bị này ã có một dữ liệu sẵn sàng. Khi cung cấp CS1=0 ể ọc cổng dữ liệu ể lấy lOMoARcPSD| 10435767

dữ liệu, tín hiệu này sẽ xoá luôn tín hiệu sẵn sàng ể chuẩn bị cho lần truyền dữ liệu tiếp theo.

Trong các hệ thống vi xử lý, các mạch vào ra có bắt tay thông thường ược thực hiện

bằng các bộ vào ra có lập trình, việc thiết kế mạch sẽ ơn giản hơn rất nhiều vì các mạch

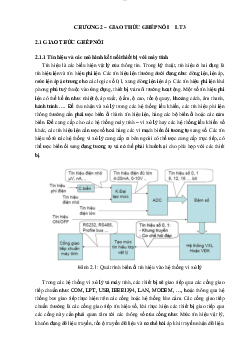

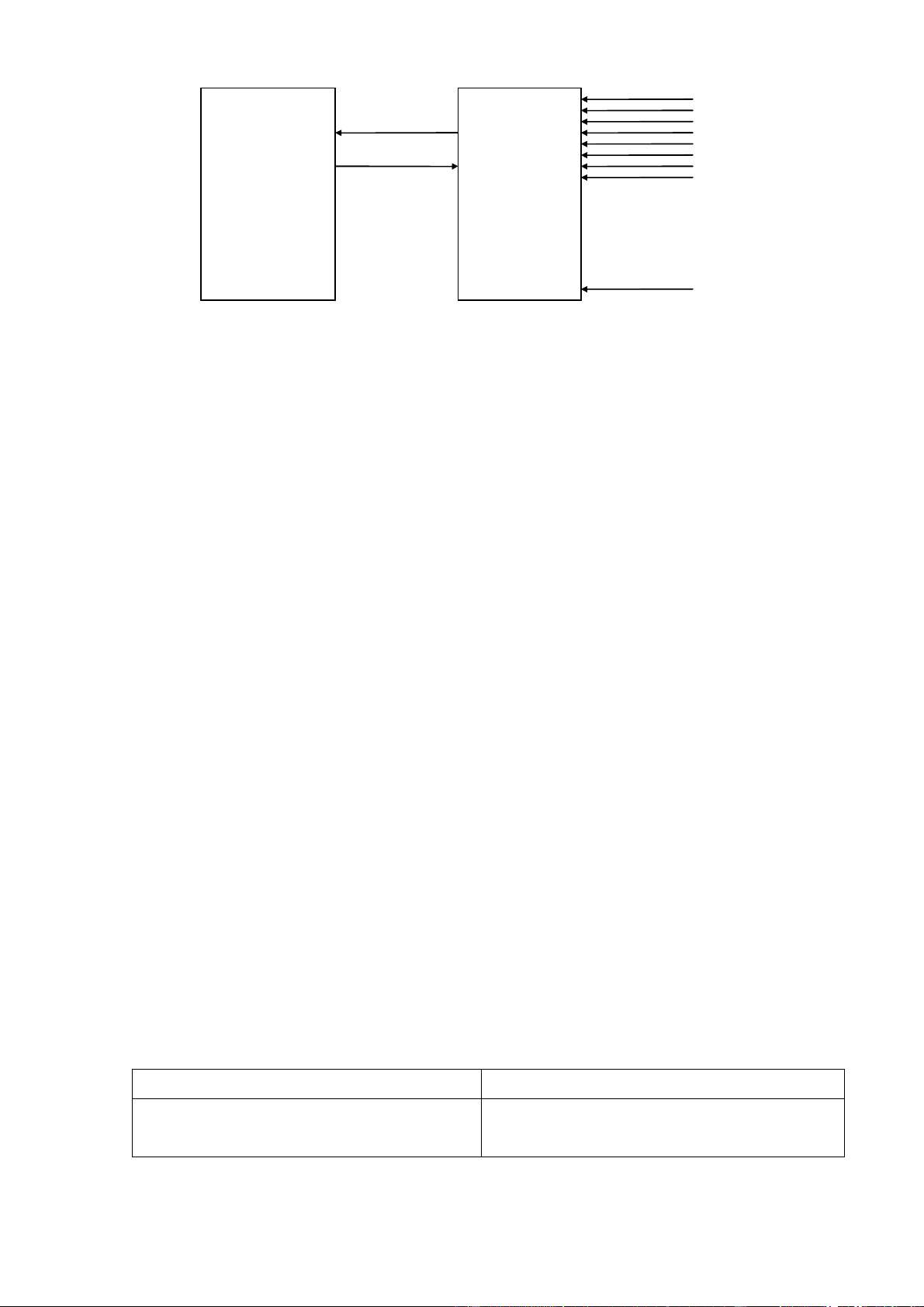

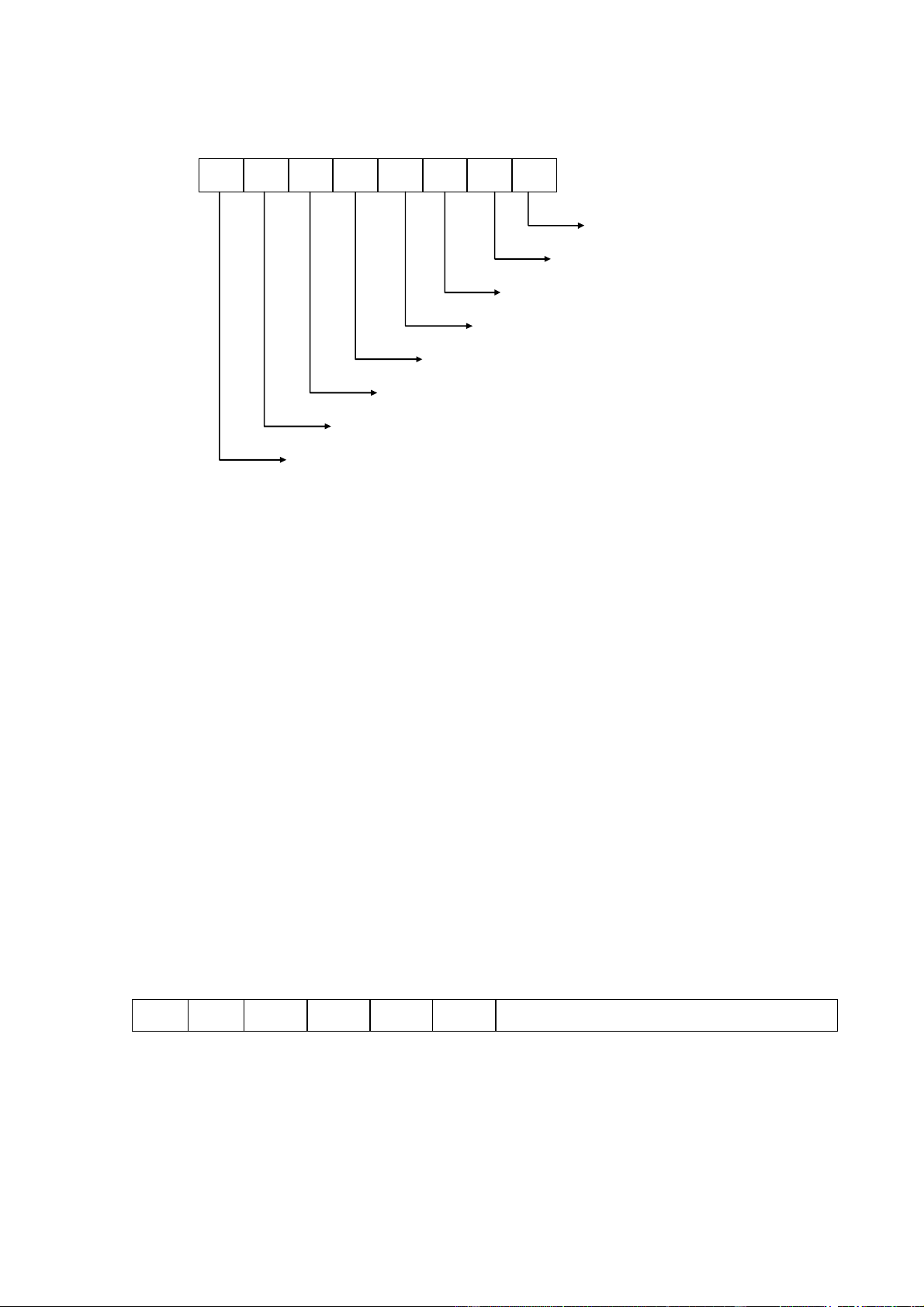

tạo tín hiệu bắt tay ược tích hợp ngay trong các vi mạch vào ra này. Hình 3.2 trình bày

sơ ồ vào ra có bắt tay sử dụng 8255.

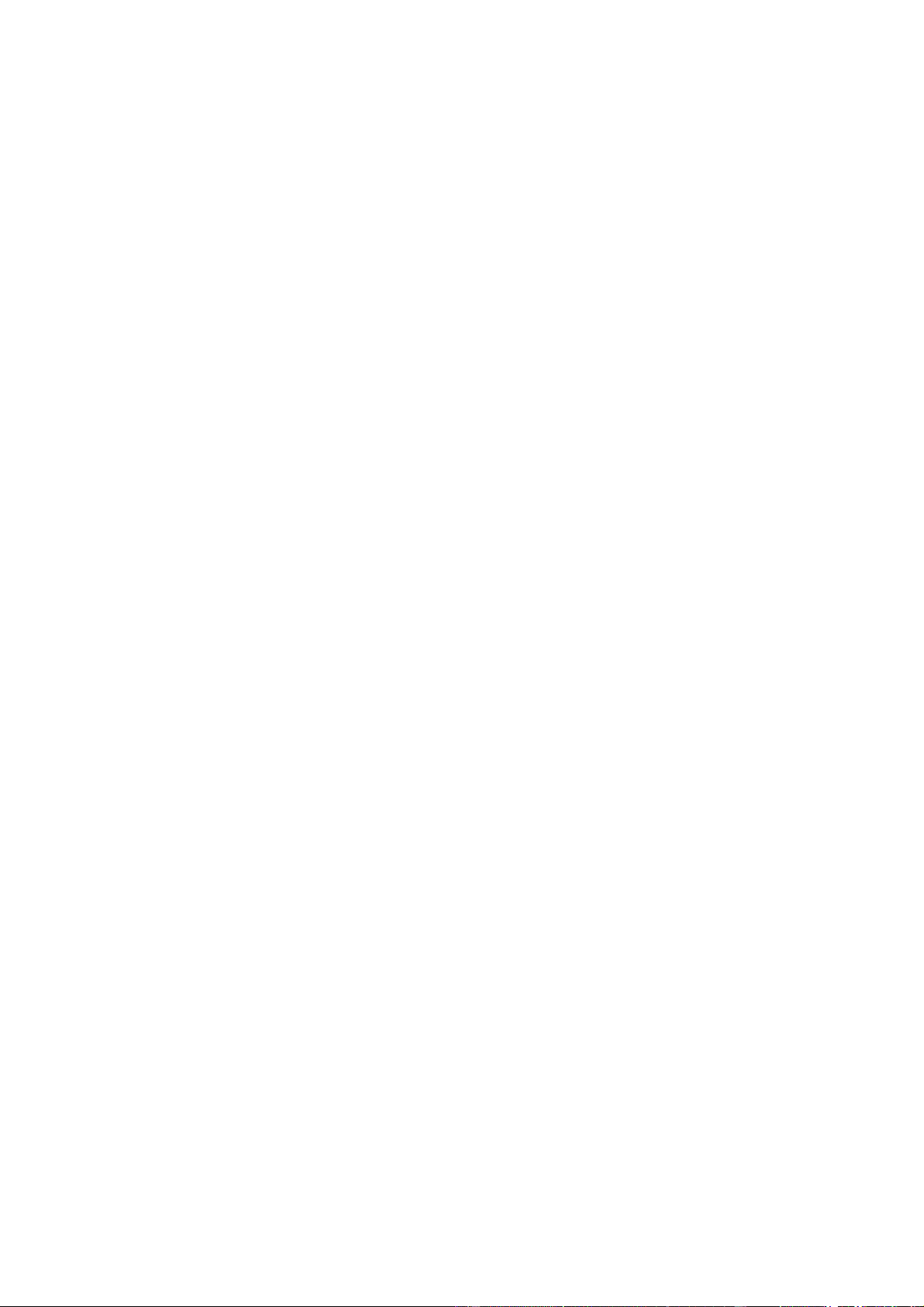

Trên sơ ồ, 8255 óng vai trò giao tiếp với một thiết bị vào và một thiết bị ra. Cổng A

của 8255 dành cho việc truyền dữ liệu vào, PC4, PC5 sử dụng làm các thiết bị bắt tay

vào. Khi thiết bị vào có dữ liệu truyền, trước hết nó kiểm tra tín hiệu ACK, nếu tín hiệu

này tích cực thì dữ liệu truyền trước ó chưa ược CPU ọc vào, nếu ACK không tích cực

thiết bị sẽ cung cấp tín hiệu STB ể cài dữ liệu vào PA của 8255, 8255 sẽ nhận dữ liệu

và tác ộng ACK. Tín hiệu STB sẽ ược giữ nguyên cho ến khi ACK hết tích cực, do ó

CPU có thể kiểm tra tín hiệu này ể xác ịnh ã có dữ liệu sẵn sàng chưa. Khi CPU ọc dữ

liệu từ cổng A, STB và ACK sẽ ược xoá.

Tương tự như vậy, khi CPU muốn truyền dữ liệu tới cổng ra, nó sẽ kiểm tra tín hiệu

ACK ể biết cổng này ã sẵn sàng nhận dữ liệu chưa. Ngoài ra, khi có một dữ liệu ã ược

nhận ở cổng vào, hoặc cổng ra ã truyền xong dữ liệu mà CPU ghi tới, 8255 sẽ cung cấp

cho CPU một tín hiệu thông báo INTR, CPU có thể kiểm tra tín hiệu này trước khi kiểm

tra trạng thái của các cổng vào ra. CPU 8255 PC4 STB C ổ ng vào ACK PC5 D 0 –D 7 D 0 -D 7 PA 0 - PA 7 INTR PC1 STB C ổ ng ra ACK PC2 D 0 –D 7 PB 0 - PB 7

Hình 3.2: Vào ra có bắt tay sử dụng 8255

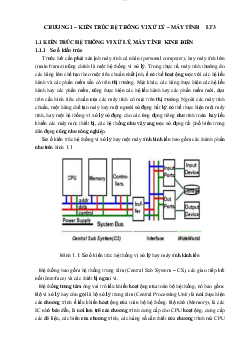

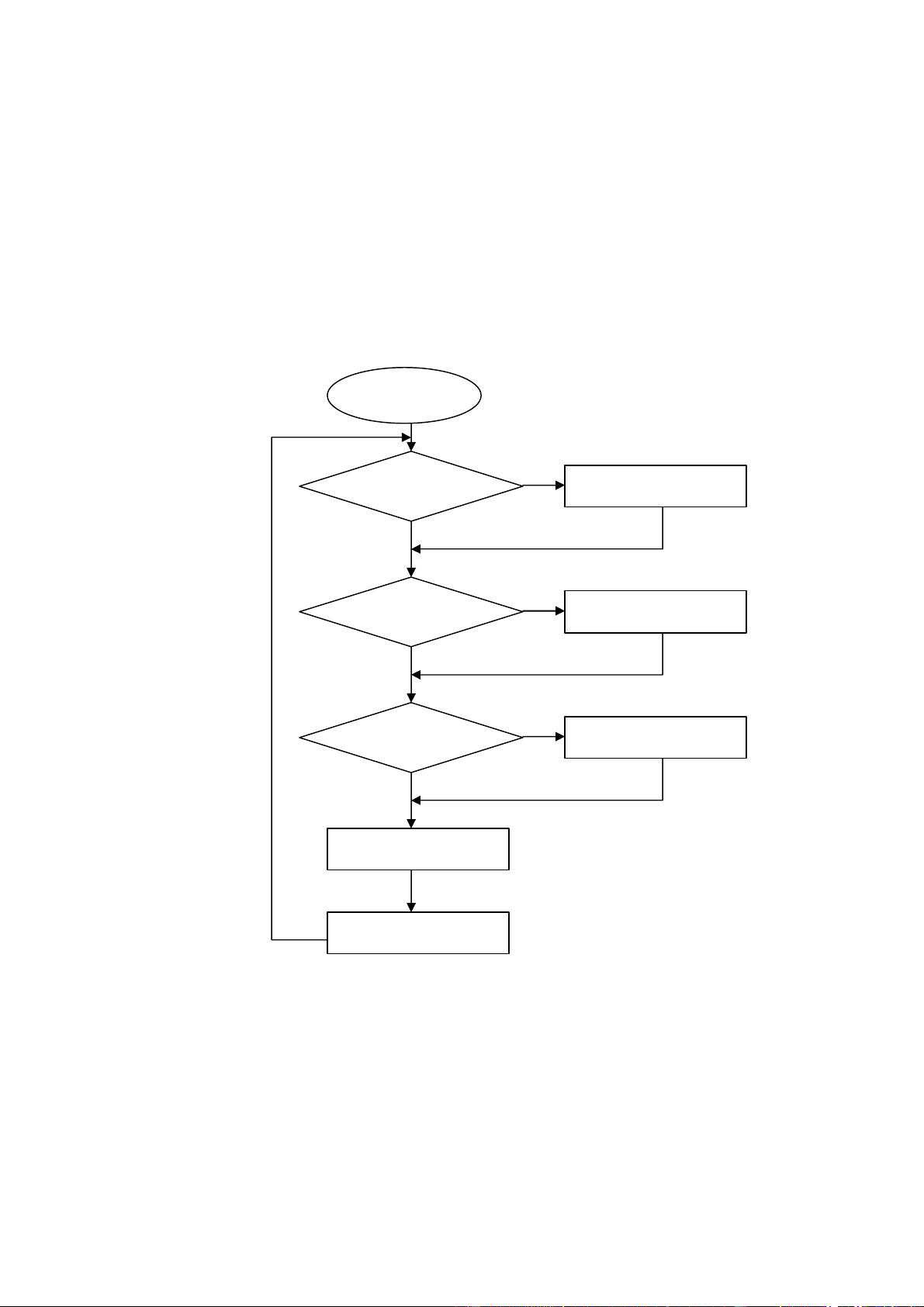

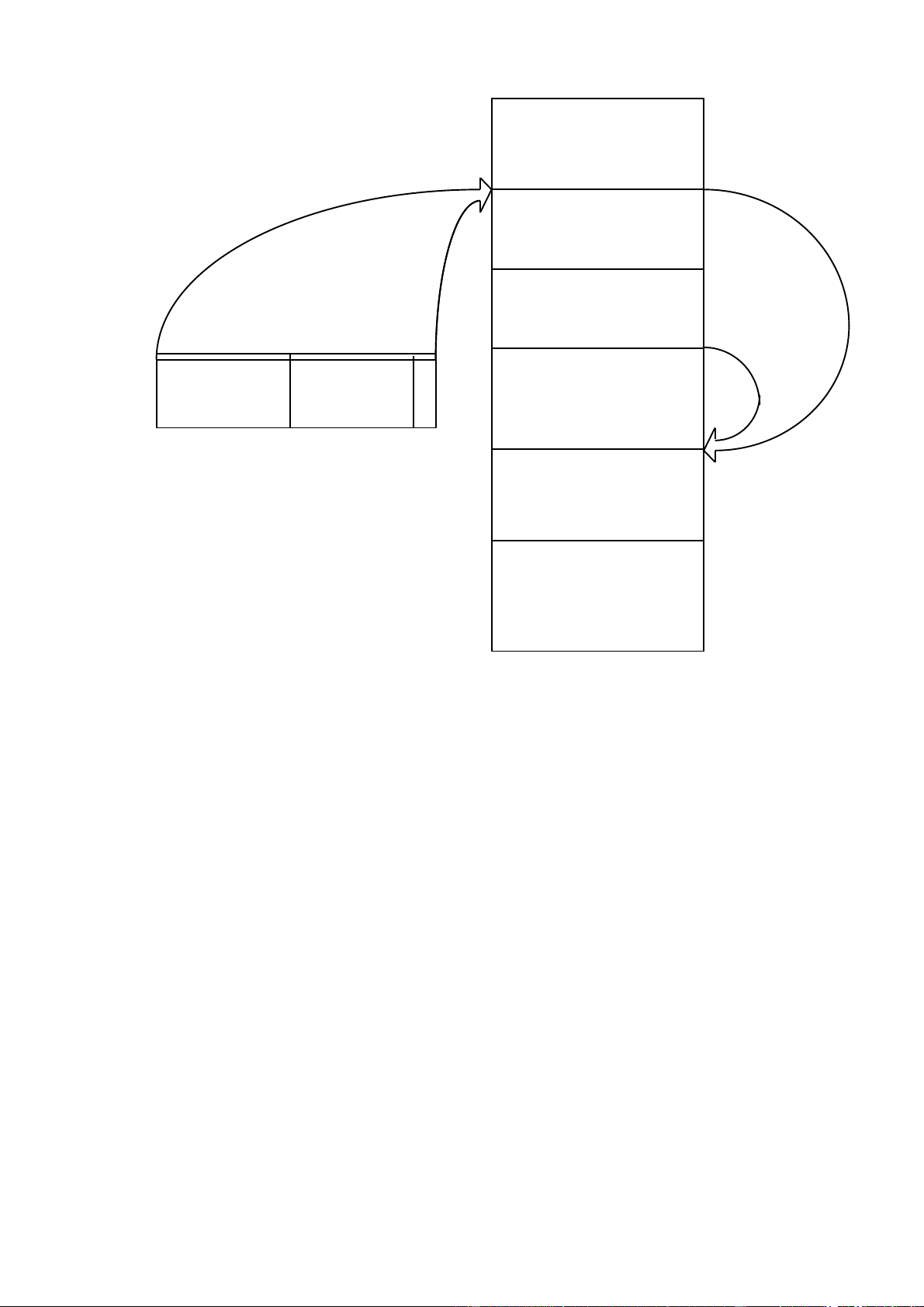

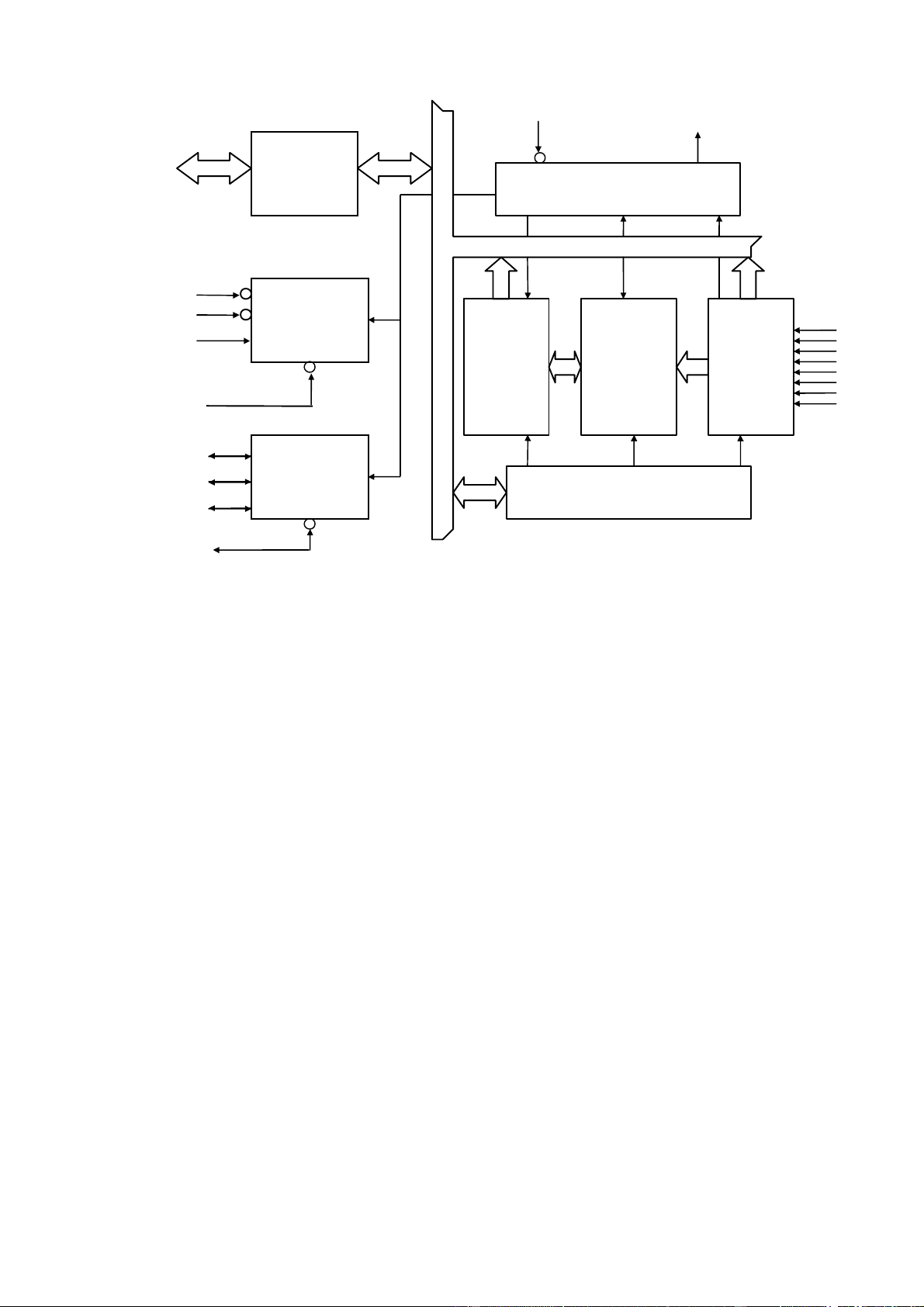

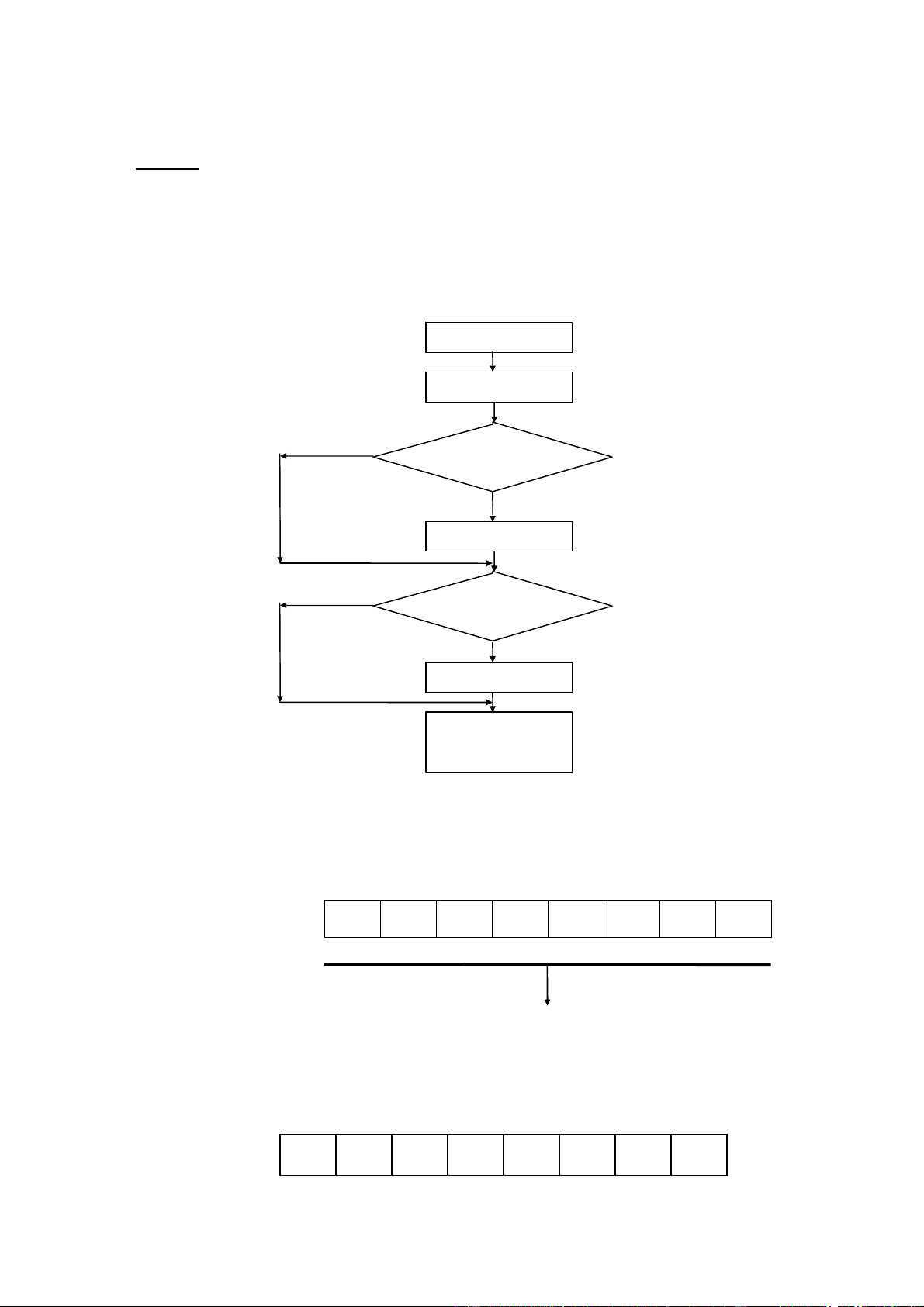

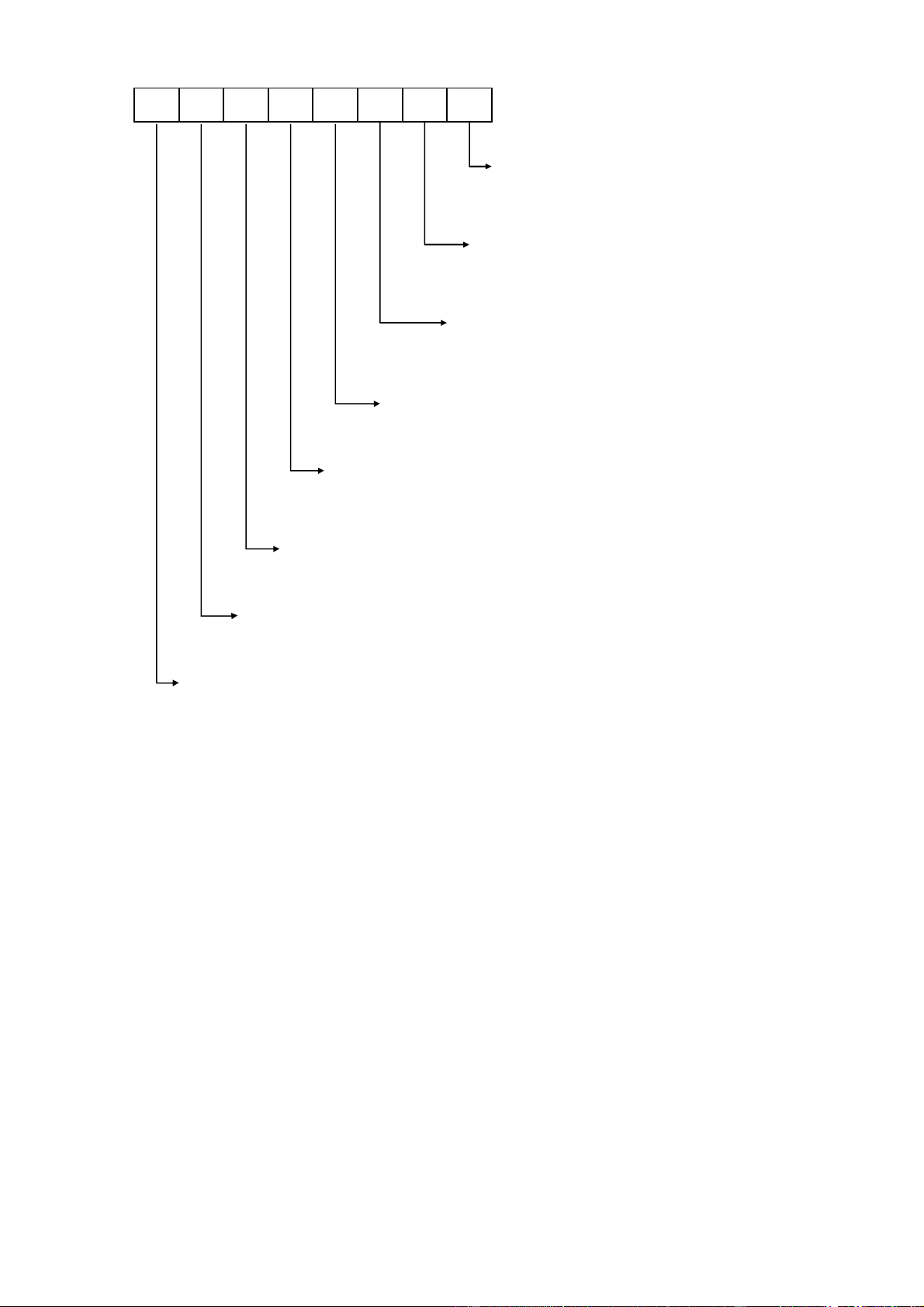

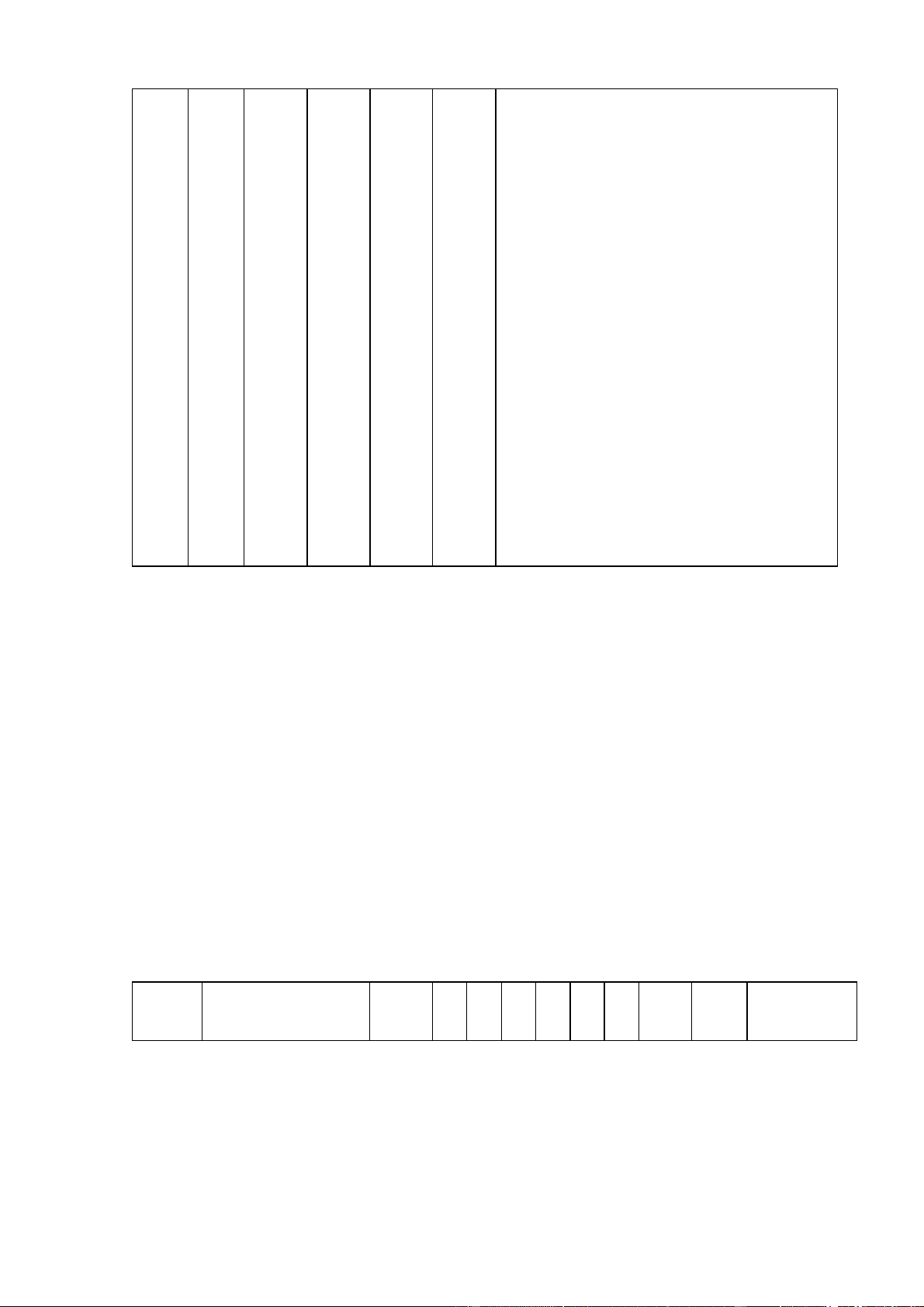

Hình 3.3 mô tả giải thuật hoạt ộng của CPU trong cơ chế thăm dò, trong cơ chế này

lần lượt từng thiết bị mà CPU quản lý sẽ ược kiểm tra và phục vụ khi có yêu cầu. Khi

tới thiết bị cuối cùng CPU sẽ thực hiện các công việc khác theo yêu cầu của hệ thống và

lại tiếp tục một vòng phục vụ thiết bị mới. Với cơ chế hoạt ộng này, hệ thống phát sinh một số vấn ề sau: lOMoARcPSD| 10435767

- Nếu tốc ộ hoạt ộng của CPU không ủ nhanh, một số thiết bị có thể không ược phục

vụ khi có yêu cầu. Ví dụ khi nhấn phím, bàn phím chưa ến vòng phục vụ, còn khi ã

hết nhấn chương trình mới ọc cổng bàn phím, hoặc tốc ộ nhấn phím của người sử

dụng nhanh hơn tốc ộ phục vụ của CPU.

- Khi thiết bị không hoạt ộng, CPU vẫn phải thực hiện việc kiểm tra trạng thái của chúng.

Để khắc phục các nhược iểm trên, các máy tính và các hệ thống vi xử lý lớn thường

iều khiển các thiết bị vào ra bằng phương pháp ngắt. Quét vòng Thi ế t bị 1 yêu

Yes Chương trình phụ c vụ c ầ u ? thi ế t bị 1 No Thi ế t bị 2 yêu

Yes Chương trình phụ c vụ c ầ u ? thi ế t bị 2 No Thi ế t bị 3 yêu

Yes Chương trình phụ c vụ c ầ u ? thi ế t bị 3 No … Các công vi ệ c khác

Hình 3.3: Giải thuật hoạt ộng phục vụ thiết bị của CPU theo phương pháp thăm dò

3.3 PHƯƠNG PHÁP NGẮT 3.3.1 Khái niệm

Với phương pháp thăm dò dù chỉ kết nối thụ ộng theo dữ liệu hay có bắt tay, CPU

ều óng vai trò chủ ộng nó i quét thường xuyên các thiết bị xem có cần phục vụ hay

không. Giải pháp này sẽ làm lẵng phí thời gian của CPU khi các thiết bị không có nhu

cầu phục vụ thường xuyên, mà CPU vẫn phải thực hiện các lệnh kiểm tra thiết bị. Có lOMoARcPSD| 10435767

một giải pháp vào ra khác tránh ược nhược iểm trên, ó là cơ chế ngắt. Trong giải pháp

này các thiết bị có yêu cầu phục vụ sẽ gửi yêu cầu tới CPU bằng cách cung cấp tín hiệu

từ ngoài, lúc này CPU sẽ tạm ngưng công việc nó ang thực hiện ể phục vụ thiết bị,

khi thiết bị ược phục vụ xong CPU sẽ quay về với công việc mà nó ang thực hiện dở.

Hầu hết các họ vi xử lý ều cho phép ngưng chương trình bình thường ang thực hiện

ể chuyển qua một chương trình tại vị trí ặc biệt, bằng một số tín hiệu cung cấp từ bên

ngoài hoặc một số lệnh ặc biệt trong chương trình. Việc chuyển iều khiển này giống

như cơ chế gọi chương trình con, hoạt ộng ược chuyển từ chương trình chính qua

chương trình con phục vụ cho ngắt, nhưng theo một cơ chế ặc biệt hơn chương trình

con, và chúng thường ược sử dụng cho việc iều khiển hoạt ộng của các thiết bị ngoại vi,

hoặc xử lý tình huống trong các trường hợp ặc biệt khác.

Như vậy, ngằt là cách iều khiển thiết bị ngoại vi theo yêu cầu. Tín hiệu mà thiết bị

ngoại vi gửi tới CPU khi cần phục vụ ược gọi là tín hiệu yêu cầu ngắt (IRQ – Interrupt

Request). Khi CPU ược cho phép phục vụ thiết bị, nó sẽ lưu lại các ngữ cảnh của chương

trình hiện tại bao gồm: Địa chỉ chương trình hiện hành nơi nó bị ngắt và thanh ghi trạng

thái. Sau ó CPU tìm ịa chỉ chương trình phục vụ ngắt tương ứng với thiết bị, và chuyển

iều khiển tới hoạt ộng tại chương trình này. Các CPU khác nhau, có thể có các cơ chế

tìm ịa chỉ chương trình ngắt khác nhau. Khi gặp lệnh kết thúc chương trình phục vụ ngắt

(IRET, RETI…), CPU phục hồi lại các ngữ cảnh cũ và quay về thực hiện chương trình

cũ (chương trình ã bị ngắt), bằng cách phục hồi lại các thanh ghi trạng thái và lấy lại ịa

chỉ chương trình ã lưu trữ.

Theo cơ chế trên, ngắt là một phương pháp hiệu quả ể phục vụ các sự kiện không

ược sắp ặt trước của các thiết bị ngoại vi. Việc iều khiển cơ chế ngắt ược thực hiện kết

hợp giữa phần mềm và phần cứng của hệ thống, nó cho phép hệ thống hoạt ộng một

cách a nhiệm, từ nhiệm vụ này tạm ngưng ể chuyển qua thực hiện một nhiệm vụ khác

rồi quay về nhiệm vụ cũ.

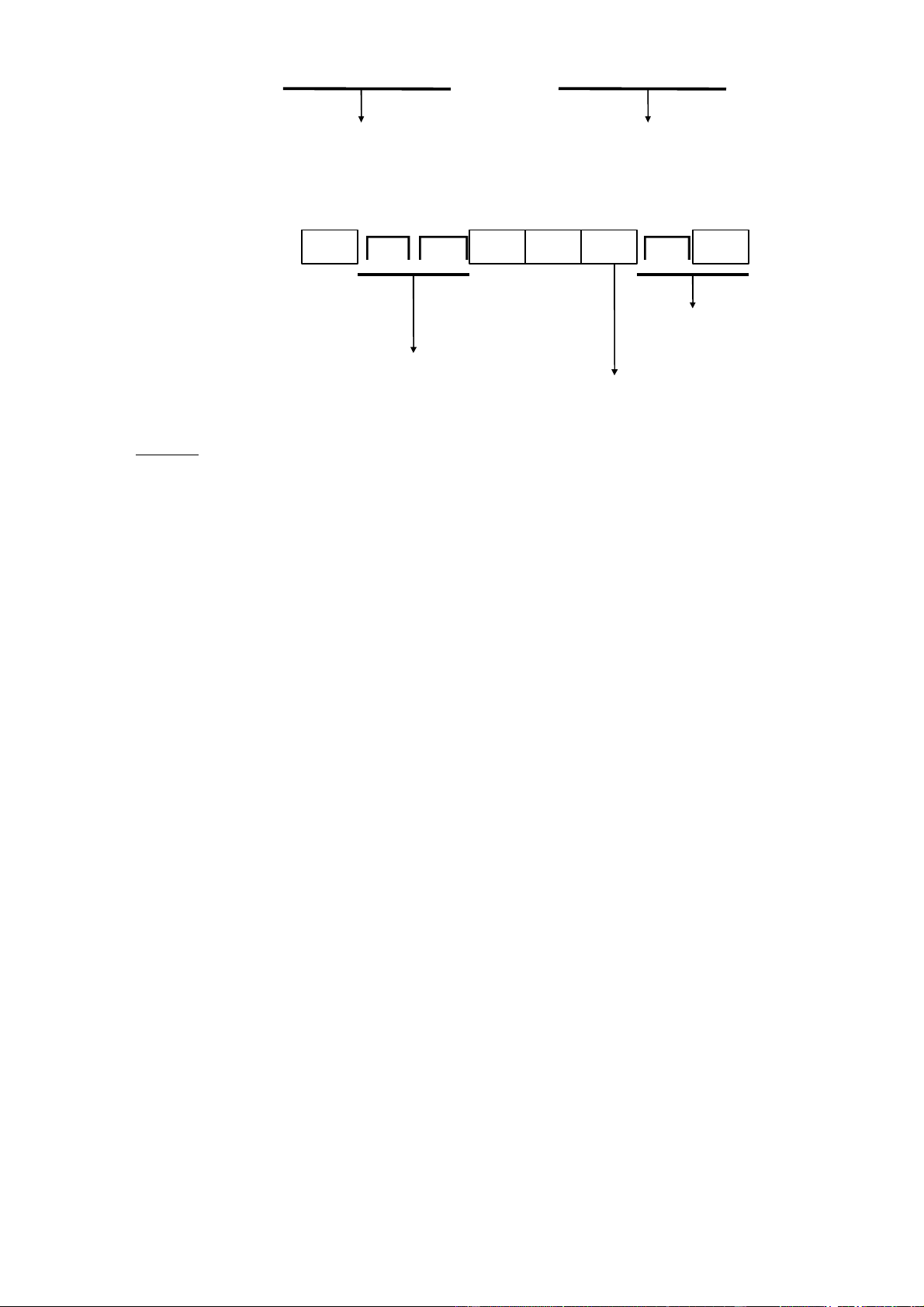

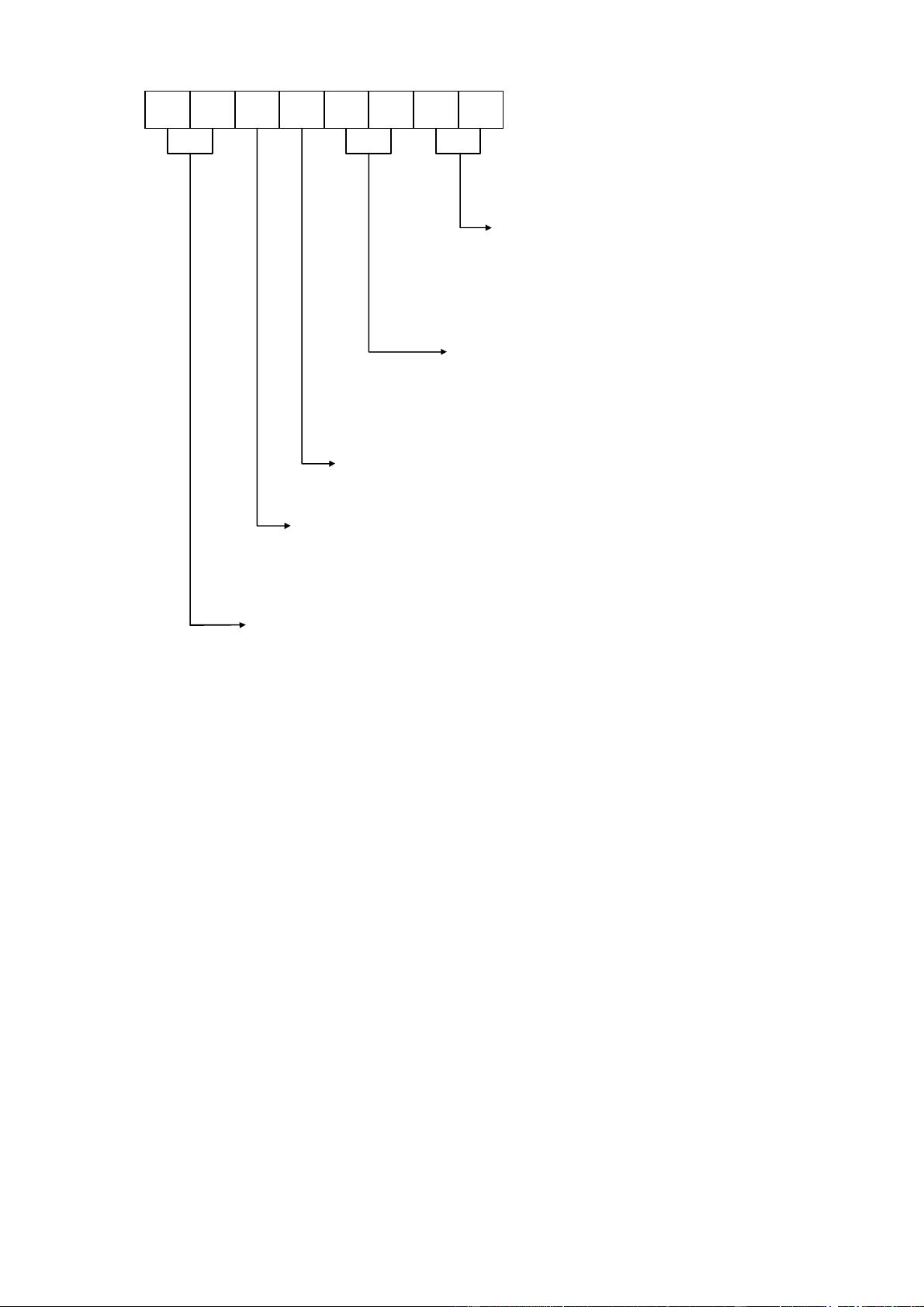

Để phục vụ ngắt ược nhiều thiết bị, trong các hệ thống vi xử lý thường sử dụng bộ

iều khiển ưu tiên ngắt (PIC – Priority Interrupt Control). Các tín hiệu yêu cầu sẽ ược ưa

tới bộ iều khiển ưu tiên ngắt và tùy theo thứ tự ưu tiên sẽ gửi tới CPU như hình 3.4.

Thứ tự ưu tiên cho các yêu cầu ngắt có thể ược cố ịnh từ trước hoặc xoay vòng tròn,

thiết bị nào mơi ược phục vụ sẽ ược thiết lập mức ưu tiên thấp nhất.

Nếu chỉ có một yêu cầu ngắt nó sẽ ược chuyển ngay tới CPU, nếu có nhiều yêu cầu

ngắt xảy ra ồng thời thì yêu cầu nào có ộ ưu tiên cao hơn sẽ ược bộ iều khiển ngắt gửi

tới CPU phục vụ trước. Kiểu ưu tiên và mức ưu tiên cho các yêu cầu ngắt sẽ ược lập

trình khi khởi ộng bộ iều khiển ưu tiên ngắt. lOMoARcPSD| 10435767 INTR CPU B ộ iề u khi ể n INTA ng ắ t Các yêu c ầ u ng ắ t

Hình 3.4: Cung cấp các yêu cầu ngắt cho CPU thông qua bộ iều khiển ngắt.

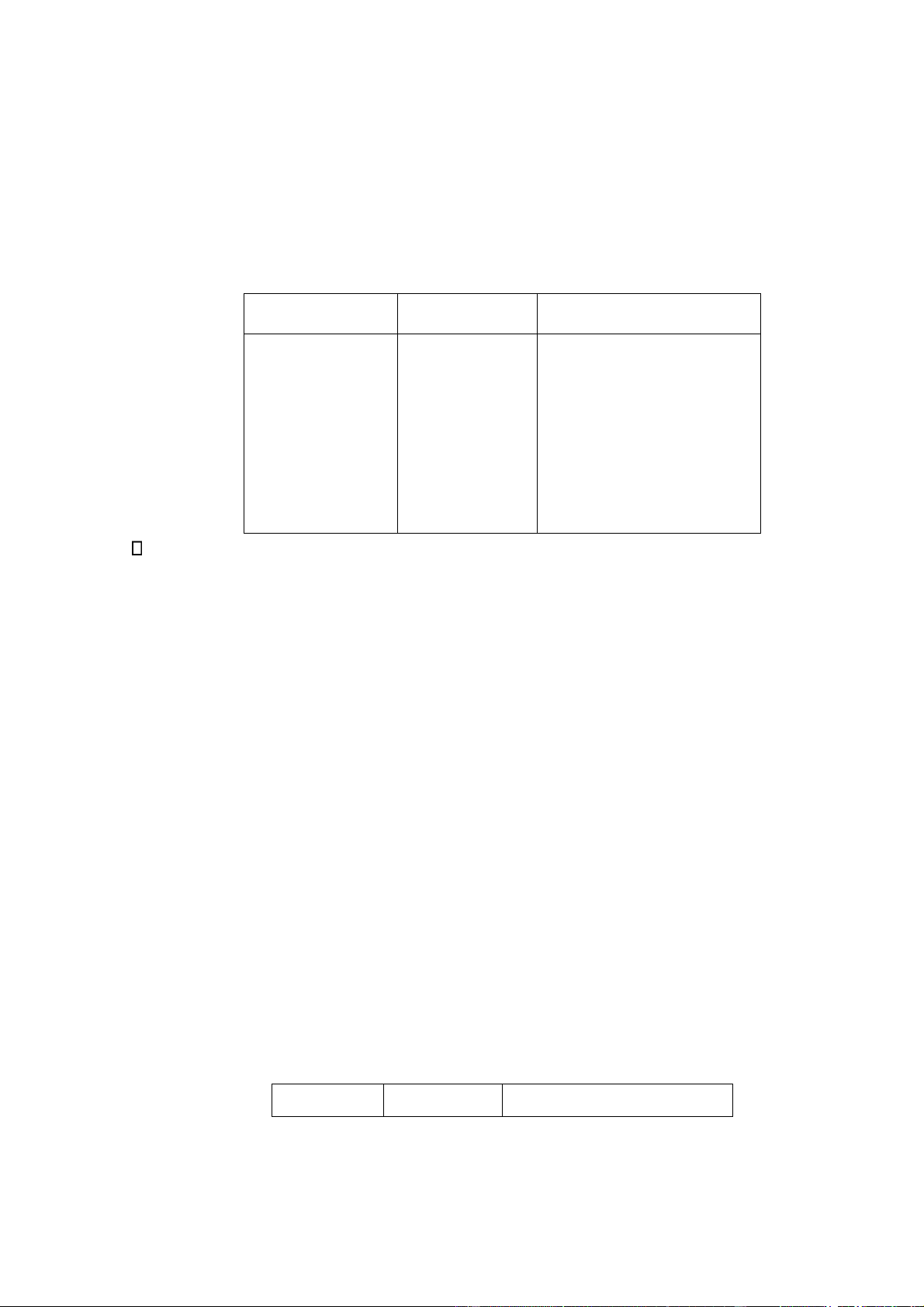

Việc tạm ngừng một chương trình này ể chuyển iều khiển qua một chương trình khác

của ngắt, giống như với chương trình con, tuy nhiên hai cơ chế này có các công việc

thực hiện khác nhau. Bảng 3.1 trình bày sự khác nhau giữa việc thực hiện chương trình

con và ngắt trong một hệ thống vi xử lý. 3.3.2 Phân loại

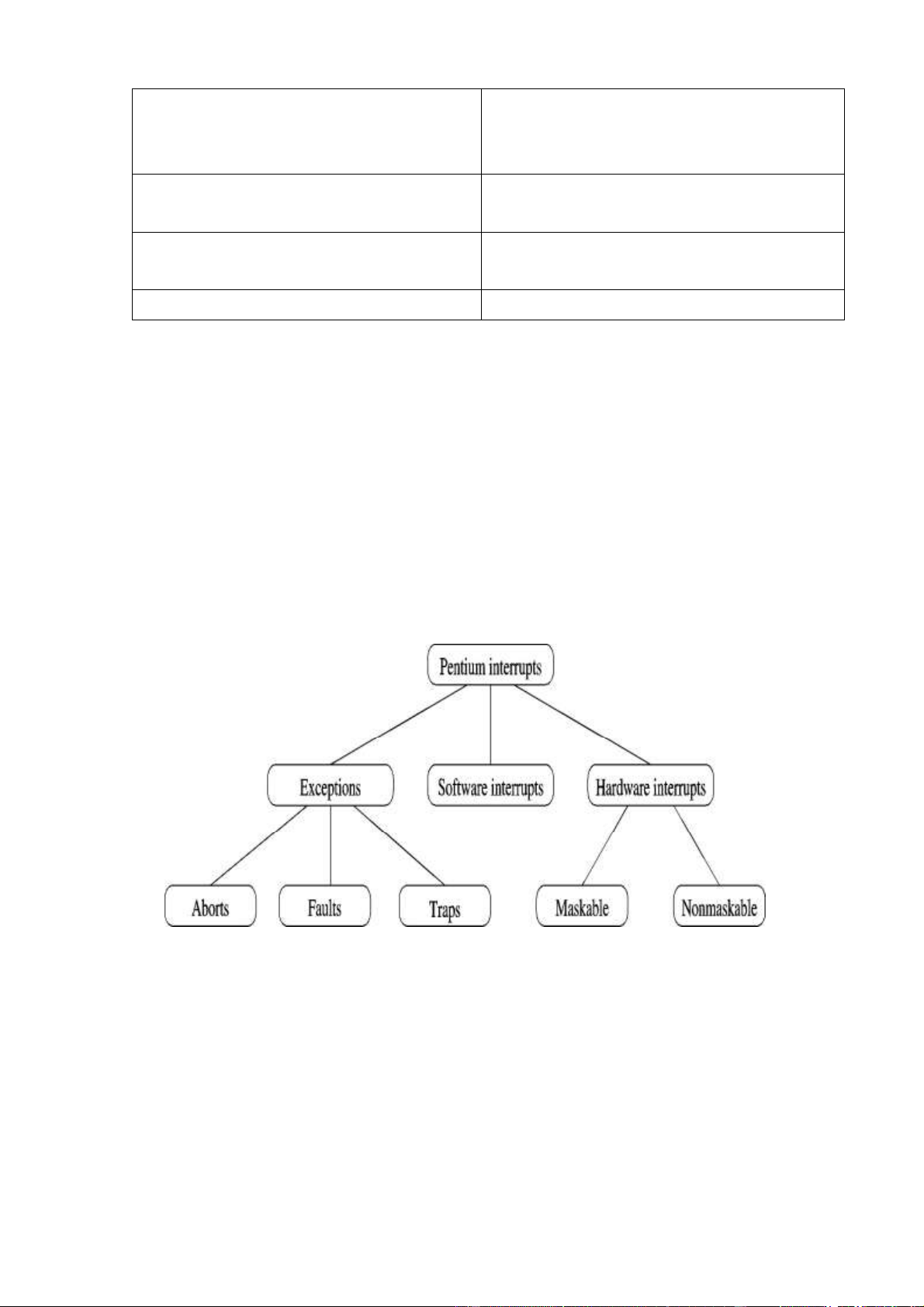

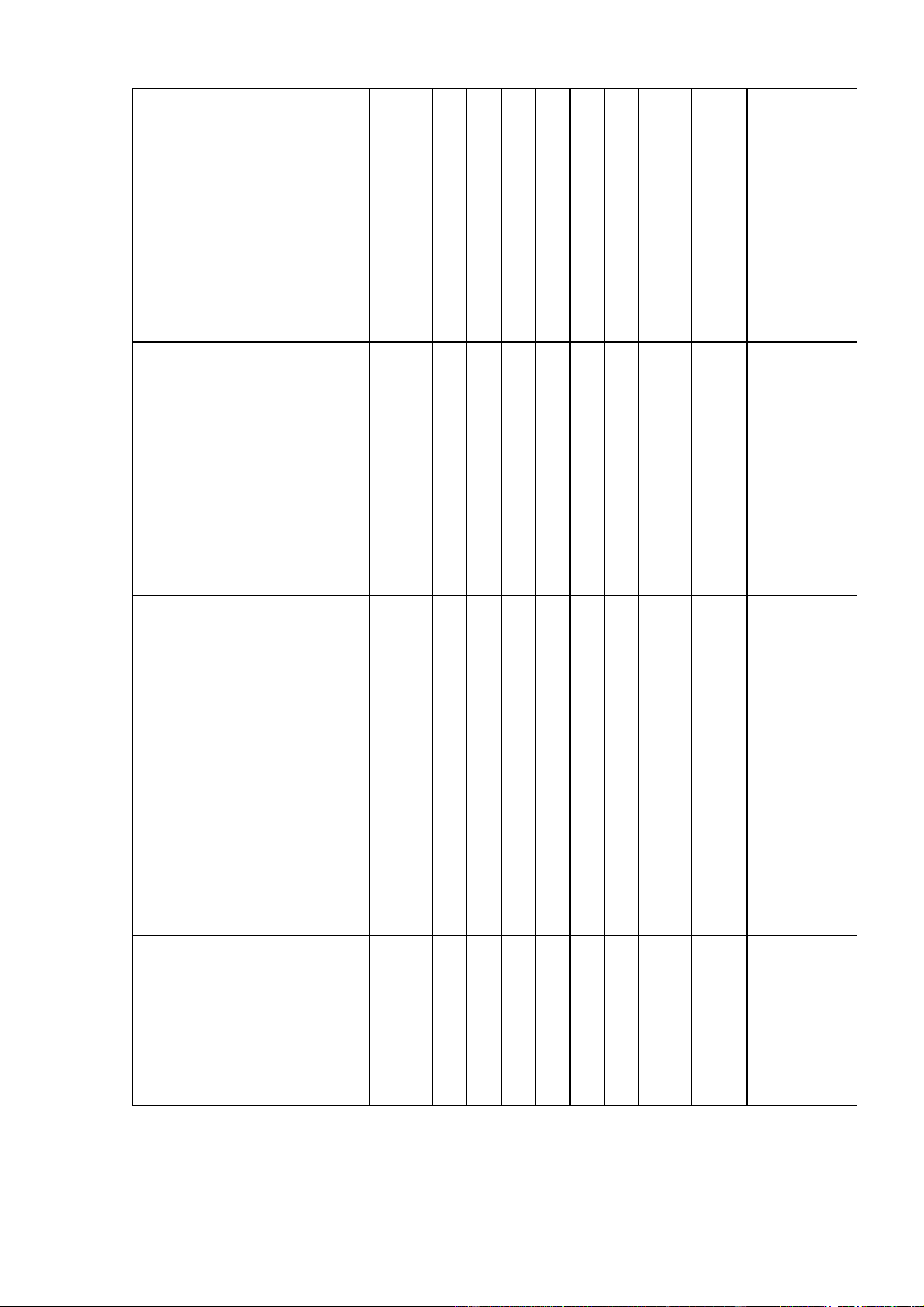

Phân loại các ngắt trong một hệ thống pentium nói riêng, hay một hệ thống vi xử lý

nói chung ược trình bày trên hình 3.5. Ngắt xảy ra từ ba nguyên nhân chính: do ngoại lệ

(exeptions), do các lệnh ngắt ược thực hiện trong chương trình, hoặc do các tín hiệu yêu

cầu ngắt cung cấp từ các thiết bị ngoại vi.

Ngoại lệ là các trường hợp ặc biệt xảy ra trong quá trình hoạt ộng của hệ thống bao gồm:

- Các trạng thái bỏ dở một thao tác hay một tiến trình ang hoạt ộng (Aborts) do xảy ra

lỗi trong hệ thống, thường là lỗi thiếu tài nguyên của hệ thống, hay lỗi hư hỏng một

số dữ liệu mà chỉ ảnh hưởng tới một phần nhỏ của tiến trình hoạt ộng.

- Ngoại lệ còn ược thực hiện ể xử lý các lỗi (Faults) trong quá trình hoạt ộng như: lỗi

chia cho 0, lỗi tràn số nguyên,…

- Ngoại lệ còn xảy ra do các bẫy (Traps), chúng là các quy trình xử lý một số thao tác

ặc biệt trong hệ thống như giám sát các thông số hoạt ộng hiện hành của hệ thống,

chạy từng bước chương trình ể tìm lỗi….

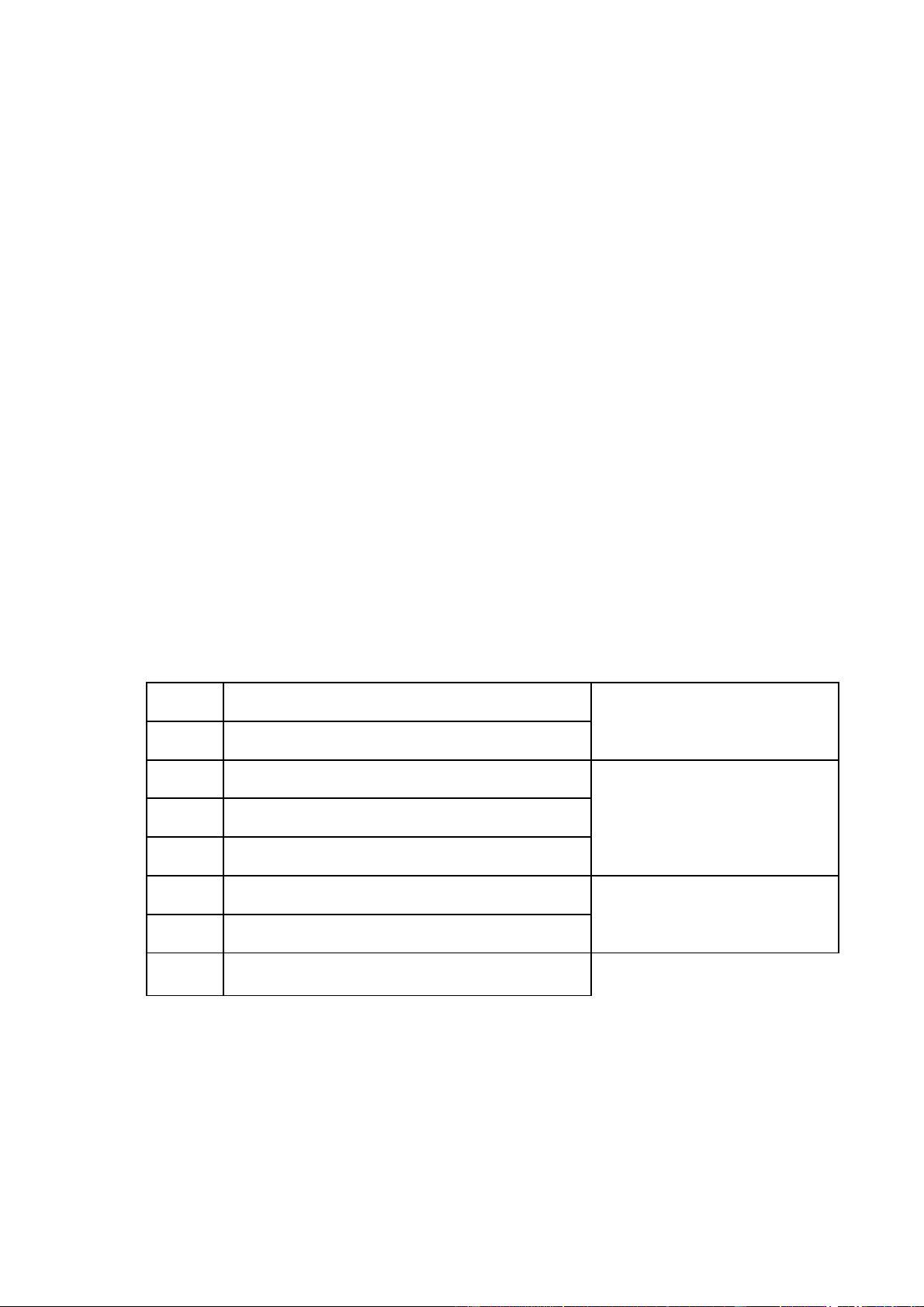

Bảng 3.1: So sánh giữa ngắt và chương trình con

Chương trình ngắt Chương trình con

Khởi tạo bằng cả phần cứng và phần

Chỉ có thể khởi tạo bằng phần mềm mềm lOMoARcPSD| 10435767

Có thể xử lý các sự kiện sắp ặt trước hoặc Chỉ xử lý các sự kiện sắp ặt trước ược viết

không sắp ặt trước, ở bên trong cũng như trong chương trình. bên ngoài hệ thống.

Các ISRs thường trú trong bộ nhớ.

Các chương trình con ược nạp vào bộ nhớ

cùng với chương trình chính.

Sử dụng số ể xác ịnh chương trình phục Sử dụng tên ể xác ịnh chương trình con.

vụ ngắt, gọi là vector ngắt

Thanh ghi cờ ược tự ộng lưu trữ

Không lưu trữ thanh ghi cờ

Các chương trình ngắt thông thường ược thực hiện và thường trú trong bộ nhớ của

hệ thống, ví dụ như các chương trình iều khiển thiết bị trong ROM BIOS máy tính, các

chương trình ngắt của hệ iều hành ược nạp lên bộ nhớ RAM khi hoạt ộng. Do ó, nếu iều

khiển chương trình ược chuyển tới các chương trình này, chúng sẽ ược hoạt ộng giống

như ược chuyển tới bằng cơ chế ngắt. Một số hệ thống vi xử lý cung cấp chức năng

chuyển iều khiển tới các chương trình ngắt bằng các lệnh ngắt mềm.

Khi thực hiện các lệnh này, CPU cũng tiến hành các thao tác giống hết như khi có yêu

cầu từ thiết bị ngoại vi hay khi xảy ra ngoại lệ. Ví dụ lệnh INT n (n=00-ffH) của vi xử

lý intel sẽ chuyển iều khiển tới chương trình ngắt có số hiệu xx.

Hình 3.5: Phân loại các ngắt trong hệ thống vi xử lý

Với các ngắt cứng, là các yêu cầu bằng tín hiệu cung cấp từ các thiết bị ngoại vi,

thông thường các CPU có hai tín hiệu ể nhận các tín hiệu yêu cầu ngắt là: ngắt không

che (NMI - Non Maskable Interrupt), và ngắt có thể che ược bằng phần mềm (INT -

Interrupt). Tín hiệu yêu cầu ngắt NMI có ộ ưu tiên cao hơn INT, và khi nhận ược tín

hiệu NMI thì CPU bắt buộc phải chuyển iều khiển qua chương trình ngắt. Còn khi nhận

ược tín hiệu INT thì CPU sẽ xét cờ chơ phép ngắt, nếu cờ ngắt ã ược lập nó sẽ chuyển

iều khiển qua chương trình ngắt, còn nếu cờ ngắt chưa ược lập thì yêu cầu ngắt sẽ lOMoARcPSD| 10435767

không ược phục vụ. Cờ ngắt có thể ược lập hay xóa bằng lệnh hợp ngữ trong chương

trình, với các công việc quan trọng không cho phép ngắt, người sử dụng có thể cấm ngắt

bằng lệnh xoá cờ cho phép ngắt.

3.3.3 Tổ chức ngắt của các hệ Vi xử lý/Máy tính 3.3.3.1

Tổ chức ngắt của vi xử lý Z80

- Ngắt có thể che:

Trong hệ thống Z80 ngắt INT sẽ tác ộng ở cạnh xuống của tín hiệu ưa tới ngõ vào

INT, và cờ ngắt IFF ã ược thiết lập bằng lệnh EI. Cờ ngắt cũng bị xóa khi chương trình

ngắt ược thực hiện, khi reset, hoặc khi thực hiện lệnh DI. Khi áp ứng ngắt INT CPU

Z80 có thể hoạt ộng ở một trong 3 chế ộ: Mode 0, Mode 2 và Mode 3 tùy thuộc vào

lệnh khởi tạo chế ộ ngắt thực hiện trước khi có tín hiệu yêu cầu ngắt là IM0, IM1 hay IM2.

Mode 0: khi áp ứng ngắt mode 0 CPU Z80 sẽ yêu cầu thiết bị cung cấp một lệnh vào

BUS dữ liệu, thường là lệnh RST (vì khi này cơ chế cung cấp lệnh sẽ ơn giản do chỉ

có một byte), nhưng cũng có thể là một lệnh gọi chương trình con hoặc một lệnh bất kỳ nào ó.

Mode 1: khi áp ứng trong mode này Z80 sẽ nhảy tới ịa chỉ 0038H, tại ịa chỉ này có

thể là chương trình phục vụ ngắt, cũng có thể chỉ là một lệnh nhảy tới chương trình ngắt.

Cũng có thể sử dụng một lệnh nhảy gián tiếp (ví dụ JP (HL)) ể có thể quyết ịnh ịa chỉ

chương trình ngắt trước khi có tín hiệu yêu cầu ngắt.

Mode 2 : Mode này là khả năng áp ứng ngắt mạnh nhất của CPU Z80. Khi khởi ộng

mode này, CPU sẽ thực hiện chương trình phục vụ ngắt tại ịa chỉ chứa trong các ô nhớ

có ịa chỉ cung cấp bởi thanh ghi ịa chỉ trang ngắt I và thiết bị yêu cầu ngắt.

Thanh ghi I cung cấp 8 bit cao, còn thiết bị yêu cầu ngắt sẽ cung cấp 8 bit thấp của ô

nhớ ó. Thực ra thiết bị chỉ cần cung cấp 7 bit cao, còn bit có trọng số nhỏ nhất (D0) luôn

có giá trị là 0, vì giá trị mới trong thanh ghi PC phải ược giữ trong hai ô nhớ liên tiếp. lOMoARcPSD| 10435767 000H . . nnmmH .

Byte th ấ p của ị a chỉ chương trình phụ c vụ ng ắ t UV (UV h)

Byte cao của ị a chỉ chương trình phụ c vụ ng ắ t (XY h) nn mm

Thanh ghi I 7 bit do thi ế t bị cung c ấ p 0 XYUVH Chương trình phụ c vụ ng ắ t

Hình 3.6: Hoạt ộng của ngắt INT mode 2 của Z80.

Dựa theo nguyên tắc hoạt ộng trên, người sử dụng có thể lập một loạt ịa chỉ của các

chương trình phục vụ ngắt cho các thiết bị khác nhau tại một vùng nhớ nào ó gọi là bảng

vector ngắt. Khi hệ thống bắt ầu hoạt ộng có thể nạp ịa chỉ trang ngắt bằng lệnh LD I,A.

Mỗi thiết bị sẽ yêu cầu chương trình phục vụ ngắt của mình bằng cách cung cấp 7 bit ịa

chỉ còn lại. Có thể biểu diễn hoạt ộng của ngắt mode 2 của Z80 trên hình 3.6 :

- Ngắt không che: NMI

Ngắt không che của Z80 sẽ ược thực hiện bất chấp giá trị của cờ ngắt IFF, khi áp

ứng ngắt này cờ ngắt IFF sẽ bị xóa, thanh ghi PC ược nạp vào ỉnh ngăn xếp và iều

khiển chương trình sau ó sẽ chuyển qua ịa chỉ 0066H. Tương tự như ngắt INT mode

1, tại ịa chỉ này có thể là chương trình phục vụ ngắt cũng có thể chỉ là một lệnh nhảy

tới chương trình phục vụ ngắt.

3.3.3.2 Ngắt của vi iều khiển 8051

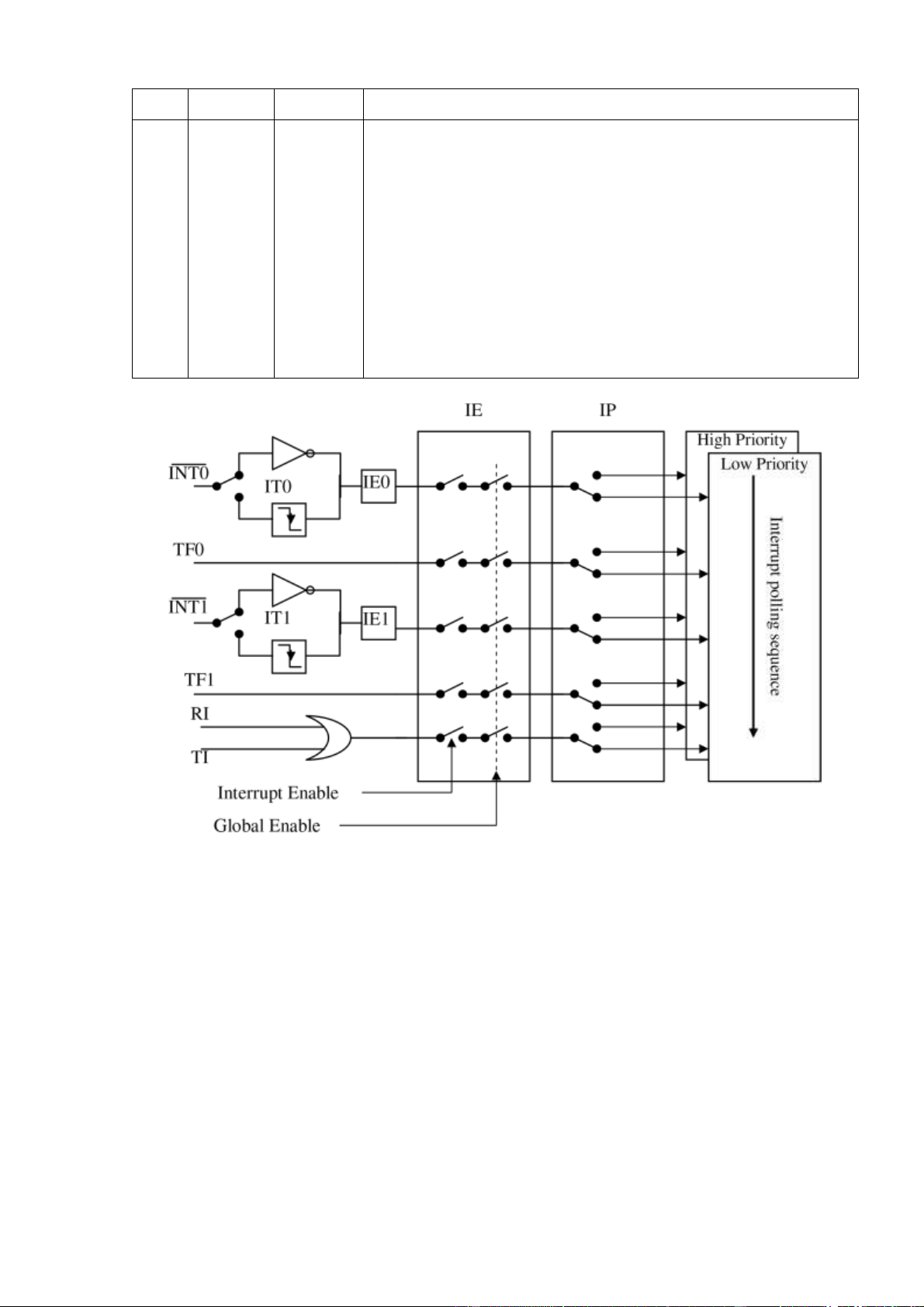

Có 5 nguồn yêu cầu ngắt trong hệ thống 8051: 2 ngắt ngoài, 2 ngắt từ timer và 1 ngắt

cổng nối tiếp. Tất cả các ngắt ều ược mặc ịnh bị cấm sau khi reset hệ thống, và ược cho

phép từng nguồn riêng biệt bằng phần mềm. lOMoARcPSD| 10435767

Khi có hai hoặc nhiều yêu cầu ngắt ồng thời, hoặc một ngắt xảy ra trong khi một

ngắt khác ang ược phục vụ, hệ thống sẽ áp ứng bằng cách xét theo vòng tuần tự và theo

mức ưu tiên ể ịnh trình cho việc thực hiện các ngắt. Vòng tuần tự thì cố ịnh, nhưng ưu

tiên ngắt thì có thể lập trình ược.

Cho phép và cấm các ngắt: Mỗi nguồn ngắt ược cho phép hoặc cấm một cách riêng

biệt qua thanh ghi cho phép ngắt (IE - Interrupt Enable) có ịnh ịa chỉ theo bit ở ịa chỉ

A8H. Mỗi nguồn ngắt sẽ có 1 bit trong thanh ghi IE ể có thể lập trình cho phép riêng

biệt, ngoài ra còn có một bit cho phép/cấm toàn bộ các ngắt (khi ược xóa sẽ cấm tất cả

các ngắt), như trình bày trong bảng 3.2.

Bảng 3.2: Các bit của thanh ghi cho phép ngắt vi iều khiển 8051 Bit Ký hiệu Địa chỉ

Chức năng (1: cho phép; 0: cấm) IE7 EA AFH

Cho phép/cấm toàn bộ các ngắt. IE6 - AEH Không ịnh nghĩa. IE5 - ADH

Dự phòng cho thế hệ kế tiếp. Cho IE4 ES ACH

phép ngắt cổng nối tiếp. IE3 ET1 ABH Cho phép ngắt timer 1. IE2 EX1 AAH

Cho phép ngắt ngoài cấp từ INT1. IE1 ET0 A9H Cho phép ngắt timer 0 IE0 EX0 A8H Cho phép ngắt ngoài INT0

Như vậy khi muốn cho phép bất kỳ ngắt nào cần phải lập hai bit: bit cho phép riêng

và bit cho phép toàn bộ. Ví dụ, các ngắt từ Timer 1 ược cho phép như sau: SETB ET1

; Cho phép ngắt từ Timer 1

SETB EA ; Đặt bit cho phép toàn bộ.

Cũng có thể sử dụng lệnh sau: MOV IE, # 10001000B

Mặc dù hai cách này có cùng kết quả sau khi reset hệ thống, nhưng chúng sẽ có kết quả

sẽ khác nếu IE ược ghi ở giữa chương trình. Cách thứ nhất không ảnh hưởng ến 5 bit

khác trong thanh ghi IE, trái lại cách thứ hai sẽ xóa các bit khác. Nên việc khởi tạo giá

trị cho IE theo cách thứ hai thường sử dụng ở ầu chương trình (nghĩa là sau khi cấp

nguồn hoặc reset hệ thống), còn khi muốn cho phép và cấm các ngắt ngay trong chương

trình thì nên dùng cách thứ nhất, ể tránh ảnh hưởng ến các bit khác trong thanh ghi IE.

Ưu tiên ngắt: Mỗi nguồn ngắt ược lập trình riêng vào một trong hai mức ưu tiên qua

thanh ghi ưu tiên ngắt IP (Interrupt Priority) ược ịa chỉ theo bit ở ịa chỉ B8H. Chức năng

các bit của IP ược mô tả trong bảng 3.3.

Bảng 3.3: Các bit thanh ghi ưu tiên ngắt vi iều khiển 8051 lOMoARcPSD| 10435767 Bit Ký hiệu Địa chỉ

Chức năng (1: mức ưu tiên cao; 0: mức ưu tiên thấp) IP7 - - Không ịnh nghĩa. IP6 - - Không ịnh nghĩa. IP5 - BDH Dự phòng. IP4 PS BCH

Ưu tiên cho ngắt cổng nối tiếp. IP3 PT1 BBH Ưu tiên cho ngắt timer 1. IP2 PX1 BAH

Ưu tiên cho ngắt ngoài INT1. IP1 PT0 B9H Ưu tiên cho ngắt timer 0. IP0 PX0 B8H

Ưu tiên cho ngắt ngoài INT0.

Hình 3.7: Cơ chế ngắt của 8051.

IP mặc ịnh bị xóa sau khi reset hệ thống ể ặt tất cả các ngắt ở mức ưu tiên thấp. Việc

“ưu tiên” cho phép một ISR sẽ bị ngắt bởi một ngắt khác, nếu ngắt này có ộ ưu tiên cao

hơn ngắt ang phục vụ. Điều này thực hiện dễ dàng trên 8051, vì chỉ có hai mức ưu tiên.

Nếu một ISR có ưu tiên thấp ang thực thi, khi một ngắt có ưu tiên cao xảy ra thì ISR

hiện hành sẽ bị ngắt. ISR có ưu tiên cao không thể bị ngắt.

Chương trình chính thực hiện ở mức cơ sở và không liên hệ với bất cứ ngắt nào, nó có

thể luôn bị ngắt, bất chấp ưu tiên của ngắt. Nếu hai ngắt có ộ ưu tiên khác nhau xảy ra

ồng thời, thì ngắt có ộ ưu tiên cao hơn sẽ ược phục vụ trước.

Vòng ưu tiên tuần tự: Nếu hai ngắt cùng ộ ưu tiên xảy ra ồng thời, vòng tuần tự sẽ xác

ịnh ngắt nào ược phục vụ trước. Vòng tuần tự ược qui ịnh là: INT 0, Timer 0,

INT 1, Timer 1, cổng nối tiếp. lOMoARcPSD| 10435767

Hình 3.7 minh họa các cơ chế phục vụ của 5 nguồn ngắt,. Trạng thái của tất cả các nguồn

ngắt khả dụng qua các bit cờ tương ứng trong các SFR. Dĩ nhiên, nếu có bất kỳ ngắt nào

bị cấm, ngắt không xảy ra, nhưng phần mềm vẫn có thể kiểm tra cờ ngắt.

Ngắt cổng nối tiếp có từ logic OR của ngắt thu (RI) và ngắt phát (TI). Các bit cờ tạo

các ngắt ược tóm tắt ở bảng 3.4.

Bảng 3.4: Các cờ ngắt của vi iều khiển 8051 Ngắt Cờ SFR và vị trí bit INT0 IE0 TCON.1 INT1 IE1 TCON.3 Timer 1 TF1 TCON.7 Timer 0 TF0 TCON.5 Serial port TI SCON.1 Serial port RI SCON.0

Các vector xử lý ngắt.

Khi một ngắt xảy ra và ược CPU chấp nhận, chương trình chính sẽ bị ngắt quãng và

những hoạt ộng sau xảy ra:

- Hoàn tất việc thực thi lệnh hiện hành. - Cất PC vào ngăn xếp.

- Trạng thái ngắt hiện hành ược cất bên trong.

- Các ngắt bị chặn ở mức ngắt.

- Nạp vào PC ịa chỉ vector của ISR. - ISR thực thi.

ISR thực thi và áp ứng các yêu cầu của ngắt. ISR hoàn tất bằng lệnh RETI (quay về

từ ngắt). Điều này làm lấy lại giá trị cũ của PC từ ỉnh ngăn. Việc thực hiện chương trình

chính tiếp tục ở chỗ mà nó ã bị dừng. Các vector ngắt.

Khi chấp nhận ngắt, giá trị ược nạp vào PC ược gọi là vector ngắt. Nó là ịa chỉ bắt

ầu của ISR cho nguồn tạo ngắt. Các vector ngắt ược cho ở bảng 3.5. Ngắt Cờ Địa chỉ vector ngắt lOMoARcPSD| 10435767 Bảng 3.5: Reset RST 0000H INT0 IE0 0003H Các vector Timer 0 TF0 000BH ngắt của vi INT1 IE1 0013H iều khiển Timer 1 TF1 001BH 8051 Serial port RI hoặc TI 0023H Bộ nhớ chương trình bên ngoài. LJMP main FFFF Chương trình chính 0030

002F Điểm bắt ầu sau khi reset và khi xảy ra ắt các ng

Hình 3.8: Tổ chức bộ nhớ chương trình khi sử dụng các ngắt. lOMoARcPSD| 10435767

Vector reset hệ thống (RST ở ịa chỉ 0000H) có trong bảng, vì nó giống ngắt, nó ngắt

chương trình chính và nạp giá trị mới cho PC bằng 0.

Khi chuyển ến một chương trình ngắt, cờ gây ngắt tự ộng ược xóa bởi phần cứng.

Ngoại lệ chỉ có RI và TI của các ngắt cổng nối tiếp cần ược xoá bằng phần mềm. Vì có

tới hai nguồn có thể xảy ra cho ngắt cổng nối tiếp, nên CPU không xóa cờ ngắt này. Các

bit phải ược kiểm tra trong ISR ể xác ịnh nguồn ngắt và cờ tạo ngắt sẽ ược xóa bằng

phần mềm. Thông thường sẽ có một lệnh rẽ nhánh thích hợp tuỳ theo nguồn ngắt. Vì

các vector ngắt ở phần ầu của bộ nhớ chương trình, nên lệnh ầu tiên của chương trình

chính thường là lệnh nhảy qua vùng nhớ này, ví dụ như LJMP 0030H.

Thiết kế chương trình dùng các ngắt.

Khung một chương trình sử dụng ngắt có thể thực hiện như sau: ORG 0000H ; Điểm vào reset LJMP MAIN … ; Các iểm vào ISR ORG 0030H

; Điểm vào chương trình chính … MAIN:

; Bắt ầu chương trình chính. … …

Lệnh ầu tiên nhảy ến ịa chỉ 0030H, vừa qua các vị trí vector bắt ầu của các ISR. Như

trình bày trên hình 8.19, chương trình chính bắt ầu ở ịa chỉ 0030H. Các chương trình

phục vụ ngắt có kích thước nhỏ: Các chương trình phục vụ ngắt phải bắt ầu ở gần phần

ầu của bộ nhớ chương trình, dưới các ịa chỉ trong bảng Các vector ngắt. Mặc dù chỉ có

8 byte ở giữa các iểm vào ngắt, có thể ủ ể thực hiện hoạt ộng phục vụ ngắt mong muốn

và quay về chương trình chính.

Nếu chỉ có một nguồn ngắt ược sử dụng, ví dụ Timer 0, thì có thể sử dụng một khung chương trình như sau: ORG 0000H ; Reset LJMP MAIN ORG 000BH ; Điểm vào Timer 0

T0ISR: ; Bắt ầu ISR cho Timer 0 RETI

; Quay về chương trình chính

MAIN: ; Chương trình chính

Nếu sử dụng nhiều ngắt, cần phải bảo ảm mỗi chương trình phục vụ ngắt bắt ầu ở

úng ịa chỉ ã qui ịnh cho nó, và không chạy quá sang ISR kế. Trong ví dụ trên, vì chỉ có

một ngắt ược sử dụng, chương trình chính có thể bắt ầu ngay sau lệnh RETI. Các chương

trình phục vụ ngắt có kích thước lớn: Nếu ISR dài hơn 8 byte, cần có lệnh nhảy ể chuyển lOMoARcPSD| 10435767

nó tới nơi khác trong bộ nhớ chương trình, nếu không nó sẽ i lố qua iểm vào của ngắt

kế. Với lệnh nhảy ến vùng nhớ khác, có thể mở rộng chiều dài ISR. Ví dụ chỉ xét Timer

0, có thể sử dụng khung chương trình sau: ORG 0000H

; Điểm bắt ầu sau khi reset LJMP MAIN ORG 000BH

; Điểm bắt ầu của ngắt Timer 0 LJMP T0ISR ORG 0030H

; Dưới các vector ngắt tiếp theo MAIN: … T0ISR: ; ISR cho Timer 0 … RETI

; Quay về chương trình chính.

Xét một chương trình ơn giản nhất không thực hiện gì cả, chương trình chính chỉ

khởi ộng các timer, cổng nối tiếp và các thanh ghi ngắt sau ó không làm gì nữa. Công

việc hoàn toàn ược thực hiện trong các ISR. Sau các lệnh khởi ộng, chương trình chính

chứa lệnh: HERE: SJMP HERE

Hay dạng viết gọn như sau: SJMP $

Khi ngắt xảy ra, chương trình chính bị ngắt quãng tạm thời, trong khi ISR thực hiện.

Lệnh RETI ở cuối ISR trả iều khiển về chương trình chính và nó tiếp tục không làm gì

cả. Trong nhiều ứng dụng iều khiển, nhiều công việc thật ra ược thực hiện hoàn toàn trong các ISR.

Khi cần các công việc thực hiện ngoài ngắt, lệnh SJMP $ (HERE: SJMP HERE) có

thể ược thay thế bằng các lệnh cần thực hiện trong ứng dụng. Các ngắt của 8051.

Các ngắt timer: Các ngắt timer có ịa chỉ vector ngắt là 000BH (Timer 0) và 001BH

(Timer 1). Ngắt timer xảy ra khi các thanh ghi timer (TLx/THx) tràn và lập cờ báo tràn

(TFx) lên 1. Chú ý rằng các cờ timer (TFx) không cần phải xóa bằng phần mềm. Khi

cho phép các ngắt, TFx tự ộng bị xóa bằng phần cứng khi CPU chuyển ến ISR.

Các ngắt cổng nối tiếp: Ngắt cổng nối tiếp xảy ra khi hoặc cờ ngắt phát (TI) hoặc cờ

ngắt thu (RI) ược ặt lên 1. Ngắt phát xảy ra khi truyền xong một ký tự vừa ược ghi vào

SBUF. Ngắt thu xảy ra khi một ký tự ã ược nhận xong và ang ợi trong SBUF ể ược ọc.

Ngắt cổng nối tiếp khác với ngắt timer là cờ gây ra ngắt không bị xóa bằng phần cứng

khi CPU chuyển tới ISR. Nguyên nhân là do có hai nguồn ngắt cổng nối tiếp: TI và RI.

Nguồn ngắt phải ược xác ịnh trong ISR và cờ tạo ngắt cần ược xóa bằng phần mềm.

Các ngắt ngoài: Các ngắt ngoài xảy ra khi có một mức thấp hoặc cạnh xuống trên chân

INT0 hoặc INT1 của 8051. Các cờ tạo các ngắt này là các bit IE0 và IE1 trong TCON.

Khi quyền iều khiển ã chuyển ến ISR, cờ tạo ra ngắt chỉ ược xóa nếu ngắt ược tích cực lOMoARcPSD| 10435767

bằng cạnh xuống. Nếu ngắt ược tích cực theo mức, thì mức cao của nguồn yêu cầu ngắt

bên xoá cờ thay cho phần cứng. Việc chọn ngắt tích cực mức thấp hay tích cực cạnh

xuống ược lập trình qua các bit IT0 và IT1 trong TCON. Ví dụ, nếu IT1 = 0, ngắt ngoài

1 ược kích khởi bằng mức thấp ở chân INT1. Nếu IT1 = 1, ngắt ngoài 1 sẽ ược kích khởi

bằng cạnh xuống. Trong chế ộ này, nếu các mẫu liên tiếp trên chân INT1 chỉ mức cao

trong một chu kỳ và thấp trong chu kỳ kế, cờ yêu cầu ngắt IE1 trong TCON ược ặt lên

1. Rồi bit cờ IE1 yêu cầu ngắt. Vì các chân ngắt ngoài ược lấy mẫu một lần ở mỗi chu

kỳ máy, ngõ vào cần ược giữ trong tối thiểu 12 chu kỳ dao ộng ể bảo ảm lấy mẫu úng.

Nếu ngắt ngoài ược tác ộng theo cạnh xuống, nguồn bên ngoài phải giữ chân yêu cầu

cao tối thiểu 1 chu kỳ và giữ nó ở mức thấp thêm một chu kỳ nữa ể bảo ảm phát hiện

ược cạnh xuống. IE0 và IE1 tự ộng ược xóa khi CPU chuyển tới ngắt. Nếu ngắt ngoài

ược tác ộng theo mức, nguồn bên ngoài phải giữ yêu cầu tác ộng cho ến khi ngắt ược

yêu cầu thật sự ược tạo ra. Rồi nó phải không tác ộng yêu cầu trước khi ISR ược hoàn

tất, nếu không một ngắt khác sẽ ược lặp lại. Thông thường khi vào ISR người ta làm

nguồn yêu cầu ưa tín hiệu tạo ngắt về trạng thái không tác ộng.

3.3.3.3 Cơ chế ngắt của CPU Intel x86 Khái quát:

Giống như vi xử lý Pentiumm một yêu cầu ngắt trong hệ thống x86 cũng có thể cung

cấp từ một trong 3 nguồn: ngắt cứng INTR (Interrupt Request) hoặc NMI. Ngắt mềm

bằng một lệnh ngắt trong chương trình (INT), và ngoại lệ xuất phát từ một số iều kiện

lỗi trong một số lệnh mà chương trình thực hiện.

Tại cuối mỗi chu kỳ thực hiện lệnh x86 sẽ kiểm tra các yêu cầu ngắt. Khi có yêu cầu

8086 sẽ áp ứng bằng các bước sau:

- Nạp thanh ghi cờ vào ỉnh ngăn xếp và giảm thanh ghi con trỏ ngăn xếp i 2.

- Không cho phép ngắt INT bằng cách xóa cờ ngắt IF trong thanh ghi cờ.

- Xóa cờ bẫy TF trong thanh ghi cờ.

- Nạp thanh ghi oạn lệnh CS vào ỉnh ngăn xếp và giảm con trỏ ngăn xếp i 2.

- Nạp thanh ghi con trỏ lệnh IP vào ỉnh ngăn xếp và giảm con trỏ ngăn xếp i 2. - Nhảy

xa tới chương trình con phục vụ ngắt tương ứng theo yêu cầu. lOMoARcPSD| 10435767 Chương trình chính PUSH FLAGS

Chương trình phụ c vụ ng ắ t CLEAR IF CLEAR TF PUSH các thanh ghi PUSH CS PUSH IP Nhả y t ới chương trình ng ắ t POP IP POP CS POP FLAGS POP các thanh ghi IRET

Hình 3.9: Qui trình phục vụ ngắt của 8086/8088.

Quá trình trên ược tổng kết trong hình 3.9. Như trên hình vẽ, x86 cất thanh ghi cờ

vào ỉnh ngăn xếp, không cho phép ngõ vào yêu cầu ngắt INTR và chức năng chạy từng

bước, rồi thực hiện lệnh gọi xa tới chương trình phục vụ ngắt. Lệnh IRET tại cuối

chương trình phục vụ ngắt sẽ chuyển iều khiển quay về chương trình chính.

Như ã biết khi thực hiện lệnh gọi xa x86 sẽ lập giá trị mới cho thanh ghi oạn CS và

thanh ghi con trỏ lệnh IP. Để thực hiện việc gọi xa gián tiếp, 8086 lấy giá trị mới cho

CS và IP từ 4 ô nhớ. Tương tự như vậy, khi áp ứng ngắt x86 cũng lấy ịa chỉ chương

trình ngắt từ 4 ô nhớ liên tiếp. Trong hệ thống x86, 1KB bộ nhớ từ ịa chỉ 00000H tới

ịa chỉ 003FFH ược dành riêng ể chứa các ịa chỉ của các chương trình ngắt ược gọi là

bảng vector ngắt, hay bảng con trỏ ngắt. Mỗi ịa chỉ sẽ chứa trong 4 ô nhớ, nên bảng này

sẽ chứa ược ịa chỉ của 256 chương trình ngắt. Hình 3.10 trình bày bảng vector ngắt. Chú

ý là giá trị nạp cho thanh ghi con trỏ lệnh (IP) luôn ặt tại ịa chỉ thấp, còn cho thanh ghi

oạn lệnh (CS) nằm ở ịa chỉ cao. Mỗi từ kép cho một vector ngắt ược nhận dạng bằng

một số trong khoảng từ 0 tới 255. Nó ược gọi là số hiệu ngắt hay số kiểu ngắt.

Trong bảng 5 vector ngắt ầu tiên dành cho các ngắt ặc biệt, các vector từ 5 tới 31 dự

phòng cho các thế hệ vi xử lý sau của Intel, các vector từ 32 tới 255 ã ược sử dụng cho

các ngắt cứng và các ngắt mềm. Do mỗi vector ngắt gồm 4 byte, vì thế x86 sẽ xác ịnh

ịa chỉ của các vector ngắt trong bảng bằng cách nhân số hiệu ngắt với 4. Người sử dụng

cũng có thể thay thế ịa chỉ chương trình của mình vào bảng vector ngắt, lúc này mỗi lần

xảy ra ngắt iều khiển sẽ ược chuyển tới chương trình của người sử dụng thay vì chuyển

tới chương trình phục vụ ngắt cũ. lOMoARcPSD| 10435767 03FFH 244 vector Con trỏ ngắt kiểu 255 ngắt ã sử 03FCH dụng Con trỏ ngắt kiểu 33 084H Con trỏ ngắt kiểu 32 080H 27 vector

Con trỏ ngắt kiểu 31 (dự trữ) ngắt dự phòng

Con trỏ ngắt kiểu 5 (dự trữ) 014H

Con trỏ ngắt kiểu 4 (tràn) 010H

Con trỏ ngắt kiểu 3 (1byte lệnh INT) 5 vector ngắt dành

Con trỏ ngắt kiểu 2 (ngắt không che) 00CH

Con trỏ ngắt kiểu 1 (chạy từng bước) riêng 008H

Con trỏ ngắt kiểu 0 (lỗi chia) 004H 000H

Hình 3.10: Bang vector ng̉ ắt trong h tḥ ông 8086/8088.́

Các kiểu ngắt của x86

- Ngắt 0 - chia cho 0

X86 sẽ tự ộng thực hiện ngắt kiểu 0 khi kết quả các phép chia vượt quá khả năng

chứa trong thanh ghi ích. Khi ó các cờ, CS, IP sẽ ược nạp vào ỉnh ngăn xếp, IF và TF

sẽ bị xóa. Sau ó CS và IP sẽ ược nạp giá trị mới từ các ịa chỉ

00002Hvà 00000H trong bảng vector ngắt. Vì ngắt 0 xảy ra một cách tự ộng không thể

cấm ược, do ó ể tránh ngắt này trong chương trình phải kiểm tra ể chắc rằng số chia

khác 0. Hoặc viết một chương trình phục vụ ngắt mới, sau ó ổi vector ngắt hiện có trong

bảng, nhưng khi ó chương trình sẽ khá phức tạp.

- Ngắt 1: Chạy từng bước

Ngắt này sẽ thực hiện chương trình theo từng lệnh, khi này có thể xem nội dung của

các ô nhớ và các thanh ghi ể kiểm tra kết quả của lệnh. Khi lệnh ã thực hiện úng có thể

cho phép CPU thực hiện lệnh tiếp theo. Nói cách khác trong chế ộ chạy từng bước x86

ngưng lại sau khi chạy xong mỗi lệnh, và chờ quyết ịnh tiếp theo từ người sử dụng. Nhờ

việc lập xóa thanh ghi cờ nên thủ tục chạy từng bước thực hiện khá dễ dàng trong hệ

thống x86. Khi cờ bẫy ược lập, 8086 sẽ tự ộng thực hiện ngắt lOMoARcPSD| 10435767

1 sau khi thực hiện xong một lệnh, với vector ngắt ược lấy trong bảng vector ngắt tại các

ịa chỉ từ 00004H tới 00008H. Khi ó cờ bẫy sẽ ược lập các thanh ghi ược lưu vào ỉnh

ngăn xếp, chương trình con phục vụ cho ngắt 1 sẽ tùy thuộc theo hệ thống.

Chú ý là không có lệnh thiết lập hay xóa cờ bẫy, muốn thực hiện công việc trên cần

nạp thanh ghi cờ vào ỉnh ngăn xếp sau ó sử dụng một lệnh xử lý dữ liệu ể lập bit, và

cuối cùng phục hồi lại thanh ghi cờ từ ỉnh ngăn xếp. Trong quá trình thực hiện chương

trình phục vụ ngắt cờ bẫy sẽ ược xóa. -

Ngắt 2: Phục vụ ngắt không che x86 sẽ tự ộng thực hiện ngắt 2 khi nhận ược

một cạnh lên tại ngõ vào NMI. Ngắt này luôn ược thực hiện mà không bị che bởi phần

mềm, vì thế ngắt này thường ược sử dụng cho các công việc quan trọng. Ví dụ có thể

sử dụng ngắt 2 ể lưu chương trình khi mất nguồn. -

Ngắt 3 : Thiết lập iểm dừng trong chương trình.

Ngắt này ược sử dụng cho việc gỡ rối một chương trình. Khi chèn vào chương trình

một iểm dừng hệ thống sẽ thực hiện các lệnh của chương trình cho tới iểm dừng rồi

chuyển iều khiển qua thủ tục ngắt 3. Tùy theo từng hệ thống, thủ tục ngắt

3 có thể gửi nội dung các thanh ghi, hoặc các ô nhớ lên màn hình rồi chờ cho tới khi

nhận ược lệnh kế tiếp từ người sử dụng.

- Ngắt 4 : Ngắt tràn

Cờ tràn OF của x86 sẽ tự ộng ược thiết lập sau khi thực hiện các phép tính số học

mà kết quả có sự tràn bit 1 qua bit có trọng số lớn nhất. Ví dụ khi cộng 01101100

(108 thập phân) với 01010001 (81 thập phân) kết quả sẽ là 10111101 (189 thập phân).

Kết quả này chỉ úng ối với phép cộng số nhị phân không dấu, mà không úng ối với số

nhị phân có dấu. Đối với số nhị phân có dấu, bit cao nhất bằng 1 sẽ chỉ thị số âm và

giá trị sẽ là bù 2, như vậy kết quả ở trên sẽ là -67 thập phân. Có hai cách ể phát hiện và

áp ứng một lỗi tràn. Cách thứ nhất có thể sử dụng lệnh JO (nhảy khi cờ tràn = 1) ngay

sau các lệnh số học, nếu cờ tràn ược thiết lập sau lệnh số học iều khiển chương trình sẽ

ược chuyển tới ịa chỉ thị trong lệnh JO ể có thể xử lý lỗi tràn. Cách thứ hai là việc phát

hiện và áp ứng một lỗi tràn ược ặt vào một ngắt. Trong chương trình sau các lệnh số học

sẽ ặt lệnh INT 0 ể chuyển tới chương trình ngắt khi cờ ngắt ược lập.

- Các ngắt mềm từ 0 tới 255

Lệnh INT của x86 có thể sử dụng ể gọi các ngắt mềm từ 0 tới 255. Ngắt ược gọi sẽ chỉ

thị bằng số hiệu của nó trong lệnh INT, ví dụ INT 32H sẽ gọi chương trình ngắt 32H.

Địa chỉ chương trình ngắt trong bảng vector ngắt sẽ nằm tại ịa chỉ bằng số hiệu ngắt

nhân 4. Lệnh INT có nhiều cách sử dụng, có thể dùng INT 0 ể chạy thử chương trình

phục vụ ngắt chia cho 0, mà không cần phải thực hiện lệnh chia cho 0 thực sự, hoặc

cũng có thể thử chương trình ngắt NMI bằng lệnh INT 2 mà không cần có tín hiệu yêu

cầu ngắt ưa vào chân NMI. lOMoARcPSD| 10435767

- Các yêu cầu ngắt 0 tới 255

Ngõ vào INTR của x86 cho phép nhận các tín hiệu yêu cầu ngắt từ bên ngoài ể thực

hiện các chương trình ngắt tương ứng với chúng. Khác với ngõ vào NMI, INTR có thể

che ược bằng phần mềm. Nếu cờ ngắt IF bị xóa thì các yêu cầu ưa tới INTR sẽ không

ược áp ứng. Cờ ngắt IF có thể thiết lập bằng lệnh STI, và xóa bằng lệnh CLI. Khi

reset cờ ngắt IF sẽ tự ộng ược xóa, như vậy trước khi muốn 8086 áp ứng ngắt cần phải lập IF.

Khi chuyển iều khiển qua chương trình ngắt, cờ ngắt cũng tự ộng ược xóa. Điều này

ược thực hiện do 2 nguyên nhân sau: nguyên nhân thứ nhất là do nếu không xóa cờ ngắt

thì khi chương trình phục vụ một ngắt này ang thực hiện có thể sẽ có một yêu cầu ngắt

mới, làm iều khiển chương trình sẽ chuyển tiếp tới một chương trình ngắt mới nữa.

Nếu muốn iều ó xảy ra thì chỉ việc thực hiện lệnh lập IF tại ầu chương trình ngắt.

Nguyên nhân thứ hai là nếu không xóa IF thì khi trạng thái mức cao tại ngõ vào INTR

còn ược giữ chương trình ngắt sẽ bị gọi lại trong chính nó nhiều lần. Lệnh IRET tại

cuối chương trình ngắt sẽ phục hồi thanh ghi cờ, iều này làm cho cờ ngắt trở về mức 1

tiếp tục cho phép x86 áp ứng ngắt.

3.3.3.4 Ngắt của máy tính

Để nhận ược nhiều yêu cầu ngắt hệ thống máy tính sử bộ iều khiển ưu tiên ngắt (PIC

– Priority Interrupt Controller). PIC sẽ nhận một trong các ường yêu cầu ngắt IR ể gửi

tới chân yêu cầu ngắt INTR của CPU. Nếu cờ IF ược lập CPU sẽ trả lời yêu cầu ngắt

bằng tín hiệu INTA (Interrupt Acknowledge), sau ó nó sẽ ọc vào vector ngắt cung cấp

từ PIC qua các ường dữ liệu thấp D0 tới D7. Vector ngắt chính là số hiệu ngắt ược lập

trình trước trong PIC nó sẽ ược nhân với 4 ể xác ịnh vị trí chứa ịa chỉ chương trình

phục vụ ngắt trong bảng vector ngắt. Khi có ồng thời 2 hoặc nhiều nguồn yêu cầu ngắt,

CPU sẽ áp ứng cho ngắt có ộ ưu tiên cao nhất, sau ó sẽ tới các ngắt có ộ ưu tiên tiếp

theo. Độ ưu tiên của các ngắt cũng ược lập trình trước trong PIC. Bộ iều khiển ưu tiên

ngắt sử dụng trong hệ thống máy tính là vi mạch 8259 có sơ ồ khối trên hình 3.11. lOMoARcPSD| 10435767 INTA INT DATA BUS BUFFER CONTROL LOGIC D0 - D7 RD READ/WRITE LOGIC IN IR0 WR SERVICE PRIORITY A0 INTERRUPT REQUEST REG RESOLVER REG ( ISR) (IRR ) IR7 CS CASCADE CAS0 BUFFER / CAS1 INTERRUPT MASK REG COMPARATOR I ( MR) CAS2 CP/EN

Hình 3.11: Sơ ồ khối bộ iều khiển ngắt 8259.

Trước hết xem xét chức năng của các tín hiệu. Các tín hiệu của 8259 ược chia thành 3 nhóm chính:

- Bus dữ liệu D0 - D7 sử dụng ể CPU lập trình 8259 hoạt ộng theo các chế ộ khác

nhau, và theo chiều ngược lại sử dụng ể 8259 cung cấp vector ngắt tới CPU.

- Các tín hiệu yêu cầu ngắt IR0 - IR7 nhận tín hiệu yêu cầu ngắt từ các thiết bị. -

Các tín hiệu iều khiển bao gồm :

+ RD, WR nhận iều khiển từ CPU ể xác ịnh chiều truyền dữ liệu giữa CPU và 8259.

+ A0 xác ịnh các vị trí khác nhau trong 8259 truyền nhận dữ liệu với CPU. CS chọn

mạch: nhận tín hiệu từ giải mã ịa chỉ chọn mạch cho phép 8259 ược phép hoạt ộng.

+ CAS0 - CAS3 (Cascade): tín hiệu sử dụng cho việc ghép tầng 8259.

+ SP/EN: khi 8259 làm việc ở chế ộ không có ệm trên bus dữ liệu thì tín hiệu này sử

dụng ể chọn 8259 là mạch chủ hay mạch tớ. Còn khi 8259 có ệm thì tín hiệu này óng

vai trò là tín hiệu cho phép EN ể mở cổng ệm dữ liệu tại thời iểm thích hợp. + INT sử

dụng cung cấp yêu cầu ngắt tới CPU, INTA nhận tín hiệu chấp nhận tín hiệu yêu cầu ngắt từ CPU. lOMoARcPSD| 10435767

Chức năng các thanh ghi bên trong 8259 bao gồm: -

Thanh ghi mặt nạ ngắt (IMR) sử dụng ể cho phép (unmask) hoặc không cho phép

(mask) phục vụ các ngõ vào yêu cầu ngắt. Mỗi bit trong thanh ghi này sẽ tương ứng

với một ngõ vào yêu cầu ngắt. Có thể không cho phép một ngõ vào ó bằng cách ghi 0

tới bit tương ứng của nó trong IMR. -

Thanh ghi yêu cầu ngắt (IRR) sẽ giữ lại các yêu cầu ngắt của các ngõ vào. Khi

có tín hiệu yêu cầu ngắt ưa tới ngõ vào nào thì bit tương ứng của nó trong thanh ghi

này sẽ ược lập lên 1. -

Thanh ghi phục vụ ngắt (ISR) sẽ lưu trạng thái các ngõ vào yêu cầu ngắt ang ược

phục vụ. Bit tương ứng trong thanh ghi sẽ ược lập tương ứng với ngõ vào ang ược phục vụ. -

Khối xử lý ưu tiên (Priority resolver) sẽ óng vai trò quyết ịnh yêu cầu tại ngõ vào

nào ược phục vụ, bằng cách xem xét các bit trong các thanh ghi IMR, ISR và IRR.

Ví dụ: giả sử IR2 và IR4 không bị che và có một tín hiệu yêu cầu ngắt ưa tới ngõ

vào IR4. Yêu cầu trên IR4 sẽ lập bit thứ 4 trong thanh ghi IRR lên 1. Trước tiên bộ xử

lý ưu tiên xem bit tương ứng với nó trong thanh ghi IMR, nếu bit này bằng 1 yêu cầu

ngắt bị che và sẽ không ược phục vụ. Nếu bằng 0 bộ xử lý ưu tiên sẽ kiểm tra các bit

trong thanh ghi ISR ể xem có ngõ vào nào có mức ưu tiên cao hơn ang ược phục vụ hay

không. Nếu có một ngõ vào có mức ưu tiên cao hơn ang ược phục vụ thì bộ xử lý ưu

tiên sẽ không tạo ra tác ộng nào cả. Ngược lại nếu không có yêu cầu ngắt ưu tiên cao

hơn ang ược phục vụ thì bộ xử lý ưu tiên sẽ chuyển mạch cho tín hiệu yêu cầu ngắt

gửi tới CPU. Khi CPU áp ứng bằng tín hiệu trả lời INTA, 8259 sẽ gửi số hiệu ngắt ã

ược lập trình từ trước tới CPU theo Bus dữ liệu. Lập trình cho 8259.

Để 8259 có thể hoạt ộng ược, thì sau khi cấp nguồn nó phải ược lập trình từ 2 tới

4 từ iều khiển ICW (Input Control Word), và sau ó là các từ iều khiển OCW (Output

Control Word). Các từ iều khiển sẽ ịnh nghĩa các chế ộ hoạt ộng cụ thể cho 8259, chúng ược ịnh nghĩa như sau:

Các từ iều khiển ICW: ICW1

Bit D0 (IC4) xác ịnh 8259 ược nối với họ vi xử lý nào. Khi nối với hệ thống

16/32 bit 8086/8088 thì nhất thiết phải cần ICW4 (IC4=1), còn ối với hệ thống 8 bit

8080/8085 thì IC4=0 và như vậy các bit của ICW4 sẽ bị xóa về 0. Bit D1 (SNGL) ịnh

nghĩa 8259 hoạt ộng trong chế ộ chỉ có 1 mạch chủ hay có thêm các mạch tớ. D2 (ADI)

ịnh nghĩa khoảng cách ịa chỉ của bảng vector ngắt. D3 (LITM) ịnh nghĩa ngõ vào yêu

cầu ngắt tác ộng mức hay cạnh. Các bit còn lại là các bit ịa chỉ

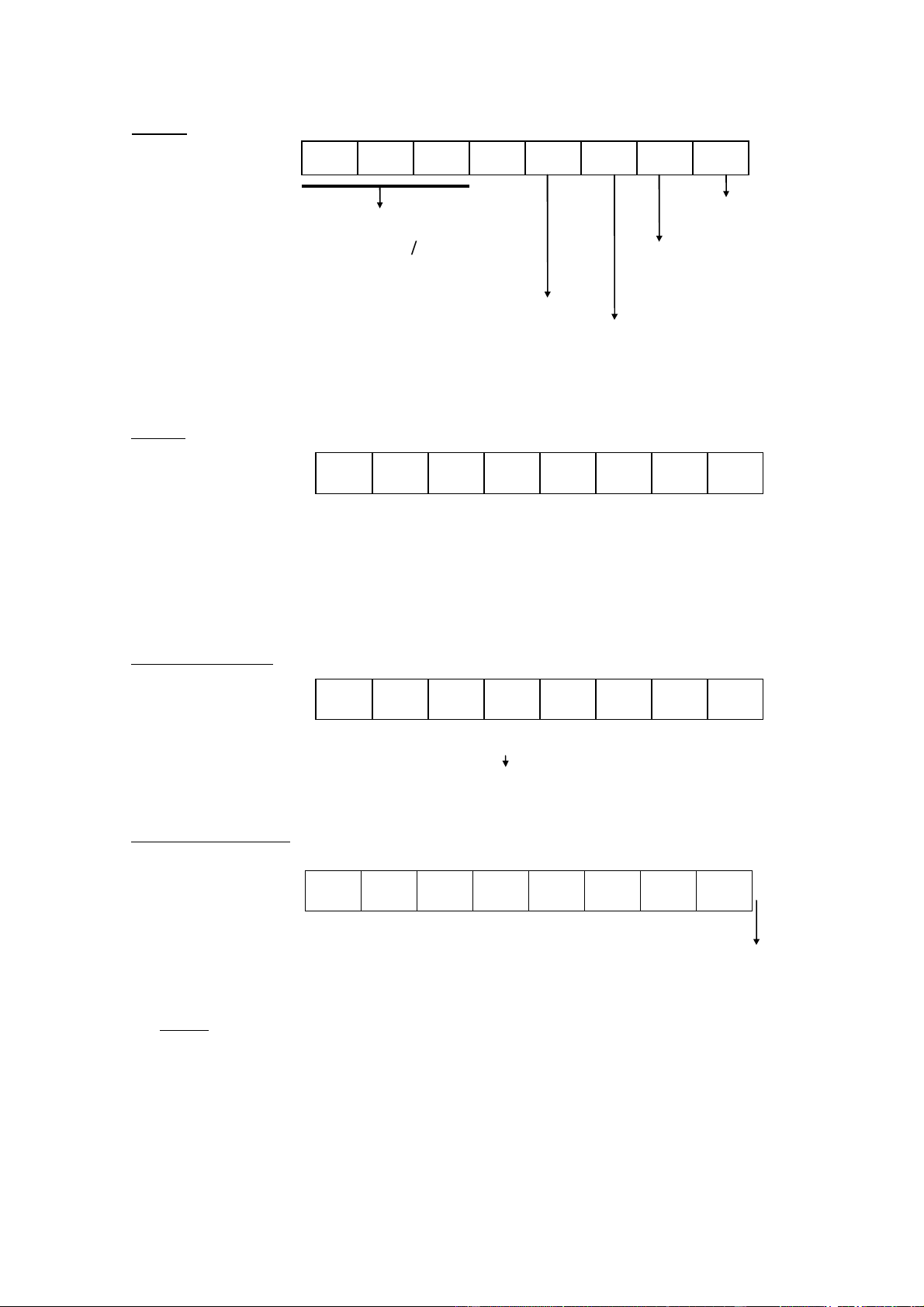

A7A6A5 trong hệ thống 8080/85, ối với các hệ thống 16/32 bit chúng không xác ịnh. lOMoARcPSD| 10435767 ICW1: A0=0 A7 A6 A5 1 LTIM ADI SNGL IC4 1: C ầ n ICW4

Là ị a chỉ vector ố i v ớ i 8080/85 0: bỏ ICW4

Không xá c ị nh v ớ i h ệ /32 bit 16 Single: 1: chỉ có 1 mạ ch 8259 0: nhi ề u mạ ch 8259

Level Trigger Mode: Ch ế ộ củ a xung yêu c ầ u ng ắ t 1: theo mức dương Address Interval: 0: theo cạnh lên K/c giữa các vector ngắt

1: 4 byte (80x86/88) 0: 8 byte (8080/85) ICW2: T7 T6 T5 T4 T3 T2 T1 T0 A0=1

ICW2 là 8 bit ịa chỉ cao của vector ngắt (AD15 - AD8) trong hệ thống 8080/85, là

vector ngắt (T7- T3)trong hệ thống 8086/88. ICW3 mạch chủ: S7 S6 S5 S4 S3 S2 S1 S0 A0=1

1: ngõ vào tương ứng có 1 mạch tớ

0: không có mạch tớ ở ngõ vào ICW3 cho mạch tớ: A0=1 0 0 0 0 0 ID2 ID1 ID0

000 cho mạch tớ tại ngõ vào IR0 …

111 cho mạch tớ tại ngõ vào IR7. • ICW2

Từ iều khiển này cho phép chọn kiểu ngắt (số hiệu ngắt) ứng với các bit T7-T3

trong hệ thống 8086/88, khi ó các bit còn lại luôn ược gán giá trị 0 ứng với ngõ vào

IR0. Các vector ngắt của các ngõ vào tiếp theo sẽ lần lượt tăng lên 1. Ví dụ nếu

ICW2 = 40H thì các vector ngắt sẽ lần lượt mang số hiệu từ 40H tới 47H. Trong các

hệ thống 8080/85 thì ICW2 sẽ cung cấp các bit ịa chỉ cao của ịa chỉ vector ngắt. lOMoARcPSD| 10435767 • ICW3

Từ iều khiển này chỉ dùng tới khi bit SNGL trong ICW1 = 0 tức là trong hệ thống có

nhiều 8259 nối tầng với nhau. Như vậy sẽ tồn tại hai loại ICW3: một cho mạch chủ

(master) và 1 cho mạch tớ (slave). Các bit ICW3 của 8259 chủ sử dụng ể chỉ ịnh ngõ

vào nào có ghép tầng (cascade). Trong 8259 tớ chỉ sử dụng 3 bit thấp ể xác ịnh nó ược

nối tới ngõ vào nào của 8259 chủ. A0=1 0 0 0 SFNM BUF M/S AEOI PM N Special Fully Nested Mode P mode

Ch ế ộ l ồ ng hoàn toàn. 1: 8086/88 1: S FNM 0: 8080/8085 0 x: Ch ế ộ không ệ m Auto End Of Interrupt: 10: Ch ế ệ m mạ ch t ớ 1: EO I t ự ộ ng

11: Chế ộ ệm mạch chủ 0: EOI thông thường • ICW4

Từ iều khiển này chỉ dùng ến khi trong từ iều khiển ICW1 có bit D0 =1. Bit PM

cung cấp khả năng chọn vi xử lý làm việc với 8259.

Bit SFNM = 1 cho phép chọn chế ộ ưu tiên cố ịnh ặc biệt. Trong chế ộ này các yêu cầu

ngắt với mức ưu tiên cao nhất hiện thời từ một mạch tớ làm việc theo kiểu nối tầng sẽ

ược mạch chủ nhận biết ngay cả khi mạch chủ còn ang phục vụ một yêu cầu ngắt ở

mạch tớ khác nhưng với mức ưu tiên thấp hơn. Sau khi các yêu cầu ngắt ược phục vụ

xong thì chương trình phục vụ ngắt phải có lệnh kết thúc yêu cầu ngắt EOI ặt trước

lệnh IRET ưa ến cho mạch 8259 chủ.

Khi SFNM = 0 thì chọn chế ộ ưu tiên cố ịnh ( mức ưu tiên giảm từ IR0 tới IR7).

Nếu 8259 không dùng tới ICW4 thì chế ộ này cũng ược coi như mặc ịnh. Trong chế ộ

này nếu chỉ có một yêu cầu ngắt ang ược phục vụ thì các yêu cầu có mức ưu tiên thấp

hơn sẽ bị cấm, và các yêu cầu có mức ưu tiên cao hơn sẽ ngắt các yêu cầu có mức ưu tiên thấp hơn.

Bit BUF cho phép chọn chế ộ làm việc giữa 8259 và CPU là có ệm hay không có ệm.

Khi BUF =1 M/S = 0/1 sẽ chọn ệm ở mạch chủ hoặc mạch tớ.

Bit AEOI = 1 cho phép kết thúc yêu cầu ngắt tự ộng. Lúc này 8259 sẽ tự ộng xóa ISRi

= 0 khi xung INTA chuyển lên mức cao mà không làm thay ổi thứ tự ưu tiên. Ngược lại

khi AEOI = 0 chương trình phục vụ ngắt phải có thêm lệnh EOI trước IRET ưa tới cho 8259.

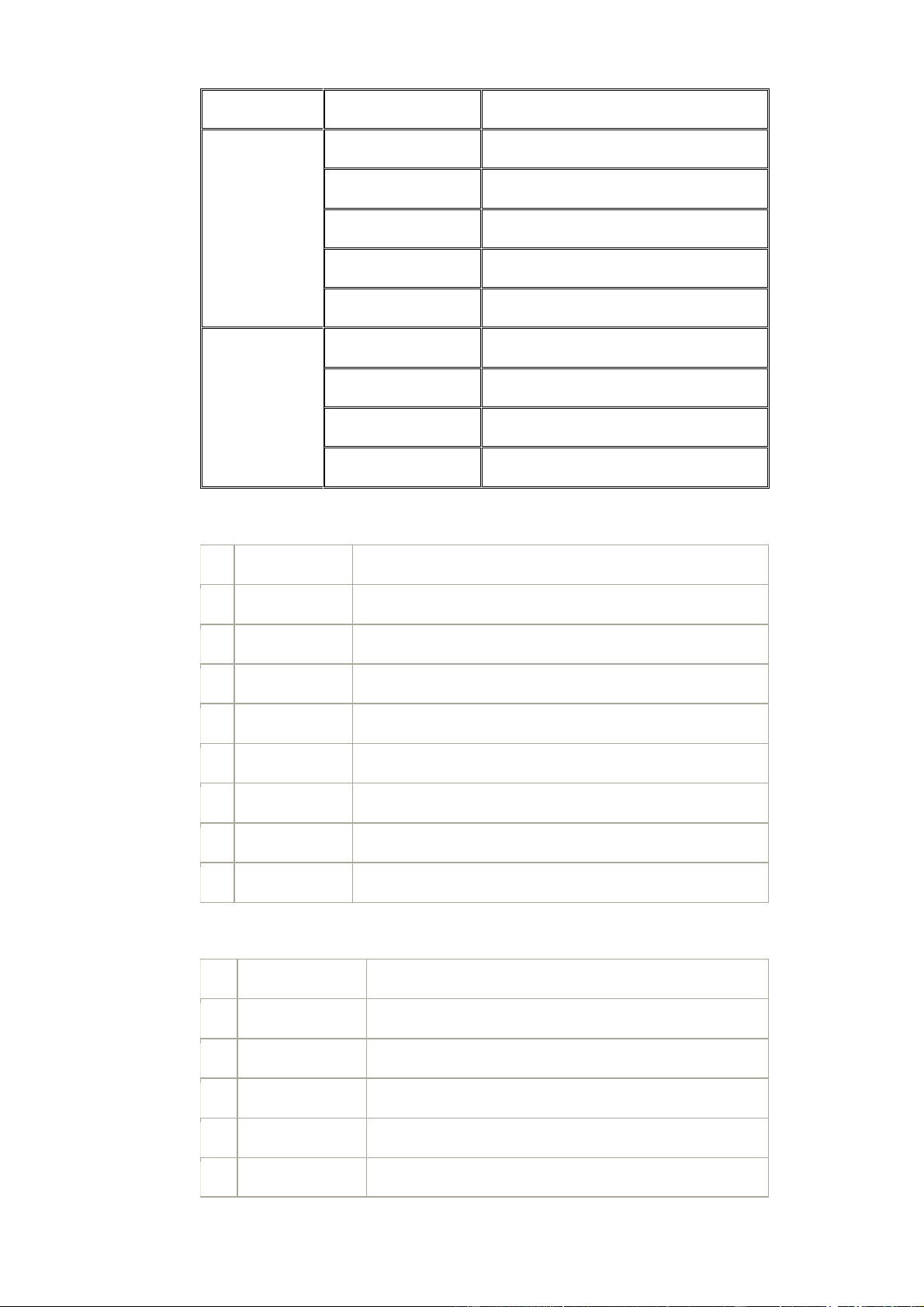

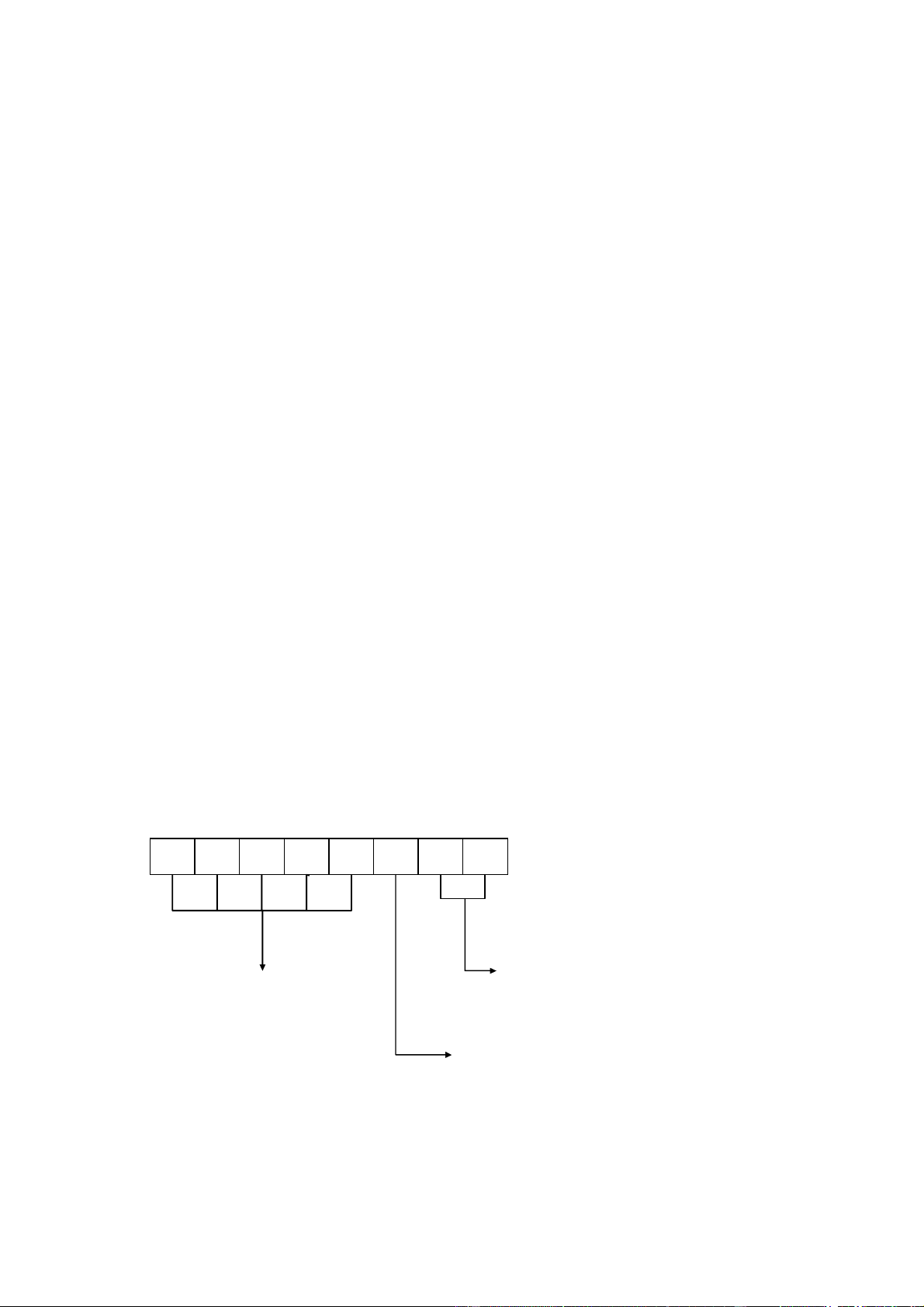

Các từ iều khiển ICW ược lập trình cho 8259 theo giải thuật hình 3.12:

Các từ iều khiển hoạt ộng OCW: lOMoARcPSD| 10435767

Các từ iều khiển OCW sẽ quyết ịnh 8259 hoạt ộng như thế nào khi nó ã ược khởi ộng

bằng các từ ều khiển ICW. OCW1:

OCW1 dùng ể ghi giá trị của các bit mặt nạ vào thanh ghi mặt nạ IMR. Khi một bit

mặt nạ nào ó của IMR ược lập thì yêu cầu tương ứng với ngõ vào ó sẽ không ược phục

vụ. Từ iều khiển này phải ược ghi tới 8259 ngay sau các từ ICW. Cũng có thể ọc lại

IMR ể xem tại thời iểm hiện tại ngõ vào nào có yêu cầu bị che. ICW1 ICW2 D1 (ICW1) = 1 ? ICW3 D1 (ICW1) = 1 ? ICW4 S ẵ n sàng nh ậ n yêu c ầ u ng ắ t

Hình 3.12: Giải thuật lập trình các từ iều khiển ICW cho 8259. • OCW1 M7 M6 M5 M4 M3 M2 M1 M0 A0=1

Mặt nạ các ngắt tại các ngõ vào yêu cầu: 1: có mặt nạ 0: không có mặt nạ • OCW2 A0=0 R SL EOI 0 0 L2 L1 L0 lOMoARcPSD| 10435767

Mã hóa chế ộ kết thúc Mã hóa mức ưu tiên ngắt bị tác ộng

ngắt 000: mức 0; … ; 111: mức 7 • OCW3 A0=0 0 ESM SMM 0 1 P ERIS RIS 10: ọ c IRR ở l ầ n sau 11: ọ c ISR ở l ầ n sau Special Mask Mode

10:xóa chế ộ mặt nạ ặc biệt

Thăm dò trạng thái hiện tại của yêu cầu ngắt.1: ọc

11:lập chế ộ mặt nạ ặc biệt mã ưu tiên cao nhất ở lần ọc sau OCW2:

Các bit R, SL, EOI cho phép chúng ta chọn cách thức kết thúc ngắt khác nhau. Một

vài cách kết thúc ngắt còn tác ộng tới các yêu cầu ngắt ược chỉ ịnh với mức ưu tiên

ược mã hóa bởi 3 bit L3L2L1.

Các chế ộ kết thúc ngắt bao gồm:

- Chế ộ ưu tiên cố ịnh:

Đây là chế ộ làm việc mặc ịnh của 8259 sau khi ã ược nạp các từ làm việc khởi ầu.

Trong chế ộ này có mức ưu tiên tại các ngõ vào mặc ịnh giảm dần từ IR0 tới IR7. Các

ngõ vào có mức ưu tiên thấp hơn sẽ bị cấm, và các yêu cầu có mức ưu tiên cao hơn

sẽ ngắt các yêu cầu có mức ưu tiên thấp hơn.

- Chế ộ quay mức ưu tiên.

Ở chế ộ này khi một yêu cầu ngắt ược phục vụ xong nó sẽ ược gán mức ưu tiên thấp

nhất ể tạo iều kiện cho các yêu cầu ngắt khác có cơ hội ược phục vụ. - Chế ộ quay mức ưu tiên chỉ ịnh.

Trong chế ộ này cần phải chỉ rõ ngõ vào nào ược gán mức ưu tiên thấp nhất bằng các

bit L2L1L0. Ngõ vào có chỉ số kế tiếp nó sẽ ược gán mức ưu tiên cao nhất. Với các

chế ộ ưu tiên trên các bit R, SL,EOI trong OCW2 ược mã hóa ể chỉ thị các chế ộ kết

thúc ngắt khác nhau như sau:

1. Kết thúc ngắt thông thường: Chương trình con phục vụ ngắt phải có lệnh EOI ặt

trước lệnh trở về IRET cho 8259. Mạch 8259 sẽ xác ịnh yêu cầu ngắt vừa ược

phục vụ và xóa bit tương ứng với nó trong thanh ghi ISR, tạo iều kiện cho yêu cầu

ngắt ở chính ngõ vào này hoặc các ngắt có yêu cầu thấp hơn ược phục vụ.

2. Kết thúc yêu cầu ngắt chỉ ịnh: chương trình con phục vụ ngắt cũng phải có lệnh

EOI ặt trước lệnh IRET. Mạch 8259 sẽ xóa ích danh bit ISR ược chỉ ịnh bởi các bit lOMoARcPSD| 10435767

L2L1L0 ể tạo iều kiện cho yêu cầu ngắt ở chính ngõ vào này hoặc các ngõ vào có

yêu cầu thấp hơn ược phục vụ.

3. Quay ổi mức ưu tiên khi kết thúc ngắt thông thường: chương trình con phục vụ ngắt

cũng cần lệnh EOI. Mạch 8259 sẽ xác ịnh ngõ vào vừa ược phục vụ, xóa bit tương

ứng trong ISR và gán cho ngõ vào này mức ưu tiên thấp nhất, còn ầu vào có chỉ số

kế tiếp (i+1) sẽ ược gán mức ưu tiên cao nhất.

4. Quay ổi mức ưu tiên trong chế ộ kết thúc ngắt tự ộng: chỉ cần cung cấp lệnh chọn

chế ộ này một lần bằng cách chọn chế ộ quay khi EOI tự ộng. Từ ó trở i 8259 sẽ ổi

mức ưu tiên mỗi khi kết thúc ngắt như mô tả trong phần 3. Muốn xóa bỏ chế ộ này

chỉ việc lập trình lại chế ộ khác cho 8259.

5. Quay ổi mức ưu tiên khi kết thúc yêu cầu ngắt chỉ ịnh: chương trình phục vụ ngắt

phải có lệnh EOI chỉ ích danh trước lệnh IRET. Mạch 8259 sẽ xóa bit tương ứng

trong thanh ghi ISR và gán mức ưu tiên thấp nhất cho ngõ vào có chỉ số chỉ ịnh bởi L2L1L0.

6. Lập mức ưu tiên: chế ộ này cho phép thay ổi mức ưu tiên cố ịnh hoặc mức ưu tiên

gán trước bằng cách gán mức ưu tiên thấp nhất cho ngõ vào chỉ ịnh bởi L2L1L0, yêu

cầu ngắt có chỉ số kế tiếp (i+1) sẽ có mức ưu tiên cao nhất.

Các bit R,S,L và EOI ược mã hóa cho các chế ộ như mô tả trong bảng 3.6.

Bảng 3.6: Mã hoá các chế ộ EOI của 8259 001 Lệnh EOI thông thường Kết thúc ngắt EOI 011 Lệnh EOI chỉ ịnh 101

Đổi mức ưu tiên khi có EOI thường

Đổi mức ưu tiên tự ộng 100

Lập chế ộ quay khi có EOI tự ộng 000

Xóa chế ộ quay khi có EOI tự ộng 111

Đổi mức ưu tiên khi có EOI chỉ ịnh

Đổi mức ưu tiên chỉ ịnh 110 Lập mức ưu tiên 010 Không làm gì cả

Từ iều khiển hoạt ộng OCW3 sau khi ghi vào 8259 cho phép thực hiện các công việc sau:

+ Chọn ra các thanh ghi ể ọc.

+ Thăm dò trạng thái yêu cầu ngắt bằng cách ọc trạng thái của ngõ vào có mức ưu tiên

cao nhất cũng với mã ầu vào của nó.

+ Thao tác với mặt nạ ặc biệt. lOMoARcPSD| 10435767

Khi ọc các thanh ghi IRR và ISR có thể biết ược các ngõ vào nào ang có yêu cầu

phục vụ, và ngõ vào nào ang ược phục vụ.

Bằng việc cho bit P của OCW3 = 1 có thể ọc ược trên bus dữ liệu ở lần ọc ngay sau

ó từ thăm dò, trong từ thăm dò này sẽ có các thông tin về yêu cầu ngắt có mức ưu tiên cao nhất như hình sau: I x x x x W2 W1 W0

1: Đang có yêu cầu ngắt

Mã hóa số hiệu ngõ vào có mức

0: không có yêu cầu ngắt ưu tiên cao nhất

Chú ý trước khi ọc từ thăm dò cần phải cấm các yêu cầu ngắt bằng lệnh CLI.

Bit ESM = 1 cho phép thao tác với chế ộ mặt nạ ặc biệt. Chế ộ mặt nạ ặc biệt ược dùng

ể thay ổi chế ộ ưu tiên ngay bên trong chương trình con phục vụ ngắt. Ví dụ trong

trường hợp có một yêu cầu ngắt bị cấm (bị che bởi chương trình phục vụ ngắt với từ

lệnh OCW1) mà ta lại muốn cho phép các yêu cầu ngắt với mức ưu tiên thấp hơn so

với yêu cấu ngắt bị cấm ó ược tác ộng, khi ó cần phải sử dụng chế ộ mặt nạ ặc biệt. Khi

ã ược thiết lập thì chế ộ mặt nạ ặc biệt sẽ tồn tại cho ến khi xóa bằng cách ghi vào 8259

một từ OCW3 khác có bit SMM = 0. Mặt nạ ặc biệt không ảnh hưởng tới các yêu cấu

ngắt với mức ưu tiên cao hơn.

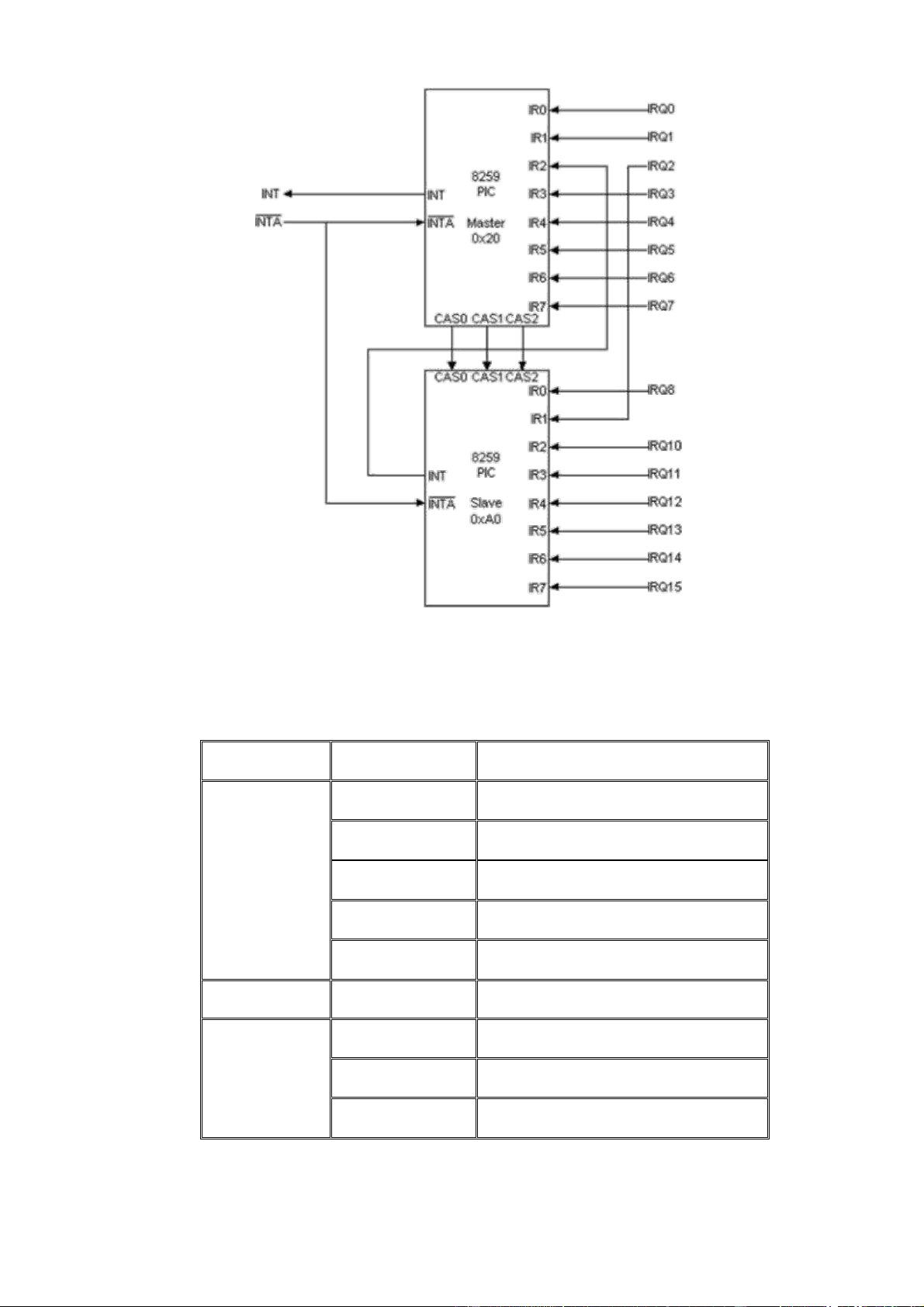

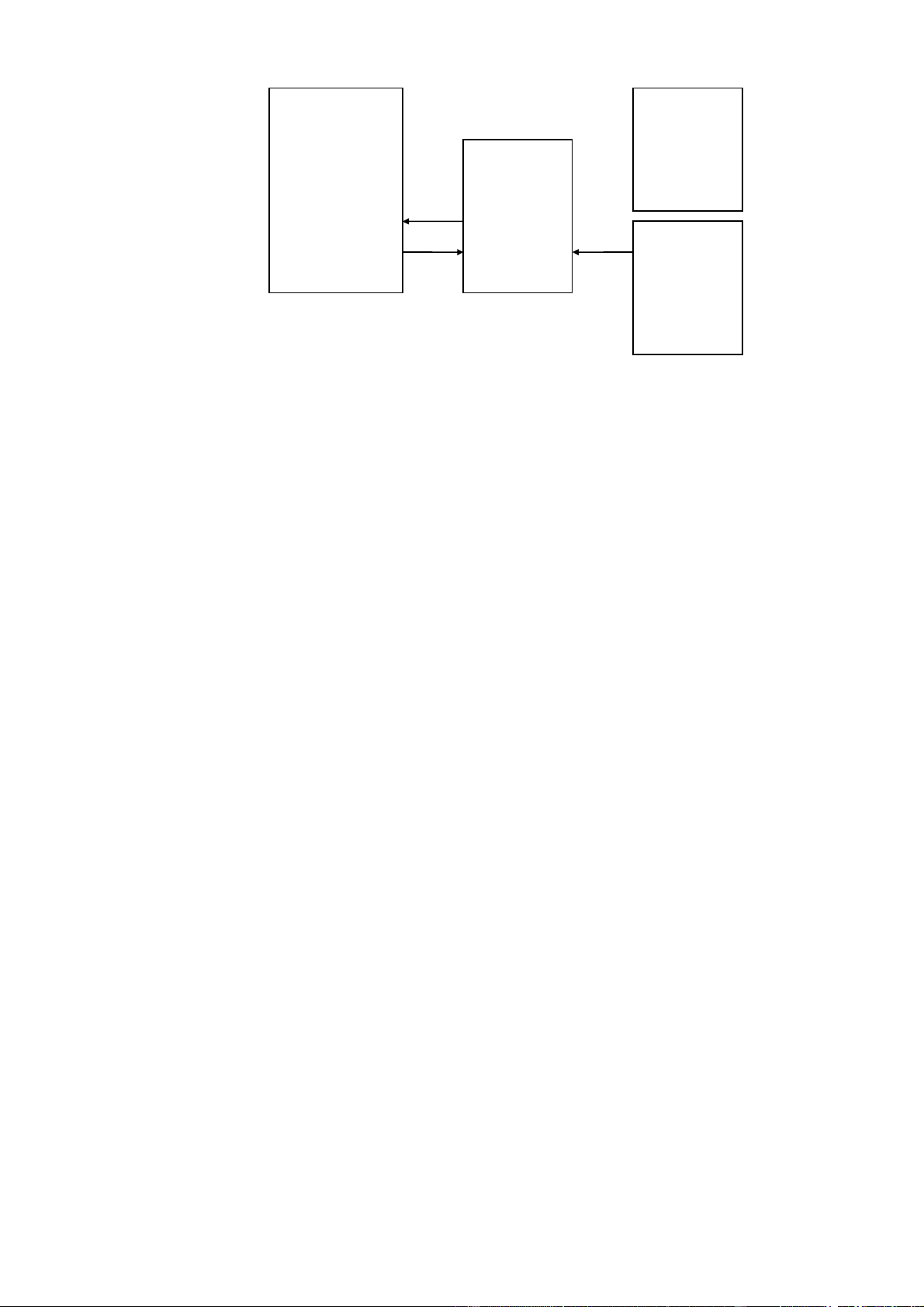

Trong máy tính PC, cấu hình phần cứng của hệ thống ngắt bao gồm 2 bộ iều khiển ưu

tiên ngắt ược kết nối như trên hình 3.13. Các ịa chỉ sử dụng cho PIC1 ược cho trong

bảng 3.7 và PIC2 trong bảng 3.8. Các thiết bị phần cứng mà PIC1 iều khiển cho trong

bảng 3.9, PIC2 trong bảng 3.10. lOMoARcPSD| 10435767

Hình 3.13: Kết nối phần cứng các bộ iều khiển ngắt trong máy tính

Bảng 3.7: Các ịa chỉ sử dụng cho PIC1 trong máy tính. Địa chỉ Đọc/ghi Chức năng Ghi Thanh ghi ICW1 Ghi Thanh ghi OCW2 20h Ghi Thanh ghi OCW3 Đọc Thanh ghi IRR Đọc Thanh ghi ISR 21h Ghi Thanh ghi ICW2 Ghi Thanh ghi ICW3 Ghi Thanh ghi ICW4 Đọc/Ghi Thanh ghi IMR

Bảng 3.8: Các ịa chỉ sử dụng cho PIC2 trong máy tính lOMoARcPSD| 10435767 Địa chỉ Đọc/Ghi Chức năng Ghi Thanh ghi ICW1 Ghi Thanh ghi OCW2 A0h Ghi Thanh ghi OCW3 Đọc Thanh ghi IRR Đọc Thanh ghi ISR Ghi Thanh ghi ICW2 Ghi Thanh ghi ICW3 A1h Ghi Thanh ghi ICW4 Đọc / Ghi Thanh ghi IMR

Bảng 3.9: Các thiết bị yêu cầu ngắt qua PIC1 Bit Disable IRQ Function 7 IRQ7

Cổng máy in - Parallel Port 6 IRQ6

Bộ iều khiển ĩa mềm - Floppy Disk Controller 5 IRQ5

Card âm thanh - Reserved/Sound Card 4 IRQ4

Cổng nối tiếp - Serial Port 3 IRQ3

Cổng nối tiếp - Serial Port 2 IRQ2 PIC2 1 IRQ1 Bàn phím - Keyboard 0 IRQ0

Bộ ịnh thời hệ thống - System Timer

Bảng 3.10: Các thiết bị yêu cầu ngắt qua PIC2 Bit Disable IRQ Function 7 IRQ15 Dự phòng - Reserved 6 IRQ14

Đĩa cứng - Hard Disk Drive 5 IRQ13

Đồng xử lý toán học - Maths Co-Processor 4 IRQ12 Con chuột PS/2 - PS/2 Mouse 3 IRQ11 Dự phòng - Reserved lOMoARcPSD| 10435767 2 IRQ10 Dự phòng - Reserved 1 IRQ9

Chuyển qua IRQ2 - Redirected IRQ2 0 IRQ8

Đồng hồ thời gian thực - Real Time Clock

3.4 TRUY NHẬP TRỰC TIẾP BỘ NHỚ - DMA

3.4.1 Nguyên tắc chung.

Trong các nguyên tắc vào ra quét vòng và ngắt ã biết, dữ liệu ược truyền trực tiếp giữa

CPU và các cổng vào ra, tốc ộ truyền dữ liệu sẽ tùy thuộc vào các lệnh của CPU, vì thế

sẽ không thể thực hiện việc truyền dữ liệu một cách nhanh chóng. Mặt khác, khi truyền

dữ liệu giữa bộ nhớ và vào ra, do cấu trúc một bus dữ liệu, nên dữ liệu cần truyền qua

trung gian là CPU. Ví dụ muốn lấy giá trị từ một cổng vào ra ghi tới bộ nhớ, trước hết

CPU phải thực hiện một chu kỳ ọc dữ liệu từ vào ra vào trong thanh ghi, và sau ó thực

hiện một chu kỳ ghi từ thanh ghi ra bộ nhớ. Để truyền dữ liệu với tốc ộ nhanh hơn người

ta sử dụng phương pháp vào ra bằng cơ chế thâm nhập trực tiếp bộ nhớ (DMA - Direct

Memory Access). Trong cơ chế này thiết bị ngoại vi sẽ truyền dữ liệu theo khối với bộ

nhớ mà không thông qua sự iều khiển của CPU, bộ iều khiển DMA tạo ra các ịa chỉ một

cách tuần tự ể truyền trực tiếp dữ liệu giữa bộ nhớ và vào ra, mà không phải thực hiện

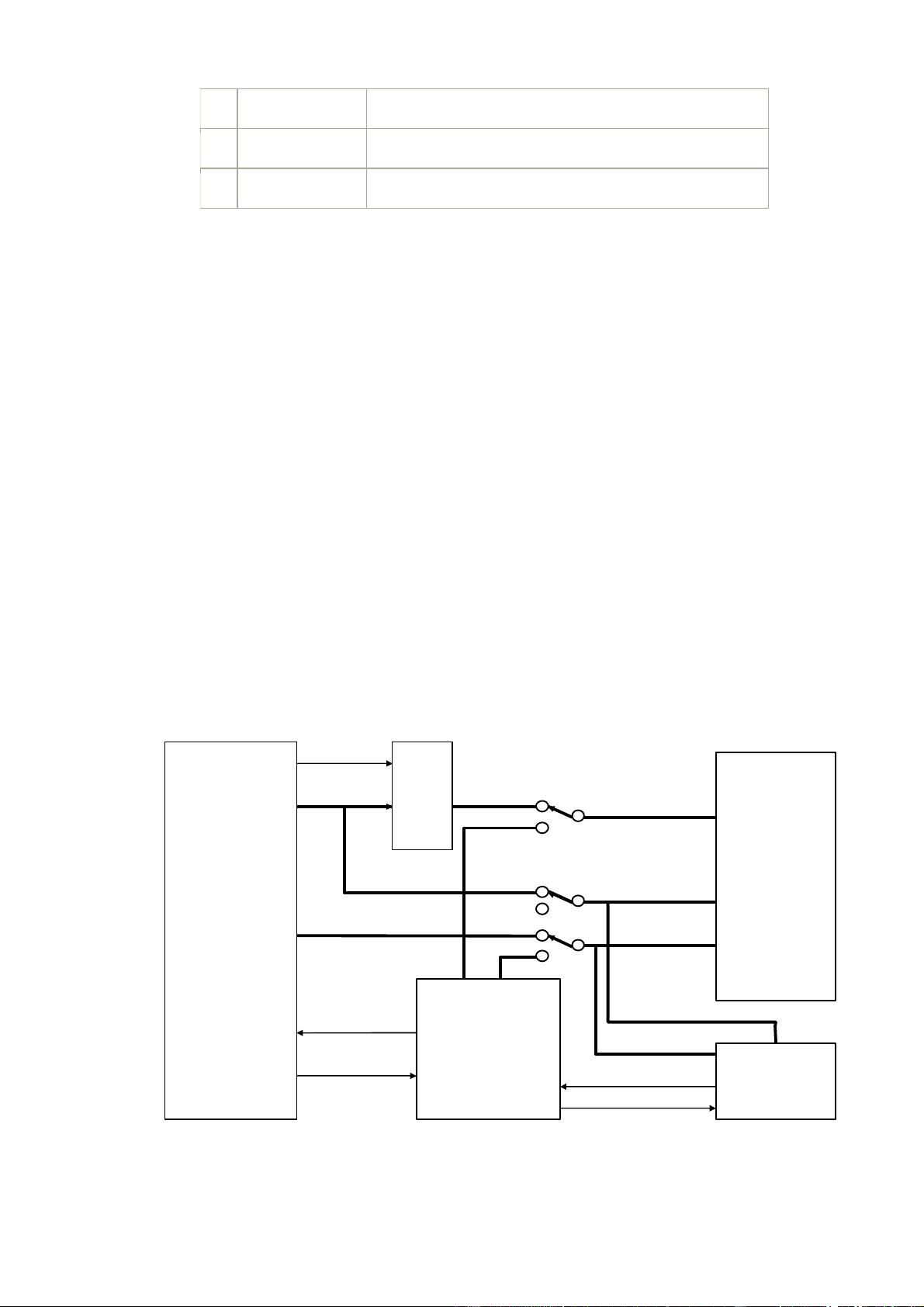

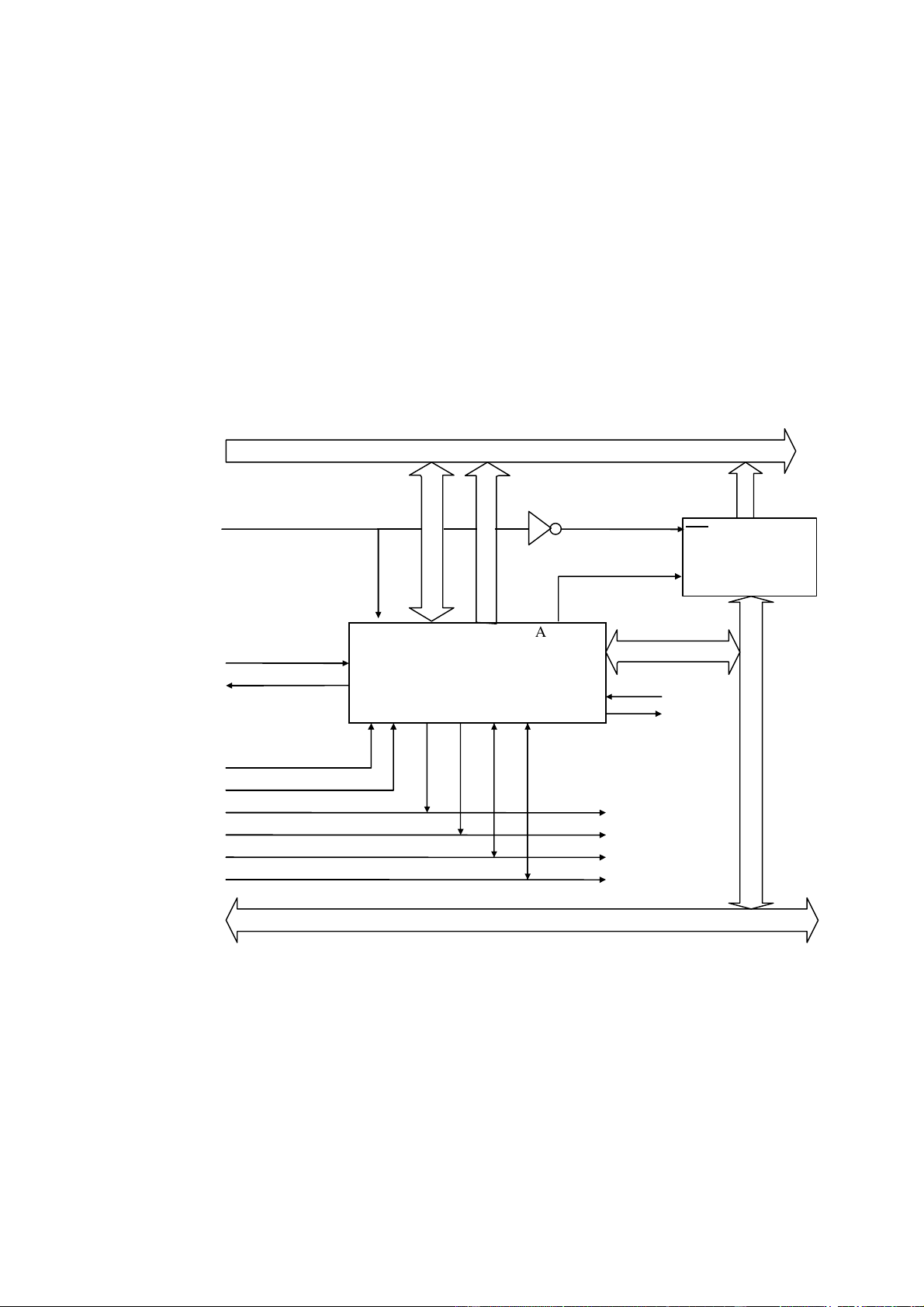

các chu kỳ ọc ghi như CPU, do ó tốc ộ truyền sẽ nhanh hơn rất nhiều. Sơ ồ khối của hệ

thống vào ra dữ liệu theo nguyên tắc DMA có thể mô tả như hình 3.14. ADDRESS LATCHES ALE AD0-AD15 CPU MEMORY DATA BUS DATA BUS CONTROL BUS CONTROL BUS (IOR, IOW, MEMR,MEMW) DATA BUS HOLD HRQ DMA CONTROL BUS CONTROLLER HLDA HLDA DREQ PERIPHERAL DACK DEVICE

Hình 3.14: Nguyên tắc vào ra bằng DMA trong hệ thống vi xử lý. lOMoARcPSD| 10435767

Trong sơ ồ này CPU và DMAC sẽ luôn phiên sử dụng các BUS ịa chỉ, dữ liệu, và

iều khiển thông qua việc iều khiển chuyển mạch ba công tắc lên phía trên hoặc xuống

phía dưới. Khi hệ thống bắt ầu hoạt ộng các công tắc nằm ở phía trên, vì thế các Bus sẽ

nối ghép giữa CPU với bộ nhớ và các thiết bị ngoại vi. Hệ thống sẽ hoạt ộng bình thường

cho ến khi cần thực hiện một chu kỳ truy cập DMA (ví dụ ọc 1 file từ ĩa từ trong hệ

thống máy vi tính PC). Để ọc một khối dữ liệu từ thiết bị, cần phải gửi một chuỗi lệnh

tới thiết bị ể xác ịnh vị trí của khối dữ liệu. Khi thiết bị ã có dữ liệu sẵn sàng ể truyền nó

sẽ gửi tín hiệu yêu cầu DMA bằng tín hiệu DREQ tới bộ iều khiển DMA (DMAC). Nếu

DMAC ược lập trình không che (cho phép hoạt ộng khi có yêu cầu ), nó sẽ gửi tín hiệu

yêu cầu treo bus HRQ tới ngõ vào HOLD của CPU. Lúc này CPU sẽ treo các bus của

nó lên trạng thái trở kháng cao (tương ương với việc chuyển mạch các công tắc xuống

phía dưới, ngắt CPU ra khỏi các Bus), và trả lời chấp nhận yêu cầu treo bus bằng tín

hiệu HLDA cho bộ iều khiển DMA. Khi nhận ược tín hiệu chấp nhận HLDA từ CPU,

bộ iều khiển DMA sẽ bắt ầu thực hiện việc iều khiển các Bus. Nó sẽ gửi ịa chỉ tới bộ

nhớ ể xác ịnh vị trí mà byte ầu tiên sẽ ược ghi vào. Tiếp theo DMAC sẽ gửi tín hiệu chấp

nhận DMA bằng tín hiệu DACK tới cho thiết bị, tín hiệu này sẽ thông báo cho thiết bị

trạng thái sẵn sàng cho thiết bị gửi ra một byte dữ liệu. Cuối cùng DMAC sẽ tạo ra cả

hai tín hiệu ghi bộ nhớ (MEMW) và ọc vào ra (IOR) một cách ồng thời, IOR sẽ cho phép

thiết bị cung cấp dữ liệu ra data Bus, MEMW cho phép bộ nhớ nhận dữ liệu từ data Bus.

Như vậy DMA ã iều khiển việc ghi trực tiếp dữ liệu từ thiết bị tới bộ nhớ mà không thông qua CPU.

Khi ã hoàn thành việc truyền dữ liệu, DMAC sẽ giải phóng Bus và dừng tác ộng tín

hiệu HOLD. CPU sẽ quay về iều khiển BUS trở lại cho ến khi có một yêu cầu DMA

mới. CPU sẽ tiếp tục thực hiện tiếp chương trình tại nơi mà nó ã dừng lại ể thực hiện yêu cầu DMA.

Quá trình ghi trực tiếp dữ liệu từ bộ nhớ tới thiết bị sẽ ược thực hiện hoàn toàn tương

tự. Khi ó DMAC sẽ tạo ra các tín hiệu iều khiển ọc bộ nhớ (MEMR) và ghi vào ra (IOW) một cách ồng thời.

Trong thực tế có 3 chế ộ trao ổi dữ liệu theo nguyên tắc DMA:

- Treo CPU một khoảng thời gian ể trao ổi cả mảng dữ liệu.

- Treo CPU một số chu kỳ máy ể trao ổi từng byte

- Tận dụng thời gian CPU không sử dụng Bus ể truyền dữ liệu.

Để hiểu rõ các nguyên tắc này chúng ta có thể xem xét tính năng của bộ iều khiển DMA 8237-A của hãng Intel.

3.4.2 Vi mạch DMAC 8237 - A

3.4.2.1 Các ặc tính cơ bản lOMoARcPSD| 10435767

Điều khiển cho phép hoặc không cho phép các kênh DMA một cách riêng biệt.

Có 4 kênh DMA ộc lập nhau.

Có khả năng truyền dữ liệu từ bộ nhớ tới bộ nhớ.

Có thể truyền theo chiều tăng hoặc giảm ịa chỉ.

Hiệu suất truyền dữ liệu rất cao: với xung nhịp 5Mhz có thể truyền 1.6MB/1 giây.

Có khả năng ghép tầng (cascade) ể tăng số kênh DMA.

Có tín hiệu ngõ vào kết thúc việc truyền dữ liệu.

Có khả năng nhận yêu cầu DMA bằng phần mềm.

3.4.2.2 Sơ ồ khối và chức năng các khối

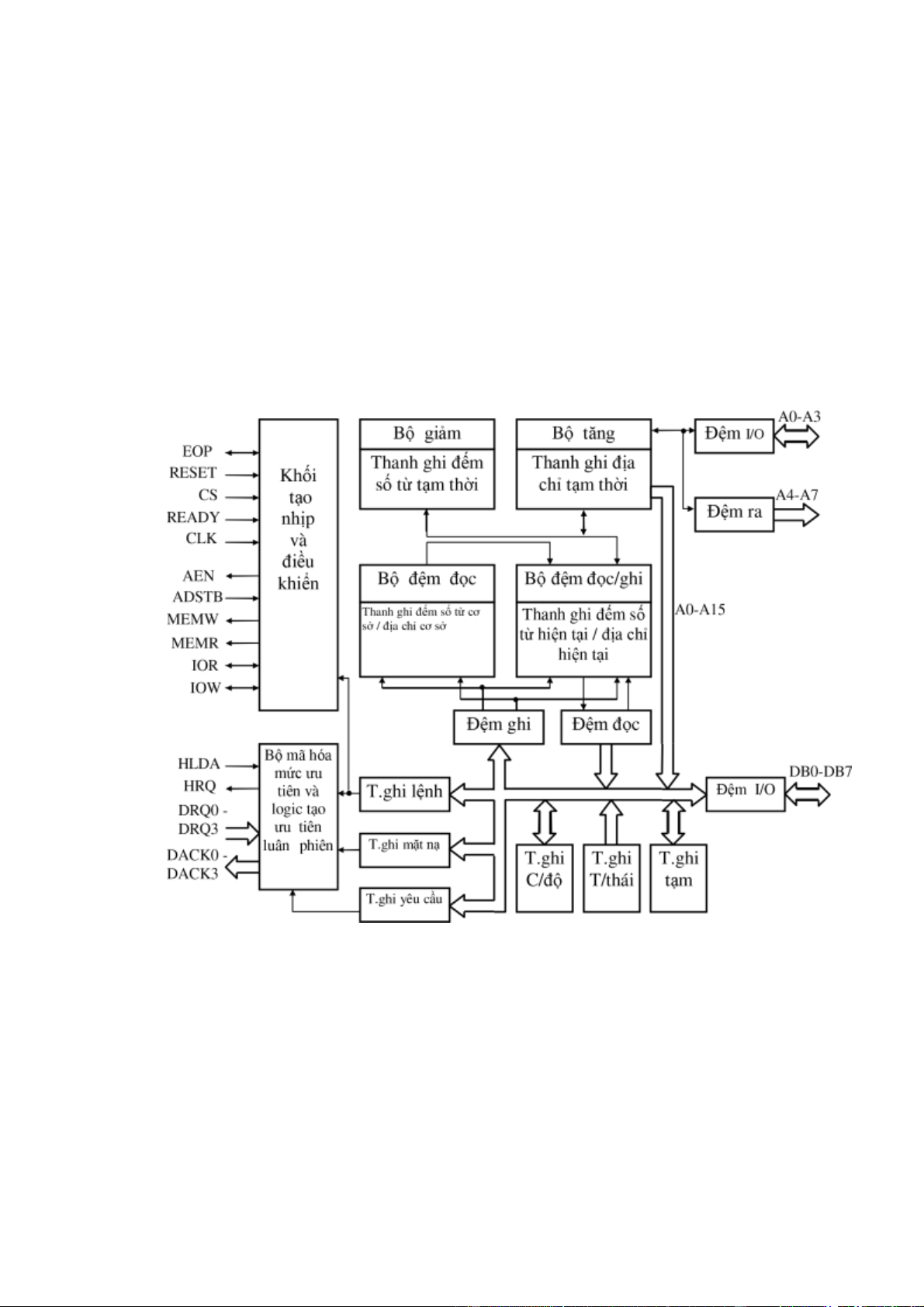

Hình 3.15: Sơ ồ khối bộ iều khiển DMA 8037,

Như hình 3.15, sơ ồ khối của 8237 bao gồm nhiều khối logic và các thanh ghi.

Bus nội nối các thanh ghi cho phép thay ổi các tín hiệu iều khiển giữa các khối.

8237 có tất cả 324 bit nhớ bên trong tạo thành các thanh ghi bao gồm: -

4 thanh ghi ịa chỉ cơ sở 16 bit.

- 4 thanh ghi ếm số từ cơ sở 16 bit.

- 4 thanh ghi ịa chỉ hiện hành 16 bit. lOMoARcPSD| 10435767

- 4 thanh ghi ếm số từ hiện hành 16 bit. - 1 thanh ghi ịa chỉ tạm thời 16 bit.

- 1 thanh ghi ếm số từ tạm thời 16 bit.

- 1 thanh ghi trạng thái 8 bit. - 1 thanh ghi lệnh 8 bit.

- 1 thanh ghi tạm thời 8 bit.

- 4 thanh ghi chế ộ 6 bit. - 1 thanh ghi mặt nạ 4 bit.

- 1 thanh ghi yêu cầu 4 bit.

8237 có 3 khối iều khiển logic bao gồm:

- Khối iều khiển ịnh thời có chức năng tạo các tín hiệu ịnh thời bên trong và bên ngoài cho 8237.

- Khối iều khiển lệnh chương trình có chức năng mã hóa các lệnh gửi tới từ CPU ể

phục vụ một chu kỳ DMA. Nó cũng giải mã từ chế ộ ể chọn kiểu DMA trong suốt chu kỳ phục vụ.

- Khối mã hóa ưu tiên sẽ giải quyết các tranh chấp ưu tiên giữa các kênh DMA có ưu

cầu phục vụ tại cùng một thời iểm.

Các tín hiệu của 8237.

+ Vcc, Vss: cấp nguồn +5 Vdc

+ CLK (Clock): Ngõ vào cung cấp xung nhịp cho 8237 ể iều khiển ịnh thời toàn bộ

hoạt ộng bên trong của 8237, và nó sẽ quyết ịnh tốc ộ truyền dữ liệu của 8237.

Có thể cấp Clock 3 MHz với 8237A, và 5 MHz với 8237 -5.

+ CS (Chip Select): tín hiệu chọn mạch, sử dụng ể CPU chọn 8237 như một ịa chỉ vào

ra trong suốt chu kỳ nó làm việc, cho phép CPU truyền dữ liệu với 8237.

+ RESET: Ngõ vào tác ộng mức cao xóa toàn bộ các thanh ghi lệnh, thanh ghi trạng

thái, thanh ghi yêu cầu và thanh ghi tạm thời, nó cũng xóa toàn bộ các bit che phục vụ.

Thiết lập lại toàn bộ trạng thái ban ầu của 8237.

+ READY: Ngõ vào cung cấp từ bộ nhớ tới 8237 trong các chu kỳ ọc ghi, tín hiệu này

sử dụng ể bộ nhớ thông báo trạng thái sẵn sàng của nó tới 8237 cho phép 8237 giao

tiếp ược với các bộ nhớ chậm.

+ HLDA (Hold Acknowledge): Ngõ vào tác ộng mức cao nhận tín hiệu chấp yêu cầu

treo bus gửi tới từ CPU. Khi nhận ược tín hiệu này 8237 sẽ bắt ầu chiếm bus của CPU

ể thực hiện chu kỳ DMA.

+ DREQ0 - DREQ3: (DMA REQUEST) là các ngõ vào nhận các yêu cầu DMA từ

thiết bị. Trong chế ộ ưu tiên cố ịnh (fixed) DREQ0 sẽ có mức ưu tiên cao nhất, cho tới

DREQ3 có mức ưu tiên thấp nhất. Yêu cầu gửi tới kênh nào thì sẽ ược trả lời trên

ường DACK tương ứng. Cực tính yêu cầu ở các ngõ vào này có thể lập trình ược, khi

RESET nó sẽ tác ộng mức cao. Tín hiệu yêu cầu cần ược duy trì cho tới khi DACK tác ộng. lOMoARcPSD| 10435767

+ DB0 - DB7 (Data Bus): là bus dữ liệu hai chiều ba trạng thái, nối tới bus hệ

thống. Bus này có thể sử dụng ghi các từ iều khiển lập trình các thanh ghi của 8237, và

ọc trạng thái hiện hành của các thanh ghi trạng thái, tạm thời, và thanh ghi ếm số từ.

Trong các chu kỳ DMA 8 bit ịa chỉ cao sẽ ược cung cấp ra các ngõ ra này, chứa vào bộ

cài bên ngoài bằng tín hiệu ADSTB. Trong chu kỳ truyền dữ liệu giữa các ô nhớ

(Memory - Memory), dữ liệu sẽ ược ọc vào 8237 thông qua data bus trong chu kỳ ọc,

rồi chuyển ra data bus ể chứa vào vị trí mới trong chu kỳ ghi.

+ IOR (Input / Output Read): là ường tín hiệu hai chiều 3 trạng thái. Trong chu kỳ rỗi

(Idle) nó ược cung cấp tới từ CPU ể ọc giá trị các thanh ghi iều khiển. Trong chu kỳ

hoạt ộng DMA, tín hiệu này là ngõ ra sử dụng ể 8237 ọc dữ liệu từ thiết bị ngoại vi trong chu kỳ DMA ghi.

+ IOW(Input / Output Write) là ường tín hiệu hai chiều 3 trạng thái. Trong chu kỳ rỗi

(Idle) nó ược cung cấp tới từ CPU, ể CPU có thể ghi các thông tin cần thiết tới 8237.

Trong chu kỳ hoạt ộng DMA, tín hiệu này là ngõ ra sử dụng ể 8237 ghi dữ liệu tới thiết

bị ngoại vi, trong chu kỳ DMA ọc.

+ EOP (End Of Process) : Là tín hiệu hai chiều tác ộng mức thấp, cho phép kết thúc

phục vụ DMA hiện hành. Khi thiết bị bên ngoài muốn kết thúc phục vụ DMA hiện hành

nó cung cấp tới ngõ vào này một xung mức thấp. Khi 8237 thực hiện xong một chu kỳ

DMA nó sẽ cung cấp tín hiệu thông báo tới ngõ ra này. Tóm lại khi có mức thấp tại

ngõ này quá trình phục vụ DMA sẽ kết thúc, trạng thái của 8237 cần ược tạo lập lại.

Nếu 8237 ược lập trình cho phép tự ộng khởi ộng (auto initialize), thì thanh ghi cơ sở

sẽ ược ghi tới thanh ghi hiện hành của kênh ó. Bit che (mask) và bit TC (Terminal Count)

của kênh hiện hành trong thanh ghi trạng thái sẽ ược lập, trừ khi kênh ó ã ược lập trình tự ộng khởi ộng.

+ A0 - A3 (Address): là các tín hiệu hai chiều 3 trạng thái, trong chu kỳ rỗi (không phục

vụ DMA) các tín hiệu này là các ngõ vào sử dụng ể CPU ịnh vị các thanh ghi iều khiển

bên trong 8237. Trong trạng thái phục vụ DMA chúng là các ngõ ra cung cấp các bit ịa

chỉ thấp ra bus ịa chỉ, sử dụng cho các bộ nhớ và thiết bị ngoại vi. + A4 - A7 (Address)

: là các ngõ ra 3 trạng thái cung cấp 4 bit ịa chỉ trong các chu kỳ phục vụ DMA.

+ HRQ (Hold Request) : là ngõ ra gửi yêu cầu treo bus tới CPU, nó ược tác ộng khi có

yêu cầu trên một kênh vào DREQ không che. Ngõ vào HLDA cần phải tác ộng sau HRQ

ít nhất sau 1 chu kỳ xung nhịp.

+ DACK0 - DACK3 (DMA Acknowledge): là các ngõ ra thông báo cho thiết bị ngoại

vi biết yêu cầu DMA của nó ược chấp nhận. Mức tác ộng của các ngõ này có thể lập

trình ược, khi khởi ộng lại nó sẽ tác ộng mức thấp. lOMoARcPSD| 10435767

+ AEN (Address Enable) : là ngõ ra tác ộng mức cao cài 8 bit ịa chỉ cao lên bus hệ

thống, tín hiệu này có thể sử dụng ể cấm các thiết bị khác truy cập bus trong khi ang phục vụ DMA.

+ ADSTB (Address Strobe): là ngõ ra tác ộng mức cao cài các ường ịa chỉ cao ra bộ cài bên ngoài.

+ MEMR (Memory Read) : là ngõ ra 3 trạng thái tác ộng mức thấp sử dụng cho phép

8237 ọc bộ nhớ trong chu kỳ DMA ọc, hoặc trong chu kỳ truyền dữ liệu giữa bộ nhớ và bộ nhớ.

+ MEMW (Memory Write) : là ngõ ra 3 trạng thái tác ộng mức thấp sử dụng cho phép

8237 ghi bộ nhớ trong chu kỳ DMA ghi, hoặc trong chu kỳ truyền dữ liệu giữa bộ nhớ và bộ nhớ. Address Bus A0 -A15 AEN A8-A15 OE STB AEN A0-A3 A4-A7 ADSTB DB0- HLDA HLDA DB7 HOLD HRQ DREQ 0-3

CLK RESET MEMR MEMW IOR IOW DACK 0-3 CLOCK RESET MEMR MEMW IOR IOW Data Bus D0 -D7

Hình 3.16: Sơ ồ khối kết nối giữa 8237 và Bus hệ thống.

Nối ghép 8237 với hệ thống CPU.

Khi phục vụ một yêu cầu DMA ở một trong các ngõ vào DREQ, 8237 sẽ gửi yêu

cầu treo bus tới CPU bằng cách cung cấp mức cao tới ngõ ra HRQ, CPU nhận tín

hiệu này tại ngõ vào HOLD, lúc này nó thực hiện hết chu kỳ lệnh hiện hành rồi treo

các bus lên trạng thái trở kháng cao và trả lời cho 8237 bằng tín hiệu HLDA. Khi lOMoARcPSD| 10435767

nhận ược tín hiệu trả lời của CPU, 8237 bắt ầu quá trình chiếm bus ể thực hiện

chu kỳ phục vụ DMA. Địa chỉ mà 8237 tạo ra bao gồm 2 byte,

8 bit cao cung cấp tới các ngõ ra A0-A7, 8 bit thấp sẽ cung cấp ra data bus DB0DB7

và ược xung ADSTB cài vào bộ cài 8 bit cung cấp tới bộ nhớ.

Hoạt ộng DMA.

8237 ược thiết kế hoạt ộng ở hai chu kỳ chính là: chu kỳ rỗi (Idle cycle) và

chu kỳ tích cực (active cycle). Trong mỗi chu kỳ này có thể chia thành nhiều trạng thái

khác nhau . 8237 phân biệt bảy trạng thái hoạt ộng riêng biệt bao gồm:

- Trạng thái không tích cực IS (Inactive State): Trạng thái này không có yêu cầu

DMA hợp lệ, các ngõ vào yêu cầu ở trạng thái treo. IS ược tính cả thời iểm 8237 trong

trạng thái ang lập trình.

- S0 là trạng thái ầu tiên của chu kỳ phục vụ DMA, lúc này 8237 ang gửi yêu cầu

treo Bus nhưng CPU chưa gửi trả tín hiệu xác nhận HLDA. 8237 sẽ ở trạng thái này

cho ến khi CPU cung cấp tín hiệu chấp nhận yêu cầu treo BUS HLDA, tín hiệu này của

CPU sẽ cho phép 8237 bắt ầu chu kỳ truyền dữ liệu của nó.

- S1, S2, S3 và S4 là các chu kỳ làm việc trong chu kỳ phục vụ DMA. Khi giao

tiếp với các bộ nhớ có tốc ộ áp ứng chậm một trạng thái chờ có thể thêm vào giữa S2

và S3 cho ến khi tín hiệu ngõ vào READY của 8237 hết tích cực. Chú ý là dữ liệu ược

truyền trực tiếp giữa bộ nhớ và vào/ra với, các tín hiệu MEMR và IOW hoặc MEMW

và IOR tác ộng một cách ồng thời tại một thời iểm. Dữ liệu sẽ không ọc vào hoặc ghi

ra 8237 trong các chu kỳ truyền dữ liệu giữa vào ra và bộ nhớ.

Việc truyền dữ liệu giữa các ô nhớ một chu kỳ ọc từ ô nhớ truyền và 1 chu kỳ

ghi vào ô nhớ nhận cho mỗi byte. Như vậy trong chu kỳ này sẽ yêu cầu 8 trạng thái

cho việc truyền một byte. Các trạng thái S11, S12, S13, S14 cho việc ọc dữ liệu từ

bộ nhớ, và các trạng thái S21, S22, S23, S24 cho việc ghi dữ liệu vào bộ nhớ. Chu kỳ rỗi.

Khi không có kênh DMA nào yêu cầu ược phục vụ, 8237 sẽ chuyển qua chu kỳ

rỗi và thực hiện trạng thái SI. Trong chu kỳ này 8237 sẽ kiểm tra các ngõ vào DREQ

tại mỗi chu kỳ xung CLK xem có yêu cầu DMA nào cần phục vụ hay không. Trong

chu kỳ này 8237 cũng kiểm tra ngõ vào CS xem CPU có thực hiện các chu kỳ ọc

ghi các thanh ghi của nó hay không. Khi CS và HLDA ều ở mức thấp 8237 sẽ ở

trạng thái lập trình các iều kiện hoạt ộng. CPU lúc này có thể thực hiện các công

việc như tạo lập, thay ổi kiểm tra các tình trạng hiện thời của 8237 bằng cách ọc

ghi các thanh ghi bên trong 8237. Các ường ịa chỉ vào A0 - A3 sử dụng ể CPU

xác ịnh tới các thanh ghi mà nó muốn ọc hoặc ghi. Các tín hiệu IOR và IOW lúc này

sẽ là các ngõ vào cung cấp từ CPU ể ịnh nghĩa chu kỳ là ọc hay ghi. Khi ó ối

với các thanh ghi ếm ịa chỉ, hoặc các thanh ghi ếm số từ 6 bit sẽ có thêm 1 bit ể lOMoARcPSD| 10435767

xác ịnh phần cao hay phần thấp của chúng ược phép truyền dữ liệu với CPU. Các

bit này có thể lập trình trước bằng phần mềm, và sẽ xóa khi có tín hiệu RESET.

Đặc biệt trong chế ộ này CPU có thể lập trình các chế ộ hoạt ộng cho 8237

với sự tác ộng CS, IOW và các bit ịa chỉ tương ứng. Các lệnh sẽ bao gồm cả

việc lập xóa các Flip/Flop chọn phần cao hay thấp của các thanh ghi, và lệnh

RESET toàn bộ các thanh ghi của 8237.

Chu kỳ tích cực.

Khi ang trong chu kỳ rỗi, nếu có tín hiệu yêu cầu cung cấp tới ngõ vào DREQ không

bị lập trình che của 8237, nó sẽ gửi tín hiệu HRQ tới vi xử lý và chuyển qua chu kỳ

tích cực. Trong chu kỳ này 8237 sẽ làm việc ở 1 trong 4 chế ộ. Chế ộ truyền byte.

Trong chế ộ này 8237 ược lập trình chỉ thực hiện 1 chu kỳ truyền, các bộ ếm số

từ và ịa chỉ sẽ ược tăng hoặc giảm sau mỗi lần truyền. Khi bộ ếm số từ quay lại từ

0 tới FFFFH thì kết thúc ếm TC (Terminal Count) sẽ ược tự ộng thiết lập nếu kênh ã ược lập trình TC.

DREQ phải giữ nguyên mức tích cực cho ến khi DACK tích cực. Khi DREQ không

còn giữ mức tích cực, HRQ sẽ hết tác ộng giải phóng bus hệ thống. Nếu nó tác ộng trở

lại và nhận ược tín hiệu HLDA, một chu kỳ truyền byte khác sẽ ược thực hiện. Điều

này cho phép việc truyền dữ liệu xem vào các chu kỳ hoạt ộng của CPU. Việc ịnh thời

hoạt ộng của 8237 sẽ tùy thuộc vào ặc tính của vi xử lý.

Chế ộ truyền khối.

Trong chế ộ truyền khối 8237 sẽ thực hiện việc truyền dữ liệu cho ến khi bộ ếm số từ

chuyển từ 0000H tới FFFFH, hoặc khi ngõ vào EOP tác ộng mức 0. DREQ chỉ cần giữ

mức tác ộng cho ến khi DACK tác ộng. Nếu ược lập trình thì quá trình tự ộng khởi ộng

sẽ thực hiện khi kết thúc phục vụ DMA.

Chế ộ truyền theo yêu cầu.

Trong chế ộ này 8237 sẽ truyền dữ liệu liên tục cho tới khi kết thúc ếm TC (bộ ếm từ

chuyển từ 0000H tới FFFFH), hoặc khi gặp tín hiệu EOP, hoặc khi DREQ hết tích cực.

Như vậy thiết bị có thể duy trì việc truyền dữ liệu cho ến khi hết dung lượng của nó.

Khi dữ liệu chưa truyền hết mà gặp TC, hoặc có tín hiệu EOP thì phục vụ DMA sẽ ược

thiết lập lại vì DREQ vẫn còn tích cực..

Chế ộ xếp tầng.(Cascade Mode). 8237 tầng thứ hai lOMoARcPSD| 10435767 8237 t ầ ng th ứ nh ấ t CPU DREQ HRQ DACK HLDA HOLD HRQ HLDA HLDA DREQ HRQ HLDA DACK

Hình 3.17: Hệ thống xếp tầng 8237.

Trong chế ộ này có thể xếp tầng nhiều bộ iều khiển DMA ể tăng số yêu cầu ngõ

vào. Các tín hiệu HRQ và HLDA của 8237 thêm sẽ ược nối vào DREQ và DACK

của 8237 trước nó. Điều này cho phép 8237 phía sau truyền yêu cầu qua 8237 trước nó,

trình tự ưu tiên vẫn ược duy trì, và ngõ vào mới yêu cầu sẽ phải chờ cho ến khi có tín

hiệu chấp nhận yêu cầu DACK. Vì thế kênh xếp tầng của 8237 chủ chỉ sử dụng cho

8237 cộng thêm, và nó sẽ quyết ịnh mức ưu tiên cho các kênh cộng thêm ó. Nó không

ược ưa ra ịa chỉ của mình vì như vậy sẽ gây ra xung ột với các kênh cộng thêm của

nó. 8237 sẽ áp ứng các tín hiệu DREQ và DACK còn tất cả các tín hiệu khác ngoại

trừ HRQ ều không ược phép tác ộng.

Hình 3.17 mô tả việc xếp tầng thêm hai 8237 tớ vào hai kênh của 8237 chủ, tạo

thành hệ thống DMA hai mức. Có thể tăng thêm nhiều 8237 vào các kênh khác của

8237 tầng thứ nhất. Cũng có thể tăng thêm số kênh yêu cầu bằng cách, xếp tầng vào

các kênh của các 8237 tầng thứ hai tạo thành hệ thống 3 tầng.

Các kiểu truyền dữ liệu.

Trong mỗi chế ộ truyền nêu trên 8237 có thể ở một trong 3 kiểu truyền là: ọc ghi và

kiểm tra. Trong kiểu ghi dữ liệu sẽ ược chuyển từ thiết bị vào ra tới bộ nhớ bằng cách

tác ộng ồng thời các tín hiệu IOR và MEMW. Trong kiểu ọc dữ liệu sẽ ược chuyển

từ bộ nhớ tới thiết bị vào ra bằng cách tác ộng ồng thời các tín hiệu

MEMR và IOW. Kiểu kiểm tra sẽ thực hiện các việc truyền giả. Trong kiểu này 8237

tạo ra ịa chỉ và áp ứng EOP giống như trong kiểu ọc và ghi, nhưng các tín hiệu iều

khiển bộ nhớ và vào ra sẽ không ược tác ộng. Chế ộ kiểm tra không ược cho phép hoạt

ộng trong chu kỳ truyền dữ liệu giữa bộ nhớ và bộ nhớ. Truyền dữ liệu giữa bộ nhớ - bộ nhớ.

Chu kỳ này cho phép việc truyền một khối dữ liệu từ vùng nhớ này qua vùng nhớ khác

với thời gian ngắn nhất. Một bit trong thanh ghi lệnh có thể lập trình cho các kênh 0

và 1 có thể hoạt ộng ở chế ộ truyền giữa bộ nhớ và bộ nhớ. Quá trình sẽ ược bắt ầu lOMoARcPSD| 10435767

bằng cách thiết lập yêu cầu DMA bằng phần mềm (không phải bằng tín hiệu ưa tới

ngõ vào DREQ). Khi ó 8237 sẽ thực hiện việc yêu cầu DMA như bình thường. Sau

khi nhận ược tín hiệu trả lời HLDA từ CPU, 8237 sẽ thực hiện 8 trạng thái truyền

trong chế ộ truyền khối. Đầu tiên nó sẽ ọc dữ liệu từ bộ nhớ, thanh ghi ịa chỉ hiện

hành của kênh 0 ược sử dụng giữ ịa chỉ nguồn dữ liệu có thể tăng hoặc giảm như thông

thường. Dữ liệu ọc ược từ bộ nhớ sẽ ược chứa vào thanh ghi tạm thời bên trong 8237.

Kênh 1 sẽ ghi dữ liệu trong thanh ghi tạm thời tới ịa chỉ chứa trong thanh ghi ịa chỉ

hiện hành của nó, thanh ghi này cũng có thể tăng hoặc giảm như thông thường. Bộ ếm

số từ của kênh 1 sẽ ược giảm, và khi nó chuyển từ 0000H sang FFFFH thì TC sẽ xảy

ra, TC và ngõ ra EOP sẽ tác ộng chỉ thị kết thúc phục vụ DMA.

Kênh 0 có thể lập trình ể duy trì một ịa chỉ cho tất cả các lần truyền, iều này cho phép

lấp ầy một vùng nhớ chỉ bằng một từ duy nhất (chỉ thay ổi ịa chỉ ích, không thay ổi ịa chỉ nguồn).

8037 sẽ áp ứng tín hiệu EOP trong suốt quá trình truyền dữ liệu giữa bộ nhớ và

bộ nhớ. Điều này cho phép thực hiện việc so sánh tìm kiếm trong một chuỗi dữ liệu

có sắp xếp, bằng cách cung cấp tín hiệu tới ngõ vào EOP khi tìm ược dữ liệu mong muốn.

Tự ộng khởi ộng.

Bằng cách lập một bit trong thanh ghi chế ộ , có thể lập trình cho một kênh tự ộng

khởi ộng. Trong chế ộ này giá trị của các thanh ghi ịa chỉ hiện hành, và thanh ghi ếm

số từ hiện hành sẽ ược phục hồi lại bằng giá trị của các thanh ghi cơ sở tương ứng khi

EOP. Giá trị của các thanh ghi cơ sở ược CPU nạp ồng thời với các thanh ghi hiện hành,

nhưng chúng không bị thay ổi trong suốt quá trình phục vụ DMA. Bit che (mask) sẽ

không ược xoá trong chế ộ tự ộng khởi ộng. Ngay sau quá trình khởi ộng lại kênh sẽ

sẵn sàng thực hiện một yêu cầu DMA khác mà không cần sự can thiệp nào thêm từ

CPU. Nếu không lập trình chế ộ khởi ộng lại, các thông số của kênh phải ược CPU

lập trình lại sau khi EOP, mới có thể sẵn sàng cho một phục vụ DMA mới. Trình tự ưu tiên.

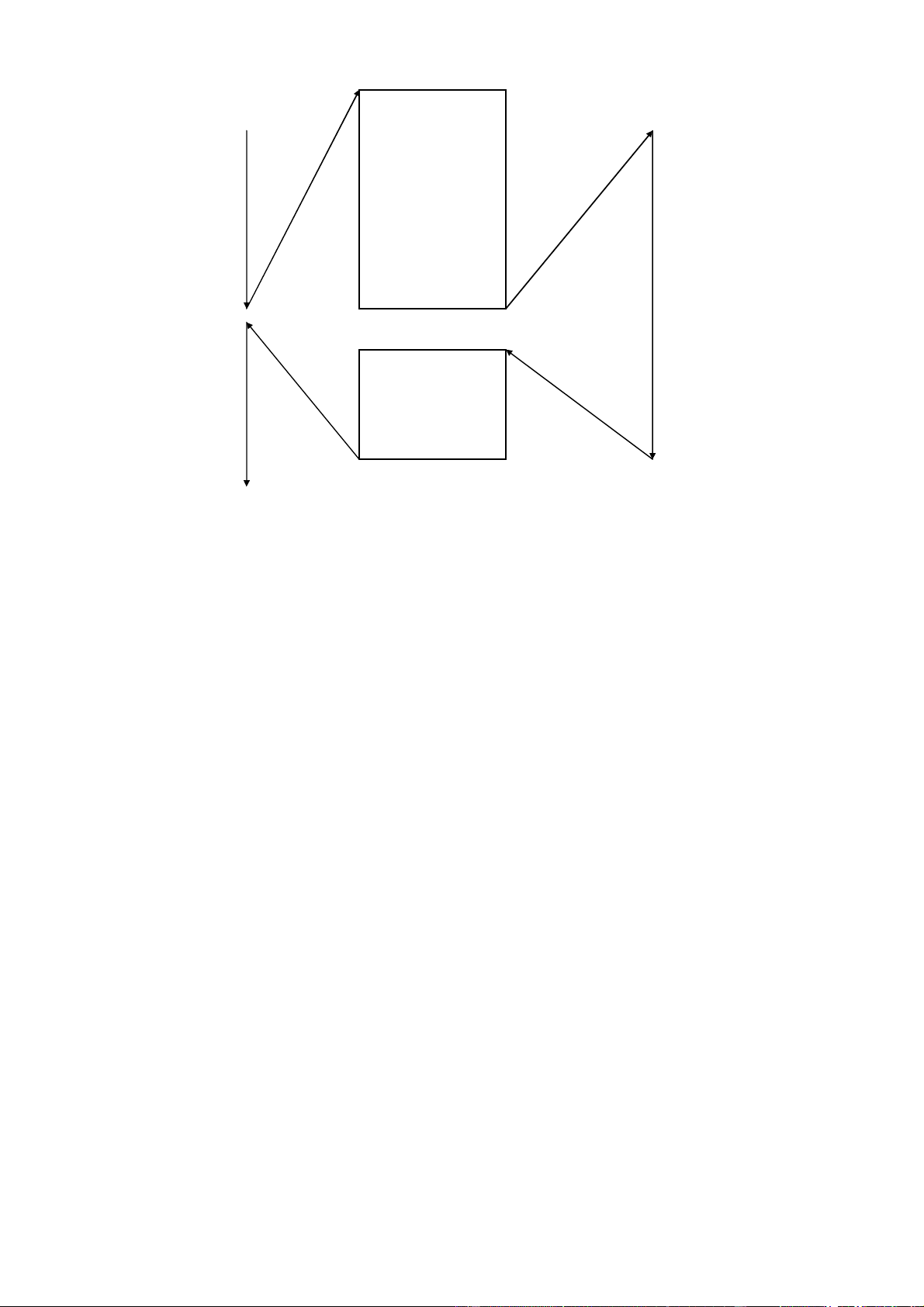

8237 có hai kiểu mã hóa ưu tiên có thể chọn bằng phần mềm ó là chế ộ ưu tiên

cố ịnh và chế ộ ưu tiên quay vòng. Trong chế ộ ưu tiên cố ịnh, ưu tiên sẽ giảm

dần theo số thứ tự của các kênh, kênh 0 có ộ ưu tiên cao nhất cho tới kênh 3 sẽ có ộ

ưu tiên thấp nhất. Khi một kênh ược phục vụ, yêu cầu của các kênh khác sẽ

bị ngăn chặn cho ến khi phục vụ ược thực hiện xong. Ưu tiên thấp nhất 3 Ưu tiên cao nhất 0 1 Phục vụ 2 lOMoARcPSD| 10435767 2 Phục 3 vụ Phục vụ 3 Yêu 0 0 1 cầu 1 2 Hình

3.18: Chế ộ ưu tiên phục vụ DMA quay vòng

Trong chế ộ ưu tiên quay vòng, kênh vừa ược phục vụ xong sẽ có mức ưu tiên thấp

nhất, kênh kế tiếp của nó sẽ có mức ưu tiên cao nhất, các kênh còn lại sẽ có ộ ưu tiên

theo vòng. Một chu trình ví dụ có thể biểu diễn như hình 3.18. Định thời rút gọn.

8237 có thể thực hiện chu kỳ truyền dữ liệu với chu kỳ rút gọn chỉ với 2 chu kỳ clock.

Chu kỳ S1 sử dụng cho việc tạo ịa chỉ, việc ọc ghi dữ liệu sẽ ược thực hiện trong S2. Tạo ịa chỉ.

Để giảm bớt số chân, 8237 kết hợp 8 bit ịa chỉ cao vào bus dữ liệu tạo thành bus a

hợp DB0 -DB7. Trong S1 các bit ịa chỉ cao sẽ cung cấp ra các ngõ này cùng với tín

hiệu cài ịa chỉ ADSTB. Cạnh lên của ADSTB sẽ cài các bit ịa chỉ này ra bộ cài ịa chỉ

bên ngoài. Tín hiệu cho phép ịa chỉ AEN sẽ cho phép ặt các ường ịa chỉ này lên bus hệ

thống trong các trạng thái còn lại. Byte ịa chỉ thấp sẽ ược cung cấp trực tiếp ra các

ường A0-A7, ưa lên bus ịa chỉ hệ thống.

Khi phục vụ trong chế ộ truyền khối và truyền theo yêu cầu bao gồm nhiều chu kỳ

truyền, các ịa chỉ sẽ ược tạo ra một cách tuần tự. Với các chu kỳ truyền bằng các ịa chỉ

kế tiếp nhau, các bit ịa chỉ cao chỉ phải thay ổi một lần trong 256 lần truyền. Do ó các

ường ịa chỉ cao và tín hiệu ADSTB chỉ tác ộng 1 lần sau 256 lần truyền, 255 lần truyền

còn lại các ường này chỉ dành cho dữ liệu. lOMoARcPSD| 10435767 7 6 5 4 3 2 1 0

0: Không cho phép truy ề n b ộ nh ớ - b ộ nh ớ

1: Cho phép truy ề n b ộ nh ớ - b ộ nh ớ

0: Không cho phép kênh 0 gi ữ nguyên ị a chỉ

1: Cho phép kênh 0 gi ữ nguyên ị a chỉ x: khi bit D 0 = 0

0: DMAC bị c ấ m hoạt ộ ng

1: DMAC ượ c phép hoạt ộ ng 0:

Chê ộ ị nh th ờ i bình th ườ ng 1: Ch

ế ộ ị nh th ờ i rút gọ n ( chỉ truy ề n 2 CLK) x: khi bit D0 = 0

0: Ch ế ộ ưu tiên cố ị nh 1: Ch ế ộ ưu tiên quay vòng

0: Ghi kéo dài (cho b ộ nh ớ ch ậ m) 1: Ghi thông th ườ ng x: Khi bit D3 = 0 0: DR EQ tá c ộ ng m ứ c cao 1: DREQ tá c ộ ng m ứ c th ấ p 0: DA

CK tá c ộ ng m ứ c th ấ p

1: DREQ tá c ộ ng m ứ c cao

Hình 3.19: Thanh ghi lệnh của 8237.

Mô tả các thanh ghi.

Thanh ghi ịa chỉ hiện hành.

Mỗi kênh DMA có 1 thanh ghi ịa chỉ hiện hành 16 bit. Thanh ghi này sẽ giữ ịa chỉ

trong suốt quá trình phục vụ DMA. Giá trị ịa chỉ sẽ tự ộng tăng hoặc giảm sau mỗi lần

truyền. Giá trị của thanh ghi này có thể CPU ọc ược mỗi lần 8 bit, và nó có thể phục

hồi lại giá trị ban ầu từ thanh ghi cơ sở nếu kênh ược lập trình tự ộng khởi ộng lại. Quá

trình tự ộng khởi ộng lại chỉ xảy ra sau khi EOP. lOMoARcPSD| 10435767 7 6 5 4 3 2 1 0

00: chọ n l ậ p trình thanh ghi ch ế ộ kênh 0

01: chọ n l ậ p trình thanh ghi ch ế ộ kênh 1 10:

chọ n l ậ p trình thanh ghi ch ế ộ kênh2

11: chọ n l ậ p trình thanh ghi ch ế ộ kênh 3 ề n ki ể m tra 01: Tr uy ề n ghi 10: Tr uy ền ọ c chọ 11:

n l ậ p trình thanh ghi ch ế ộ kênh 3

0: không kh ởi ộ ng t ự ộ ng 1: kh ởi ộ ng t ự ộ ng 0: