Preview text:

lOMoARcPSD| 10435767

CHƯƠNG 5 – GIAO TIẾP SỐ LT6

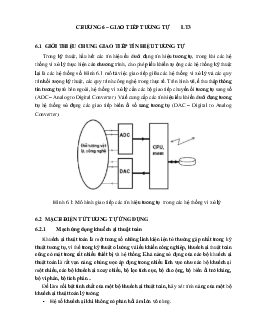

5.1 GIAO TIẾP SONG SONG 5.1.1 Nguyên lý Các cổng vào ra song song

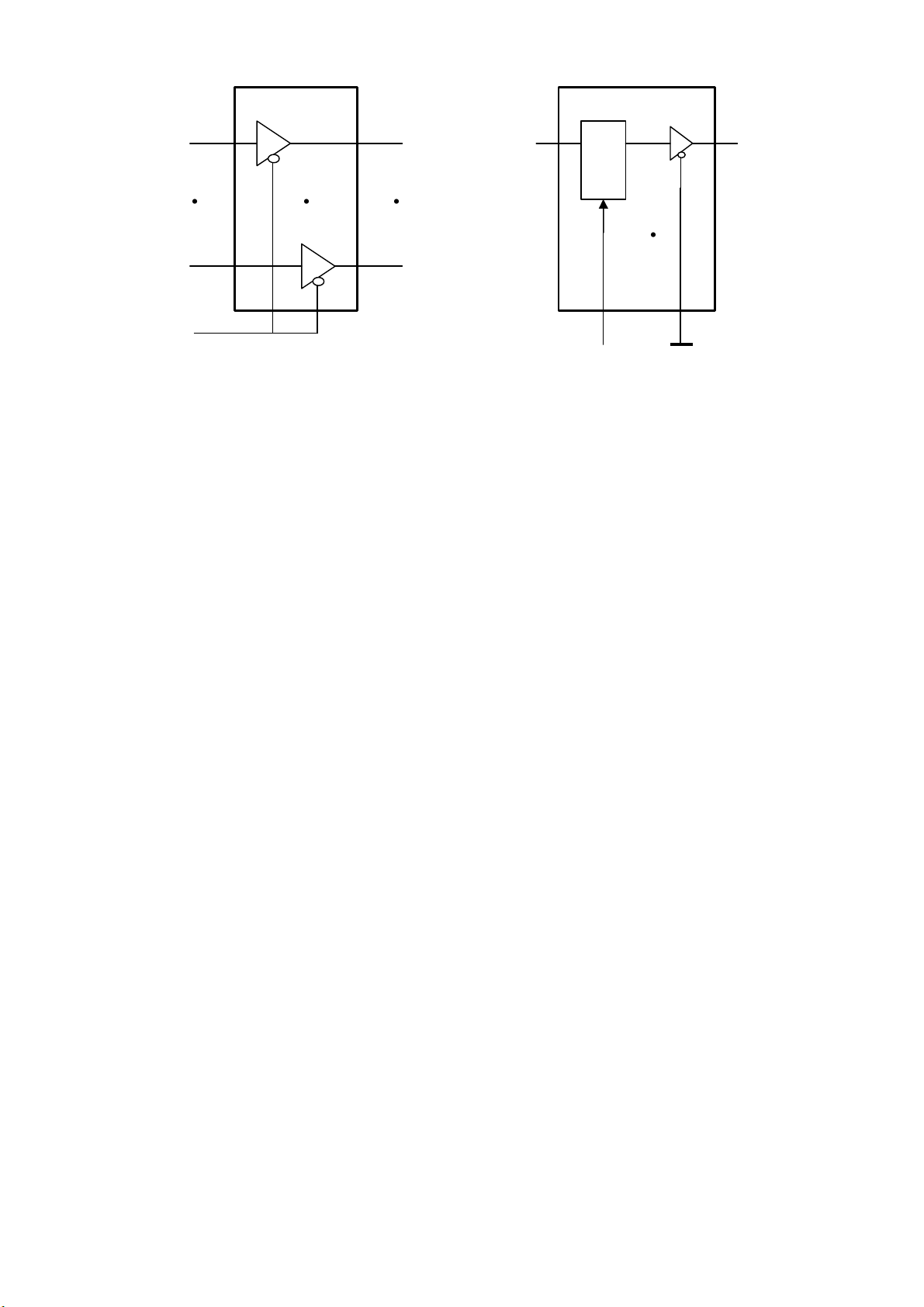

ược thực hiện theo nguyên tắc của các bộ ệm

(buffer), cài (latch) trên hình 5.1. Với cổng ệm, khi tín hiệu cho phép OC ở trạng thái

không tích cực (mức 1), ngõ ra sẽ ở trạng thái trở kháng cao, khi tín hiệu cho phép OC

tích cực (mức 0), trạng thái ngõ ra sẽ có mức logic giống trạng thái ngõ vào. Còn ối với

các cổng cài, khi tín hiệu cho phép G không tích cực, ngõ ra giữ nguyên trạng thái hiện

tại của nó, nếu tín hiệu cho phép tích cực trạng thái logic ngõ ra sẽ tương ứng với logic

ngõ vào. Trong các hệ thống vi xử lý, các bộ ệm cài này một ầu sẽ nối tới Bus dữ liệu

của CPU, ầu còn lại nối tới thiết bị, ngõ vào cho phép sẽ ược nối tới ngõ ra của giải mã

ịa chỉ. Khi truy cập dữ liệu, CPU cung cấp ịa chỉ tương ứng làm ngõ vào cho phép của

các cổng này tích cực, sau ó nó sẽ truyền dữ liệu với thiết bị qua cổng. Giải mã ịa chỉ

ảm bảo cho ứng với một giá trị ịa chỉ của CPU cung cấp, chỉ có một cổng vào ra duy

nhất ược cho phép hoạt ộng. D Q G OC Cổng ệm 3 trạng thái Cổng cài

Hình 5.1: Các thành phần tạo nên các cổng vào ra song song cơ bản.

Với nguyên tắc của các cổng ệm cài nêu trên, có rất nhiều mạch tích hợp mật ộ vừa

ược sản xuất sử dụng làm các cổng vào ra cơ bản trong hệ thống vi xử lý. Thông thường

các vi mạch này có 8 hoặc 16 ường vào ra, hình 5.2 mô tả cấu trúc của các vi mạch ệm 74LS244 và cài 74LS373. lOMoARcPSD| 10435767 74 LS244 74 LS373 D0 Q0 D0 D Q Q0 . . . . . . G . . . . . . D7 Q7 OC G OC

Hình 5.2: Các vi mạch vào ra cơ bản.

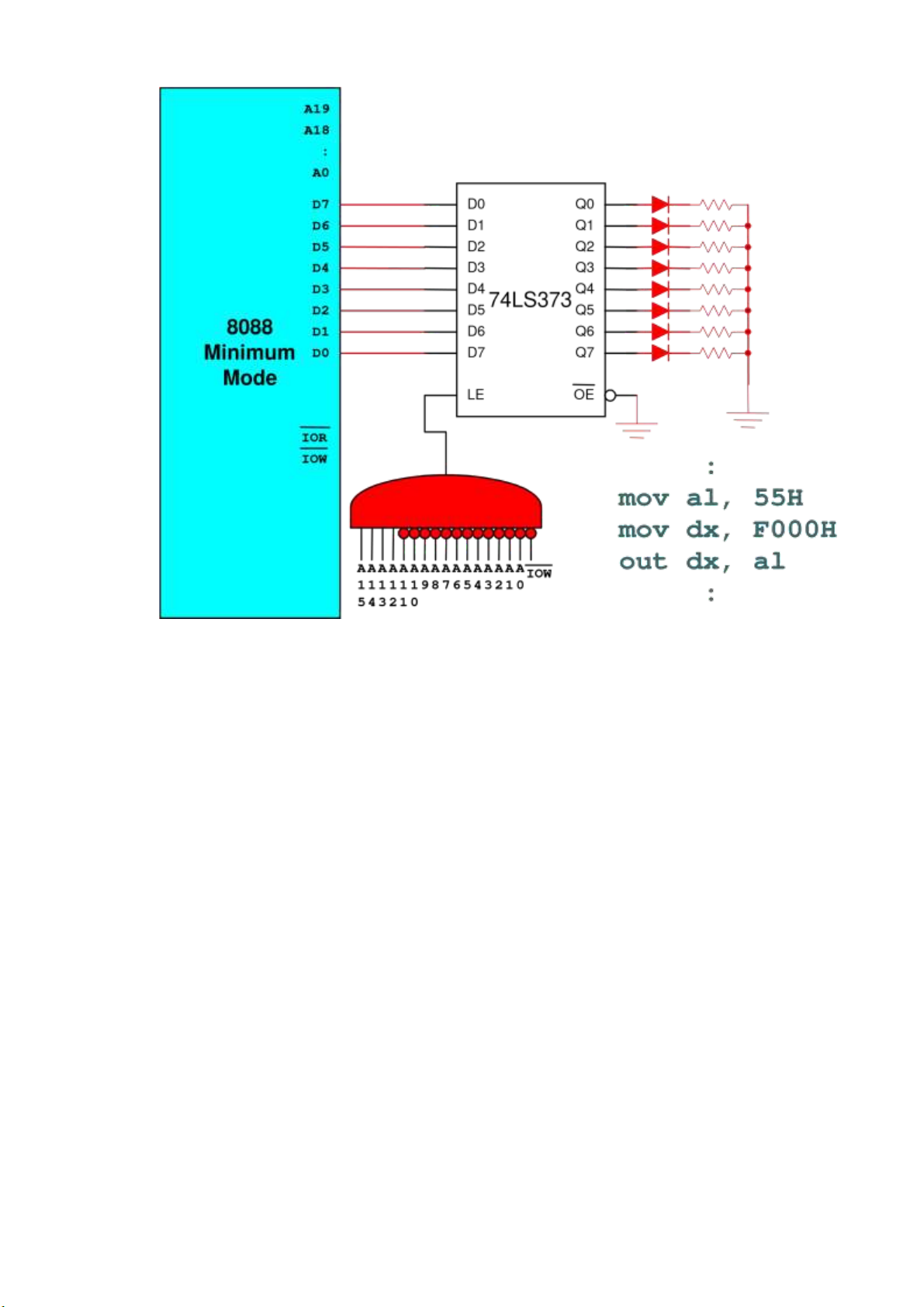

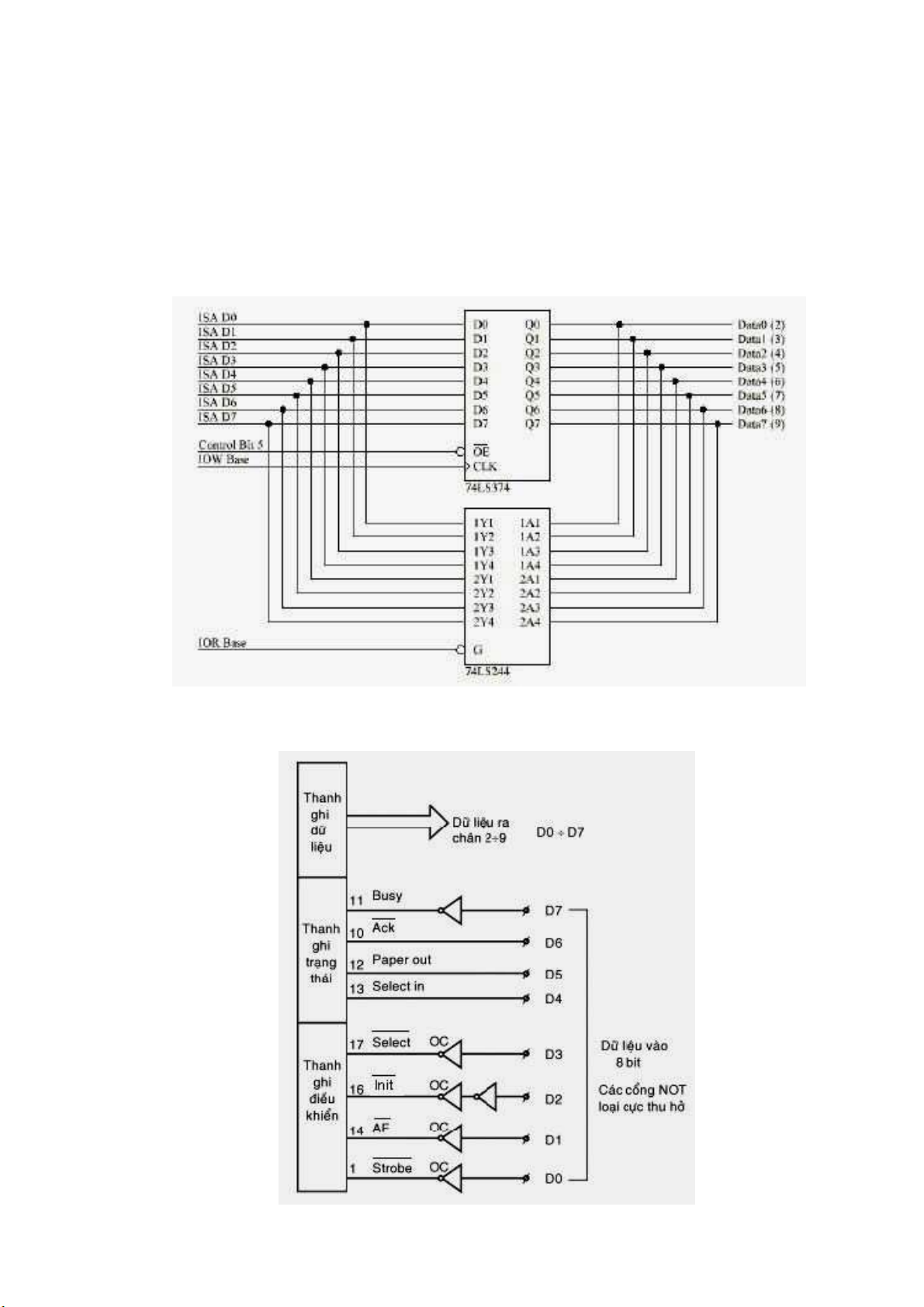

Hình 5.3 mô tả việc giải mã ịa chỉ và ghép nối một cổng ra cơ bản 8 bit iều khiển 8

led ơn trong một hệ thống vi xử lý 8088. Trên hình vẽ, các ngõ vào của các D-Flip Flop

trong vi mạch 74LS373 ược nối tới bus dữ liệu của hệ thống vi xử lý. Các ường ịa chỉ

và tín hiệu IOW cấp tới ngõ vào của cổng AND. Ngõ ra của cổng AND sẽ ở mức cao

khi tất cả các ngõ vào bằng 1. Và khi ó, dữ liệu từ ngõ vào 74LS373 sẽ ược chuyển tới

ngõ ra làm các Led sáng tắt theo dữ liệu này. Lệnh “OUT DX,AL” sẽ cấp tín hiệu

IOW=0, giá trị của DX=F000H sẽ cung cấp tới các ường ịa chỉ A15-A0, ngõ ra cổng

AND sẽ bằng 1 và dữ liệu từ AL=55H cung cấp tới các ường dữ liệu D7D0 sẽ ược

chuyển qua ngõ ra các cổng cài trong 74LS373 làm các Led sáng – tắt xen kẽ. Khi lệnh

OUT thực hiện xong, IOW trở về mức 1, cổng cài óng lại nhưng các led vẫn giữ nguyên

trạng thái do ược cấp từ chân Q của Flip-Flop. lOMoARcPSD| 10435767

Hình 5.3: Kết nối cổng ra cơ bản trong hệ thống vi xử lý

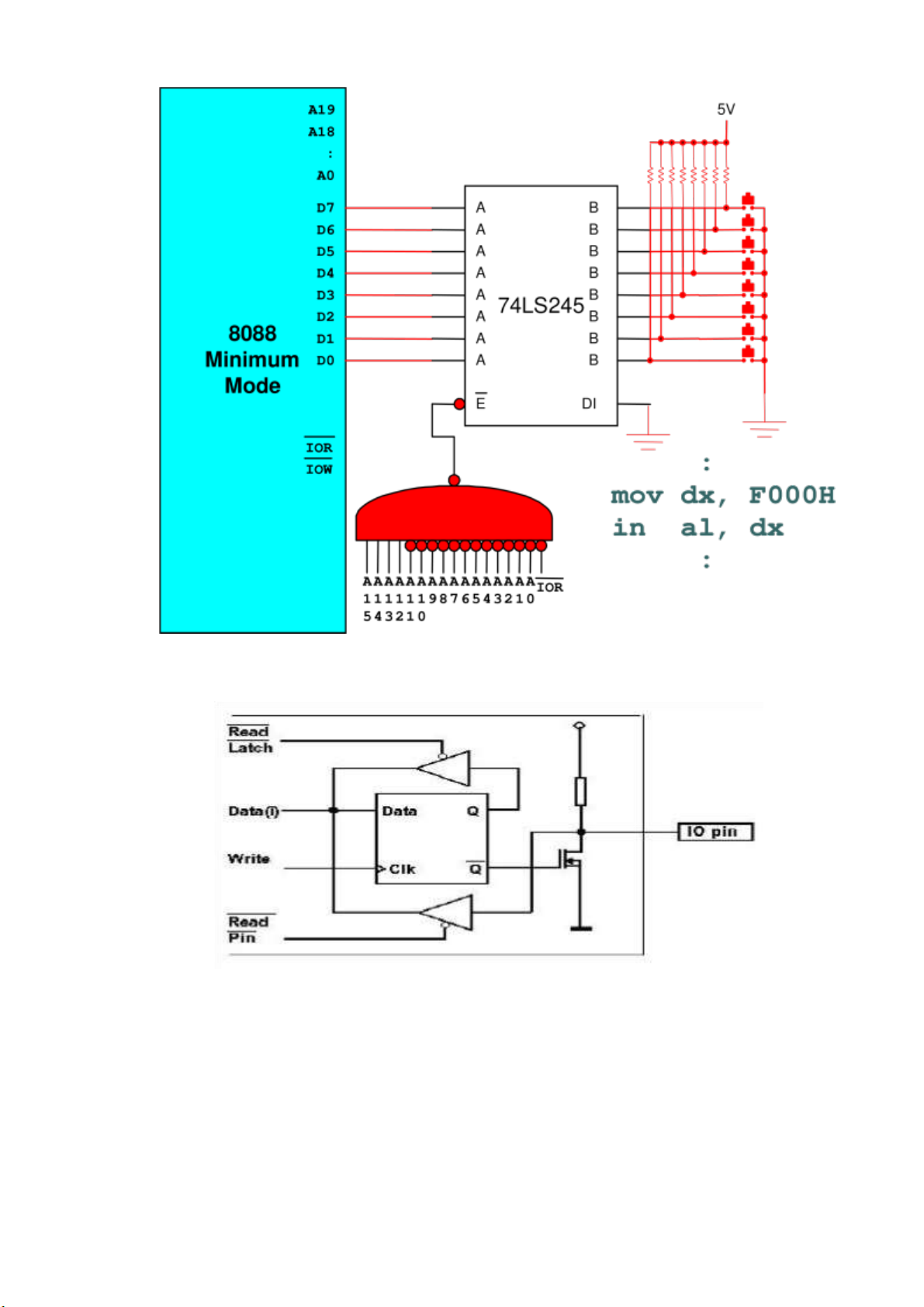

Hình 5.4 mô tả kết nối một cổng vào cơ bản 8 bit nhận dữ liệu từ 8 phím nhấn.

Tương tự như lệnh OUT, lệnh “IN DX,AL” sẽ cấp tín hiệu IOR=0, A15A0=DX=F000H

làm ngõ ra cổng NAND bằng 0. Tín hiệu này sẽ mở các cổng ệm 3 trạng thái chuyển dữ

liệu từ các nút nhấn vào bus dữ liệu và lấy vào trong CPU. Chú ý không ược sử dụng

các mạch cài cho các cổng vào, vì dữ liệu luôn giữ ở ngõ ra mạch cài sẽ gây xung ột bus

dữ liệu khi CPU truy cập một vị trí khác trong hệ thống. lOMoARcPSD| 10435767

Hình 5.4: Kết nối cổng vào cơ bản trong hệ thống vi xử lý

Hình 5.5: Cấu trúc một cổng vào ra số kết hợp

Với các cấu trúc ệm cài cơ bản như trên, chúng chỉ óng vai trò hoặc là cổng vào,

hoặc là cổng ra cơ bản. Trong các vi mạch vào ra tích hợp mật ộ cao hoặc các cổng vào

ra của các bộ vi iều khiển, một cổng số thường tích hợp tích năng của cả ngõ vào và ngõ

ra, chúng sẽ có cấu trúc như mô tả trên hình 5.5. Trên hình vẽ, khi cung cấp tín hiệu

Read Pin, dữ liệu trên ngõ IO sẽ ược lấy vào bên trong mạch qua cổng ệm 3 trạng thái.

Khi muốn ghi một dữ liệu ra ngoài chân I/O, ặt dữi liệu cần ghi vào chân Data và cấp lOMoARcPSD| 10435767

tín hiệu Write. Giả sử ặt mức 0 vào chân data, sau khi cấp Write ngõ ra Q của D – Flip

Flop sẽ bằng 0, Q ảo bằng 1 làm MOSFET dẫn bão hoà, ngõ ra sẽ có mức logic 0. Mạch

còn có chức năng ọc lại giá trị ang ược giữ tại cổng bằng cách cung cấp tín hiệu Read Latch.

Hình 5.6: Cấu trúc một cổng vào ra số có bắt tay

Đối với các cổng vào ra cơ bản trên, khi muốn cung cấp dữ liệu tới thiết bị, CPU chỉ

ơn giản thực hiện một lệnh OUT, hoặc khi muốn nhận dữ liệu từ thiết bị CPU sẽ thực

hiện lệnh IN. Trong khi ó, có thể các thiết bị mà CPU truy cập chưa sẵn sàng hoạt ộng.

Ví dụ như, máy in chưa ược bật nguồn thì không thể nhận dữ liệu từ CPU ể in, bàn phím

không ược nhấn thì không cung cấp ược mã phím nhấn khi CPU ọc. Để chắc chắn dữ

liệu ược truyền nhận giữa CPU và các thiết bị ngoại vi, trong các hệ thống vi xử lý

thường thiết kế thêm các mạch iện tử thực hiện các chức năng bắt tay giữa CPU và thiết bị.

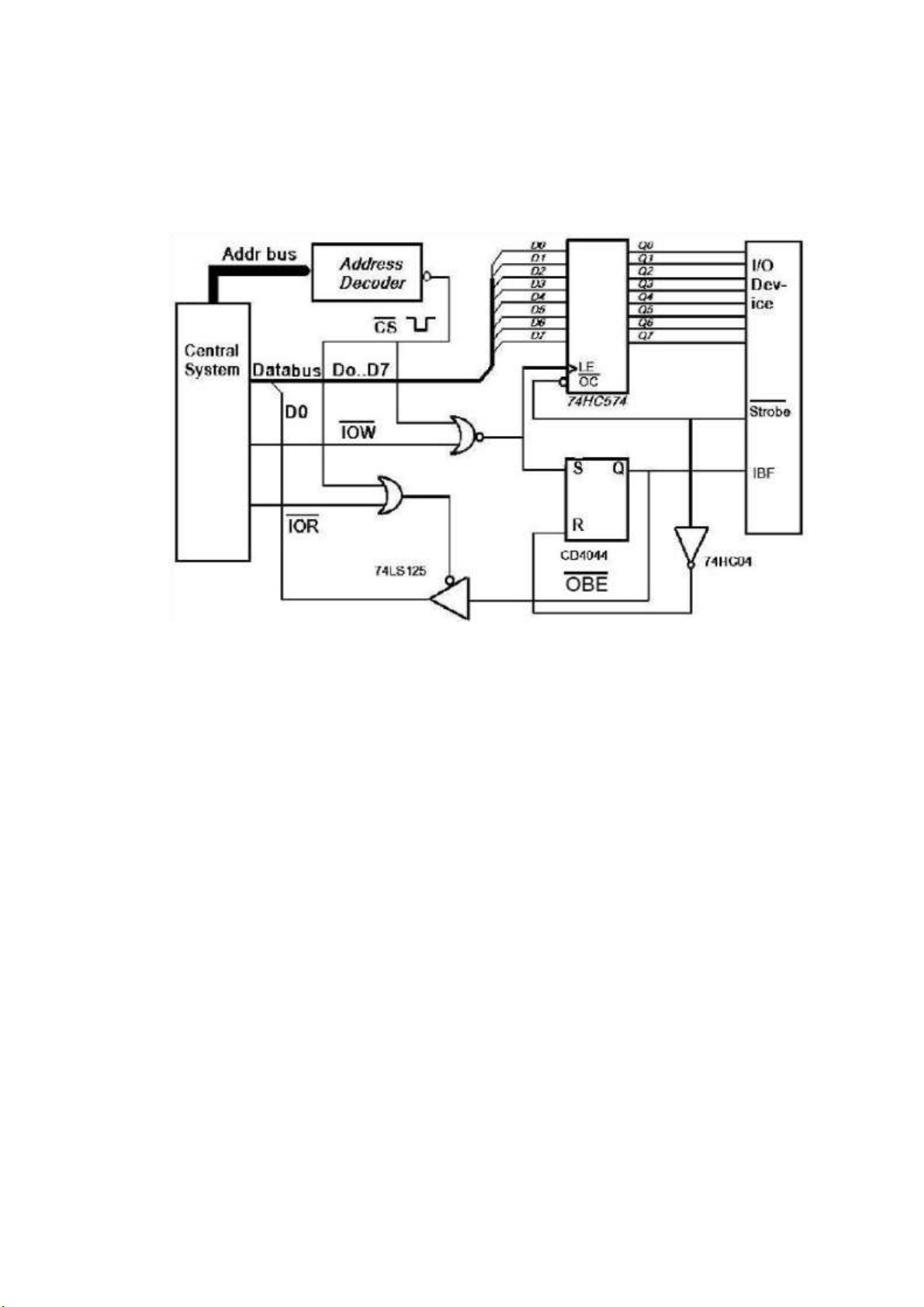

Hình 5.6 mô tả một mạch ra có tín hiệu bắt tay. Khi CPU muốn ghi dữ liệu tới thiết

bị, trước hết nó cấp ịa chỉ tới bộ giải mã ịa chỉ làm CS=0, cấp tín hiệu IOW=0. Hai tín

hiệu CS và IOW ược ưa vào cổng NOR cấp tới LE của 74HC154 mức logic 1, tín hiệu

này sẽ mở cổng ể dữ liệu từ bus dữ liệu của CPU chuyển qua 74HC574 cấp tới thiết bị.

Tín hiệu ưa tới LE cũng ồng thời ưa tới ngõ vào S của D Flip Flop, làm ngõ ra Q của nó

tác ộng mức 1, mức 1 này ược cấp tới ngõ vào IBF của thiết bị, báo cho thiết bị biết ã

có một dữ liệu từ CPU ược gởi tới cho nó. Khi thiết bị nhận dữ liệu mà CPU ã cung cấp,

nó tác ộng tín hiệu Strobe mức 0 ể lấy dữ liệu từ trong 74HC574 ra, ồng thời Strobe lOMoARcPSD| 10435767

cũng ược ảo trạng thái cấp tới ngõ và R của D FlipFlop xoá tín hiệu IBF. CPU cũng có

thể ọc tín hiệu IBF ể xác ịnh xem dữ liệu ã ược thiết bị lấy xong chưa bằng cách thực

hiện lệnh IN làm IOR=0 và với ịa chỉ làm CS=0.

Để việc truyền nhận dữ liệu tốt hơn trong các hệ thống vi xử lý thường sử dụng các

vi mạch vào ra tích hợp mật ộ cao với các cơ chế vào ra phức tạp hơn. 5.1.2

Cổng vào ra song song lập trình ược

Các cổng vào ra lập trình trước hết cung cấp thêm các tín hiệu bắt tay với thiết bị

ngoại vi kết nối với nó, ngoài ra nó còn ược tích hợp nhiều chế ộ hoạt ộng khác nhau mà

người sử dụng có thể chọn bằng cách lập trình bằng các lệnh thích hợp trong chương

trình. Trong phần này sẽ giới thiệu bộ vào ra song song lập trình PPI 8255 của hãng Intel

ược sử dụng trong hầu hết các hệ thống máy tính.

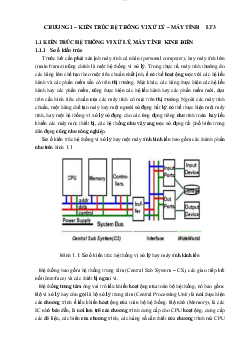

Vi mạch 8255 ược gọi là mạch nối ghép vào ra lập trình ược (programmable

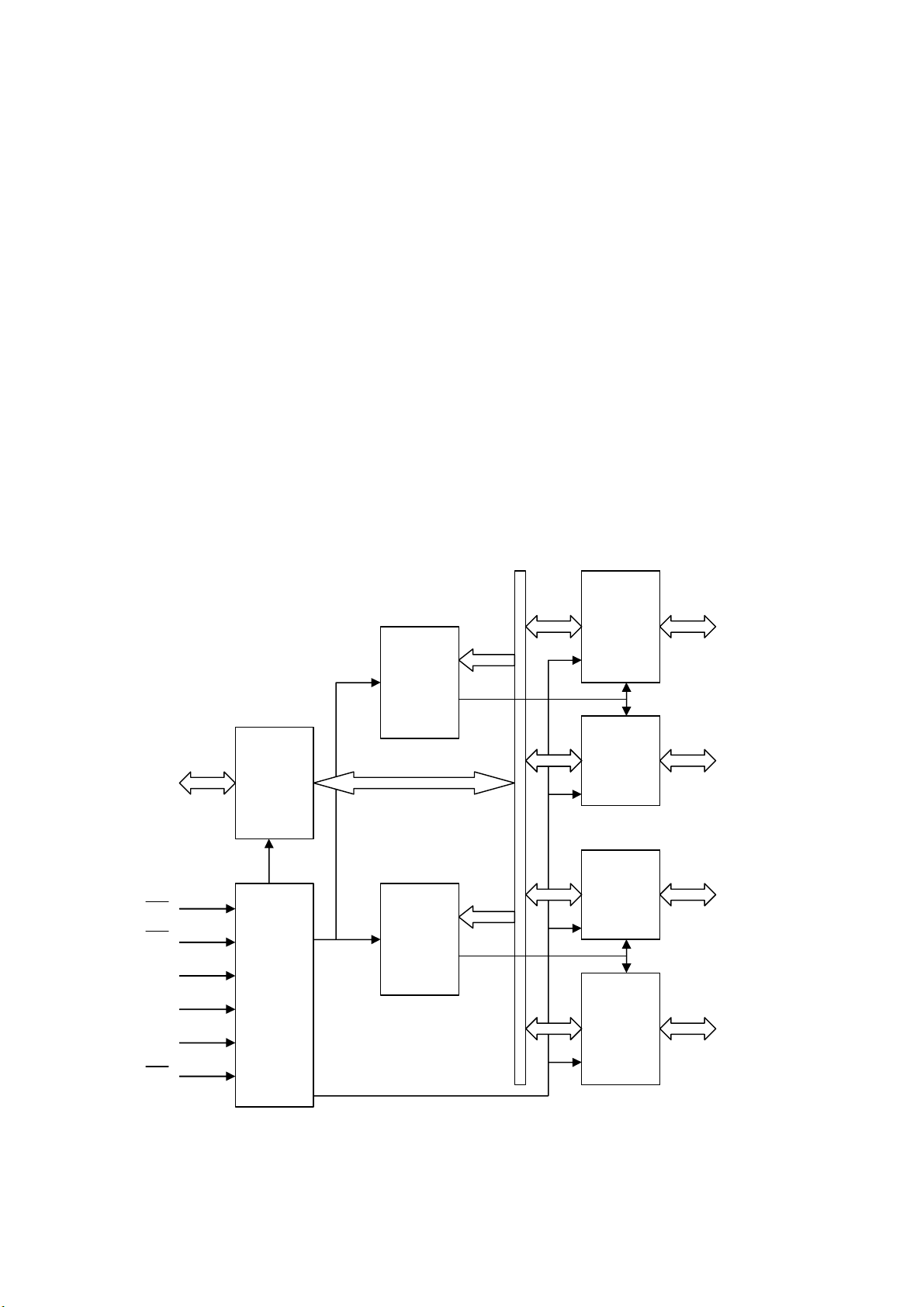

peripheral interface – PPI) có sơ ồ khối biểu diễn trên hình 5.7. Bus n ộ i Nhóm A PA0 – PA7 C ổ ng A Điề u khi ể n Nhóm A Nhóm A Đệ m Bus PC0 – PC3 C ổ ng C D0 – D7 d ữ li ệ u ( cao) Nhóm B PC4 – PC7 C ổ ng C Điề u RD ( th ấ p) Logic khi ể n WR iề u Nhóm B khi ể n A0 ọ c ghi A1 Nhóm B PB0 – PB7 C ổ ng B Reset CS

Hình 5.7: Sơ ồ khối bộ vào ra lập trình 8255. lOMoARcPSD| 10435767

8255 có ba cổng vào ra song song PA, PB và PC ược chia thành hai nhóm A và B ể

iều khiển. Các cổng PA và PB có ệm cài cả ngõ vào và ngõ ra, còn cổng PC ệm cài ngõ

ra, ngõ vào chỉ có ệm. Các cổng có các chế ộ hoạt ộng khác nhau phụ thuộc vào sự iều

khiển của các bộ iều khiển nhóm A và B. Bộ ệm Bus dữ liệu tương thích mức logic giữa

CPU và thiết bị, ồng thời óng vai trò kiểm soát việc truyền dữ liệu giữa các cổng vào ra

và CPU. Khối logic iều khiển ọc ghi cung cấp tín hiệu chọn cổng và chọn chiều truyền

dữ liệu tương ứng theo trạng thái của các tín hiệu iều khiển ngõ vào như mô tả trong bảng 5.1:

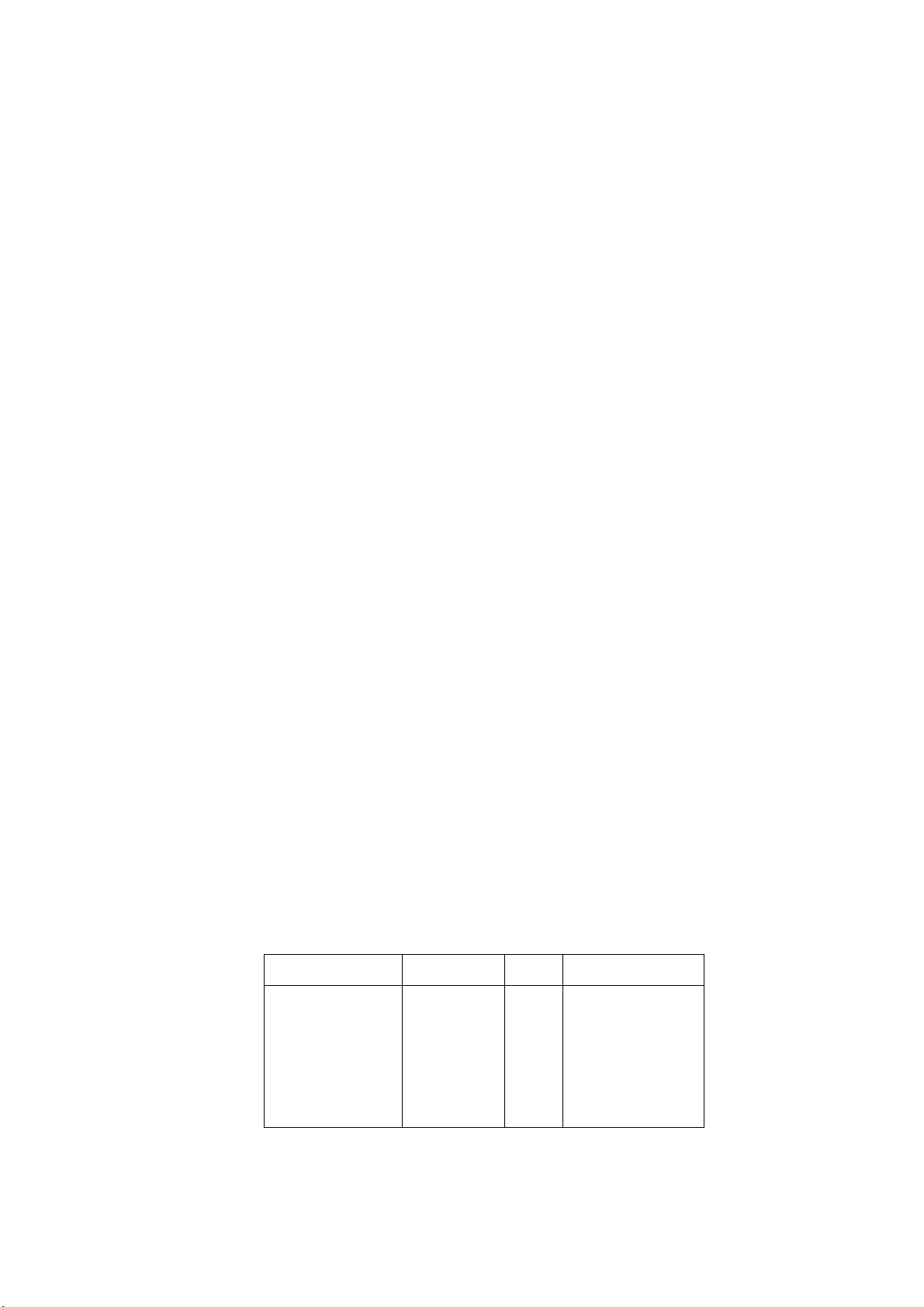

Bảng 5.1: Tín hiệu iều khiển các chế ộ hoạt ộng của 8255 CS A0 A1 RD WR Chế ộ hoạt ộng 1 X X X X Không chọn mạch 0 0 0 0 1 Đọc PA 0 0 0 1 0 Ghi PA 0 0 1 0 1 Đọc PB 0 0 1 1 0 Ghi PB 0 1 0 0 1 Đọc PC 0 1 0 1 0 Ghi PC 0 1 1 1 0 Ghi từ iều khiển 0 1 1 0 1 Cấm

Các cổng của 8255 chỉ có thể truy cập ược khi nó ã ược lập trình trước, việc lập trình

cho 8255 ược thực hiện bằng cách ghi từ iều khiển tới ịa chỉ cổng iều khiển của nó. 8255

có hai dạng từ iều khiển là từ iều khiển lập xoá bit cổng C và từ iều khiển chế ộ, hai loại

từ iều khiển này ược xác ịnh bằng trạng thái bit D7 của chúng. C2 0 x x x C1 C0 S/R

Hình 5.8: Từ iều khiển lập xoá bit cổng C của 8255.

Từ iều khiển lập xoá bit cổng C biểu diễn trên hình 5.8, bit D7 cho từ iều khiển này

luôn bằng 0, các bit D6 D5 D4 có thể mang giá trị bất kỳ, các bit D3 D2 D1 = C2 C1 C0 mã

hoá vị trí bit cổng C ược lập xoá, bit D0 = S/R (Set/Reset) xác ịnh việc lập hoặc xoá bit.

Ví dụ, muốn lập bit PC2 của cổng C lên 1 có thể ghi dữ liệu 00000101 tới ịa chỉ của cổng iều khiển. 1 MA1 MA0 A CH MB B CL lOMoARcPSD| 10435767

Hình 5.9: Từ iều khiển chọn chế ộ của 8255.

Từ iều khiển chọn chế ộ cho 8255 biểu diễn trên hình 5.9: bit D7 của nó luôn bằng 1,

D6 D5 = MA1 MA0 chọn chế ộ cho nhóm A bao gồm PA và phần cao PC (00: chế ộ 0; 01:

chế ộ 1; 1x: chế ộ 2), D4 = A sử dụng chọn chiều truyền dữ liệu cho

PA (1: vào; 0: ra), D3 = CH chọn chiều truyền dữ liệu cho PC phần cao, D2 = MB chọn

chế ộ cho nhóm B gồm cổng PB và PC phần thấp (0: chế ộ 0; 1: chế ộ 1), D1 = B chọn

chiều truyền cho PB và D0 = CL chọn chiều truyền cho PC phần thấp.

Các cổng của 8255 có 3 chế ộ làm việc:

- Chế ộ 0: vào ra dữ liệu cơ bản, các cổng giống như các bộ ệm cài thông thường ược

chọn theo trạng thái của các ngõ vào ịa chỉ A0 và A1. Tùy theo việc lập trình từ iều

khiển, các cổng này hoặc chỉ vào, hoặc chỉ ra.

- Chế ộ 1: là chế ộ truyền dữ liệu một chiều có bắt tay, chế ộ này chỉ sử dụng cho các

cổng PA và PB cổng PC sử dụng cho các tín hiệu bắt tay.

- Chế ộ 2: là chế ộ truyền dữ liệu hai chiều có bắt tay, chế ộ này chỉ sử dụng cho PA,

PC óng vai trò là tín hiệu bắt tay, PB lúc này có thể hoạt ộng trong chế ộ 0 hoặc 1.

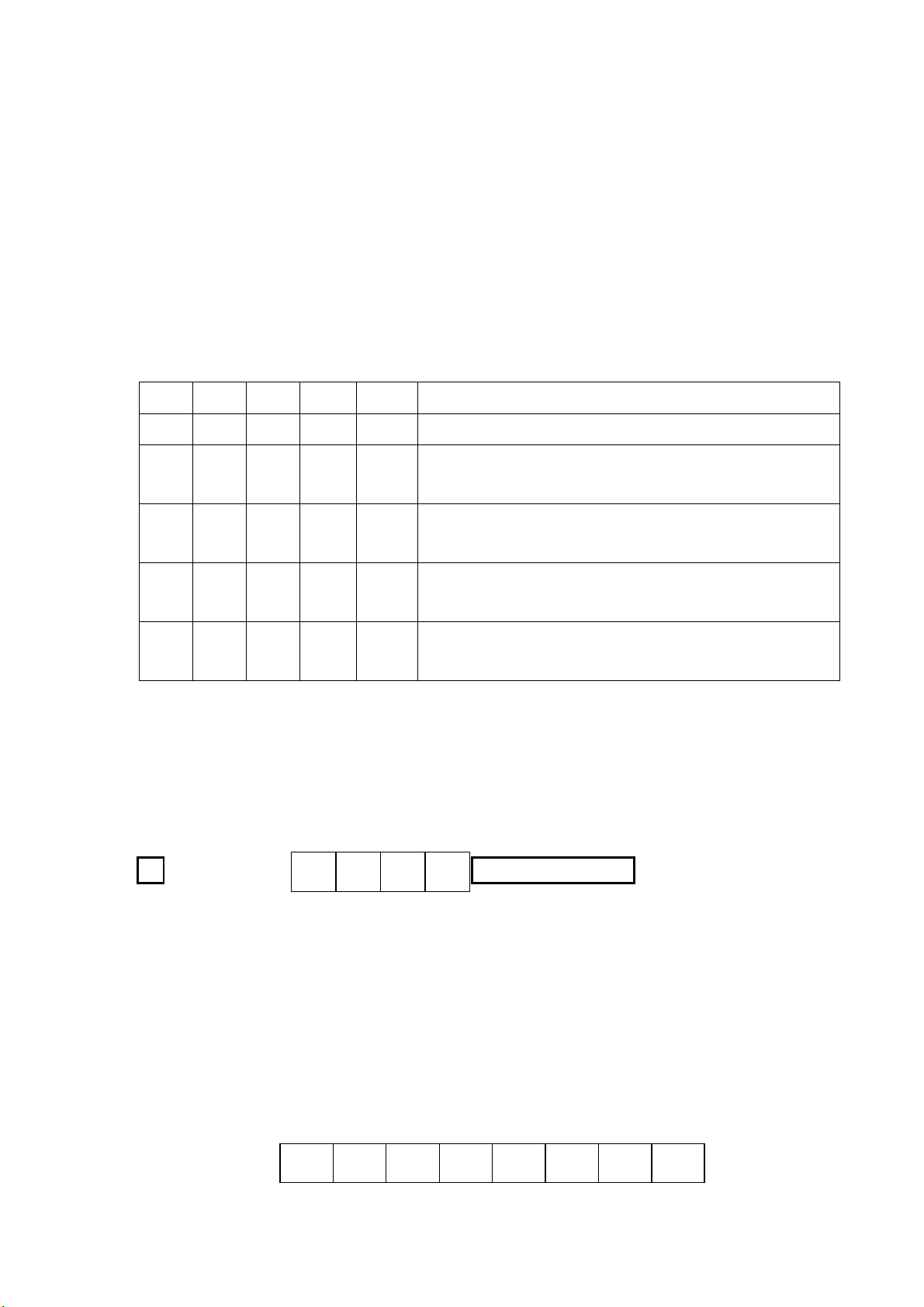

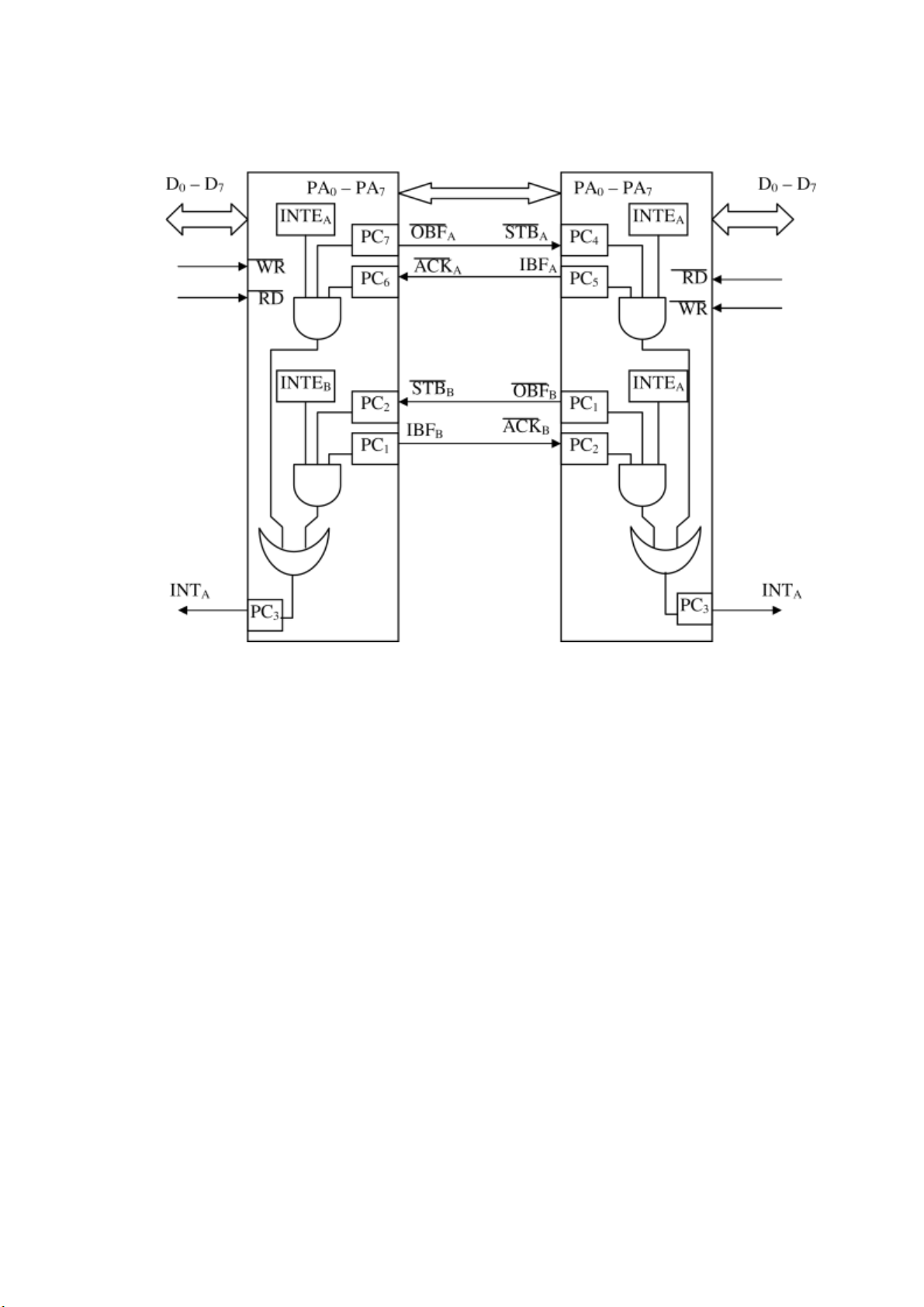

Hình 5.10 mô tả việc truyền dữ liệu giữa hai bộ vào ra 8255 ở chế ộ 1, trong ó 8255

bên trái có cổng A truyền, cổng B nhận, ngược lại 8255 bên phải có cổng A nhận, cổng B truyền dữ liệu. lOMoARcPSD| 10435767

Hình 5.10: Truyền dữ liệu bằng 8255 ở chế ộ 1.

Các tín hiệu của cổng truyền bao gồm:

- OBF (Output Buffer Full): là tín hiện ngõ ra tác ộng mức thấp khi bộ ệm ngõ ra ầy.

Tức là tín hiệu này sẽ tích cực khi CPU ghi tới cổng truyền 1 byte dữ liệu mà bên

nhận chưa nhận lấy nó. Tín hiệu này sẽ ược nối tới STB của cổng nhận, ể chốt dữ liệu vào cổng nhận.

- ACK (acknowledge): là tín hiệu ngõ vào tác ộng mức thấp sử dụng cho việc nhận

tín hiệu trả lời từ cổng nhận, thông báo ể cổng truyền biết cổng nhận ã nhận xong dữ

liệu, lúc này cổng truyền có thể truyền tiếp một dữ liệu khác.

- INTR (interrupt): là tín hiệu ra tác ộng mức cao thông báo một byte CPU ghi tới

cổng truyền ã ược truyền xong tới thiết bị. Tín hiệu này có thể sử dụng yêu cầu ngắt

CPU ể thực hiện việc ghi tới một dữ liệu khác.

- INTE (Interrupt Enable): là cờ cho phép ngắt truyền bên trong 8255, nó có thể lập

xoá bằng bit PC5 cho cổng A và PC6 cho cổng B (khi truyền). Khi INTE bị xoá, yêu

cầu sẽ không ược gửi tới CPU khi 8255 truyền xong một dữ liệu. Định thời các tín

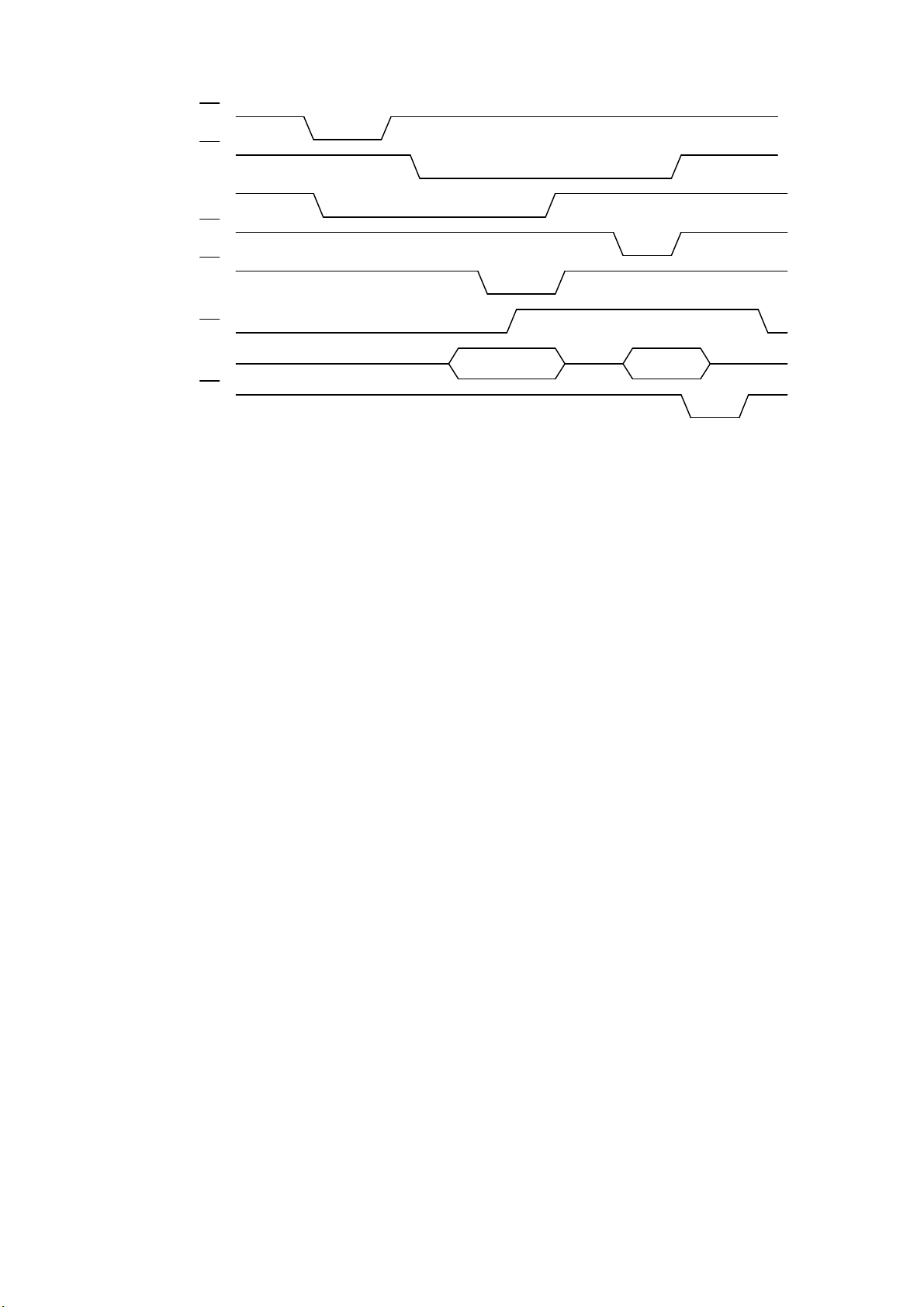

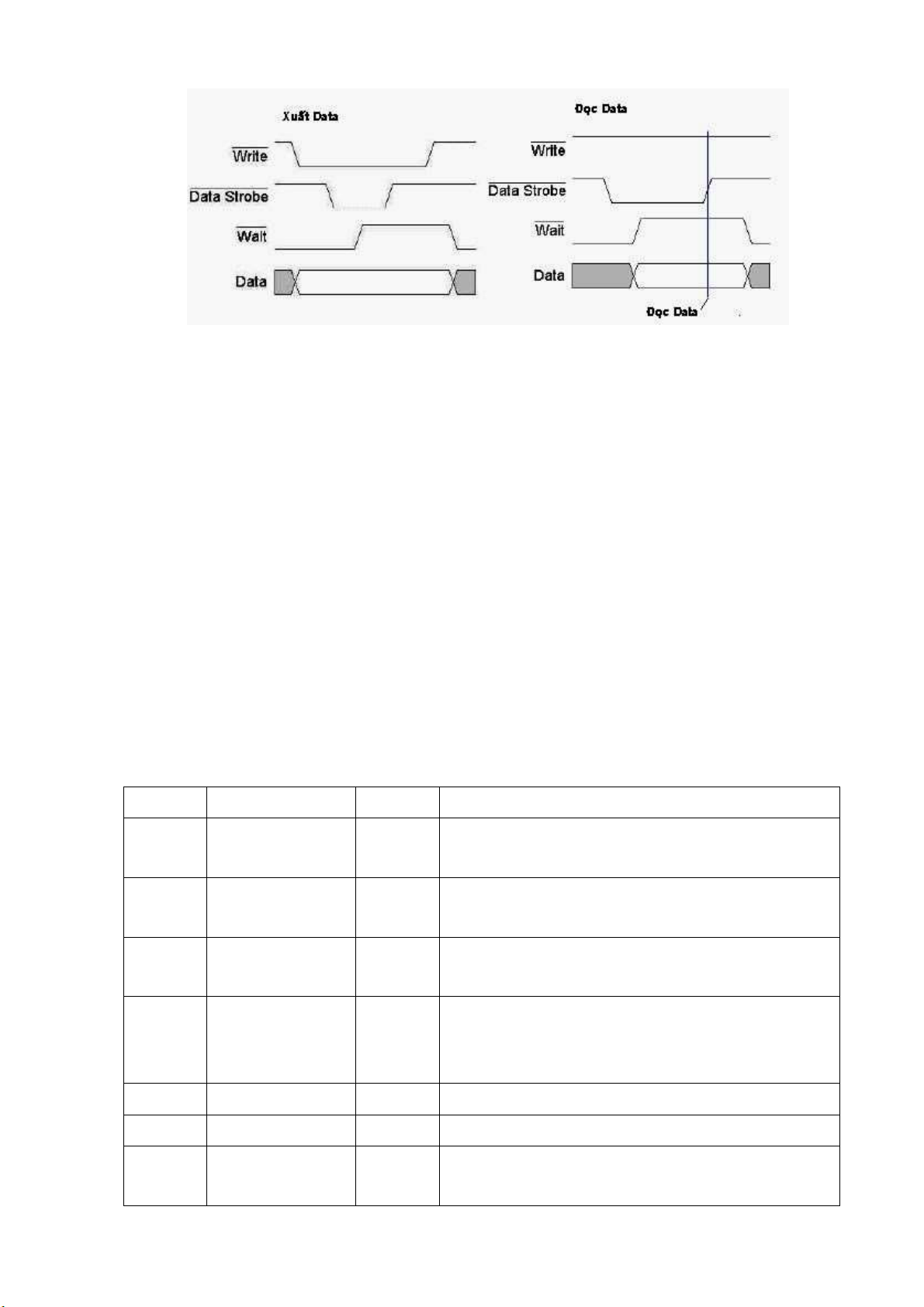

hiệu iều khiển cho cổng truyền biểu diễn trên hình 5.11 lOMoARcPSD| 10435767 WR OBF INTR ACK Data Out

Hình 5.11: Định thời hoạt ộng các tín hiệu iều khiển cho PA chế ộ 1

Các tín hiệu bắt tay cho cổng nhận dữ liệu trong chế ộ 1 bao gồm:

- STB (Strobe): là ngõ vào, khi ngõ vào này tác ộng dữ liệu trên các ường nối tới cổng

vào sẽ ược chốt vào bộ ệm ngõ vào ó. Trên hình 5.17, tín hiệu này ược cấp từ OBF của cổng truyền.

- IBF (Input Buffer Full): là tín hiệu ngõ ra tác ộng mức cao thông báo dữ liệu ã ược

chốt vào bộ ệm nhận, tín hiệu này chỉ ược xoá khi CPU ọc dữ liệu.

- INTR (Interrupt Request): là tín hiệu yêu cầu ngắt, thông báo cho CPU biết ã có một

dữ liệu sẵn sàng ể CPU ọc, tín hiệu này chỉ ược xoá khi CPU thực hiện một chu kỳ

ọc kéo tín hiệu RD của nó xuống mức thấp.

- INTE (Interrupt Enable):cờ cho phép ngắt trong 8255 ược lập xoá thông qua việc lập xoá bit PC4. Data IN INTR STB RD IBF

Hình 5.12: Định thời hoạt ộng các tín hiệu bắt tay ngõ vào chế ộ 1. lOMoARcPSD| 10435767

Định thời hoạt ộng của các tín hiệu bắt tay cho cổng nhận dữ liệu biểu diễn trên hình 5.12.

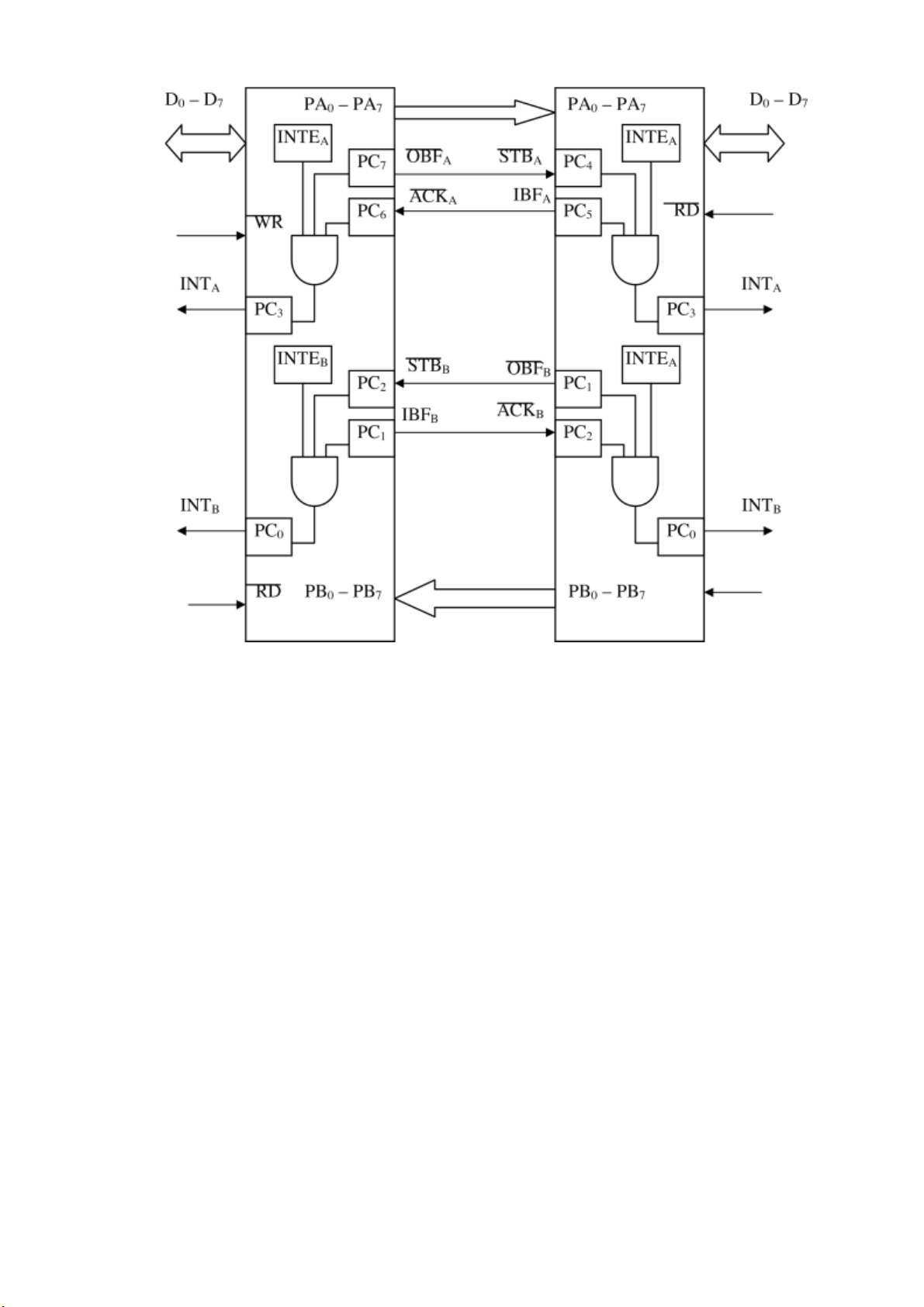

Hình 5.13: Truyền dữ liệu bằng 8255 ở chế ộ 2.

Có thể mô tả giao tiếp truyền nhận trong chế ộ 1 như sau: trước hết khi cổng truyền

còn trống, 8255 truyền sẽ yêu cầu CPU bên truyền ghi một byte tới cho nó bằng tín hiệu

yêu cầu ngắt. Khi CPU ghi dữ liệu (tín hiệu WR tác ộng mức thấp), ngõ ra OBF của

cổng truyền ược kéo xuống mức thấp ưa tới ngõ vào STB ể cài dữ liệu vào cổng nhận.

Khi nhận ược dữ liệu, cổng nhận thông báo trở lại cho cổng truyền bằng tín hiệu IBF

mức cao ưa tới ngõ vào ACK, và ồng thời yêu cầu CPU iều khiển nhận ọc dữ liệu bằng

tín hiệu INTR mức cao. Khi CPU chưa ọc, bộ nhận vẫn duy trì IBF = ACK = 1, do ó

OBF của bộ truyền vẫn tác ộng. CPU ọc dữ liệu kéo RD của 8255 xuống mức thấp xóa

tín hiệu yêu cầu ngắt, ồng thời IBF trở về mức 0 bên truyền sẽ dừng tác ộng tín hiệu

OBF và yêu cầu ngắt ể CPU ghi tới một dữ liệu mới. lOMoARcPSD| 10435767 WR OBF INTR ACK STB IBF Data RD

Hình 5.14: Định thời tín hiệu bắt tay trong chế ộ 2.

Hình 5.13 mô tả nguyên tắc kết nối truyền dữ liệu của hai bộ vào ra 8255 ở chế ộ 2

bằng cổng A. Các tín hiệu bắt tay cho chế ộ này có ý nghĩa tương tự như trong chế ộ 1,

riêng tín hiệu yêu cầu ngắt INTR sử dụng chung cả hai chiều truyền và nhận. Do ó khi

có tín hiệu INTR, hệ thống phải xác ịnh nguồn yêu cầu ngắt từ các tín hiệu tương ứng ở

cổng C. Các Định thời hoạt ộng của các tín hiệu bắt tay trong chế ộ 2 biểu diễn trên hình 5.14.

5.1.3 Cổng vào ra song song LPT (Centronics Port)

Cổng song song LPT tiền thân là cổng do hãng Centronics phát triển vào năm 1970.

Sau này trở thành cổng song song phổ biến trên các máy tính cá nhân trong một thời

gian dài, và ược tiêu chuẩn hoá thành chuẩn IEEE 1284. Cổng vào ra song song là hình

thức truyền thông dụng thường sử dụng giao tiếp: printer, plotter,… Dữ liệu ược truyền

song song, hỗ trợ duplex. Các chuẩn giao tiếp song song (IEEE 1284): có 3 kiểu cổng song song thông dụng:

- SPP - standard parallel port: Là cổng song song chuẩn có tín hiệu truyền một chiều,

tốc ộ tương ối thấp từ 50 – 150 KBps. Khi muoán nhaäp döõ lieäu vaøo maùy tính

coù theå duøng mode Nibble truyeàn 4 bit hay mode Byte truyeàn 8 bit.

- EPP - enhanced parallel port: Là cổng song song tăng cường, chuẩn này truyền dữ

liệu theo hai chiều nên tốc ộ tương ối nhanh hơn SPP.

- ECP - Extended capabilities port: Là cổng song song mở rộng khả năng truyền dữ

liệu theo hai chiều, chiếm một kênh DMA.

Các chế ộ cổng có thể thay ổi trong BIOS SETUP của máy tính khi khởi ộng máy. lOMoARcPSD| 10435767 5.1.3.1 Cổng SPP

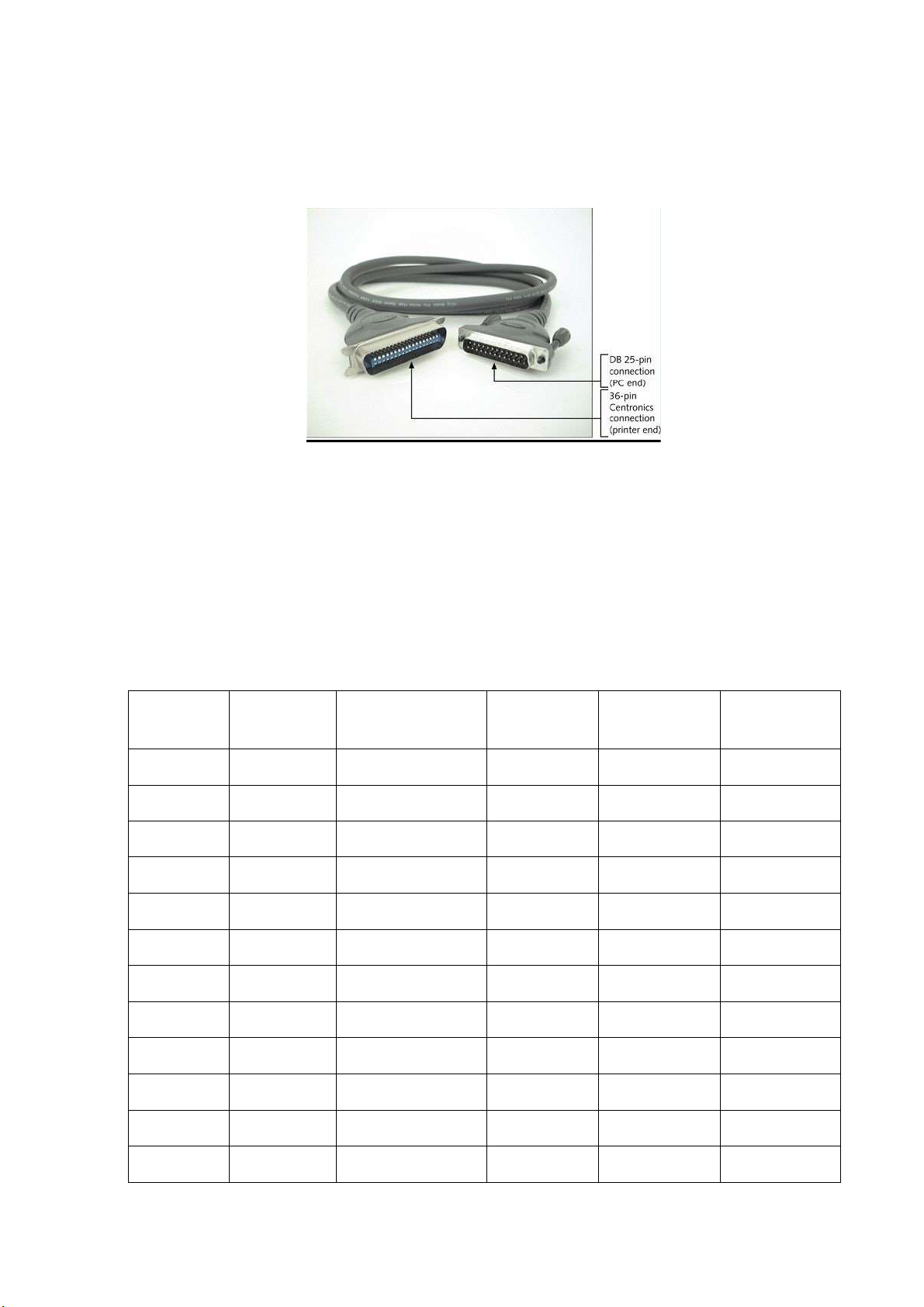

Cổng song song SPP có ầu nối 25 chân cái thường dùng ể kết nối với máy in ầu nối

Centronics 34 chân như trên hình 5.15.

Hình 5.15: Đầu nối Centronics cổng LPT

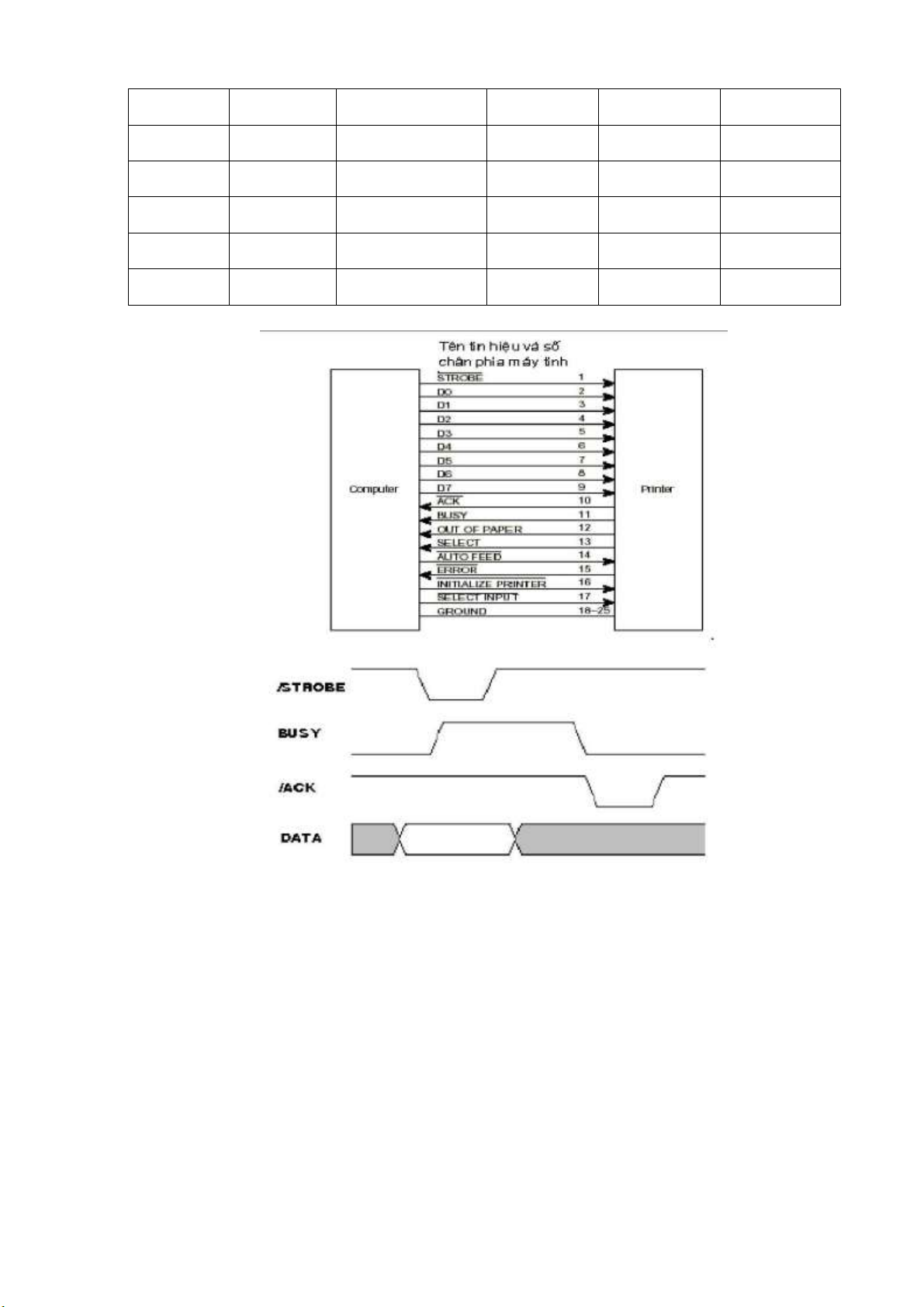

Bảng 5.2 cho sơ ồ chân và ý nghĩa các chân của cổng SPP khi dùng với máy in, dấu

“/” có nghĩa tích cực thấp. Ví dụ, chân 15 là /Error hướng vào, nếu chân này xuống mức

0 là có lỗi. Cột Đảo ghi chữ Có tức là tín hiệu ược ảo mức, ví dụ chân 17 khi ưa mức

logic 0 ứng với chân này vào thanh ghi iều khiển thì ở chân 17 xuất hiện mức 1.

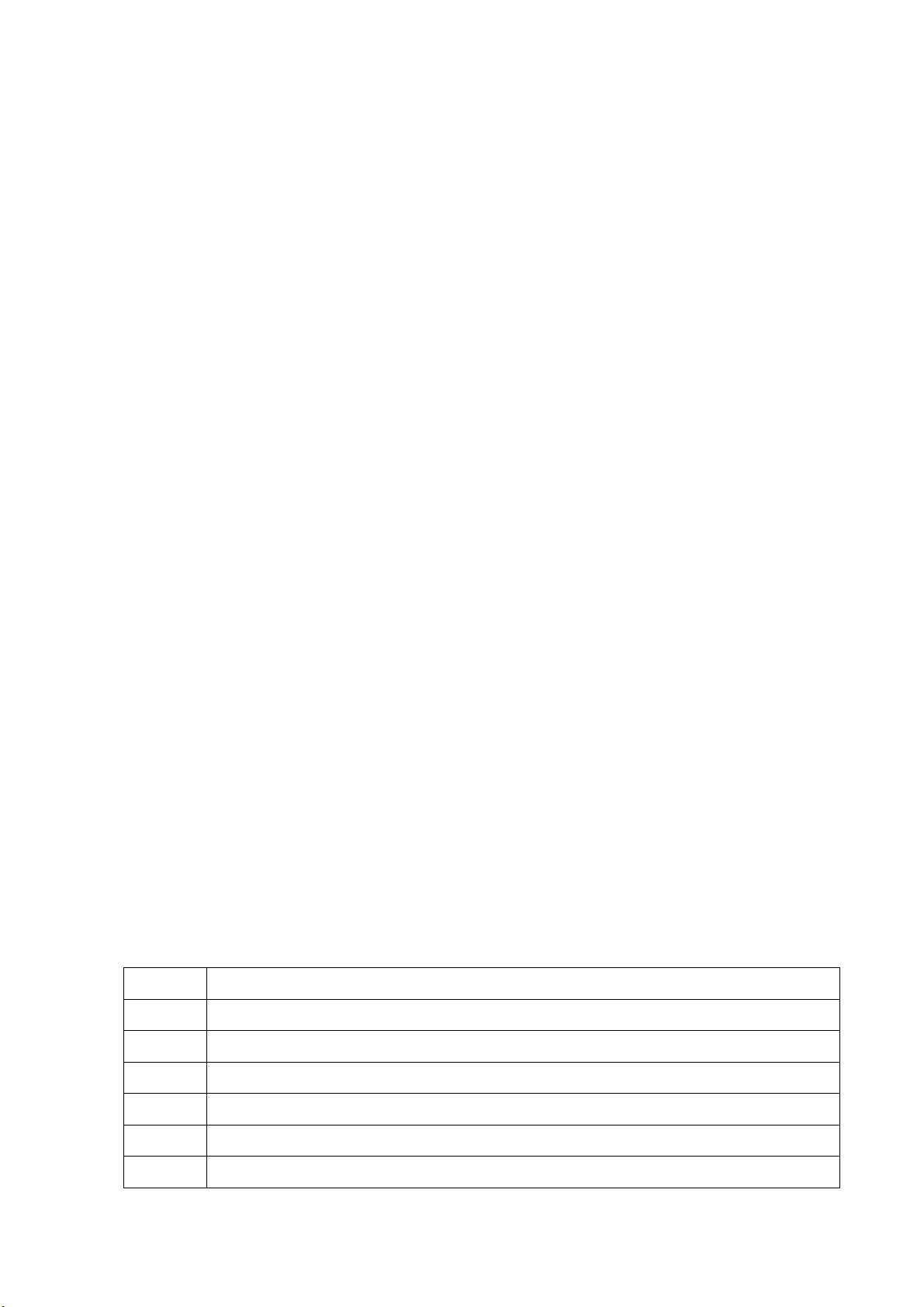

Bảng 5.2: Sơ ồ chân của ầu nối phía máy tính (cổng SPP) và phía máy in Chaân D – Chaân Höôùng Thanh ghi Ñaûo 25 Centronics Tín hieäu SPP 1 1 /Strobe Vaøo/Ra Ñieàu khieån Coù 2 2 Data 0 Ra Data 3 3 Data 1 Ra Data 4 4 Data 2 Ra Data 5 5 Data 3 Ra Data 6 6 Data 4 Ra Data 7 7 Data 5 Ra Data 8 8 Data 6 Ra Data 9 9 Data 7 Ra Data 10 10 /Ack Vaøo Traïng thaùi 11 11 Busy Vaøo Traïng thaùi Coù 12 12 Paper Out Vaøo Traïng thaùi lOMoARcPSD| 10435767 13 13 Select Vaøo Traïng thaùi 14 14 /Auto-Linefeed Vaøo/Ra Ñieàu khieån Coù 15 32 /Error Vaøo Traïng thaùi 16 31 /Init Vaøo/Ra Ñieàu khieån 17 36 /Select Printer Vaøo/Ra Ñieàu khieån Coù 18 - 25 19 - 30 Mass

Hình 5.16: Kết nối máy in và máy tính qua cổng LPT

Ngõ ra cổng song song tương thích với cổng TTL, dòng cấp và thu khoảng vài mA

ến 16mA tùy loại kết cấu phần cứng (công nghệ ASIC). Giao tiếp cổng song song với

máy in thường ược thực hiện theo hình 5.16.

Ban ầu dữ liệu 8 bit ược ưa ra, máy tính ọc chân Busy nếu ở mức thấp thì máy in

rảnh, sẽ ưa ra tín hiệu Strobe rộng 1msec và máy in ọc dữ liệu, máy in ọc xong sẽ báo

trở lại bằng ACK rộng 5msec. Nếu máy in bận thì nó sẽ cấp tín hiệu Busy sẽ ở mức cao.

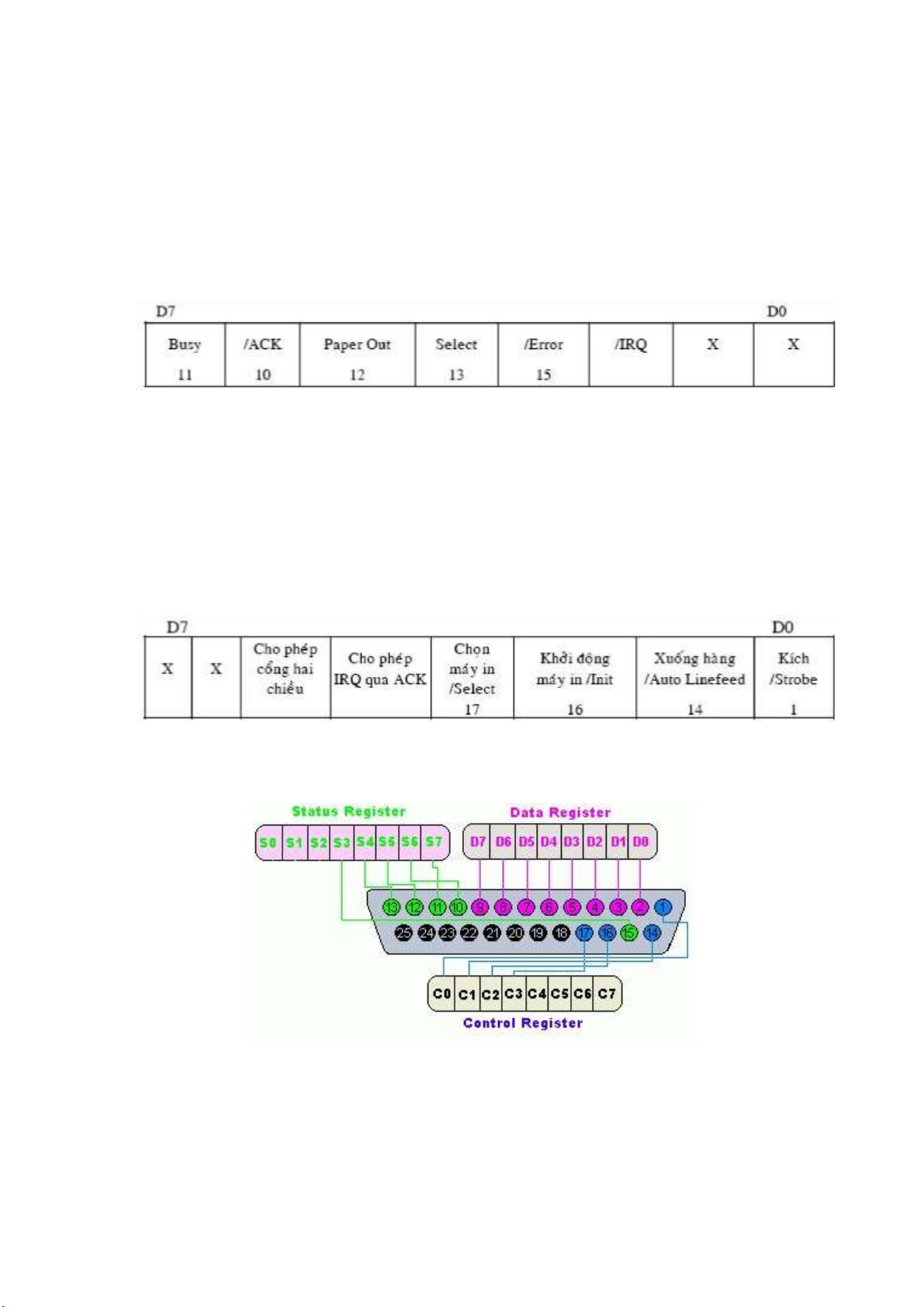

Việc giao tiếp ược thực hiện qua 3 thanh ghi: thanh ghi dữ liệu, thanh ghi iều khiển và

thanh ghi trạng thái. Thông thường sử dụng hai ịa chỉ gốc là: lOMoARcPSD| 10435767

378H cho LPT1 (line printer 1)

278H cho LPT2 Một số máy dùng ịa chỉ 03BC.

Thanh ghi dữ liệu của LPT có ịa chỉ gốc +0, 8 bit, nó sử dụng ể nhận dữ liệu ể xuất ra

ngoài, dữ liệu ược chốt. Thanh ghi trạng thái ịa chỉ gốc +1 là thanh ghi chỉ ọc dùng ể

nhận tín hiệu từ ngoài vào, có 5 tín hiệu vào như trên hình 5.17. Bit Busy sẽ lấy trạng

thái ảo của ngõ vào Busy

Hình 5.17: Thanh ghi trạng thái cổng LPT

Thanh ghi iều khiển có bốn ường ra iều khiển, ịa chỉ gốc +2, các ường này dùng cực

thu hở do ó có thể giao tiếp hai chiều. Các chân 1, 11, 14 và 17 ược ảo phần cứng, bit

D6 thanh ghi trạng thái (chân số 10) từ 1 → 0 thì gây ra ngắt IRQ7 nếu ược cho phép

bởi D4 của thanh ghi iều khiển =1.

Hình 5.18: Thanh ghi iều khiển cổng LPT

Hình 5.19: Kết nối các thanh ghi ến cổng LPT

Hình 5.19 mô tả kết nối giữa các thanh ghi bên trong và các chân cổng bên ngoài trên

SPP. Một số mainboard hỗ trợ giao tiếp hai chiều qua thanh ghi dữ liệu hình 5.20. Khi lOMoARcPSD| 10435767

ó bit D5 của thanh ghi iều khiển bằng 1 thì cho phép các chân 2..:9 của thanh ghi dữ liệu

có chiều i vào, nghĩa là có thể ưa tín hiệu vào các chân này rồi ọc thanh ghi dữ liệu.

Các chân của thanh ghi iều khiển có ngõ ra cực thu hở nên có thể nhận tín hiệu vào

nếu trước ó ta ã nạp 8 bit sao cho các ngõ ra ứng với thanh ghi này lên 1 (hình 5.21). Do

các tín hiệu /Busy, /Select, /AF và /Strobe ã ược ảo phần cứng nên ta thêm các cổng ảo,

logic ọc vào phản ảnh úng mức tín hiệu.

Hình 5.20: Thanh ghi dữ liệu hai chiều tr ên cổng LPT lOMoARcPSD| 10435767

Hình 5.21: Giao tiếp song song hai chiều trên cổng LPT

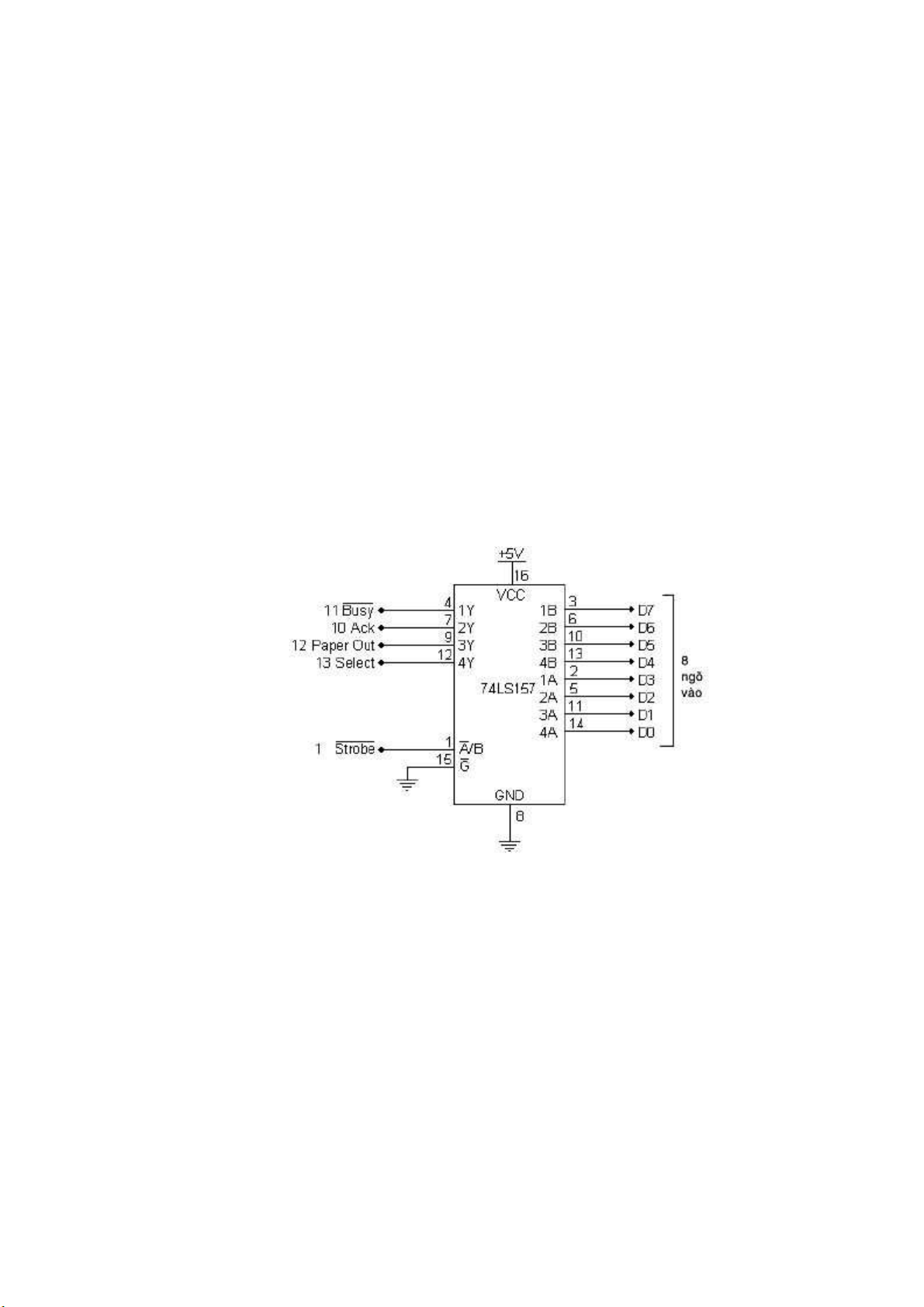

Trong một số trường hợp, các chân ra của thanh ghi iều khiển không dùng loại cực

thu hở mà dùng cột totem chỉ có một chiều xuất, lúc ó có thể dùng bộ phân kênh ể ọc 4

bit dữ liệu vào thanh ghi trạng thái, ọc hai lần sẽ ược 8 bit dữ liệu (hình 5.22). Trên sơ ồ

này, chân /Strobe ược dùng ể chọn nửa byte thấp khi ở mức 0 tức là bit D0 của thanh

ghi iều khiển ở mức 1. Với sơ ồ này, việc xuất nhập dữ liệu 8 bit ược thực hiện như sau:

1- Xác ịnh ịa chỉ gốc của cổng LPT

2- Muốn xuất dữ liệu, ghi dữ liệu 8 bit vào thanh ghi dữ liệu, muốn xuất nhiều hơn

8 bit có thể dùng kèm các tín hiệu Init, Select … bằng cách ghi vào thanh ghi iều khiển byte thích hợp.

3- Muốn ọc dữ liệu, ghi bit D0 = 1 vào thanh ghi iều khiển, ọc 4 bit cao của thanh

ghi trạng thái (4 bit thấp của dữ liệu vào), rồi dời phải 4 bit, sau ó cho D0 của thanh ghi

iều khiển bằng 0, ọc 4 bit cao của thanh ghi trạng thái (4 bit cao của dữ liệu vào), kết

hợp hai lần ọc ta ược 1 byte rồi XOR với 88H ể ảo hai bit D7 và D3 (do Busy ảo).

Hình 5.22: Vào ra 8 bit với 74LS157

5.1.3.2 Cổng epp (enhanced parallel port)

Cổng EPP là sản phẩm liên kết của Intel, Xircom và Zenith, có hai chuẩn là EPP1.7

và EPP1.9, vận tốc truyền từ 500 Kbytes/s ến 2 Mbytes/s nhờ sự hỗ trợ của phần cứng

và kỹ thuật DMA. Khi chuyển cổng song song sang chế ộ EPP (vào mục Setup khi khởi

ộng máy tính ể ặt chế ộ) các chân cổng sẽ mang tên gọi và ý nghĩa khác như trong bảng

5.3, và cổng sẽ có thêm một số thanh ghi chức năng mới như bảng 5.4. lOMoARcPSD| 10435767

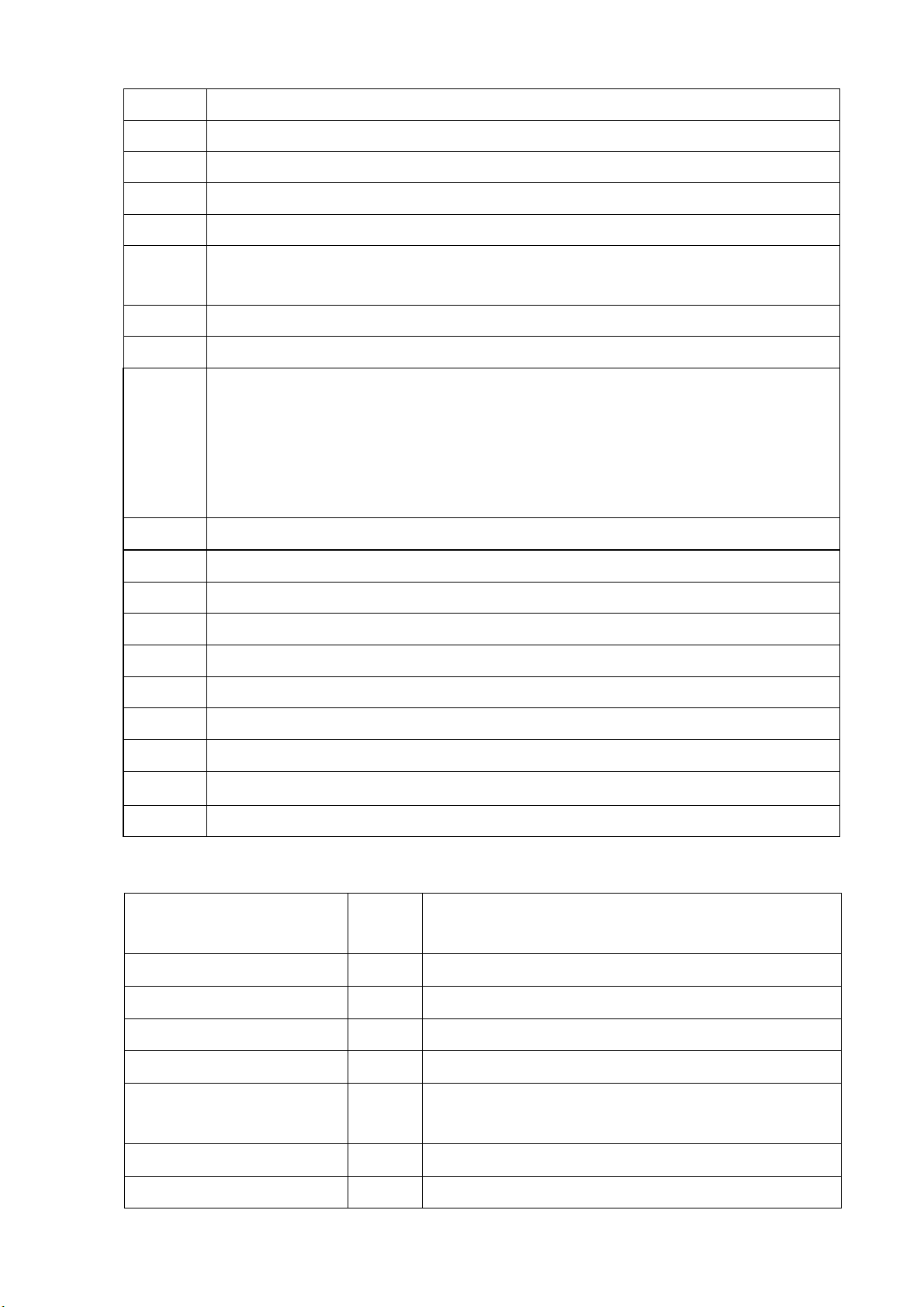

Bảng 5.3: Các tín hiệu trên cổng EPP Chân Tên

Vào/Ra Chức năng 1 Ghi /Write Ra

Khi thấp xuất dữ liệu ra Khi cao ọc vào 2 - 9 Data 0 - 7

Vào - Ra Tuyến dữ liệu hai hướng 10 Ngắt Interrupt Vào Ngắt ở cạnh lên 11 Chờ /Wait Vào

Dùng ể bắt tay, chu kỳ EPP bắt

ầu khi thấp, chấm dứt khi cao 12, 13, 15 Không dùng 14 /Data Strobe Ra

Khi ở mức thấp truyền dữ liệu 16 /Reset Ra Reset, tích cực thấp 17 /Address Strobe Ra

Khi ở mức thấp truyền ịa chỉ 18 – 25 Mass

Bảng 5.4: Các thanh ghi cổng EPP Địa chỉ Tên Đọc / Ghi

Gốc + 0 Thanh ghi dữ liệu (SPP) Ghi

Gốc + 1 Thanh ghi trạng thái (SPP) Đọc

Gốc + 2 Thanh ghi iều khiển (SPP) Ghi

Gốc + 3 Thanh ghi ịa chỉ (EPP) Đọc / Ghi

Gốc + 4 Thanh ghi dữ liệu (EPP) Đọc / Ghi Gốc + 5

Gốc + 6 Dùng ể truyền 16/32 bit Gốc + 7

Ba thanh ghi ầu giống như trong SPP. Muốn truyền dữ liệu theo EPP ta ưa dữ liệu

vào thanh ghi gốc +4 và mạch logic sẽ tạo các tín hiệu cần thiết. lOMoARcPSD| 10435767

Hình 5.23: Giản ồ xuất nhập dữ liệu

Giản ồ ọc ghi dữ liệu trên cổng EPP như trên hình 5.23. Trong chu kỳ ghi dữ liệu,

chân /Write và /Data Strobe tích cực thấp chờ cho ến khi /Wait lên mức cao (báo bên kia

ã nhận dữ liệu), sau ó /Data Strobe và /Write trở lại mức cao kết thúc truyền.

Khi nhận dữ liệu, ầu tiên chương trình ọc thanh ghi gốc +4. Nếu /Wait mức thấp thì

/Data Strobe sẽ ở mức thấp chờ khi /Wait ở mức cao bên kia báo ã gửi dữ liệu tới, /Data

Strobe sẽ ở mức cao và dữ liệu ược ọc vào. Chu kỳ xuất và nhập dữ liệu cũng giống như

chu kỳ xuất và nhập ịa chỉ. Thường kết hợp ịa chỉ và dữ liệu ể truy xuất dữ liệu từ các ịa chỉ ngoại vi khác nhau.

Phần cứng ngoại vi có nhiệm vụ xử lý các chân /Write, /Data Strobe, /Address

Strobe ưa vào các mạch cài hay cho phép và xuất tín hiệu /wait phù hợp. Thông qua tín

hiệu Interrupt (chân số 10) ngoại vi sẽ tác ộng ến máy tính, bit 0 của thanh ghi trạng thái

là bit báo hết thời gian EPP. Nếu trong khoảng 10µs ường /Wait không tác ộng khi /Data

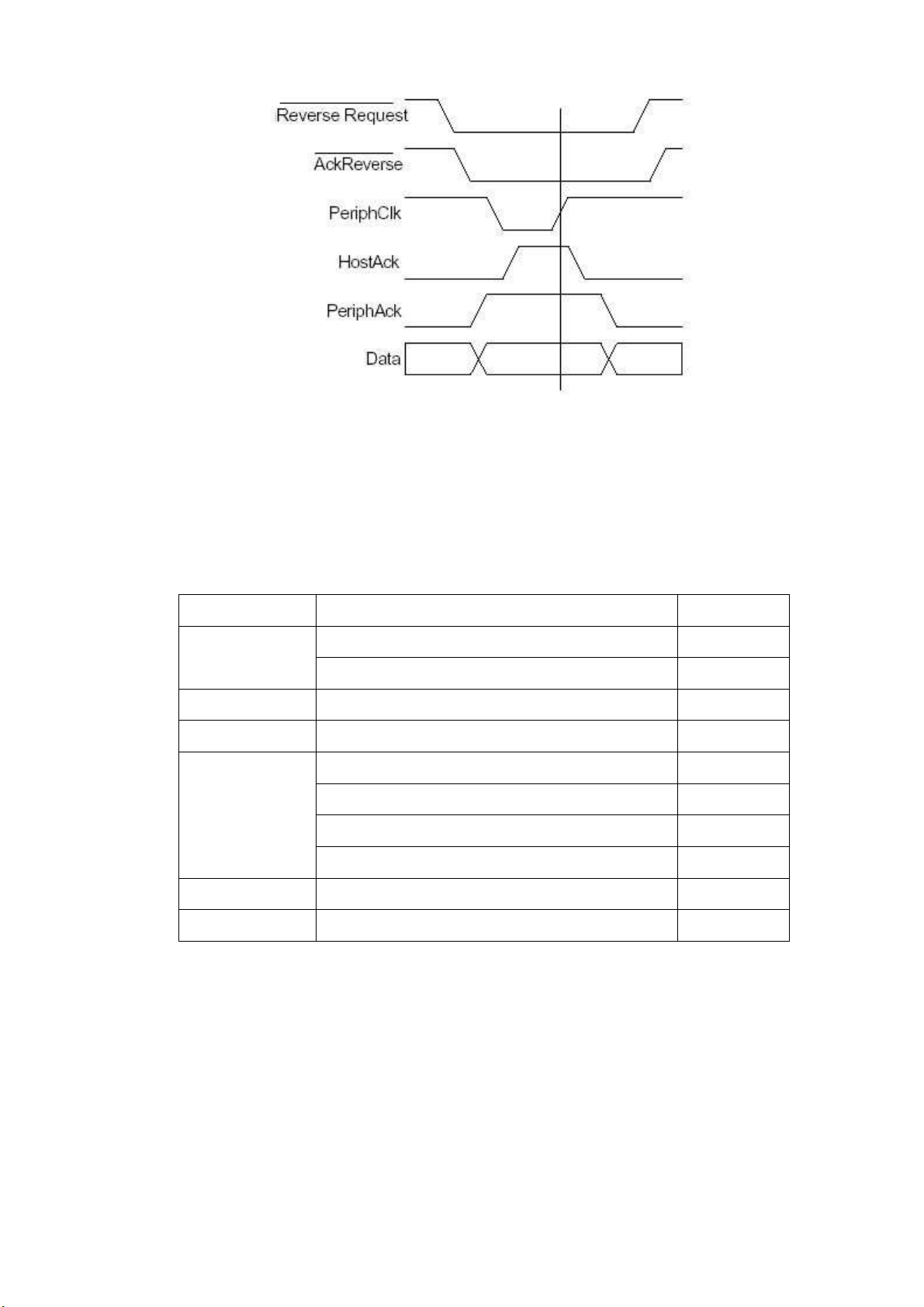

Strobe hay /Address strobe tác ộng thì bit này sẽ ược ặt lên 1. Bảng 5.5: Các tín hiệu trên cổng ECP Chân

Tín hiệu ECP Hướng Chức năng 1 HostClk Ra

Thấp cho biết có dữ liệu, cạnh lên dùng ể cài dữ liệu ra 2 – 9 Data 0 – 7 Hai

Tuyến dữ liệu hai chiều chiều

Thấp cho biết ngoại vi cần ưa dữ liệu vào máy 10 PeriphClk Vào

tính, cạnh lên dùng ể cài dữ liệu vào

Khi ngoại vi nhận dữ liệu thì lên mức cao. Nếu 11 PeriphAck Vào

ngoại vi gởi dữ liệu thì mức cao báo chu kỳ dữ

liệu, mức thấp báo chu kỳ lệnh 12 /AckReverse Vào

Khi thấp ngoại vi chấp nhận truyền dữ liệu 13 X – Flag Vào Cờ mở rộng HostAck Ra

Ở mức cao báo chu kỳ dữ liệu, ở mức thấp báo 14 chu kỳ lệnh lOMoARcPSD| 10435767 15 PeriphRequest Vào

Yêu cầu máy tính nhận số liệu 16 / Ra

Khi ở mức thấp cho biết dữ liệu nhập vào máy ReverseRequest tính 18 – 29 Mass 5.1.3.3 Cổng ECP

Cổng ECP ược phát triển bởi Hewlett Packard và Microsoft, sử dụng phần cứng hỗ

trợ cho việc truyền dữ liệu nên có vận tốc truyền nhanh, tương tự cổng EPP. Đặc iểm

của cổng ECP là nén dữ liệu khi truyền, cho phép tăng tốc ộ truyền dữ liệu.

Cổng ECP dùng 11 thanh ghi từ gốc+0 ến gốc+7 và gốc+400H ến gốc +402H. Chân

cổng ECP ược qui ịnh trong bảng 5.5.

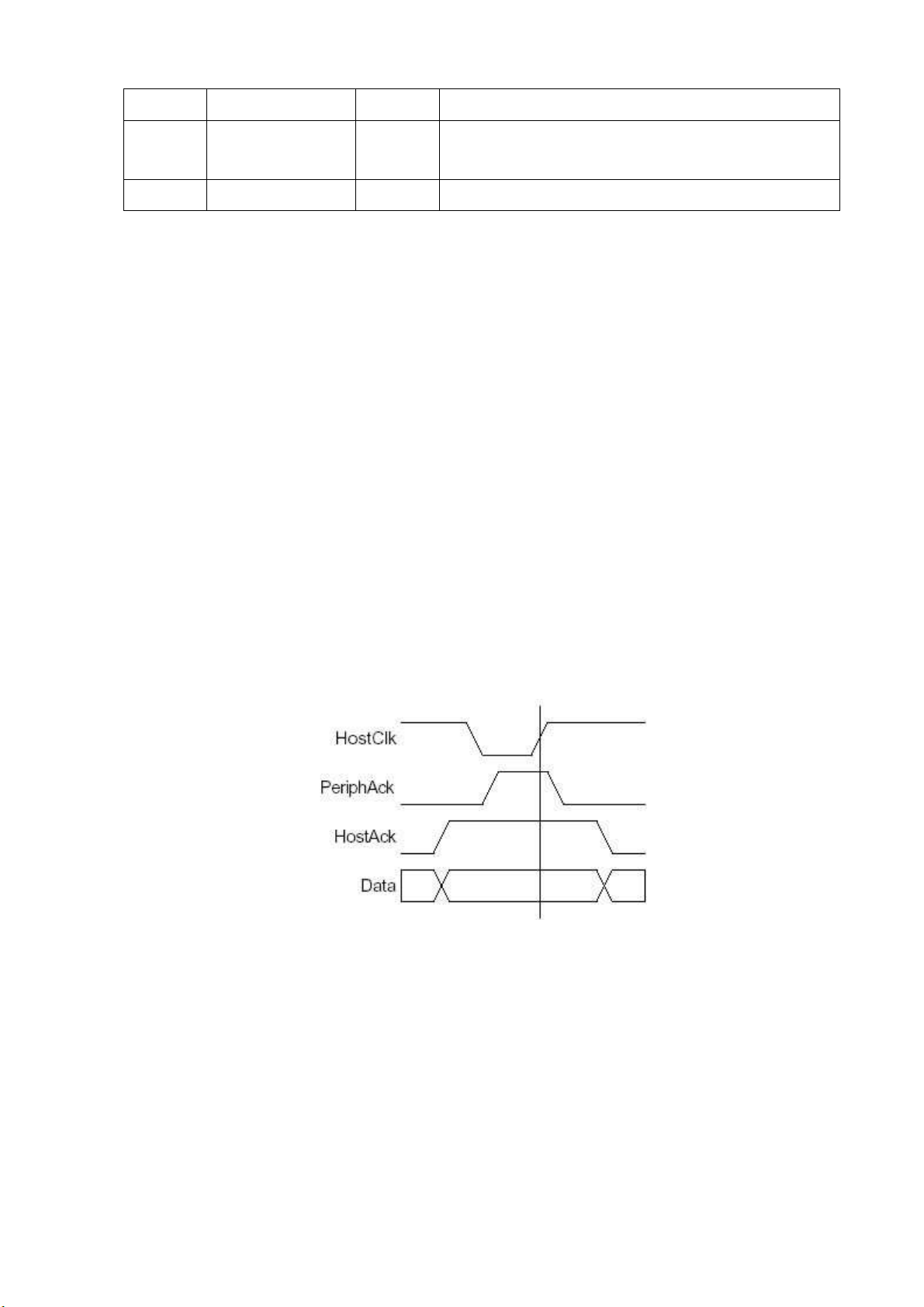

Khi truyền dữ liệu từ máy tính ra ngoại vi thì HostAck sẽ ổi mức, còn truyền dữ liệu

từ ngoại vi vào máy tính thì PeriphAck ổi mức. Trên tuyến dữ liệu có thể truyền dữ liệu

hay lệnh. Nếu Host Ack và Periph Ack ở mức cao là truyền dữ liệu. Nếu máy tính gởi

lệnh, Host Ack mức thấp; nếu ngoại vi gởi lệnh, Periph Ack mức thấp. Lệnh gồm hai

loại, nếu bit 7 của tuyến dữ liệu (chân 9) ở mức thấp thì 7 bit còn lại dùng ể cho biết

thông tin về nén dữ liệu. Nếu bit 7 ở mức cao thì 7 bit còn lại là ịa chỉ kênh. Khi truyền

dữ liệu nén, ầu tiên truyền số lần lặp lại của byte dữ liệu, sau ó truyền byte dữ liệu, ví dụ

truyền 25 byte ký tự ‘A’ thì gởi byte 24 (Run length Count) sau ó gởi byte ‘A’.

Hình 5.24: Giản ồ truyền dữ liệu từ máy tính ra ngoại vi lOMoARcPSD| 10435767

Hình 5.25: Giản ồ truyền dữ liệu từ ngoại vi vào máy tính

Ngoại vi nhận ược byte 24 trong chu kỳ lệnh sẽ lặp lại byte ‘A’ ở chu kỳ dữ liệu 25

lần. Tỷ số nén tối a 64/1. Để tăng tốc ộ truyền dữ liệu, cổng ECP dùng các thanh ghi

sắp xếp kiểu FIFO và một số thanh ghi phụ như mô tả trong bảng 5.6

Bảng 5.6: Các thanh ghi cổng ECP Địa chỉ Tên Đọc / Ghi Thanh ghi dữ liệu (SPP) Ghi Gốc + 0 Địa chỉ FIFO (ECP) Đọc / Ghi Gốc + 1

Thanh ghi trạng thái (mọi mode) Đọc / Ghi Gốc + 2

Thanh ghi iều khiển (mọi mode) Đọc / Ghi

Data FIFO (mode FIFO cổng song song) Đọc / Ghi Gốc + 400 H Data FIFO (ECP) Đọc / Ghi Test FIFO (mode Test) Đọc / Ghi Thanh ghi cấu hình A Đọc / Ghi

Gốc + 401 H Thanh ghi cấu hình B Đọc / Ghi

Gốc + 402 H Thanh ghi iều khiển mở rộng Đọc / Ghi

Thanh ghi iều khiển mở rộng cho phép chọn kiểu hoạt ộng của cổng song song.

Thanh ghi cấu hình A và B sử dụng ể ặt cấu hình của cổng ECP.

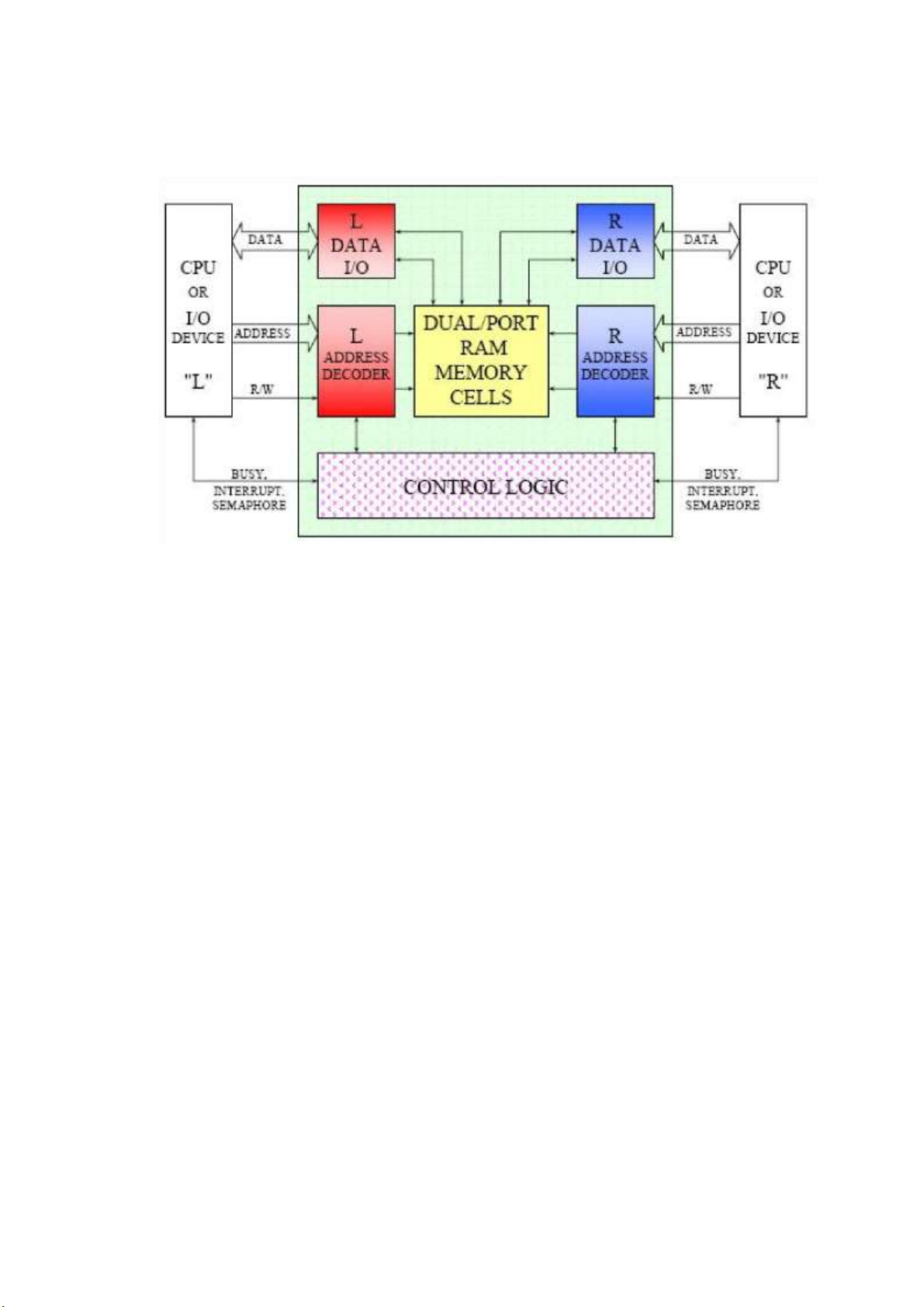

5.1.4 Bộ nhới RAM hai cổng - Dual ported Ram

Bộ nhớ Ram hai cổng ược phát triển cho việc truyền khối dữ liệu giữa hai hệ thống

vi xử lý với tốc ộ cao. Nó ược ứng dụng nhiều trong các hệ thống chuyển mạch, PLC

hay cho các card tăng tốc ồ họa (AGP). Thông thường các bộ nhớ hai cổng sử dụng các lOMoARcPSD| 10435767

khối nhớ SRAM 1 – 64KB nhưng ược thiết kế thêm các mạch phụ cận ể có thể truy cập

ồng thời hai chu kỳ tại cùng một thời iểm. Sơ ồ khối một bộ nhớ RAM hai cổng như trên hình 5.26.

Hình 5.26: Sơ ồ khối bộ nhớ Ram hai cổng

Để truy cập ồng thời bộ nhớ Ram hai cổng sẽ có hai bus ịa chỉ, hai bus dữ liệu, và

hai bus iều khiển ọc ghi trái và phải. Ngoài ra nó còn có thêm khối iều khiển logic ể

tránh các tranh chấp trong quá trình truy cập.

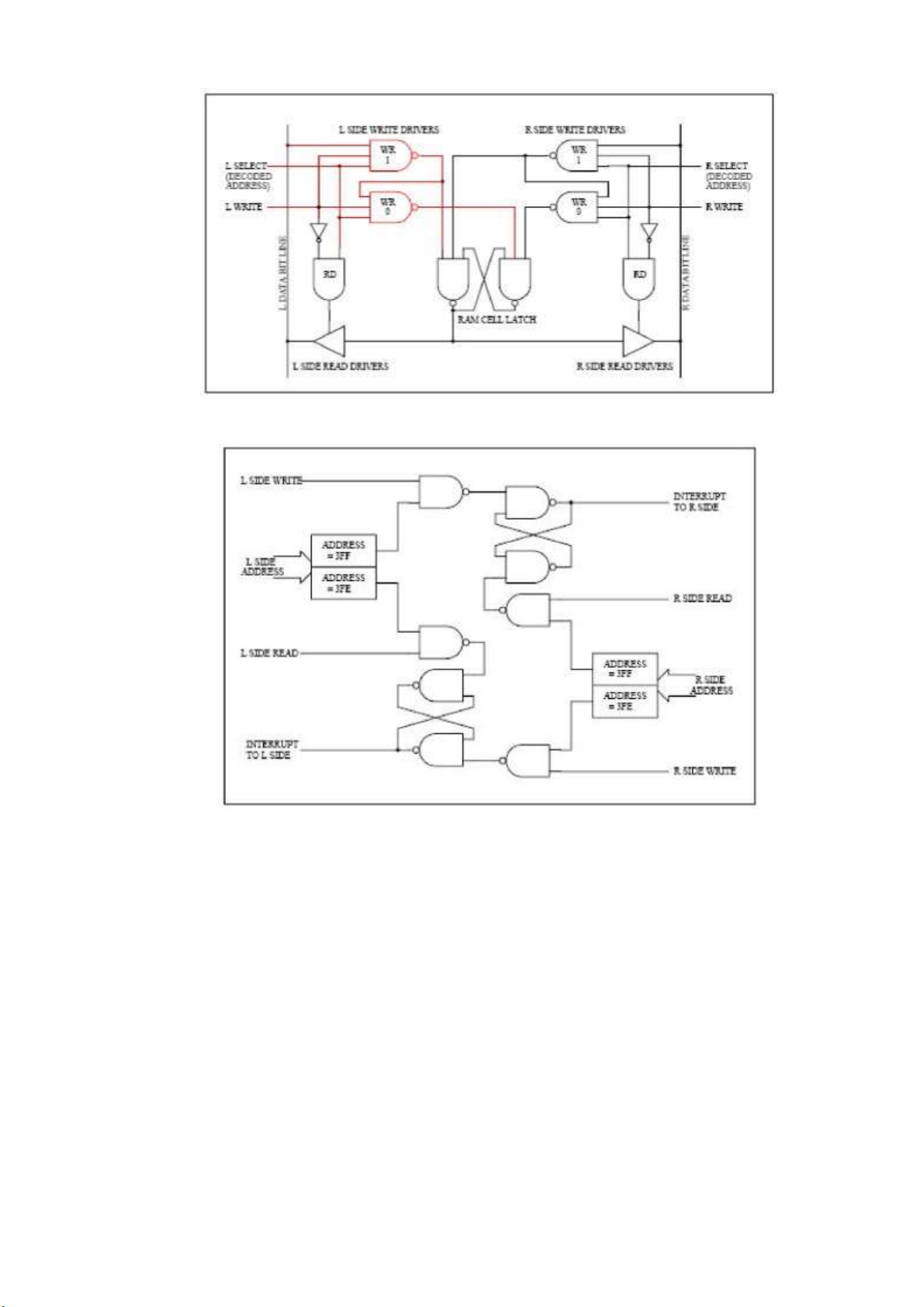

Cấu tạo một bit RAM hai cổng như trên hình 5.27. Trên hình vẽ, khi ặt một dữ liệu

vào DATA BIT LINE bên trái hoặc bên phải, nếu chọn úng ịa chỉ ường SELECT

DECODE ADDRESS sẽ bằng 1, tín hiệu WRITE mức 1, thì ngõ ra cổng NAND WR 1

sẽ bằng 0 làm Flip – Flop chứa bit 1. Ngược lại, khi chọn úng ịa chỉ và WRITE =1,

nhưng dữ liệu ưa vào là 0 thì ngõ ra cổng NAND WR 0 sẽ bằng 1, bit nhớ sẽ chứa giá

trị 0. Cấu trúc mạch hoàn toàn ối xứng nên bit nhớ này có thể ghi ược cả từ hai hướng.

Khi muốn ọc dữ liệu, cần chọn úng ịa chỉ và cấp tín hiệu WRITE bằng 0, dữ liệu có thể

ọc ồng thời ra từ cả hai hướng. lOMoARcPSD| 10435767

Hình 5.27: Cấu tạo một bit nhớ Ram hai cổng

Hình 5.28: Cấu tạo mạch tạo ngắt chống tranh chấp

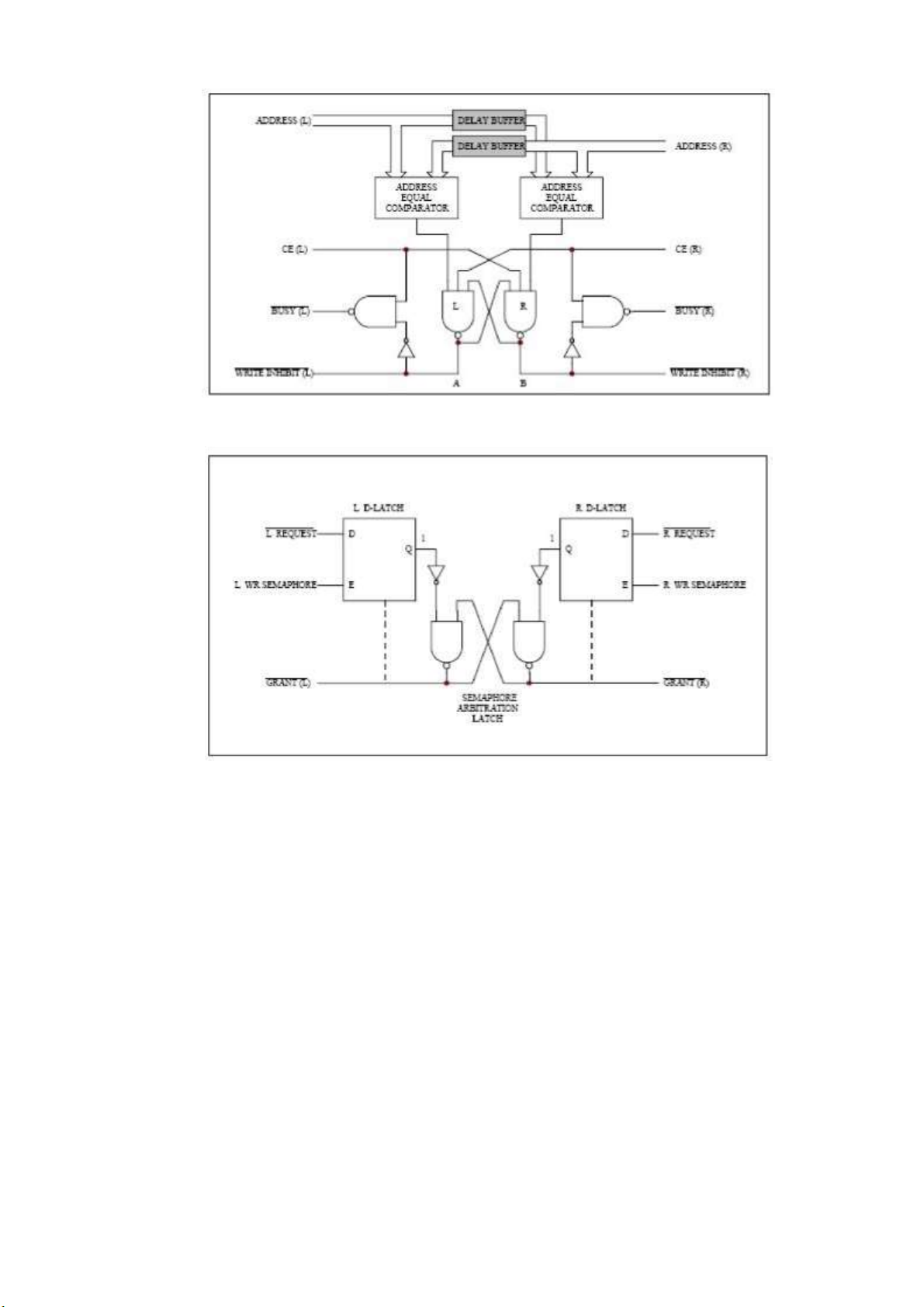

Để tránh tranh chấp cùng một ô nhớ khi ồng thời ọc ghi từ hai cổng các bộ nhớ RAM

hai cổng sử dụng các loại mạch như: ngắt, báo bận (busy) hoặc báo cờ. Hình 5.28 mô tả

cấu trúc mạch ngắt. Trên hình vẽ, khi bên phải ang thực hiện chu kỳ ọc ô nhớ 3FFh, các

tín hiệu R SIDE READ và ngõ ra mạch giải mã ịa R SIDE ADDRESS sẽ ồng thời bằng

1 cấp vào cổng NAND là ngõ ra của nó bằng 0, mức 0 này ược ưa tới mạch Flip – Flop

tạo tín hiệu ngắt ở trên. Lúc này, nếu bên trái không thực hiện chu kỳ ghi dữ liệu, hoặc

ang ghi dữ liệu vào ịa chỉ khác, L SIDE WRITE =0 hoặc ngõ ra mạch giải mã ịa chỉ bên

trái L ADDRESS =0), thì ngõ ra ngắt bên phải sẽ bằng 0, các hoạt ộng ọc ghhi xảy ra

bình thường. Nhưng nếu bên trái ang ghi ngay tại ịa chỉ

3FFh mà bên phải ang ọc, tín hiệu ngắt bên phải sẽ tác ộng bằng 1, hệ thống CPU bên

phải sẽ nhận biết tín hiệu này ể quyết ịnh có ọc tiếp dữ liệu hay ngưng lại. lOMoARcPSD| 10435767

Hình 5.28: Cấu tạo mạch tạo tín hiệu bận chống tranh chấp

Hình 5.29: Cấu tạo mạch tạo cờ chống tranh chấp

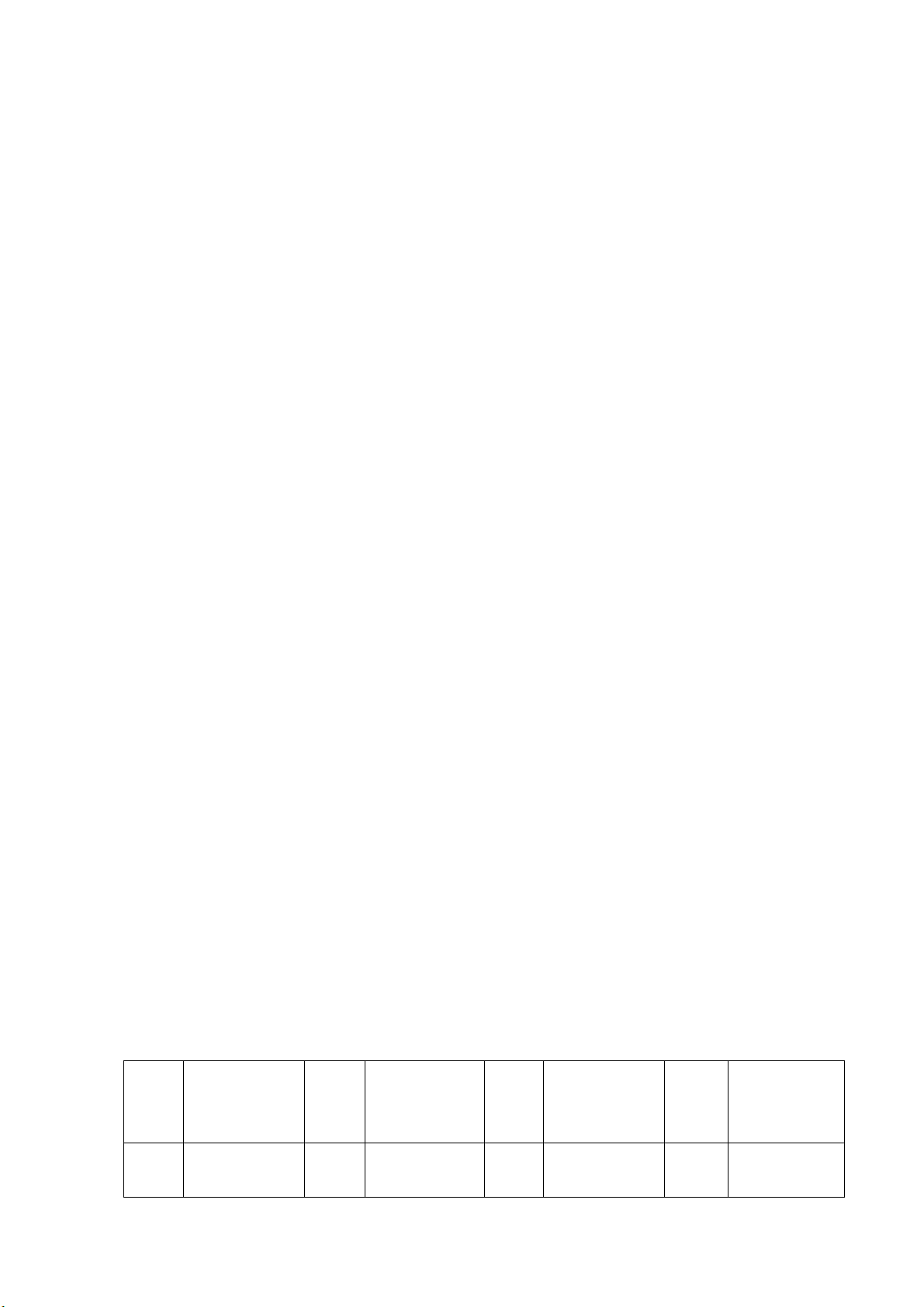

Hình 5.28 là mạch tạo tín hiệu bận và cấm ghi khi xảy ra tranh chấp. Khi hai ịa chỉ

cung cấp từ hai phía truy cập bằng nhau, ngõ ra bộ so sánh tác ộng bằng 1, nếu hai bên

ều cung cấp tín hiệu chọn mạch CE=1 thì một trong hai ường A hoặc B sẽ có mức 0,

một bên sẽ bị cấm ghi. Bên nào có tín hiệu cấm ghi bằng 0 (CE ang bằng 1) thì bên ó sẽ

có tín hiệu báo bận BUSY bằng 0.

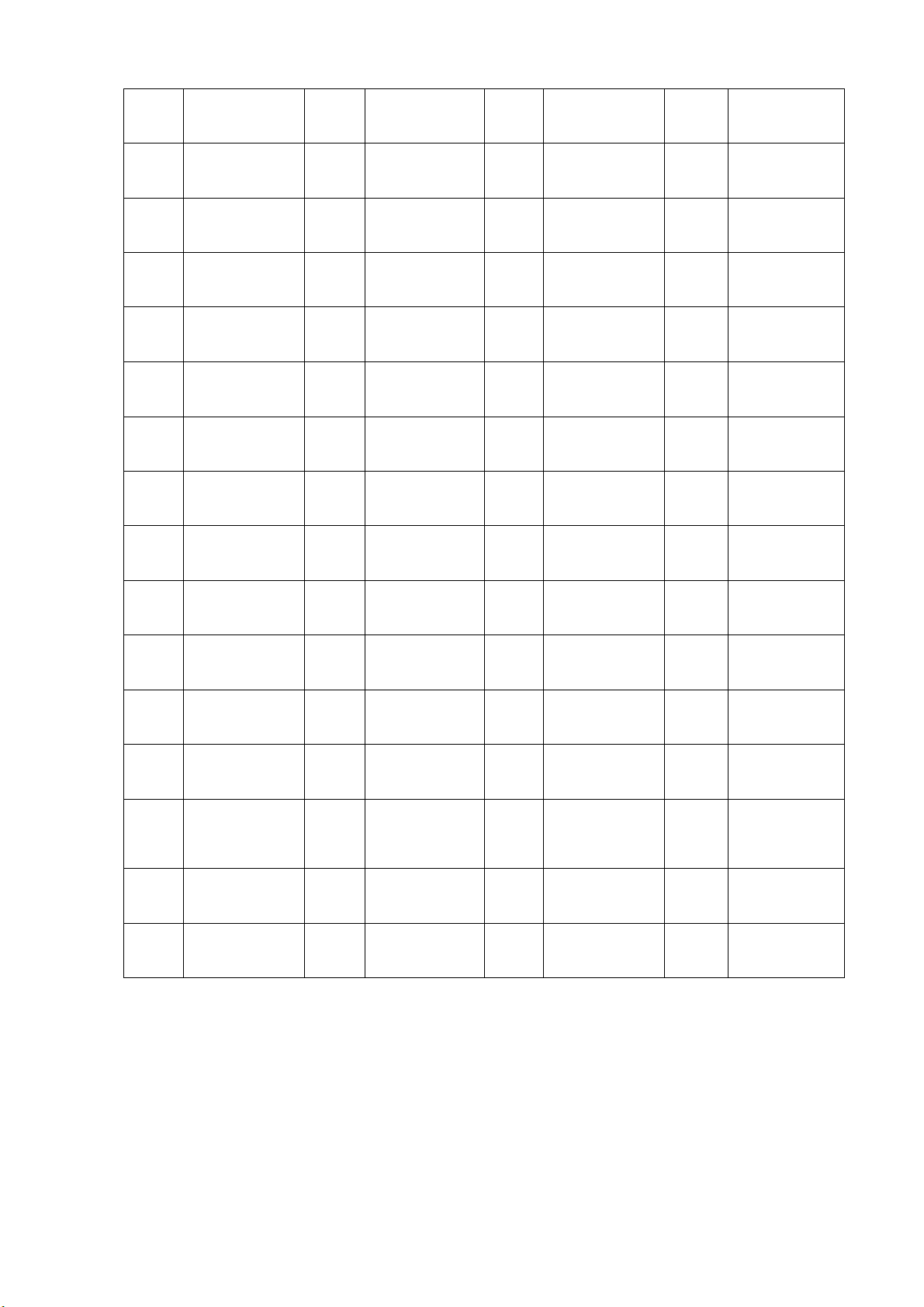

Hình 5.29 mô tả mạch tạo tín hiệu cờ trong Ram hai cổng. Trong mạch khi hai bên cấp

trùng ịa chỉ và cùng yêu cầu truy cập, hai tín hiệu R REQUEST và L REQUEST sẽ ồng

thời bằng 0. Hai cờ báo ghi WR SEMAPHORE cũng ồng thời bằng 1, thì một trong hai

ngõ ra GRANT sẽ tác ộng mức 0, ể hệ thống bên ó tạm ngưng chu kỳ truy cập dữ liệu.

5.1.5 PCMCIA (Personal Computer Memory Card International Association)

PCMCIA là chuẩn giao diện cho phép gằn các card giao tiếp nhỏ vào máy tính laptop,

notebook hoặc palm top. Giao diện này ầu tiên ược thiết kế cho các thẻ nhớ (Version lOMoARcPSD| 10435767

1.0), nhưng sau ó ược phát triển cho rất nhiều bộ tương thích ngoại vi như fax modem,

card âm thanh, card mạng, bộ iều khiển CD-ROM, các card vào ra số …. Hầu hết các

card giao tiếp PCMCIA ều ược thiết kết theo chuẩn loại II (Type II) hoặc loại III (Type

III). Thẻ nhớ Type I có ộ dày 3.3 mm, Type II nâng lên 5 mm, Type III cho phép card

có ộ dày 10.5 mm. Một chuẩn mới Type IV cho phép cắm các card có ộ dày lớn hơn

10.5 mm. Các chuẩn sau luôn cho phép tương thích sử dụng các chuẩn card trước ó, ví

dụ chuẩn Type IV cho phép sử dụng các card Type I, Type II và Type III.

Chuẩn PCMCIA sử dụng bus dữ liệu 16 bit (D0 – D15) và bus ại chỉ 26 bit (A0 –

A25), và như vậy nó cho phép ịnh vị tới dung lượng nhớ 226 word (64 Mword). Dải bộ

nhớ của cổng PCMCIA bao gồm:

- Vùng bộ nhớ chung và bộ nhớ thuộc tính với dung lượng là 128 MB.

- Không gian ịa chỉ vào ra 65,536 (64k) ịa chỉ vào ra truy xuất 8 bit.

Tuỳ theo chế ộ truy xuất cổng PCMCIA sẽ có tốc ộ truy xuất khác nhau:

- Chế ộ cardbus (32 bit burst mode): truy xuất theo byte (byte mode) sẽ có tốc ộ 32

MBps, theo từ (word mode) 66 MBps, và theo từ kép (Dword mode) sẽ là 132 MBps.

- Chế ộ truyền dữ liệu với bộ nhớ 16 bit (chu kỳ nhỏ nhất là 100 nsec): Truyền theo

byte ạt tốc ộ cực ại 10 MBps, theo từ sẽ là 20 MBps.

- Chế ộ truyền dữ liệu với vào ra 16 bit (chu kỳ nhỏ nhất là 255 nsec): truyền theo byte

ạt tốc ộ 3.92 MBps, theo từ ạt tốc ộ 7.85 MBps.

Giao diện PCMCIA cho phép thiết bị giao tiếp sử dụng không gian ịa chỉ bộ nhớ

chính, hoặc không gian ịa chỉ vào ra. Ví dụ, một modem PCMCIA sẽ sử dụng vùng nhớ

cổng COM chuẩn cho các thanh ghi của nó (như các ịa chỉ 3F8H – 3FFh của COM1

hoặc 2F8h – 2FFh của COM2). Bất kỳ việc truy xuất một không gian nhớ nào cũng ược

chuyển hướng tới PCMCIA thay vì tới vùng nhớ chính hoặc vùng vào ra của hệ thống.

Các vùng không gian ịa chỉ này ược gọi là các cửa sổ. MỘt ịa chỉ ược ịnh nghĩa với ịa

chỉ bắt ầu (START) và ịa chỉ cuối (LAST). Các thanh ghi iều khiển của PCMCIA sẽ giữ các ịa chỉ này.

Bảng 5.7 mô tả các chân kết nối và các tín hiệu chính trên PCMCIA, các tín hiệu của nó bao gồm:

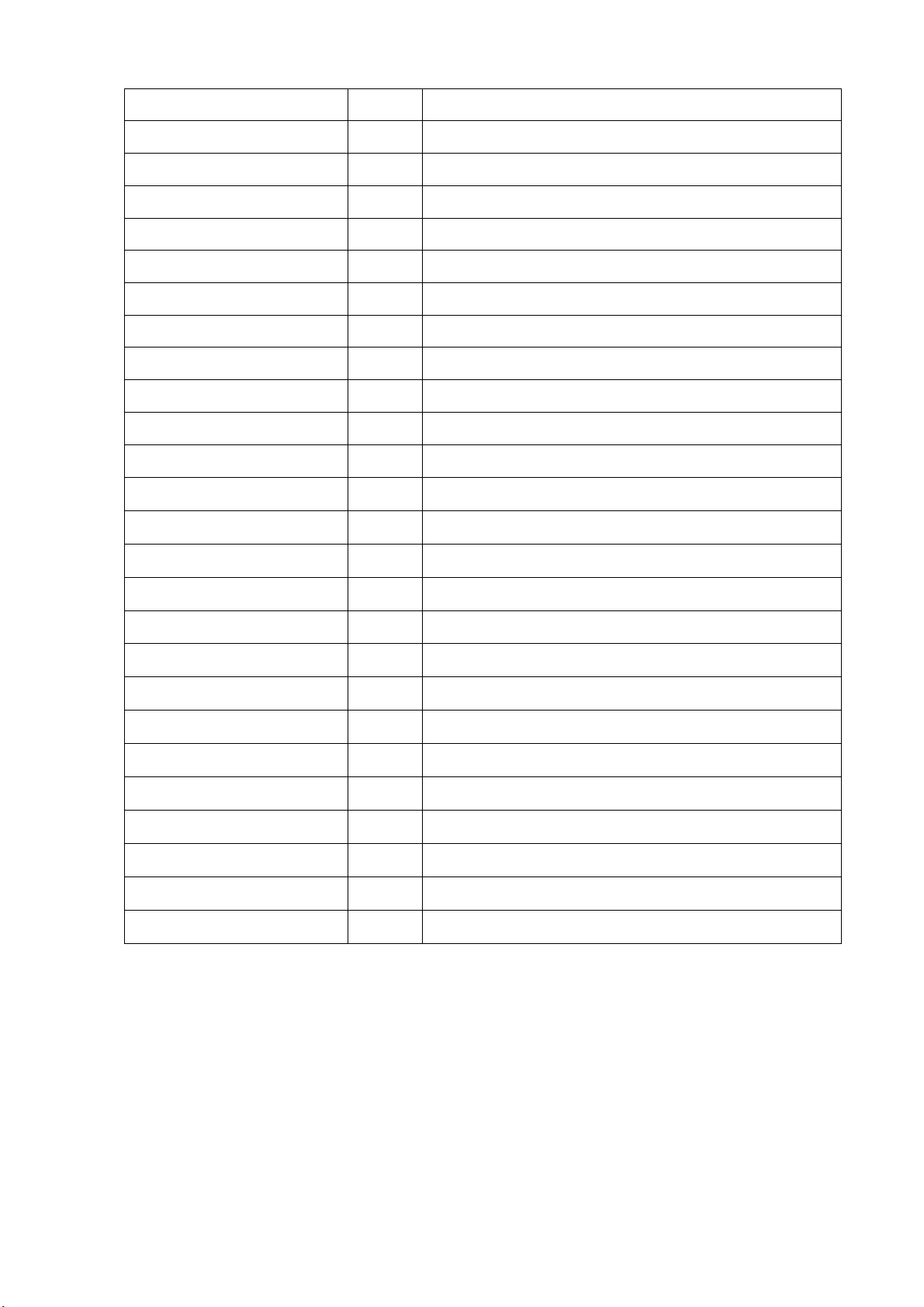

Bảng 5.7: Các tín hiệu chính trên PCMCIA Tín hiệu Tín hiệu Tín hiệu Tín hiệu Chân Chân Chân Chân nối nối nối nối 1 GND 18 Vpp1 35 GND 52 Vpp2 lOMoARcPSD| 10435767 2 D3 19 A16 36 Card Detect 1 53 A22 3 D4 20 A15 37 D11 54 A23 4 D5 21 A12 38 D12 55 A24 5 D6 22 A7 39 D13 56 A25 6 D7 23 A6 40 D14 57 RFU 7 /Card Enable 1 24 A5 41 D15 58 RESET 8 A10 25 A4 42 Card Enable 2 59 /Wait 9 /Output Enable 26 A3 43 Refresh 60 /Inpack 10 A11 27 A2 44 /IOR 61 Reg. Select 11 A9 28 A1 45 /IOW 62 /SPKR 12 A8 29 A0 46 A17 63 /STSCHG 13 A13 30 D0 47 A18 64 D8 14 A14 31 D1 48 A19 65 D9 15 /WR Enable- 32 D2 49 A20 66 D10 Program Ready-/Busy 16 33 /IOIS16 50 A21 67 /Card Detect 2 17 +5V 34 GND 51 +5V 68 GND

- A25-A0: bus ịa chỉ, ịnh vị 226 ại chỉ bộ nhớ hoặc 216 ịa chỉ vào ra.

- D7 – D0: bus dữ liệu 16 bit.

- /CARD DETECT 1, /CARD DETECT 2: Sử dụng cho việc nhận dạng card có ược

cắm vào bus hay không. Khi có card ược cắm vào bus, một trong các tín hiệu này sẽ

ược kéo xuống mức thấp.

- /Card Enable1: sử dụng cho phép 8 bit cao của bus dữ liệu. lOMoARcPSD| 10435767

- /Card Enable 2: sử dụng cho phép 8 bit thấp của bus dữ liệu.

- /Output Enable: ược thiết lập mức thấp từ máy tính ể ọc dữ liệu từ PCMCIA.

- /Register Select: thiết lập mức cao khi truy xuất vùng nhớ chung, và thiết lập mức

thấp khi truy cập vùng nhớ thuộc tính.

- Reset: sử dụng ể reset card PCMCIA.

- Refresh: sử dụng ể làm tươi bộ nhớ trên PCMCIA

- /Wait: ược cấp từ PCMCIA khi nó không thể truyền dữ liệu ủ nhanh theo yêu cầu,

tín hiệu này sẽ tạo ra các chu kỳ chờ trong hệ thống.

- /Write Enable-Program: sử dụng ể lập trình thiết bị PCMCIA.

- Vpp1, Vpp2: cấp iện áp lập trình cho bộ nhớ Flash.

- Ready-/busy: sử dụng ể thông báo trạng thái sẵn sàng hoặc bận của thiết bị PCMCIA

(khi thiết bị sẵn sàng tín hiệu này sẽ ở mức cao).

- /IOIS16: sử dụng ể thông báo trạng thái chống ghi trên PCMCIA card. Mức cao sẽ

chỉ thị công tắc chống ghi ang ược bật.

- /InpAck: sử dụng ể thiết bị PCMCIA chấp nhận chu kỳ truyền dữ liệu.

- /IOR: ược cấp từ hệ thống ể ọc dữ liệu từ card PCMCIA (nó phải ược sử dụng cùng

với tín hiệu tích cực trên Register Select).

- /IOW: ược cấp từ hệ thống ể ghi dữ liệu tới card PCMCIA (nó phải ược sử dụng

cùng với tín hiệu tích cực trên Register Select).

- /SPKR: tín hiệu này ược sử dụng ể card PCMCIA truyền dữ liệu âm thanh tới loa của hệ thống.

- /STGCHG: sử dụng ể nhận dạng sự thay ổi trạng thái của card.

Bộ iều khiển PCMCIA (PCIC) iển hình thường ược sử dụng là vi mạch 82365SL của

Intel. Bảng 5.8 mô tả các thanh ghi chính của ầu nối PCMCIA thứ nhất. Địa chỉ cho các

thanh ghi của ầu cắm thứ 2 sẽ dời ịa chỉ i 40H. Địa chỉ cơ sở của PCIC trong Windows

ược thiết lập giá trị mặc ịnh là 3E0h. PCIC sẽ truy cập vùng ịa chỉ từ 3E0h tới 3E1h.

Cửa sổ vào ra 0/1 sẽ ược truy xuất thông qua:

- 08h/0Ch cho byte thấp của ịa chỉ vào ra ầu tiên.

- 09h/0Dh cho byte cao của ịa chỉ vào ra ầu tiên.

- 0Ah/0Eh cho byte cao của ịa chỉ vào ra cuối cùng.

- 0Bh/0Fh cho byte cao của ịa chỉ vào ra cuối cùng. lOMoARcPSD| 10435767

Các thanh ghi ược truy xuất bằng các nạp giá trị chỉ số thanh ghi vào 3E0h và sau ó

thanh ghi này sẽ ược truy cập qua ịa chỉ 3E1h. Các cửa sổ bộ nhớ 0/1/2/3/4 sẽ

ược truy xuất thông qua:

- 10h/18h/20h/28h/30h cho byte thấp của ịa chỉ bộ nhớ ầu tiên.

- 11h/19h/21h/29h/31h cho byte cao của ịa chỉ bộ nhớ ầu tiên.

- 12h/1Ah/22h/2Ah/32h cho byte thấp của ịa chỉ bộ nhớ cuối cùng.

- 13h/1Bh/23h/2Bh/33h cho byte cao của ịa chỉ bộ nhớ cuối cùng.

- 14h/1Ch/24h/2Ch/34h cho byte thấp của card offset.

- 15h/1Dh/25h/2Dh/35h cho byte cao của card offset.

Ví dụ khi muốn nạp giá trị 22h vào thanh ghi thay ổi trạng thái của card có thể sử dụng các lệnh C sau:

_outp (0x3E0, 4h); /trỏ tới thanh ghi thay ổi trạng thái của card.

_outp (0x3E1, 22h); /nạp giá trị 22h vào thanh ghi thay ổi trạng thái card.

Bảng 5.8: Các thanh ghi của bộ iều khiển PCMCIA Chỉ số Tên thanh ghi Chú giải thanh ghi 00h PCIC Identification Thanh ghi nhận dạng PCIC 01h Interface Status Trạng thái giao tiếp 02h Power Supply (RESETDRV)

Nguồn cung cấp (iều khiển reset) 03h Interrupt Control Điều khiển ngắt 04h Card status change Thay ổi trạng thái card 05h Configuration Cấu hình 06h Memory windows Enable

Cho phép cửa sổ bộ nhớ 07h I/O windows control

Điều khiển cửa sổ vào ra 08h

First setup for IO window 0 (low) Thiết lập ịa chỉ ầu cho cửa sổ IO số 0 byte thấp lOMoARcPSD| 10435767 09h FIRST setup for IO window 0

Thiết lập ịa chỉ ầu cho cửa sổ IO số (high) 0 byte cao 0Ah LAST setup for IO window 0

Thiết lập ịa chỉ cuối cho cửa sổ IO (low) số 0 byte thấp 0Bh LAST setup for IO window 0

Thiết lập ịa chỉ cuối cho cửa sổ IO (low) số 0 byte cao 0Ch FIRST setup for IO window 1

Thiết lập ịa chỉ ầu cho cửa sổ IO số (low) 1 byte thấp 0Dh FIRST setup for IO window 1

Thiết lập ịa chỉ ầu cho cửa sổ IO số (high) 1 byte cao 0Eh LAST setup for IO window 1

Thiết lập ịa chỉ cuối cho cửa sổ IO (low) số 1 byte thấp 0Fh LAST setup for IO window 1

Thiết lập ịa chỉ cuối cho cửa sổ IO (low) số 1 byte cao 10h

FIRST setup for memory window Thiết lập ịa chỉ ầu cho cửa sổ bộ nhớ 0 (low) số 0 byte thấp 11h

FIRST setup for memory window Thiết lập ịa chỉ ầu cho cửa sổ bộ nhớ 0 (low) số 0 byte cao 12h LAST setup for memory window

Thiết lập ịa chỉ cuối cho cửa sổ bộ 0 (low) nhớ số 0 byte thấp 13h LAST setup for memory window

Thiết lập ịa chỉ cuối cho cửa sổ bộ 0 (low) nhớ số 0 byte cao

Bảng 5.9: Chức năng các bit của thanh ghi cho phép cửa sổ (chỉ số 06h hoặc 46h) Bit Tên Chức năng 7

IOW1 IO Window 1 - Bằng 1 cho phép IO Window 1 6

IOW0 IO Window 0 - Bằng 1 cho phép IO Window 0 5

DEC Bằng 1 thì tín hiệu /MEMCS16 tạo ra từ A23-A12, nếu bằng 0 sẽ tạo ra từ A23-A17 lOMoARcPSD| 10435767 4

MW4 Memory Window 4 - Bằng 1 cho phép cửa sổ bộ nhớ số 4 3

MW3 Memory Window 3 - Bằng 1 cho phép cửa sổ bộ nhớ số 3 2

MW2 Memory Window 2 - Bằng 1 cho phép cửa sổ bộ nhớ số 2 1

MW1 Memory Window 1 - Bằng 1 cho phép cửa sổ bộ nhớ số 1 0

MW0 Memory Window 0 - Bằng 1 cho phép cửa sổ bộ nhớ số 0

Bảng 5.10: Chức năng các bit thanh ghi thiết lập ịa chỉ ầu cho cửa sổ bộ nhớ Bit Tên Chức năng 7 DS

Data bus Size - Bằng 1 cho phép bus dữ liệu 16 bit, 0 bus dữ liệu 8 bit 6 0WS

Zero Wait State - Bằng 1 không có chu kỳ chờ, 0 cộng thêm chu kỳ chờ 5

SCR1 Scratch bit - Không sử dụng 4

SCR0 Scratch bit - Không sử dụng 3-0

WSA Window Start Address – Địa chỉ bắt ầu cửa sổ A23 – A20

Byte thấp của thanh ghi này chứa các bit A19-A12 ịa chỉ bắt ầu cửa sổ.

Bảng 5.11: Chức năng các bit thanh ghi thiết lập ịa chỉ cuối cho cửa sổ bộ nhớ Bit Tên Chức năng

7,6 WS1, WS0 Wait state – Trạng thái chờ 5,4 Reserved - Dự phòng 3-0 WEA

Window End Address – Địa chỉ cuối cửa sổ A23 – A20

Byte thấp của thanh ghi này chứa các bit A19-A12 ịa chỉ cuối cửa sổ.

Bảng 5.12: Chức năng các bit thanh ghi thiết lập card offset Bit Tên Chức năng 7 WP

Write Protect – Bằng 1 chống ghi lOMoARcPSD| 10435767 6 REG

/REGISTER SELECT Enable – bằng 1 cho phép truy cập vùng

nhớ thuộc tính, bằng 0 truy cập vùng nhớ chung 5-0 WSA

Window Start Address – Địa chỉ bắt ầu cửa sổ A23 – A20

Byte thấp của thanh ghi này chứa các bit A19-A12 ịa chỉ bắt ầu cửa sổ.

Bảng 5.13: Chức năng các bit thanh ghi thiết lập ịa chỉ ầu cho cửa sổ vào ra Bit Byte Chức năng 7-0 Byte cao

Giữ các bit ịa chỉ A15-A8 của ịa chỉ bắt ầu của sổ vào ra 7-0

Byte thấp Giữ các bit ịa chỉ A7-A0 của ịa chỉ bắt ầu của sổ vào ra

Bảng 5.14: Chức năng các bit thanh ghi thiết lập ịa chỉ cuối cho cửa sổ vào ra Bit Byte Chức năng 7-0 Byte cao

Giữ các bit ịa chỉ A15-A8 của ịa chỉ cuối của sổ vào ra 7-0

Byte thấp Giữ các bit ịa chỉ A7-A0 của ịa chỉ cuối của sổ vào ra

Bảng 5.15: Chức năng các bit thanh ghi iều khiển cho cửa sổ vào ra Bit Tên Chức năng 7,3 WS1, WS0

Wait State for Window 1 and 0 – Bằng 1 cho phép trạng thái

chờ tại cửa số vào ra (số 1 và số 0) 6,2 0WS1, 0WS0

Zero Wait State for Window 1 and 0 – Bằng 1 không có

trạng thái chờ tại các cửa sổ vào ra 5,1 CS1, CS0

/IOIS16 source: bằng 1 chọn /IOIS16 từ máy tính, bằng 0

chọn data size từ DS1 và DS0

Bảng 5.16: Thông số kỹ thuật các loại PCMCIA PC Card Small PC

Miniature SmartMedia MultiMedi Compact Card card card a card Flash Độ dài (mm) 85.6 45.0 33.0 45.0 32.0 36.0 Rộng (mm) 54.0 42.8 38.0 37.0 24.0 43.0 lOMoARcPSD| 10435767 Cao (mm) 3.3/5.0/10.5 3.3/5.0/10.5 3.5 0.76 1.4 3.3/5.0

Chân/Đầu cắm Chân/Đầu cắm Elastrometic Chân/Đầu cắm Đầu nối Bề mặt Bề mặt Số chân 68 68 60 22 7 50 Sử dụng Bộ nhớ, vào Bộ nhớ, Bộ nhớ DRAM, Flash, Flash, ra, Card bus vào ra ROM, ROM ROM FLASH 5.1.6

Giao tiếp iều khiển hiển thị màn chỉ thị LED, LCD

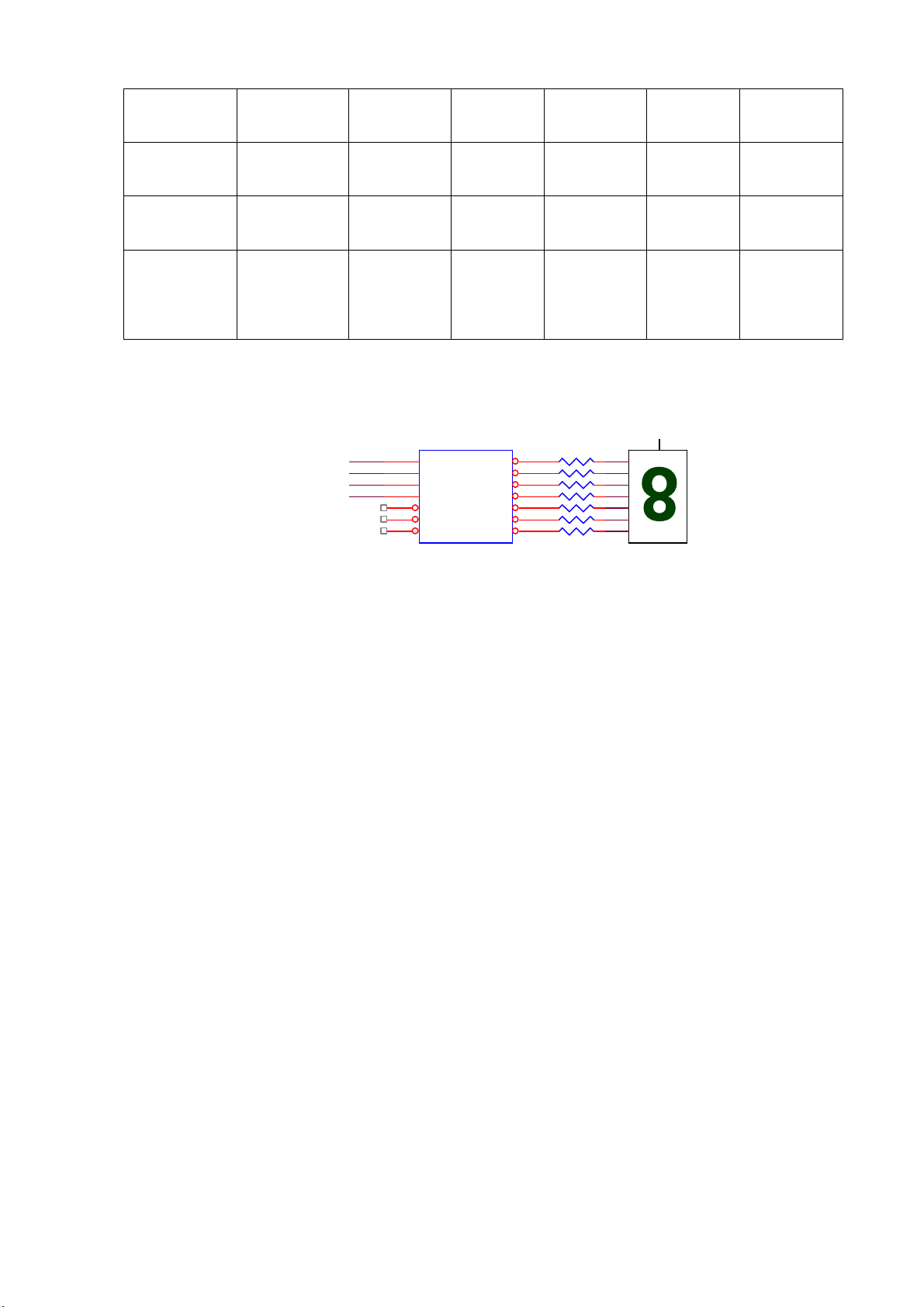

5.1.6.1 Giao tiếp với bộ hiển thị led 7 oạn Vcc U1 7 13 1 A 1 12 2 B BCD Input 2 11 6 4 C 10 4 8 D 9 BI/RBO E 5 15 RBI F 3 14 LT G 7447

Hình 5.30: Bộ hiển thị sử dụng bằng mạch lái LED 7 oạn.

Các bộ hiển thị led 7 oạn là loại giao tiếp hiển thị ược sử dụng phổ biển trong các hệ

thống vi xử lý vừa và nhỏ, chúng rất tiện dụng trong việc hiển thị các con số cho phép

xác ịnh ược các thông số mà người sử dụng muốn thiết lập cho hệ thống hoạt ộng. Một

lợi iển quan trọng của các bộ hiển thị LED 7 oạn là có thể nhìn thấy với khoảng các khá xa. lOMoARcPSD| 10435767

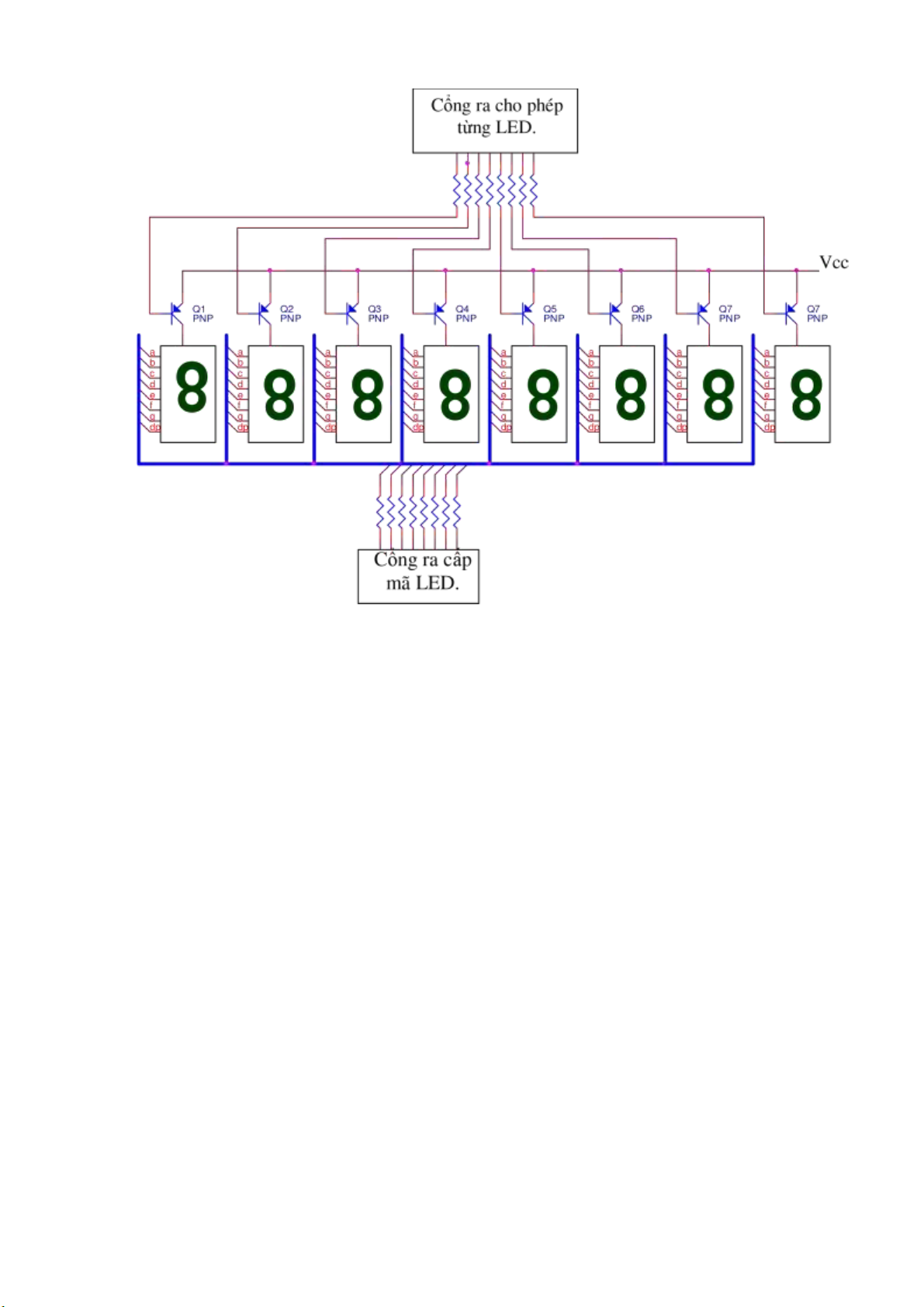

Hình 5.31: Hiển thị LED theo chế ộ quét.

Việc iều khiển hiện thị các con số có thể thực hiện bằng cách cung cấp mã BCD qua

một cổng ra, tới bộ giải mã led 7 oạn như trình bày trên hình 5.30. Khi sử dụng nhiều

LED có thể sử dụng nhiều cổng ra cài dữ liệu.

Khi muốn hiển thị cả dấu phân cách thập phân và một số ký tự với cách hiển thị qui ịnh

trước, có thể cung cấp các mã tương ứng cho LED thẳng từ một cổng ra của vi xử lý. Để

tiết kiệm số lượng cổng ra, có thể sử dụng kiểu iều khiển quét với mạch phần cứng như

hình 5.31. Trong sơ ồ này, mã hiển thị trên các ược cấp chung ể ưa tới tất cả mọi LED,

muốn LED nào chỉ thị giá trị cung cấp ở trên chỉ cần cung cấp bit 1 ể mở transistor tương

ứng cấp iện vào Kathode chung. Để tất cả các èn ều sáng, cung cấp tuần tự các mã hiển

thị và bit 1 cấp iện áp cho èn và thực hiện nhiều lần ể lưu ánh sáng lại trên èn. Nếu tần

số quét èn lớn hơn áp ứng của mắt (khoảng 40Hz), mắt người sẽ không thấy sự chớp tắt của èn.

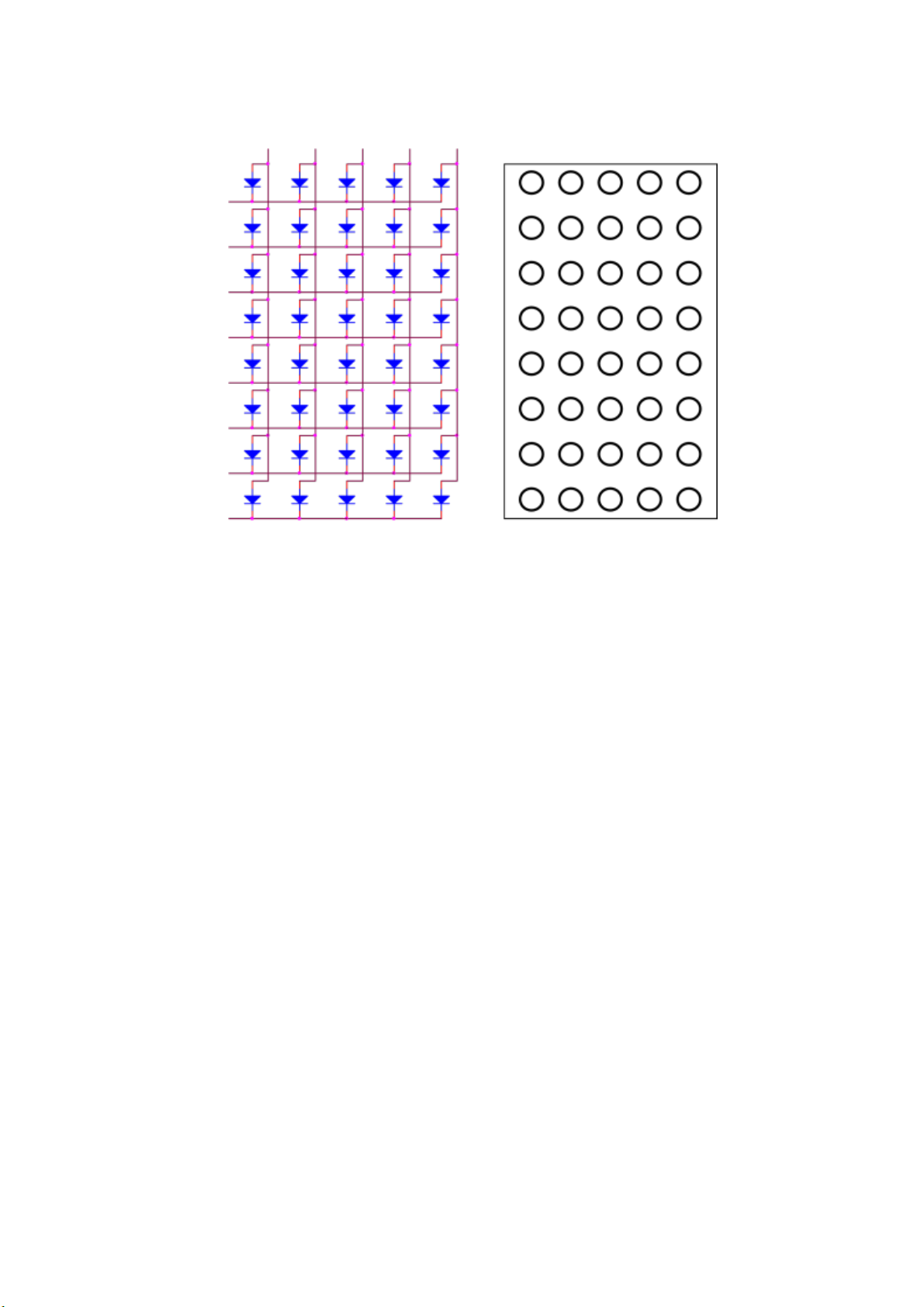

5.1.6.2 Giao tiếp bộ hiển thị LED ma trận

Để hiển thị các ký tự hoặc hình ảnh người ta còn sử dụng các LED ma trận iểm hoặc

các màn hình tinh thể lỏng loại ma trận iểm. Với các bộ hiển thị LED dạng ma trận hình

5.32, ể sáng lên một iểm cần cung cấp mức 1 vào cột và mức 0 vào hàng tương ứng với lOMoARcPSD| 10435767

nó. Như vậy với ma trận iểm 8 hàng 5 cột trên hình 5.32, thì ể hiển thị một ký tự cần

cung cấp lần lượt 5 byte mã của nó ra các hàng, tương ứng với 5 cột lần lượt bằng 1.

Hình 5.32: Cấu tạo èn hiển thị LED ma trận.

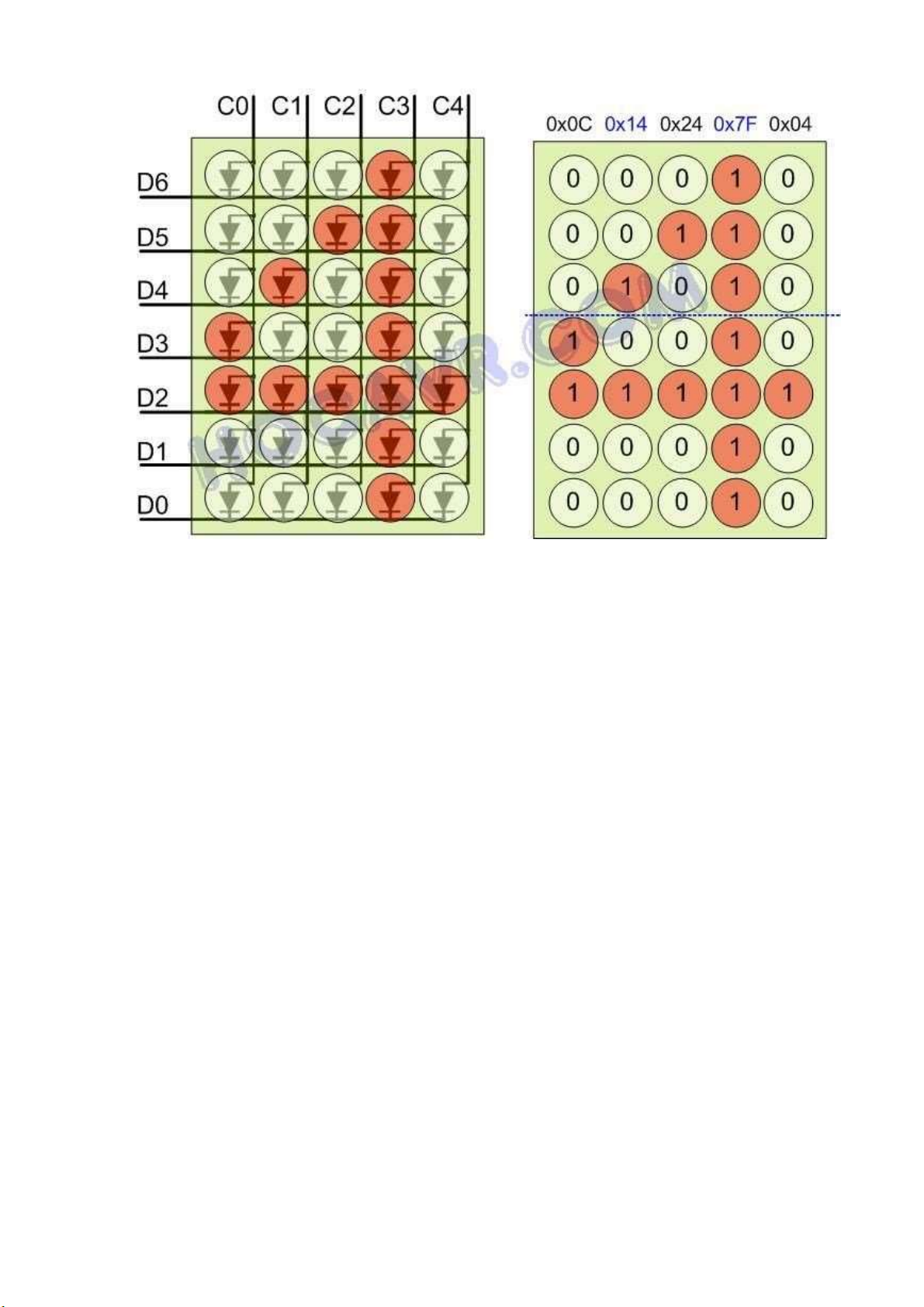

Các ma trận LED có thể chế tạo dưới dạng khối, một khối thông thường là một ma trận

iểm 5x8, 8x8 …. Hình 5.33 mô tả các mã hiển thị số 4 trên một LED ma trận iểm 5x8.

Các bộ hiển thị LED ma trận cũng có thể thực hiện bằng các LED ơn với bản mạch in

kết nối chúng thành ma trận. Các LED cũng ược chế tạo nhiều màu sắc, và với công

nghệ Ultra LED, người sử dụng có thể thực hiện các bảng LED có ộ sáng cao, các bảng

hiển thị LED có thể nhì thấy rất rõ khi ặt ngoài trời dưới ánh sáng mặt trời. Với phần

mềm iều khiển hợp lý các ký tự và hình ảnh hiển thị trên LED có thể chuyển ộng theo nhiều chiều.

Với các màn hình ma trận LED mà mỗi iểm bao gồm ba màu cơ bản (Red, Green, Blue),

với công nghệ iều chế ộ rộng xung ể iều khiển ộ sáng của từng màu, người ta có thể thực

hiện các màn hình màu bằng ma trận LED có kích thước rất lớn. lOMoARcPSD| 10435767

Hình 5.33: Mã hiển thị trên bộ hiển thị LED ma trận

5.1.6.3 Giao tiếp với các bộ hiển thị LCD

Tương tự ối với việc iều khiển màn hình LED ma trận, các màn hình tinh thể lỏng

dạng cũng ược iều khiển dưới dạng ma trận iểm, nhưng chú ý các màn hình tinh thể lỏng

cần phải iều khiển bằng tín hiệu iện áp ảo cực liên tục ể tránh từ hoá các tinh thể lỏng.

Vì vậy các màn hình tinh thể lỏng thường ược gắn sẵn mạch lái khi thương mại. Các

màn hình LCD lớn thường có các cổng chuẩn ể nhận dữ liệu, các cổng náy có thể là các

cổng nhận tín hiệu tương tự (R, G, B), cũng có thể là các cổng nhận tín hiệu số. Để sử

dụng các màn hình này cần phải thực hiện các cổng chuẩn và ịnh dạng dữ liệu trên các cổng này.

Đối với các bộ hiển thị LCD loại nhỏ, mã hiển thị cung cấp cho chúng có thể dưới

dạng ASCII, hoặc một dạng qui ịnh trước, vị trí hiển thị trên màn hình sẽ tính theo các

bit ịa chỉ cung cấp cho mạch lái, hoặc vị trí hiển thị có thể thay ổi theo các lệnh mà chúng

ược cung cấp. Để cụ thể sau ây sẽ xem xét cấu tạo và hoạt ộng của bộ hiển thị loại nhỏ

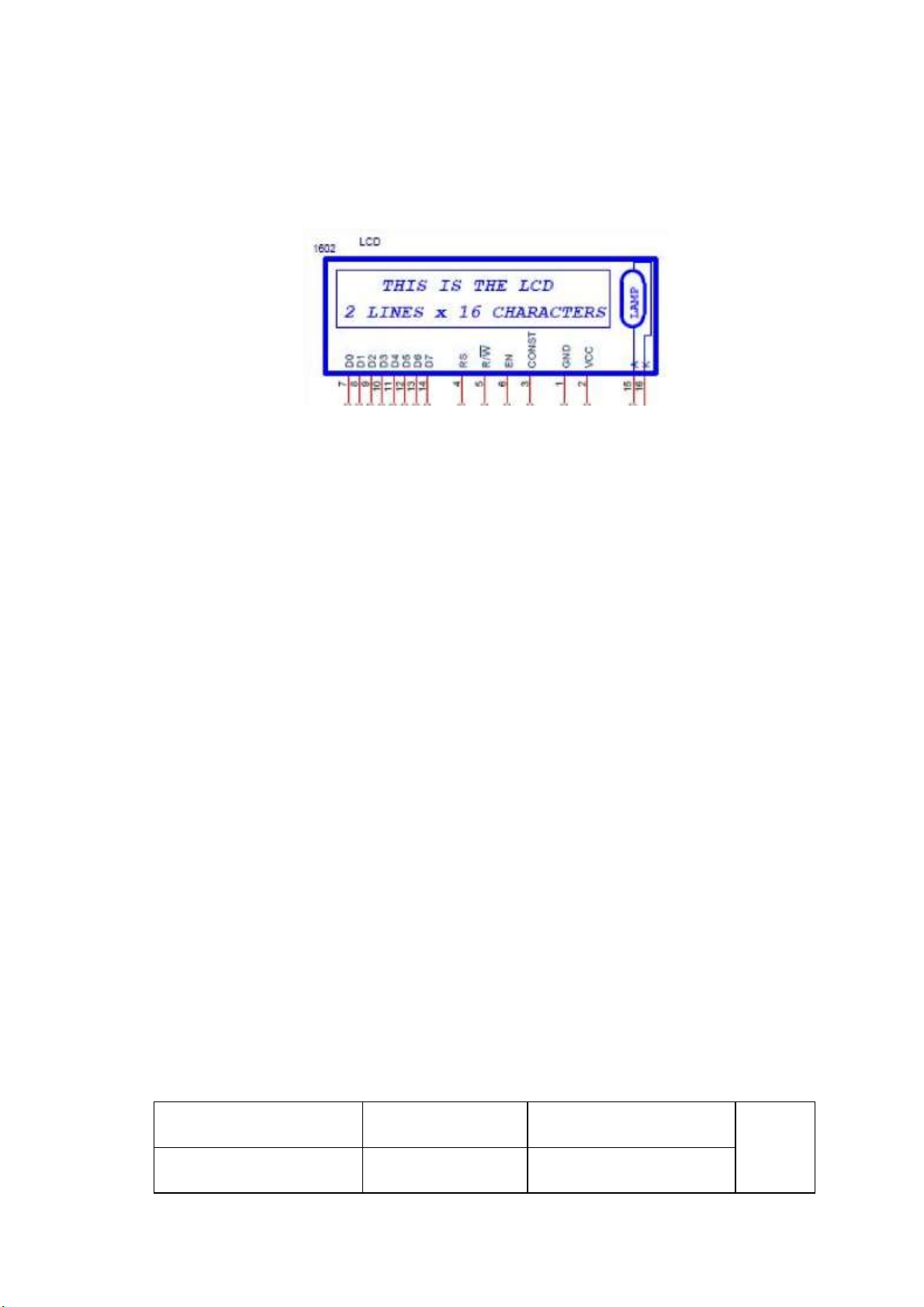

LCD1602A. Sơ ồ của LCD1602A như mô tả trên hình 5.34 bao gồm các tín hiệu sau:

- CONST (contrast): chỉnh ộ tương phản ( ộ sáng của hình ảnh trên LCD).

- EN (Enable): cho phép ọc/ghi dữ liệu. Trong chế ộ ọc, EN tác ộng bằng xung dương

(cạnh lên) và trong chế ộ ghi, EN tác ộng bằng xung âm (cạnh xuống).

- RS (register selection): chọn thanh ghi lệnh (RS = 0) hoặc thanh ghi dữ liệu (RS = 1).

- R/W: ọc (R/W = 1) hay ghi (R/W = 0). lOMoARcPSD| 10435767

- D7 – D4: bus dữ liệu (chế ộ 8 bit: 4 bit cao, chế ộ 4 bit: dùng cho truyền 4 bit cao và

4 bit thấp). Ngoài ra, bit D7 còn dùng làm ngõ ra cho cờ Busy. - D3 – D0: 4 bit thấp

trong chế ộ 8 bit hay bỏ trống trong chế ộ 4 bit. - A, K: anode và cathode èn nền của LCD.

Hình 5.34: Các tín hiệu của bộ hiển thị LCD 1602A

Các thành phần chức năng của LCD1602A gồm:

Cờ Busy (BF – Busy flag): Nếu BF = 1, LCD ang trong quá trình thực thi một lệnh. Khi

ó, các lệnh gởi tiếp theo sẽ bị bỏ qua. BF ược ọc tại chân D7 khi RS = 0 và R/W = 1. Do

ó, trước khi thực hiện một lệnh, cần kiểm tra BF trước, nếu BF = 0 thì mới gởi lệnh.

- DDRAM (Display Data RAM): chứa các ký tự sẽ hiển thị trên LCD, tối a là 80x8

bit (80 ký tự). Khi hiển thị ở chế ộ 1 dòng, ịa chỉ của DDRAM có phạm vi từ 00h ÷

4Fh còn khi ở chế ộ 2 dòng, ịa chỉ DDRAM từ 00h ÷ 27h cho dòng 1 và 40h ÷ 67h cho dòng 2.

- Bộ ếm ịa chỉ (AC - Address Counter): dùng ể lưu ịa chỉ hiện hành của DDRAM

và CGRAM, có thể thực hiện ọc AC khi RS = 0 và R/W = 1.

- CGROM (Character Genaration ROM): chứa các mô hình ký tự sẽ hiển thị trên

LCD, bao gồm 192 ký tự 5x7 theo bảng mã ASCII (nghĩa là khi DDRAM chứa giá

trị 41h tương ứng với mã ASCII của ký tự ‘A’ thì trên LCD sẽ hiện ‘A’), trong ó chỉ

có các mã từ 00h – 0Fh sẽ không lấy theo mã ASCII mà lấy theo các ký tự ã ịnh nghĩa trong CGRAM.

- CGRAM (Character Genaration RAM): chứa các mô hình ký tự do người sử dụng

ịnh nghĩa ể hiển thị các ký tự không có sẵn trong CGROM. CGRAM cho phép tạo

tối a 8 ký tự 5x8 (xem bảng 5.17).

Bảng 5.17 – Các ký tự ịnh nghĩa trong CGRAM

Mã ký tự (dữ liệu Địa chỉ CGRAM

Dữ liệu trong CGRAM Mẫu DDRAM)

D7 D6 D5 D4 D3 D2 D1 A5 A4 A3 A2 A1 A0 S P7 P6 P5 P4 P3 P2 P1 P0 ố D0 lOMoARcPSD| 10435767 0 0 0 0 X 0 0 0 0 0 0 0 0 X X X 0 1 1 1 0 mẫu 1 0 0 1 1 0 0 0 1 0 1 0 1 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 1 0 0 0 1 1 0 1 1 0 0 0 1 1 1 0 1 0 0 0 1 0 1 1 1 0 0 0 0 0 : : 0 0 0 0 X 1 1 0 1 0 0 0 0 X X X 0 1 1 1 0 mẫu 7 0 0 1 1 0 0 0 1 0 1 0 1 0 0 0 0 0 1 1 1 0 1 1 1 1 0 0 1 0 0 0 1 1 0 1 1 0 0 0 1 1 1 1 0 0 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 X 1 1 1 1 1 0 0 0 X X X 1 0 0 0 1 pattern 8 0 0 1 1 0 0 0 1 0 1 0 1 0 0 0 1 0 1 1 1 1 1 1 1 1 0 0 1 0 0 0 1 1 0 1 1 0 0 0 1 1 1 0 1 0 0 0 1 1 lOMoARcPSD| 10435767 1 1 1 0 0 0 0 0

Ví dụ: Để ịnh nghĩa chữ Đ tại vị trí 1 trong CGRAM, ịa chỉ và dữ liệu tương ứng là: Địa chỉ Dữ liệu 00h 1 1 1 1 0 1Eh 01h 0 1 0 0 1 09h 02h 0 1 0 0 1 09h 03h 1 1 0 1 1Dh 1 04h 0 1 0 0 1 09h 05h 0 1 0 0 1 09h 06h 1 1 1 1 0 1Eh 07h 0 0 0 0 0 00h

Nghĩa là tại ịa chỉ 00h của CGRAM chứa giá trị là 1Eh và tương tự cho ến ịa chỉ 07h.

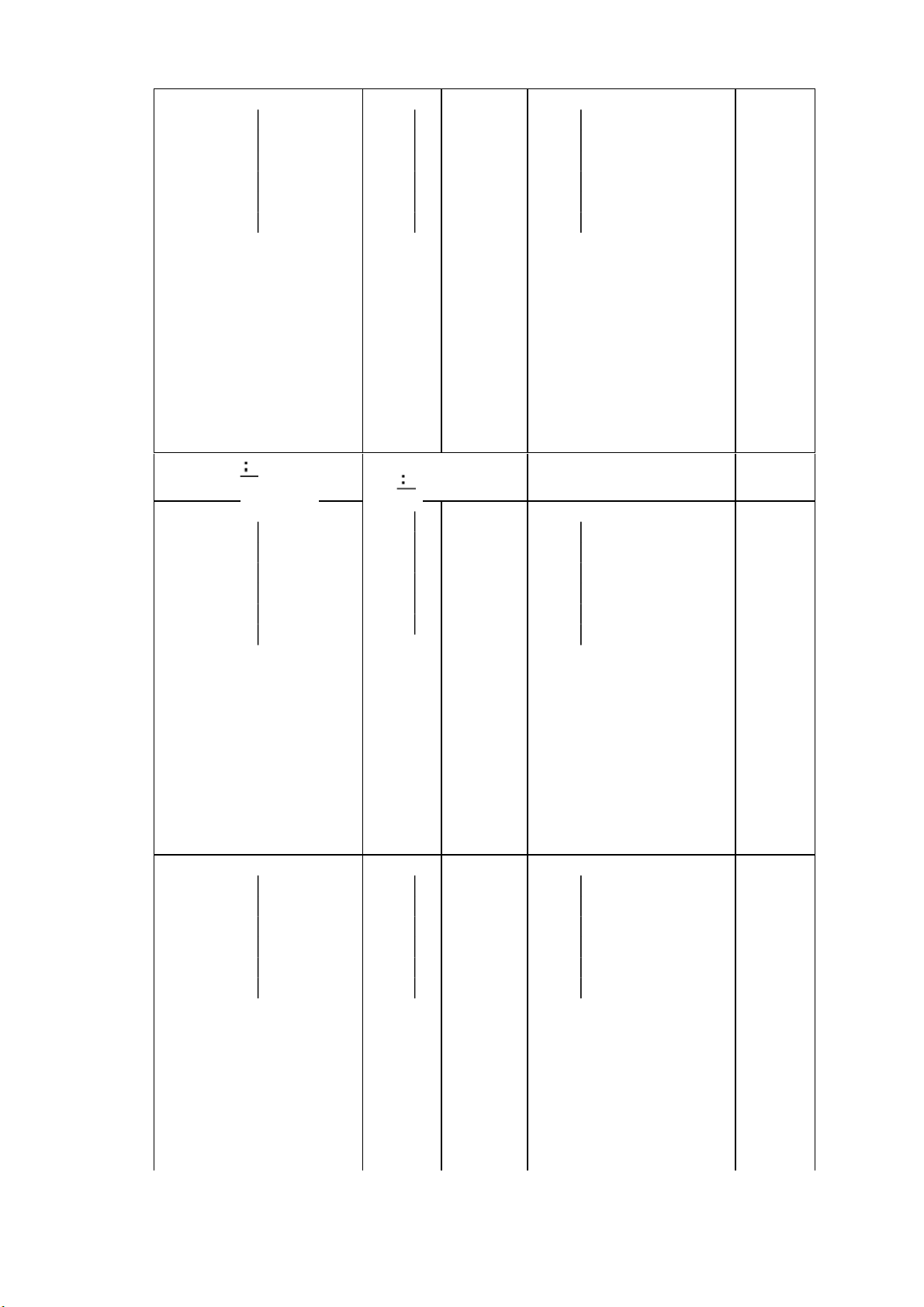

Các chế ộ truyền dữ liệu: LCD1602A có 2 chế ộ truyền dữ liệu: chế ộ 8 bit (dùng cả

D0 – D7) và chế ộ 4 bit (không dùng D3 – D0, chỉ dùng D7 – D4). Trong trường hợp

dùng chế ộ 4 bit, dữ liệu 8 bit sẽ ược truyền 2 lần: truyền 4 bit cao rồi tiếp tục truyền 4

bit thấp. Sau khi thực hiện truyền xong 8 bit, BF mới chuyển lên 1. Hai chế ộ truyền này

mô tả như hình 5.35 và 5.36. lOMoARcPSD| 10435767 RS R/W E Internal Internal operation signal DB7 No busy DB7 DATA DATA Busy Busy INSTRUCTION Busy Flag Check Busy Flag Check Busy Flag Check INSTRUCTION

Hình 5.35: Định thời chế ộ truyền 8 bit LCD 1602A RS R/W E Internal Internal operation signal DB7 No busy DB7 D7 D3 D3 D7 Busy INSTRUCTION Busy Flag Check Busy Flag Check INSTRUCTION

Hình 5.36: Định thời chế ộ truyền 4 bit LCD 1602A

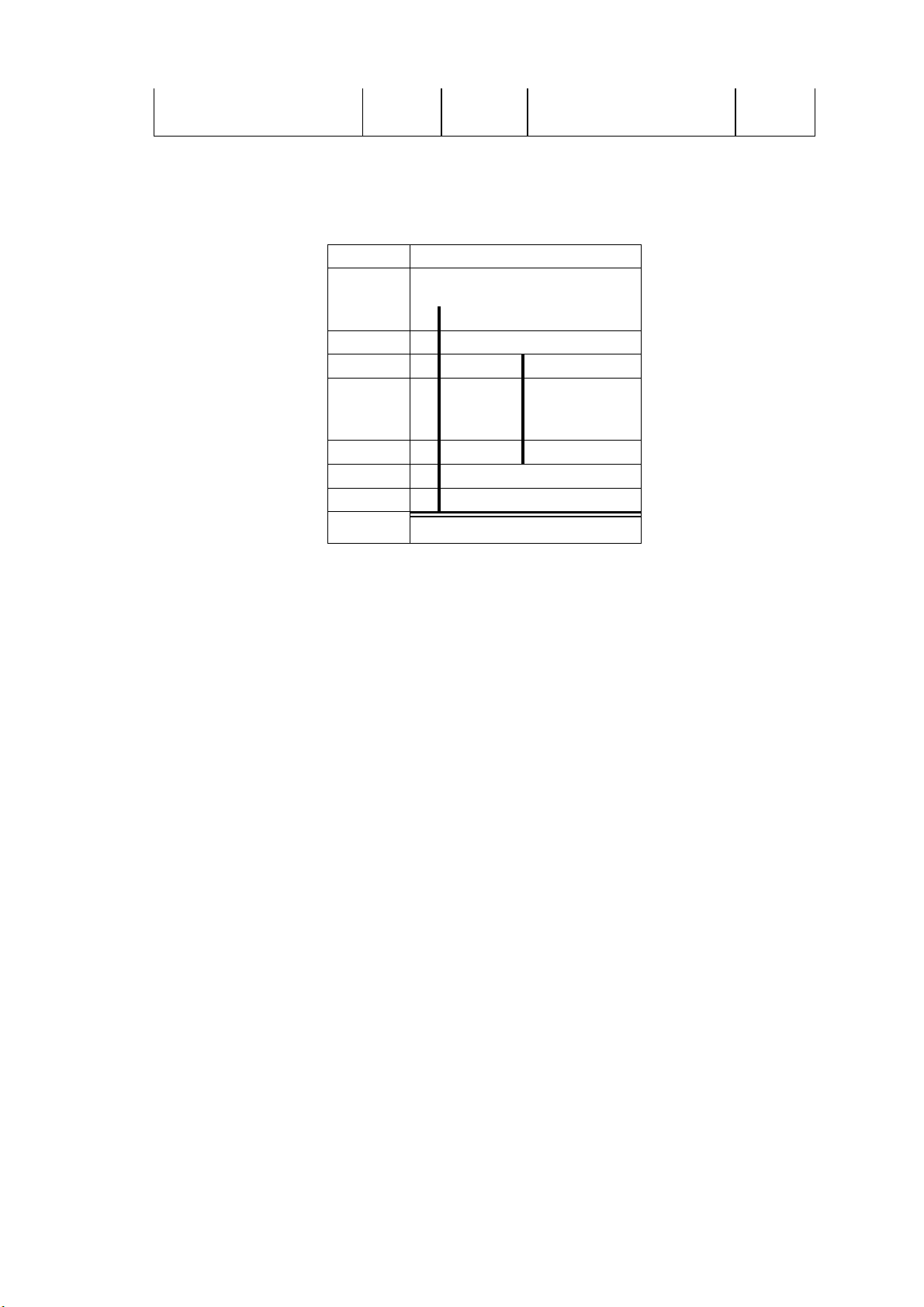

Bảng 5.18: Bảng mã lệnh LCD lOMoARcPSD| 10435767 Lệnh Mã lệnh Mô tả Thời gian(fosc= 270kHz)

RS R/W DB DB DB DB DB DB DB DB 7 Clear 0 0 0 0 0 0 0 0 0 1

Write “20H” to DDRAM, and 1.53ms Display set

DDRAM address to “00H” from AC. Return 0 0 0 0 0 0 0 0 1

X Set DDRAM address to “00H” 1.53ms Home

from AC and return cursor to its

original position if shifted. The contents of DDRAM are not changed. Entry 0 0 0 0 0 0 0 1 I/D S

Assign cursor moving direction. 39us Mode Set I/D=”1”: increment, I/D=”0”: decrement and display shift enable bit.

S=”1”: make entire display shift of all lines during DDRAM write.

S=”0”: display shift disable Display 0 0 0 0 0 0 1 D C B

Set display/cursor/blink on/off 39us ON/OFF D=”1”: display on, Control D=”0”: display off, C=”1”: cursor on, C=”0”: cursor off, B=”1”: blink on, B=”0”: blink off. Cursor 0 0 0 0 0 1 S/C R/L X X Cursor or display shift, 39us or S/C=”1”: display shift, Display S/C=”0”: cursor shift, Shift R/L=”1”: shift to right, R/L=”0”: shift to left. Function 0 0 0 0 1 DL N F X X Set interface data length 39us Set DL=”1”: 8-bit DL=”0”: 4-bit N=”1”: 2-line display N=”0”: 1-line.display F=”0” 5*7-dot F=”1” 5*10-dot Set 0 0 0 1 AC AC AC AC AC AC 5

4 Set CGRAM address in address 39us CGRAM 3 2 1 0 counter Address Set

0 0 1 AC AC AC AC AC AC AC 6 5 4 3 2 1 0 Set DDRAM address in address 39us DDRAM counter Address

Read Busy 0 1 BF AC AC AC AC AC AC AC 6 5 4 3 2 1 Can be known whether during 0us Flag and 0 internal operation or not by Address reading BF. The contents of address counter can also be read. BF=”1”: busy state, BF=”0”: ready state.

Write Data 1 0 D7 D6 D5 D4 D3 D2 D1 D0 Write data into internal RAM 43us (DDRAM/CGRAM).

Read Data 1 1 D7 D6 D5 D4 D3 D2 D1 D0 Read data from internal RAM 43us (DDRAM/CGRAM) lOMoARcPSD| 10435767

Bảng 5. 19: Các lệnh thông dụng của LCD 1602A Hex Lệnh 01H Xóa màn hình màn hình 02H Trở về ầu chuỗi

04H Dịch con trỏ sang trái 06H Dịch con trỏ sang phải 05H Dịch màn hình sang phải 07H

Dịch màn hình sang trái Tắt 08H con trỏ, tắt hiển thị

0AH Tắt hiển thị, bật con trỏ

0CH Bật hiển thị, tắt con trỏ 0EH

Bật hiển thị, nhấp nháy con trỏ 0FH

Tắt hiển thị, nhấp nháy con trỏ 10H

Dịch vị trí con trỏ sang trái 14H

Dịch vị trí con trỏ sang phải 18H

Dịch toàn bộ màn hình sang trái

5.1.7 Cảm biến vòng quay (Rotary Encoder)

Bộ cảm biến vòng quay (Rotary Encoder) là một thiết bị biến ổi sự chuyển ộng thành

một chuỗi xung số. Bằng các ếm các xung, hoặc xét mã mà Encoder cung cấp có thể xác

ịnh ược vi trí chuyển ộng chính xác của thiết bị. Encoders có hai loại cấu hình là tuyến

tính (linear encoder) và quay (rotary encoder). Bộ mã hoá vị trí quay ược sản xuất ở hai dạng cơ bản là:

- Mã hoá tuyệt ối (absolute encoder): Tạo ra một từ số duy nhất tương ứng với mỗi vị trí quay của nó.

- Mã hoá tăng (incremental encoder): cung cấp các xung số khi quay cho phép o ược

vị trí tương ứng với góc quay.

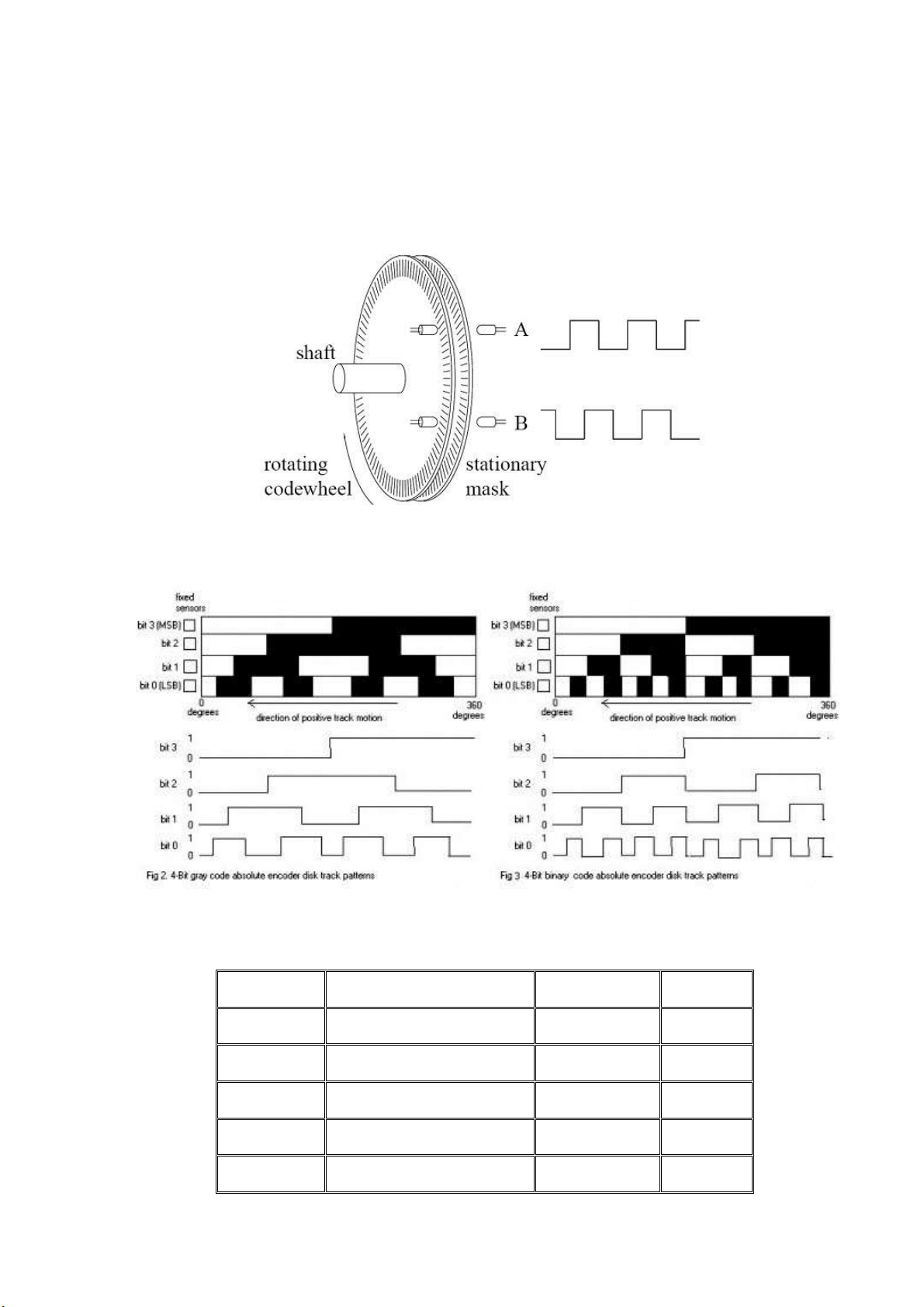

Hầu hết các cảm biến quay ược chế tạo từ một ĩa thuỷ tinh hoặc nhựa ược xẻ rãnh,

bộ thu phát quang ặt hai bên ĩa quay sẽ cảm nhận các rãnh trên ĩa ể tạo ra các xung hoặc

các tổ hợp số nhị phân. Hình 5.37 mô tả nguyên lý của một encoder với một ĩa mã hoá

quay tròn và một mặt nạ che ứng nguyên. Tấm che ứng nguyên này thường không ược sử dụng.

Trong bộ cảm biến vòng quay tuyệt ối, ĩa quang ược thiết kế ể tạo ra một từ mã nhị

phân riêng cho N vị trí khác nhau của trục quay. Ví dụ, nếu encoder có 8 vạch thì nó có

thể tạo ra 256 giá trị nhị phân cho một vòng quay hay cứ 1,406 ộ thì tổ hợp nhị phân do lOMoARcPSD| 10435767

encoder cung cấp sẽ thay ổi. Hầu hết các absolute encoder ều tạo ra các mã nhị phân tự

nhiên (binary) hoặc mã gray. Hình 5.38 mô tả cấu trúc ĩa quang 4 vạch ể tạo ra mã nhị

phân tư nhiên 4 bit và mã gray 4 bit. Bộ cảm biến quang sẽ cảm nhận các vùng trắng

trên các vạch ĩa ể tạo ra bit 0 và vùng en ể tạo ra bit 1 của mã. Mã tạo ra tương ứng với

góc quay của trục ược cho trong bảng 5.20.

Hình 5.37: Nguyên lý rotery encoder

Hình 5.38: Đĩa quang 4 vạch trong các absolute encoder tạo mã gray và nhị phân

Bảng 5.20: Mã ngõ ra của absolute encoder

Thập phân Khoảng góc quay (ộ) Mã nhị phân Mã Gray 0 0-22.5 0000 0000 1 22.5-45 0001 0001 2 45-67.5 0010 0011 3 67.5-90 0011 0010 4 90-112.5 0100 0110 lOMoARcPSD| 10435767 5 112.5-135 0101 0111 6 135-157.5 0110 0101 7 15.75-180 0111 0100 8 180-202.5 1000 1100 9 202.5-225 1001 1101 10 225-247.5 1010 1111 11 247.5-270 1011 1110 12 270-292.5 1100 1010 13 292.5-315 1101 1011 14 315-337.5 1110 1001 15 337.5-360 1111 1000

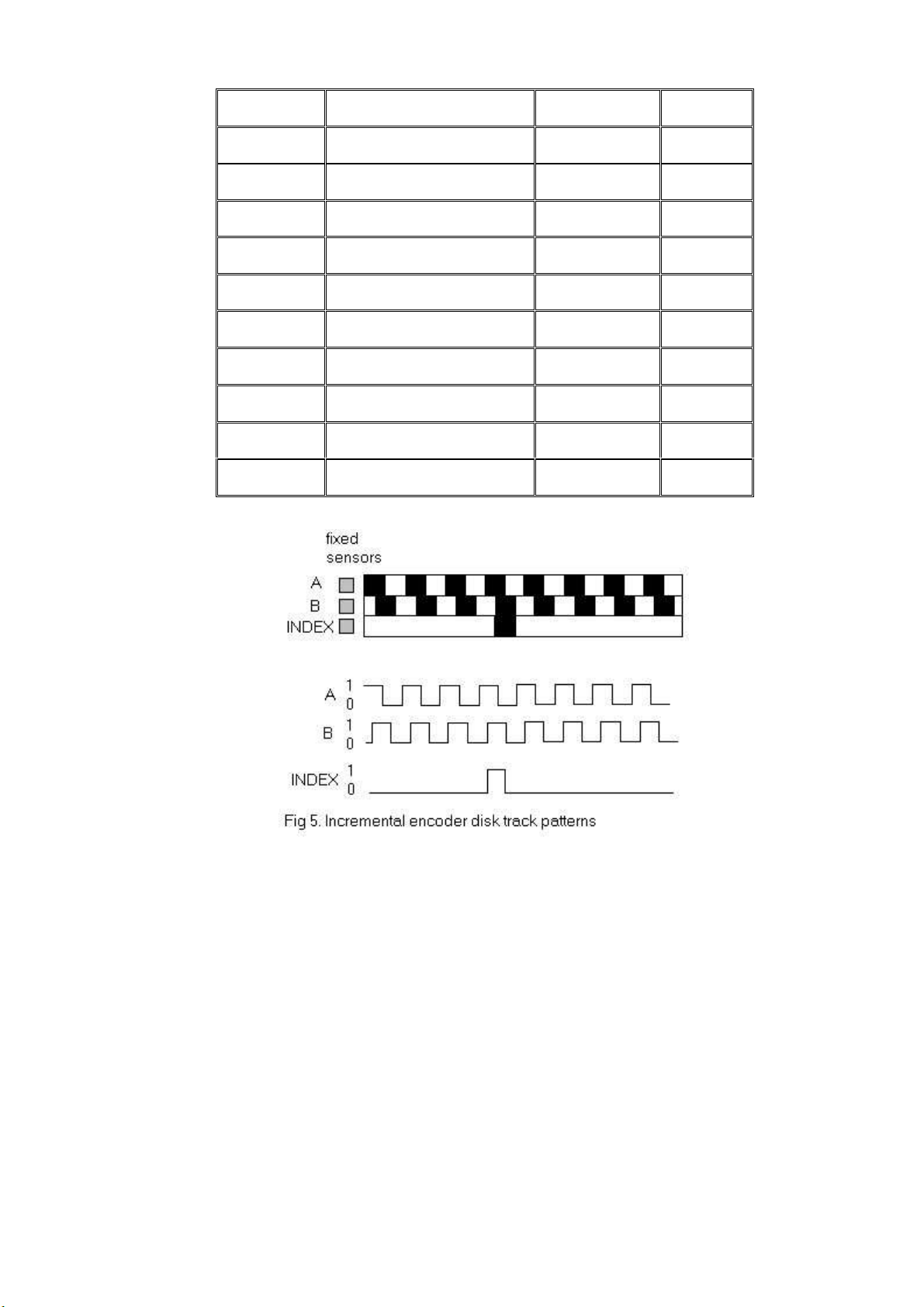

Hình 5.39: Đĩ a quang và dạ ng sóng ngõ ra encoder tăng

Các bộ encoder tăng (ôi khi ược gọi là các encoder tương ối), có thiết kế ơn giản hơn

các encoder tuyệt ối. Nó gồm ĩa quay hai vạch với hai bộ cảm biến cung cấp các xung

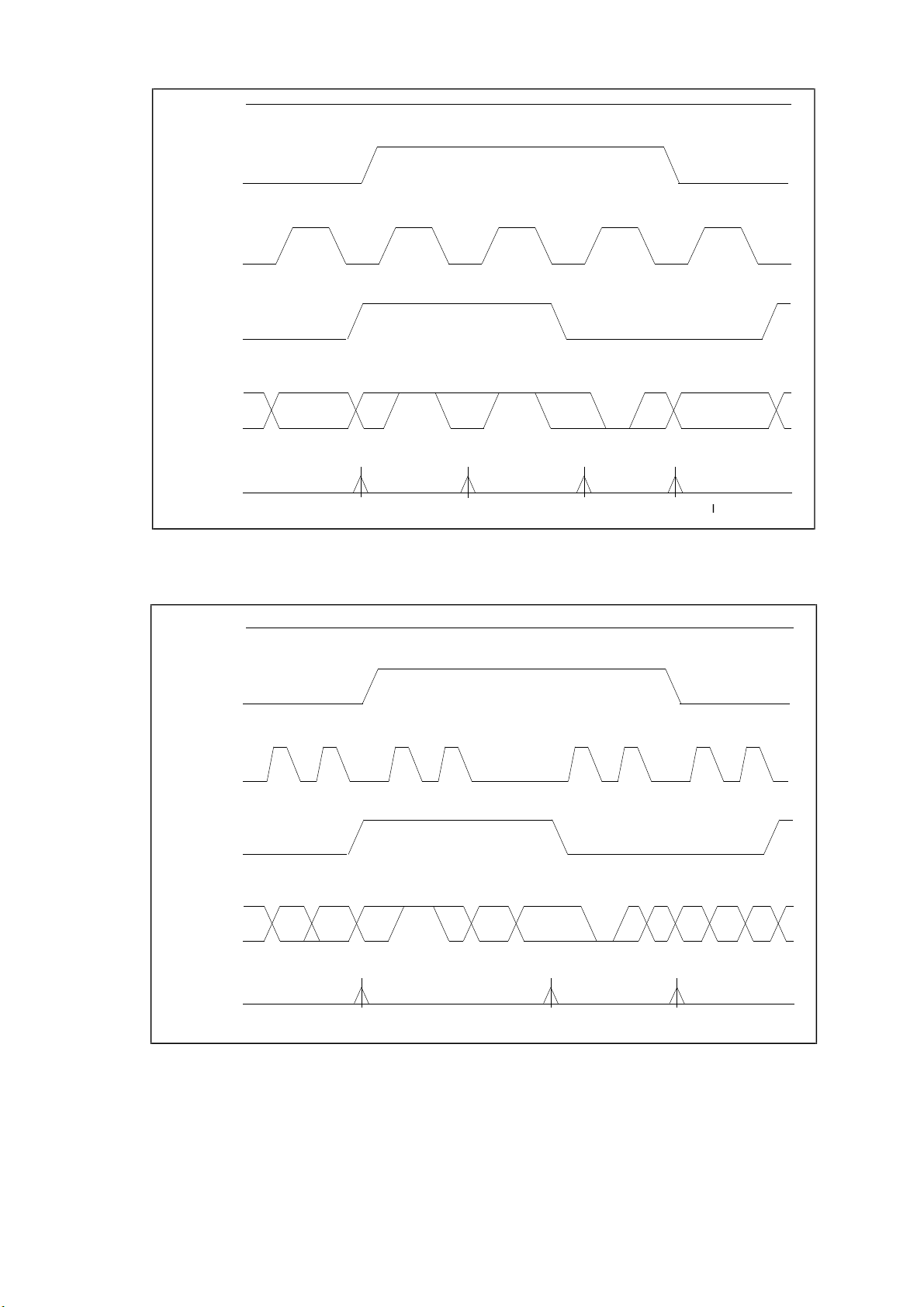

ngõ ra ược gọi là các kênh A và B. Khi trục quay chuỗi xung tạo ra trên các kênh này có

tần số tỷ lệ thuận với tốc ộ quay của trục. Cấu tạo của ĩa quang và dạng sóng ra trên các

kênh ược mô tả trên hình 5.39. Bằng cách ếm số xung tạo ra và nếu biết trước khoảng

chia trên ĩa quang sẽ có thể o ược góc chuyển dịch của trục quay. Góc lệch pha giữa

xung hai kênh A và B cũng cho phép xác ịnh ược chiều quay, bằng cách xác ịnh kênh

dẫn hướng cho kênh kia. Hai tín hiệu ở hai kênh sẽ lệch pha ¼ chu kỳ. Thông thường

encoder tăng thường ược thiết kế ể tạo ra xung thứ 3, gọi là xung chỉ số (INDEX), một

xung sẽ ược tạo ra sau một vòng quay, và xung này rất tiện dung ể ếm số vòng quay,

hoặc xác ịnh ã quay hết một vòng. Nó cũng thường ược sử dụng cho việc xác ịnh vị trí lOMoARcPSD| 10435767

bắt ầu của các chuyển ộng tịnh tiến (home base hoặc zero position). Để việc chế tạo ơn

giản và giảm giá thành chế tạo encoder, người ta còn sử dụng các ĩa quang một vạch.

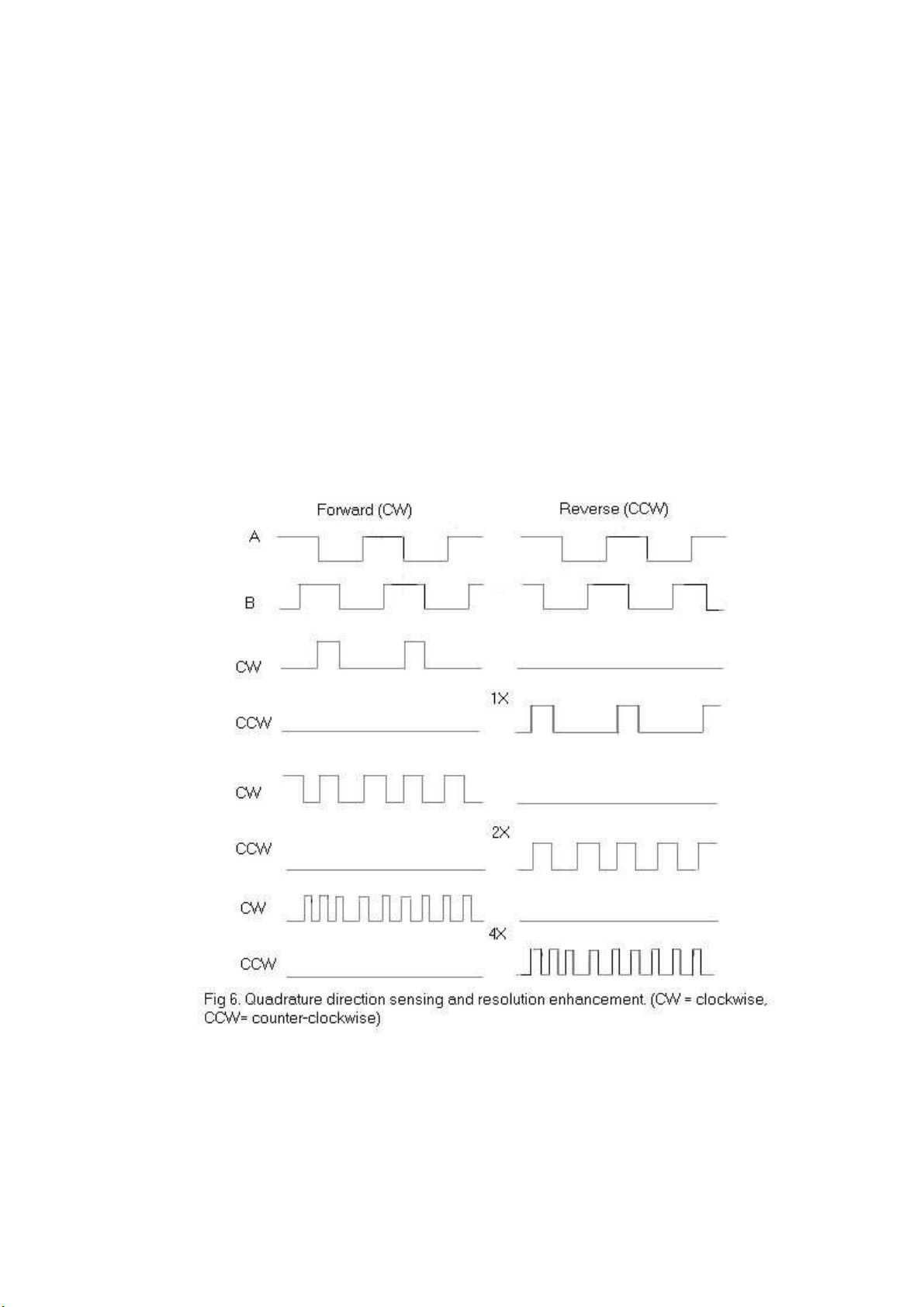

Việc giải mã các tín hiệu hai kênh A và B ể xác ịnh chiều quay như mô tả trên hình

5.40. Việc giải mã này có thể sử dụng các mạch tuần tự theo các cách khác nhau, trên

hình 5.40 mô tả ba cách ể tạo ra các xung 1X, 2X, 4X. Ngõ ra 1X chỉ cung cấp một xung

sau một chu kỳ của tín hiệu kênh A hoặc kênh B. Ngõ ra 4X sẽ tạo ra một xung tại mỗi

cạnh lênh và xuống của các tín hiệu A và B, như vậy nếu có 1 xung 1X thì sẽ có 4 xung

ở ngõ ra 4X. Hướng quay cùng hay ngược chiều kim ồng hồ sẽ ược xác ịnh bằng mức 1

của một tín hiệu tại cạch chuyển mức của tín hiệu thứ 2. Ví dụ, trong chế ộ 1X, tại cạnh

xuống của tín hiệu kênh A, kênh B có trạng thái bằng 1, suy ra chiều truyền ang cùng

chiều kim ồng hồ, và nếu tại cạnh xuống của B tín hiệu A bằng 1 thì trục ang quay ngược

chiều kim ồng hồ. Như vậy nếu chỉ có một xung ngõ ra sẽ không thể xác ịnh ược hướng quay của trục.

Hình 5.40: Xá c ị nh chi ề u quay theo xung hai kênh A và B

5.1.8 Giao tiếp công suất cao

Các ngõ ra của các bộ vào ra số thông thường chỉ cung cấp dòng iện khoảng vài chục

mA khi mức thấp, và khoảng 1 tới 2 mA khi ở mức cao. Vì vậy nếu muốn iều khiển các

thiết bị có công suất lớn như: các bóng èn iện, các công tắc iện từ (solenoid), các ộng cơ lOMoARcPSD| 10435767

… bằng hệ thống vi xử lý, chúng ta cần phải sử dụng các bộ giao tiếp công suất lớn ể

khuếch ại các tín hiệu số này cả về dòng iện mức và dạng iện áp.

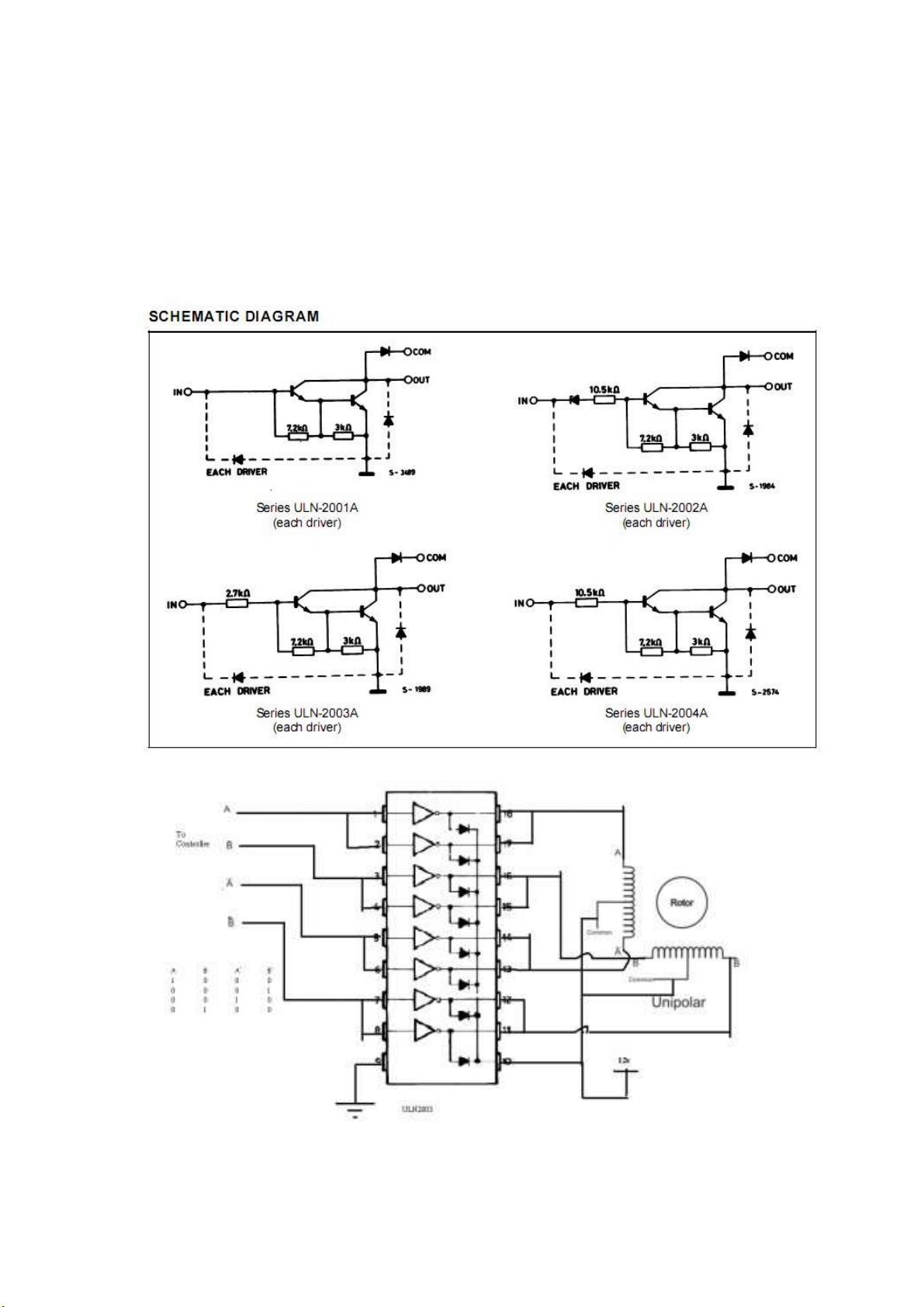

Khi cần giao tiếp với các thiết bị với công suất không lớn lắm, có thể sử dụng các bộ

ệm TTL như 74LS07, 7406 …. Các bộ ệm loại này có thể cho dòng iện 40mA khi cung

cấp mức thấp, hoặc một số IC lái thông dụng họ ULN có thể cung cấp dòng iện tới gần 1

A. Hình 5.41 mô tả cấu trúc bên trong của các IC họ ULN và ví dụ về việc sử dụng ể iều khiển ộng cơ bước.

Hình 5.41: Cấu trúc và ứng dụng IC khuếch ại dòng DC lOMoARcPSD| 10435767

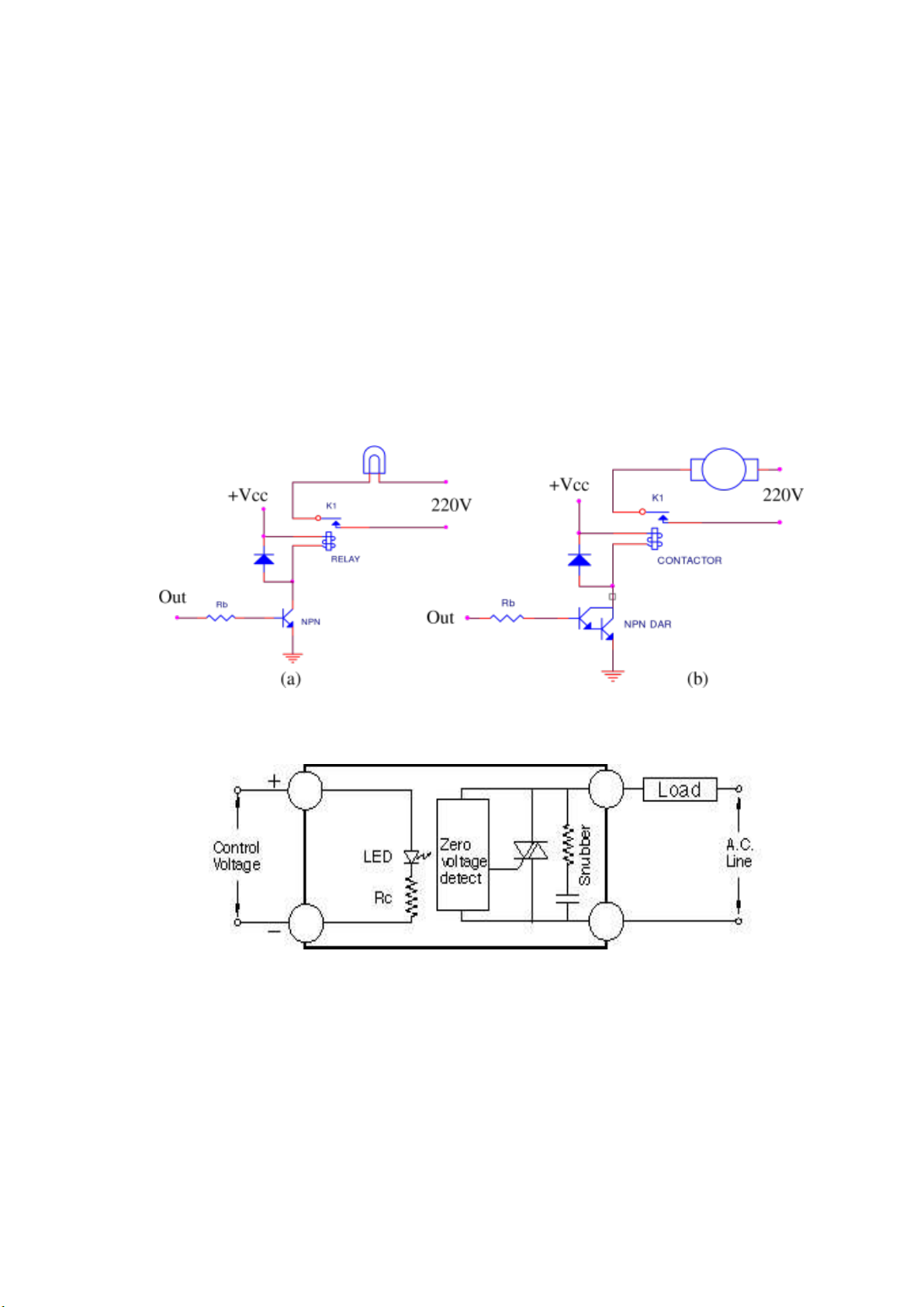

Với các tải yêu cầu dòng iện lớn hơn như các công tắc iện từ, các relay có thể sử

dụng các transistor ệm làm việc ở chế ộ khoá (hình 5.42a). Khi cần dòng iện lớn hơn có

thể sử dụng các transistor công suất, nếu dòng iện tải yêu cầu lớn (dòng cực C lớn) sẽ

yêu cầu cung cấp dòng iện cực B lớn lúc này cần ghép hai hoặc nhiều tầng transistor

(hình 5.42b). Cấu trúc này có thể cho dòng iện tải lên tới vài chục Ampere. Nhưng với

dòng iện vài chục ến vài trăm mA, thông thường người ta sử dụng các hệ thống kết nối

Relay – Contactor. Khi tần số óng ngắt yêu cầu lớn, các thiết bị óng cắt tiếp iểm dễ hư

hỏng và không áp ứng kịp, có thể sử dụng các linh kiện iện tử công suất như: SCR, Triac,

IGBT, hay thông dụng và hiệu quả nhất là các contactor iện tử (Solid – State Relay), như

trên hình 5.43. Các linh kiện này có khả năng óng ngắt với tần số rất lớn và không gây

nhiễu nguồn iện, cũng như các thiết bị khác. LAMP MOTOR AC

Hình 5.42: Mạch ệm transistor.

Hình 5.43: Cấu tạo contactor iện tử lOMoARcPSD| 10435767

Hình 5.44: Giao tiếp công suất bằng MOSFET (a) và IGBT (b)

Các linh kiện bán dẫn như MOSFET và IGBT có tổng trở vào lớn nên thường yêu cầu

dòng kích vào khá nhỏ, nhưng vẫn có khả năng cung cấp dòng tải lớn. Hình 5.44 trình

bày việc sử dụng MOSFET và IGBT trong việc óng ngắt dòng cho các cuộn dây hoặc ộng cơ iện.

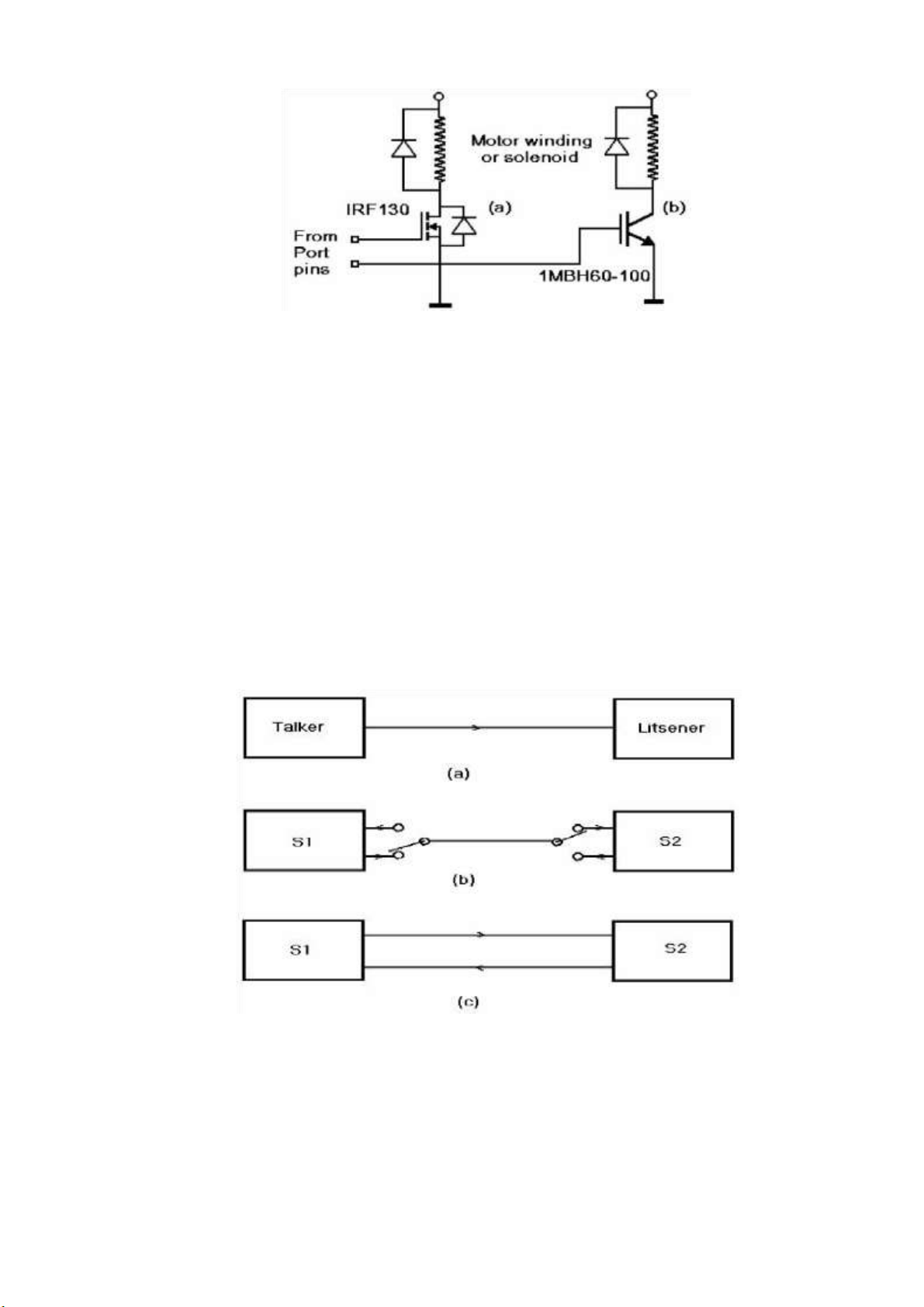

5.2 GIAO TIẾP NỐI TIẾP 5.2.1 Khái niệm

Trong các hệ thống vi xử lý thông tin thường ược truyền song song dưới dụng byte

hoặc từ (nhiều byte). Khi truyền dữ liệu với thiết bị bên ngoài ở khoảng cách xa, ể tiết

kiệm dây dẫn và tránh nhiễu xuyên kênh giữa các ường tín hiệu song song, người ta

thường truyền chuỗi bit nối tiếp trên một ường dây. Đường truyền nối tiếp giữa hai thiết

bị có thể theo ba chế ộ như mô tả trên hình 5.45.

Hình 5.45: Truyền dữ liệu nối tiếp (a) Simplex, (b) Hafl Duplex, (c) Full duplex

Trong chế ộ ơn công (simplex) dữ liệu chỉ truyền theo một chiều, hệ thống có một

bộ phận chỉ truyền và một bộ phận chỉ nhận (hình 5.34a). Chế ộ bán song công sử dụng

một ường truyền, nhưng có thể chuyển kết nối qua các bộ thu phát dữ liệu ở hai ầu, ể có lOMoARcPSD| 10435767

thể truyền dữ liệu theo hai chiều (hình 5.45b). Chế ộ song công sử dụng hai ường dây ể

truyền nhận dữ liệu theo hai chiều.

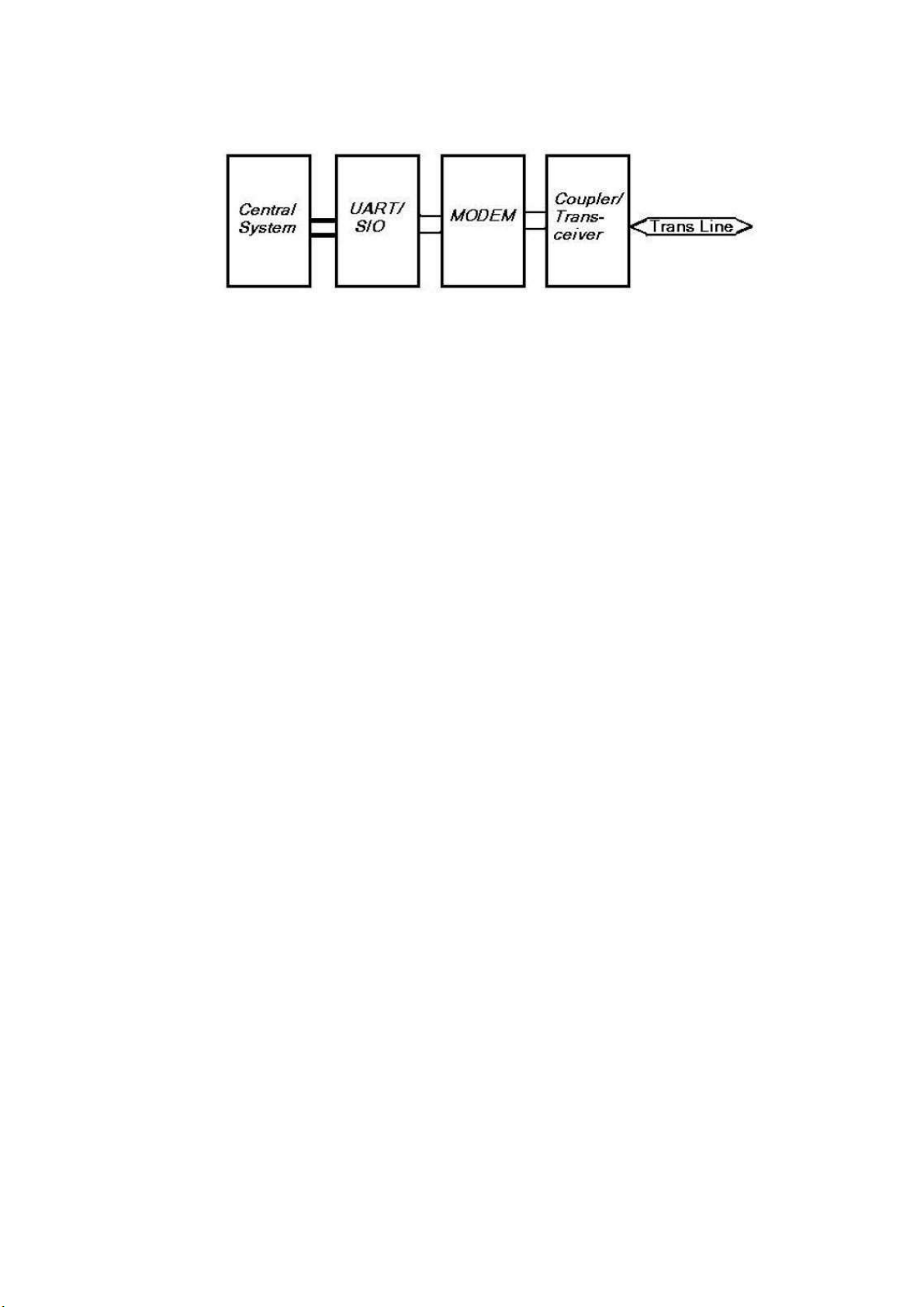

Hình 5.46: Các thành phần trong hệ thống truyền dữ liệu nối tiếp

Hình 5.46 mô tả các thành phần trong hệ thống truyền nhận dữ liệu nối tiếp trên ường

truyền xa, dữ liệu song song trong hệ thống vi xử lý (Central system) ược biến ổi thành

tín hiệu nối tiếp qua bộ truyền nhận nối tiếp (UART/SIO).

Bộ truyền nhận nối tiếp có chức năng chuyển dữ liệu song song từ hệ thống thành

chuỗi dữ liệu nối tiếp, thêm các bit chức năng ể tạo thành khung truyền dữ liệu, theo

chiều truyền. Theo chiều nhận, nó nhận chuỗi dữ liệu nối tiếp, thông báo lỗi (nếu có) và

loại bỏ các bit chức năng, ể chuyển thành dữ liệu song song chuyển cho CPU. Nếu ường

truyền ngắn ngõ ra khối UART/SIO có thể kết nối trực tiếp với một hệ thống vi xử lý

khác. Khi ường truyền xa, ngõ ra của UART/SIO ược nối tới khối iều chế và giải iều chế tín hiệu MODEM.

MODEM nhận tín hiệu số và iều chế lên tần số cao ể chống nhiễu và giảm suy hao

trên ường truyền, cho phép tín hiệu có thể truyền trên khoảng cách lớn. Tín hiệu số cũng

có thể iều chế ơn giản thành ộ lệch iện áp giữa hai ường dây (IEEE 485). Để truyền nhận

tín hiệu có thể dùng chung một ường dây cần thêm khối ghép ường truyền (Coupler Transceiver).

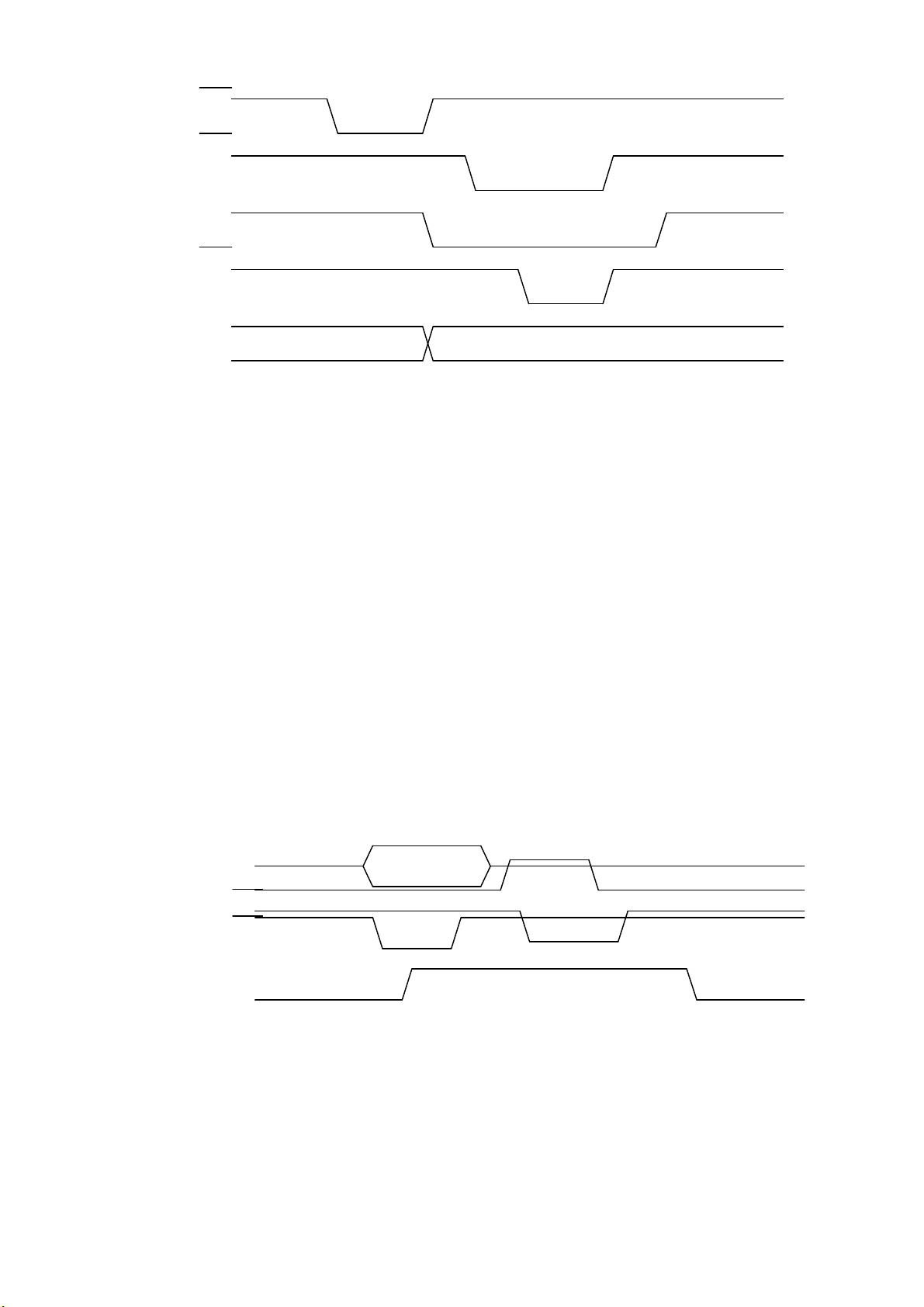

Dữ liệu truyền nối tiếp ược óng gói vào các khung truyền theo các tiêu chuẩn khác

nhau. Có hai chuẩn truyền thường sử dụng cho cổng nối tiếp trong các hệ thống vi xử lý

là: truyền cận ồng bộ (Asynchronous) và truyền ồng bộ (synchronous). Trong chuẩn cận

ồng bộ, mỗi dữ liệu truyền sẽ ược óng gói trong một khung truyền với các bit chức năng

ược thêm vào. Còn với chuẩn ồng bộ thì các bit dữ liệu sẽ ược truyền liên tiếp sau khi ã ồng bộ giữa hai bên.

5.2.2 Chuẩn RS-232c/V24

RS-232C (Recommended Standard 232 version C) là một tiêu chuẩn do Electronic

Industries Association ( EIA) ưa ra, liên quan ến việc truyền dữ liệu giữa các máy tính

bằng cổng nối tiếp tương thích RS- 232C, ể có thể dùng với modem ngoài, máy in, máy

quét hình, và các thiết bị ngoại vi khác.

Các thiết bị ghép nối trên cổng RS232C ược chia thành 2 loại: DTE (Data Terminal

Equipment) và DCE (Data Communication Equipment). DCE là các thiết bị trung gian lOMoARcPSD| 10435767

như MODEM còn DTE là các thiết bị tiếp nhận hay truyền dữ liệu như máy tính, PLC,

vi iều khiển, …. Việc trao ổi tín hiệu thông thường qua 2 chân RxD (nhận) và TxD

(truyền). Các tín hiệu còn lại có chức năng hỗ trợ ể thiết lập và iều khiển quá trình truyền,

ược gọi là các tín hiệu bắt tay (handshake). Ưu iểm của quá trình truyền dùng tín hiệu

bắt tay là có thể kiểm soát ường truyền.

Chuẩn RS-232 quy ịnh mức logic 1 ứng với iện áp từ -3V ến -15V (mark), mức logic

0 ứng với iện áp từ 3V ến 15V (space) và có khả năng cung cấp dòng từ 10 mA ến 20

mA. Ngoài ra, tất cả các ngõ ra ều có ặc tính chống ngắn mạch. Chuẩn RS-232C cho

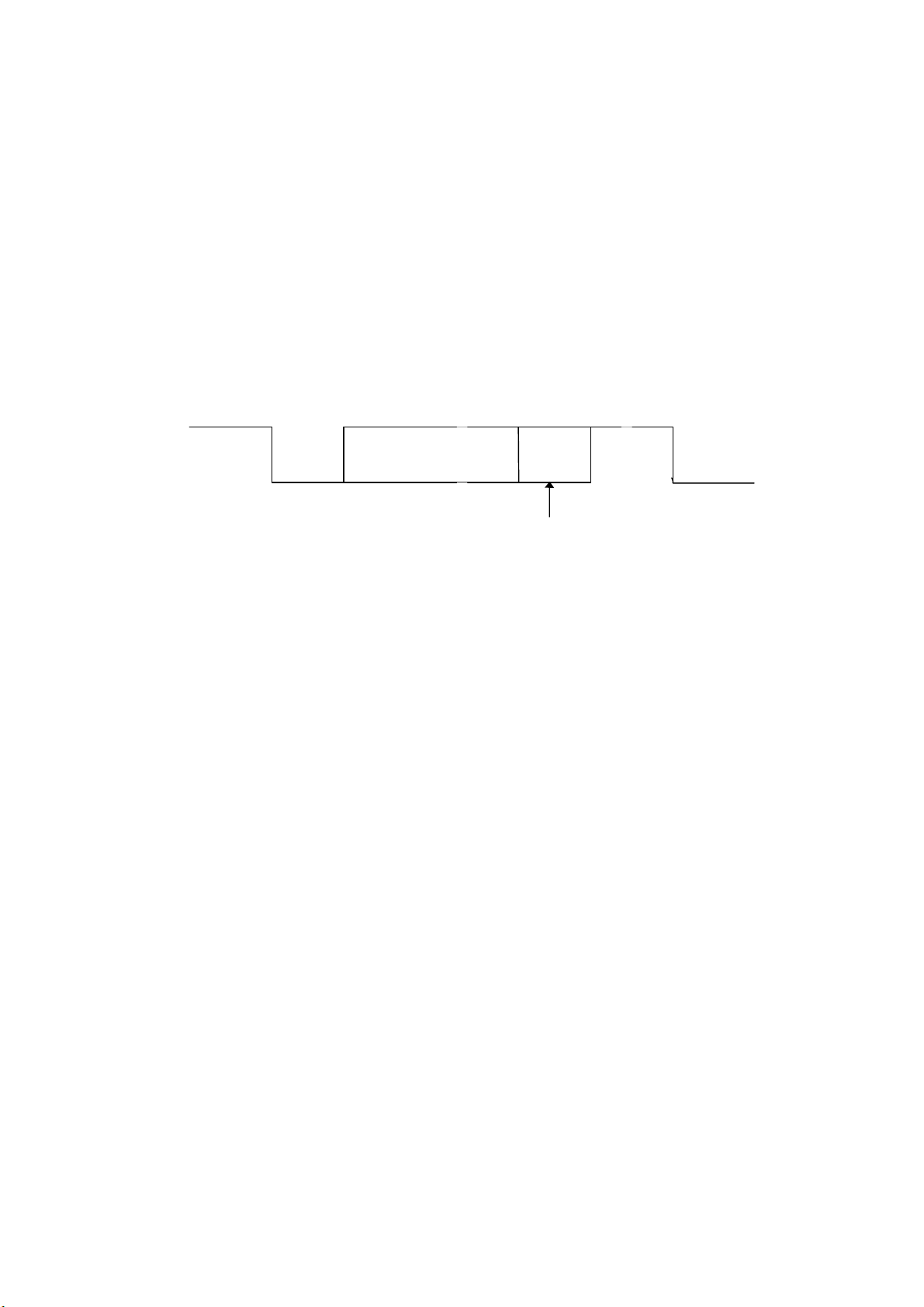

phép truyền tín hiệu với tốc ộ ến 20.000 bps nhưng nếu cáp truyền ủ ngắn có thể lên ến 115.200 bps. TxD Bit chăn Making

Các bit d ữ li ệu ượ c Start bit lẻ Stop bit làm d ấ u l ậ p trình tr ướ c Tạo ra khi ượ c l ậ p trình

Hình 5.47: Khung truyền dữ liệu bên truy ền trong chế ộ cận ồng bộ.

Các phương thức nối giữa DTE và DCE:

- Đơn công (simplex connection): dữ liệu chỉ ược truyền theo 1 hướng.

- Bán song công ( half-duplex): dữ liệu truyền theo 2 hướng, nhưng mỗi thời iểm chỉ

ược truyền theo 1 hướng.

- Song công (full-duplex): số liệu ược truyền ồng thời theo 2 hướng.

Định dạng của khung truyền dữ liệu theo chuẩn RS-232C theo chế ộ cận ồng bộ như trên hình 5.47.

Khi không truyền dữ liệu, ường truyền sẽ ở trạng thái mark ( iện áp -10V). Khi bắt

ầu truyền, DTE sẽ ưa ra xung Start (space: 10V) và sau ó lần lượt truyền từ D0 ến D7 và

Parity, cuối cùng là xung Stop (mark: -10V) ể khôi phục trạng thái ường truyền. Dạng

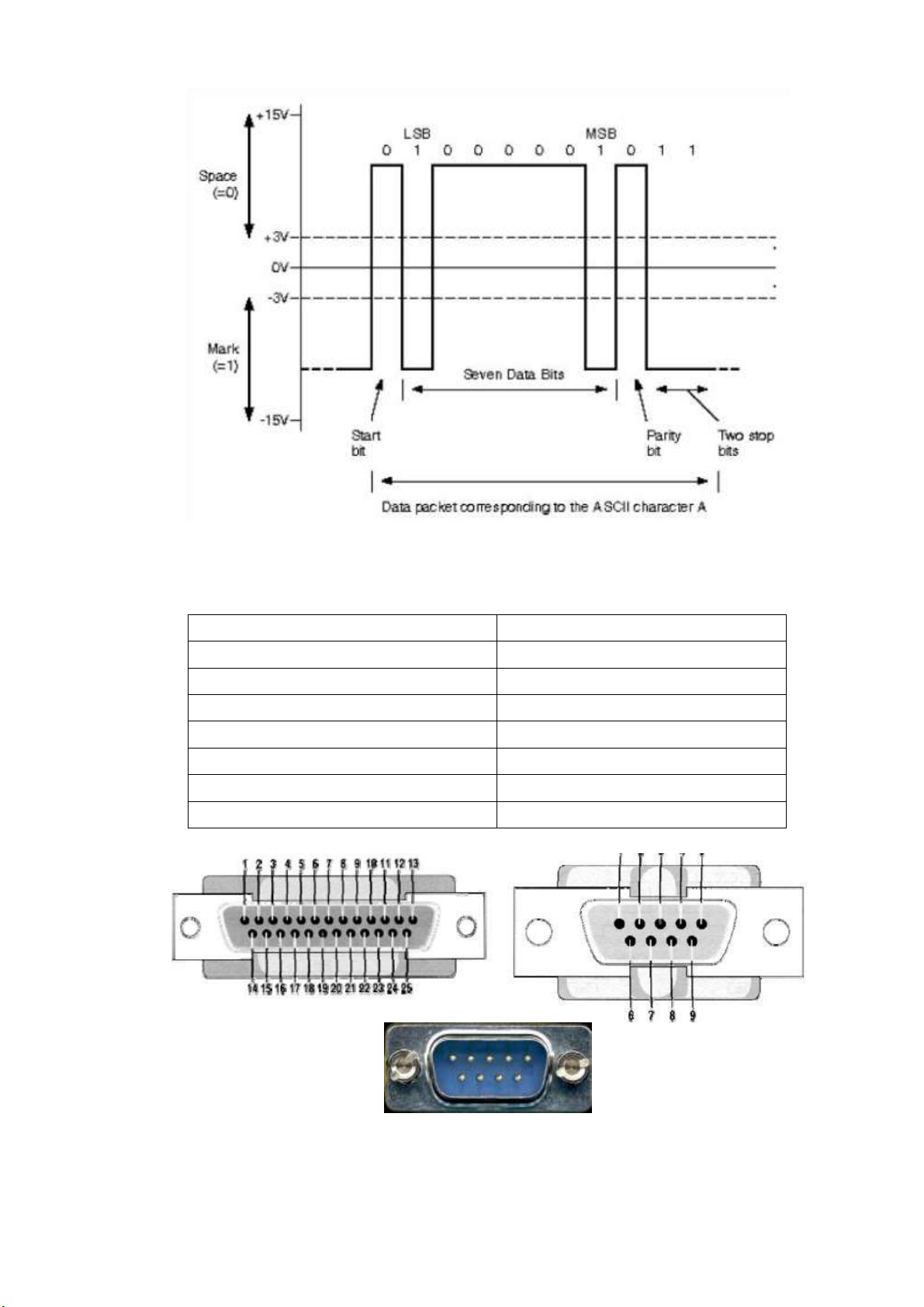

tín hiệu truyền mô tả như hình 5.48 (truyền ký tự A). Các ặc tính kỹ thuật của chuẩn RS- 232C cho trong bảng 5.21.

Đầu nối tín hiệu chuẩn RS232 có hai dạng 25 chân (DB25) và 9 chân (DB9) như mô

tả trên hình 5.49. Chức năng của các tín hiệu ược cho trong bảng 5.22. lOMoARcPSD| 10435767

Hình 5.48: Tín hiệu trên cổng RS232C khi truyền ký tự A

Bảng 5.21: Đặc tính kỹ thuật cổng RS232C Chiều dài cable cực ại 15m

Tốc ộ dữ liệu cực ại 20 Kbps

Điện áp ngõ ra cực ại ± 25V Điện áp ngõ ra có tải ± 5V ến ± 15V Trở kháng tải 3K ến 7K Điện áp ngõ vào ± 15V Độ nhạy ngõ vào ± 3V Trở kháng ngõ vào 3K ến 7K

Hình 5.49: Các loại ều nối tín hiệu theo chuẩn RS232 lOMoARcPSD| 10435767

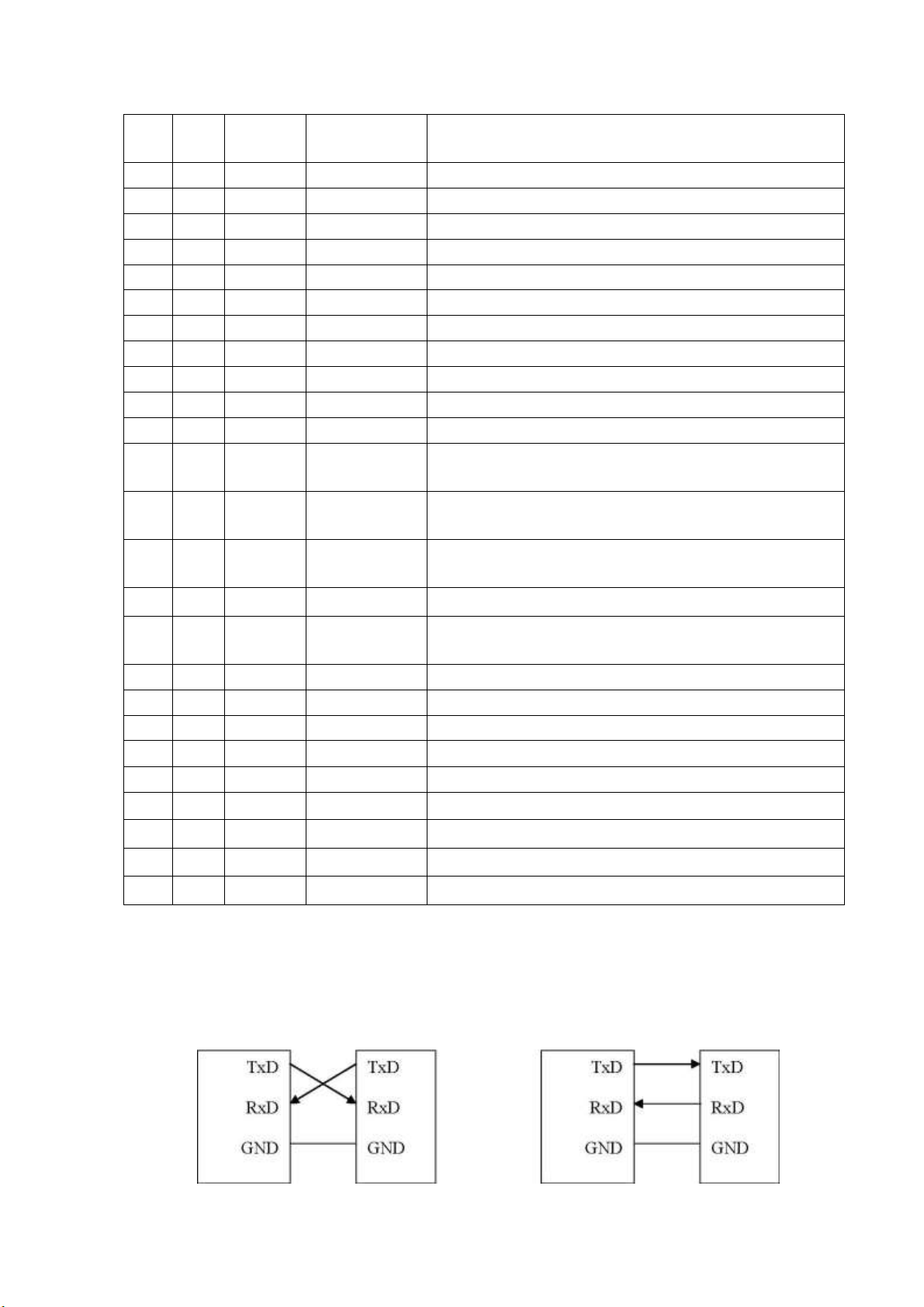

Bảng 5.22: Chức năng các tín hiệu trên cổng truyền RS232C

D25 DB9 Tín hiệu Hướng Mô tả truyền 1 - - -

Protected ground: nối ất bảo vệ 2 3 TxD

DTEDCE Transmitted data: chân truyền dữ liệu 3 2 RxD

DCEDTE Received data: chân nhận dữ liệu 4 7 RTS

DTEDCE Request to send: DTE yêu cầu truyền dữ liệu 5 8 CTS

DCEDTE Clear to send: DCE sẵn sàng nhận dữ liệu 6 6 DSR

DCEDTE Data set ready: DCE sẵn sàng làm việc 7 5 GND - Ground: nối ất (0V) 8 1 DCD

DCEDTE Data carier detect: DCE phát hiện sóng mang 20 4 DTR

DTEDCE Data terminal ready: DTE sẵn sàng làm việc 22 9 RI

DCEDTE Ring indicator: báo chuông 23 -

DSRD DCEDTE Data signal rate detector: dò tốc ộ truyền 24 - TSET

DTEDCE Transmit Signal Element Timing: tín hiệu ịnh thời truyền i từ DTE 15 - TSET

DCEDTE Transmitter Signal Element Timing: tín hiệu ịnh thời

truyền từ DCE ể truyền dữ liệu 17 - RSET

DCEDTE Receiver Signal Element Timing: tín hiệu ịnh thời

truyền từ DCE ể truyền dữ liệu 18 - LL

Local Loopback: kiểm tra cổng 21 - RL

DCEDTE Remote Loopback: Tạo ra bởi DCE khi tín hiệu nhận từ DCE lỗi 14 - STxD

DTEDCE Secondary Transmitted Data 16 - SRxD

DCEDTE Secondary Received Data 19 - SRTS

DTEDCE Secondary Request To Send 13 - SCTS

DCEDTE Secondary Clear To Send 12 -

SDSRD DCEDTE Secondary Received Line Signal Detector 25 - TM Test Mode 9 -

Dành riêng cho chế ộ test 10 -

Dành riêng cho chế ộ test 11 Không dùng

Kết nối truyền dữ liệu giữa hai thiết bị theo chuẩn RS232C có thể thực hiện theo kiểu

Null Modem, chỉ có các ường dây cho việc truyền nhận dữ liệu, không sử dụng các tín

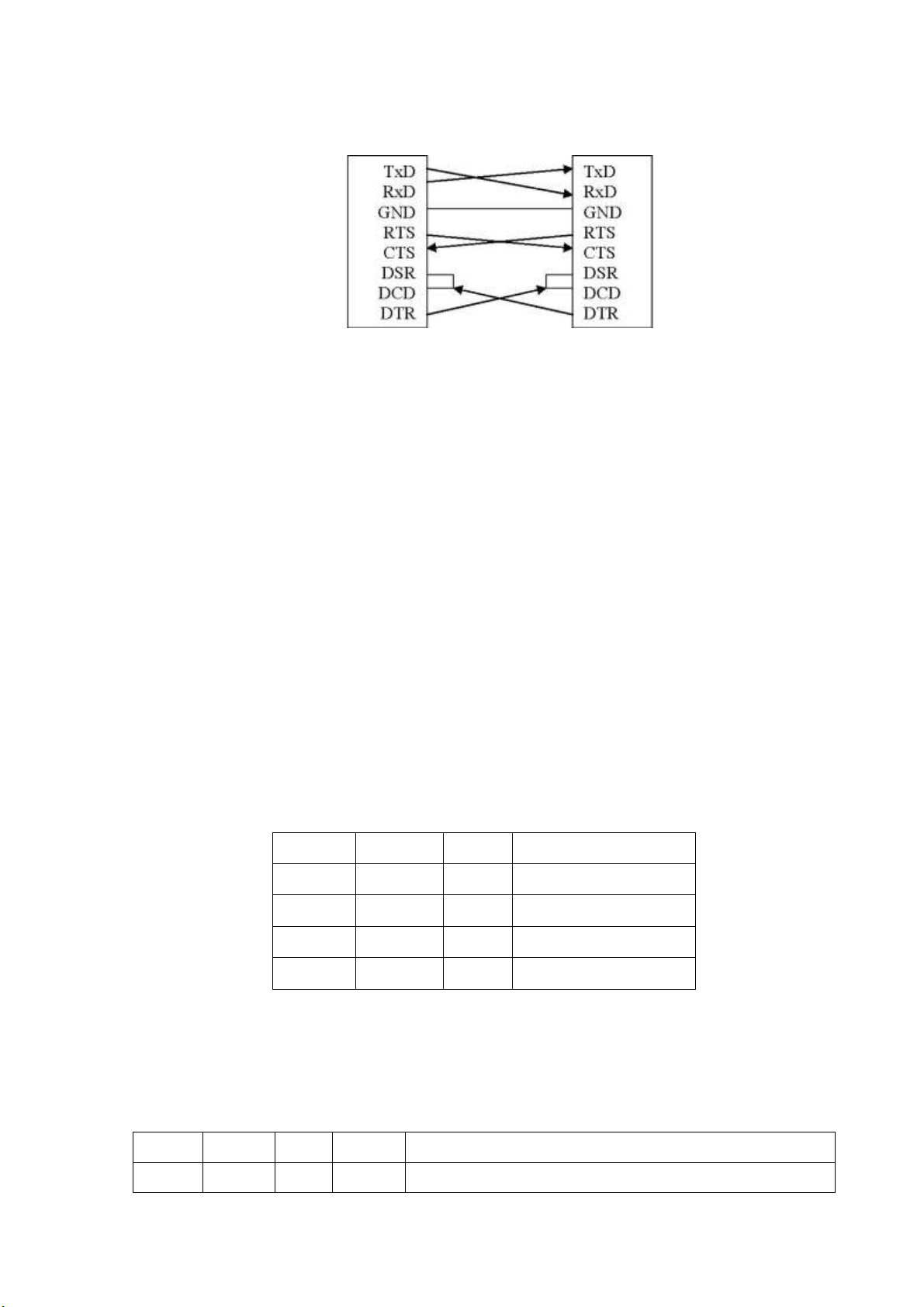

hiệu bắt tay, như trên hình 5.50. Hoặc cũng có thể kết nối có tín hiệu bắt tay như trên hình 5.51. DTE1 DTE2 DTE DCE lOMoARcPSD| 10435767

Hình 5.50: Kết nối Null Modem trên cổng RS232

Hình 5.51: Kết nối trong truyền thông nối tiếp d ùng tín hiệu bắt tay

Khi DTE1 cần truyền dữ liệu thì cho DTR tích cực tác ộng lên DSR của DTE2

cho biết sẵn sàng nhận dữ liệu và cho biết ã nhận ược sóng mang của MODEM (ảo). Sau

ó, DTE1 tích cực chân RTS ể tác ộng ến chân CTS của DTE2 cho biết DTE1 có thểnhận

dữ liệu. Khi thực hiện kết nối giữa DTE và DCE, do tốc ộ truyền khác nhau nên phải

thực hiện iều khiển lưu lượng. Quá trinh iều khiển này có thể thực hiện bằng phần mềm

hay phần cứng. Quá trình iều khiển bằng phần mềm thực hiện bằng hai ký tự Xon và

Xoff. Ký tự Xon ược DCE gởi i khi rảnh (có thể nhận dữ liệu). Nếu DCE bận thì sẽ gởi

ký tựXoff. Quá trình iều khiển bằng phần cứng dùng hai chân RTS và CTS. Nếu DTE

muốn truyền dữ liệu thì sẽ gởi RTS ể yêu cầu truyền, DCE nếu có khả năng nhận dữ liệu

( ang rảnh) thì gởi lại CTS.

5.2.3 Cổng RS-232 máy tính

Các cổng nối tiếp trong máy tính ược ánh số là COM1, COM2, COM3, COM4 với

các ịa chỉ như trong bảng 5.22.

Bảng 5.22: Địa chỉ các cổng nối tiếp trong máy tính Tên

Địa chỉ Ngắt Vị trí chứa ịa chỉ COM1 3F8h 4 0000h:0400h COM2 2F8h 3 0000h:0402h COM3 3E8h 4 0000h:0404h COM4 2E8h 3 0000h:0406h

Giao tiếp cổng nối tiếp trong máy tính sử dụng vi mạch UART với các thanh ghi

cho trong bảng 5.23. Các thanh ghi này có thể truy xuất trực tiếp kết hợp với ịa chỉ cổng

(ví dụ như thanh ghi cho phép ngắt của COM1 có ịa chỉ là BACOM1 + 1 = 3F9h.

Bảng: 5.23: Các thanh ghi UART cổng nối tiếp

Offset DLAB R/W Tên Chức năng 0 W

THR Transmitter Holding Register ( ệm truyền) lOMoARcPSD| 10435767 0 0 R

RBR Receiver Buffer Register ( ệm thu) 1

R/W BRDL Baud Rate Divisor Latch (số chia byte thấp) 0

R/W IER Interrupt Enable Register (cho phép ngắt) 1 1 R/W BRDH Số chia byte cao R

IIR Interrupt Identification Register (nhận dạng ngắt) 2 W

FCR FIFO Control Register – iều khiển FIFO 3

R/W LCR Line Control Register ( iều khiển ường dây) 4

R/W MCR Modem Control Register ( iều khiển MODEM) 5 R

LSR Line Status Register (trạng thái ường dây) 6 R

MSR Modem Status Register (trạng thái MODEM) 7 R/W

Scratch Register (thanh ghi tạm)

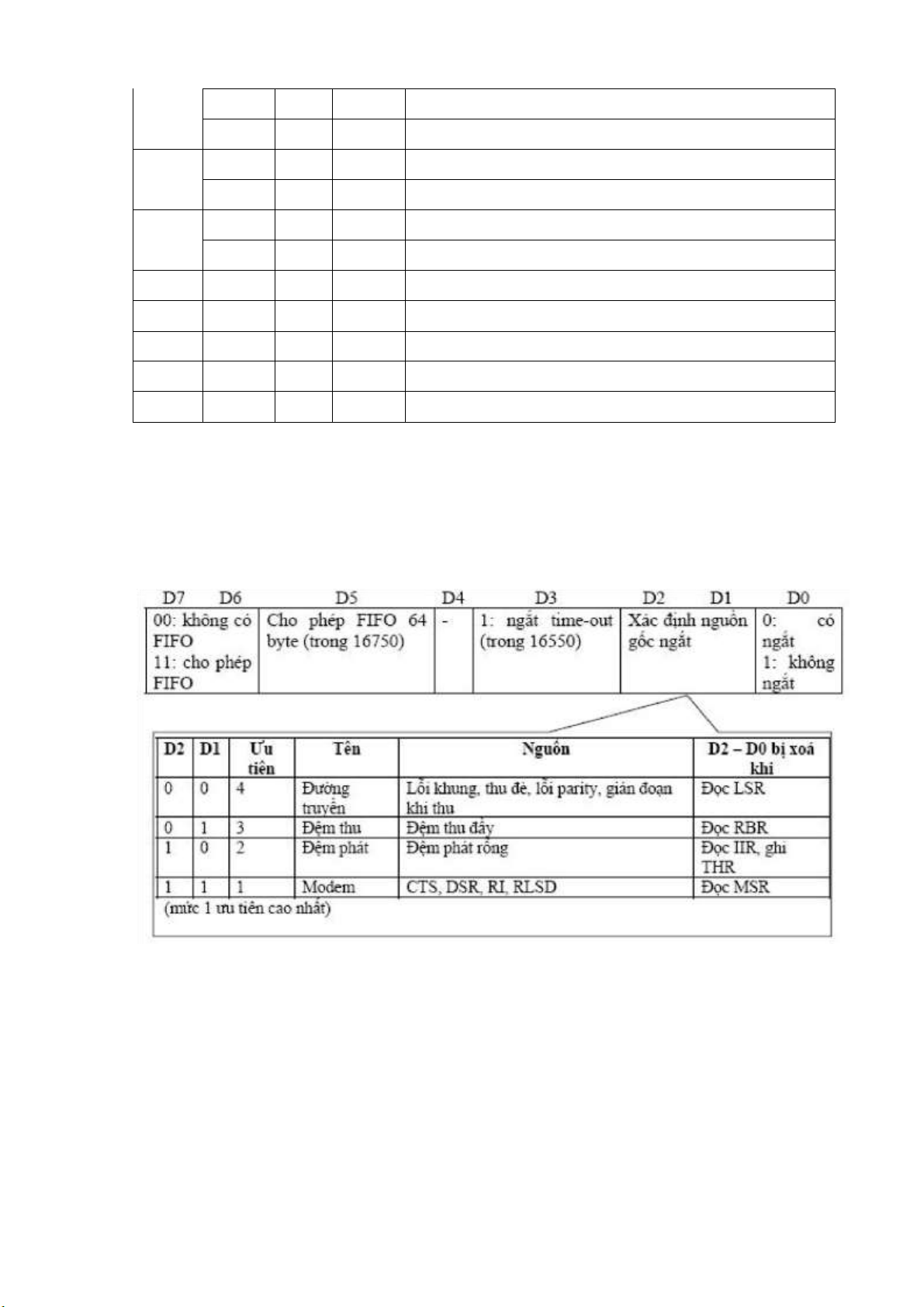

Thanh ghi IIR (Interrupt Identification): IIR xác ịnh mức ưu tiên và nguồn gốc của

yêu cầu ngắt mà UART ang chờ phục vụ. Khi cần xử lý ngắt, CPU thực hiện ọc các bit

tương ứng ể xác ịnh nguồn gốc của ngắt. chức năng các bit của IIR như hình 5.52.

Hình 5.52: Chức năng các bit thanh ghi IIR

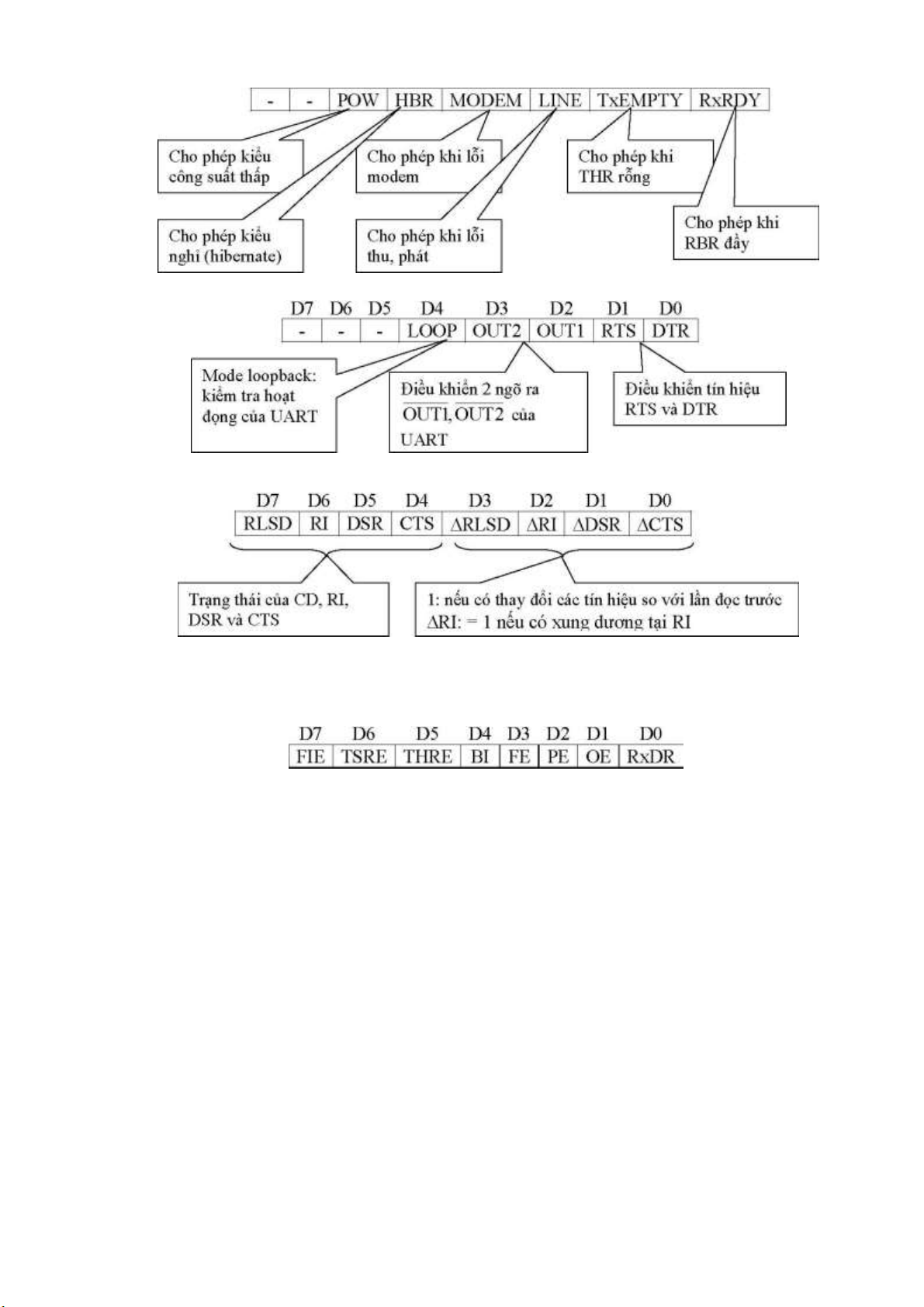

Chức năng của các bit trong các thanh ghi: thanh ghi cho phép ngắt IER (Interrupt

Enable Register), thanh ghi iều khiển modem MCR (Modem Control Register), thanh

ghi trạng thái modem MSR ( Modem Status Register) như mô tả trên hình 5.53. Thanh ghi IER lOMoARcPSD| 10435767

MCR (Modem Control Register)

MSR (Modem Status Register)

Hình 5.53: Chức năng các bit của các thanh ghi IER, MCR, MSR Hình 5.54: Thanh ghi LSR

Thanh ghi thông báo trạng thái ường truyền LSR (Line Status Register): có các bit

như trên hình 5.54. Chức năng các bit như sau:

- FIE: FIFO Error – sai trong FIFO.

- TSRE: Transmitter Shift Register Empty – thanh ghi dịch rỗng (=1 khi ã phát 1 ký

tự và bị xoá khi có 1 ký tự chuyển ến từ THR.

- THRE: Transmitter Holding Register Empty (=1 khi có 1 ký tự ã chuyển từ THR –

TSR và bị xoá khi CPU ưa ký tự tới THR).

- BI: Break Interrupt (=1 khicó sự gián oạn khi truyền, nghĩa là tồn tại mức logic 0

trong khoảng thời gian dài hơn khoảng thời gian truyền 1 byte và bị xoá khi CPU ọc LSR).

- FE: Frame Error (=1 khi có lỗi khung truyền và bị xoá khi CPU ọc LSR).

- PE: Parity Error (=1 khi có lỗi parity và bị xoá khi CPU ọc LSR). lOMoARcPSD| 10435767

- OE: Overrun Error (=1 khi có lỗi thu è, nghĩa là CPU không ọc kịp dữ liệu làm cho

quá trình ghi chồng lên RBR xảy ra và bị xoá khi CPU ọc LSR).

- RxDR: Receiver Data Ready (=1 khi ã nhận 1 ký tự và ưa vào RBR và bị xoá khi CPU ọc RBR).

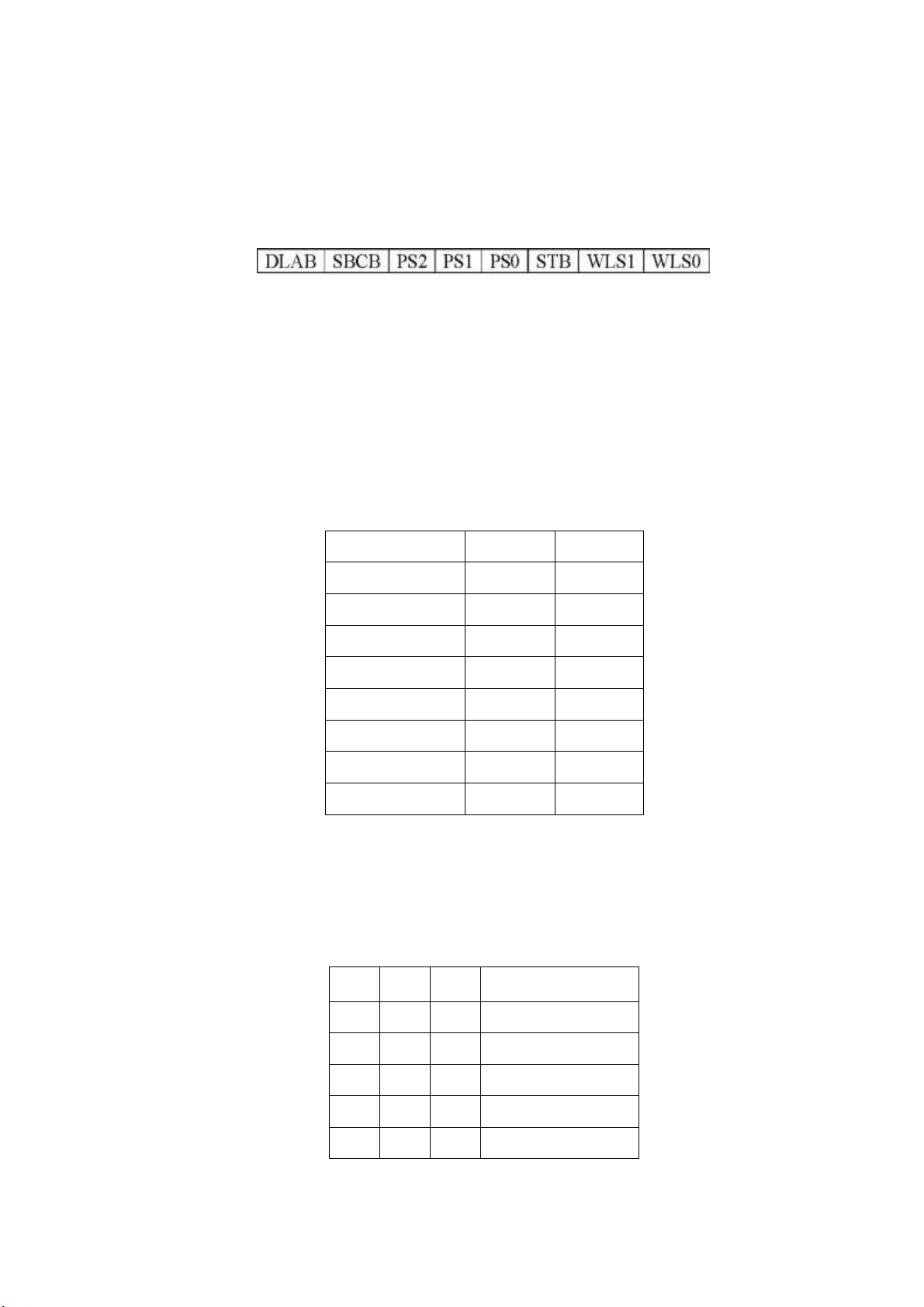

Thanh ghi iều khiển ường truyền LCR (Line Control Register) có các bit sau:

- DLAB (Divisor Latch Access Bit) = 0: truy xuất RBR, THR, IER, = 1 cho phép ặt

bộ chia tần trong UART ể cho phép ạt tốc ộ truyền mong muốn.

- UART dùng dao ộng thạch anh với tần số 1.8432 MHz ưa qua bộ chia 16 thành tần

số 115,200 Hz. Khi ó, tuỳ theo giá trị trong BRDL và BRDH, ta sẽ có tốc ộ mong

muốn. Ví dụ như ường truyền có tốc ộ truyền 2,400 bps có giá trị chia

115,200 / 2,400 = 48d = 0030h BRDL = 30h, BRDH = 00h. Một

số giá trị thông dụng xác ịnh tốc ộ truyền cho như sau: Tốc ộ (bps) BRDH BRDL 1,200 00h 60h 2,400 00h 30h 4,800 00h 18h 9,600 00h 0Ch 19,200 00h 06h 38,400 00h 03h 57,600 00h 02h 115,200 00h 01h

- SBCB (Set Break Control Bit) =1: cho phép truyền tín hiệu Break (=0) trong khoảng

thời gian lớn hơn một khung. - PS (Parity Select):

PS2 PS1 PS0 Mô tả X X 0 Không kiểm tra 0 0 1 Kiểm tra lẻ 0 1 1 Kiểm tra chẵn 1 0 1 Parity là mark 1 1 1 Parity là space lOMoARcPSD| 10435767

- STB (Stop Bit) = 0: 1 bit stop, =1: 1.5 bit stop (khi dùng 5 bit dữ liệu) hay 2 bit stop

(khi dùng 6, 7, 8 bit dữ liệu). - WLS (Word Length Select):

WLS1 WLS0 Độ dài dữ liệu 0 0 5 bit 0 1 6 bit 1 0 7 bit 1 1 8 bit lOMoARcPSD| 10435767

Hình 5.55: Các mạch chuyển mức giao tiếp TTL và RS232C Cổng nối tiếp máy

tính ược thực hiện theo chuẩn RS232C nên có mức tín hiệu khác với các hệ thống vi xử

lý bên ngoài (thông thường các hệ thống CPU chạy với mức logic TTL (0 – 5Volt). Vì

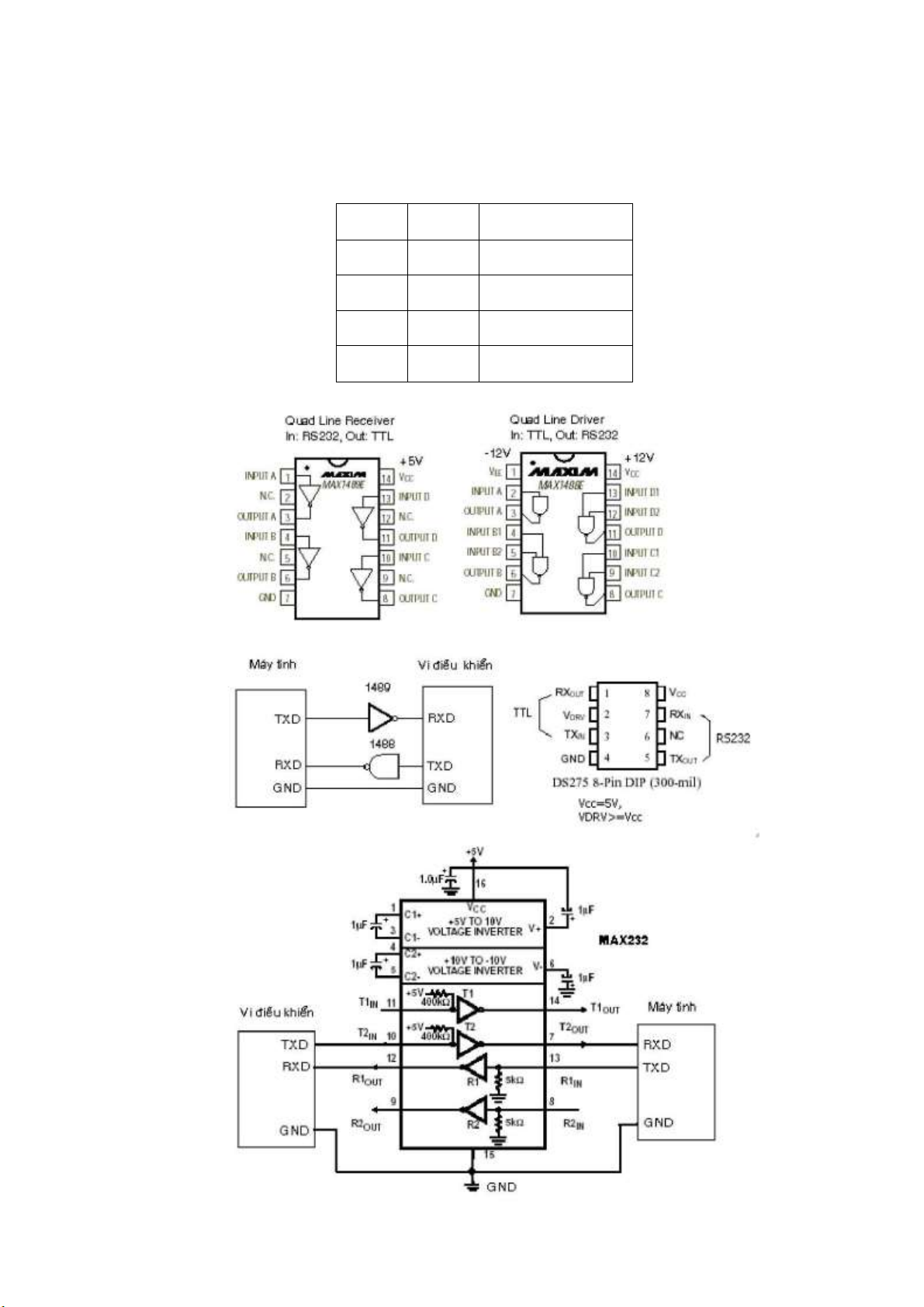

vậy, cần các vi mạch tương thích mức iện áp cho việc giao tiếp này. Các vi mạch thường

dùng là cặp MC1488-MC1489, MAX232 (Maxim) hoặc DS275 (Dallas), hình 5.55.

Loại MAX232 thông dụng hơn cả vì chỉ cần nguồn 5V, nguồn ±10V do mạch dao ộng 16KHz bên trong cung cấp.

Chuẩn RS 232 dùng ường truyền không cân bằng vì các tín hiệu ều lấy iểm chuẩn là

ường mass chung, bị ảnh hưởng của nhiễu tác ộng, do ó tốc ộ truyền và khoảng cách

truyền bị giới hạn. Khi cần tăng khoảng cách và tốc ộ truyền, phương pháp truyền hai

dây vi sai trở nên hữu hiệu hơn vì hai dây có ặc tính giống nhau, tín hiệu truyền i là hiệu

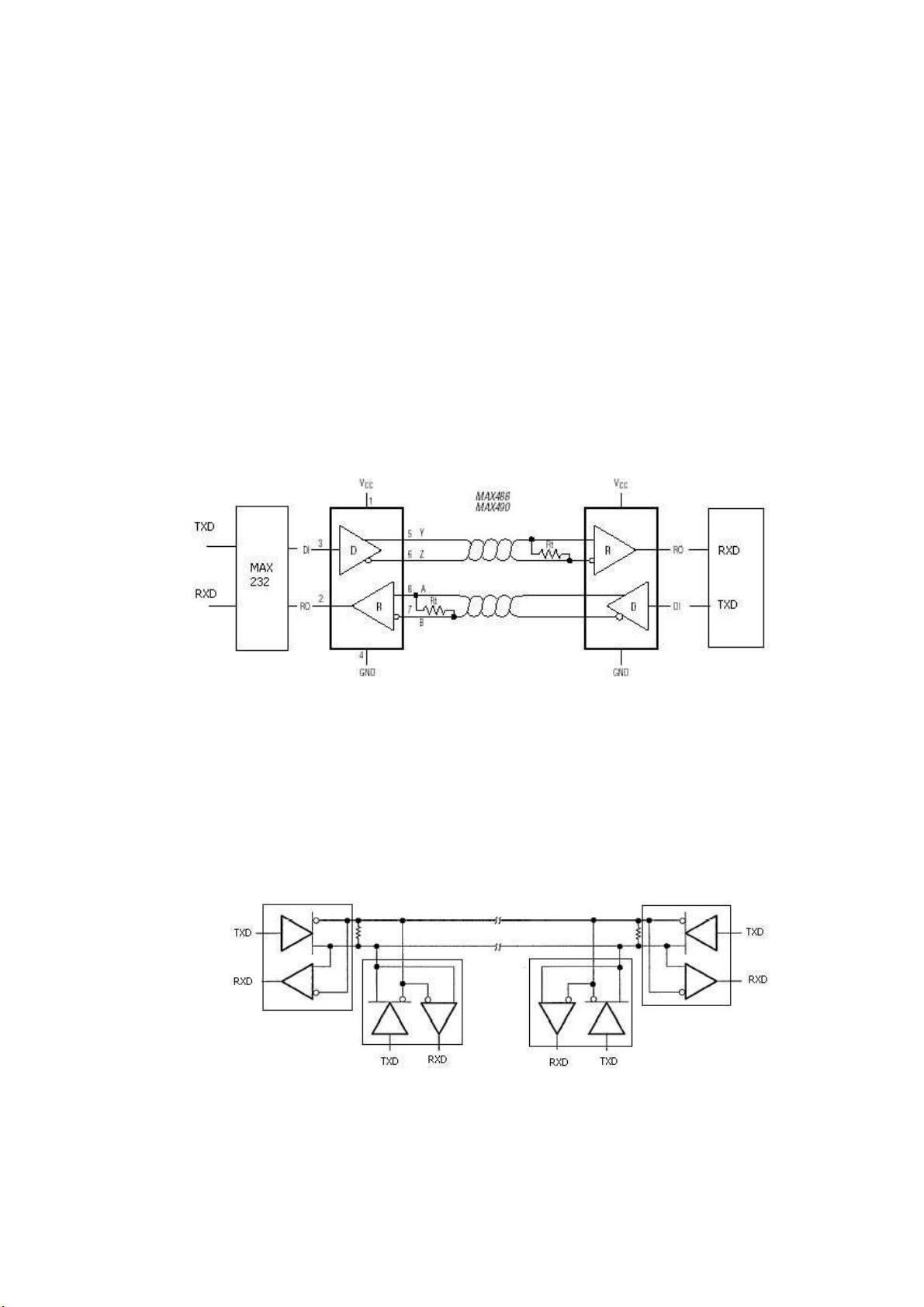

số iện áp giữa hai dây, do ó loại trừ ược nhiễu chung. Hai chuẩn thường dùng là RS422

và RS485. Tuy nhiên chuẩn RS422 ít thông dụng hơn RS485.

Hình 5.56: Ghép nối truyền nhận nối tiếp vi sai RS422

Chuẩn RS422 dùng 4 dây do ó cho phép truyền song công, tức là cùng lúc có thể

thu phát. Tín hiệu từ máy tính theo chuẩn RS 232 có mức iện áp ±15V phải ổi sang mức

TTL 0 - 5V dùng vi mạch MAX232, sau ó tín hiệu ơn ược ổi sang tín hiệu vi sai dùng

vi mạch MAX485 (488, 489, 490, 491). Điện áp vi sai phải lớn hơn 200mV. Nếu VAB >

200mV ta coi như trị logic 1 ược truyền còn nếu VAB <− 200mV thì trị logic 0 ược truyền.

Hình 5.56 mô tả kết nối trên ường truyền RS422.

Hình 5.57: Cấu trúc mạng truyền nối tiếp RS485

Chuẩn RS422 không cho phép có hơn hai thiết bị truyền nhận tin trên ường dây. Với

chuẩn RS485 ta có thể nối 32 thiết bị thu phát trên hai dây có khoảng cách tối a 1200m lOMoARcPSD| 10435767

và vận tốc truyền ến 10Mbit/s. Hai iện trở kết thúc 120 Ohm ược nối với hai ầu xa nhất

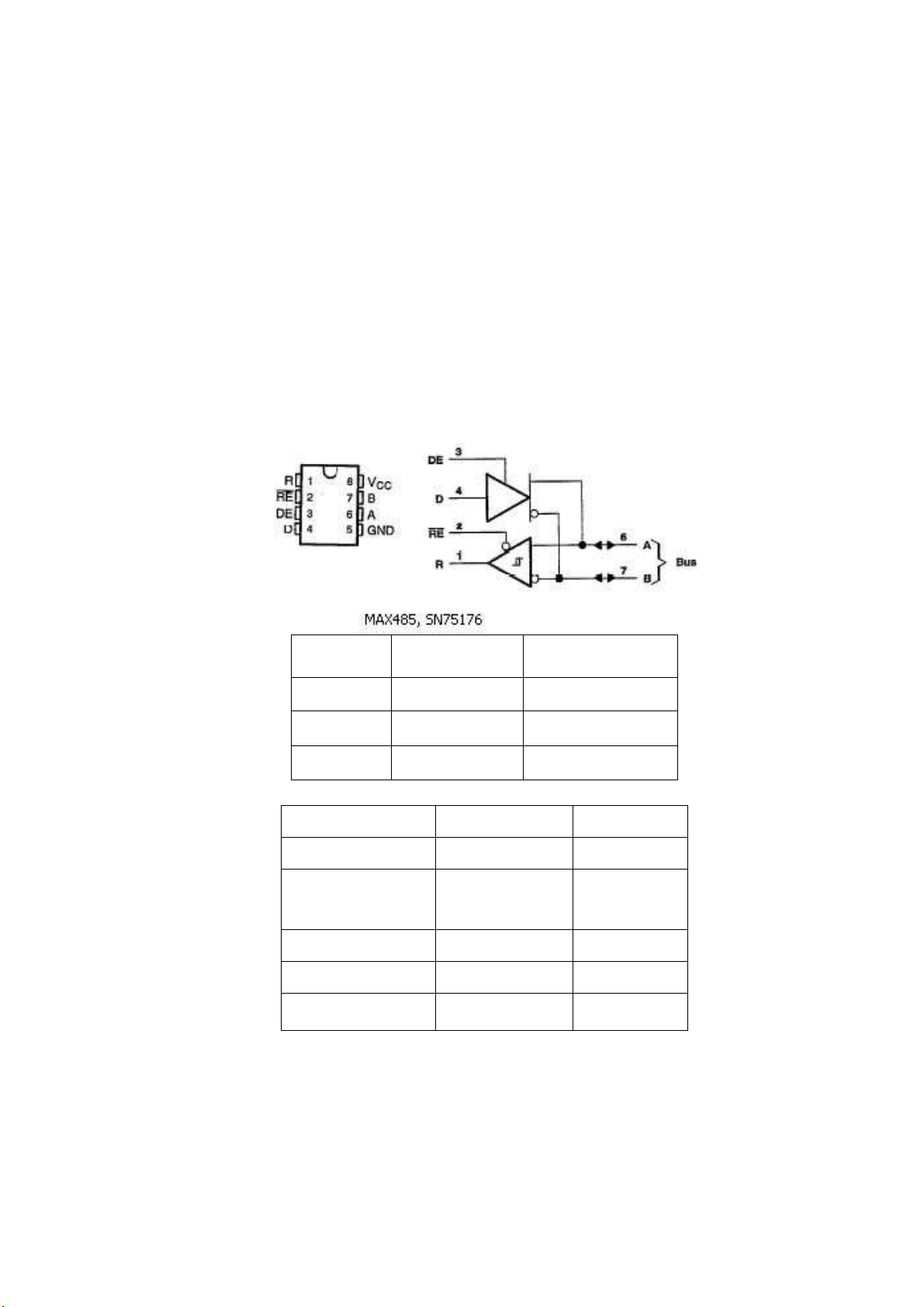

của mạng, dây dẫn là loại dây xoắn ôi 26AWG. Chuẩn này dùng vi mạch lái SN75176

hay họ Maxim MAX481, 483, 485 , 487, 488, 489, 490, 1487. Tiêu biểu là vi mạch

MAX485 chuyển ổi từ tín hiệu ơn sang tín hiệu vi sai, có chân iều khiển cho ngõ ra vi

mạch ở tổng trở cao, nhờ vậy có thể nối chung nhiều vi mạch lái với nhau. Hình 5.57

mô tả mạng truyền dữ liệu nối tiếp kết nối theo chuẩn RS 485.

MAX485 gồm bộ lái và bộ thu, tín hiệu vào bộ lái D logic TTL ổi thành hai tín hiệu

A và B, khi tín hiệu iều khiển DE mức thấp thì hai chân AB cách ly với vi mạch. Tín

hiệu vào bộ thu là A và B, tín hiệụ ra R logic TTL tùy thuộc hiệu iện áp giữa A và B,

khi /RE logic 1 thì R cách ly với vi mạch. Hình 5.58 mô tả cấu trúc và các ặc tính kỹ

thuật của IC Max485 và SN75176. Input D Control DE OUTPUT A B H H H L L H L H X L Z Z VID=VA-VB Control /RE Output R VID≥ 0.2 V L H -- 0.2V≤VID≤0.2V L ? VID≤-0.2V L L X H Z Ngo vã ̀o hở L H

Hình 5.58: Cấu tạo và hoạt ộng vi mạch truyền nối tiếp RS485 5.2.4 Modem

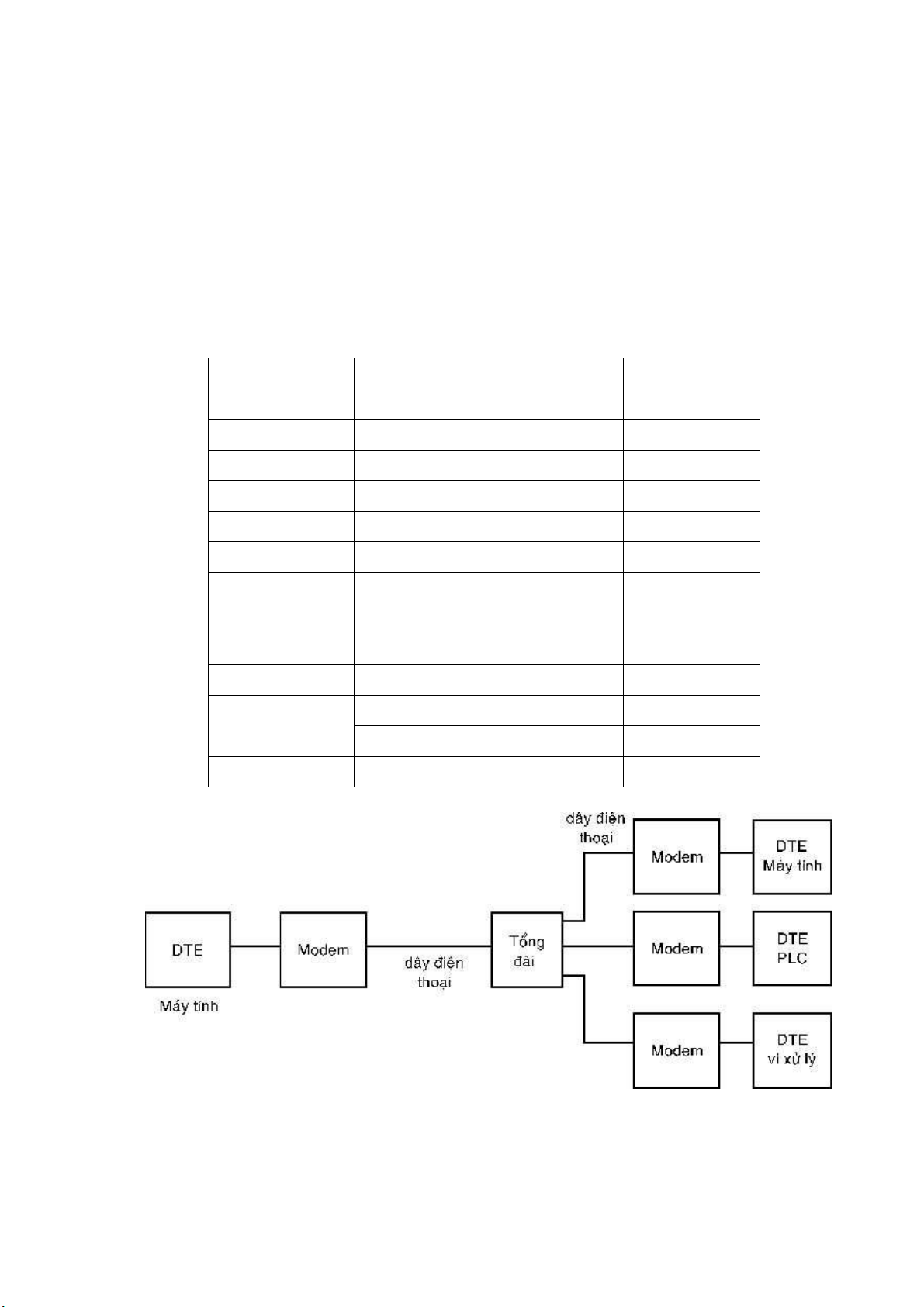

Modem (modulator + demodulator) cho phép ghép nối hai DTE qua khoảng cách

nhờ ường dây iện thoại công cộng có sẵn hay ường dây iện thoại riêng. Tín hiệu số từ lOMoARcPSD| 10435767

DTE dùng ể iều chế sóng mang rồi truyền i, ở nơi thu sóng mang ược giải iều chế rồi ổi

lại thành tín hiệu số ưa vào DTE.

Ngoài việc truyền tín hiệu số thông qua modem còn có thể trao ổi thoại, fax,

videophone. Modem (xuất hiện từ thập niên 60) chia làm hai loại là: modem trong và

modem ngoài. Modem trong, ược cắm vào slot PCI của máy tính và thường ược gắn ịa

chỉ là COM3 hay COM4, vận tốc truyền tối a 56kbps, có giá rẻ hơn. Modem ngoài

ghép với máy tính qua ường cáp 25 – 9, 9 – 9 hay 25 – 25, tín hiệu ược truyền theo

chuẩn RS 232 (± 12V) hoặc USB.

Bảng 5.23 Các tín hiệu giao tiếp của modem DTE 9 chân DTE 25 chân DCE Modem 1 FG 1 FG 3 2 TD → 2 TD 2 3 RD ← 3 RD 7 4 RTS → 4 RTS 8 5 CTS ← 5 CTS 6 6 DSR ← 6 DSR 5 7 SG 7 SG 1 8 DCD ← 8 DCD 4 20 DTR → 20 DTR 9 22 RI ← 22 RI Truyền ồng 15 TXCLK ← 15 TXCLK bộ 17 RXCLK ← 17 RXCLK 24 XTCLK → 24 XTCLK

Hình 5.59: Truyền dữ liệu trên ường iện thoại bằng modem

Hai modem kết nối với nhau thông qua quay số và tổng ài iện thoại sẽ thực hiện kết

nối. Cấu trúc kết nối truyền dữ bằng modem qua ường iện thoại ược mô tả trên hình lOMoARcPSD| 10435767

5.59. Việc trao ổi dữ liệu giữa máy tính và modem thực hiện theo cơ chế bắt tay phần cứng hay phần mềm.

- Bắt tay phần cứng: DTE muốn truyền dữ liệu liên quan DCE thì cho RTS = H và chờ

CTS trả lời modem. Ngược lại modem muốn truyền dữ liệu thì cho DSR = H và chờ

DTR. Khi DTE là vi iều khiển có thể cho RTS và DTR của modem ở mức cao hoặc

iều khiển các chân này qua cổng nhập xuất I/0.

- Bắt tay phần mềm: dùng hai ký tự XON (CtrlS) (transmitter ON) và XOFF (CtrlQ)

(transmitter off) ể bắt ầu truyền hay ngưng truyền dữ liệu. Dùng phương pháp này có

thể gây ra sai lầm khi dữ liệu trùng với XON hay XOFF.

Do ường dây iện thoại công cộng chủ yếu dùng cho iện thoại nên tần số giới hạn

3300Hz, iều này làm hạn chế vận tốc truyền dữ liệu (ịnh lý Shannon) do ó các hãng sản

xuất modem phải tìm cách nâng cao tốc ộ truyền và ộ tin cậy thông tin bằng các phương

pháp iều chế, nén tín hiệu và sửa sai. Hiện nay tốc ộ tối a là

56kbps trên lý thuyết, còn thông thường sử dụng modem ngoài tốc ộ là 33,6kbps.

Modem có thể thực hiệc các giải pháp iều chế như:

- Điều biên AM: mức 0 và 1 ược biểu thị bằng hai iện áp khác nhau của sóng mang. -

Điều tần FM: dùng hai tần số khác nhau 1070 Hz cho logic 0 và 1270 Hz cho logic 1

ở một chiều, còn chiều ngược lại theo thứ tự là 2025 Hz và 2225 Hz. Hai dải tần số

khác nhau nên modem hoạt ộng song công trên một ường dây.

- Điều pha PM: sóng mang có tần số cố ịnh nhưng dùng pha 0 và pha 180° ể biểu thị logic.

- Điều chế TCM (Trellis Coded Modulation): kết hợp iều pha và iều biên.

Có các tổ chức quốc tế về tiêu chuẩn truyền thông như ITU (International

TeleCommunications Union) của Liên Hiệp Quốc, ISO (International Standards

Organization) và CCITT (International Telegraph and Telephone Consultative Committee) thuộc ITU.

Các tổ chức này ịnh ra các chuẩn về modem ký hiệu V.XX. Bảng 5.24 là các chuẩn gần nhất:

Bảng 5.24 Các chuẩn modem Điều chế Chuẩn Năm Vận tốc QAM V 32 1984 9600 TCM V 32 bis 1991 14400 TCM V 32 Ter 19200 TCM V 34 1994 28800 TCM V 90 1998 56000

Để tăng vận tốc truyền, modem dùng phương pháp nén dữ liệu, ví dụ như phương

pháp mã Huffman, ký tự thường truyền ược mã hóa ít bit hơn các ký tự khác hay phương lOMoARcPSD| 10435767

pháp run length coding thay một loạt bit giống nhau bằng bit ó và số lần lặp. Tỷ số nén

có thể lên ến 4: 1 hay 2: 1 tùy thuộc loại dữ liệu.

Các giao thức phổ biến là MNP (Microcom Networking Protocol) V.42 bis với

LAPM (Link Access Protocol for Modems). Khi truyền file cần phải tuân thủ các qui

ịnh của giao thức truyền FTP (File Transfer Protocol).

XMODEM chia tập tin thành khối 128 byte, mỗi khối ược kèm tổng kiểm tra hay CRC

(cyclic redundancy check) 4 byte . YMODEM dùng khối 1024 byte. ZMODEM dùng

khối kích thước thay ổi tùy theo trạng thái ường truyền. Trong trường hợp dùng máy

tính o lường iều khiển có thể dùng các giao thức khác

Khi thực hiện kết nối, ầu tiên DTE gởi lệnh kiểm tra ến modem xem có liên lạc ược

không, sau ó gởi lệnh quay số, modem sẽ quay số iện thoại nơi cần kết nối, nếu kết nối

ược sẽ báo cho DTE ể truyền dữ liệu, ầu tiên modem sẽ truyền với vận tốc cao nhất có

thể có, nếu không trao ổi thông tin ược nó sẽ chuyển sang vận tốc truyền thấp hơn hay

giao thức khác, quá trình tiếp tục cho ến khi kết nối ược hay không có khả năng kết nối, hết thời gian.

Tập lệnh modem, thường gọi là tập lệnh Hayes (do hãng chế tạo modem Hayes

Micro Computer Products ề nghị), còn gọi là tập lệnh AT vì bắt ầu mỗi lệnh bằng ký tự

chú ý AT (attention) . Thông qua tập lệnh, DTE có thể iều khiển modem và nhận thông

tin từ nó. Trong modem có một số thanh ghi gọi là thanh ghi S, cho phép DTE thay ổi cấu hình modem.

Lệnh AT luôn luôn khởi ầu bằng AT và gồm một hay nhiều lệnh kế tiếp nhau kết

thúc bằng Enter ( mã ASCII 13); chiều dài chuỗi lệnh không quá 40 hay 64 ký tự, tùy loại modem.

Lệnh +++ và A/ không cần khởi ầu bằng AT và không cần phím enter. Với máy

tính, muốn kiểm tra modem có thể dùng tiện ích hyperterminal của Windows 9X. Trên

màn hình sẽ xuất hiện khung soạn thảo và ta có thể ánh lệnh ến modem, nhận trả lời từ