Preview text:

TRƯỜNG ĐẠI HỌC VĂN LANG

KHOA KỸ THUẬT – CƠ ĐIỆN – MÁY TÍNH TIỂU LUẬN CUỐI KỲ

THÍ NGHIỆM ĐIỆN TỬ SỐ Students Nguyễn Văn Trung 207KN29979 : Mentor: Thầy Lê Nguyễn Hòa Bình 2 HO CHI MINH CITY, 2023 ĐỀ BÀI:

1. Tìm hiểu lịch sử, cấu trúc của chương trình của ngôn ngữ VHDL dùng trong kỹ

thuật số. Vận dụng ngôn ngữ lập trình VHDL của các mạch số cơ bản viết cổng

AND , cổng OR , NAND, NOR 3 ngõ vào.

2. Tìm hiểu mạch tổ hợp: mạch cộng, mạch mã hóa, mạch giải mã, mạch dồn kênh và mạch ghép kênh.

3. Tìm hiểu về cấu trúc máy tính và hệ điều hành. Lời nói đầu

Kính thưa thầy. Trong suốt quá trình học kỳ, em đã có cơ hội nắm bắt và áp dụng kiến

thức lý thuyết vào thực tế thông qua các thí nghiệm điện tử số.

Qua quá trình nghiên cứu và thực hiện thí nghiệm, em đã có được cái nhìn sâu sắc hơn

về cách các mạch số hoạt động và ứng dụng của chúng trong thế giới thực.

Em đã đặt ra câu hỏi nghiên cứu và thực hiện thí nghiệm để trả lời chúng, với mong

muốn đóng góp một phần nhỏ vào sự hiểu biết chung về lĩnh vực này.

Hy vọng rằng thông qua bài tiểu luận này, em đã trình bày một cách rõ ràng và chân

thực về kết quả của mình. em mong nhận được ý kiến đóng góp và phản hồi xây dựng

từ quý thầy để từ đó còn học hỏi và hoàn thiện hơn trong tương lai. Xin chân thành cảm ơn! 3 Mục lục 1.

Tìm hiểu lịch sử, cấu trúc của chương trình của ngôn ngữ VHDL dùng trong

kỹ thuật số. Vận dụng ngôn ngữ lập trình VHDL của các mạch số cơ bản viết

cổng AND , cổng OR , NAND, NOR 3 ngõ vào..........................................................4 1.1

Lịch sử.............................................................................................................. 4 1.2

Cấu trúc............................................................................................................4 1.3

Vận dụng ngôn ngữ lập trình VHDL của các mạch số cơ bản viết cổng AND ,

cổng OR , NAND, NOR 3 ngõ vào............................................................................7

1.3.1 Cổng AND.................................................................................................7

1.3.2 Cổng OR....................................................................................................8

1.3.3 Cổng NAND..............................................................................................8

1.3.4 Cổng NOR 3 ngõ vào.................................................................................9 2.

Tìm hiểu mạch tổ hợp: mạch cộng, mạch mã hóa, mạch giải mã, mạch dồn

kênh và mạch ghép kênh...........................................................................................10 2.1

mạch cộng......................................................................................................10

2.1.1 Mạch Cộng Đơn (Half Adder):................................................................10

2.1.2 Mạch Cộng Đầy Đủ (Full Adder):...........................................................10

2.1.3 Carry-Lookahead Adder..........................................................................11 2.2

MẠCH MÃ HÓA...........................................................................................12 2.3

Mạch giải mã..................................................................................................13 2.4

Mạch dồn kênh...............................................................................................14 2.5

Mạch ghép kênh.............................................................................................15 3.

Tìm hiểu về cấu trúc máy tính và hệ điều hành...............................................16 3.1

Các thành phần cơ bản của máy tính..............................................................16 3.2

Hệ điều hành...................................................................................................18 4 TRÌNH BÀY:

1. TÌM HIỂU LỊCH SỬ, CẤU TRÚC CỦA CHƯƠNG TRÌNH CỦA NGÔN

NGỮ VHDL DÙNG TRONG KỸ THUẬT SỐ. VẬN DỤNG NGÔN NGỮ

LẬP TRÌNH VHDL CỦA CÁC MẠCH SỐ CƠ BẢN VIẾT CỔNG AND ,

CỔNG OR , NAND, NOR 3 NGÕ VÀO. 1.1 LỊCH SỬ

Vào năm 1983, VHDL được khai triển theo yêu cầu của Bộ Quốc phòng Hoa Kỳ để

ghi lại hành vi của các mạch ASIC mà các công ty cung cấp linh kiện đang dùng trong

thiết bị của họ. Chuẩn MIL-STD-454N, Yêu cầu 64, Mục 4.5.1 "Ghi chép về ASIC

bằng VHDL" có chỉ định rõ yêu cầu ghi chép tư liệu của "Các thiết bị Vi điện tử" bằng ngôn ngữ VHDL.

Ý tưởng giả lập các mạch ASIC chỉ từ thông tin trong các tư liệu trên cuốn hút đến nỗi

các trình giả lập mạch logic được phát triển để đọc định dạng file VHDL này. Bước

phát triển tiếp sau đó là các công cụ tổng hợp mạch logic đọc mã VHDL và xuất ra

cách cài đặt bằng phần cứng của mạch đã cho.

Do Bộ Quốc phòng Hoa Kỳ yêu cầu cú pháp của VHDL gần với Ada nhất có thể để

tránh phải "phát minh lại" các khái niệm đã có sẵn và được thực nghiệm kĩ từ trước

trong ngôn ngữ Ada, VHDL mượn khá nhiều khái niệm và cú pháp ngôn ngữ từ Ada. 1.2 CẤU TRÚC

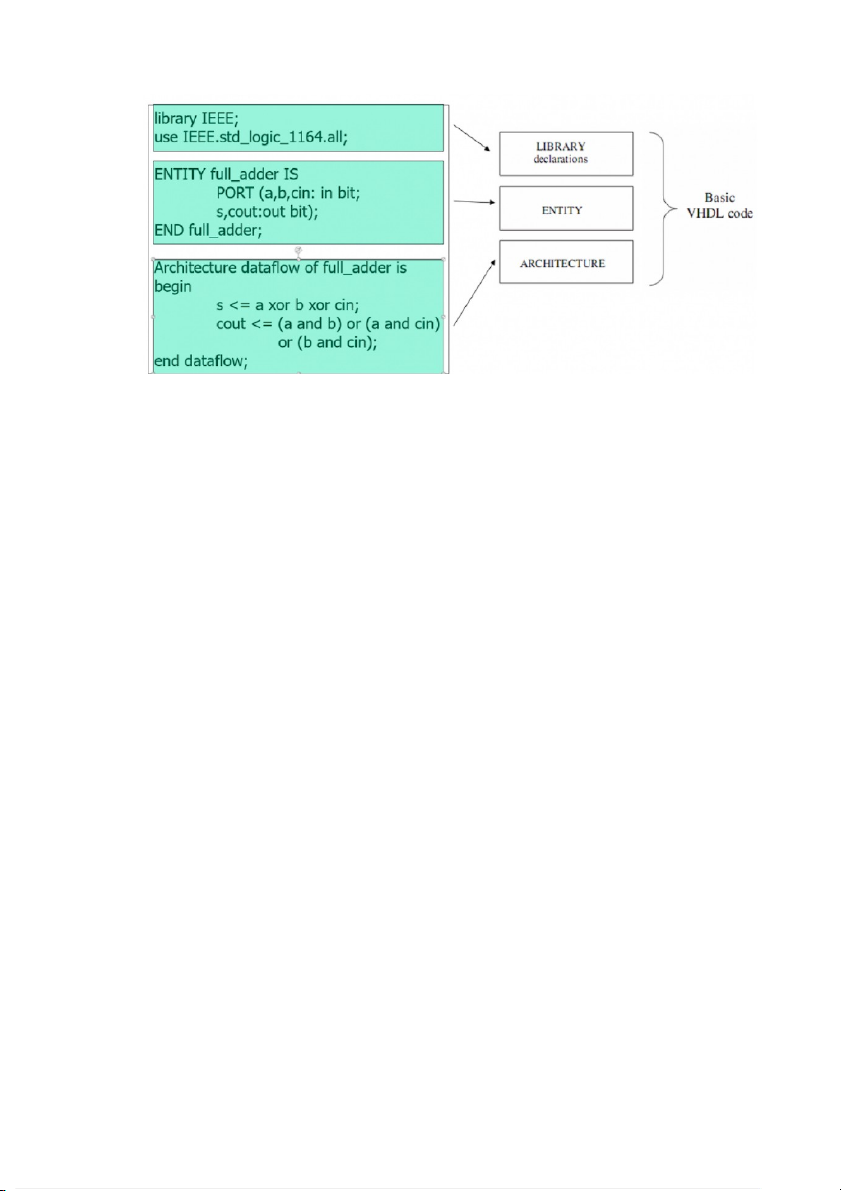

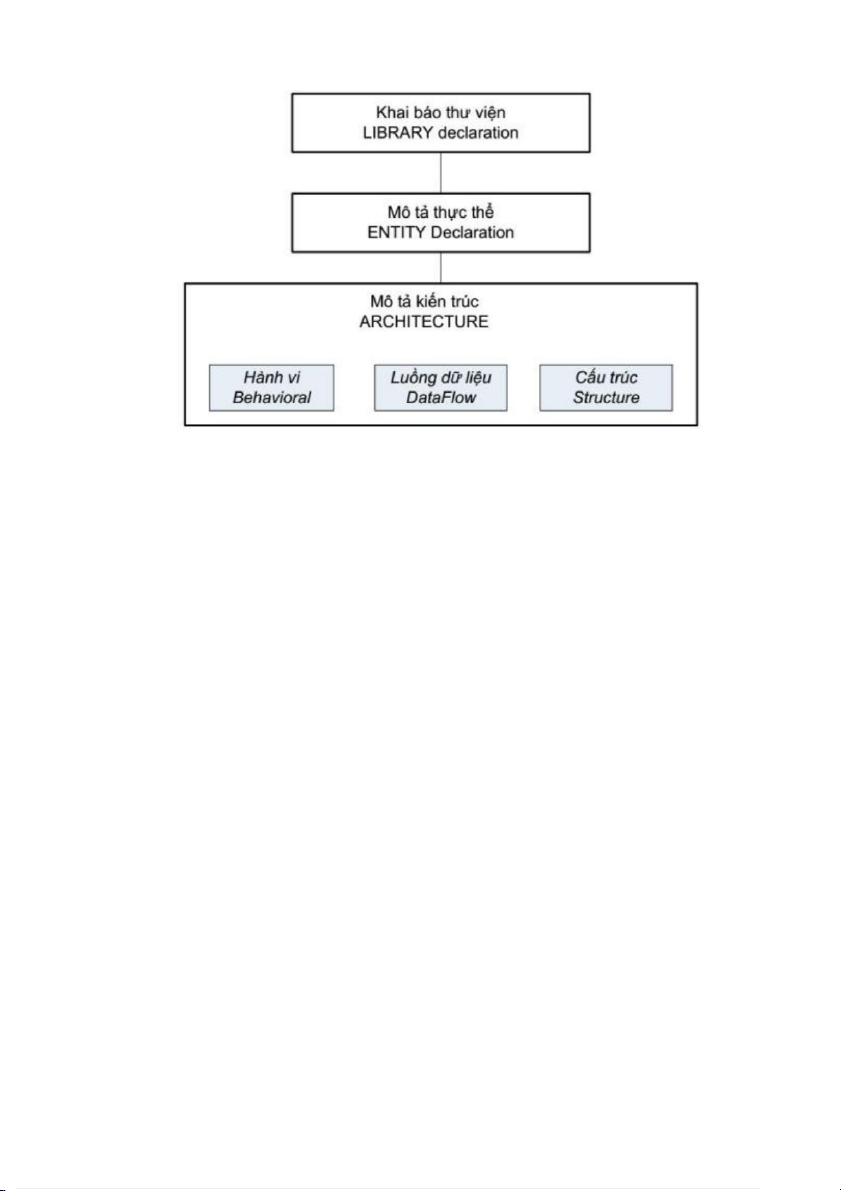

Tất cả các chương trình VHDL bao gồm ít nhất ba thành phần cơ bản sau đây:

Khai báo thư viện (LIBRARY): Chứa danh sách tất cả các thư viện sẽ được sử

dụng trong thiết kế. Ví dụ: ieee, std, work, v.v. 5

ENTITY (thực thể): Entity dùng để khai báo tên của thực thể, các port của thực

thể và các thông tin liên quan đến thực thể.

ARCHITECTURE (kiến trúc): Kiến trúc mô tả chức năng cơ bản của thực thể

và chứa nhiều phát biểu mô tả hành vi của thực thể. Kiến trúc luôn luôn có liên

quan đến thực thể và các mô tả hành vi của thực thể.

Signal and Component Declarations: Trong phần architecture, bạn có thể khai

báo các tín hiệu và components sẽ được sử dụng trong mạch.

Body of Architecture: Trong phần này, bạn triển khai logic của mạch sử dụng

các tín hiệu, components, và toán tử logic.

Configuration (Optional): Configuration là một phần tùy chọn, được sử dụng để

kết hợp nhiều entities và architectures lại với nhau. 6

Cấu trúc của chương trình VHDL như sau: LIBRARY library_name;

USE library_name.package_name.package_parts; ENTITY entity_name IS PORT (

port_name : signal_mode signal_type;

port_name : signal_mode signal_type; …); END entity_name;

ARCHITECTURE architecture_name OF entity_name IS [declarations] BEGIN (code) END architecture_name;

1.3 VẬN DỤNG NGÔN NGỮ LẬP TRÌNH VHDL CỦA CÁC MẠCH SỐ

CƠ BẢN VIẾT CỔNG AND , CỔNG OR , NAND, NOR 3 NGÕ VÀO. 1.3.1 Cổng AND -- File: and_gate.vhdl

-- Description: VHDL code for a 2-input AND gate 7 library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity AND_GATE is Port ( input1 : in STD_LOGIC; input2 : in STD_LOGIC; output : out STD_LOGIC); end AND_GATE;

architecture Behavioral of AND_GATE is begin process (input1, input2) begin -- AND operation

output <= input1 AND input2; end process; end Behavioral;

Trong ví dụ trên, AND_GATE là tên của mô-đun VHDL, và nó có hai đầu vào (input1

và input2) và một đầu ra) (output). Kiến trúc (architecture) được gọi là "Behavioral,"

và trong quá trình (process) định nghĩa hoạt động của cổng AND. 1.3.2 Cổng OR -- File: or_gate.vhdl

-- Description: VHDL code for a 2-input OR gate library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity OR_GATE is Port ( input1 : in STD_LOGIC; 8 input2 : in STD_LOGIC; output : out STD_LOGIC); end OR_GATE;

architecture Behavioral of OR_GATE is begin process (input1, input2) begin -- OR operation

output <= input1 OR input2; end process; end Behavioral;

Tương tự như ví dụ về cổng AND, trong mô-đun OR_GATE, có hai đầu vào (input1

và input2) và một đầu ra (output). Trong phần kiến trúc (architecture) được gọi là

"Behavioral," quá trình (process) định nghĩa hoạt động của cổng OR. 1.3.3 Cổng NAND

-- this is a dataflow model of a 2-input NAND gate LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.all; ENTITY NAND2gate IS PORT ( x: IN STD_LOGIC; y: IN STD_LOGIC; f: OUT STD_LOGIC) ; END NAND2gate;

ARCHITECTURE Dataflow OF NAND2gate IS BEGIN

f <= x NAND y; --signal assignment 9 END Dataflow; Trong mã VHDL trên:

entity NAND_gate định nghĩa các đầu vào (A và B) và đầu ra (Y) của cổng NAND.

architecture dataflow là phần trong đó chúng ta mô tả cách cổng NAND hoạt động.

Trong trường hợp này, nó được triển khai bằng cách sử dụng cổng NOT (not) để thực

hiện phép toán NAND trên A và B. 1.3.4 Cổng NOR 3 ngõ vào LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.all; ENTITY NOR3gate IS PORT ( x: IN STD_LOGIC; y: IN STD_LOGIC; z: IN STD_LOGIC; f: OUT STD_LOGIC) ; END NOR3gate;

ARCHITECTURE Dataflow OF NOR3gate IS

SIGNAL xory, xoryorz: STD_LOGIC; BEGIN xory <= x OR y; xoryorz <= xory OR z; f <= NOT xoryorz; END Dataflow; Trong mã VHDL trên:

entity NOR3_gate định nghĩa cổng NOR với 3 đầu vào (A, B, C) và một đầu ra (Y). 10

architecture dataflow là phần trong đó chúng ta mô tả cách cổng NOR hoạt động.

Trong trường hợp này, nó được triển khai bằng cách sử dụng cổng NOT (not) và cổng

OR (or) để thực hiện phép toán NOR trên A, B và C.

2. TÌM HIỂU MẠCH TỔ HỢP: MẠCH CỘNG, MẠCH MÃ HÓA, MẠCH

GIẢI MÃ, MẠCH DỒN KÊNH VÀ MẠCH GHÉP KÊNH. 2.1 MẠCH CỘNG

Mạch cộng, hay adder, là một mạch số học được thiết kế để thực

hiện phép toán cộng giữa hai hoặc nhiều số. Mạch cộng là một phần

quan trọng trong các mô-đun xử lý của máy tính và các hệ thống số

khác. Có một số loại mạch cộng khác nhau, bao gồm mạch cộng đơn

(half adder), mạch cộng đầy đủ (full adder), và các biến thể phức tạp

hơn như carry-lookahead adder.

2.1.1 Mạch Cộng Đơn (Half Adder):

Mô Tả: Mạch cộng đơn thực hiện phép cộng giữa hai bit đầu vào và tạo ra hai bit đầu

ra: một bit kết quả (sum) và một bit nhớ (carry). Đầu Vào: A, B (2 bit)

Đầu Ra: Sum (A XOR B), Carry (A AND B)

2.1.2 Mạch Cộng Đầy Đủ (Full Adder):

Mô Tả: Mạch cộng đầy đủ cải tiến mạch cộng đơn bằng cách thêm một bit nhớ đầu

vào và tạo ra hai bit đầu ra: một bit kết quả (sum) và một bit nhớ (carry).

Đầu Vào: A, B (2 bit), Carry In

Đầu Ra: Sum (A XOR B XOR Carry In), Carry Out (A AND B OR (Carry In AND (A XOR B))) 2.1.3 Carry-Lookahead Adder

Mô Tả: Carry-lookahead adder là một biến thể phức tạp hơn giúp giảm độ trễ trong

quá trình cộng. Nó sử dụng các mạch logic để tính toán trước các bit nhớ mà không

cần chờ kết quả của các bit trước đó.

Ưu Điểm: Giảm độ trễ so với mạch cộng đầy đủ khi có nhiều bit cần cộng. 11

Một mạch cộng 4-bit có thể được xây dựng bằng cách sử dụng nhiều

mạch cộng đầy đủ kết nối lại với nhau. Mỗi bộ cộng sẽ cộng 4 bit đầu

vào và bit nhớ từ bộ cộng trước đó. 2.2 MẠCH MÃ HÓA

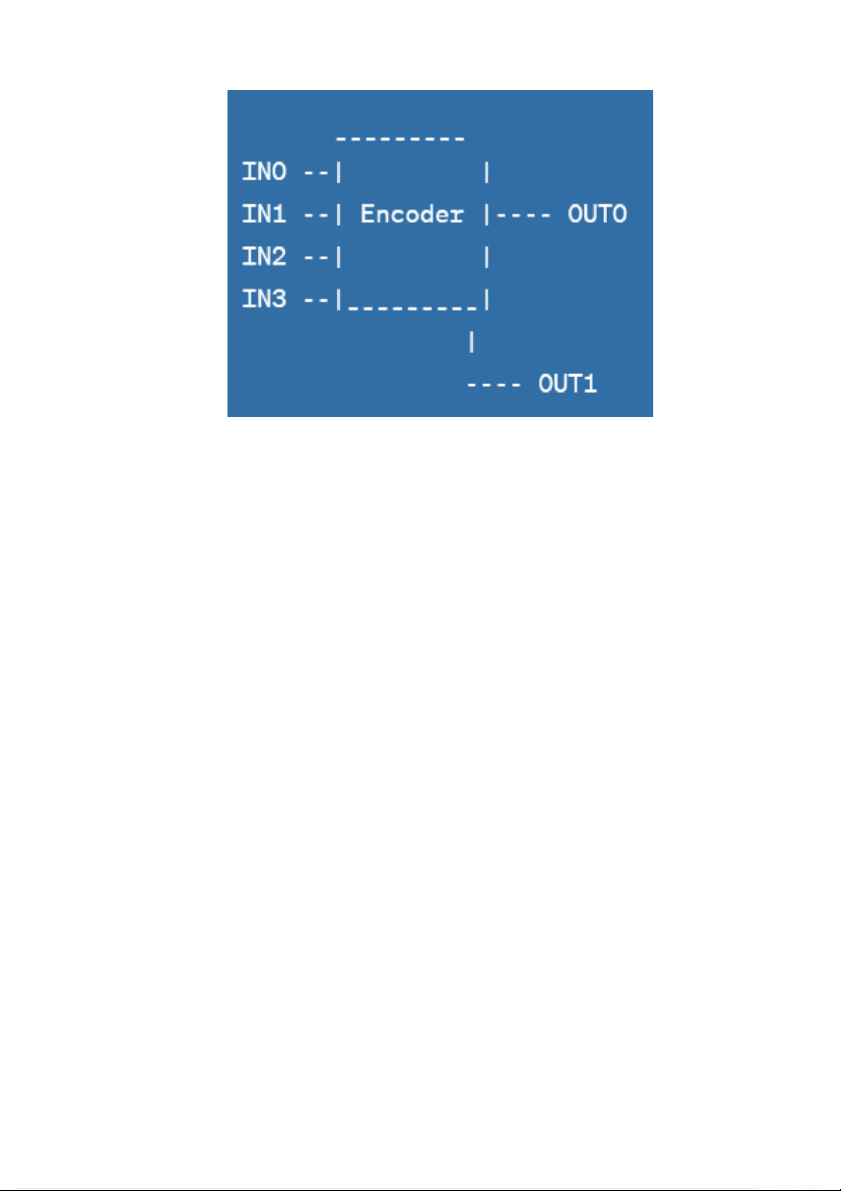

Mạch mã hóa, hay encoder, là một mạch số học được thiết kế để chuyển đổi một tập

hợp các tín hiệu đầu vào thành một tín hiệu đầu ra duy nhất. Chức năng chính của

mạch mã hóa là giảm số lượng dữ liệu đầu vào bằng cách biểu diễn chúng dưới dạng ít

bit hơn, thường là một đầu ra duy nhất. Cấu Trúc Mạch Mã Hóa:

Mạch mã hóa thường bao gồm nhiều đầu vào (IN), một đầu ra (OUT), và thỉnh thoảng

một số bit kiểm soát để xác định trạng thái hoạt động của mạch. Chức Năng Hoạt Động:

Mạch mã hóa xác định một giá trị đặc biệt của các tín hiệu đầu vào và tạo ra một đầu

ra duy nhất tương ứng với giá trị đó. Nếu có nhiều tín hiệu đầu vào cùng có giá trị,

mạch mã hóa thường chỉ chọn một giá trị duy nhất để đại diện. Ứng Dụng:

Mạch mã hóa thường được sử dụng để giảm số lượng dây truyền thông tin trong hệ

thống và làm cho việc truyền thông tin trở nên hiệu quả hơn, đặc biệt trong các ứng

dụng truyền thông và lưu trữ dữ liệu.

Một ví dụ đơn giản là mạch mã hóa 4-đầu vào (IN0, IN1, IN2, IN3)

thành 2-đầu ra (OUT0, OUT1) 12 2.3 MẠCH GIẢI MÃ

Mạch giải mã, hay decoder, là một mạch số học được thiết kế để chuyển đổi một tín

hiệu đầu vào thành một tập hợp các tín hiệu đầu ra. Chức năng chính của mạch giải mã

là dịch ngược lại quá trình mã hóa, trong đó một số bit đầu vào được chuyển đổi thành

một tập hợp lớn hơn các giá trị đầu ra.

Cấu Trúc Mạch Giải Mã:

Mạch giải mã thường có nhiều đầu vào (IN), một số bit đầu ra (OUT), và thỉnh thoảng

một tín hiệu kiểm soát để xác định trạng thái hoạt động của mạch. Chức Năng Hoạt Động:

Khi một tín hiệu đầu vào được đưa vào, mạch giải mã sẽ xác định giá trị của nó và

kích hoạt một trong các tín hiệu đầu ra tương ứng. Mỗi giá trị của tín hiệu đầu vào sẽ

được ánh xạ đến một giá trị đầu ra cụ thể. Ứng Dụng:

Mạch giải mã thường được sử dụng trong các ứng dụng như bộ giải mã địa chỉ bộ nhớ

(memory address decoder) trong hệ thống máy tính, hay trong việc chuyển đổi từ một

định dạng đầu vào thành một định dạng đầu ra khác.

Một ví dụ phổ biến về mạch giải mã là mạch giải mã BCD-7 đoạn, nơi

một số BCD (Binary Coded Decimal) 4-bit đầu vào được chuyển đổi 13

thành tín hiệu 7 đoạn để hiển thị số từ 0 đến 9 trên một hiển thị LED

7 đoạn. Mỗi giá trị BCD đầu vào (0000 đến 1001) sẽ được ánh xạ đến

một trong 10 giá trị 7 đoạn tương ứng. 2.4 MẠCH DỒN KÊNH

Mạch dồn kênh, hay multiplexer (mux), là một mạch số học được thiết kế để chọn một

trong nhiều đầu vào và đưa ra một đầu ra dựa trên tín hiệu kiểm soát. Nó thường được

biểu diễn dưới dạng hình hộp với nhiều đầu vào và một đầu ra.

Cấu Trúc Mạch Dồn Kênh:

Mạch dồn kênh thường bao gồm nhiều đầu vào (IN), một đầu ra (OUT), và một tín

hiệu kiểm soát (SEL) để xác định đầu vào nào sẽ được chọn. Số lượng đầu vào có thể

là 2^n, với n là số bit của tín hiệu kiểm soát. Chức Năng Hoạt Động:

Khi tín hiệu kiểm soát thay đổi, mạch dồn kênh sẽ chọn một trong các đầu vào tương

ứng để truyền thông tin từ đầu vào đến đầu ra. Mỗi đầu vào có thể được xem như là

một kênh riêng lẻ, và thông tin từ kênh được chọn sẽ được đưa ra đầu ra. Ứng Dụng:

Mạch dồn kênh thường được sử dụng để kết hợp nhiều nguồn thông

tin và chuyển đổi giữa chúng dựa trên điều kiện xác định. Ví dụ,

trong việc chọn giữa nhiều đường dữ liệu đến một bộ xử lý hoặc bộ

nhớ, mạch dồn kênh rất hữu ích. Công Thức Chọn Kênh:

Nếu n là số bit của tín hiệu kiểm soát, thì số lượng đầu vào của mạch dồn kênh sẽ là

2^n. Công thức chọn kênh được sử dụng để xác định đầu vào nào sẽ được kích hoạt tại

một thời điểm cụ thể: 14

Ví dụ về một mạch dồn kênh 4 đầu vào (IN0, IN1, IN2, IN3) và 1 đầu ra (OUT) 2.5 MẠCH GHÉP KÊNH

Mạch ghép kênh, hay demultiplexer (demux), là một mạch số học được thiết kế để

chia một đường dữ liệu đầu vào thành nhiều đường dữ liệu đầu ra dựa trên tín hiệu

kiểm soát. Nó thường được biểu diễn dưới dạng hình hộp với một đường dữ liệu đầu

vào và nhiều đường dữ liệu đầu ra.

Cấu Trúc Mạch Ghép Kênh:

Mạch ghép kênh thường có một đầu vào (IN), một tín hiệu kiểm soát (SEL), và nhiều

đầu ra (OUT). Số lượng đầu ra phụ thuộc vào bộ chọn (selector) hay tín hiệu kiểm

soát. Số lượng đầu ra có thể là 2^n, với n là số bit của tín hiệu kiểm soát. Chức Năng Hoạt Động:

Khi tín hiệu kiểm soát thay đổi, mạch ghép kênh sẽ chọn một trong các đầu ra tương

ứng để truyền thông tin từ đầu vào đến. Mỗi đầu ra có thể được xem như là một kênh

riêng lẻ, và thông tin từ đầu vào sẽ được định tuyến tới một trong các kênh này. Ứng Dụng:

Mạch ghép kênh thường được sử dụng để phân tách một tín hiệu từ

một nguồn đầu vào ra nhiều nguồn đầu ra khác nhau, giống như

cách một truyền hình có thể chọn giữa nhiều kênh. Công thức chọn kênh:

Nếu n là số bit của tín hiệu kiểm soát, thì số lượng đầu ra của demux sẽ là 2^n. Công

thức chọn kênh được sử dụng để xác định kênh nào sẽ được kích hoạt tại một thời điểm cụ thể: 15

Ví dụ về một mạch ghép kênh 2 đầu vào (IN1, IN2) và 4 đầu ra (OUT0, OUT1, OUT2, OUT3):

3. TÌM HIỂU VỀ CẤU TRÚC MÁY TÍNH VÀ HỆ ĐIỀU HÀNH.

3.1 CÁC THÀNH PHẦN CƠ BẢN CỦA MÁY TÍNH

Cấu trúc máy tính là cách mà các thành phần cơ bản của một hệ thống máy tính được

tổ chức và kết nối với nhau để thực hiện các chức năng tính toán. Cấu trúc máy tính

bao gồm nhiều thành phần, trong đó có bộ xử lý, bộ nhớ, các thiết bị ngoại vi, và các

đường truyền thông tin giữa chúng. Dưới đây là một số khái niệm quan trọng trong cấu trúc máy tính:

Bộ xử lý (CPU): Là "trái tim" của máy tính, nơi thực hiện các phép tính toán và

quản lý các tác vụ khác. Bộ xử lý thường bao gồm một bộ điều khiển (control unit) và

một bộ logic (ALU - Arithmetic Logic Unit).

Bộ nhớ: Là nơi lưu trữ dữ liệu và các chương trình. Bộ nhớ được chia thành hai loại

chính là bộ nhớ chính (RAM - Random Access Memory) và bộ nhớ lưu trữ (ví dụ: ổ cứng).

Bus (đường truyền thông tin): Là các đường truyền thông tin giữa các

thành phần khác nhau của máy tính, bao gồm bus dữ liệu, bus địa chỉ và bus kiểm soát. 16

Thiết bị ngoại vi: Là các thành phần bổ sung như bàn phím, chuột, màn hình,

máy in, và các thiết bị lưu trữ ngoại vi.

Bộ nguồn và điều khiển nguồn: Cung cấp nguồn điện cho các thành phần

của máy tính và điều khiển nguồn vào các phần khác nhau.

Bộ điều khiển (Control Unit): Quản lý và điều khiển hoạt động của các

thành phần khác nhau của máy tính, bao gồm việc đọc lệnh từ bộ nhớ, giải mã chúng

và thực hiện các hành động tương ứng.

ALU (Arithmetic Logic Unit): Thực hiện các phép toán số học và logic.

Điều kiện logic và nhánh: Điều khiển luồng thực hiện của chương trình bằng

cách kiểm soát việc nhảy đến các địa chỉ khác nhau trong bộ nhớ dựa trên các điều kiện. 3.2 HỆ ĐIỀU HÀNH

Hệ điều hành (Operating System - OS) là một phần mềm quản lý và điều khiển tài

nguyên của máy tính hoặc thiết bị điện tử khác. Nó cung cấp một giao diện giữa phần

cứng và phần mềm ứng dụng, giúp người dùng và các ứng dụng tương tác với tài

nguyên hệ thống. Dưới đây là một số khái niệm quan trọng về hệ điều hành:

Quản lý tài nguyên: Hệ điều hành quản lý tài nguyên phần cứng như bộ nhớ,

CPU, thiết bị đầu vào/đầu ra (I/O devices), và các tài nguyên khác. Nó đảm bảo rằng

tất cả các ứng dụng và tiến trình có thể sử dụng tài nguyên một cách hiệu quả và không xung đột. 17

Giao diện người dùng: Hệ điều hành cung cấp các giao diện để tương tác với

người dùng. Có hai loại giao diện chính là giao diện đồ họa (GUI - Graphical User

Interface) và giao diện dòng lệnh (CLI - Command Line Interface).

Quản lý bộ nhớ: Hệ điều hành quản lý bộ nhớ để lưu trữ và truy cập dữ liệu. Nó

quản lý bộ nhớ chính (RAM) và có thể tạo ra các không gian bộ nhớ ảo để mở rộng dung lượng lưu trữ.

Quản lý tập tin: Hệ điều hành quản lý tập tin và thư mục, cho phép người dùng

tổ chức và truy cập dữ liệu một cách hiệu quả.

Quản lý tiến trình: Hệ điều hành quản lý các tiến trình và luồng (processes and

threads) để đảm bảo thực hiện đồng thời và hiệu quả của các tác vụ.

Bảo mật: Bảo mật là một khía cạnh quan trọng của hệ điều hành, đảm bảo rằng tài

nguyên hệ thống được bảo vệ và chỉ có những người dùng được ủy quyền mới có thể truy cập.

Giao tiếp giữa các tiến trình: Hệ điều hành cung cấp các cơ chế để các tiến

trình có thể giao tiếp và trao đổi dữ liệu với nhau.

Ví dụ về một số hệ điều hành: 18

Một hệ điều hành (Operating System - OS) là một phần mềm quản lý tài nguyên và

cung cấp giao diện giữa người dùng và phần cứng máy tính. Dưới đây là một ví dụ cụ

thể về một hệ điều hành phổ biến - Microsoft Windows:

Hệ Điều Hành: Microsoft Windows 10 Kernel:

Windows 10 sử dụng kernel làm trung tâm của hệ điều hành. Kernel quản lý tài

nguyên hệ thống như bộ nhớ, tiến trình, tệp tin, và giao tiếp với phần cứng. Giao Diện Người Dùng:

Windows 10 cung cấp một giao diện người dùng đồ họa, có tên là Desktop, cho

phép người dùng tương tác với hệ điều hành bằng cách sử dụng chuột, bàn

phím, và màn hình cảm ứng. Quản Lý Tài Nguyên:

Hệ điều hành Windows quản lý bộ nhớ và tài nguyên hệ thống để đảm bảo ổn

định và hiệu suất cao cho các ứng dụng và tiến trình. Hệ Thống Tệp Tin:

Windows sử dụng hệ thống tệp tin NTFS để quản lý và tổ chức dữ liệu trên đĩa

cứng. Nó hỗ trợ nhiều chức năng như quản lý quyền truy cập và mã hóa tệp tin. Mạng:

Hệ điều hành Windows hỗ trợ kết nối mạng và cung cấp các giao thức như

TCP/IP để truyền dữ liệu qua mạng. Phần Mềm Ứng Dụng:

Windows hỗ trợ nhiều ứng dụng và chương trình ứng dụng đa dạng như

Microsoft Office, trình duyệt web, phần mềm giải trí, và nhiều ứng dụng khác. Bảo Mật:

Windows cung cấp các tính năng bảo mật như tường lửa, Windows Defender

(phần mềm chống virus và malware), và các cập nhật bảo mật định kỳ.

Quản Lý Tiến Trình và Dịch Vụ: 19

Kernel của Windows quản lý các tiến trình và dịch vụ chạy trên hệ thống, đảm

bảo chúng hoạt động một cách hiệu quả.

Giao Tiếp Với Phần Cứng:

Windows tương tác với phần cứng thông qua các trình điều khiển (drivers),

đảm bảo tính tương thích và sự ổn định.

Windows 10 là một ví dụ tiêu biểu về hệ điều hành máy tính dành cho người dùng cá

nhân và doanh nghiệp, và nó thường được cài đặt trên nhiều loại máy tính từ máy tính

để bàn đến laptop và thiết bị di động. Tài liệu tham khảo

https://vi.wikipedia.org/wiki/VHDL

https://fr.slideshare.net/hoangclick/bai-giangvhdl

https://iztuts.com/bai-3-cac-cong-logic-and-or-nand-xor-not/

https://dientuviet.com/gioi-thieu-ngon-ngu-vhdl/

https://vi.wikipedia.org/wiki/Microsoft_Windows