Preview text:

Bài 2: Thiết kế mạch cộng 1 Mục tiêu:

Kiến thức, kỹ năng sinh viên có ược sau bài thực hành này:

• Tạo symbol từ mạch số ã thiết kế. Sau ó, sử dụng các symbol vừa tạo ể xây dựng các mạch phức tạp hơn.

• Thiết kế mạch cộng Ripple Carry và mạch cộng Carry Lookahead. 2 Nội dung: 2.1. Tạo symbol 1. Tạo project quartus.

2. Tạo Block Diagram/Schematic File.

3. Chọn file thiết kế làm top module bằng cách “Set as Top-Level Entity”

4. Biên dịch chương trình.

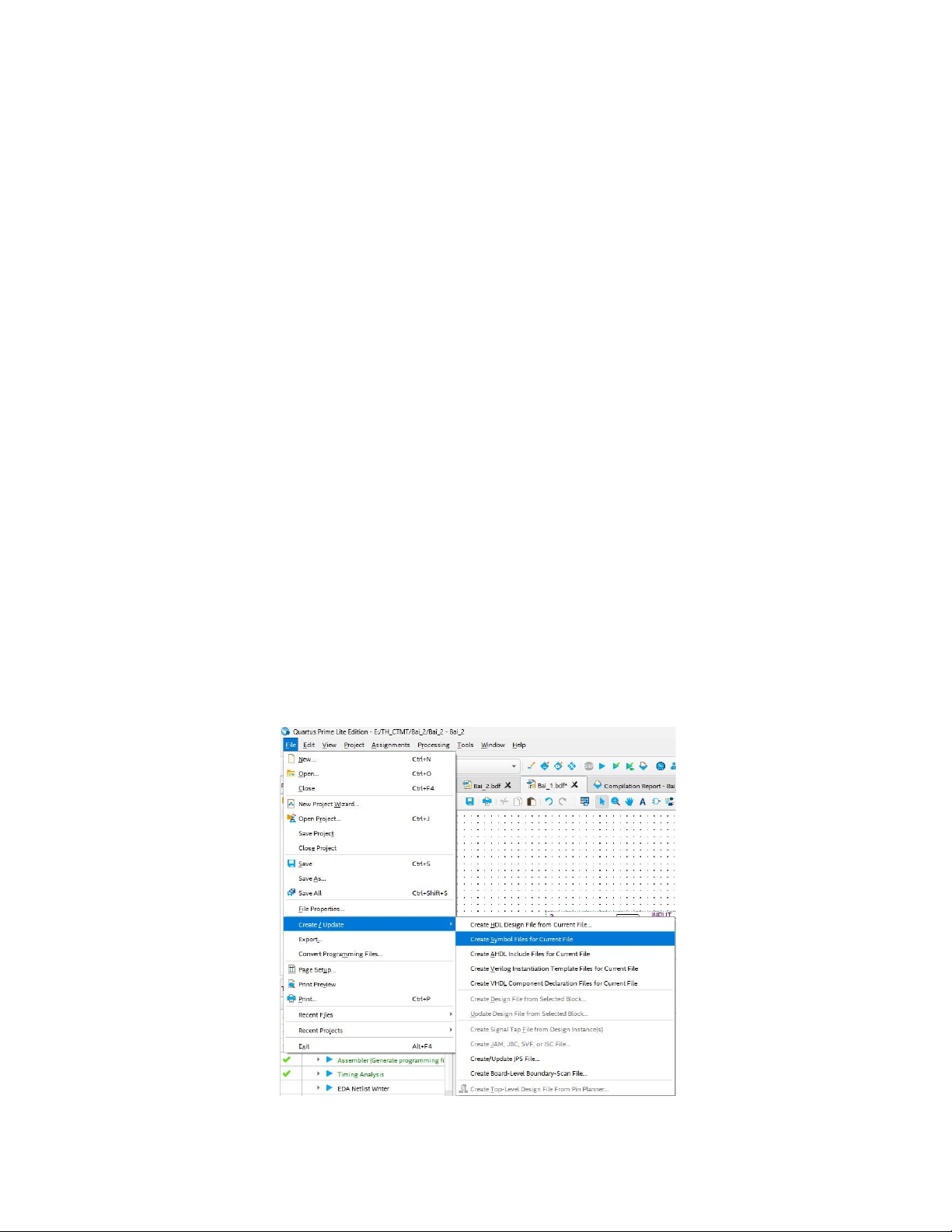

5. Chọn File Create / Update Create Symbol Files for Current File (hình 1).

6. Lưu file bsf với tên mong muốn.

Hình 1. Tạo symbol cho phần cứng tự thiết kế.

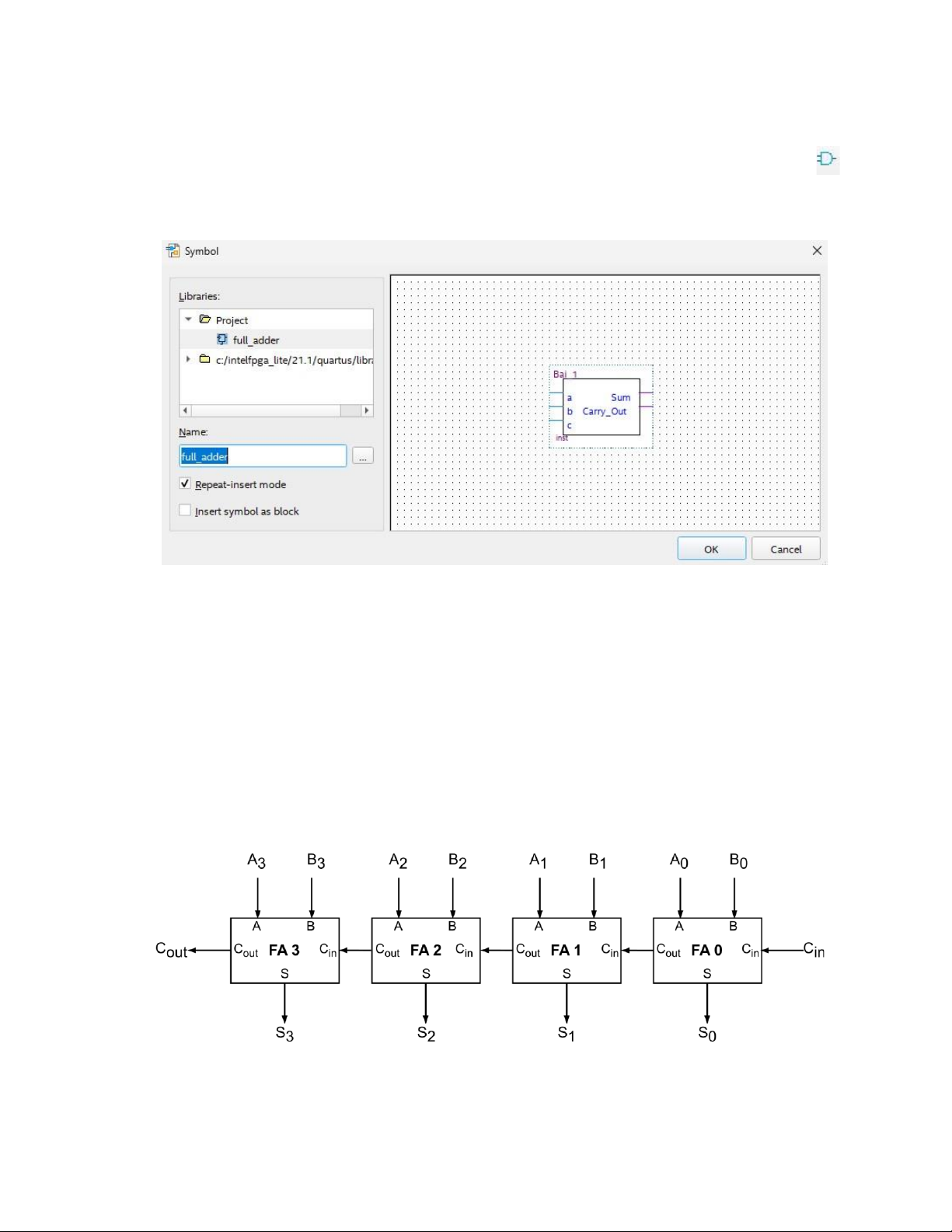

7. Để gọi symbol vừa tạo, tạo một Block Diagram/Schematic File mới, chọn Symbol tool

, trong Libraries box của cửa sổ Symbol xuất hiện thư mục project, ây là thư mục chứa

các symbol do người dùng tự tạo. Như trong hình 2, symbol full_adder ã ược tạo.

Hình 2. Cách lấy symbol tự tạo.

2.2. Thiết kế mạch cộng Ripple Carry

Mạch cộng Ripple Carry ược xây dựng bằng cách ghép nối các mạch cộng toàn phần (Full

Adder - FA) với nhau, như ược trình bày trong hình 3. Hình 3 miêu tả mạch cộng Ripple Carry 4-

bit bằng cách kết nối 4 FA, carry out của FA 0 là carry in của FA 1, tương tự như vậy với FA 2 và

FA 3. Trong thiết kế này, thực hiện phép cộng 3 toán hạng: toán hạng thứ nhất là 4-bit A3A2A1A0,

toán hạng thứ hai là 4-bit B3B2B1B0, và toán hạng thứ ba là 1-bit Cin; kết quả của phép cộng 4-bit

ược biểu diễn bằng S3S2S1S0 và Cout.

Hình 3. Mạch cộng Ripple Carry 4-bit.

2.3. Thiết kế mạch cộng Carry Lookahead

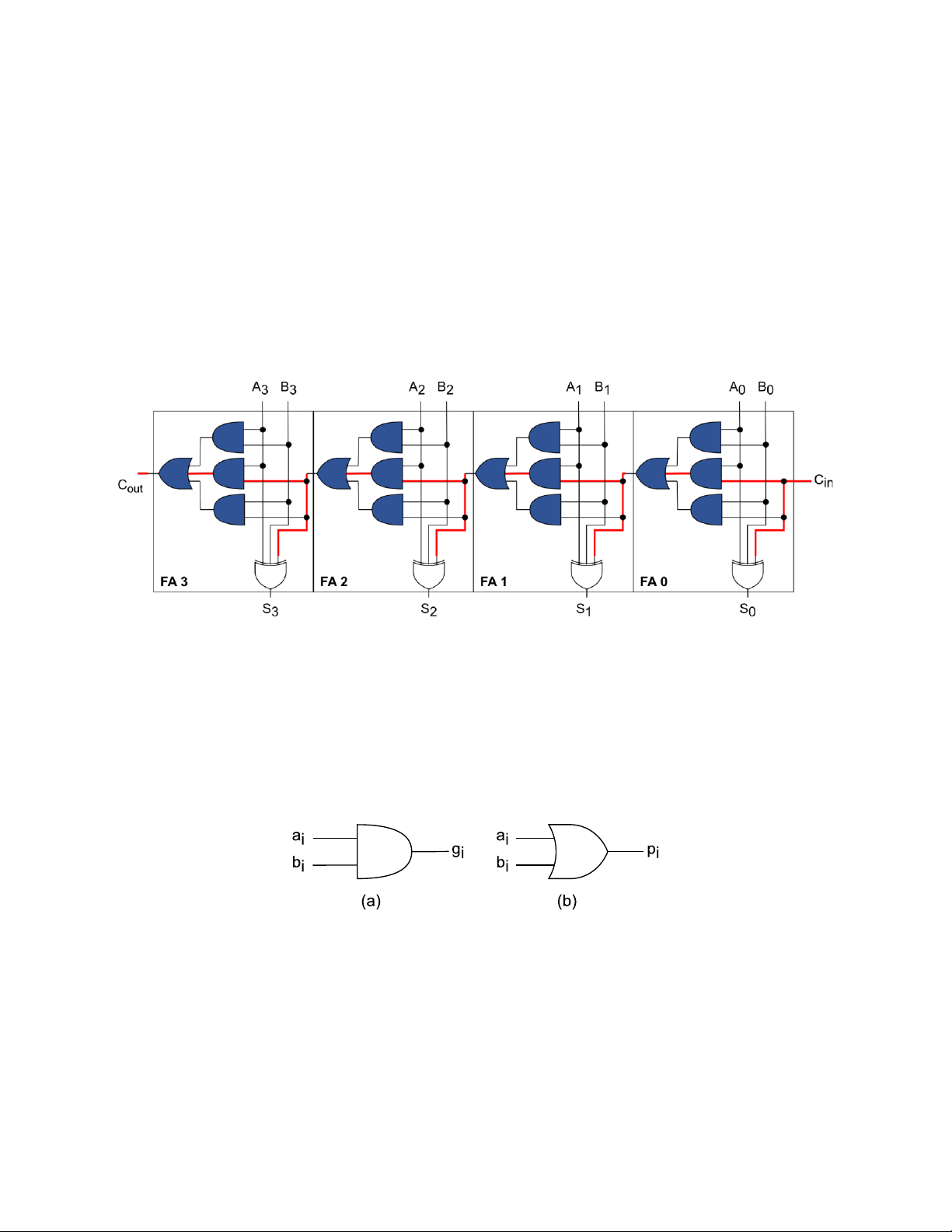

Kiến trúc của mạch cộng Ripple Carry ơn giản nhưng gây ra ộ trễ trong việc lan truyền tín

hiệu nhớ (carry), cụ thể như ược trình bày trong hình 4, khối FA sau phụ thuộc vào tín hiệu carry

của khối FA trước, carry out (Cout) của FA 3 phụ thuộc vào carry out của FA 2, carry out của FA 2

phụ thuộc vào carry out của FA 1, carry out của FA 1 phụ thuộc vào carry out của FA 0, và carry

out của FA 0 phụ thuộc vào carry in (Cin).

Hình 4. Minh hoạt ộ trễ của việc lan truyền tín hiệu carry của mạch cộng Ripple Carry.

Mạch cộng Carry Lookahead là một giải pháp cho việc rút ngắn thời gian lan truyền tín

hiệu carry. Carry Lookahead ược xây dựng dựa trên hai thành phần cốt lõi là generate (𝑔𝑖) và

propagate (𝑝𝑖). Thành phần generate là output của cổng AND hai input, trong khi ó, thành phần

propagate là output của cổng OR hai input, ược minh họa lần lượt trong hình 5.a vả hình 5.b.

Hình 5. a) generate. b) propagate.

Từ hình 4 có thể thấy ược carry của mỗi FA ược tính như sau:

Thay 𝑔𝑖 và 𝑝𝑖 vào biểu thức (1):

𝑐𝑖+1 = 𝑔𝑖 + 𝑝𝑖. 𝑐𝑖 (2)

𝑐𝑖+1 = (𝑎𝑖. 𝑏𝑖) + (𝑎𝑖. 𝑐𝑖) + (𝑏𝑖. 𝑐𝑖) = (𝑎𝑖. 𝑏𝑖) + (𝑎𝑖 + 𝑏𝑖). 𝑐𝑖 (1)

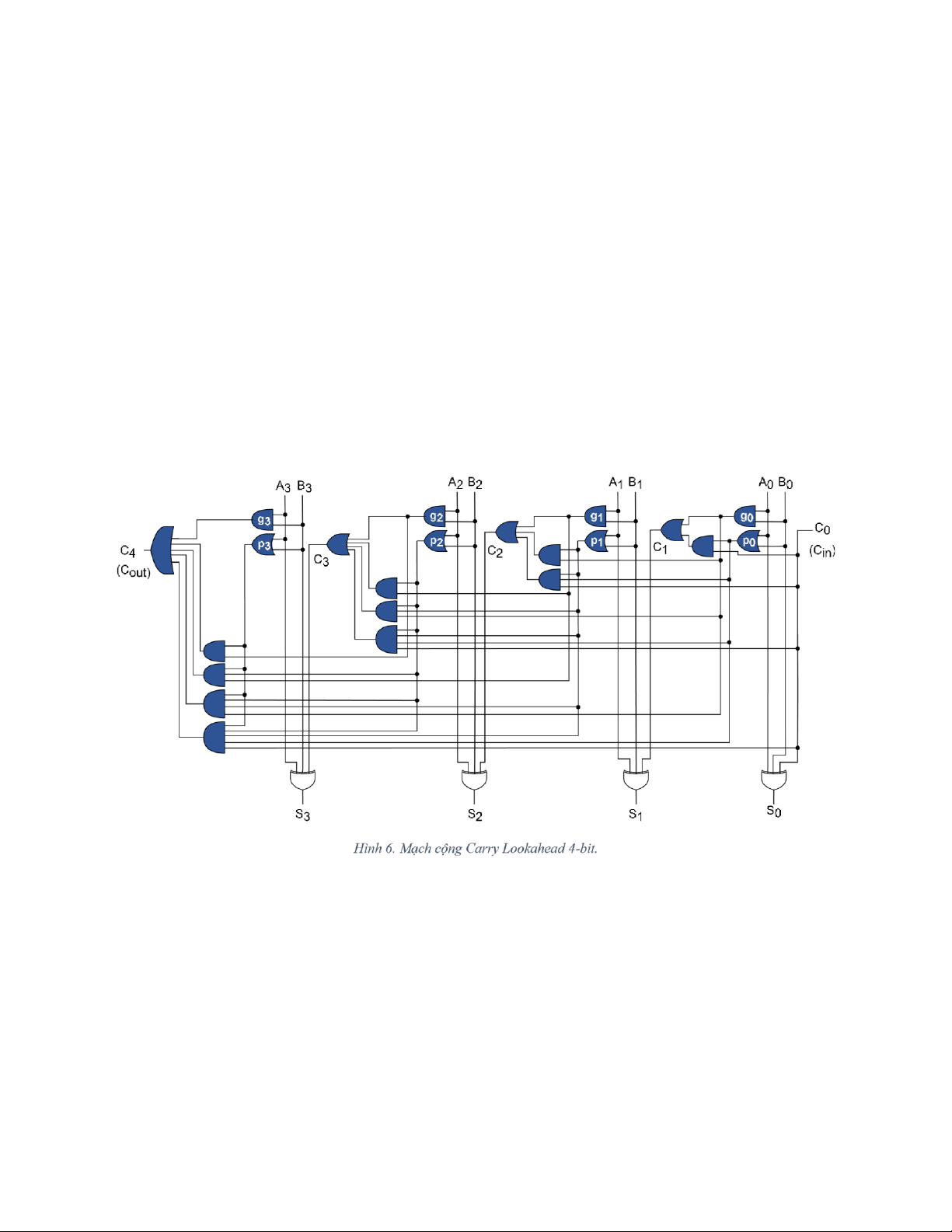

Dựa trên biến ổi (2), chúng ta có thể biểu diễn carry của mạch cộng 4-bit như sau:

𝑐1 = 𝑔0 + 𝑝𝑜. 𝑐0

𝑐2 = 𝑔1 + (𝑝1. 𝑔0) + (𝑝1. 𝑝𝑜. 𝑐𝑜)

(3) 𝑐3 = 𝑔2 + (𝑝2. 𝑔1) + (𝑝2. 𝑝1. 𝑔𝑜) + (𝑝2. 𝑝1. 𝑝0. 𝑐𝑜)

𝑐4 = 𝑔3 + (𝑝3. 𝑔2) + (𝑝3. 𝑝2. 𝑔1) + (𝑝3. 𝑝2. 𝑝1. 𝑔𝑜) + (𝑝3. 𝑝2. 𝑝1. 𝑝0. 𝑐𝑜) Lưu

ý: 𝑐0, 𝑐4 tương ứng lần lượt với 𝑐𝑖𝑛, 𝑐𝑜𝑢𝑡 trong hình 4.

Từ các biến ổi (3), kiến trúc ầy ủ của mạch cộng Carry Lookahead 4-bit ược miêu tả trong hình 6.

BÀI TẬP CHUẨN BỊ Ở NHÀ

Bài tập 1: Thực hiện mạch cộng toàn phần (Full Adder) theo yêu cầu sau: 1. Viết biểu thức.

2. Lập bảng chân trị và rút gọn. 3. Vẽ mạch ở mức cổng logic.

Bài tập 2: Cho biết ưu và khuyết iểm của mạch cộng Ripple Carry và mạch cộng Carry Lookahead. BÁO CÁO THỰC HÀNH

Bài 1: Thiết kế mạch cộng Ripple Carry 4-bit.

Bài 2: Thiết kế mạch cộng Carry Lookahead 4-bit.

Bài 3: Thiết kế mạch cộng Carry Lookahead 8-bit.

Bài 4: Giả sử rằng thời gian ể tín hiệu i qua cổng AND và OR là 1ns. Hãy ước lượng thời gian

delay của bài 1 và bài 3. Giải thích rõ cách tính và chỉ ra trên mạch thiết kế (tô ỏ ường delay nhất).

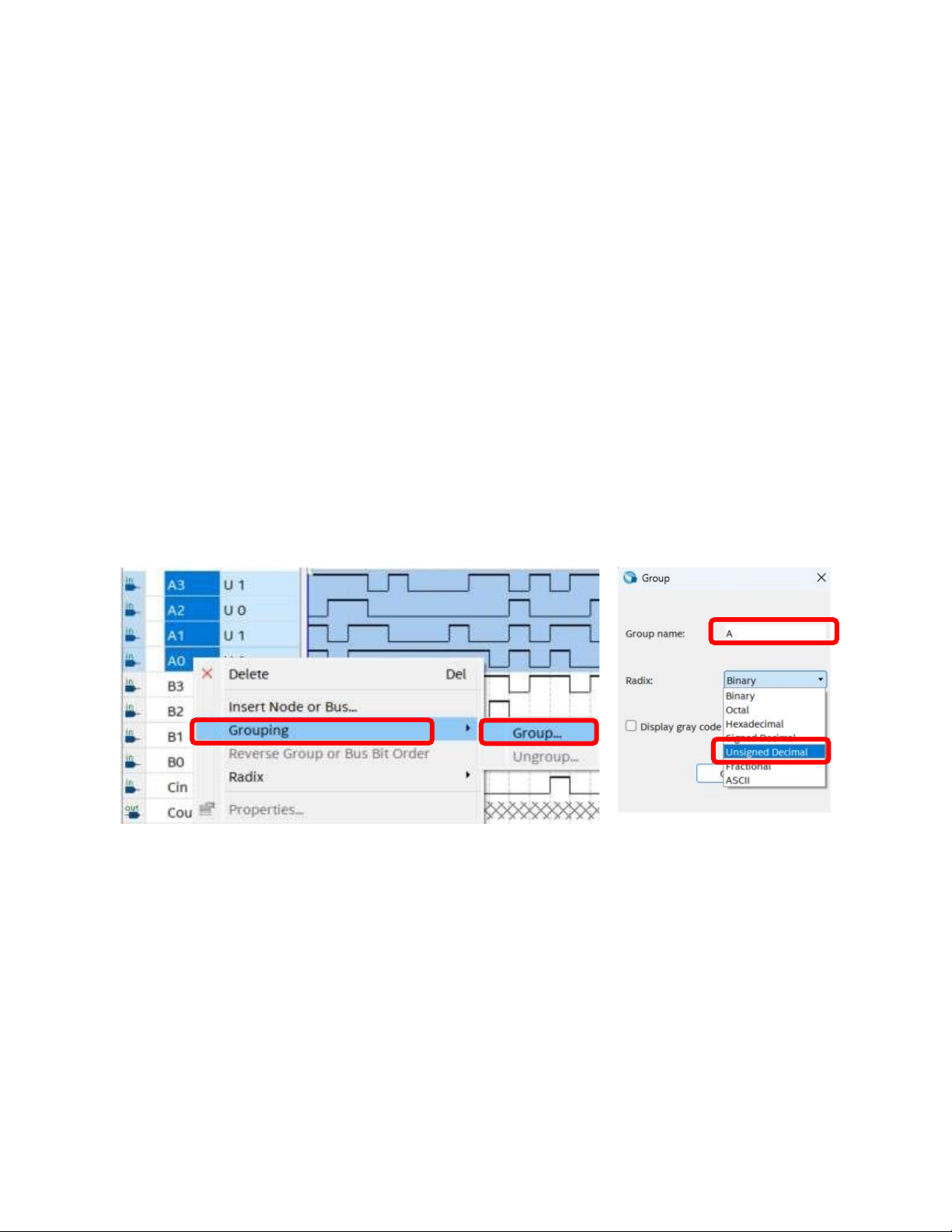

Lưu ý: Để dễ dàng quan sát sóng trong Simulation Waveform, sử tính năng group:

1. Chọn nhóm tín hiệu muốn group Grouping Group…

Lưu ý thứ tự các bit trong group: bit cao nằm trên bit thấp. Như trong hình 7, thứ từ bit 3 ến bit 0.

2. Đặt tên nhóm và chọn ịnh dạng hiển thị (hình 8).

Hình 8. Đặt tên và chọn ịnh dạng

Hình 7. Nhóm tín hiệu.

hiển thị của nhóm tín hiệu.

TÀI LIỆU THAM KHẢO

[1] Chap2_0 (Tài liệu trong thư mục doc)

[2] Chap2_1_0 (Tài liệu trong thư mục doc)

[3] Chap2_1_1 (Tài liệu trong thư mục doc)

[4] Chap3_1 (Tài liệu trong thư mục doc)

[5] Introduction to Simulation of Verilog Designs. [Offline] Available:

/ntelFPGA_lite/21.1/quartus/common/help/tutorial_quartusii_simulation_verilog.pdf.