Preview text:

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

Bài 3: Thiết kế ALU 1 Mục tiêu:

Kiến thức, kỹ năng sinh viên có được sau bài thực hành này:

• Hiểu và thiết kế các thành phần cấu thành của Arithmetic Logic Unit (ALU).

• Xây dựng ALU cơ bản bằng cách kết hợp các thành phần như: AND, OR, mạc h cộng (Full Adder - F ), NOT A , và MUX. 2 Nội dung:

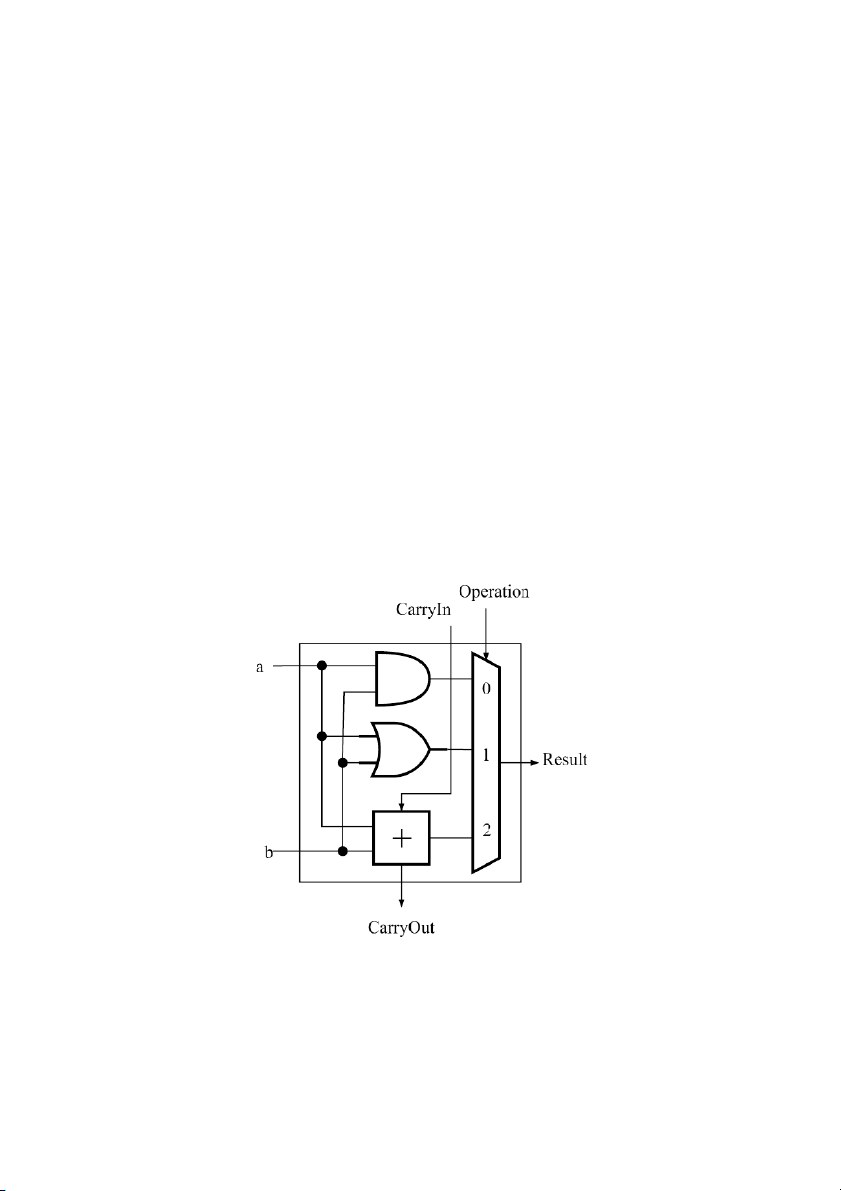

2.1. Kiến trúc ALU 1-bit

Kiến trúc ALU 1-bit được minh họa trong hinh 1 phục vụ 3 phép toán: AND, OR, và cộng

2 số. The multiplexor (MUX) dùng để lựa chọn kết quả đầu ra cho ALU, tín hiệu Operation đóng

vai trò là tín hiệu lựa chọn của bộ MUX, Operation bằng 0 chọn phép toán a AND b, Operation

bằng 1 chọn phép toán a OR b, và Operation bằng 2 chọn phép toán a cộng b.

Hình 1. Kiến trúc ALU 1-bit. 1

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

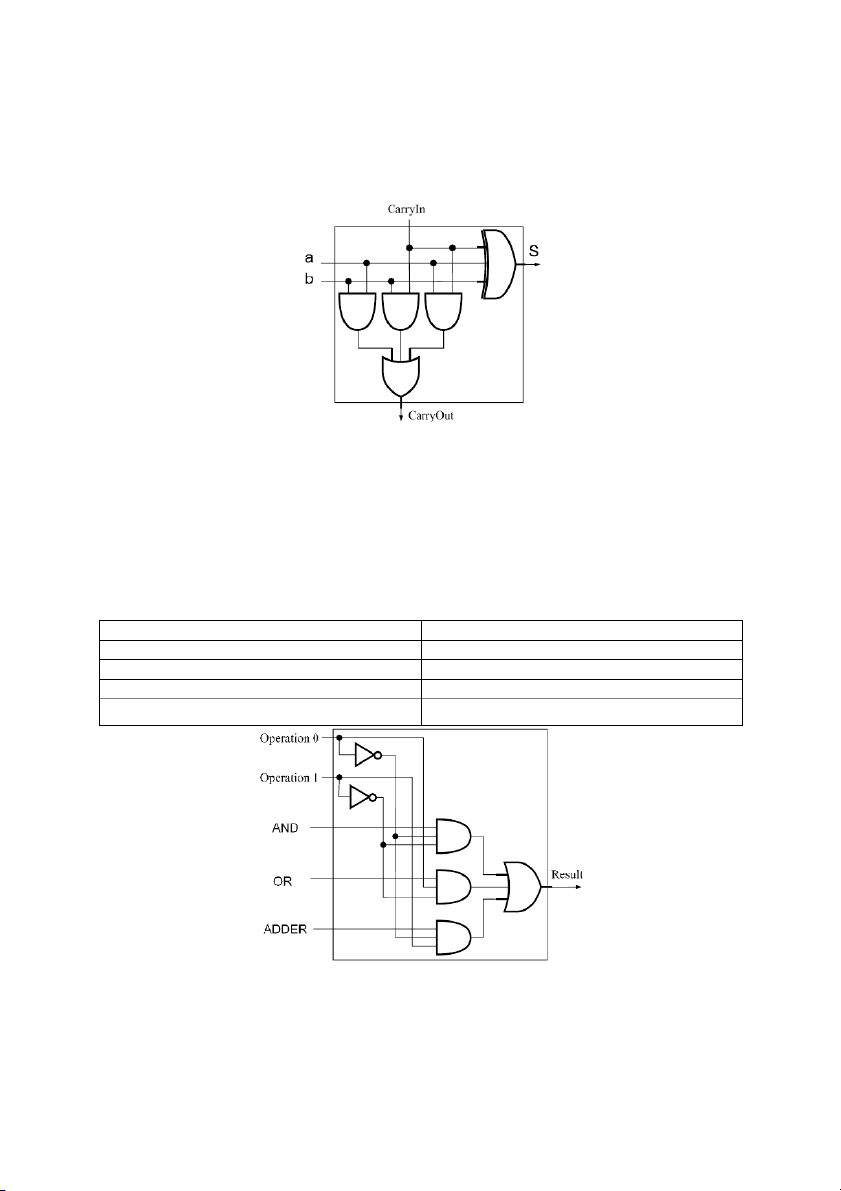

Mạch cộng trong ALU 1-bit được thiết kế như hình 2, đây là mạc h cộng toàn phần (Full

Adder - FA) với 3 input là toán hạng thứ nhất (a), toạn hạng thứ hai (b), và bit nhớ (CarryIn), tạo

ra 2 output là kết quả (S) và bit nhớ (CarryOut).

Hình 2. Mạc cộng của ALU 1-bit. h

Bộ MUX sử dụng 2-bit lựa chọn (2-bit cho tín hiệu Operation) cho 3 input: phép AND,

phép OR, và phép cộng. Bảng 1 biểu diễn tín hiệu ựa chọn cho l

3 input, với 00 cho phép AND, 01

cho phép OR, 10 cho phép cộng, và 11 không dùng. Kiến trúc phần cứng của bộ MUX được biểu diễn trong hình 3.

Bảng 1. Bảng chân trị của bộ MUX. Operation (2-bit) Result 00 AND 01 OR 10 cộng 11 x (don’t care)

Hình 3. Kiến trúc bộ MUX của ALU 1-bit. 2

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

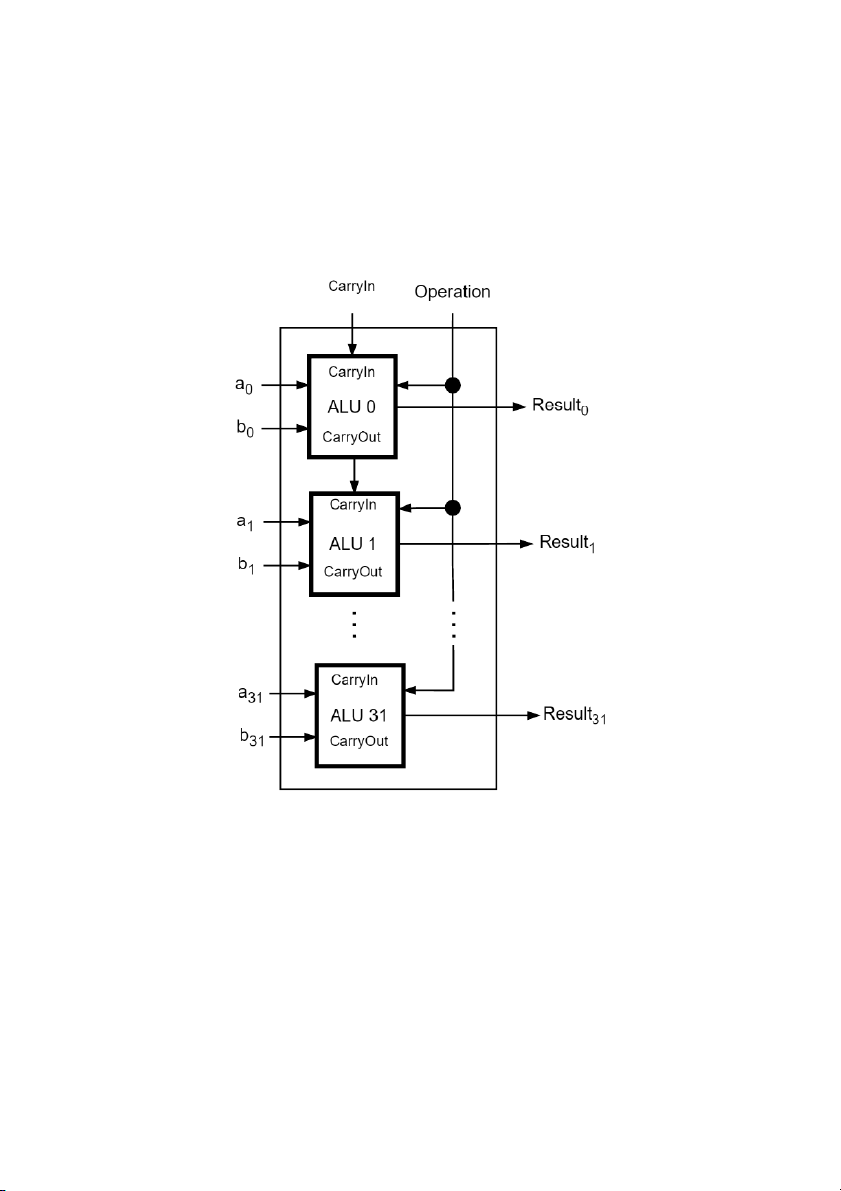

2.2. Kiến trúc ALU 32-bit

Kiến trúc ALU 32-bit được tạo ra bằng cách kết nối 32 khối ALU 1-bit với nhau như được

biểu diễn trong hình 4. Khi ghép nối các ALU 1-bit với nhau, các mạc

h cộng được kết nối trực

tiếp với nhau hình thành kiến trúc mạch cộng Ripple Carry.

Hình 4. Kiến trúc ALU 32-bit. 3

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

BÀI TẬP CHUẨN BỊ Ở NHÀ

Bài tập: Thiết kế bộ MUX 4 ngõ vào: 1. Lập bảng chân trị.

2. Rút gọn biểu thực bằng biểu đồ Karnaugh. 3. Vẽ mạch. 4

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính BÁO CÁO THỰC HÀNH

Bài 1: Thiết kế bộ MUX 4 đầu vào:

• Thực hiện trên Block Diagram.

• Kiểm tra thiết kế bằng Simulation Waveform.

• Đóng gói thiết kế thành symbol.

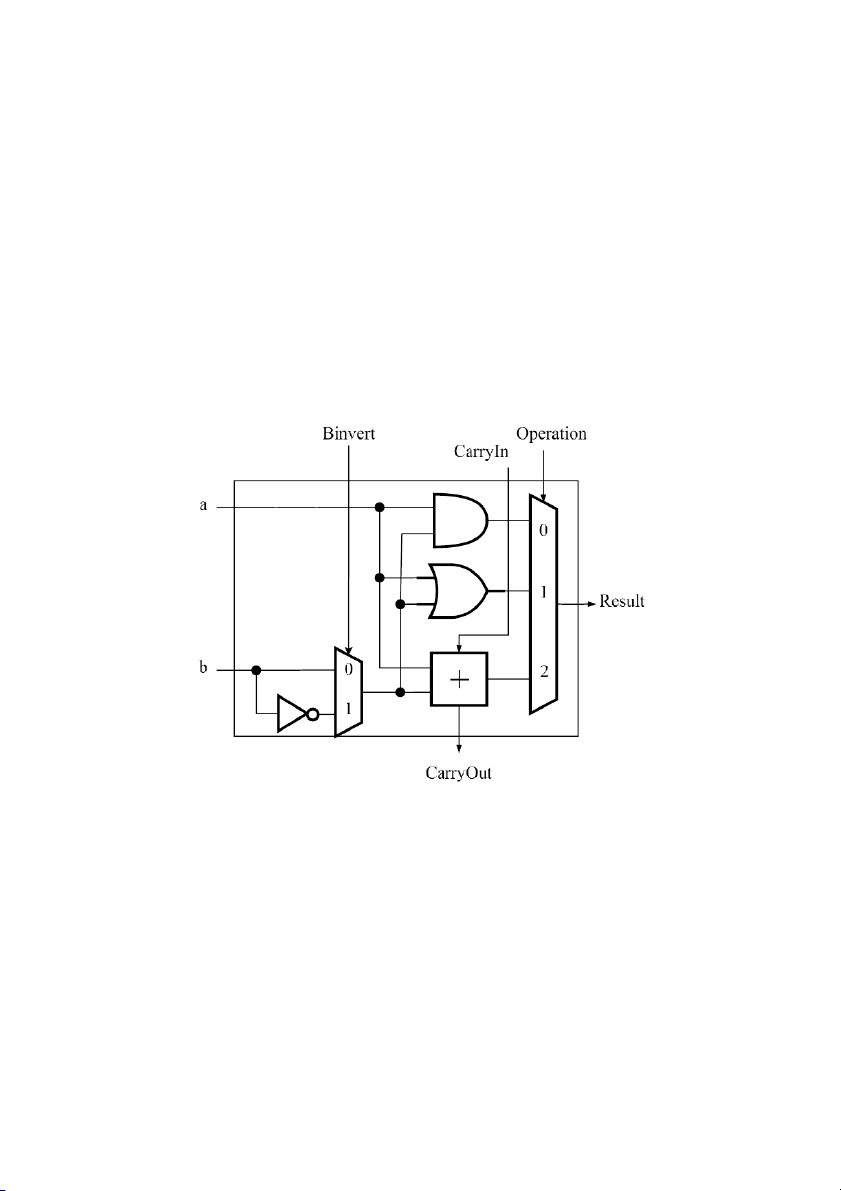

Bài 2: Thiết kế bộ ALU 1-bit như hình 1.

Bài 3: Thiết kế ALU 1-bit thực hiện phép AND, OR, cộng, và trừ như hình 5. Cho biết cách thực

hiện phép trừ từ kiến trúc này.

Hình 5. Kiến trúc ALU 1-bit: AND, OR, cộng, và trừ.

Bài 4: Thiết kế bộ ALU 8-bit: Đóng gói kết quả bài 3 thành symbol và sử dụng symbol này để thiết kế bộ ALU 8-bit.

Lưu ý: Sử dụng tính nắng group và thay đổi định dạng hiển thị (hex, dec) trong Simulation

Waveform để thuận tiện cho việc kiểm tra kết quả. 5

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

TÀI LIỆU THAM KHẢO

[1] Chap3_1 (Tài liệu trong thư mục doc)

[2] Introduction to Simulation of Verilog Designs. [Offline] Available:

/ntelFPGA_lite/21.1/quartus/common/help/tutorial_quartusii_simulation_verilog.pdf. 6