Preview text:

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

Bài 1: Giới thiệu công cụ thiết kế mạch số 1 Mục tiêu:

Kiến thức, kỹ năng sinh viên có được sau bài thực hành này:

• Tạo project cơ bản từ phần mềm Quartus Prime.

• Sử dụng Block Diagram thiết kế mạch số.

• Sử dụng Simulation Waveform kiểm tra tính đúng đắn của mạch số. 2 Nội dung:

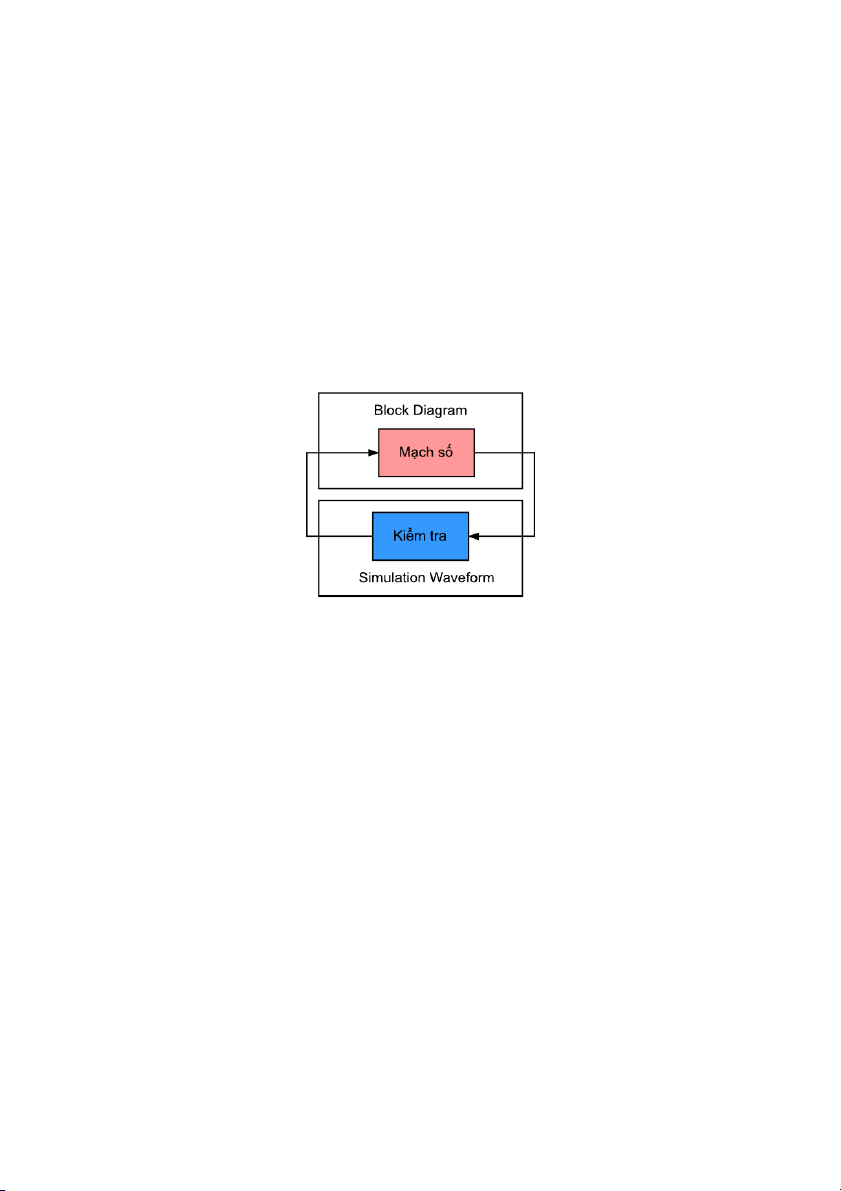

Hình 1. Mô hình thiết kế - k ểm tra. i

Bài thực hành này sử dụng mô hình thiết kế - kiểm tra được miêu tả trong hình 1, bao gồm

khối mạch số và khối kiểm tra. Khối mạch số được xây dựng từ Block Diagram bằng cách kết nối

các symbol như cổng AND, OR, NOT… thành các mạch mong muốn. Mạch số vừa được tạo ra,

kết nối với khối kiểm tra, khối kiểm tra được xây dựng bằng công cụ Simulation Waveform để

cung cấp các tín hiệu input và quan sát tín hiệu output của khối mạc .

h Nếu kết quả đầu ra không

chính xác như kết quả mong muốn, điều chỉnh lại mạch số và lặp lại bước kiểm tra, cho tới khi có

được kết quả chính xác.

2.1. Tạo project Quartus Prime

Mở phần mềm Quartus Prime Lite Edition 18.1 (Trong bài hướng dẫn sử dụng phiên bản

21.1, sinh viên có thể sử dụng các phiên bản khác).

Có 2 cách để tạo project: 1

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

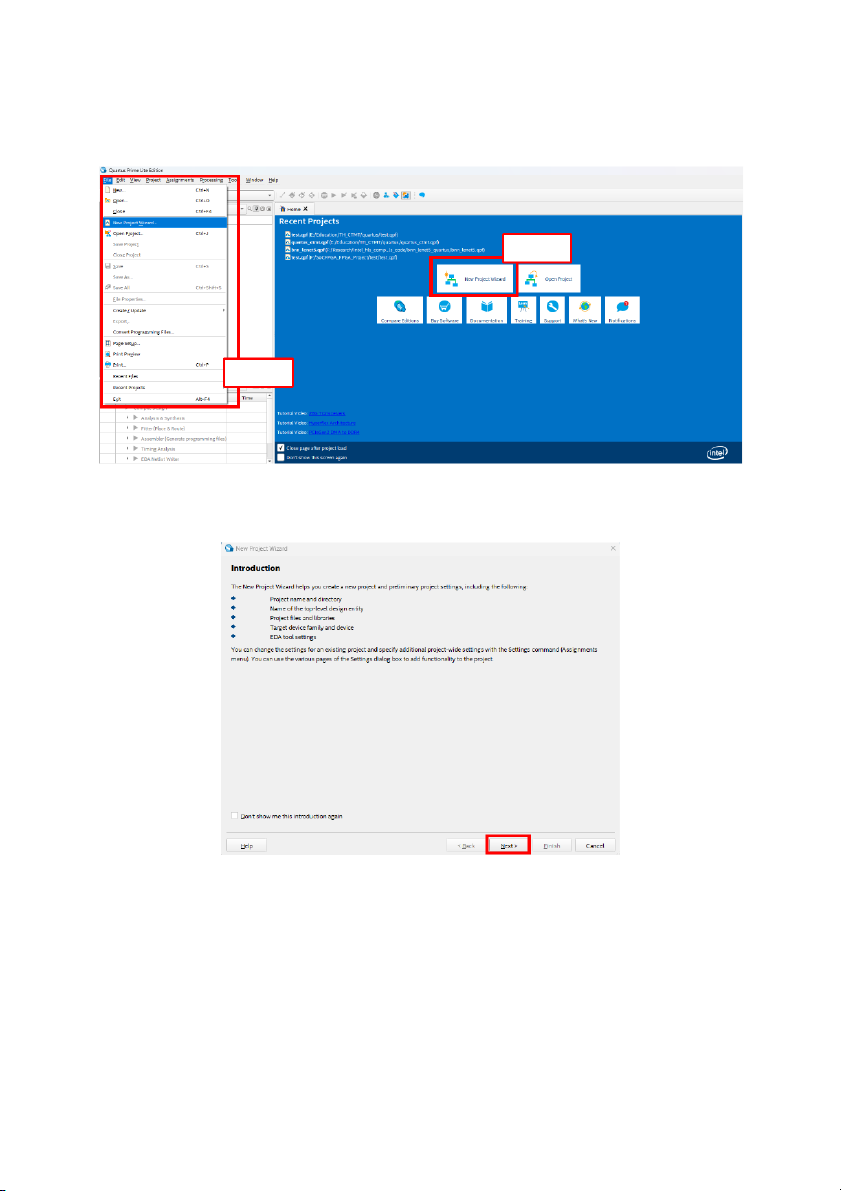

1. Chọn File →New Project Wizard… (như cách 1 trên hình 2).

2. Chọn New Project Wizard trên màn hình xanh ở giữa (như cách 2 trên hình 2). Cách 2 Cách 1

Hình 2. Giao diện chính của phần mềm Quartus Prime.

Sau đó, một cửa sổ New Project Wizard hiện lên, chọn Next.

Hình 3. Cửa sổ giới thiệu.

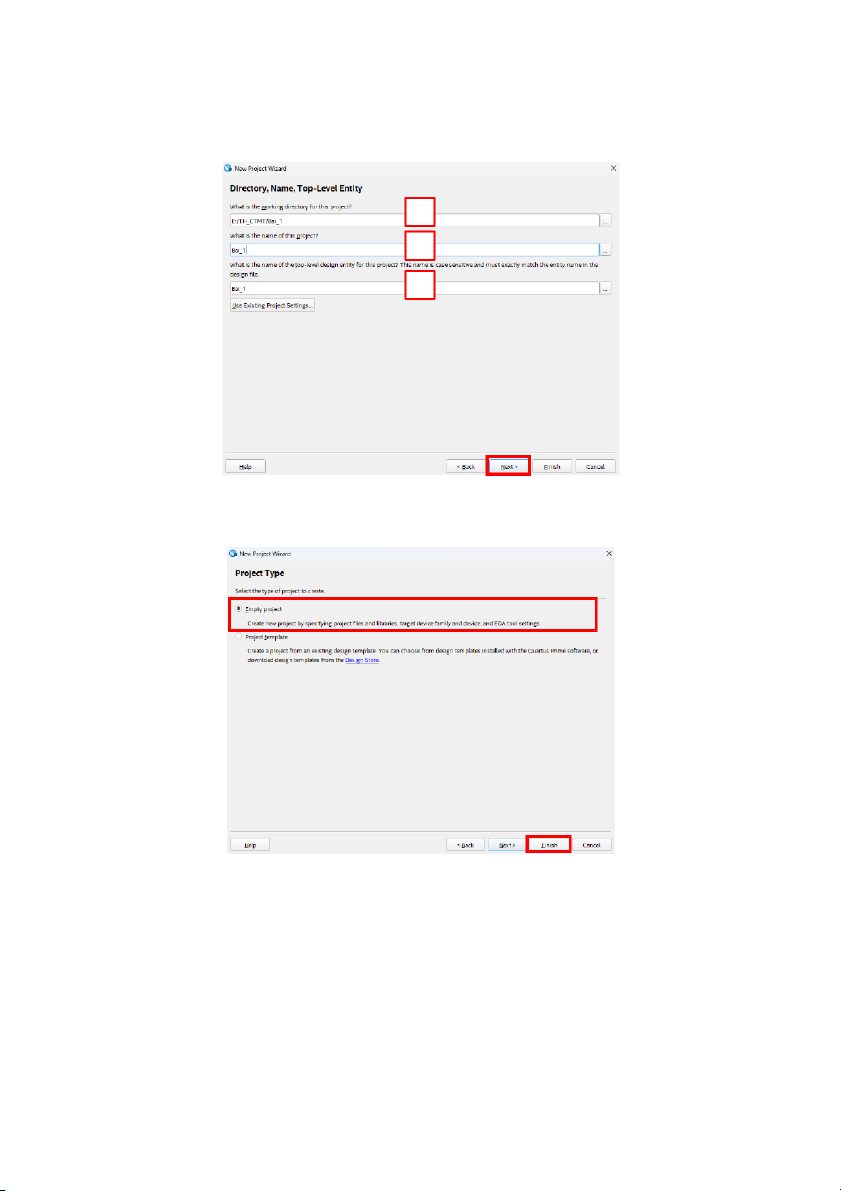

Tại của sổ Directory, Name, Top-Level Entity:

1. Chọn vị trí lưu project. Ví dụ: E:/TH_CTMT/Bai_1 (Tốt nhất là đường dẫn không có

khoảng trắng, không dấu). Lưu ý: Tạo trước một folder tại vị trí muốn lưu project.

2. Đặt tên project. Ví dụ: Bai_1. 2

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

3. Tên file top. Tên này sẽ được tự động tạo như tên project. Sau đó chọn Next. 1 2 3

Hình 4. Cửa sổ Directory, Name, Top-Level Entity.

Ở cửa sổ Project Type, chọn Empty project như Hình 5, và chọn Finish.

Hình 5. Của sổ Projec Type.

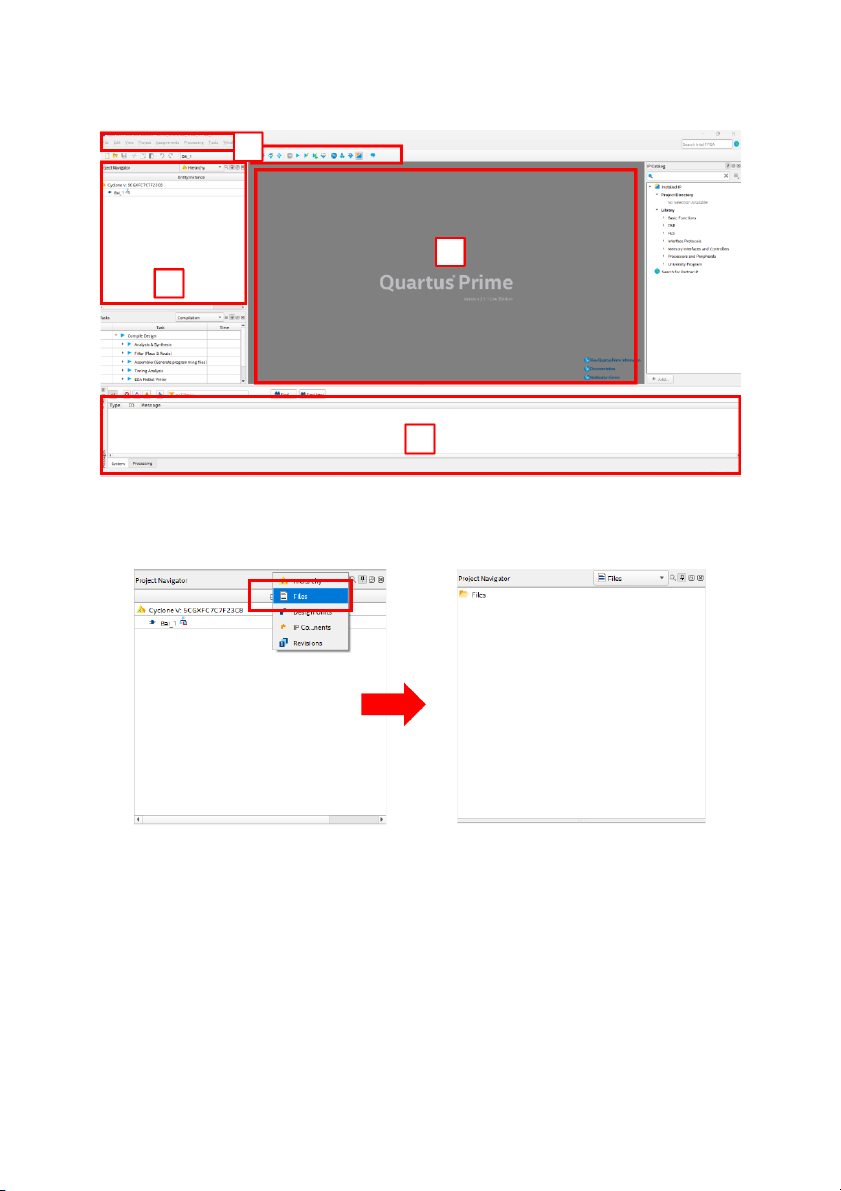

Sau khi hoàn tất, phần mềm có giao diện làm việc như hình 6.

1. Thanh Menu và thanh công cụ.

2. Cửa số quản lý file. 3. Cửa số làm việc. 3

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính 4. Cửa sổ thông báo. 1 3 2 4

Hình 6. Cửa sổ giao diện làm việc.

Tại cửa số quản lý file, Chọn Files để chuyển qua quản lý các file trong project (hình 7 và hình 8).

Hình 7. Cửa số q ản lý file: Hệ u t ố

h ng cấu trúc cấp bậc.

Hình 8. Cửa sổ q ản lý file: Files tr u ong project. 4

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

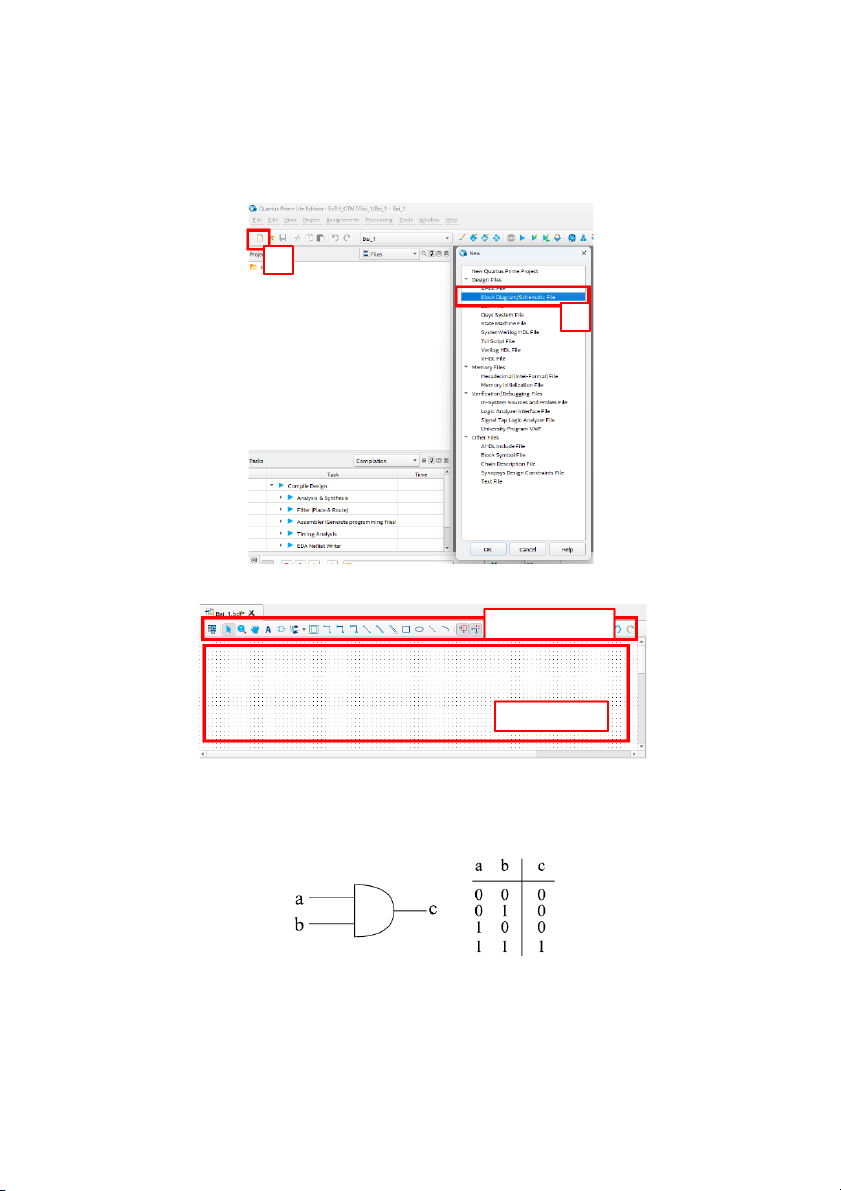

2.2. Tạo Block Diagram/Schematic File

Chọn New ( ố 1 trong hình 9 S

) → Block Diagram/Schematic File ( ố 2 trong hình 9 S ).

Xuất hiện cửa sổ làm việc như hình 10, bao gồm thanh công cụ và bảng thiết kế. 1 2

Hình 9. Tạo Block Diagram/Schematic File. Thanh công cụ Bảng thiết kế

Hình 10. Cửa sổ làm việc.

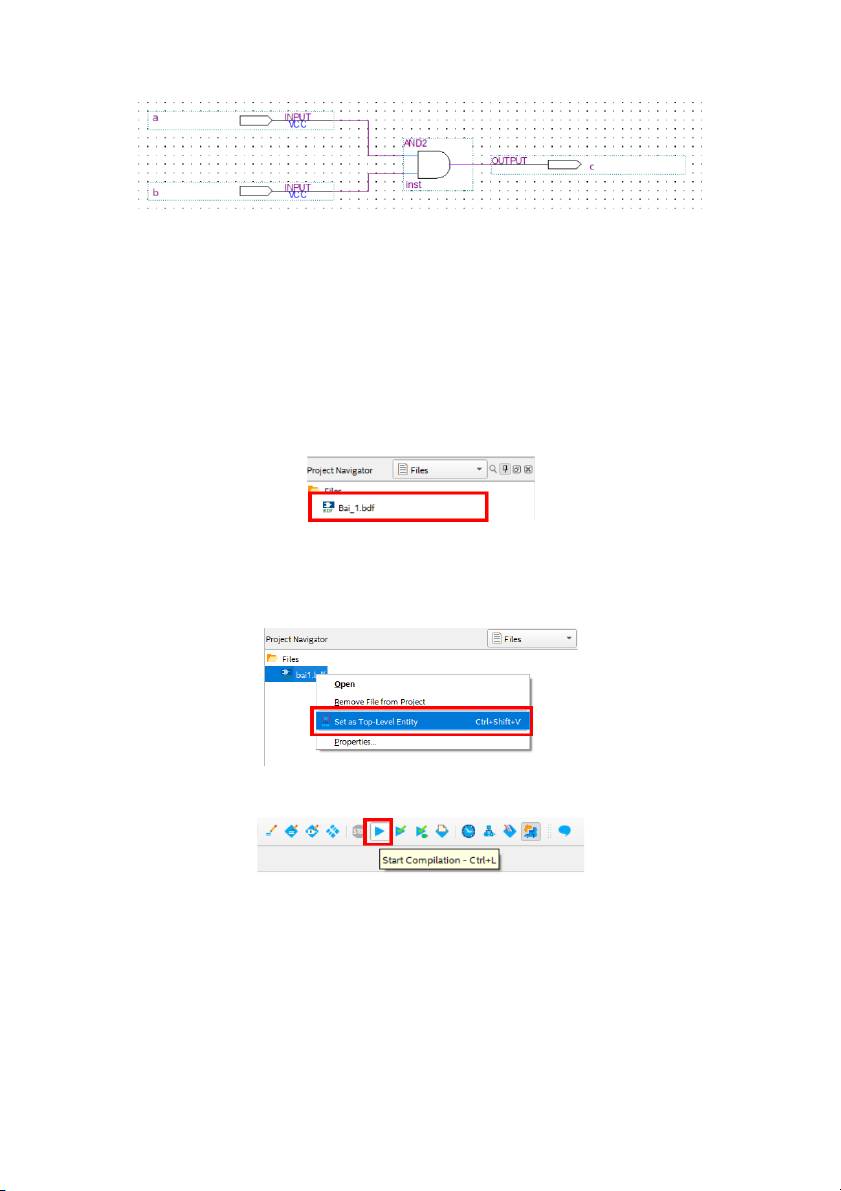

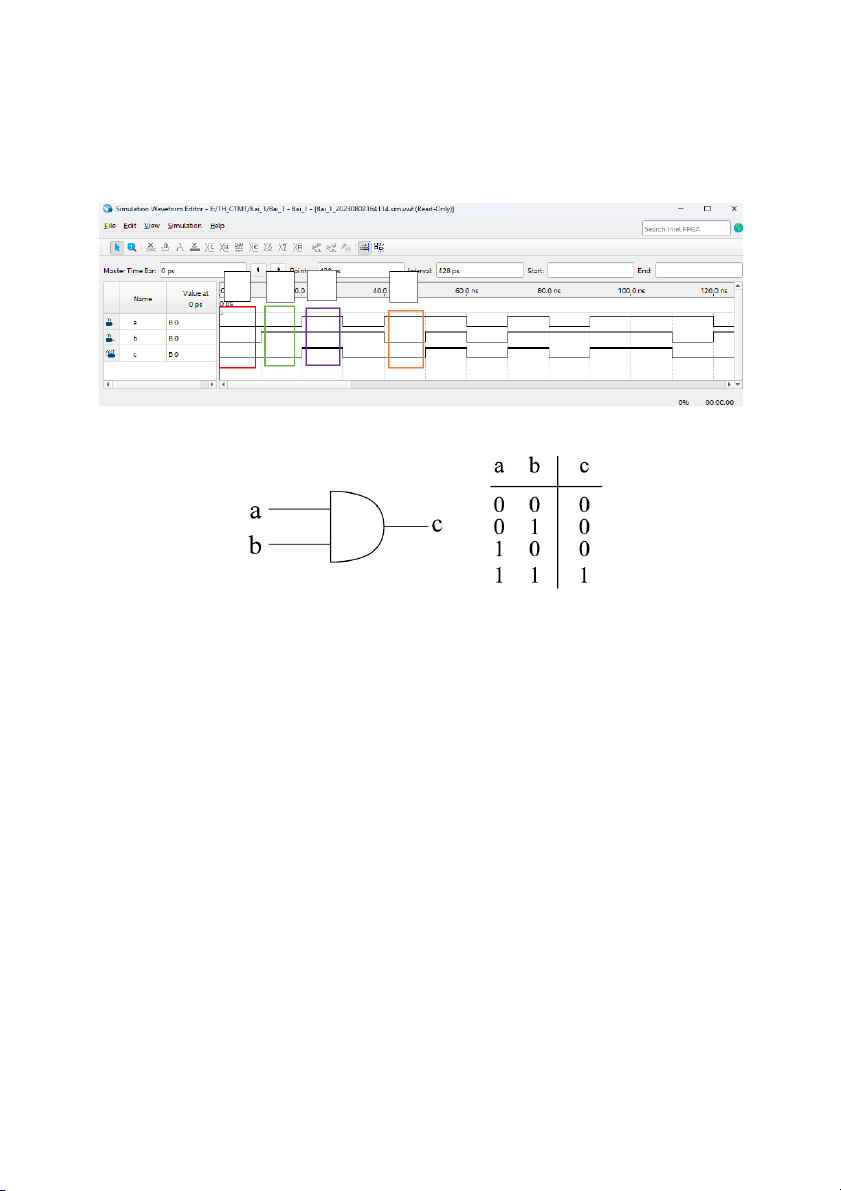

Bài hướng dẫn sử dụng cổng AND hai ngõ vào như ví dụ (hình 11), với “a” và “b” là hai

input của của AND, “c” là output. Hình 11. Cổng AND. 5

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

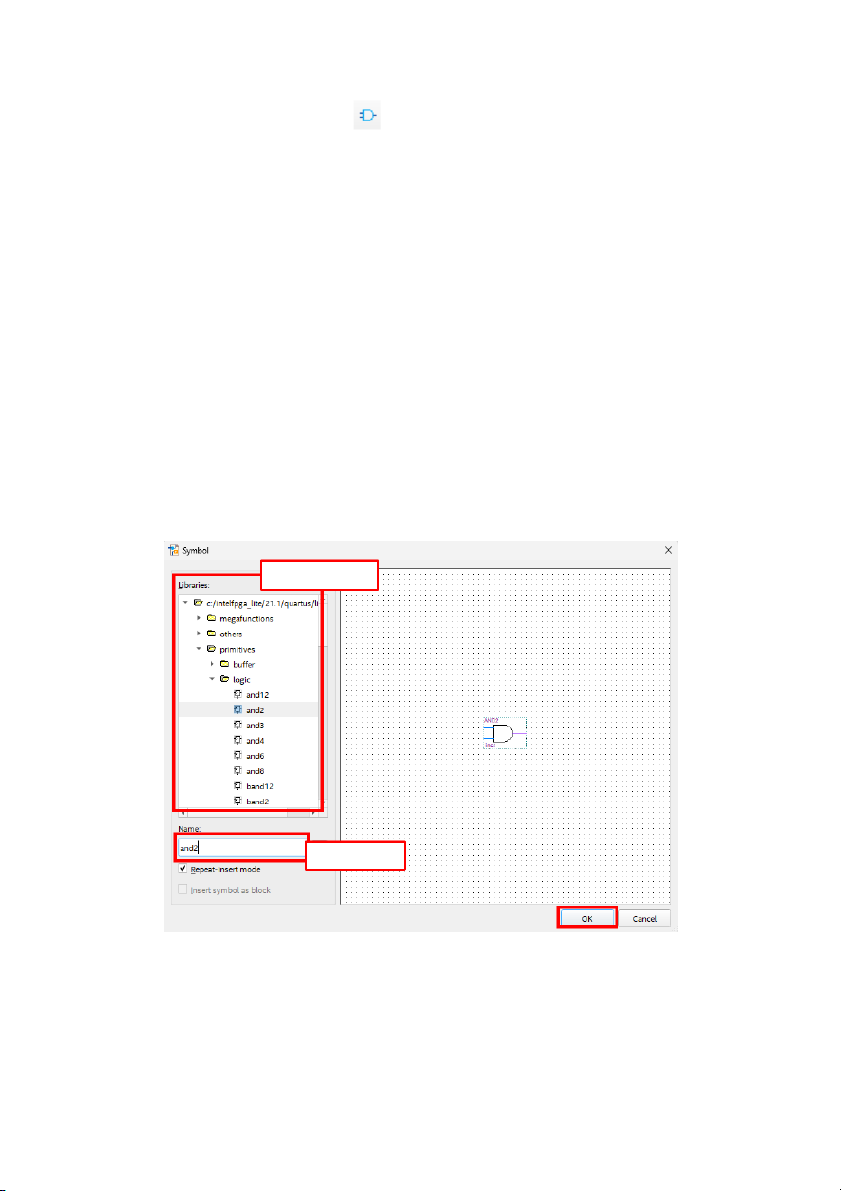

Chọn biểu tượng Symbol Tool

trên thanh công cụ. Một cửa sổ Symbol xuất hiện. Mở

rộng các cấp trong Libraries box như hình 12. Trong libraries có 3 thư mục chính: megafunctions,

others và primitives. Trong chuỗi bài thực hành này, chúng ta chỉ quan tâm thư mục primitives,

đây là thư mục chứa các cổng logic cơ bản: AND, OR, NOT, XOR…. 2.2.1. Cổng logic

Có 2 cách để c ọn symbol: h

1. Tìm kiếm symbol trên Libraries box bằng cách mở rộng các thư mục.

2. Sử dụng ô tìm kiếm (Ô tìm kiếm trong hình 12), cách này đòi hỏi phải tìm kiếm bằng từ

khóa chính xác. Ví dụ: tìm kiếm cổng AND hai đầu vào thì phải tìm kiếm với từ khóa

“and2”, tìm kiếm chỉ với từ khóa “and” sẽ báo lỗi không tìm thấy symbol.

Sau khi chọn xong symbol, chọn OK và đặt symbol vào bảng thiết kế như hình 13. Số lần

click chuột trái sẽ tương ứng với số lần xuất hiện của symbol đó trên bảng thiết kế, để thoát nhấn phím ESC. Libraries box ô tìm kiếm

Hình 12. Chọn symbol từ thư viện. 6

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

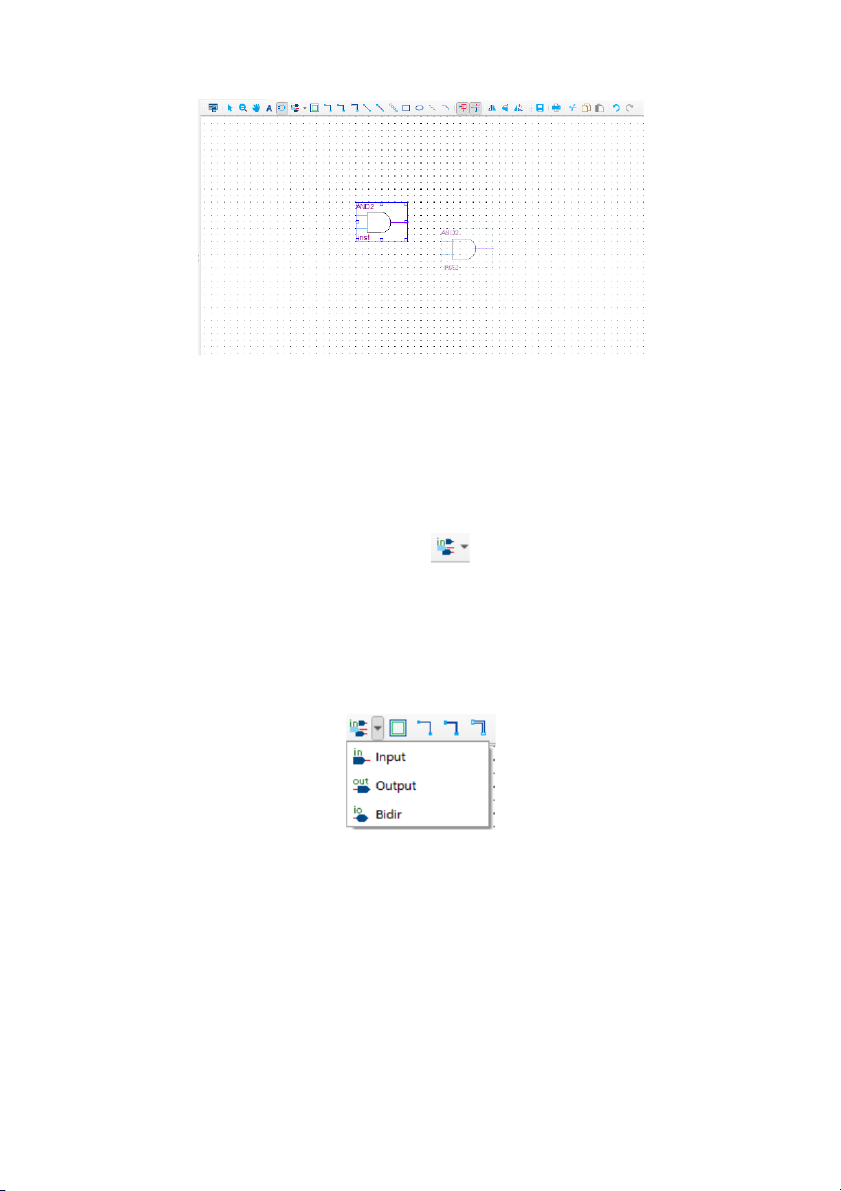

Hình 13. Đặt symbol trên bảng thiết kế.

2.2.2. Input và output

Input là nơi cung cấp dữ liệu đầu vào cho mạch số, ví dụ cổng AND như hình 11, thì cần

đưa giá trị 0 hoặc 1 vào “a” và “b”, trong khi đó “c” kết nối đến đầu ra, sau đó chúng ta theo dõi

đầu ra này để kiểm tra tính đúng đắn của mạch số.

Chọn vào mũi tên của biểu tượng Pin Tool

ở thanh công cụ, có 3 cổng xuất hiện như hình 14:

• Input: Cổng đầu vào. • Output: Cổng đầu ra.

• Bidir: Cổng có thể hoạt động như đầu vào hoặc đầu ra.

Hình 14. Ba cổng: Input, Output và Bidir.

Trong ví dụ cổng AND, chúng ta chọn 2 input và 1 output đặt lên bảng thiết kế như hình 15. 7

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

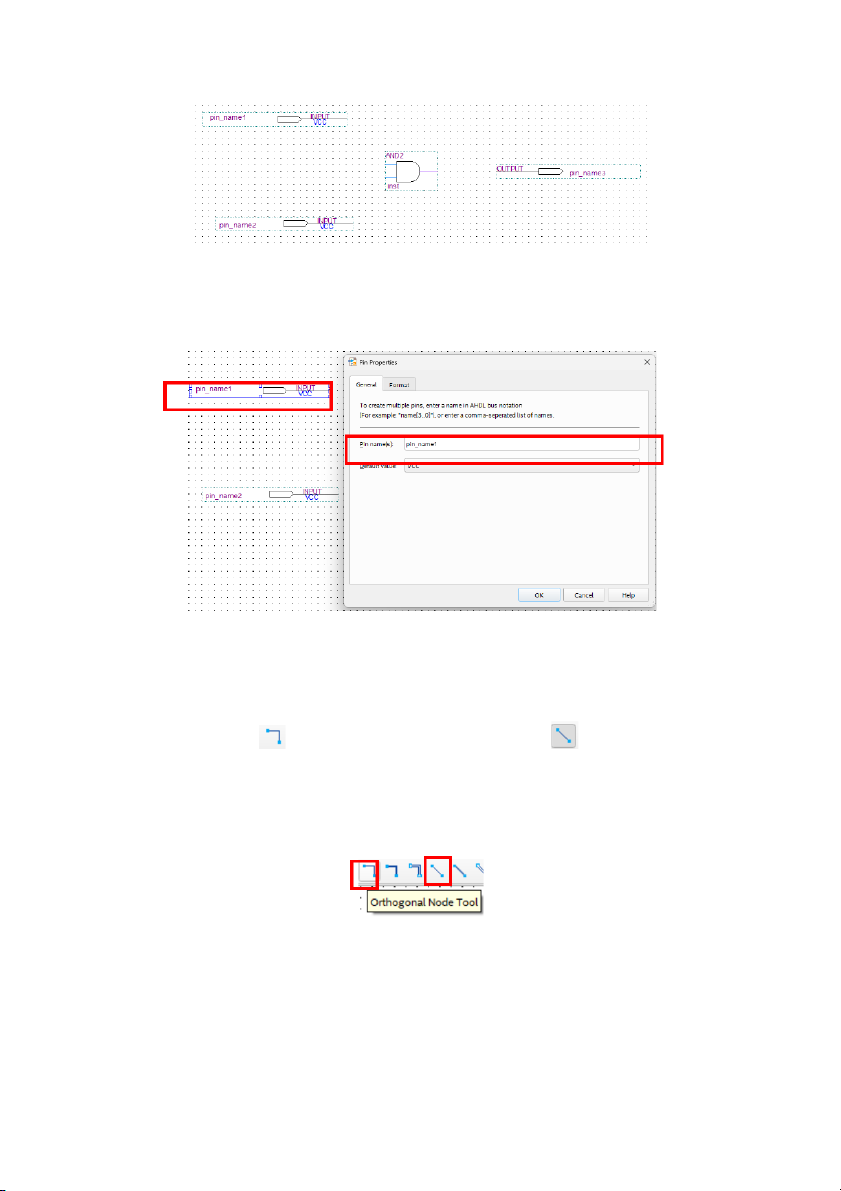

Hình 15. Đặt Input và Output lên bảng thiết kế.

Đổi tên cho symbol, chuột trái vào symbol muốn đổi tên, chuột phải → Properties, cửa

sổ Pin Properties xuất hiện như hình 16. Thay đổi tên tại trường Pin name(s).

Hình 16. Đổi tên cho symbol.

2.2.3. Kết nối symbol

Kết nối các symbol trên bảng thiết kế, chúng ta sử dụng dây (wire), chọn biểu tưởng Orthogonal Node Tool

như hình 17 hoặc Diagonal Node Tool . Chọn vào symbol muốn

kết nối và giữ chuột di chuyển đến symbol còn lại. Kết quả sau khi kết nối như hình 18. Đầu vào

input “a” và input “b” kết nối đến hai đầu vào của AND2, đầu ra của AND2 được kết nối đến output “c”.

Hình 17. Orthogonal và Diagonal Node Tool. 8

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

Hình 18. Kết quả sau khi kết nối. 2.2.4. Biên dịch

Trước khi biên dịch, cần lưu lại mạch số vừa thiết kế. Lưu bằng cách nhấn tổ hợp phím

“CTRL + s”, và lưu với tên tùy ý (không dấu và không khoảng trắng) vào trong thư mục project

đã tạo ở trên với đuôi file là bdf.

Sau khi lưu bên cửa sổ quản lý file xuất hiện file vừa thiết kế, ví dụ trong hình 19 là Bai_1.bdf.

Hình 19. Lưu file bdf.

Chuột phải vào file vừa lưu, chọn “Set as Top-Level Entity” để c ọn h file để biên dịch.

Trong trường hợp có nhiều file thiết kế, đây là cách để c ọn file để dịch và thực thi. h

Để biên dịch thiết kế, chọn Start Compilation trên thành công cụ như hình 20.

Hình 20. Biểu tượng biên dịch chương trình.

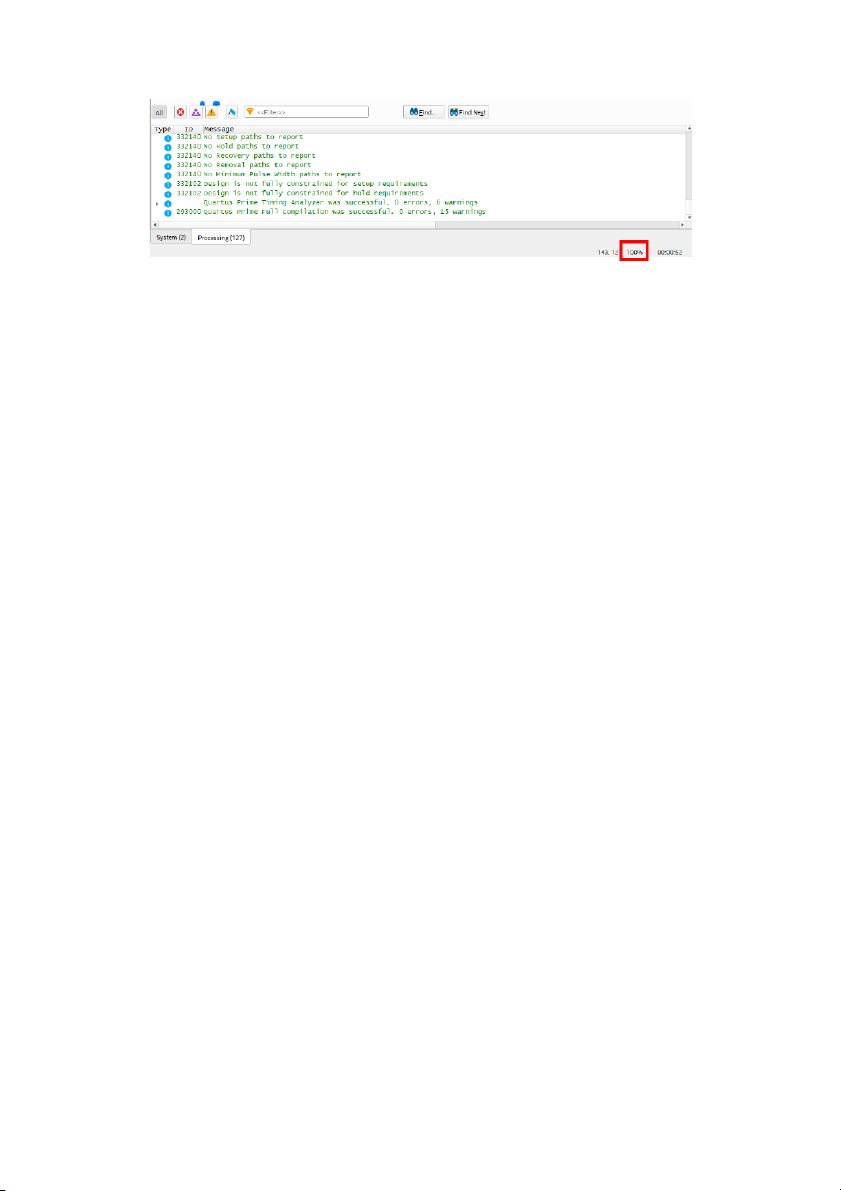

Sau khi biên dịch thành công, góc phải của cửa sổ thông báo hiển thị 100% và không xuất hiện bất cứ lỗi nào. 9

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

Hình 21. Biên dịch thành công. 10

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

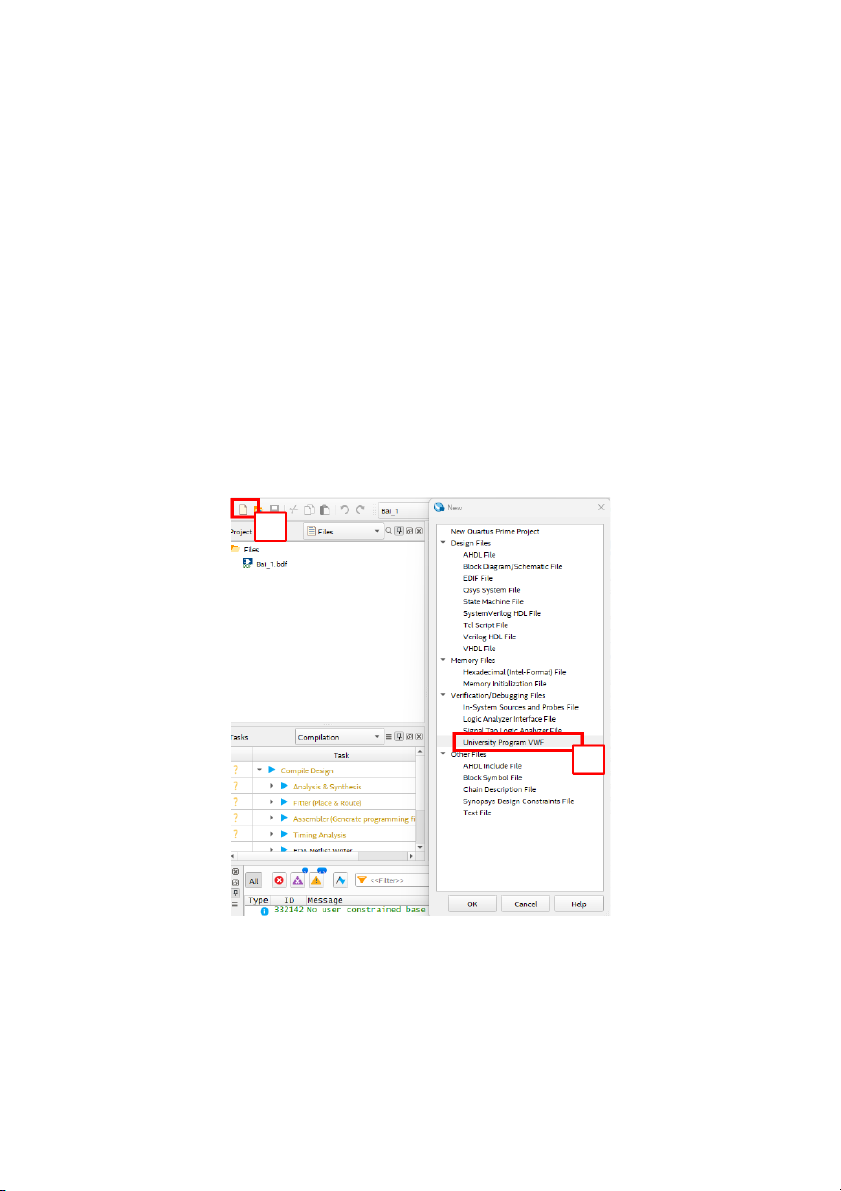

2.3. Tạo University Program VWF

Để kiểm tra tính đúng đắn của mạch số, cần tạo tín hiệu input, sau đó quan sát và so sánh

tín hiệu output với bản chân trị của mạch số. Việc tạo tín hiệu input và quan sát tín hiệu output

được thực hiện bằng dạng sóng mô phỏng (Simulation Waveform).

Chọn New → University Program VWF như hình 22.

Xuất hiện giao diện Simulation Waveform Editor như hình 23, bao gồm các thành phần chính:

1 Thanh Menu: File, Edit, Simulation… 2 Thanh công cụ.

3 Cửa sổ tên và kiểu dữ liệu của input và output. 4 Cửa số làm việc. 5 Trục thời gian. 1 2

Hình 22. Tạo Simulation Waveform. 11

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính 1 2 5 4 3

Hình 23. Cửa sỏ Simulation Waveform Editor.

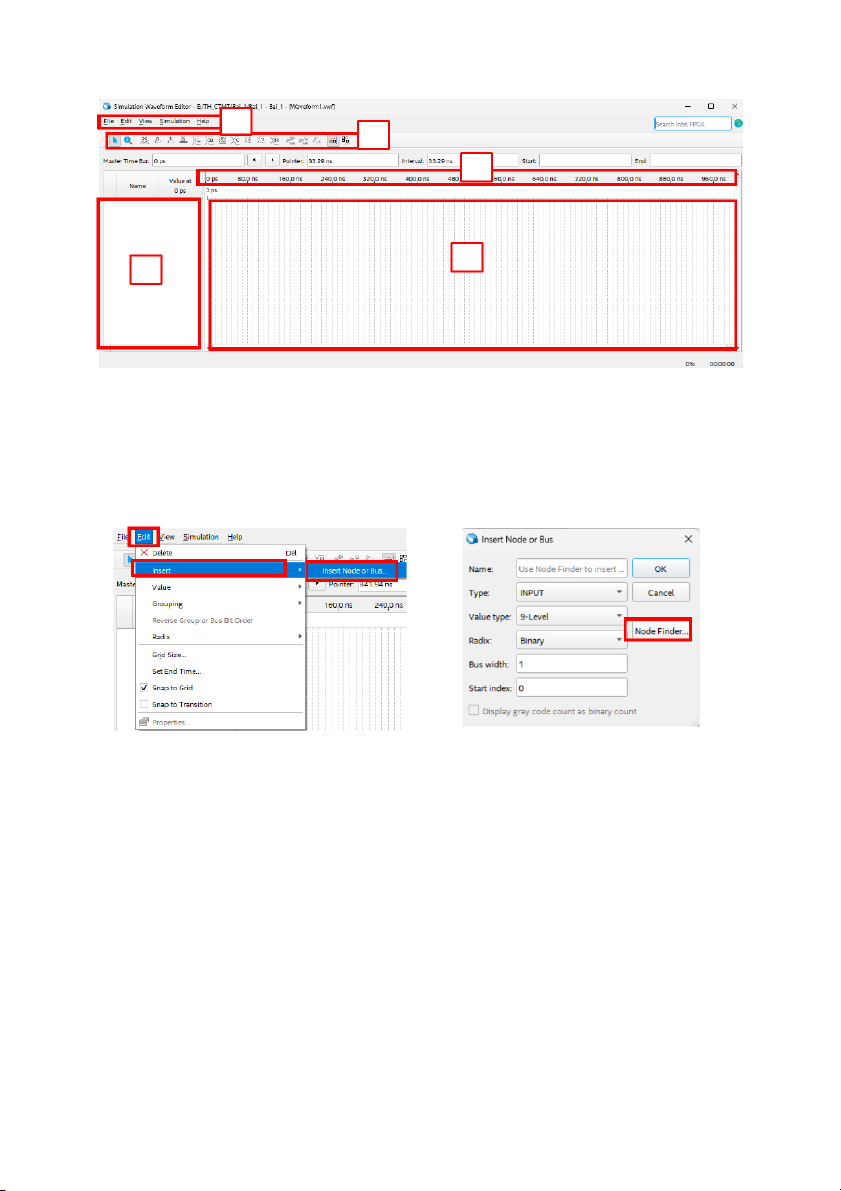

2.3.1. Thêm tín hiệu c

ủa mạch số vào mô phỏng Trên thanh , chọn Menu

Edit → Insert → Insert Node or Bus… (hình 24).

Tại cửa sổ Insert Node or Bus, chọn Node Finder… (hình 25).

Hình 24. Chọn Insert Node or Bus...

Hình 25. Cửa sổ Insert Node or Bus.

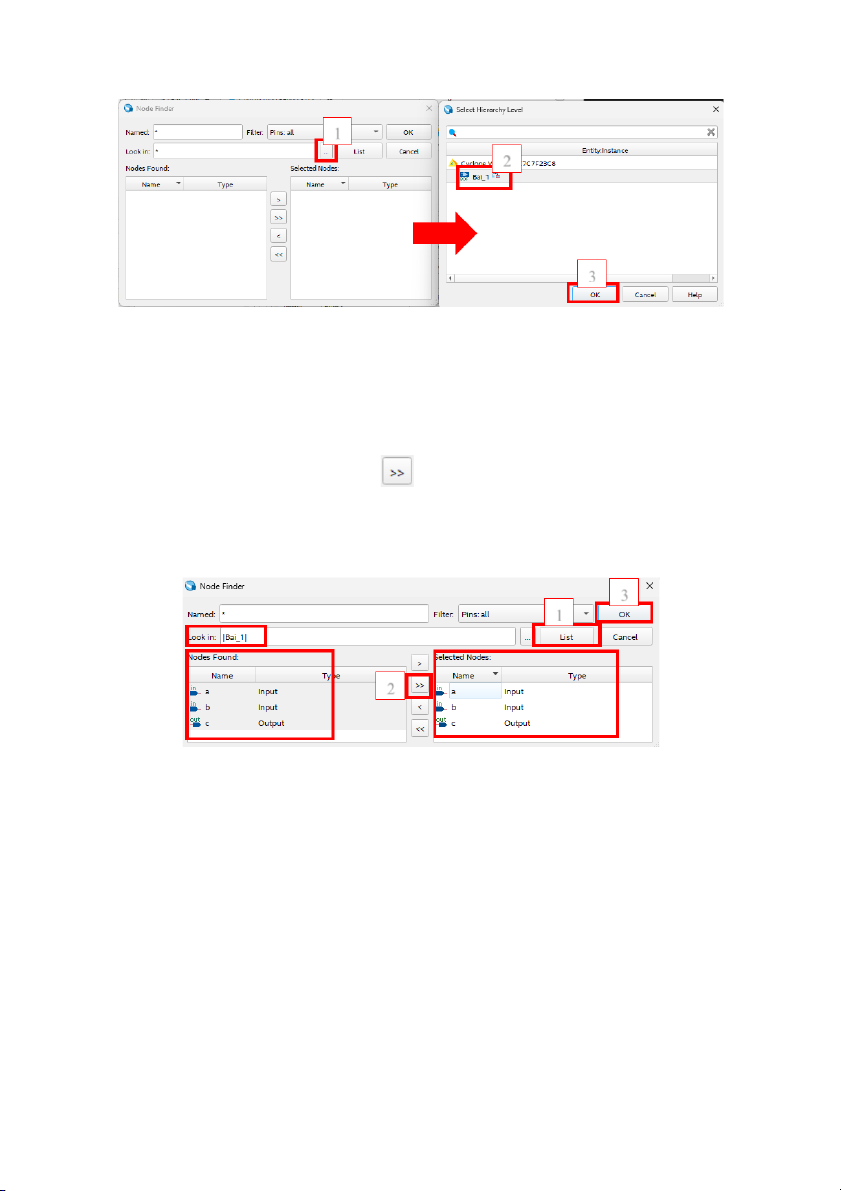

Trong cửa sổ Node Finder, chọn vào nút “ ”, và chọn vào …

top-file → OK. (Hình 25). 12

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính 1 2 3

Hình 26. Tìm kiếm top-file.

Sau đó tên file vừa chọn sẽ hiển thị tại trường Look in. Chọn List ( ố

S 1 trên hình 27) để liệt kê các đầu vào và đầu ra của thiết kế, Kết quả xuất

hiện trong cửa sổ Nodes Found.

Để lựa chọn các tín hiệu này chọn ( ố

S 2 trên hình 27), các tín hiệu này sẽ xuất hiện

trong cửa sở Selected Nodes.

Chọn OK để kết thúc. (Số 3 trên hình 27). 3 1 2

Hình 27. Chọn tín hiệu.

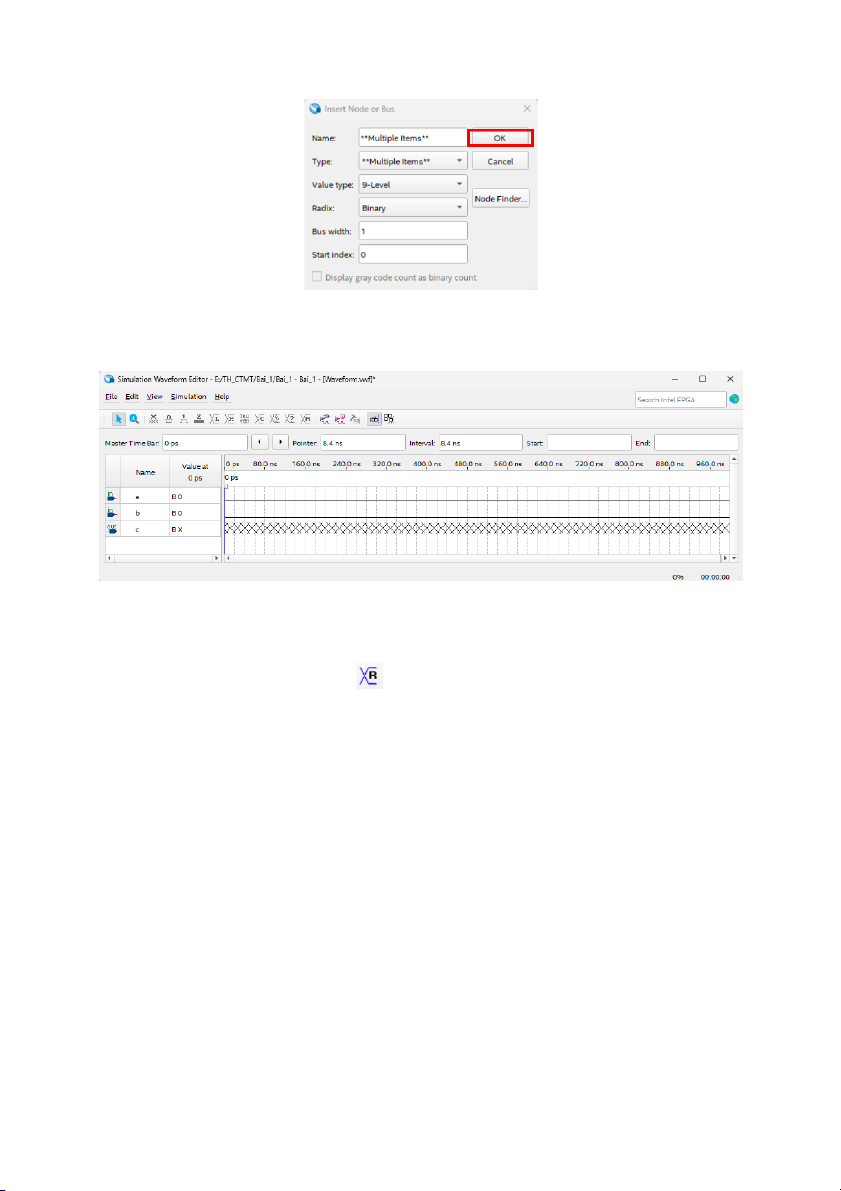

Xuất hiện cửa sổ Insert Node or Bus, lúc này ở trường

Name và Type, xuất hiện

“**Multiple items**”, chọn OK. 13

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

Hình 28. Kết thúc quá trình thêm tín hiệu.

Kết quả đạt được như hình 29, tín hiệu “a”, “b”, và “c” đã được thêm vào.

Hình 29. Kết quả sau khi thêm tín hiệu input và output của phần cứng.

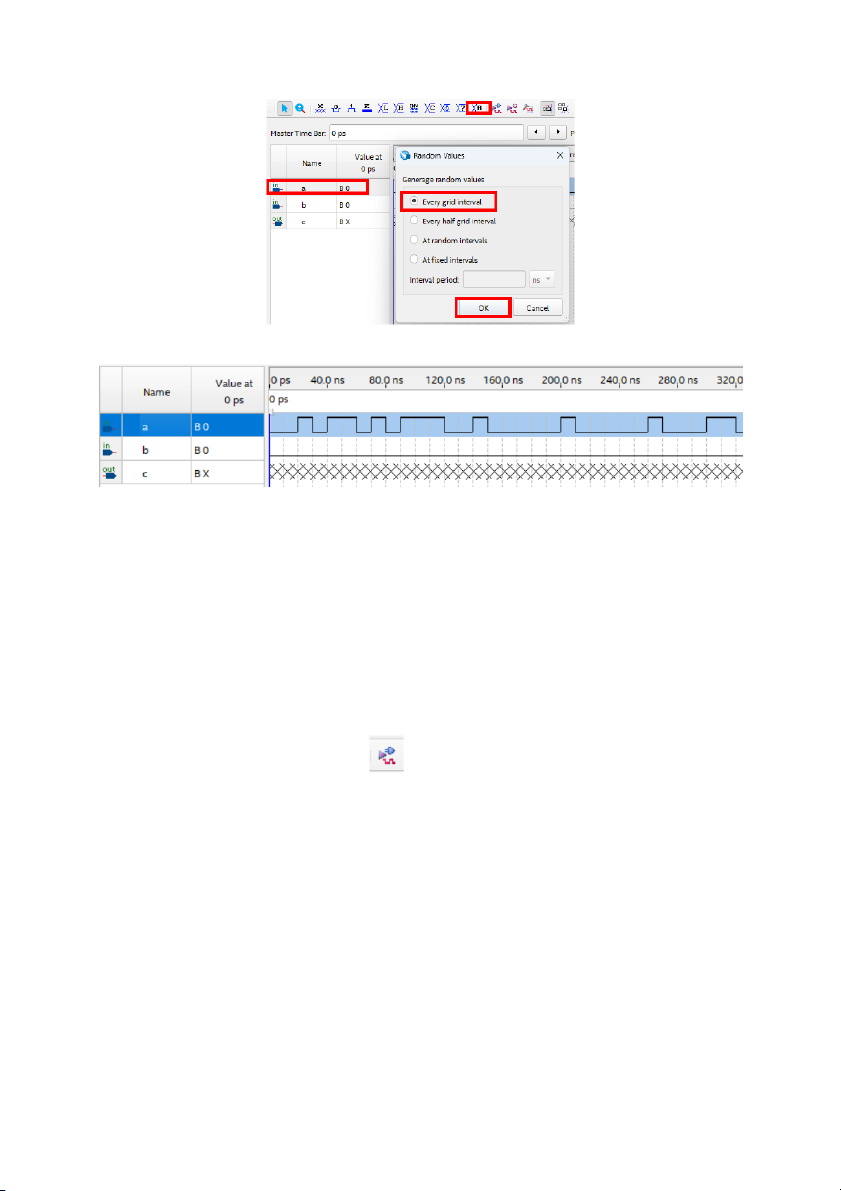

2.3.2. Tạo giá trị cho tín hiệu ủ c a mạch số

Chọn vào tín hiệu “a” → c ọn h

để tạo sóng ngẫu nhiên → Chọn Every grid interval

(Các lựa chọn khác là các cách tạo sóng khác, sinh viên có thể tự tìm hiểu) → OK.

Chú ý: Một grid interval tương ứng với khoảng cách giữa 2 đường thẳng nét đứt. Mắc

định grid interval là 10.0 ns, để thay đổi giá trị này chọn Edit → Grid Size.

Kết quả sau khi tạo sóng cho tín hiệu “a” như hình 31.

Làm tương tự đối với tín hiệu “b”.

Tín hiệu “c” là output nên không nên tạo tín hiệu. 14

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

Hình 30. Tạo sóng cho tín hiệu "a".

Hình 31. Kết quả tạo sóng ngẫu nhiên cho tín hiệu "a".

2.3.3. Khởi chạy mô phỏng

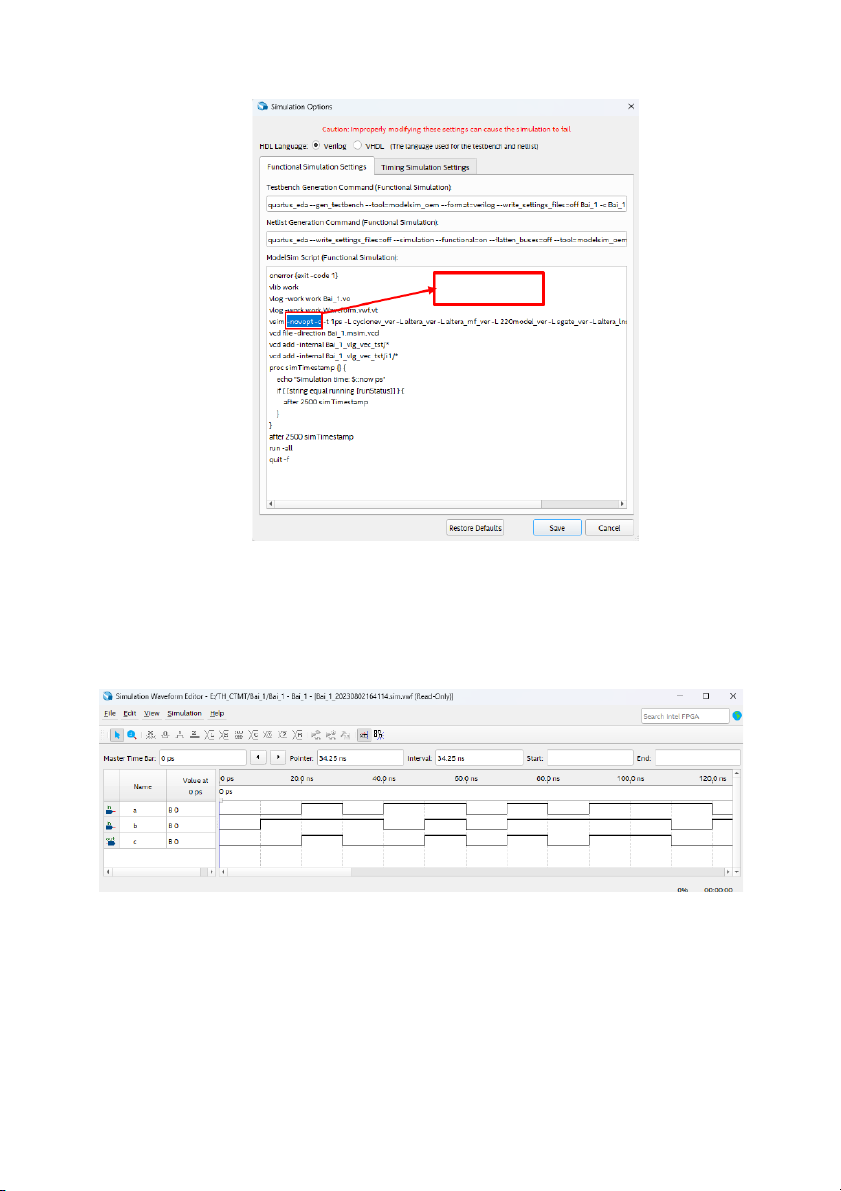

Điều chỉnh script trước khi chạy mô phỏng (hình 32):

• Chọn Simulation → Simulation Setting.

• Tại cửa sổ Simulation Options, trong tab Functional Simulation Settings, thay đổi “-

novopt -c” thành “-voptargs=+acc". • Chọn Save.

Chọn Run Functional Simulation

trên thanh công cụ, kết quả mô phỏng xuất trên cửa số mới như hình 33. 15

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính -voptargs=+acc

Hình 32. Thay đổi simulation script.

Lưu file mô phỏng: CTRL + S với tên và đường dẫn mặc định (không thay đổi tên và đường dẫn).

Hình 33. Kết quả mô phỏng. 16

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

2.3.4. Đọc và kiểm tra kết quả mô phỏng 1 2 3 4

Hình 34. Đọc kết quả mô phỏ ng.

• Tại thời điểm 1 trên hình 34, input “a” = 0, input “b” = 0, và output “c” = 0 → Đúng so với

bản chân trị: 0 & 0 = 0.

• Tại thời điểm 2 trên hình 34, input “a” = 0, input “b” = 1, và output “c” = 0 → Đúng so với

bản chân trị: 0 & 1 = 0.

• Tại thời điểm 3 trên hình 34, input “a” = 1, input “b” = 1, và output “c” = 1 → Đúng so với

bản chân trị: 1 & 1 = 1.

• Tại thời điểm 4 trên hình 34, input “a” = 1, input “b” = 0, và output “c” = 1 → Đúng so với

bản chân trị: 1 & 0 = 0. 17

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

BÀI TẬP CHUẨN BỊ Ở NHÀ

Bài tập: Cho biết ý nghĩa của các công cụ . 18

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính BÁO CÁO THỰC HÀNH

Bài 1: Thiết kế cổng XOR từ các cổng AND, OR và NOT.

Bài 2: Thiết kế cổng XOR từ cổng NAND.

Bài 3: Thiết kế mạch cộng bán phần.

Bài 4: Thiết kế mạch cộng toàn phần. 19

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

TÀI LIỆU THAM KHẢO

[1] Quartus Prime Introduction Using Schematic Designs. [Online] Available:

https://ftp.intel.com/Public/Pub/fpgaup/pub/Teaching_Materials/current/Tutorials/Schematic/Qua rtus_II_Introduction.pdf

[2] Introduction to Simulation of Verilog Designs. [Offline] Available:

/ntelFPGA_lite/21.1/quartus/common/help/tutorial_quartusii_simulation_verilog.pdf. 20