Preview text:

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

Bài 4: Giới thiệu Nios II assembly 1 Mục tiêu:

Kiến thức, kỹ năng sinh viên có được sau bài thực hành này: Làm quen với ngôn ngữ

assembly và môi trường lập trình cho CPU Nios II. 2 Nội dung:

2.1. Giới thiệu CPU Nios II

CPU Nios II được xây dựng dựa trên kiến trúc Reduced Instruction Set Computer

(RISC). Các phép toán số học và logic học được thực hiện trên các thanh ghi đa

dụng (general purpose registers). Dữ liệu giữa thanh ghi đa dụng và bộ nhớ được trao đổi

với nhau thông qua các lệnh Load và Store. Các thanh ghi trong NIOS II có độ dài 32-bit

theo kiểu little-endian. NIOS II sử dụng hai đường bus riêng biệt để truy cập lệnh

(instruction) và dữ liệu (data) theo kiến trúc Harvard.

CPU NIOS II có 32 thanh ghi đa dụng, mỗi thanh ghi 32 bits như được liệt kê ở Hình 2.1.

Một vài thanh ghi trong đó có chức năng và tên đặc biệt.

• Thanh ghi r0: còn được gọi là thanh ghi zero do luôn chứa giá trị 0. Thanh ghi này chỉ cho phép đọc.

• Thanh ghi r1: được dùng như thanh ghi tạm bởi Assembler.

• Thanh ghi r24 đến r29: được dùng trong các quá trình exceptions, không có sẵn trong User mode.

• Thanh ghi r25 đến r30: được dùng bởi JTAG Debug module.

• Thanh ghi r27 đến r28: được dùng để điều khiển stack.

• Thanh ghi r31: chứa địa chỉ trả về khi thực hiện quá trình gọi hàm. 1

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

2.2. Một số lệnh assembly cơ bản Nhóm lệnh Lệnh Ví dụ Load & Store ldw (Load Word) ldw r2, (r3) Instruction stw (Store Word) stw r2, (r3) add (Add Registers) add r2, r3, r4 Arithmetic addi (Add Immediate) addi r2, r3, 6 Instruction sub (Subtract Registers) sub r2, r3, r4 subi (Subtract Immediate) subi r2, r3, 6 and (AND Registers) and r2, r3, r4 andi (AND Immediate) andi r2, r3, 6 Logic xor (XOR Register) xor r2, r3, r4 Instruction xori (XOR Immediate) xori r2, r3, 6 or (OR Register) or r2, r3, r4 ori (OR Immediate) ori r2, r3, 16 mov mov r2, r3 Move movi movi r2, 6 Instruction movia movia r2, label

2.3. Chỉ thị cho trình biên dịch assembly (Assembly Directives) Assembler Directives Mô tả

A string of ASCII characters is loaded into consecutive byte .ascii "string"

addresses in the memory. Multiple strings, separated by commas, can be specified.

This directive is the same as .ascii, except that each string is .asciz "string"

followed (terminated) by a zero byte.

Expressions separated by commas are specified. Each

.byte expressions

expression is assembled into the next byte.

Identifies the data that should be placed in the data section of the .data

memory. The desired memory location for the data section can 2

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

be specified in the Intel FPGA Monitor Program’s system configuration window.

Marks the end of the source code file; everything after this .end

directive is ignored by the assembler.

.equ symbol, expression

Sets the value of symbol to expression. .global symbol

Makes symbol visible outside the assembled object file.

Expressions separated by commas are specified. Each

.hword expressions

expression is assembled into a 16-bit number.

Provides a mechanism for including supporting files in a source

.include "filename" program.

Advances the location counter by new-lc, where new-lc is used

as an offset from the starting location specified in the Intel FPGA .org new-lc

Monitor Program’s system configuration window. The .org

directive may only increase the location counter, or leave it

unchanged; it cannot move the location counter backwards.

Emits the number of bytes specified in size; the value of each .skip size byte is zero

Identifies the code that should be placed in the text section of the

memory. The desired memory location for the text section can .text

be specified in the Intel FPGA Monitor Program’s system configuration window.

Expressions separated by commas are specified. Each

.word expressions

expression is assembled into a 32-bit number.

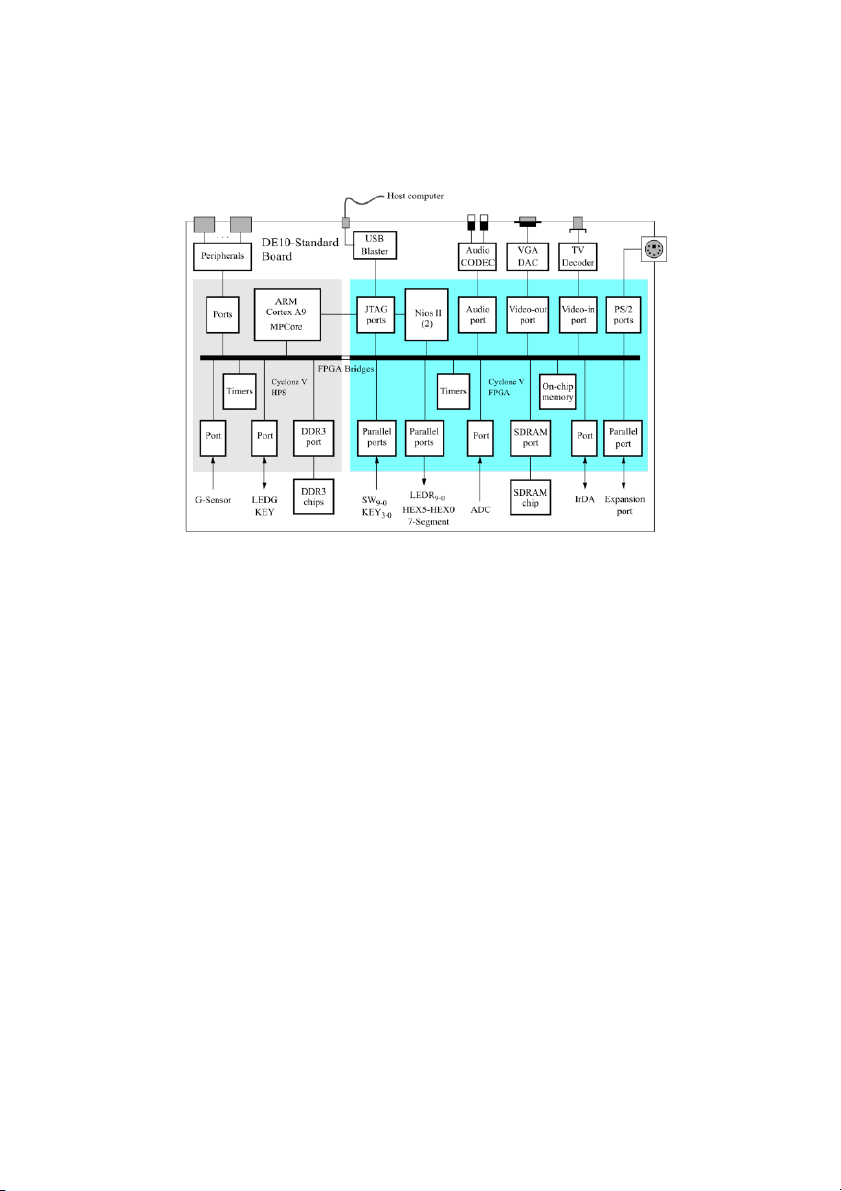

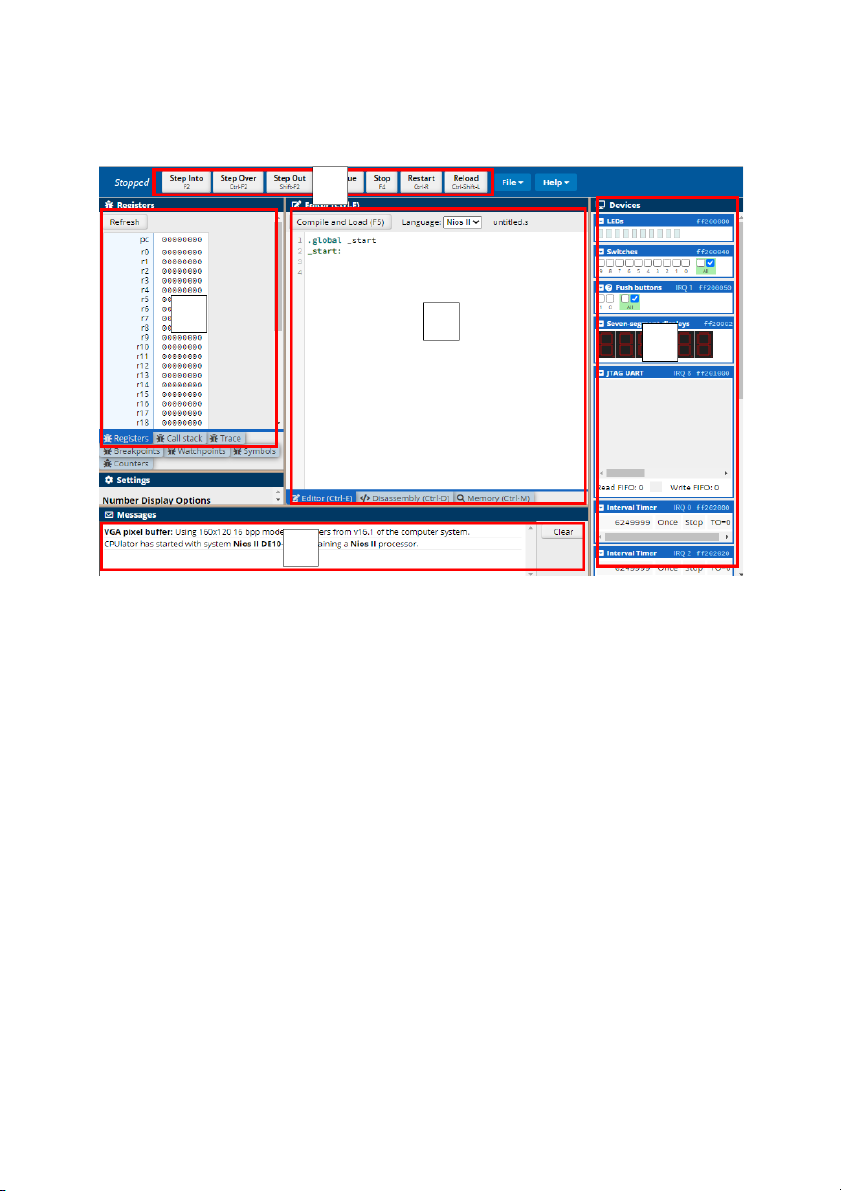

2.4. DE10-Standard Computer

DE10-Standard Computer là một hệ thống máy tính đơn giản được sử dụng trong

các khóa học về máy tính và hệ thống nhúng. Hệ thống được triển khai trên board FPGA

DE10-Standard của Intel. DE10-Standard Computer chỉ chứa một vài thành phần cơ bản

như: CPU NIOS II, bộ nhớ, và một số thiết bị ngoại vi I/O đơn giản. Hệ thống DE10- 3

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

Standard Computer được thể hiện trên hình 1. Trong bài thực hành này, chúng ta sử dụng CPU

NIOS II giao tiếp với bộ nhớ SDRAM bằng lệnh load và store.

Hình 1. Sơ đồ k ối hệ h

thống DE10-Standard Computer. 4

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính 3. Phần thực hành

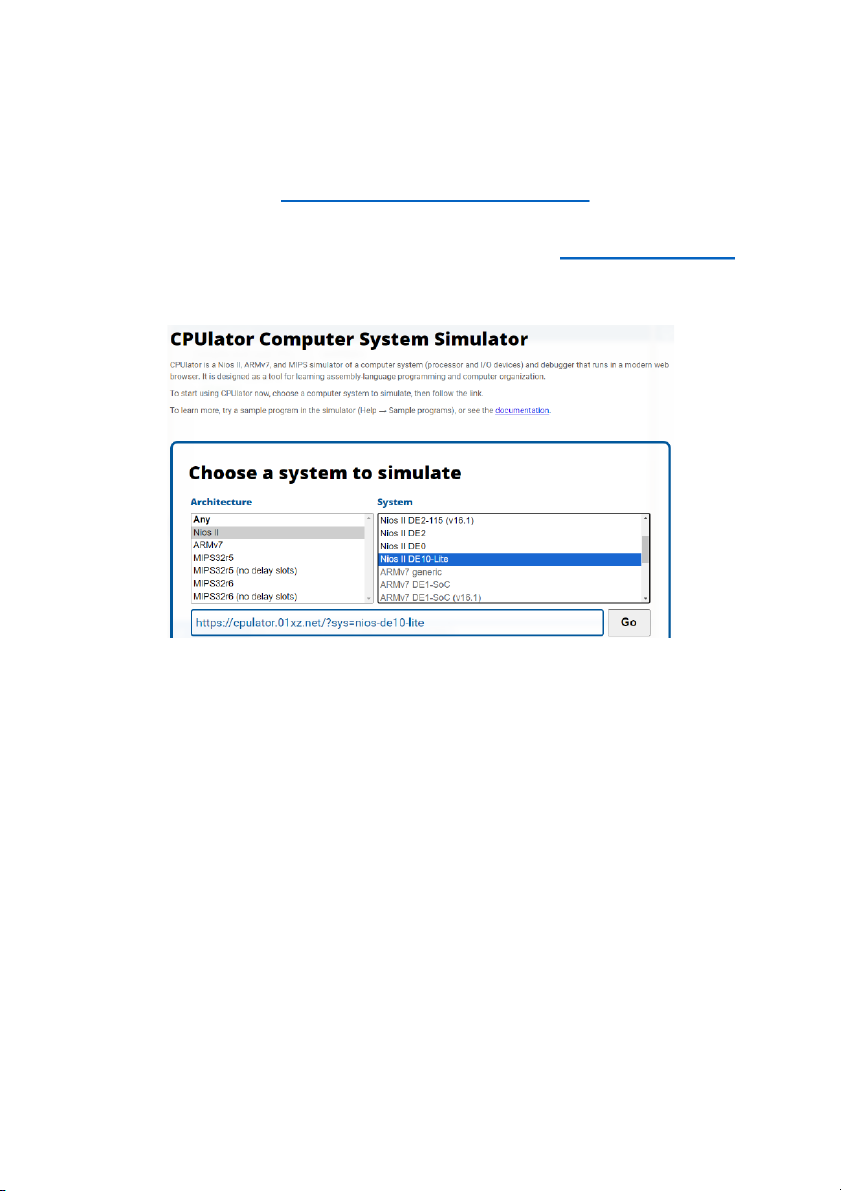

3.1. Truy cập web mô phỏng

Truy cập trang web https://cpulator.01xz.net/?sys=nios-de10-lite hoặc

Tìm kiếm trên google bằng từ khóa “cpulator intel” → Chọn https://cpulator.01xz.net/

→ Chọn Nios II trong cửa sổ Architecture → Chọn trong cửa sổ System Nios II DE10-Lite → Go (hình 2).

Hình 2. Hướng dẫn truy cập web mô phỏng cho NIOS II.

3.2. Giao diện web mô phỏng

Giao diện làm việc bao gồm:

1. Cửa sổ Register: các thanh ghi đa dụng của CPU NIOS II.

2. Cửa sổ làm việc bao gồm 3 tab chính:

a. Editor: Soạn thảo chương trình assembly.

b. Disassembly: Phân tích các lệnh assembly trong chương trình thành các lệnh

assembly thật sự trên NIOS II.

c. Memory: Bộ nhớ SDRAM, nơi lưu trữ dữ liệu và lệnh để cung cấp cho CPU thực thi.

3. Cửa sổ Message: Hiển thị thông báo. 5

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính 4. Thanh công cụ.

5. Cửa số giao tiếp với các thiết bị ngoại vi. 4 1 2 5 3

Hình 3. Giao diện web mô phỏng CPU NIOS II.

3.3. Cách sử dụng web mô phỏng

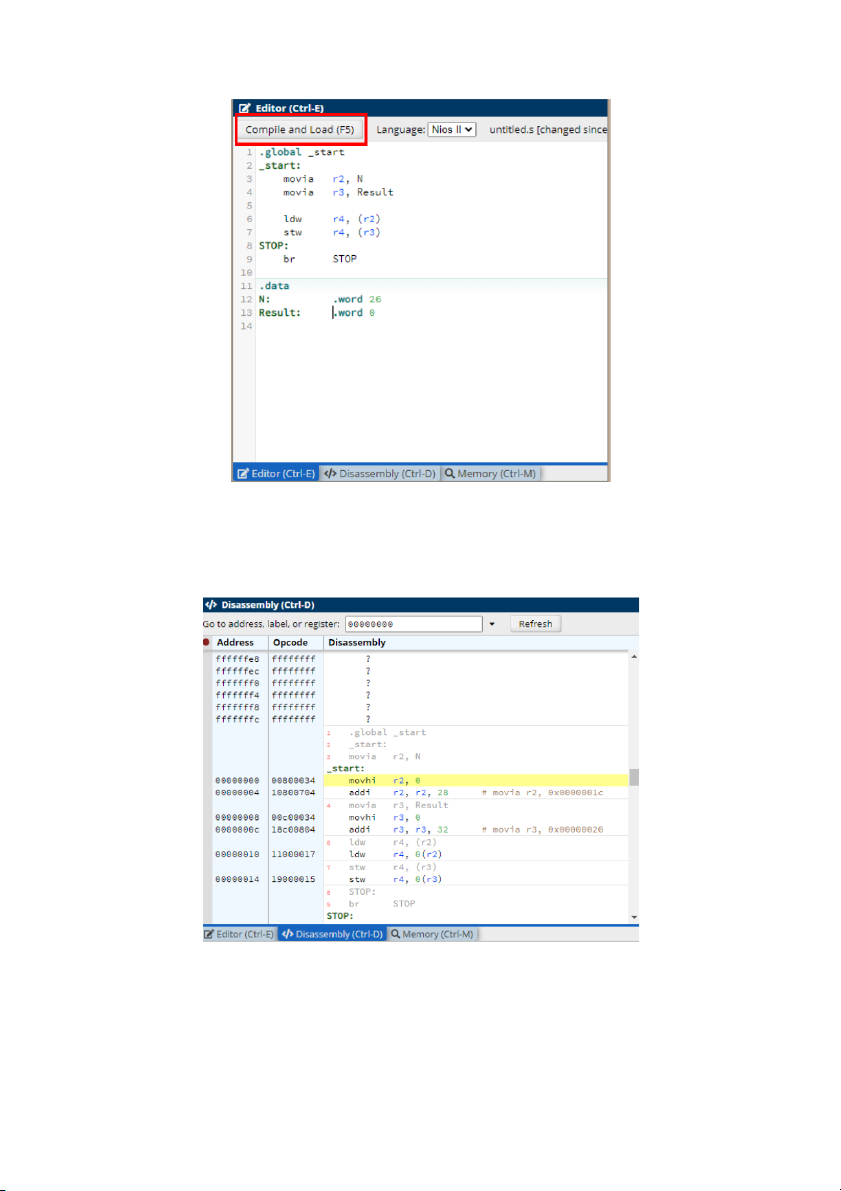

1 Có 2 cách soạn thảo chương trình assembly:

• Soạn thảo chương trình ở các Editor offline như Notepad++ trước khi sao chép và dán

vào tab Editor trên web mô phỏng. (Khuyến khích làm theo cách này vì Editor offline

dễ thao tác và quản lý code hơn)

• Soạn thảo trực tiếp trên Editor của web mô phỏng.

2 Sau khi soạn thảo hoàn tất chương trình. Chọn vào nút “Compile and Load (F5)” để biên

dịch chương trình (hình 4). 6

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

Hình 4. Biên dich chương trình.

3 Chương trình chuyển sang tab Disassembly như hình 5, dòng màu vàng là vị trí Program Counter (PC).

Hình 5. Chương trình ở trạng thái disassembly. 7

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

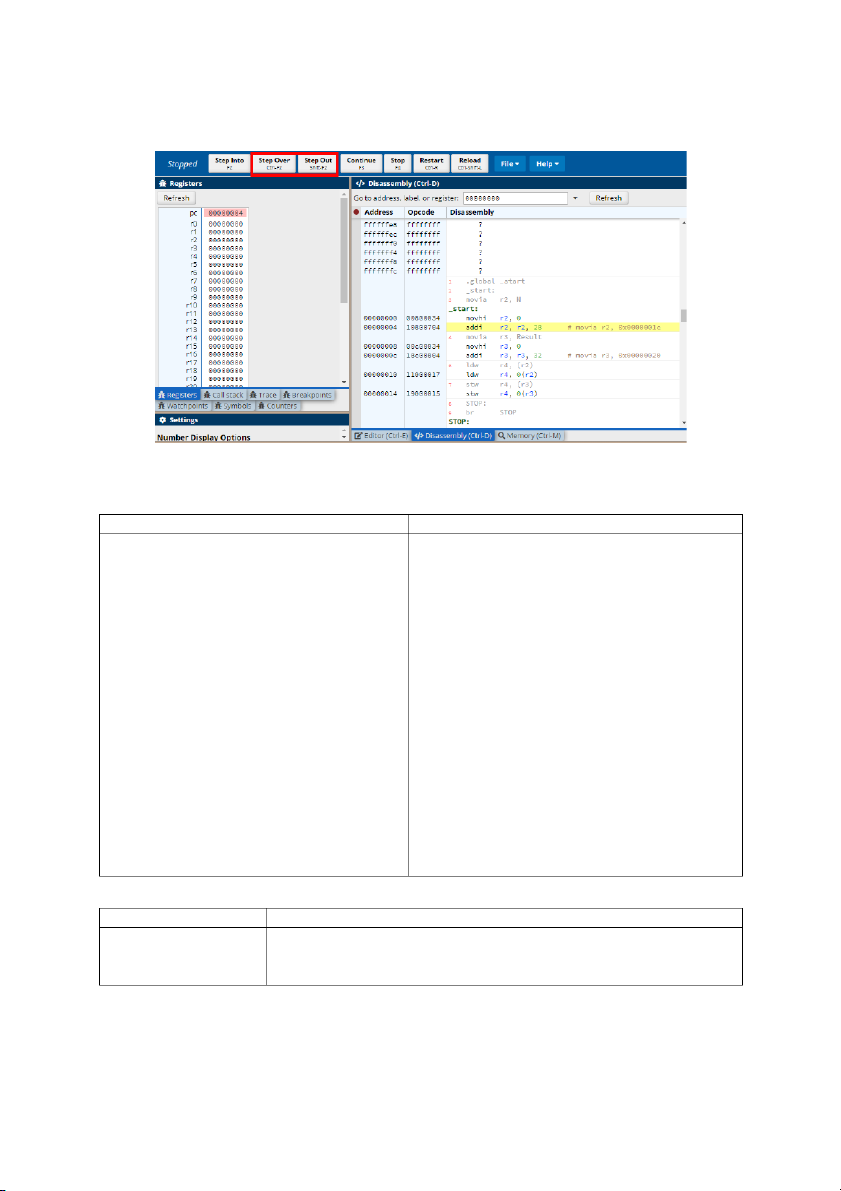

4 Nhấn “Step Out” để c ạy h

chương trình. Quan sát sự thay đổi của thanh ghi trong cửa sổ Register. Hoặc “ ” để Step Over

c ạy từng dòng của chương trình. h

Hình 6. Chạy chương trình bằng " Step Out" hoặc "Step Over".

3.4. Chương trình mẫu C code Nios II assembly void main { .text int a, b, c; .global _start a = 4; _start: b = 5; movia r2, a c = a + b; movia r3, b while(1); movia r4, c } ldw r5, (r2) ldw r6, (r3) add r7, r5, r6 stw r7, (r4) stop: br stop .data a: .word 4 b: .word 5 c: .word 0 .end

Lệnh / Chỉ t ị/ Nhãn h Chức năng

Bộ nhớ chương trình sẽ được phân thành 2 vùng nhớ Instruction và .text

Data riêng biệt. Assembly directives .text báo hiệu trình biên dịch lưu

chương trình vào vị trí vùng nhớ Instruction. 8

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

Bộ nhớ chương trình sẽ được phân thành 2 vùng nhớ Instruction và .data

Data riêng biệt. Assembly directives .data báo hiệu trình biên dịch lưu

dữ liệu vào vị trí vùng nhớ Data. a: b: Nhãn data c:

Assembly directives tạo 1 dữ liệu kiểu word (32 bit) có giá trị 4 tại .word 4 vùng nhớ Data .global _start

Assembly directives báo hiệu symbol _start có thể được truy cập từ file assembly khác start:

Nhãn bắt đầu chương trình .end

Assembly directives báo hiệu kết thúc chương trình STOP:

Lặp vô tận, tương đương với lệnh while(1) trong C br STOP

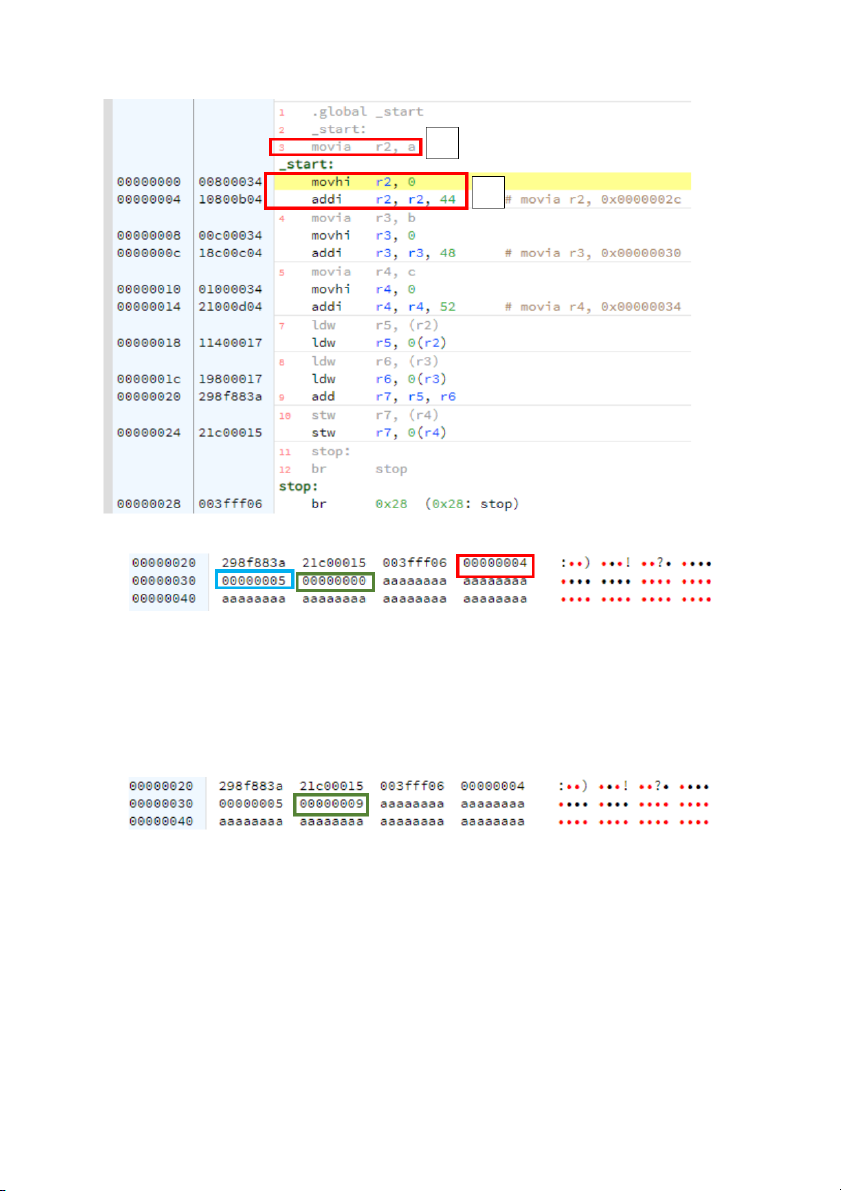

1. Tiến hành biên dịch chương trình bằng web mô phỏng, sau khi compile thành công, mở tab Disassembly. N ữ

h ng câu lệnh có đánh số màu đỏ là các câu lệnh ban đầu, dưới những câu

lệnh đó là câu lệnh được trình biên dịch tạo ra. Trong đó, có lệnh đặc biệt gọi là lệnh giả

(pseudo instruction). Ví dụ quan sát lệnh màu nâu ở dòng 3, “movia r2, a” (số 1 trên hình

7), lệnh này được phân tách thành 2 lệnh thật movhi và addi ( ố 2 trên hình 7). s

2. Mở sang tab Memory để quan sát bộ nhớ. Ô nhớ ở khung màu đỏ trên hình 8 được khởi

tạo giá trị 4 từ câu lệnh “a: .word 4”. Tương tự, ô nhớ ở khung màu xanh dương trên hình

8 có giá 5 từ câu lệnh “b: .word 5”. O nhớ ở khung màu xanh lá trên hình 8 có giá trị 0 từ

câu lệnh “c: .word 0”. 9

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính 1 2

Hình 7. Lệnh giả (Pseudo Instruction).

Hình 8. Khởi tạo bộ nhớ.

3. Chạy chương trình chọn “Step Out”.

4. Dừng chương trình “Stop”

5. Mở tab Memory, quan sát lại các ô nhớ ở khung màu xanh lá trên hình 9. Các giá trị đã thay đổi.

Hình 9. Kết quả của chương trình Fibonacci.

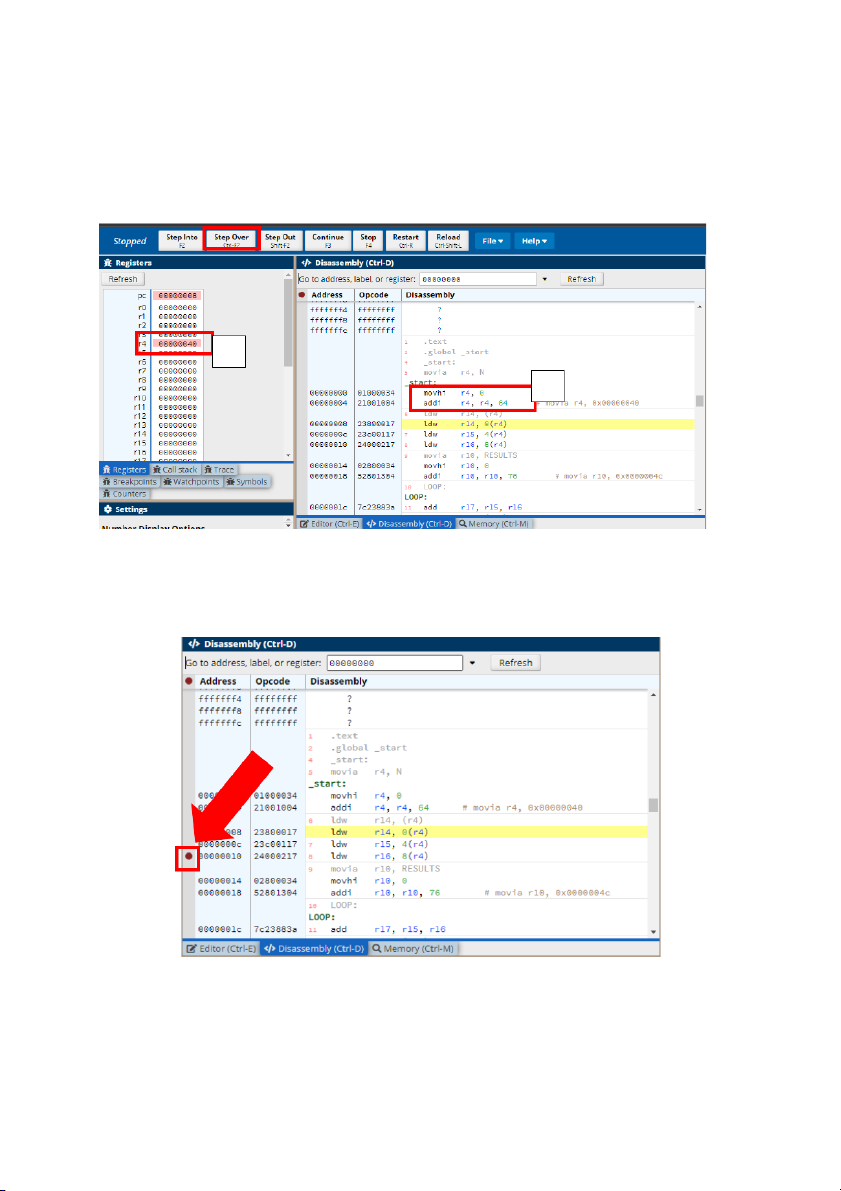

3.5. Cách debug chương trình

Sau khi biên dịch chương trình thành công, chuyển sang tab Disassembly, thực thi từng

lệnh và quan sát sự thay đổi giá trị của các thanh ghi trong cửa sổ Register và các giá trị liên quan

trong bộ nhớ tại tab Memory. Sử dụng “Step Over” để chương trình thực hiện từng dòng lệnh. 10

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

Như trong hình 10, sau khi thực hiện câu lệnh “movia r4, N”, câu lệnh này tương ứng với 2 lệnh

“movhi r4, 0” và “addi r4, r4, 64” (số 1 trên hình 10), thì thanh ghi r4 thay đổi thành 0x40 (số 2

trên hình 10). Lưu ý khi quan sát: Một lệnh được thực thi xong, khi dòng màu vàng (PC) đi qua câu lệnh đó. 2 1

Hình 10. Thực thi từng dòng lệnh.

Bên cạnh đó, sinh viên có thể sử dụng breakpoint trên cửa sổ Disassembly để debug chương

trình bằng cách chọn vào vị trí muốn đặt breakpoint như hình 11. Hình 1 . Sử dụng 1 breakpoint. 11

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

BÀI TẬP CHUẨN BỊ Ở NHÀ

Bài 1: Hãy cho biết chức năng các chỉ thị trình dịch assembly (assembler directives) sau

.global, .text, .data, .skip, .word, .fill, .end

Bài 2: Pseudo-instruction là gì? Dựa vào Phụ lục – Các lệnh assembly trong CPU NIOS II,

liệt kê một vài pseudo-instructions mà CPU NIOS II hỗ trợ. 12

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính BÁO CÁO THỰC HÀNH

Bài 1: Viết chương trình assembly kiểm tra số N là số c ẵn h

hay số lẻ. Nếu N là chẵn thì biến r = 1, ngược lại r = 0.

Bài 2: Viết chương trình assembly tính r = 1 + 2 + 3 + … + N. Với N cho trước.

Bài 3: Viết chương trình assembly tính r = 2 + 4 + 8 + … + 2*N. Với N cho trướ c.

Bài 4: Viết chương trình assembly kiểm tra số N có phải là số c ính phương ha h y không. Nếu N là số c ính phương h

thì biến r = 1, ngược lại r = 0. 13

Khoa Điện tử - Viễn thông

Bộ môn Máy tính - Hệ thống nhúng Tài liệu thực hành Cấu trúc máy tính

TÀI LIỆU THAM KHẢO

[1] DE10-Standard_Computer_NiosII (trong thư mục doc)

[2] Introduction to the Altera Nios II Soft Processor (trong thư mục doc)

[3] Phu luc - Cac lenh assembly cua CPU NIOS II (trong thư mục doc)

[4] CPUlator Simulator Documentation. [Online] Available:

https://cpulator.01xz.net/doc/#features 14