Preview text:

lOMoAR cPSD| 58137911

BÀI TẬP KIẾN TRÚC MÁY TÍNH BT 1: GIỚI THIỆU MÁY TÍNH

1) Hãy mô tả các thành phần cơ bản của kiến trúc máy tính theo mô hình John

von Neumann. Giải thích ngắn gọn về vận hành của máy tính.

*Các thành phần cơ bản của kiến trúc máy tính theo mô hình John von Neumann:

Bộ số học/logic (Arithmetic/Logic Unit): Là một mạch điện tử có nhiệm vụ thực hiện các phép

toán số học và logic. Bộ logic số học sẽ nhận các lệnh điều khiển từ bộ điều khiển; sau đó tiến

hành xử lý tín hiệu, thực hiện các phép tính số học.

• Thực hiện tính toán hoặc xử lý dữ liệu

Bộ điều khiển (Control Unit): Là các vi xử lý hoạt động với chức năng nhận và thông dịch các

thông tin nhập vào từ người dùng hay còn gọi là các lệnh của Chương trình điều khiển. Bộ điều

khiển hoạt động nhờ sự điều tiết các xung nhịp đo của đồng hồ hệ thống. (điều khiển các bộ

phận thực hiện chương trình).

• Kiểm soát việc di chuyển dữ liệu và lệnh vào/ra

• Điều khiển hoạt động của ALU • Chức năng:

o Điều khiển nhận lệnh từ bộ nhớ đưa vào thanh ghi lệnh o Tăng nội dung của

PC để trỏ sang lệnh kế tiếp

o Giải mã lệnh đã được nhận để xác định thao tác mà lệnh yêu cầu

o Phát ra các tín hiệu điều khiển thực thi lệnh

o Nhận các tín hiệu yêu cầu từ bus hệ thống và đáp ứng với các yêu cầu đó

Bộ nhớ (Memory Unit): Là một bộ phận điện tử dùng để lưu trữ các chỉ thị chờ bộ xử lý thực

thi, dữ liệu cần thiết cho cá chỉ thị và kết quả xử lý dữ liệu (thông tin). Là vùng lưu trữ chứa

đựng chương trình đang chạy và chứa dữ liệu mà chương trình chạy cần dùng

Thiết bị nhập (Input Device): là bất kỳ thiết bị phần cứng nào cho phép người dùng nhập dữ

liệu và chỉ thị vào máy tính (dùng để đưa thông tin vào máy tính). VD: bàn phím, chuột, máy scan, webcam, micro…

Thiết bị xuất (Output Device): là phần cứng truyền tải thông tin đến một hoặc nhiều người

dùng (dùng để đưa dữ liệu ra từ máy tính). VD: màn hình, máy in, máy chiếu, loa và tai nghe, modem…

*Giải thích ngắn gọn về vận hành của máy tính

Đưa dữ liệu vào máy tính bằng output, sau đó dữ liệu được ghi vào bộ nhớ và đưa đến bộ xử lý

trung tâm, dữ liệu được xử lý và được ghi vào bộ nhớ 1 lần nữa, sau đó ra thiết bị output. lOMoAR cPSD| 58137911

2) Hãy mô tả và giải thích ngắn gọn về các lớp phân cấp từ phần cứng đến phần mềm. Phân làm 3 cấp:

Ứng dụng (Application): Là các chương trình phần mềm được phát triển cho người thực

hiện các tác vụ cụ thể. Các ứng dụng thường được thiết kế theo yêu cầu của người dùng cuối

hoặc theo phản hồi từ người dùng. VD: Microsoft Word, Excel, Firefox, Google Chrome…

Phần mềm hệ thống (System software): Phần mềm nằm giữa tầng ứng dụng và phần

cứng , làm cầu nối (có nhiệm vụ giao tiếp trực tiếp phần cứng nhằm hỗ trợ cho các ứng dụng).

Bao gồm các chương trình điều khiển và duy trì các hoạt động của máy tính và các thiết bị của

nó. 2 loại phần mềm hệ thống điển hình nhất là hệ điều hành (operating system) và trình biên dịch (compiler)

Phần cứng (Hardware): đề cập đến các bộ phận vật lý hữu hình của một hệ thống máy

tính; các thành phần điện, điện tử, cơ điện và cơ khí của nó như là màn hình, chuột, bàn phím,

CPU, bo mạch chủ, các dây cáp, cũng như tủ hoặc hộp, các thiết bị ngoại vi của tất cả các loại,

và bất kỳ yếu tố vật lý nào khác có liên quan, tạo nên phần cứng hoặc hỗ trợ vật lý ví dụ như

loa, ổ đĩa mềm, ổ đĩa cứng, card đồ họa VGA, bộ phận tản nhiệt…

3) Cho một màn hình màu sử dụng 8 bit để hiển thị một màu cơ bản (đỏ - Red,

xanh lá cây – Green, xanh dương - Blue) trong mỗi pixel với độ phân giải 1280x800

pixel. Hãy cho biết dung lượng tối thiểu cần có của bộ đệm màn hình để có thể chứa một

khung ảnh (1 byte = 8 bit) Mỗi pixel sẽ cần 3x8 = 24 bit

Dung lượng tối thiểu cần có của bộ đệm màn hình để có thể chứa một khung ảnh là

1280x800x24 = 24576000 bits = 3072000 bytes

BT 2: ĐÁNH GIÁ HIỆU NĂNG

1) Cho 3 bộ xử lý P1, P2 và P3: cùng thực thi một tập lệnh với các tần số xung clock và CPI

được cho như bảng bên dưới: Bộ xử lý Clock Rate CPI P1 2 Ghz 1.5 P2 1.5 Ghz 1.0 lOMoAR cPSD| 58137911 P3 3 Ghz 2.5

a) Bộ xử lý nào có hiệu suất cao nhất dựa theo tiêu chí số lệnh thực thi trong 1 giây (IPS)

và số triệu lệnh thực thi trong một giây (MIPS).

Do ba bộ xử lý có cùng tập lệnh nên khi chạy cùng 1 chương trình, số lệnh cần chạy trên ba

máy là như nhau, tạm gọi là I

Tổng số chu kỳ xung clock chương trình cần = Tổng số lệnh c.tr` x CPI

Tổng số chu kỳ xung clock chương trình cần của P1 = I x 1.5 (chu kỳ)

Tổng số chu kỳ xung clock chương trình cần của P2 = I x 1.0

(chu kỳ) Tổng số chu kỳ xung clock chương trình cần của P3 = I x 2.5 (chu kỳ)

Thời gian thực thi c.tr = Tổng số chu kỳ xung clock c.tr cần / Tần số xung clock

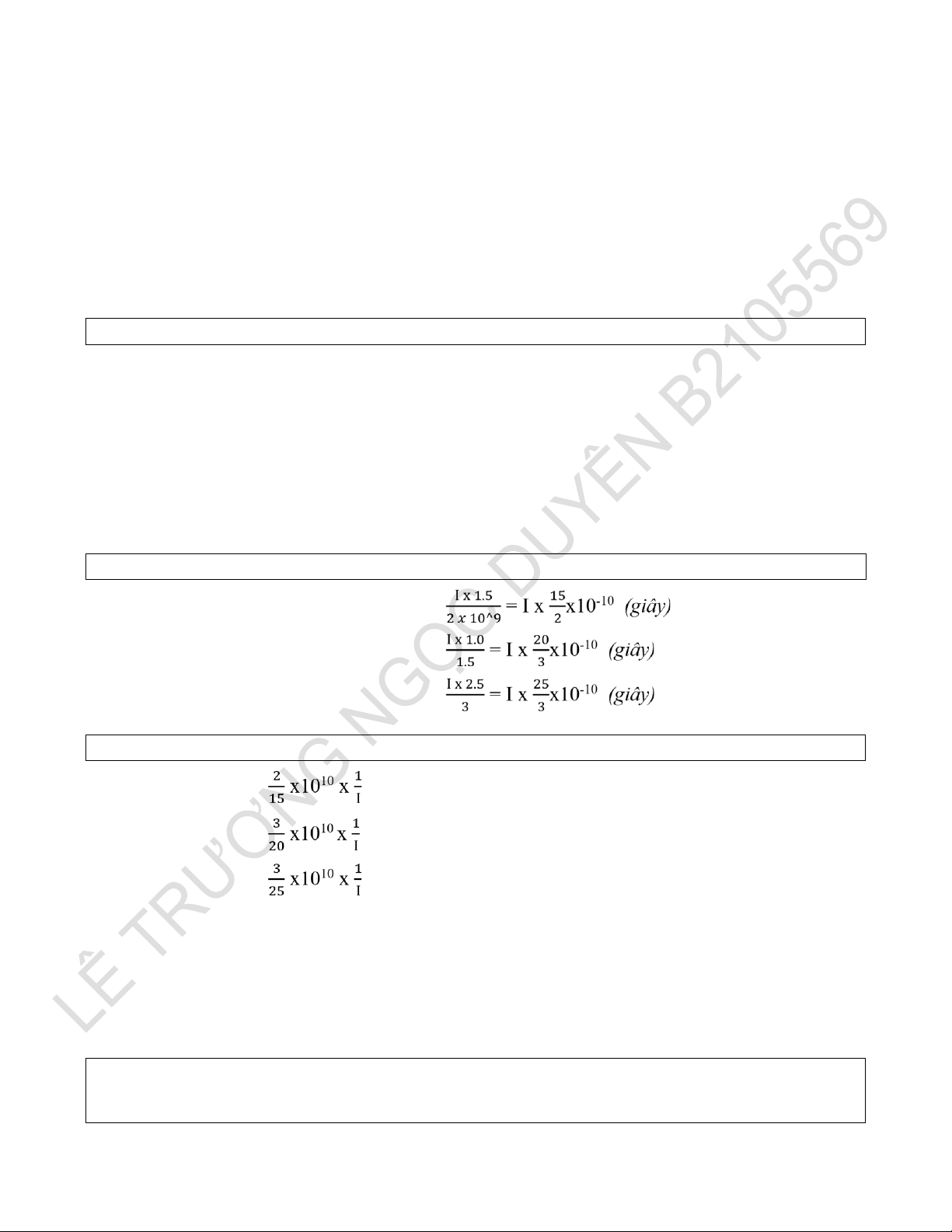

Thời gian thực thi chương trình P1 =

Thời gian thực thi chương trình P2 =

Thời gian thực thi chương trình P3 =

Hiệu suất = 1 / Thời gian thực thi chương trình Hiệu suất P1 = Hiệu suất P2 = Hiệu suất P3 =

P2 có hiệu suất cao nhất b)

Nếu các bộ xử lý thực thi 1 chương trình nào đó hết 10 giây, tính tổng số chu

kì và tổng số lượng lệnh tương ứng.

Tổng số chu kỳ = Thời gian thực thi chương trình x Tần số xung clock

Tổng số lệnh = Tổng số chu kỳ / CPI lOMoAR cPSD| 58137911

P1: Tổng số chu kỳ (P1) = 10 x 2x109 = 2x1010 (chu kỳ)

Tổng số lệnh = 2x1010 / 1.5 = 13.3 x 10^9 (lệnh)

P3: Tổng số chu kỳ (P2) = 10 x 1.5x109 = 1.5x1010 (chu kỳ)

Tổng số lệnh = 1.5x1010 / 1 = 15 x 10^9 (lệnh)

P2: Tổng số chu kỳ (P3) = 10 x 3x109 = 3x1010 (chu kỳ)

Tổng số lệnh = 3x1010 / 2.5 = 12 x 10^9 (lệnh) c)

Nếu chúng ta mong muốn giảm 30% thời gian thực thi sẽ dẫn tới việc tăng 20% CPI thì

tần số xung clock mới của từng bộ xử lý tương ứng phải là bao nhiêu?

CPI = (Thời gian thực thi x Tần số xung clock) / Tổng số lệnh chương trình

Gọi X là Tần số xung clock mới 120% = 70% x X X = 171.429%

Nếu mong muốn giảm 30% thời gian thực thi sẽ dẫn tới tăng 20% CPI thì tần số xung clock mới sẽ tăng 71,429%

Tần số xung clock (P1) = 1,71429 x 2 = 3,43 GHz

Tần số xung clock (P2) = 1,71429 x 1.5 = 2.57 GHz

Tần số xung clock (P3) = 1,71429 x 3 = 5,14 GHz

2) Xét 2 cách thiết kế khác nhau của cùng kiến trúc bộ lệnh cho hai bộ xử lý P1 và P2. Có 4

lớp lệnh: A, B, C và D. Tần số xung và CPI của mỗi cách thiết kế được cho như bảng bên dưới:

Bộ xử lý Clock rate CPI Class A CPI Class B CPI Class C CPI Class D P1 1.5 Ghz 1 2 3 4 P2 2 Ghz 2 2 2 3

a) Cho một chương trình với 10^6 lệnh được chia thành các lớp sau: 10% lớp

A, 20% lớp B, 50% lớp C và 20% lớp D. Cách thiết kế cho bộ xử lý nào thực thi lOMoAR cPSD| 58137911

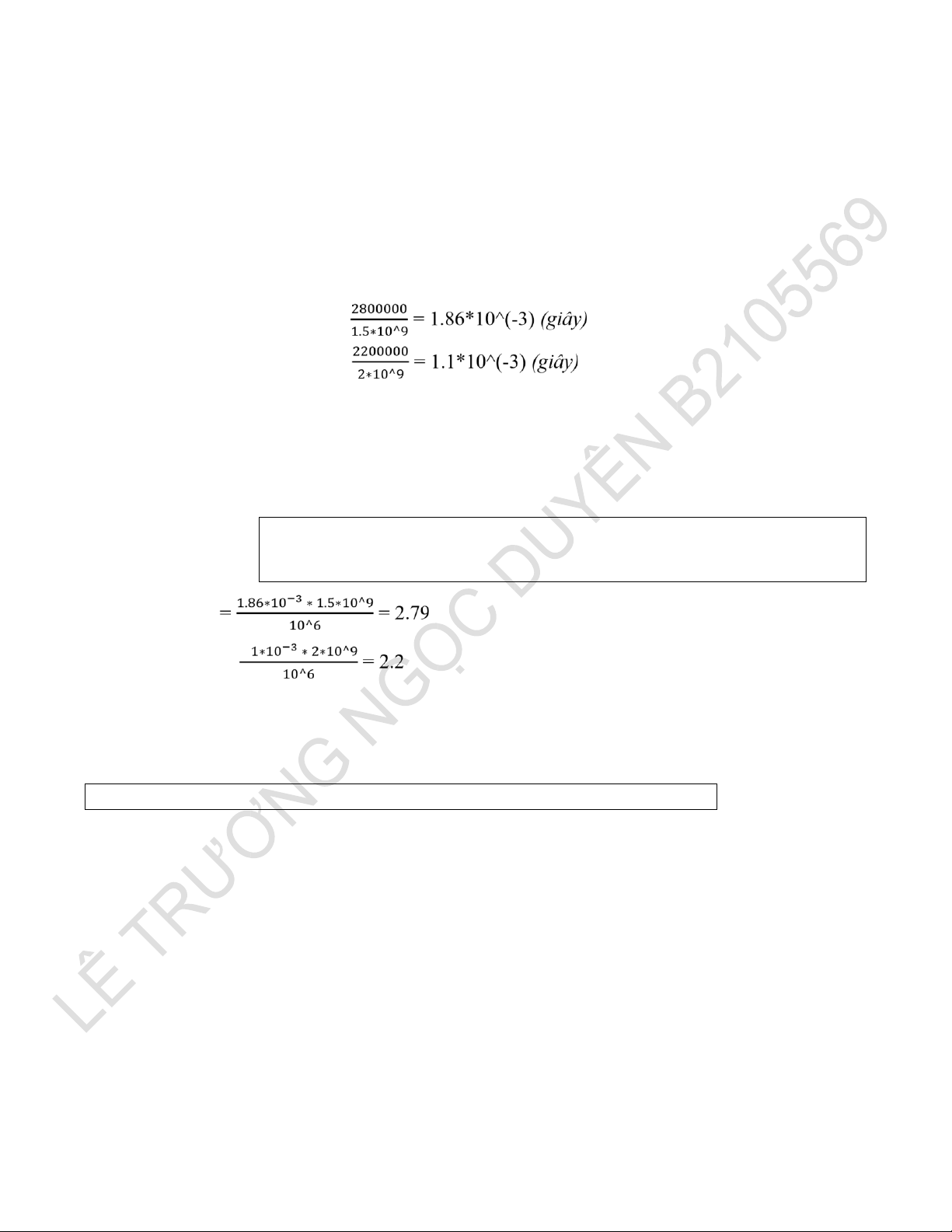

chương trình này nhanh hơn. Tổng số chu kỳ thực thi (P1) = 10^6 * (1*10% + 2*20% + 3*50% + 4*20%) = 2800000 (chu kỳ)

Tổng số chu kỳ thực thi (P2) = 10^6 * (2*10% + 2*20% + 2*50% + 3*20%) = 2200000 (chu kỳ) Thời gian thực thi (P1) = Thời gian thực thi (P2) =

Vì thời gian thực thi của P1 > P2 nên P2 nhanh hơn

b) Tính CPI trung bình của mỗi bộ xử lý với chương trình trên

CPI = Tổng số CK xung clock c.tr cần / Tổng số lệnh c.tr

= (Thời gian thực thi * Tần số xung clock) / Tổng số lệnh CPI (P1) CPI (P2) = 1 .

c) Tính tổng số chu kì xung clock của chương trình trên P1 và P2

Tổng số CK xung clock chương trình cần = Tổng số lệnh c.tr * CPI

Tổng số CK xung clock (P1) = 10^6 * 2.8 = 28*10^5 (chu kỳ)

Tổng số CK xung clock (P2) = 10^6 * 2.2 = 22*10^5 (chu kỳ)

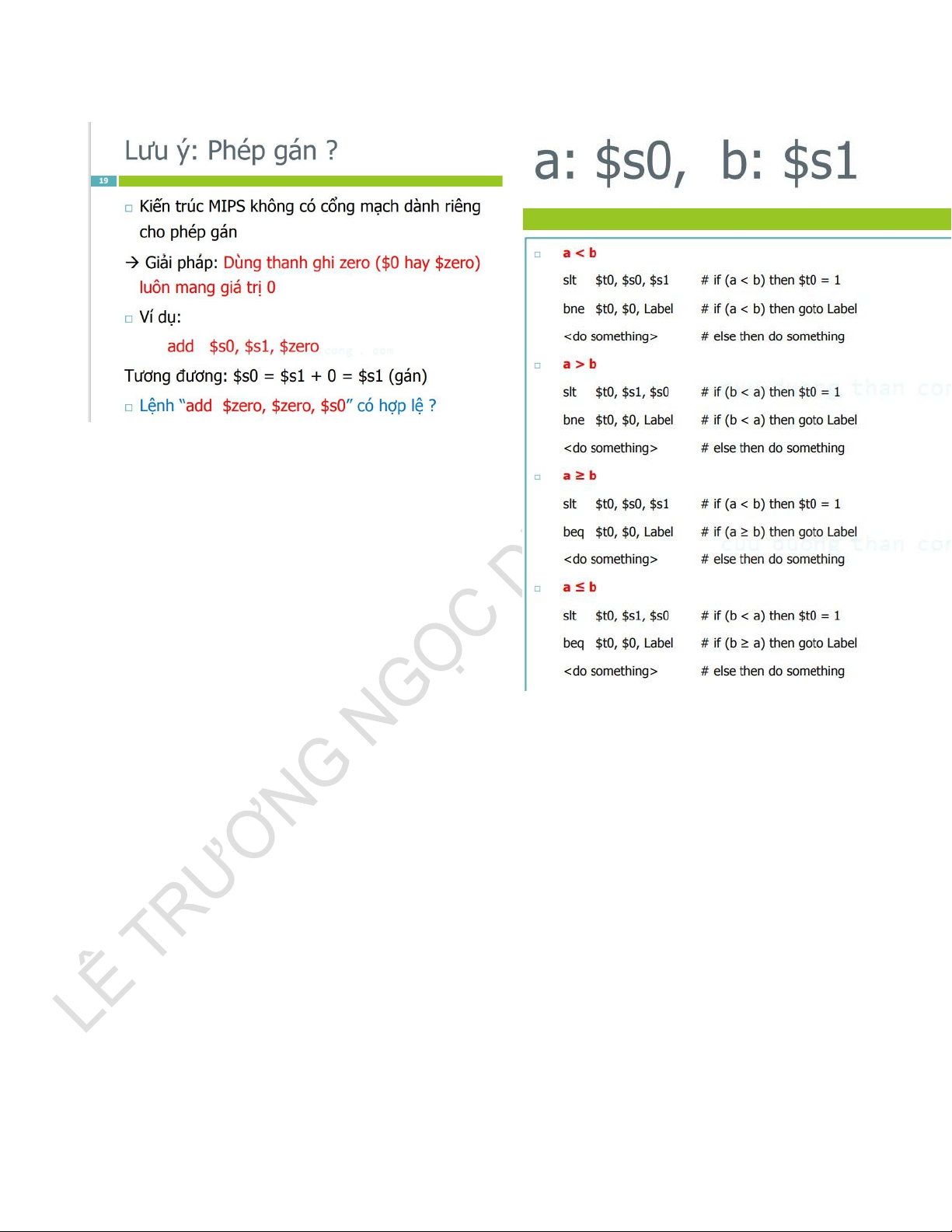

BT 3 : KIẾN TRÚC BỘ LỆNH

1) Hãy tìm mã hợp ngữ MIPS tương đương với chuơng trình C

như sau: a) x = 5 y = x - 2 a = x * 4 b = y * 2 z = (x + a) - (y + b)

Biết rằng các biến x, y, a, b là các số nguyên 32 bit x = 5 • addi x, $zero, 5 lOMoAR cPSD| 58137911

//x = 0 + 5 = 5 y = x

Lỗi! Thẻ đánh dấu không được xác định. addi y, x, -2 a = x * Lỗi! Thẻ đánh dấu không được xác định. add t0, x, 6 • add t1, x, x •

add a, t0, t1 b = y * 2 •

add b, y, y z = (x + a) - (y + b) add t0, x, a • add t1, y, b • sub z, t0, t1 b) x = y + a[5]

Giả sử mỗi phần tử của mảng a là một word/từ nhớ 4 bytes. • lw t0, 20(s0) • add x, y, t0 lOMoAR cPSD| 58137911

2) Hãy phân biệt sự khác nhau giữa Big End (Big Endian) và Little End (Little

Endian) Sự khác biệt của Little End và Big End khi lưu trữ chính là ở việc sắp xếp thứ tự các byte dữ liệu.

• Little Endian (xuất phát từ “little-end” nghĩa là kết thúc nhỏ hơn), byte cuối cùng trong

biểu diễn nhị phân trên sẽ được ghi trước. Byte thấp nhất sẽ được sắp đầu tiên tức là

(nếu ngang hàng thì) xếp phía bên trái ngoài cùng. Byte có ý nghĩa thấp được lưu trữ ở

ngăn nhớ có địa chỉ nhỏ, byte có ý nghĩa cao được lưu trữ ở ngăn nhớ có địa chỉ lớn

Nền tảng sử dụng: Intel

• Big Endian (xuất phát từ “big-end” nghĩa là kết thúc lớn hơn) thì ngược lại, là cơ chế

ghi dữ liệu theo thứ tự bình thường mà chúng ta vẫn dùng. Byte cao nhất sẽ được sắp

đầu tiên tức là (nếu ngang hàng thì) xếp phía bên trái ngoài cùng. Byte có ý nghĩa cao

được lưu trữ ở ngăn nhớ có địa chỉ nhỏ, byte có ý nghĩa thấp được lưu trữ ở ngăn nhớ

có địa chỉ lớn. Nền tảng sử dụng: IBM zSeries, Motorola 680x0…

*MIPS sử dụng Big End hay Little End? MIPS sử dụng Big End

3) Cho 2 số x, y viết theo như sau: x y 4 -6 12 -9 19 -12 60 88

Hãy biểu diễn x, y theo nhị phân 8 bit có dấu bù 2 và thực hiện tính (x + y) theo hệ nhị phân • 4 = 00000100 • -6 = 11111010 4 + (-6) = 11111110 = -2 • 12 = 00001100 • -9 = 11110111

12 + (-9) = 00000011 = 3 lOMoAR cPSD| 58137911 • 19 = 00010011 • -12 = 11110100

19 + (-12) = 00000111 = 7 60 = 00111100 88 = 01011000

60 + 88 = 10010100 = 148

4) Liệt kê các định dạng lệnh

MIPS Các định dạng lệnh MIPS:

• R-type hoặc R-format (cho các lệnh chỉ làm việc với thanh ghi)

• I-type hoặc I-format (cho các lệnh có liên quan đến số tức thời và truyền dữ liệu) J-

type hoặc J-format (lệnh nhảy, lệnh ra quyết định)

Hãy biểu diễn nhị phân lệnh: add $t0,$s1,$s2 000000 10001 10010 01000 00000 100000

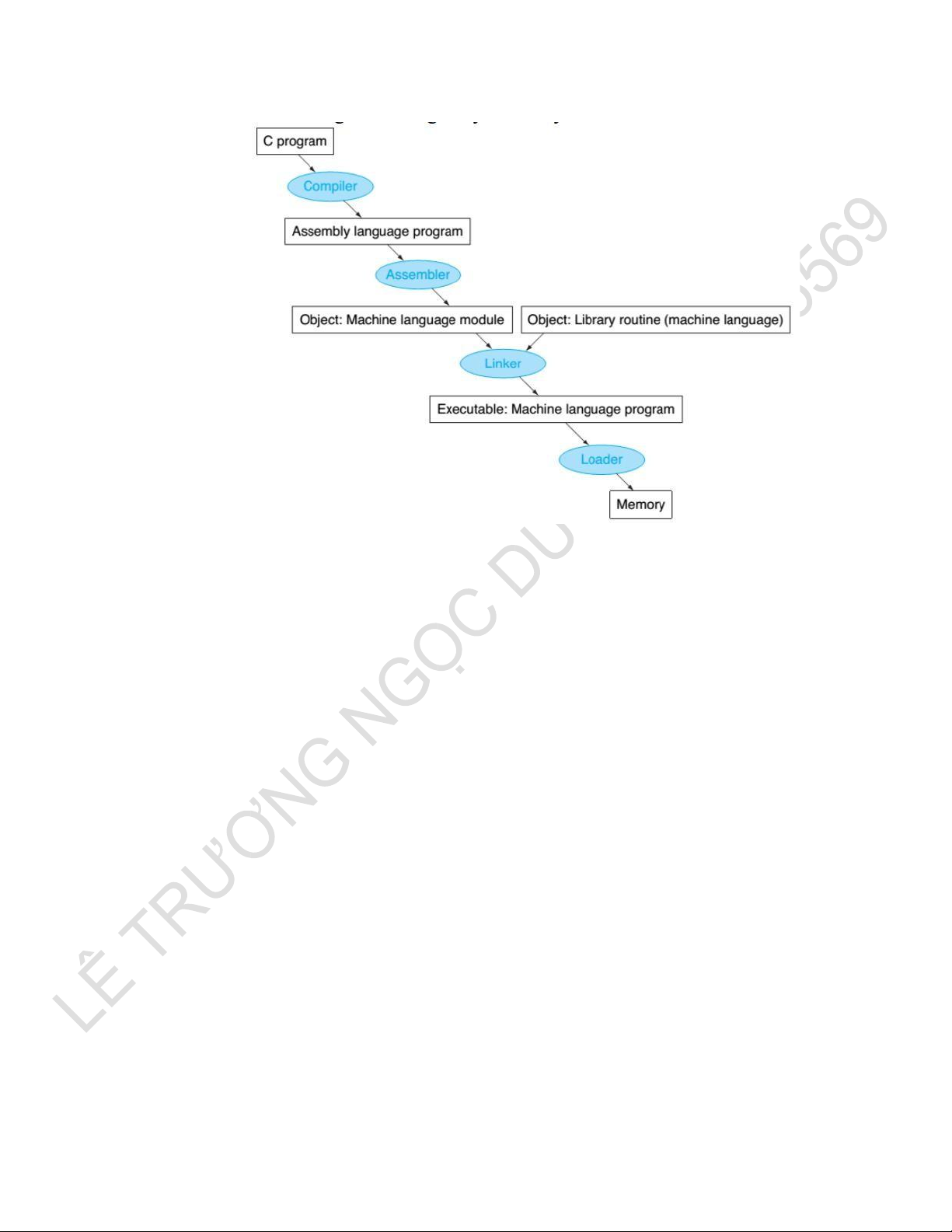

5) Mô tả các bước chuyển 1 chương trình C thành mã máy thực thi trên máy tính

(https://hanghieugiatot.com/lam-the-nao-mot-chuong-trinh-o-ngon-ngu-cap-cao-duoc-dich-

sang-ngonngu-may-bang-trinh-thong-dich) lOMoAR cPSD| 58137911

Được chia ra làm 4 giai đoạn chính:

Giai đoạn tiền xử lý – Preprocessor • Nhận mã nguồn (.c)

• Xóa bỏ tất cả chú thích, comments của chương trình

• Chỉ thị tiền xử lý (bắt đầu bằng #) cũng được xử lý Giai đoạn dịch ngôn ngữ C sang

Assembly – Compiler

• Phân tích cú pháp của mã nguồn C

• Chuyển chúng sang dạng mã Assembly là một ngôn ngữ bậc thấp (hợp ngữ) gần với tập lệnh của bộ vi xử lý

Giai đoạn dịch Assembly sang ngôn ngữ máy – Assembler

• Dịch chương trình => Sang mã máy 0 và 1

• Một tệp mã máy (.obj) sinh ra trong hệ thống sau đó Giai đoạn liên kết – Linker

• Trong giai đoạn này mã máy của một chương trình dịch từ nhiều nguồn được liên kết lại

với nhau để tạo thành chương trình đích duy nhất

• Mã máy của các hàm thư viện gọi trong chương trình cũng đc đưa vào chương trình cuối trong giai đoạn này

• Chính vì vậy mà các lỗi liên quan đến việc gọi hàm hay sử dụng biến tổng thể mà không

tồn tại sẽ bị phát hiện. Kể cả lỗi viết chương trình không có hàm main() cũng được phát hiện trong liên kết lOMoAR cPSD| 58137911

Một bộ biên dịch (Compiler) chuyển đổi ngôn ngữ C (độc lập với kiến trúc phần mềm) sang

dạng hợp ngữ (phụ thuộc kiến trúc phần mềm). Một chương trình dịch hợp ngữ (Assembler)

chuyển đổi một chương trình viết bằng hợp ngữ (Assembly Language) sang ngôn ngữ máy để

máy tính có thể thực hiện được chương trình đó

6) Cho đoạn mã sau: i f ( x < 0 ) h = 0 ; e l s e h = x;

với x, h được lưu trong $s0, $s1

Hãy dịch sang assembly MIPS đoạn mã trên slt $t0, $s0, $zero #if (x<0) then $t0=1 bne $t0, $zero, Eq #if(x<0) then goto Eq add $s1, $s0, $zero

#h = x+0 = x (skipped if x<0) j Exit #go to Exit

Eq: add $s1, $zero, $zero

#h = 0+0 = 0 (skipped if x>=0) Exit: … lOMoAR cPSD| 58137911

7) Các bước thực thi thủ tục

Để thực thi một thủ tục, chương trình phải tuân theo 6 bước sau:

1. Đặt các tham số ở một nơi mà thủ tục có thể truy xuất được

2. Chuyển quyền điều khiển cho thủ tục

3. Yêu cầu tài nguyên lưu trữ cần thiết cho thủ tục đó

4. Thực hiện công việc (task)

5. Lưu kết quả ở một nơi mà chương trình có thể truy xuất được

6. Trả điều khiển về vị trí mà thủ tục được gọi. Vì một thủ tục có thể được gọi từ nhiều vị

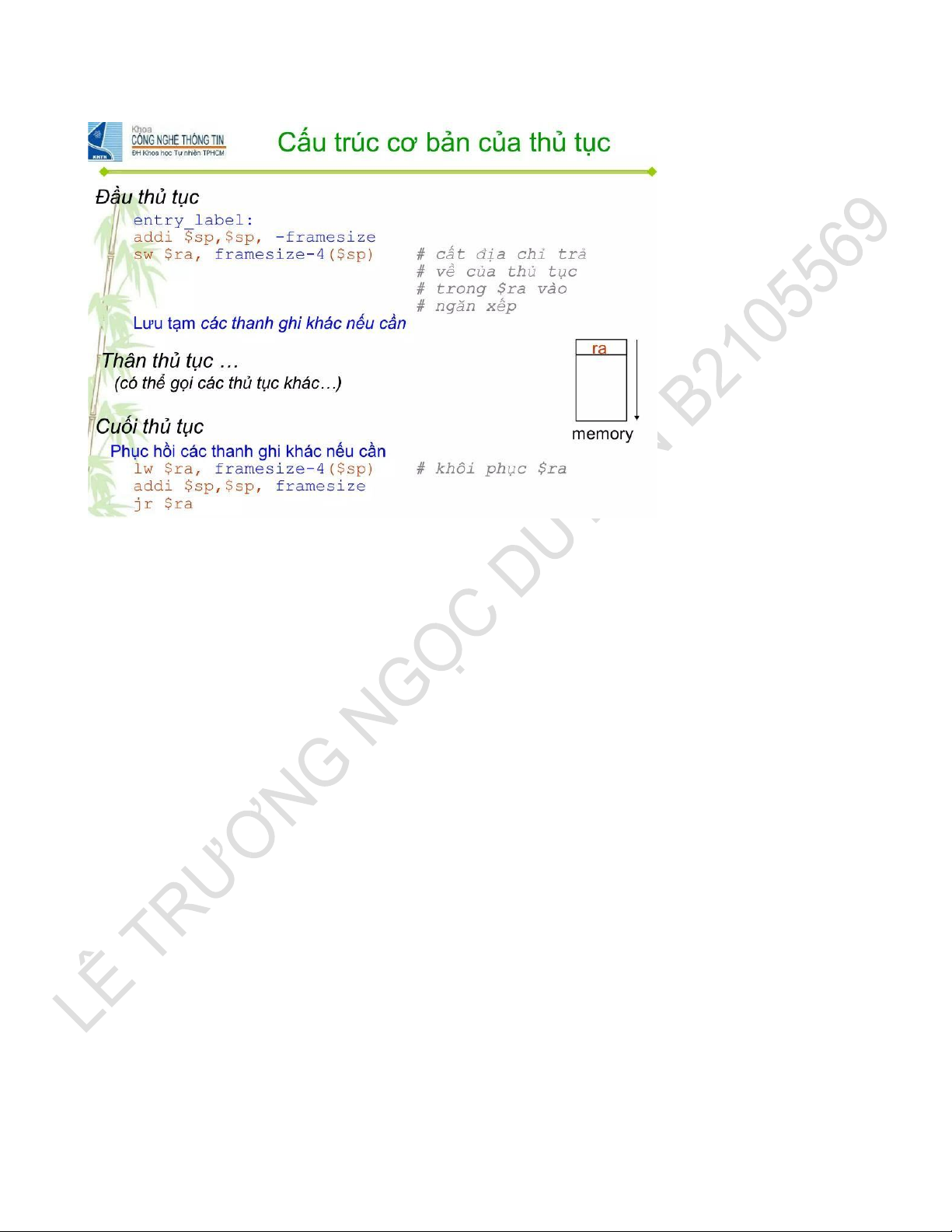

trí trong một chương trình lOMoAR cPSD| 58137911 8) Cấu trúc

thủ tục Phần đầu: •

Khai báo kích thước cho stack •

Lưu các thanh ghi cần thiết Phần thân: •

Thực hiện chức năng yêu cầu (có thể gọi các thủ tục khác…) Phần cuối: •

Phục hồi các thanh ghi cần thiết • Xóa stack

➔Để gọi thủ tục, dùng lệnh jal (Lệnh nhảy và liên kết:

jump-and-link) o Input: $a0, $a1, $a2, $a3 o Output: $v0, $v1

o Địa chỉ quay về được lưu trong $ra lOMoAR cPSD| 58137911

BT 4: TÍNH TOÁN SỐ HỌC

1) Dùng 4 bit nhị phân để biểu diễn số nguyên hệ thập phân. Thực hiện các phép tính: a) 7 + 8 7: 0 1 1 1 8: + 1 0 0 0 7+8 = 1 1 1 1 = 15 lOMoAR cPSD| 58137911 b) 7 – 8 8: 1 0 0 0 0 1 1 1 + 1 -8: 1 0 0 0 7: 0 1 1 1 -8: + 1 0 0 0 7 + (-8) = 1 1 1 1 = -1 c) 7 x 8

*GIẢI THUẬT 1 Step Multiplicand Multiplier Product 0 0000 0111 1000 0000 0000 1 100[0]

Dịch multiplicand sang trái 1 bit

Dịch multiplier sang phải 1 bit 0000 1110 0100 0000 0000 2 010[0]

Dịch multiplicand sang trái 1 bit

Dịch multiplier sang phải 1 bit 0001 1100 0010 0000 0000 3 001[0]

Dịch multiplicand sang trái 1 bit

Dịch multiplier sang phải 1 bit 0011 1000 0001 0000 0000 4 000[1]

• Product = product + multiplicand lOMoAR cPSD| 58137911

• Dịch multiplicand sang trái 1 bit

• Dịch multiplier sang phải 1 bit 0111 0000 0000 0011 1000 Stop

Product = 0011 1000 = 25 + 24 + 23 = 32 + 16 + 8 = 56

*GIẢI THUẬT 2 Step Multiplicand Product/Multiplier 0 0111 0000 1000 1 100[0]

Dịch product/multiplier sang phải 1 bit 0111 0000 0100 2 010[0]

Dịch product/multiplier sang phải 1 bit 0111 0000 0010 3 001[0]

Dịch product/multiplier sang phải 1 bit 0111 0000 0001 4 000[1]

Product = product + multiplicand 0000 + 0111

0111 Dịch product/multiplier sang phải 1 bit 0111 0011 1000 Stop

Product = 0011 1000 = 25 + 24 + 23 = 32 + 16 + 8 = 56 d) 13 : 4 lOMoAR cPSD| 58137911 Dividend = 13 ; Divisor = 4 Step (Q)uotient (D)ivisior (R)emainder 0 0000 0100 0000 0000 1101 1

• R = R – D = 0000 1101 – 0100 0000 • R<0 o R = R + D = 0000 1101 o Dịch Q sang trái 1 bit Dịch D sang phải 1 bit 0000 0010 0000 0000 1101 2

R = R – D = 0000 1101 – 0010 0000 R<0 o R = R + D = 0000 1101 o Dịch Q sang trái 1 bit Dịch D sang phải 1 bit 0000 0001 0000 0000 1101 3

R = R – D = 0000 1101 – 0001 0000 R<0 o R = R + D = 0000 1101 o Dịch Q sang trái 1 bit Dịch D sang phải 1 bit 0000 0000 1000 0000 1101 4 R = R – D 0000 1101 – 0000 1000 = 0000 0101 lOMoAR cPSD| 58137911

R>0 o Dịch Q sang trái 1 bit o Q[0] = 1 Dịch D sang phải 1 bit 0001 0000 0100 0000 0101 5

• R = R – D = 0000 0101 – 0000 0100 = 0000 0001 • R>0 o Dịch Q sang trái 1 bit o Q[0] = 1 Dịch D sang phải 1 bit 0011 0000 0010 0000 0001 Stop Quotient = 0011 Remainder = 0001

2) Thực hiện các phép tính trên số thực chấm động: a) 2.1 25 + 1.2 5 B1: 2.125 = = 1.0001 x 21

1.25 = = 101 x 2-2 = 1.01 x 20 lOMoAR cPSD| 58137911 B2:

2.125 + 1.25 = 1.0001 x 21 + 1.01 x 20 = 1.0001 x 21 + 0.101 x 21 B3: (1.0001 + 0.101) x 21 =

1.1011 x 21 B4: 1.1011 x 21 = 11011 x 2 b) 1.2 5 x 2.5 B1:

1.25 = = 101 x 2-2 = 1.01 x 20 2.5 = = 101 x 2-1 = 1.01 x 21 B2:

1.25 x 2.5 = 1.01 x 20 x 1.01 x 21 =

1.1001 x 21 B3:

Kết quả = 1.1001 x 21 = 11001 x 2 c) 2.5 : 0.2 5 = 2.5 x B1: 2.5 = = 101 x 2-1 = 1.01 x 21 lOMoAR cPSD| 58137911 = 100 x 20 B2:

2.5 : 0.25 = 1.01 x 21 x 100 x 20 = 101 x 21 B3:

Kết quả = 101 x 21 = 5 x 2 = 10 i = 2 ; i f ( i ! = j ) { f = g + h lOMoAR cPSD| 58137911 ; } addi $s3, $zero, 2 beq $s3, $s4, exit add $s0, $s1, $s2 j exit exit: - ---------------- ---------------- ---------------- ---------------- --------------- i=i+1; if(i>j){ f=g+h; } e l s e { f = g - h