Preview text:

lOMoAR cPSD| 58778885

Họ và tên: Lê Xuân Trung. MSSV: 23119219. Lớp: Thứ 7, Tiết 10-12.

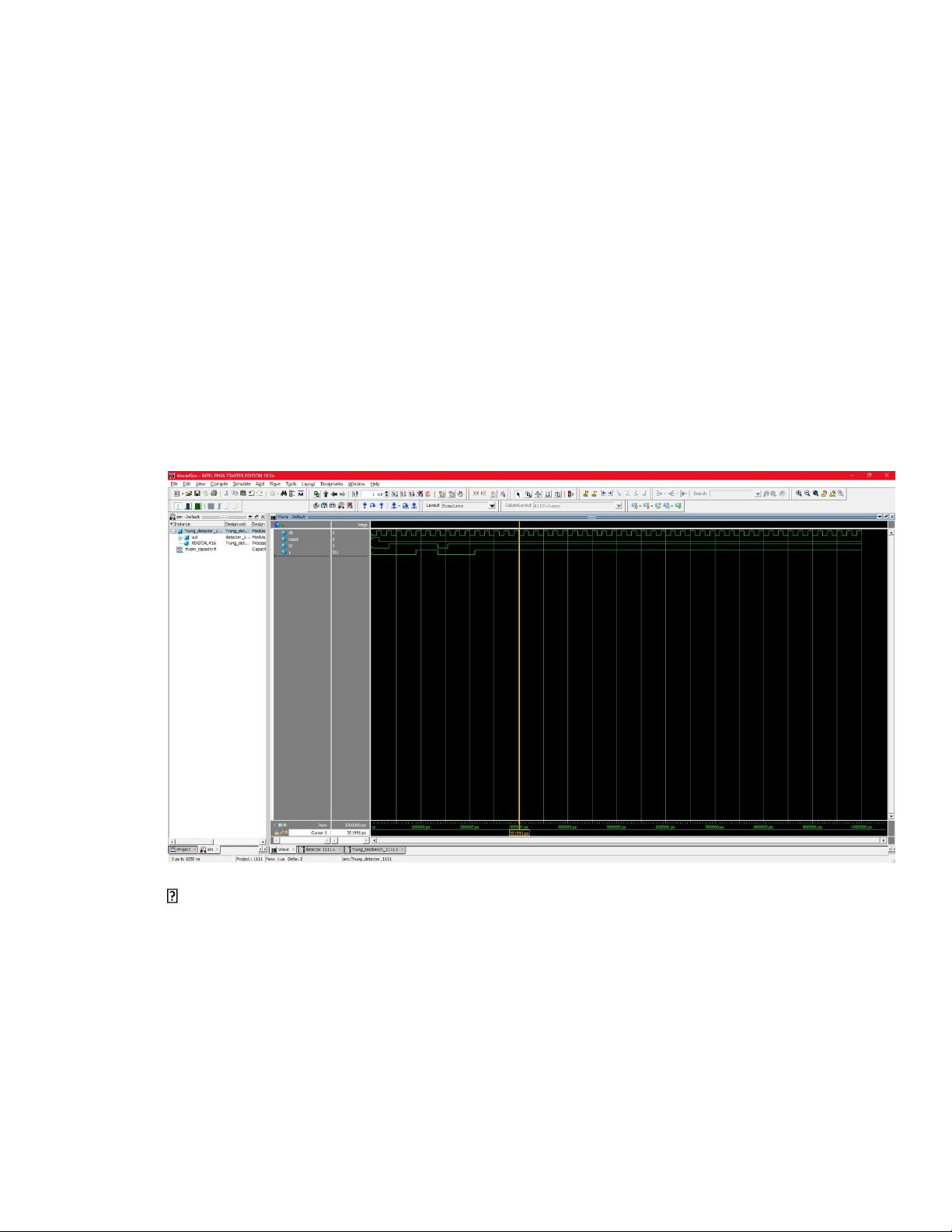

1) Thiết kế và mô phopnrg mach phát hiện chuỗi 1111 là dữ liệu nói tiếp. W là

dữ liệu theo từng xung clk cạnh lên , nếu phát hiện chuỗi 1111 nối tiếp thì y

ở mức 1. - Sơ đồ trạng thái - Code Verilog `timescale 1ns / 1ps module detector_1111 ( input clk, input reset, input W, output reg y ); parameter S0 = 2'b00, lOMoAR cPSD| 58778885 S1 = 2'b01, S2 = 2'b10, S3 = 2'b11;

reg [1:0] state, next_state; always

@(posedge clk or posedge reset) begin if (reset) state <= S0; else state <= next_state; end always @(*) begin case (state)

S0: next_state = (W) ? S1 : S0;

S1: next_state = (W) ? S2 : S0;

S2: next_state = (W) ? S3 : S0;

S3: next_state = (W) ? S3 : S0;

default: next_state = S0; endcase end

always @(*) begin if (state == S3 && W == 1) y = 1; else y = 0; end endmodule - Testbench lOMoAR cPSD| 58778885 `timescale 1ns / 1ps module Trung_detector_1111(); reg clk; reg reset; reg W; wire y; detector_1111 uut ( .clk(clk), .reset(reset), .W(W), .y(y) ); initial begin clk = 0; forever #10 clk = ~clk; end initial begin reset = 1; W = 0; #15; reset = 0; #20 W = 1; #20 W = 1; #20 W = 1; lOMoAR cPSD| 58778885 #20 W = 1; #20 W = 1; #20 W = 0; #20 W = 1; #20 W = 1; #20 W = 1; #20 W = 1; end endmodule kết quả:

Mạch đúng như yêu cầu lOMoAR cPSD| 58778885

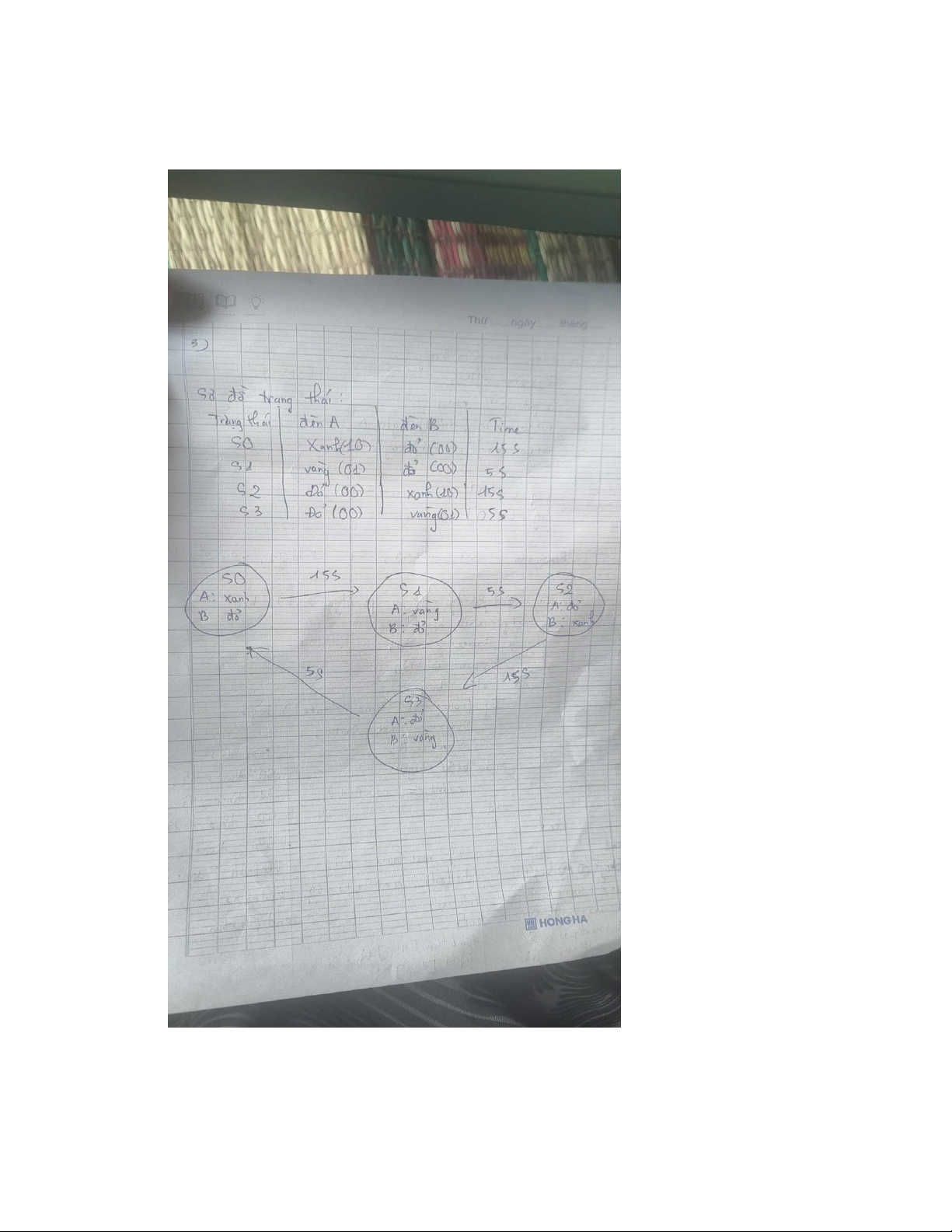

2) Thiết kế và mô phỏng mạch đèn giao thông 2 ngõ ra cho 2 trục đèn tín hiệu,

thời gian cho mỗi đèn là tương ứng xanh 15s đỏ 20s vàng 5s. - Code Verilog module traffic_light_fsm ( lOMoAR cPSD| 58778885

input clk, // Clock 1Hz (mỗi chu kỳ = 1s) input

rst, // Reset đồng bộ output reg [1:0] A, // Đèn A:

00-Đỏ, 01-Xanh, 10-Vàng output reg [1:0] B // Đèn B: 00-Đỏ, 01-Xanh, 10-Vàng );

reg [1:0] state; // Trạng thái hiện tại reg

[5:0] timer; // Bộ đếm thời gian (0–63) // Mã trạng thái

parameter S0 = 2'd0, // A: Xanh, B: Đỏ (15s)

S1 = 2'd1, // A: Vàng, B: Đỏ (5s)

S2 = 2'd2, // A: Đỏ, B: Xanh (15s)

S3 = 2'd3; // A: Đỏ, B: Vàng (5s)

always @(posedge clk or posedge rst) begin if (rst) begin state <= S0; timer <= 0; end else begin timer <= timer + 1; case (state)

S0: if (timer == 15) begin state <= S1; timer <= 0; end lOMoAR cPSD| 58778885

S1: if (timer == 5) begin state <= S2; timer <= 0; end S2:

if (timer == 15) begin state <= S3; timer <= 0; end S3: if (timer ==

5) begin state <= S0; timer <= 0; end endcase end end

// Đèn hiển thị theo trạng thái (Moore) always @(*) begin case (state)

S0: begin A = 2'b01; B = 2'b00; end // A xanh, B đỏ

S1: begin A = 2'b10; B = 2'b00; end // A vàng, B đỏ

S2: begin A = 2'b00; B = 2'b01; end // A đỏ, B xanh

S3: begin A = 2'b00; B = 2'b10; end // A đỏ, B vàng

default: begin A = 2'b00; B = 2'b00; end endcase end endmodule - Testbench

module Trung_traffic_light_fsm();

reg clk = 0, rst = 1; wire [1:0] A, B; traffic_light_fsm uut ( .clk(clk), .rst(rst), .A(A), .B(B) ); // Clock 1Hz always #500 clk = ~clk; lOMoAR cPSD| 58778885 initial begin

#1000 rst = 0; // nhả reset sau 1 chu kỳ #100000 $finish; end endmodule