Preview text:

lOMoAR cPSD| 58778885

TRƯỜNG ĐẠI HỌC SƯ PHẠM KỸ THUẬT TP.HCM

KHOA ĐIỆN – ĐIỆN TỬ

BÁO CÁO THỰC TẬP THIẾT KẾ MẠCH TÍCH HỢP VLSI

Mã môn học: ICDL416264_02CLC

GVHD: THS.Lê Minh Thành

SVTH: Nguyễn Anh Tuấn MSSV: 22161040

Thành phố Hồ Chí Minh, tháng 3 năm 2025 lOMoAR cPSD| 58778885

CHƯƠNG 1: LÝ THUYẾT VÀ MÔ PHỎNG CÁC CỔNG LOGIC

1.1 LÝ THUYẾT CỔNG NOT

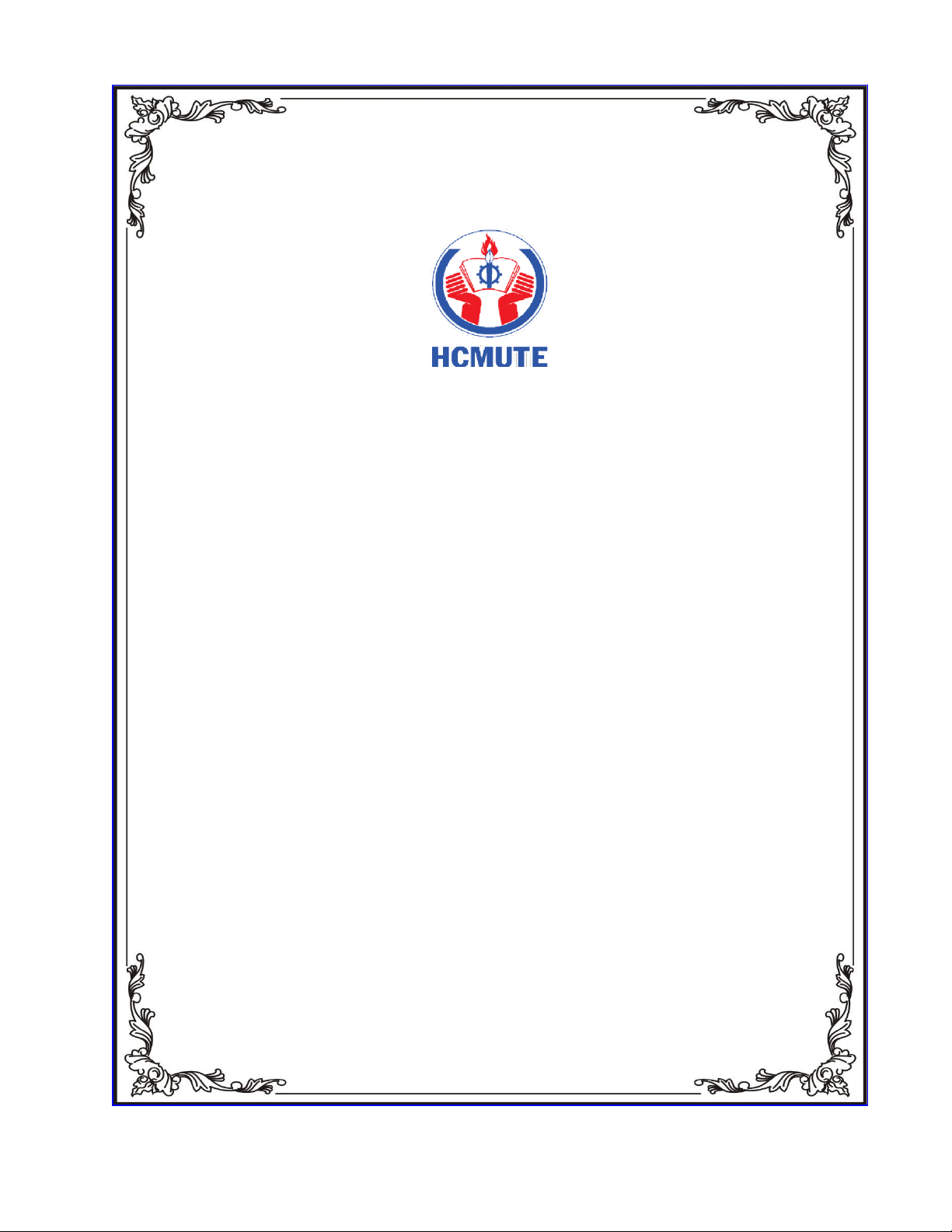

- Cổng NOT là cổng có 1 ngõ vào và 1 ngõ ra có chức năng đảo tín hiệu đầu vào.

- Ngõ vào mức 1 (mức cao) thì ngõ ra mức 0 (mức thấp).

- Ngõ vào mức 0 (mức thấp) thì ngõ ra mức 1 (mức cao). A X 0 1 1 0

Hình 1.1 Ký hiệu và bảng trạng thái cổng NOT

Hình 1.2 Sơ đồ nguyên lý

- Cổng NOT được cấu tạo từ 1 PMOS và 1 NMOS. PMOS dẫn tốt mức 1 nên

được nối với nguồn VDD, NMOS dẫn tốt mức 0 nên được nối với GND. lOMoAR cPSD| 58778885

- Tỷ lệ W/L của PMOS và NMOS phụ thuộc vào công nghệ CMOS và các yếu

tố khác nhưng phải đáp ứng điều kiện tỷ lệ W/L của PMOS gấp 2 đến 3 lần tỷ lệ W/L của NMOS

1.2 MÔ PHỎNG CỔNG NOT

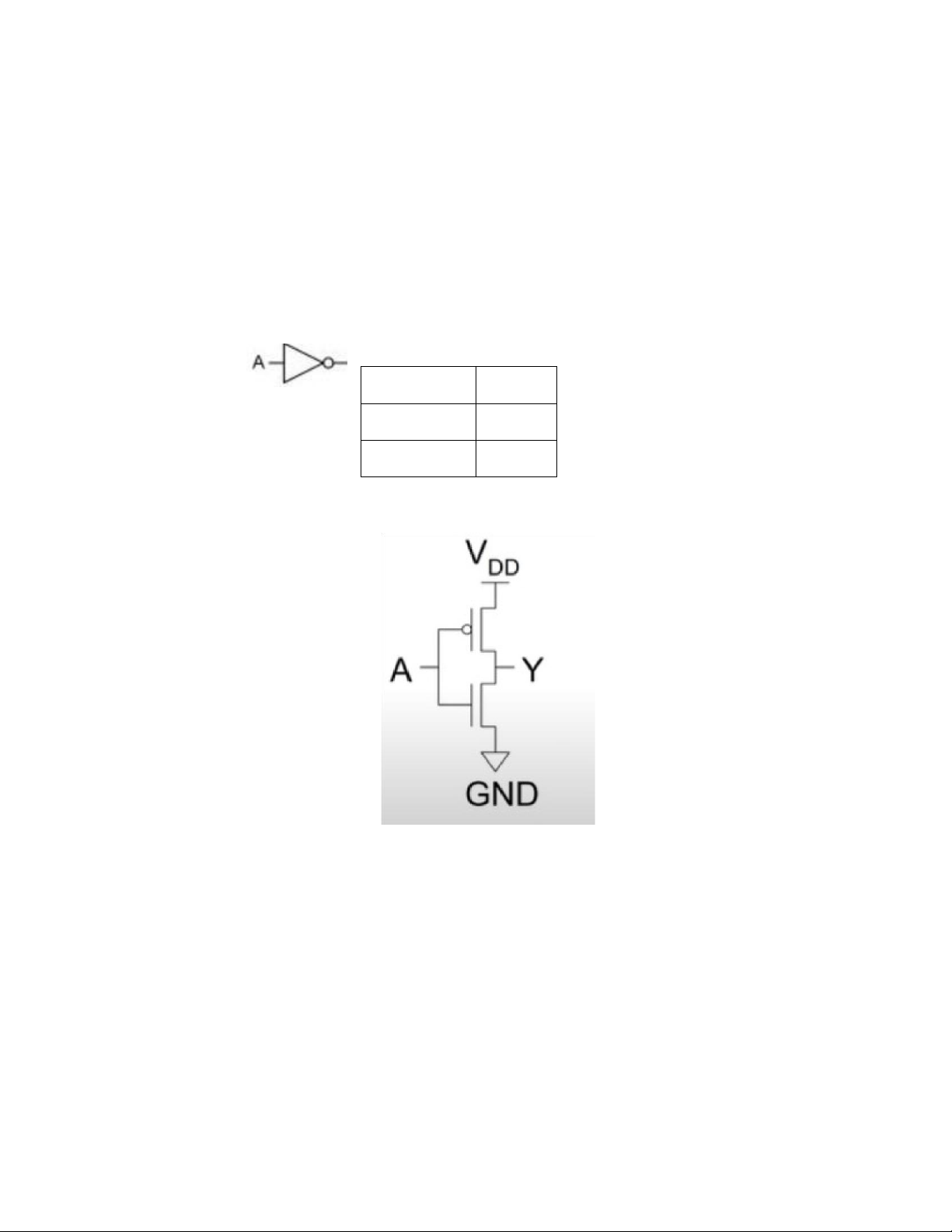

Hình 1.3 Sơ đồ nguyên lý mô phỏng cổng NOT

- Cổng NOT được tạo thành từ 1 NMOS và 1 PMOS có thông số thiết lập như sau: Bảng thông số: NMOS PMOS - L = 0.13um - L = 0.13um - W = 1.3um - W = 2.6um

- Bảng thông số thiết kế mô phỏng độ rộng (W), độ dài (L) và tỷ lệ W/L

của PMOS gấp 2 lần so với NMOS lOMoAR cPSD| 58778885

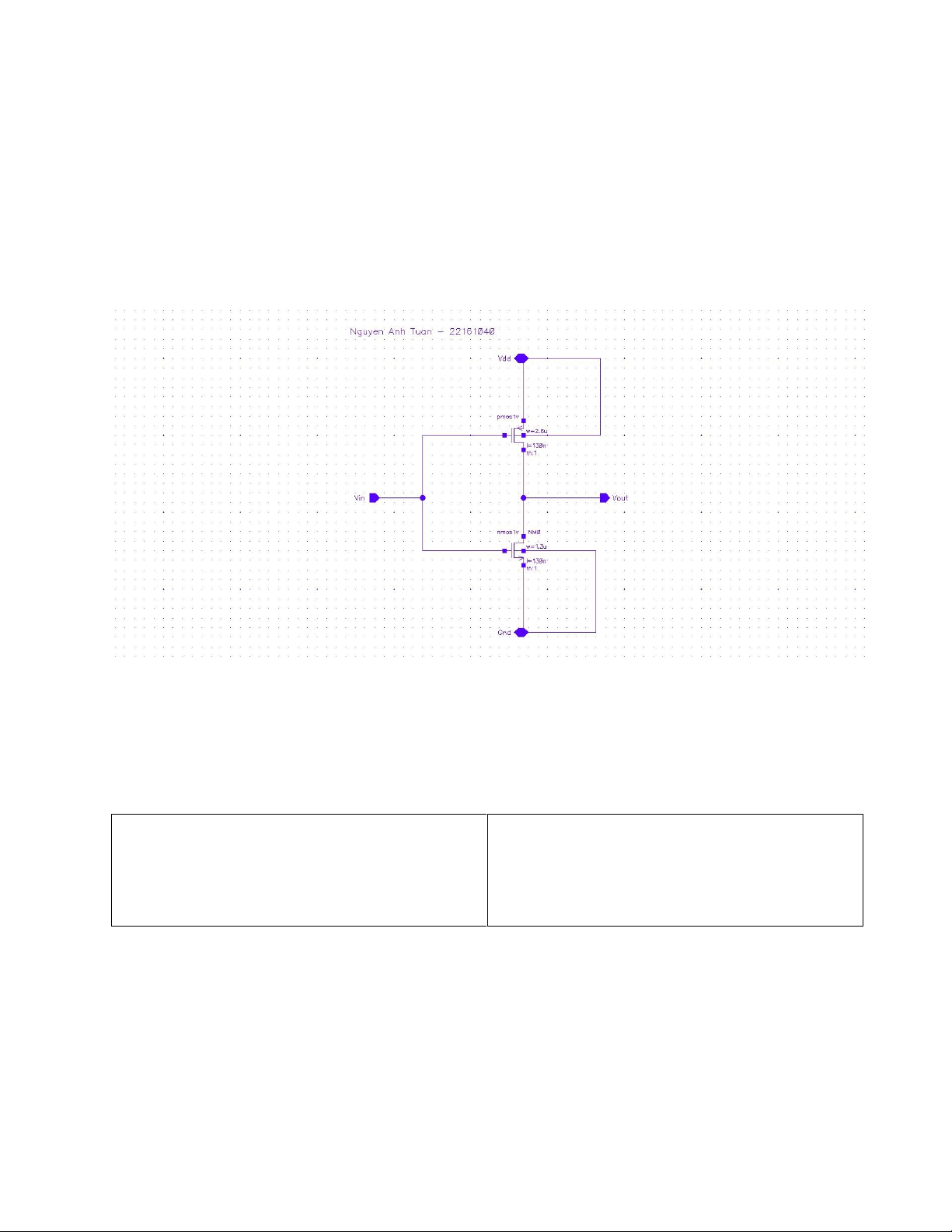

Hình 1.4 Nhiệt độ được thiết lập

- 27 độ C là nhiệt độ chuẩn trong hầu hết các mô phỏng điện tử để đảm bảo các

kết nối kết quả mô phỏng phản hồi môi trường hoạt động bình thường của mạch điện tử.

- Đóng gói linh kiện theo ký hiệu cổng NOT:

Hình 1.5 Đóng gói cổng NOT

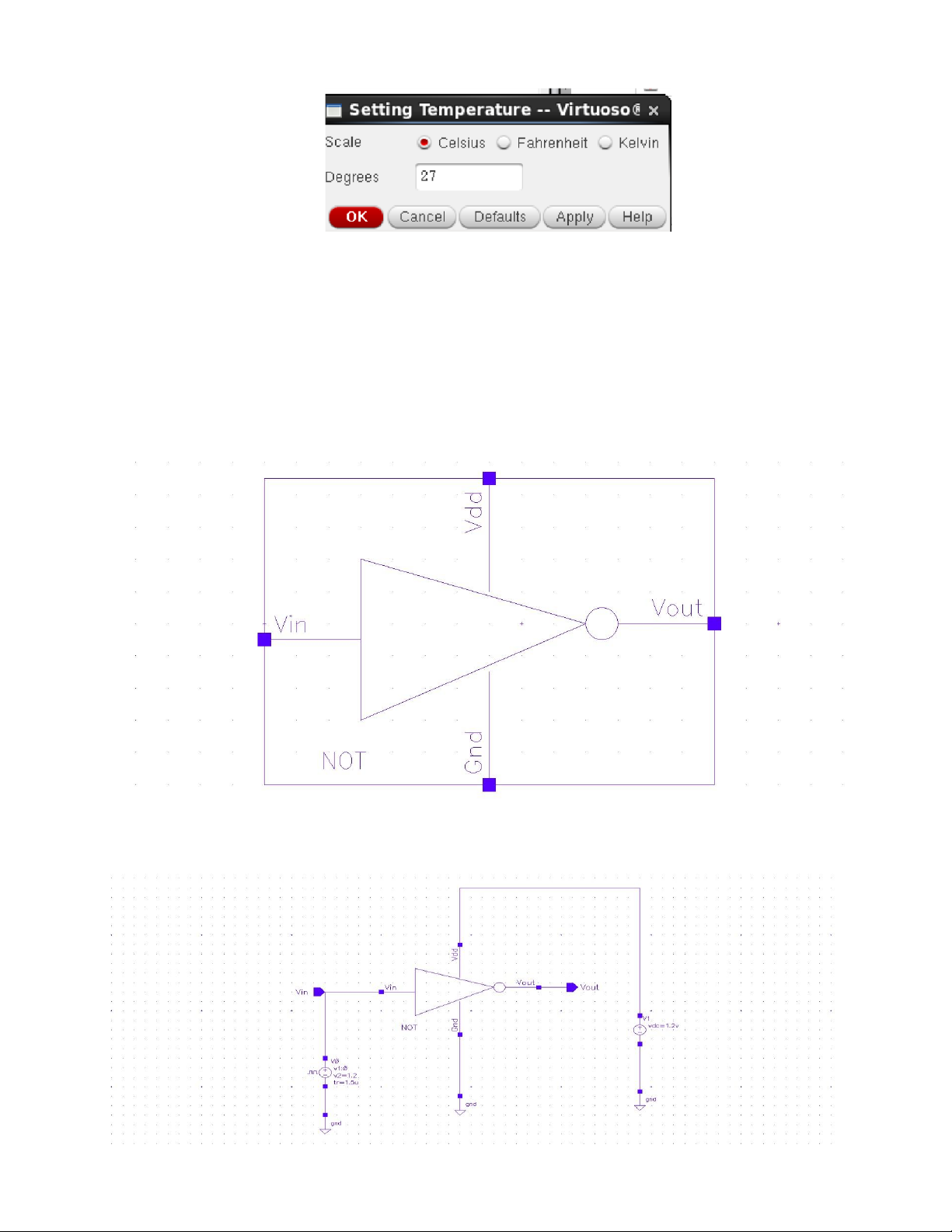

- Cấp nguồn, tín hiệu: VDD, VSS, VPULSE lOMoAR cPSD| 58778885

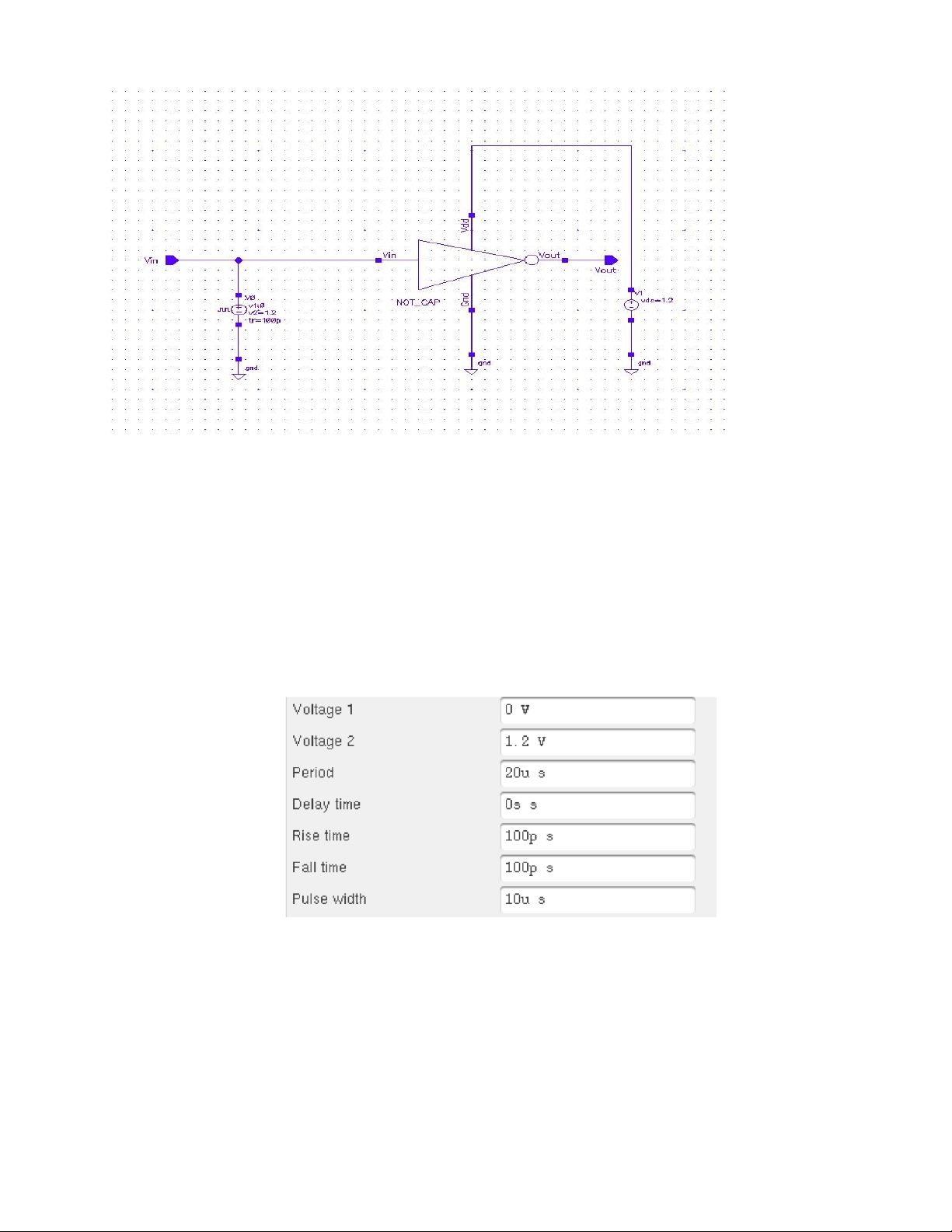

Hình 1.6 Mạch kiểm tra hoạt động cổng NOT - Thông số cài đặt:

+ Chân Vdd nối với nguồn Vdc = 1.2V.

+ Chân Gnd nối với đất.

+ Ngõ vào Vin nối với nguồn Vpulse để tạo xung đầu vào.

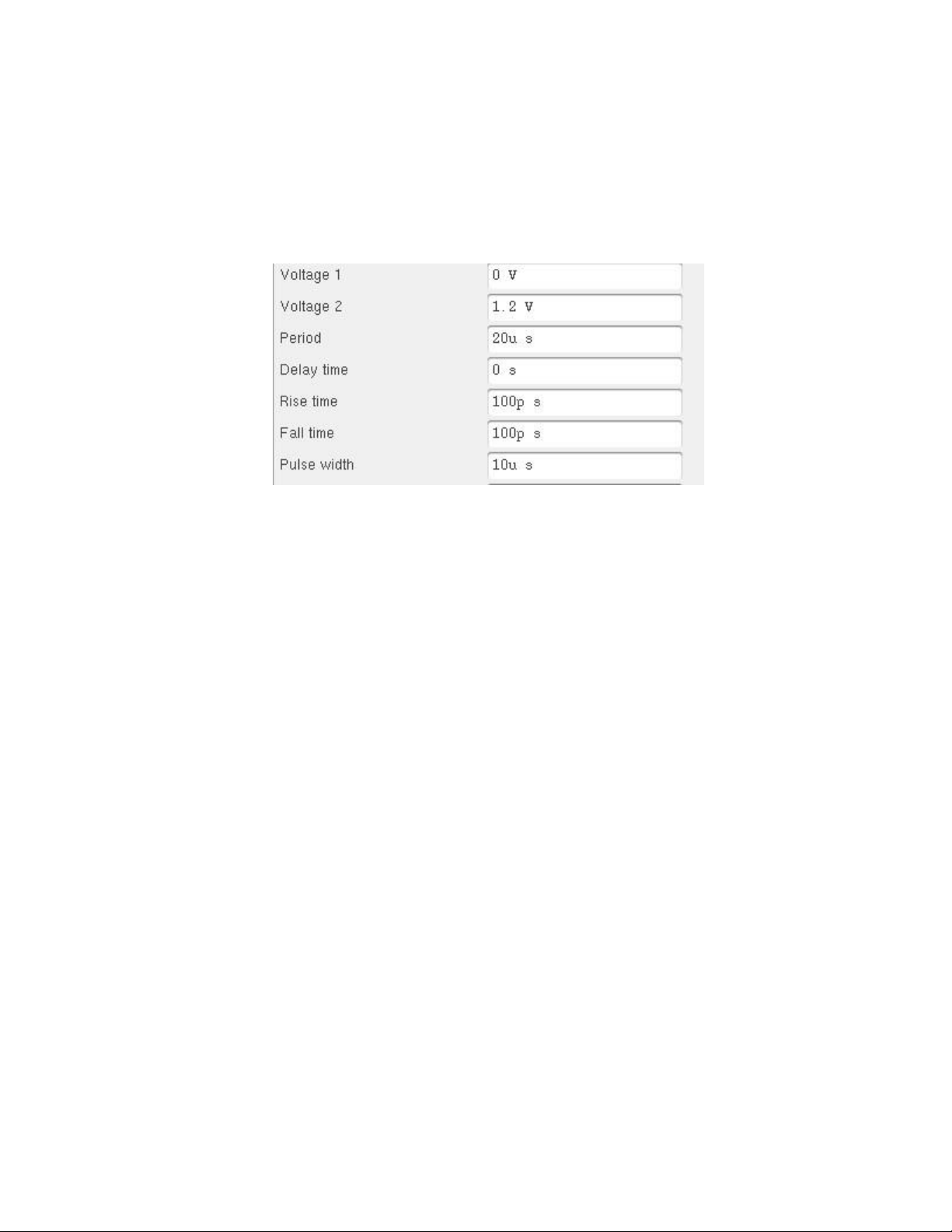

Hình 1.7 Thôngsố cài đặt

nguồn dùng tín hiệu ngõ vào - Điện áp 1(V1): 0V - Điện áp 2 (V2): 1.2V

- Độ rộng xung(Pulse width): 10us - Chu kỳ(period): 20us

- Thời gian trễ(Delay time): 0s

- Thời gian xung cạnh lên(Rise Time): 100ps

- Thời gian xung cạnh xuống(Fall Time): 100ps lOMoAR cPSD| 58778885

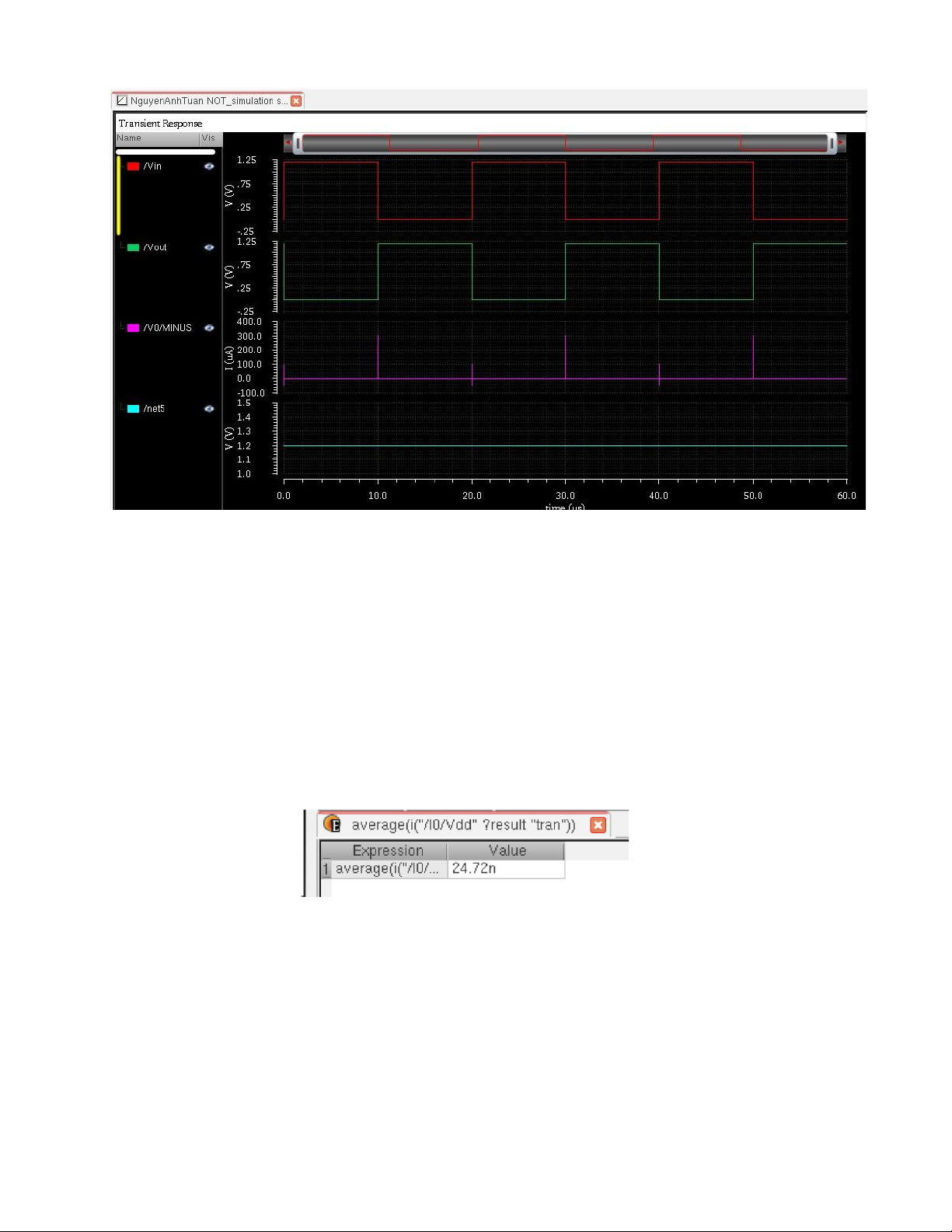

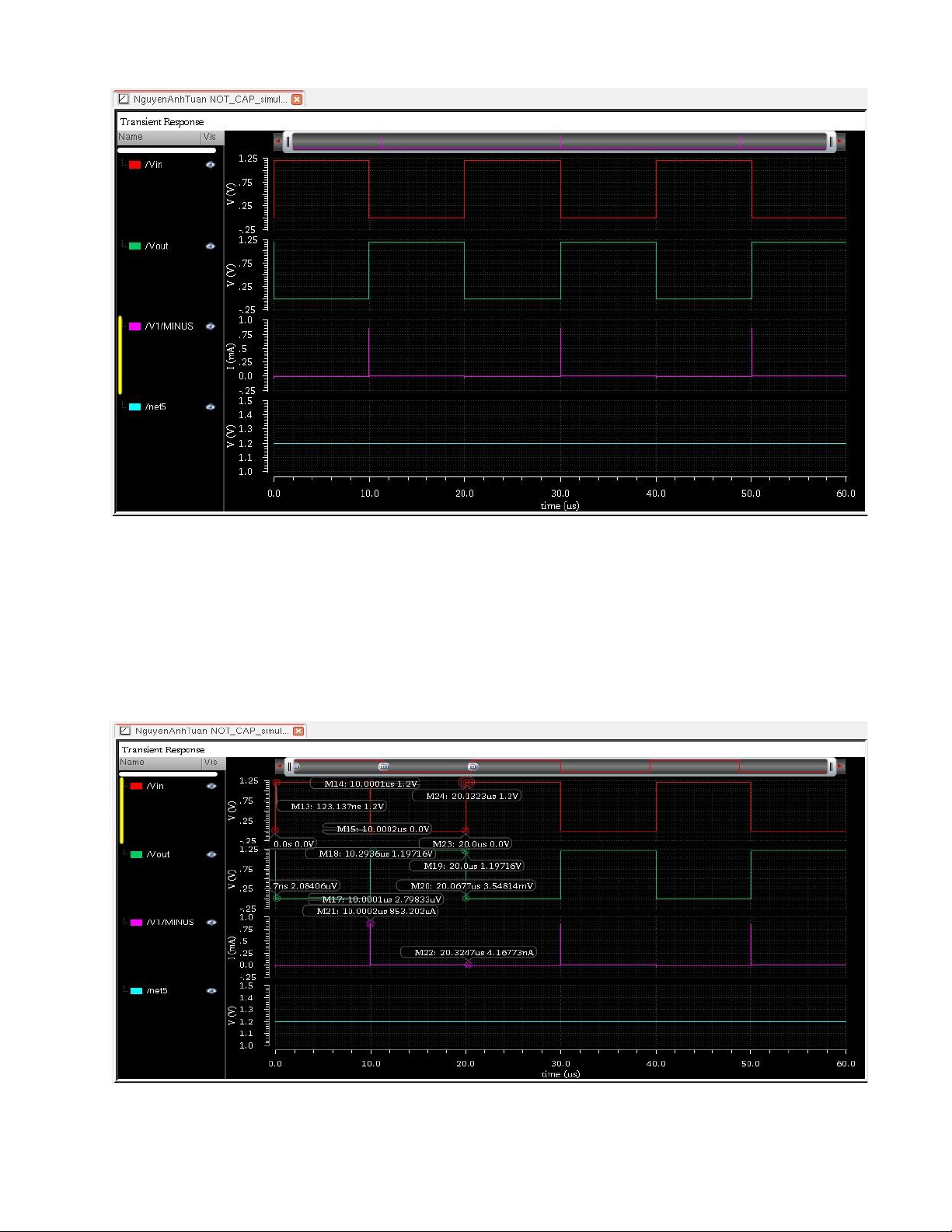

Hình 1.8 Sóng ngõ vào, ra và điểm dị thường

Vin: Ngõ vào (sóng màu đỏ)

Vout: Ngõ ra (sóng màu xanh)

+ 0us đến 10us Vin = 1.25v (mức 1) thì tín hiệu Vout = 0v (mức 0)

+ 10us đến 20us Vin = 0v (mức 0) thì tín hiệu Vout = 1.25v (mức 1)

- Dùng công cụ Caculator để tính toán công suất trung bình

Hình.1.9 Công suất trung bình lOMoAR cPSD| 58778885

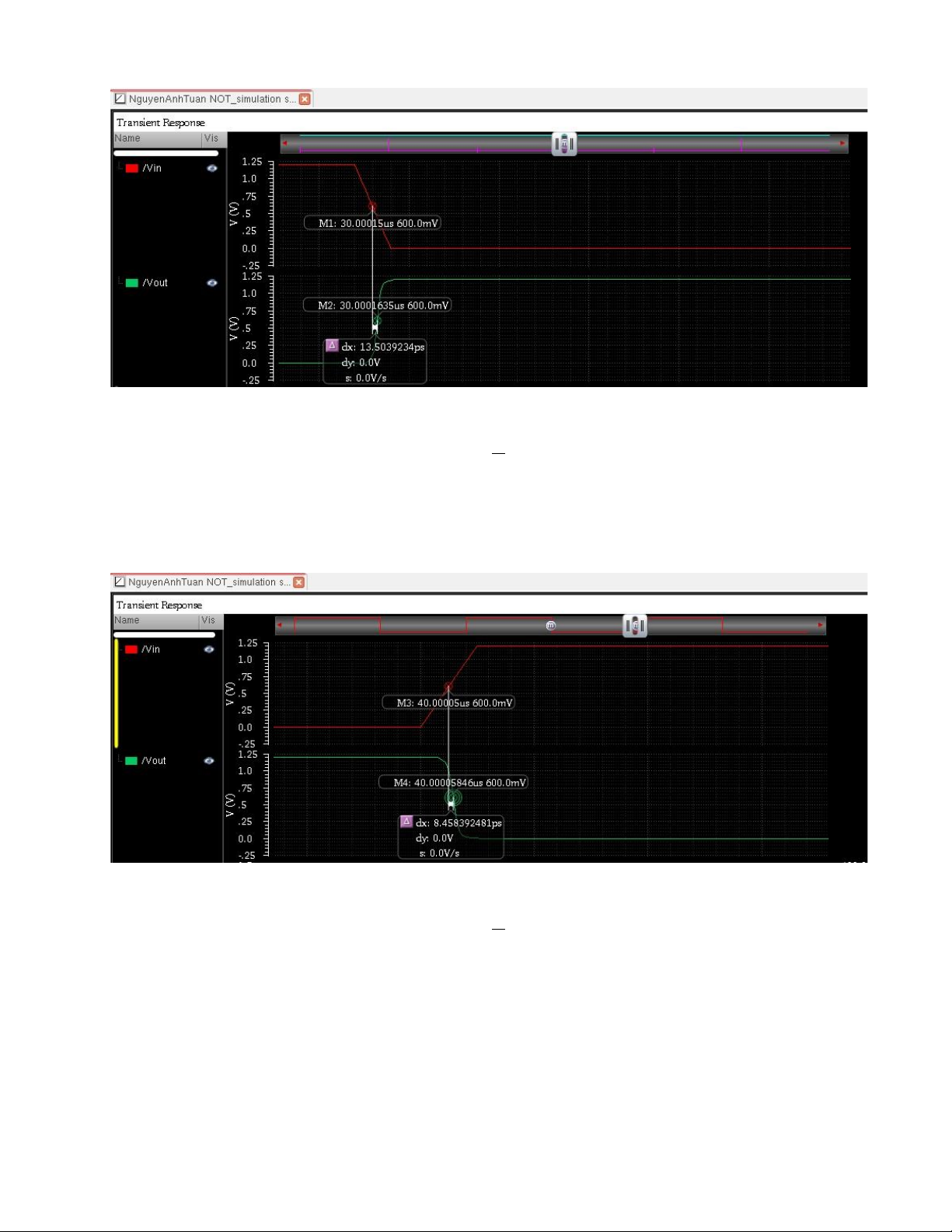

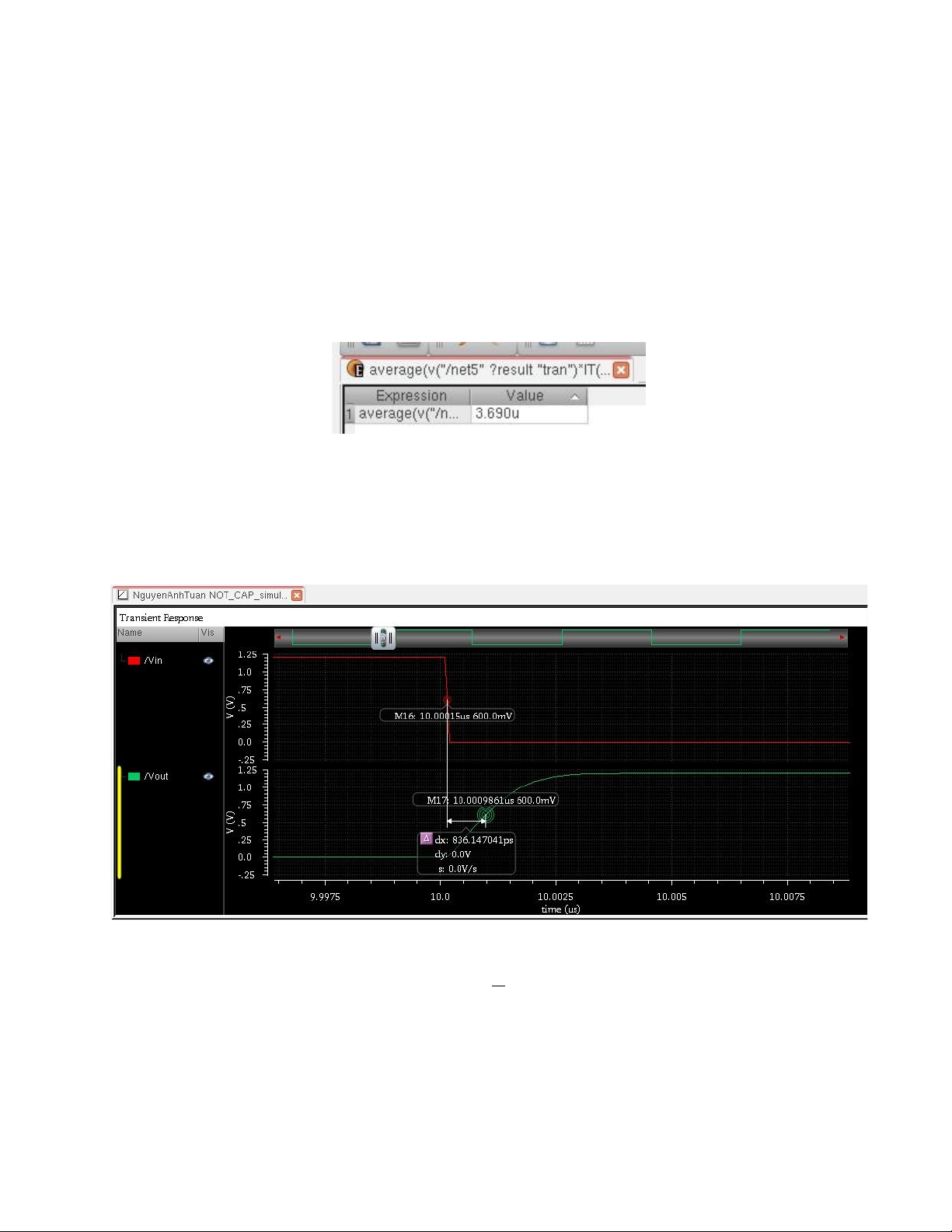

Hình 1.10 Độ trễ lan truyền cạnh lên cổng NOT V DD

- Đo độ chênh lệch điểm tại mức điện áp 2 =600mV của tín hiệu ngõ vào và tín hiệu

ngõ ra, ta tìm được độ trễ lan truyền cạnh lên là 13.5039234ps.

Hình 1.11 Độ trễ lan truyền cạnh xuống cổng NOT V DD

- Đo độ chênh lệch điểm tại mức điện áp 2 =600mV của tín hiệu ngõ vào và tín

hiệu ngõ ra, ta tìm được độ trễ lan truyền cạnh lên là 8.458392481ps.

- Độ trễ lan truyền trung bình : lOMoAR cPSD| 58778885

t pd=tpdr+2t pdf =13.5039234+28.458392481=10.98115794 ps

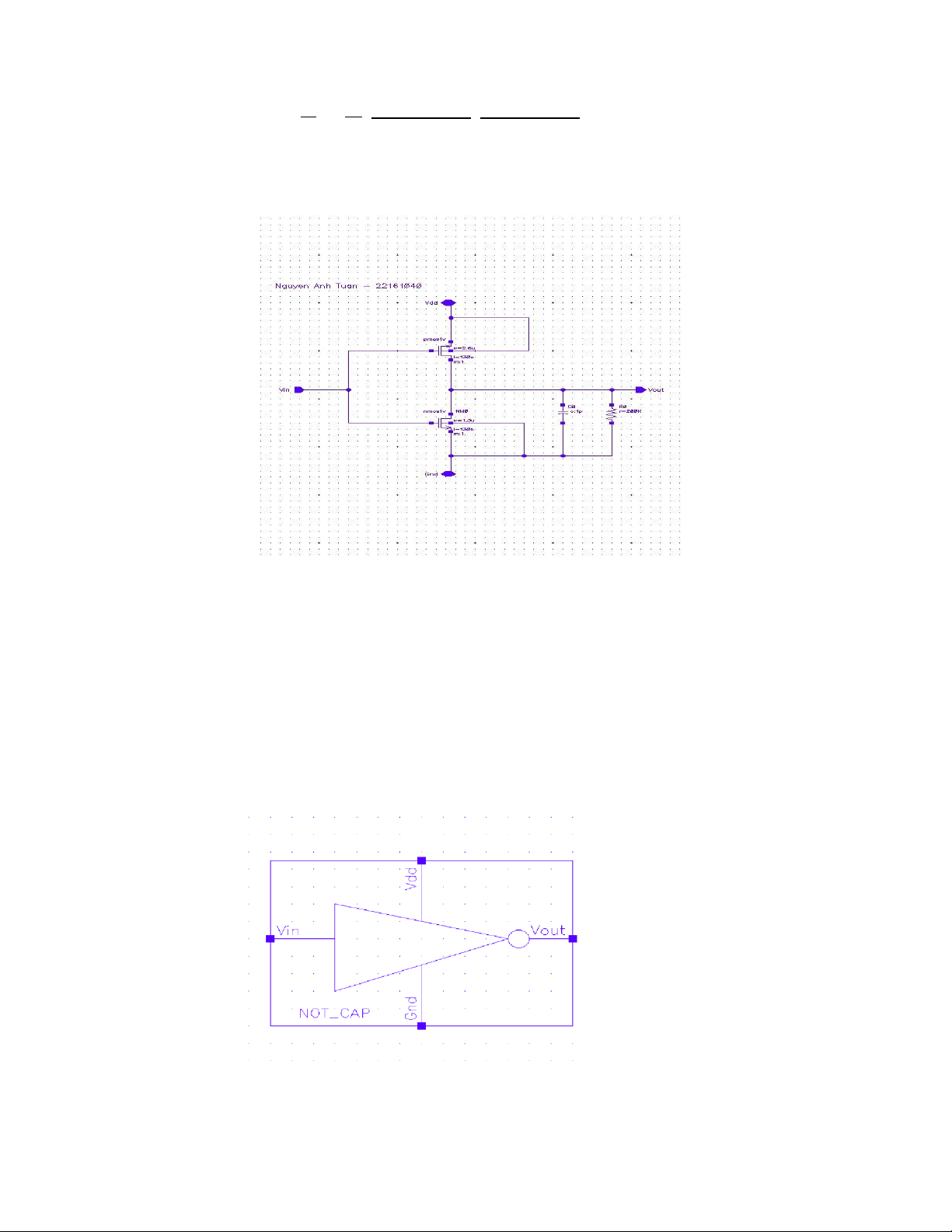

1.3 MÔ PHỎNG CỔNG NOT CÓ TỤ CR, TẢI RL

Hình 1.12. Sơ đồ nguyên lý mô phỏng cổng NOT có tụ và tải ký sinh

- Thiết lập thông số thiết kế mô phỏng độ rộng, độ dài, tỷ lệ W/L và nhiệt độ

môphỏng giống với cổng NOT không có tụ và tải ký sinh.

- Sau đó thực hiện đóng gói linh kiện

Hình 1.13 Đóng gói linh kiện cổng NOT có tụ và tải ký sinh

- Sau khi đóng gói thực hiện cấp nguồn để kiểm tra hoạt động lOMoAR cPSD| 58778885

Hình 1.14 Mạch kiểm tra hoạt động cổng NOT có tụ và tải ký sinh - Thông số thiết lập:

+ Chân Vdd nối với nguồn Vdc = 2V + Chân Gnd nối đất

+ Chân Vin nối với nguồn Vpulse với các thông số:

Hình 1.15 Thông số cài đặt nguồn Vpulse

- Thực hiện mô phỏng với các thông số đã thiết lập: lOMoAR cPSD| 58778885

Hình 1.16 Kết quả mô phỏng dạng sóng cổng NOT khi có tụ và tải

- Vin (đường màu đỏ) - Vout (đường màu xanh)

- V1/MINUS: dòng điện qua cổng NOT (đường màu hồng)

- net5: điện áp qua cổng NOT (đường màu xanh)

Hình 1.17 Sóng ngõ vào, ra và điểm dị thường của cổng NOT có tụ và tải lOMoAR cPSD| 58778885

- Từ đồ thị có thể xác định biên độ của tín hiệu ngõ vào, ngõ ra và các điểm cao thấp

bất thường của dòng điện qua cổng NOT có tụ và tải:

+ 0 - 10us, tín hiệu ngõ vào là 1.2V (mức cao) thì tín hiệu ngõ ra khoảng 2.08406uV (mức thấp).

+ 10us tới 20us, tín hiệu ngõ vào là 0V (mức thấp) thì tín hiệu ngõ ra là 1.19716V (mức cao).

- Tính công suất trung bình bằng công cụ Calculator

Hình 1.18 Công suất trung bình cổng NOT có tụ, tải

- Công suất trung bình của cổng NOT có gắn tụ, tải lớn hơn công suất trung bình của

cổng NOT không gắn tụ, tải (3.690u >24.72n) và chênh lệch 3.66528uW

Hình 1.19 Độ trễ lan truyền cạnh lên cổng NOT có gắn tụ, tải V DD

- Đo độ chênh lệch điểm tại mức điện áp 2 =600mV của tín hiệu ngõ vào và tín hiệu

ngõ ra, ta tìm được độ trễ lan truyền cạnh lên là 836.147041ps. lOMoAR cPSD| 58778885

Hình 1.20 Độ trễ lan truyền cạnh xuống cổng NOT có gắn tụ, tải V DD

- Đo độ chênh lệch điểm tại mức điện áp 2 =600mV của tín hiệu ngõ vào và tín hiệu

ngõ ra, ta tìm được độ trễ lan truyền cạnh lên là 863.251306ps.

- Độ trễ lan truyền trung bình :

t pd=tpdr+2t pdf =836.147041+2863.251306=849.6991735 ps

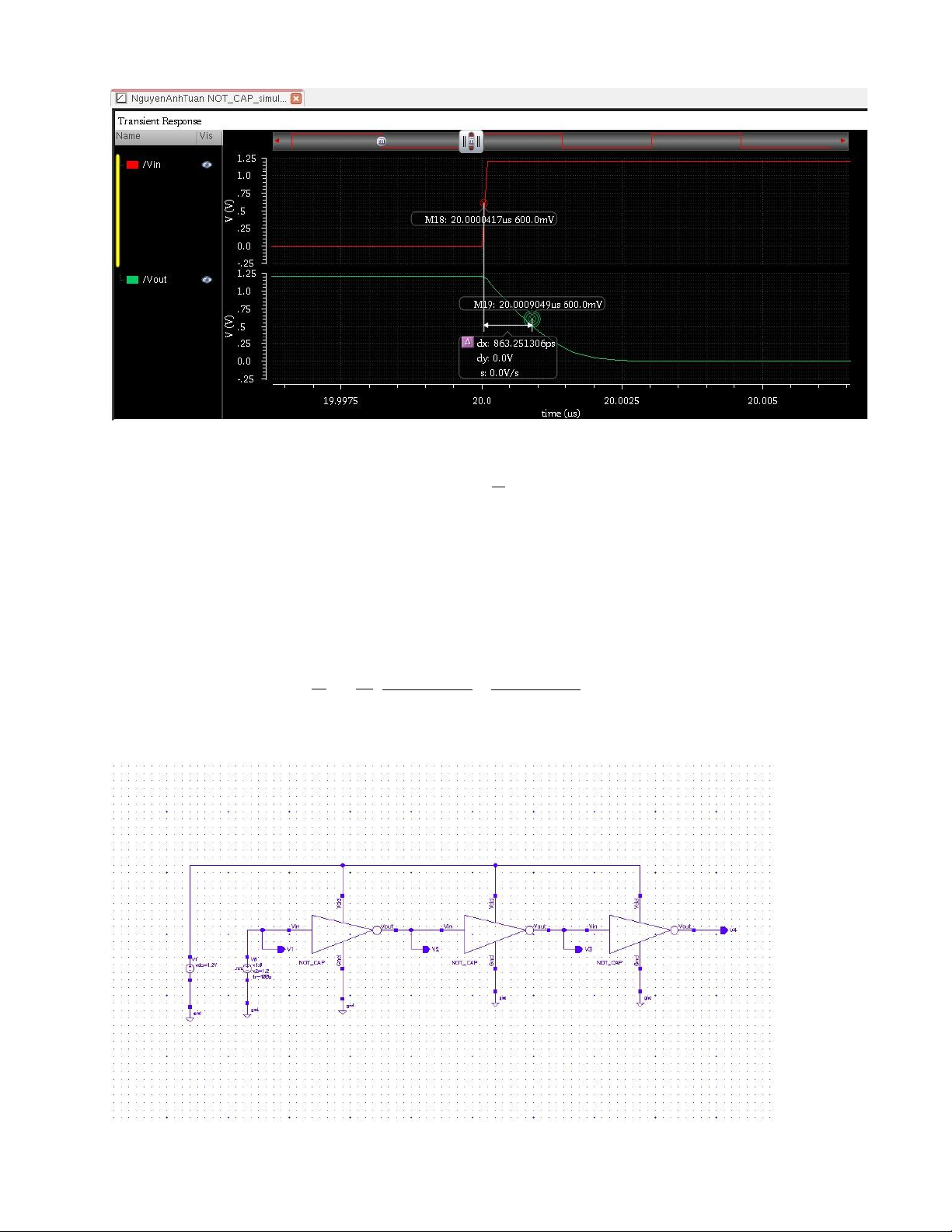

1.4. MẠCH GHÉP TẦNG 3 CỔNG NOT

Hình 1.21. Mạch ghép tầng 3 cổng NOT có tụ, tải lOMoAR cPSD| 58778885

- Thiết kế mạch ghép tầng 3 cổng NOT để xét độ trễ truyền

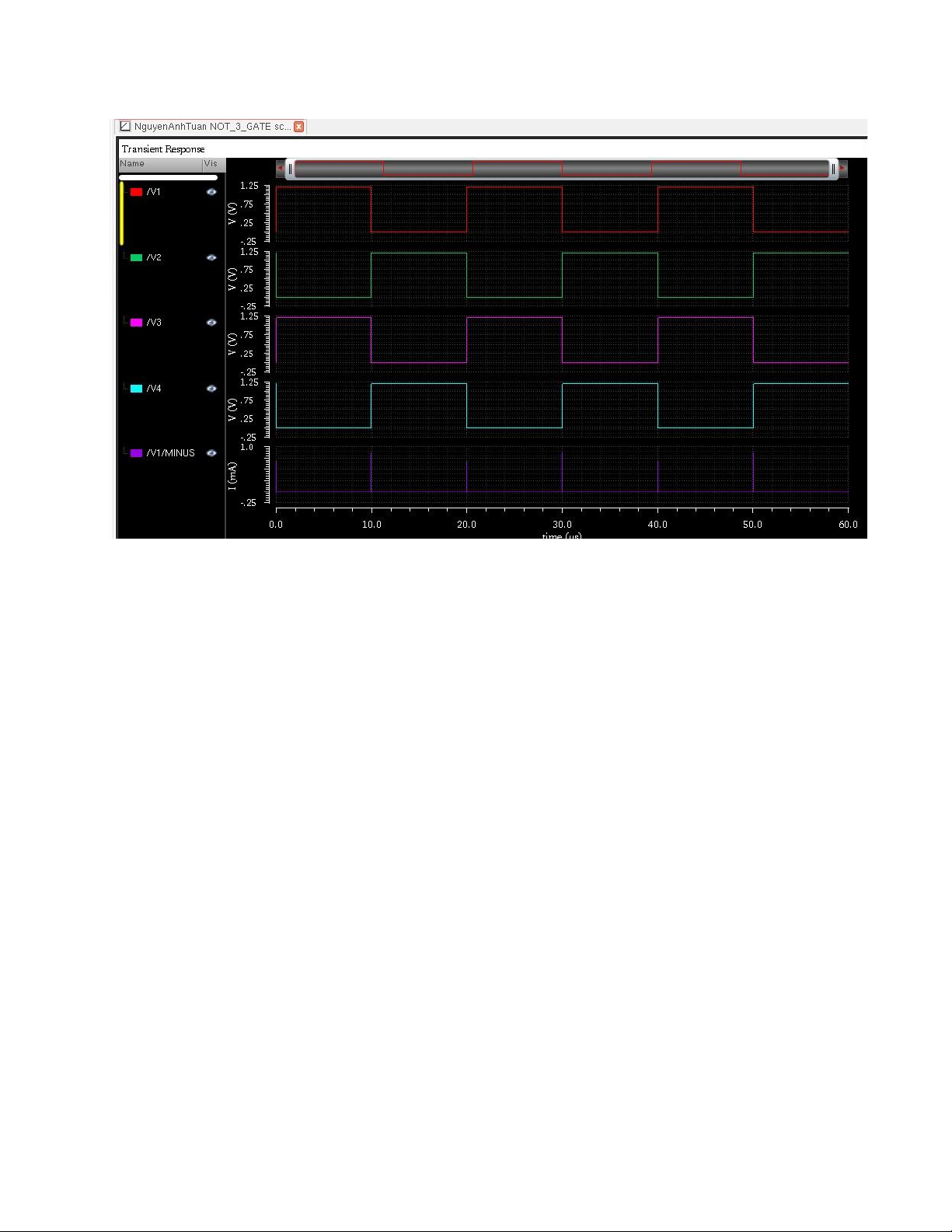

Hình 1.22. Kết quả mô phỏng dạng sóng của mạch ghép 3 cổng NOT có tụ và tải

- Sau khi thực hiện mô phỏng kết quả thu được dạng sóng như hình trên.

+ V1: ngõ vào cổng NOT đầu tiên (đường màu đỏ).

+ V2: ngõ ra cổng NOT đầu tiên, ngõ vào cổng NOT thứ 2 (đường màu xanh lá).

+ V3: ngõ ra cổng NOT thứ 2, ngõ vào cổng NOT thứ 3 (đường màu hồng).

+ V4: ngõ ra cổng NOT thứ 3 (đường màu xanh dương).

+ V1/MINUS: dòng điện qua các cổng NOT (đường màu tím). lOMoAR cPSD| 58778885

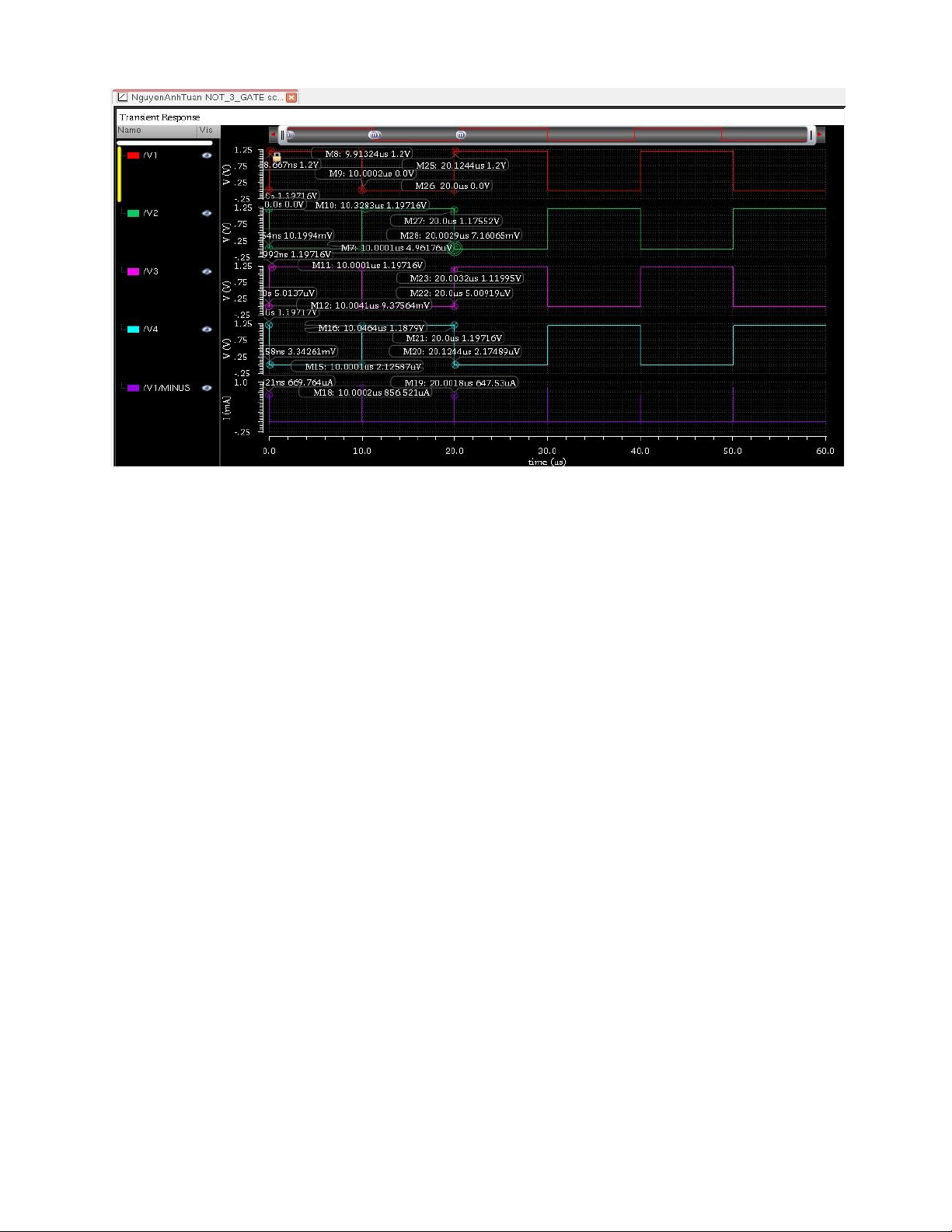

Hình 1.23 Sóng ngõ vào, ra và điểm dị thường của 3 cổng NOT - Nhận xét:

+ So sánh dạng sóng tín hiệu V1 và V2:

• Mức điện áp cao của tín hiệu V2 là 1.19716V nhỏ hơn mức điện áp cao của

tín hiệu V1 là 1.2V (lệch 2.84mV).

• Mức điện áp thấp của tín hiệu V2 khoảng 4.96176uV lớn hơn mức điện áp

thấp của tín hiệu V1 là 0V (lệch khoảng 4.96176uV).

+ So sánh dạng sóng tín hiệu V2 và V3:

• Mức điện áp cao của tín hiệu V2 và tín hiệu V3 không có sự chênh lệch.

• Mức điện áp thấp của tín hiệu V2 khoảng 4.96176uV nhỏ hơn mức điện áp

thấp của tín hiệu V3 khoảng 9.37564mV (lệch khoảng 9.37064824mV).

+ So sánh dạng sóng tín hiệu V3 và V4:

• Mức điện áp cao của tín hiệu V3 và tín hiệu V4 không có sự chênh lệch.

• Mức điện áp thấp của tín hiệu V4 khoảng 2.12587uV nhỏ hơn mức điện áp

thấp của tín hiệu V3 là 9.37564mV (lệch khoảng 9.37351413mV).

- Dùng công cụ Calculator tính công suất trung bình lOMoAR cPSD| 58778885

Hình 1.24 Công suất trung bình 3 cổng NOT

- Công suất trung bình của mạch ghép tầng 3 cổng NOT lớn hơn so với công suất trung bình của cổng

NOT có gắn tụ, tải (11.09uW > 3.690uW), gấp khoảng 3 lần. V DD

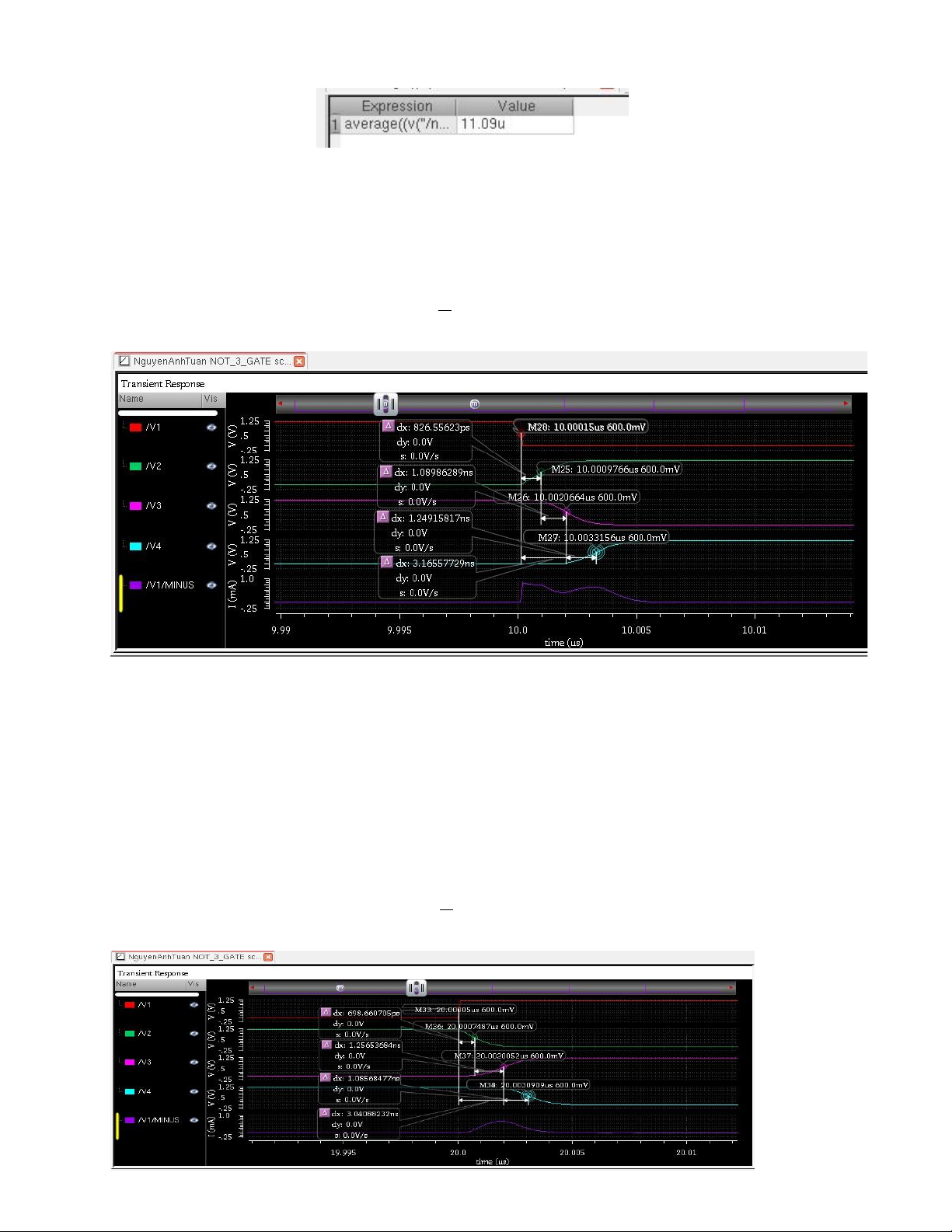

- Đo độ chênh lệch tại mức điện áp =600mV của tín hiệu ngõ vào và ngõ ra: 2

Hình 1.25 Độ trễ lan truyền tín hiệu ngõ vào, ngõ ra 3 cổng NOT

- Độ trễ lan truyền cạnh lên của tín hiệu ngõ ra V2 so với tín hiệu V1(t pdr1) là 826.55623ps.

- Độ trễ lan truyền cạnh xuống của tín hiệu ngõ ra V3 so với tín hiệu V2(t pdf 2) là 1.08986289ns.

- Độ trễ lan truyền cạnh lên của tín hiệu ngõ ra V4 so với tín hiệu V3 (t pdr3)là 1.24915817ns. - Độ trễ lan

truyền cạnh lên của tín hiệu ngõ ra V4 so với tín hiệu V1 (t pdr4)là 3.16557729ns. V DD

- Đo độ chênh lệch tại mức điện áp =600mV của tín hiệu ngõ vào và ngõ ra: 2 lOMoAR cPSD| 58778885

Hình 1.26 Độ trễ lan truyền tín hiệu ngõ vào, ngõ ra 3 cổng NOT

- Độ trễ lan truyền cạnh xuống của tín hiệu ngõ ra V2 so với tín hiệu V1(t pdf 1) là 698.660705ps.

- Độ trễ lan truyền cạnh lên của tín hiệu ngõ ra V3 so với tín hiệu V2 (t pdr2)là 1.25653684ns.

- Độ trễ lan truyền cạnh xuống của tín hiệu ngõ ra V4 so với tín hiệu V3(t pdf 3) là 1.08568477ns.

- Độ trễ lan truyền cạnh lên của tín hiệu ngõ ra V4 so với tín hiệu V1 (t pdf 4)là 3.04088232ns.

- Độ trễ lan truyền trung bình của các tín hiệu:

t pd1=tpdr1+2tpdf 1=826.55623+2698.660705=762.6084675 ps

t pd2=tpdr2+2tpdf 2=1.25653684+21.08986289=1.173199865ns t pd3=tpdr3+2t

pdf3=1.24915817+2 1.08568477=1.16742147ns

t pd4=t pdr4+2t pdf 4=3.16557729+23.04088232=3.103229805ns 1.5. KẾT LUẬN

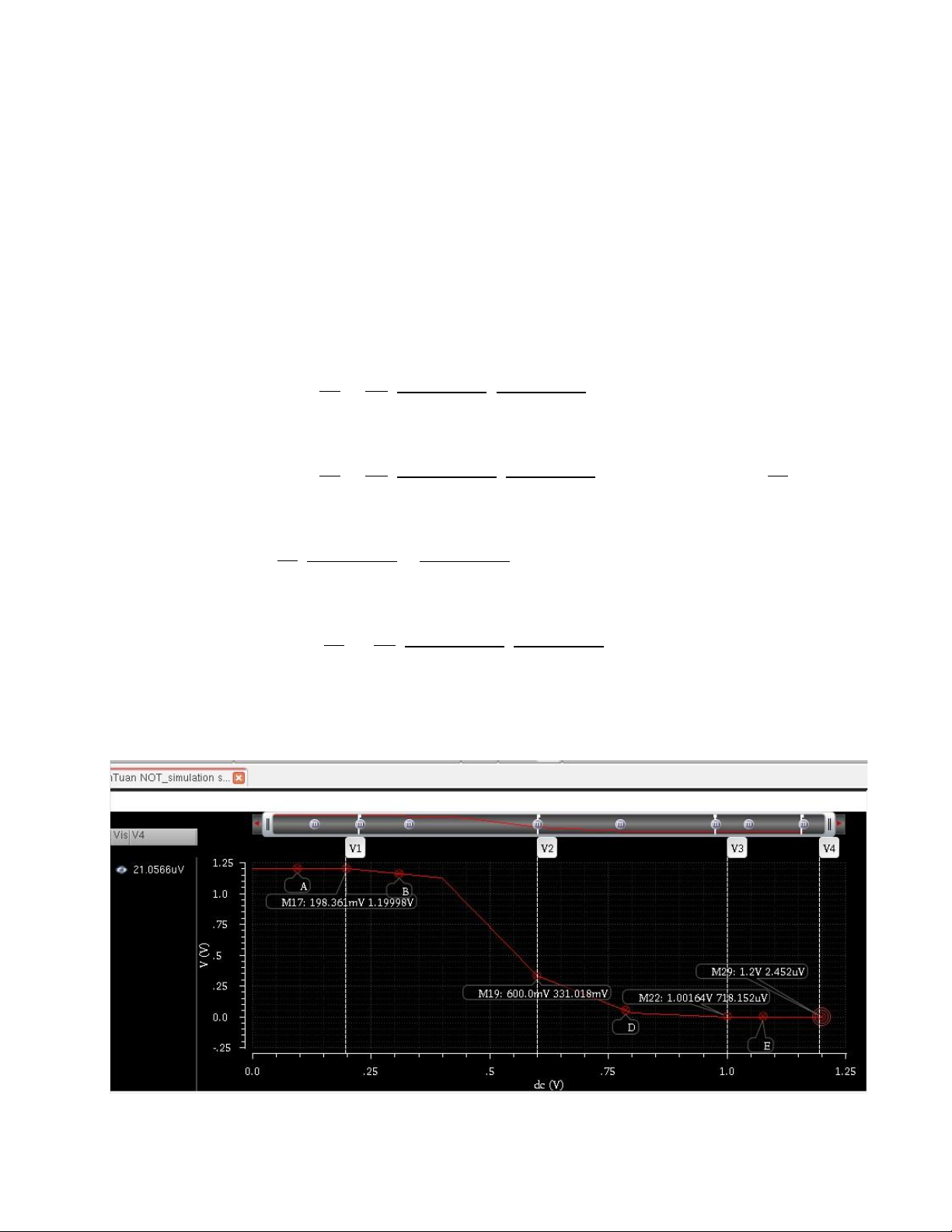

Hình 1.27 Đường đặc tuyến DC cổng NOT không có tụ, tải lOMoAR cPSD| 58778885

- Vout: đường đặc tuyến DC của tín hiệu ngõ ra (đường màu đỏ)

Bảng chế độ hoạt động của PMOS, NMOS: KHU VỰC ĐIỀU KIỆN PMOS NMOS A 0≤V¿<¿198.361mV Tuyến tính Ngưng dẫn B

198.361mV ≤V¿<600mV Tuyến tính Bão hòa C V¿=600mV Bão hòa Bão hòa D

600mV ≤V¿<1.00164V Bão hòa Tuyến tính E V¿>1.00164V Ngưng dẫn Tuyến tính

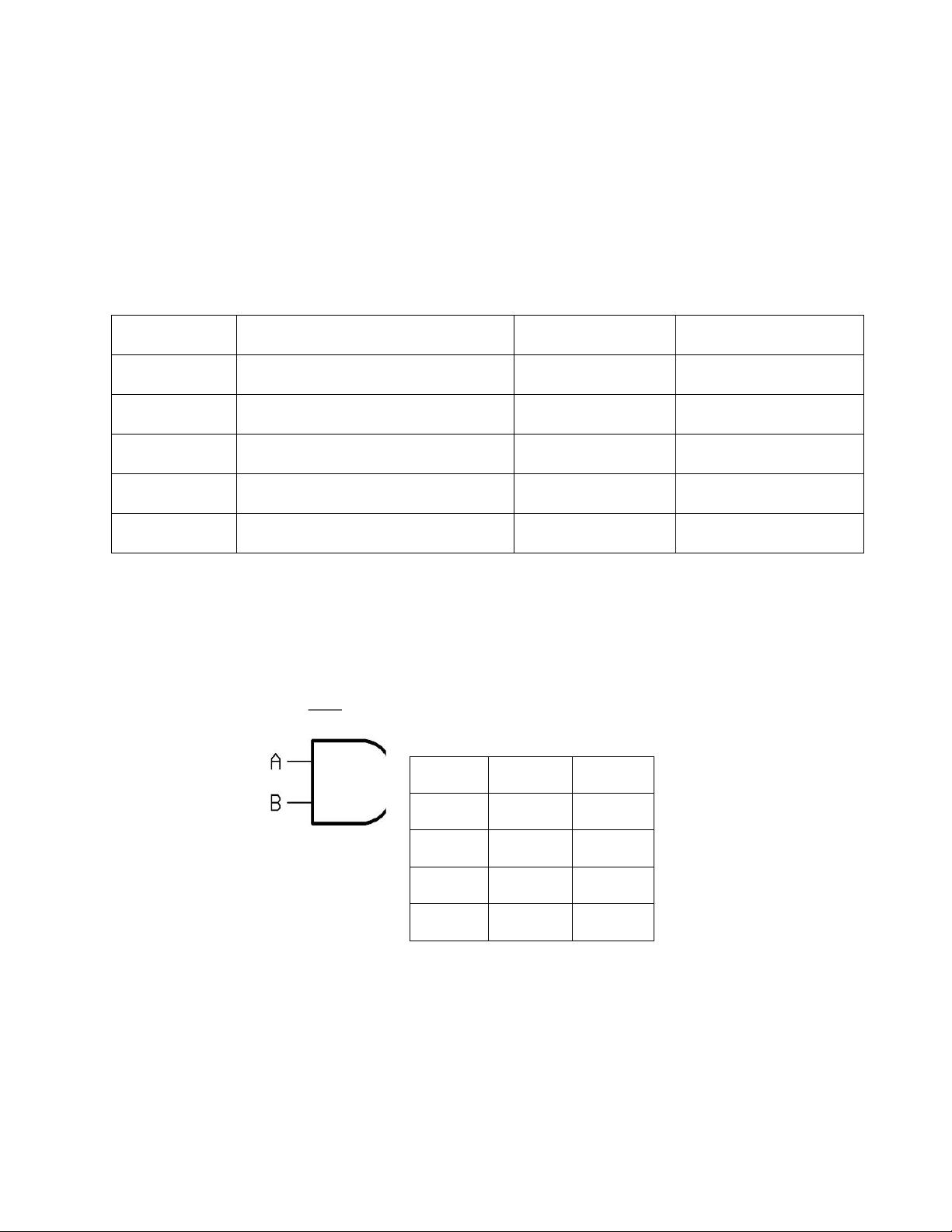

2.1. LÝ THUYẾT CỔNG NAND

- Cổng NAND (NOT AND) là một trong những cổng logic cơ bản quan trọng nhất

trong thiết kế mạch số. Nó là sự kết hợp giữa cổng AND và cổng NOT, có chức năng

phủ định đầu ra của cổng AND

- Biểu thức logic: Y = A.B A B Y 0 0 1 0 1 1 1 0 1 1 1 0

Hình 2.1. Ký hiệu và bảng trạng thái của cổng NAND

- Sơ đồ nguyên lý: Cổng NAND được thiết kế từ 2 PMOS và 2 NMOS. 2 PMOS mắc

song song, dẫn tốt mức “1” nên được nối với nguồn V DD, hai NMOS mắc nối tiếp,

dẫn tốt mức “0” nên được nối với GND. Đầu ra được lấy từ điểm chung giữa PMOS và NMOS. lOMoAR cPSD| 58778885

Hình 2.2 Sơ đồ nguyên lý cổng NAND

- Tỷ lệ W/L của PMOS và NMOS phụ thuộc vào công nghệ CMOS và các yếu

tố khác nhưng phải đáp ứng điều kiện tỷ lệ W/L của PMOS gấp 2 đến 3 lần tỷ lệ W/L của NMOS

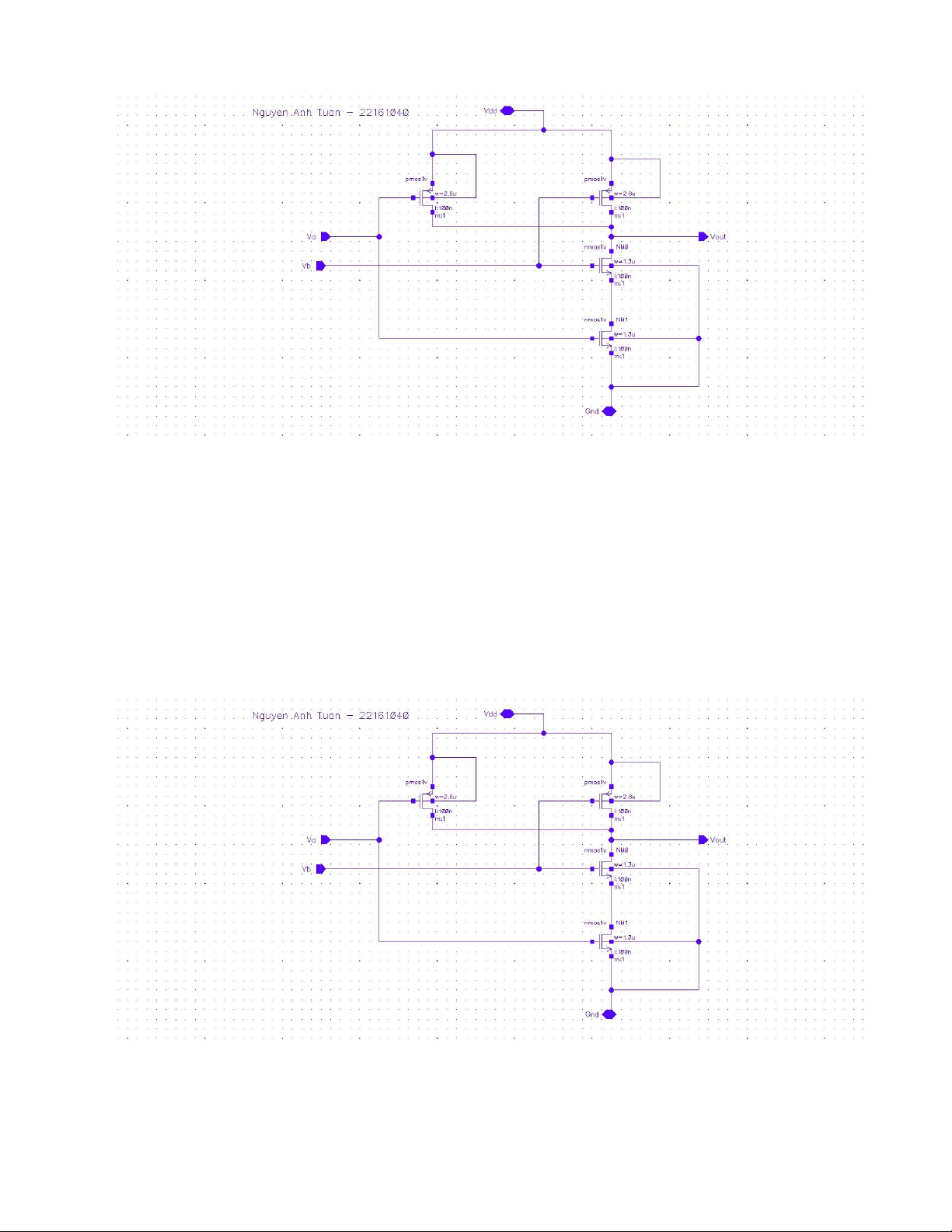

2.2 MÔ PHỎNG CỔNG NAND

- Sơ đồ nguyên lý và thông số thiết kế PMOS, NMOS:

Hình 2.3 Sơ đồ nguyên lý mô phỏng cổng NAND

- Bảng thông số thiết kế độ rộng (W), độ dài (L) và tỷ lệ W/L của PMOS gấp 2 lần NMOS lOMoAR cPSD| 58778885 Thông số PMOS NMOS L (um) 0.13u 0.13u W (um) 2.6u 1.3u

Bảng 2.4 Bảng thông số PMOS, NMOS để thiết kế mô phỏng cổng NAND

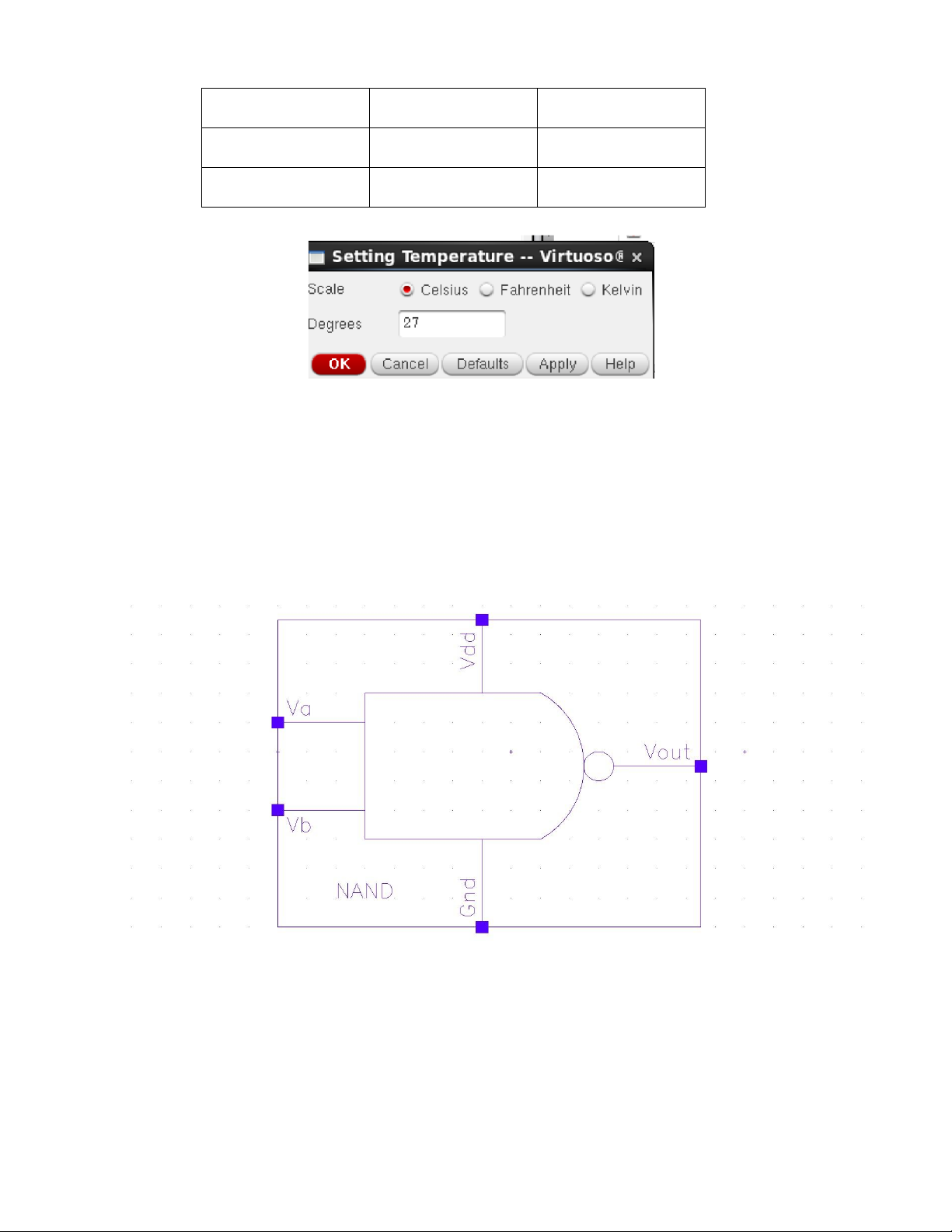

Hình 2.5 Nhiệt độ được thiết lập

- 27 độ C là nhiệt độ chuẩn trong hầu hết các mô phỏng điện tử để đảm bảo các

kết nối kết quả mô phỏng phản hồi môi trường hoạt động bình thường của mạch điện tử.

- Đóng gói thiết kế cổng NAND

Hình 2.6 Đóng gói thiết kế cổng NAND

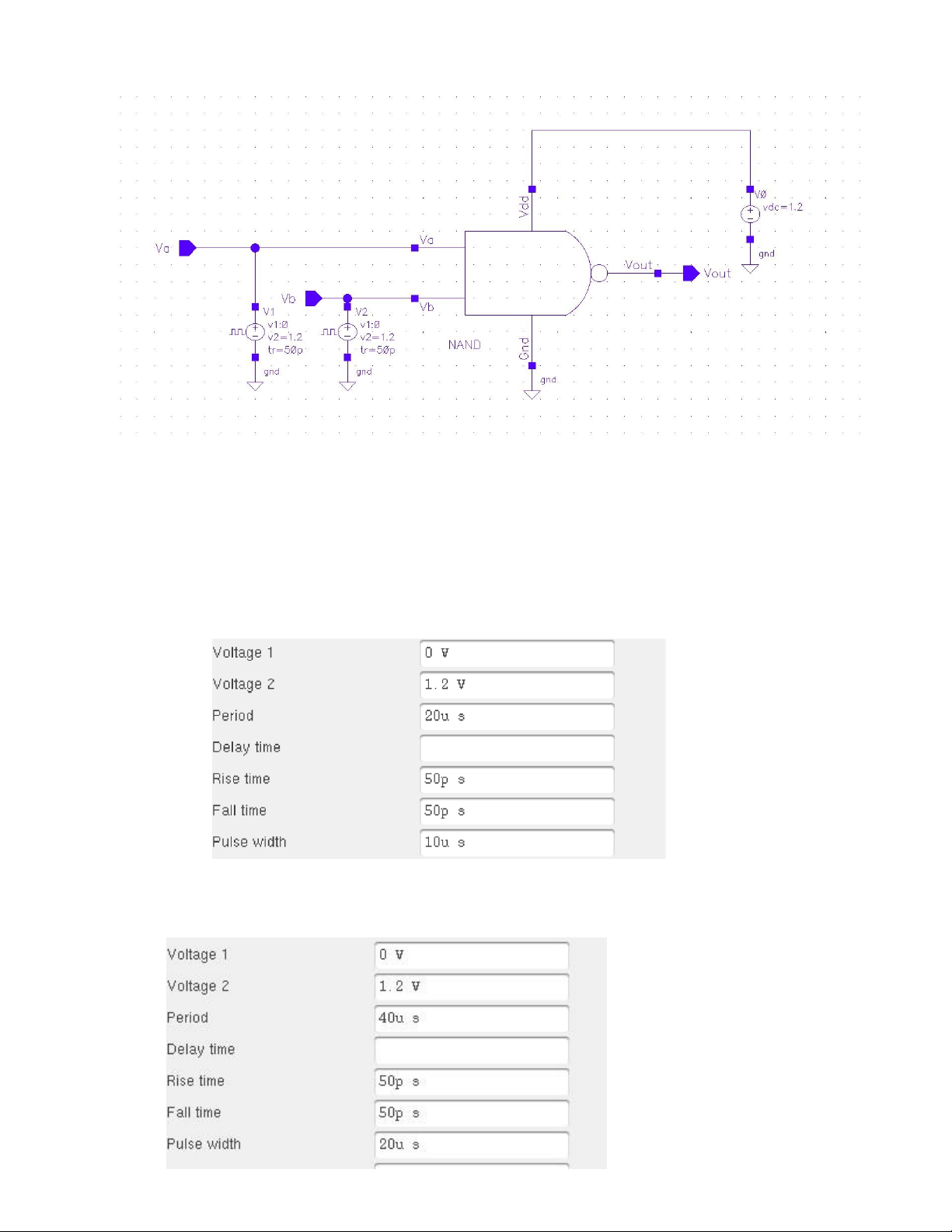

- Sau khi đóng gói thực hiện cấp nguồn để kiểm tra hoạt động lOMoAR cPSD| 58778885

Hình 2.7 Mạch kiểm tra hoạt động cổng NAND

- Thông số thiết lập:

+ Chân Vdd nối với nguồn Vdc = 1.2V + Chân Gnd nối đất

+ Chân Va nối với nguồn V1 với các thông số

Hình 2.8 Thông số cài đặt nguồn V1

+Chân Vb nối với nguồn V2 với các thông số