Preview text:

lOMoAR cPSD| 58778885

Bài học này tập trung vào việc phân tích và giải quyết các vấn đề liên quan đến tín hiệu đồng hồ

(clock) trong thiết kế VLSI (Very Large Scale Integration), đặc biệt là cách xử lý hiện tượng nhiễu

(glitch) và độ lệch tín hiệu (skew) do hiện tượng crosstalk (nhiễu chéo) gây ra. Dưới đây là giải

thích chi tiết nội dung dựa trên đoạn hội thoại và các hình ảnh được đề cập:

1. Tầm quan trọng của tín hiệu đồng hồ (Clock) trong thiết kế •

Tín hiệu đồng hồ là nền tảng đồng bộ hóa: •

Đoạn hội thoại bắt đầu bằng việc đề cập đến việc đảm bảo tín hiệu đồng hồ có độ lệch

(skew) bằng không (00:18.530 - 00:20.690: "You mean the latency difference between

between the between the clock... But this particular flip flop lock been minus the clock

with this particular flip flop flop"). Điều này cho thấy tín hiệu đồng hồ phải được thiết kế

để đồng bộ hóa chính xác giữa các flip-flop (bộ ghi tạm) trong mạch, đặc biệt ở các giai

đoạn phát (launch flop) và bắt (capture flop). •

Ý tưởng này nhấn mạnh rằng bất kỳ sự khác biệt về độ trễ (latency) giữa các tín hiệu đồng

hồ có thể dẫn đến lỗi định thời, làm gián đoạn hoạt động của toàn bộ hệ thống. •

Tầm quan trọng trong các thiết kế phức tạp: •

Hội thoại đề cập đến việc tín hiệu đồng hồ là "critical net" (00:53.720 - 00:59.550: "So

next is the Glock next shooting So Glock next are considered to be the critical next in or design").

Điều này cho thấy tín hiệu đồng hồ là một trong những đường dẫn quan trọng nhất trong thiết kế

VLSI, vì nó ảnh hưởng trực tiếp đến hiệu suất và độ tin cậy của chip. •

Nếu tín hiệu đồng hồ bị nhiễu hoặc sai lệch, nó có thể gây ra các vấn đề nghiêm trọng, như

được mô tả sau này với hiện tượng glitch và skew. •

Vai trò đồng bộ hóa toàn hệ thống: Tín hiệu đồng hồ giống như "trái tim" của một mạch

số, điều khiển nhịp độ hoạt động của tất cả các thành phần. Mọi flip-flop, bộ nhớ, hoặc logic trong

chip đều phụ thuộc vào tín hiệu này để thực hiện các thao tác như đọc, ghi, hoặc xử lý dữ liệu đúng

thời điểm. Nếu tín hiệu đồng hồ không ổn định, toàn bộ hệ thống có thể rơi vào trạng thái không xác định (metastability). •

Ảnh hưởng đến hiệu suất: Tần số của tín hiệu đồng hồ quyết định tốc độ hoạt động của

chip. Một tín hiệu đồng hồ được tối ưu hóa (ít nhiễu, độ lệch thấp) cho phép chip hoạt động ở tần

số cao hơn, cải thiện hiệu suất. Ngược lại, nếu tín hiệu bị suy thoái, tần số phải giảm xuống để

tránh lỗi, làm giảm hiệu năng. •

Ứng dụng thực tế: Trong các chip hiện đại như CPU, GPU, hoặc các hệ thống nhúng (ví

dụ: trong ô tô, máy bay), tín hiệu đồng hồ phải được bảo vệ kỹ lưỡng để đảm bảo độ tin cậy. Một

lỗi nhỏ trong đồng bộ hóa có thể dẫn đến tai nạn hoặc hỏng hóc hệ thống, như được đề cập sau

này trong hội thoại với ví dụ về bộ nhớ trong chip ô tô (03:29.950 - 03:46.040). •

Thách thức trong thiết kế: Với sự gia tăng mật độ linh kiện trong chip (nhờ công nghệ

sản xuất nhỏ hơn), tín hiệu đồng hồ dễ bị ảnh hưởng bởi các yếu tố như nhiễu điện từ, nhiệt độ, và

độ dài đường dẫn. Điều này đòi hỏi các kỹ thuật như che chắn (shielding) và phân tích định thời

(timing analysis) để duy trì tính toàn vẹn của tín hiệu. lOMoAR cPSD| 58778885

2. Hiện tượng Glitch và tác động của nó Định nghĩa Glitch:

o Glitch được giới thiệu như một xung nhiễu ngắn xuất hiện trên tín hiệu do sự tương

tác giữa các đường dẫn (02:24.810 - 02:26.280: "First of all what is a glitch"). Hội

thoại lấy ví dụ về một đường dẫn đồng hồ (clock net) bị ảnh hưởng bởi một đường

dẫn khác (aggressor) thông qua tụ điện ghép (coupling capacitance). o Ví dụ cụ

thể: Một tín hiệu đồng hồ (victim) vốn được thiết kế để duy trì trạng thái logic ổn

định, nhưng do hoạt động chuyển đổi của tín hiệu nhiễu (aggressor), nó bị nhiễu và

tạo ra một xung không mong muốn (02:32.120 - 02:48.570).

Cơ chế gây ra Glitch:

o Glitch xảy ra khi có hoạt động chuyển đổi (switching activity) trên đường dẫn

aggressor, và do tụ điện ghép mạnh, tín hiệu victim bị ảnh hưởng tiêu cực

(02:37.680 - 02:49.890). Điều này làm tín hiệu đồng hồ bị biến dạng, chẳng hạn

như xuất hiện một "dip" (giảm đột ngột) trong điện áp (03:04.970 - 03:07.620).

o Hội thoại giải thích rằng sự tương tác này có thể làm sai lệch logic dự kiến, ví dụ

từ logic 1 thành logic 0 hoặc ngược lại (03:00.010 - 03:04.950).

Tác động của Glitch:

o Lỗi dữ liệu trong bộ nhớ: Glitch có thể kích hoạt sai tín hiệu reset (RST) của bộ

nhớ, dẫn đến việc dữ liệu trong bộ nhớ bị thay đổi. Ví dụ, một chuỗi bit như

"111010111101" có thể bị ghi đè thành "010101001010" (03:13.370 - 03:24.530).

o Hậu quả nghiêm trọng: Nếu bộ nhớ này thuộc về một chip quan trọng (ví dụ: chip

ô tô hoặc hệ thống máy tính), glitch có thể khiến toàn bộ hệ thống bị reset hoặc hoạt

động sai, dẫn đến hỏng hóc nghiêm trọng (03:29.950 - 03:46.250). Hội thoại nhấn

mạnh rằng đây là một "điểm quan trọng" cần được xem xét trong thiết kế (03:46.250 - 03:51.840). •

Nguồn gốc vật lý của Glitch: Ngoài crosstalk, glitch còn có thể do nhiễu điện từ (EMI),

thay đổi điện áp nguồn (power supply noise), hoặc sự không đồng bộ trong quá trình sản

xuất chip. Trong bối cảnh hội thoại, tụ điện ghép (Cm) giữa các đường dẫn là yếu tố chính,

nhưng các yếu tố khác cũng cần được xem xét trong thực tế. •

Ảnh hưởng đến định thời: Glitch không chỉ làm sai dữ liệu mà còn làm tăng độ trễ (delay)

hoặc gây ra lỗi định thời (timing violation). Điều này đặc biệt nguy hiểm trong các hệ thống

tốc độ cao, nơi mọi chu kỳ đồng hồ đều quan trọng. Ví dụ, một glitch ngắn có thể khiến

flip-flop bắt nhầm dữ liệu, dẫn đến lỗi lan truyền. •

Phân loại Glitch: Có hai loại glitch chính:

o Positive Glitch: Xung tăng đột ngột (từ 0 lên 1 rồi trở lại 0). o Negative Glitch:

Xung giảm đột ngột (từ 1 xuống 0 rồi trở lại 1). Trong ví dụ của hội thoại, glitch là

một "dip" (giảm đột ngột), thuộc loại negative glitch. lOMoAR cPSD| 58778885

o Hiểu biết này giúp bạn nhận ra rằng glitch có thể xuất hiện dưới nhiều hình thức

tùy thuộc vào tín hiệu aggressor. •

Giải pháp phòng ngừa ngoài shielding: Ngoài kỹ thuật che chắn (shielding) được đề cập

sau này, các biện pháp khác như tăng khoảng cách giữa các đường dẫn, sử dụng bộ lọc tín

hiệu, hoặc thiết kế lại bố cục (layout) để giảm ghép điện dung cũng có thể giảm thiểu glitch.

Điều này bổ sung cho ý tưởng trong hội thoại rằng shielding chỉ là một phần của giải pháp

toàn diện (04:01.900 - 04:05.770). •

Tác động trong ứng dụng thực tế: Trong các chip hiện đại (như CPU hoặc chip tự lái),

một glitch nhỏ có thể gây ra lỗi phần mềm hoặc phần cứng nghiêm trọng, như mất dữ liệu

cảm biến trong xe tự hành. Hội thoại nhấn mạnh hậu quả với chip ô tô, nhưng tác động này

còn mở rộng đến nhiều lĩnh vực khác như y tế (thiết bị cấy ghép) hoặc hàng không.

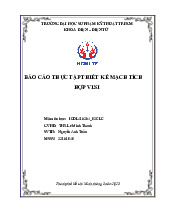

3. Hiện tượng Crosstalk và độ lệch (Skew)

Định nghĩa và cơ chế của Crosstalk:

o Crosstalk được giới thiệu như một hiện tượng xảy ra khi có sự tương tác không

mong muốn giữa các đường dẫn trong mạch do ghép điện dung (coupling

capacitance) (00:59.550 - 01:04.620: "Because because we have been locked in

such a fashion that we have zero skew but accidentally if there is something that is

there is a phenomenon there's a phenomenon of crosstalk that can happen").

o Hội thoại giải thích rằng nếu đường dẫn đồng hồ (clock net) bị ảnh hưởng bởi một

đường dẫn khác (aggressor) thông qua tụ ghép, nó có thể gây ra nhiễu, dẫn đến các

vấn đề như glitch hoặc thay đổi độ trễ (01:06.690 - 01:12.480).

Tác động của Crosstalk đến độ trễ (Delay):

o Crosstalk làm thay đổi độ trễ của tín hiệu. Hội thoại lấy ví dụ về một đường dẫn

đồng hồ vốn có độ trễ ban đầu là D, nhưng sau khi bị ảnh hưởng bởi crosstalk, độ

trễ tăng lên thành D+Δ (06:19.060 - 07:11.200). Điều này xảy ra khi tín hiệu

aggressor chuyển đổi trạng thái (ví dụ: từ logic 0 sang logic 1), tạo ra một "bump"

(sự nhô lên) trên tín hiệu victim (06:45.160 - 06:58.220). o Sự thay đổi này có thể

làm sai lệch thời gian hoạt động của các flip-flop hoặc bộ nhớ, dẫn đến lỗi định thời.

Hiện tượng Skew (độ lệch):

o Skew được định nghĩa là sự khác biệt về độ trễ (latency) giữa các tín hiệu đồng hồ

tại các điểm khác nhau (05:48.900 - 05:52.330: "So by zero skill we mean that that

said the latency of this particular latency from this clock port this to this point of the flop is a lot").

o Hội thoại giải thích rằng ban đầu, thiết kế cố gắng duy trì skew bằng 0 (độ trễ đồng

đều giữa các flip-flop). Tuy nhiên, do crosstalk, độ trễ của một đường dẫn có thể

tăng thêm Δ, dẫn đến skew có giá trị hữu hạn (07:29.830 - 07:34.200: "So now your

school becomes Elvan pleasantly so that it's normal to zero"). lOMoAR cPSD| 58778885

o Ví dụ cụ thể: Nếu L1=L2+Δ, thì skew = Δ (hình ảnh thứ ba minh họa điều này với

công thức SKEW=L1−(L2+Δ)=Δ.

Hậu quả của Skew:

o Skew không được kiểm soát có thể làm mất đồng bộ giữa các flip-flop, dẫn đến lỗi

trong chu kỳ đồng hồ. Hội thoại gợi ý rằng nếu skew tăng (ví dụ: từ 0 lên vài

picosecond trong một chip 4 triệu cổng), nó có thể ảnh hưởng nghiêm trọng đến

hiệu suất hệ thống (07:40.210 - 07:47.510). •

Cơ chế vật lý chi tiết của Crosstalk:

o Crosstalk xảy ra do hiệu ứng ghép điện dung (capacitive coupling) và ghép từ cảm

(inductive coupling) giữa các đường dẫn kim loại trên chip. Trong bối cảnh hội

thoại, tụ ghép Cm C_m Cm (hình ảnh thứ hai) là yếu tố chính, đặc biệt khi khoảng

cách giữa các đường dẫn nhỏ (như trong công nghệ sản xuất tiên tiến dưới 10nm).

o Khi tín hiệu aggressor chuyển đổi trạng thái nhanh, điện trường thay đổi đột ngột,

gây ra nhiễu trên tín hiệu victim. Điều này giải thích tại sao crosstalk trở thành vấn

đề lớn trong các thiết kế mật độ cao. • Các loại Crosstalk:

o Crosstalk tăng cường (constructive crosstalk): Khi tín hiệu aggressor và victim

chuyển đổi cùng hướng (cùng tăng hoặc cùng giảm), độ trễ giảm. o Crosstalk

giảm cường (destructive crosstalk): Khi tín hiệu chuyển đổi ngược hướng (một

tăng, một giảm), độ trễ tăng, như được mô tả trong ví dụ của hội thoại (06:38.840 -

06:50.740). Hiểu loại crosstalk giúp bạn dự đoán tác động chính xác hơn. lOMoAR cPSD| 58778885 •

Skew trong bối cảnh thực tế:

o Skew không chỉ do crosstalk mà còn do độ dài đường dẫn khác nhau, sự khác biệt

về nhiệt độ, hoặc sai số trong quá trình sản xuất. Hội thoại tập trung vào crosstalk,

nhưng các yếu tố khác cũng cần được xem xét để giảm thiểu skew hiệu quả.

o Trong một chip phức tạp, skew có thể dao động từ vài picosecond đến hàng chục

picosecond, đòi hỏi phân tích định thời chính xác (như được đề cập ở hình ảnh thứ năm). •

Giải pháp bổ sung ngoài shielding:

o Ngoài kỹ thuật che chắn (shielding) được đề cập sau này, các phương pháp như tối

ưu hóa bố cục (routing optimization), sử dụng bộ đệm đồng bộ (clock buffers), hoặc

điều chỉnh tần số đồng hồ cũng có thể giảm crosstalk và skew. Điều này bổ sung

cho ý tưởng trong hội thoại rằng shielding là một kỹ thuật quan trọng nhưng không

phải là giải pháp duy nhất (07:52.750 - 08:01.890). •

Tác động đến hiệu suất và độ tin cậy:

o Trong các ứng dụng như chip xử lý tín hiệu hoặc trí tuệ nhân tạo, skew và crosstalk

không kiểm soát được có thể làm giảm tốc độ xử lý hoặc gây lỗi dự đoán. Hội thoại

nhấn mạnh hậu quả với chip ô tô, nhưng tác động này còn mở rộng đến các lĩnh

vực yêu cầu độ tin cậy cao như viễn thông hoặc y tế.

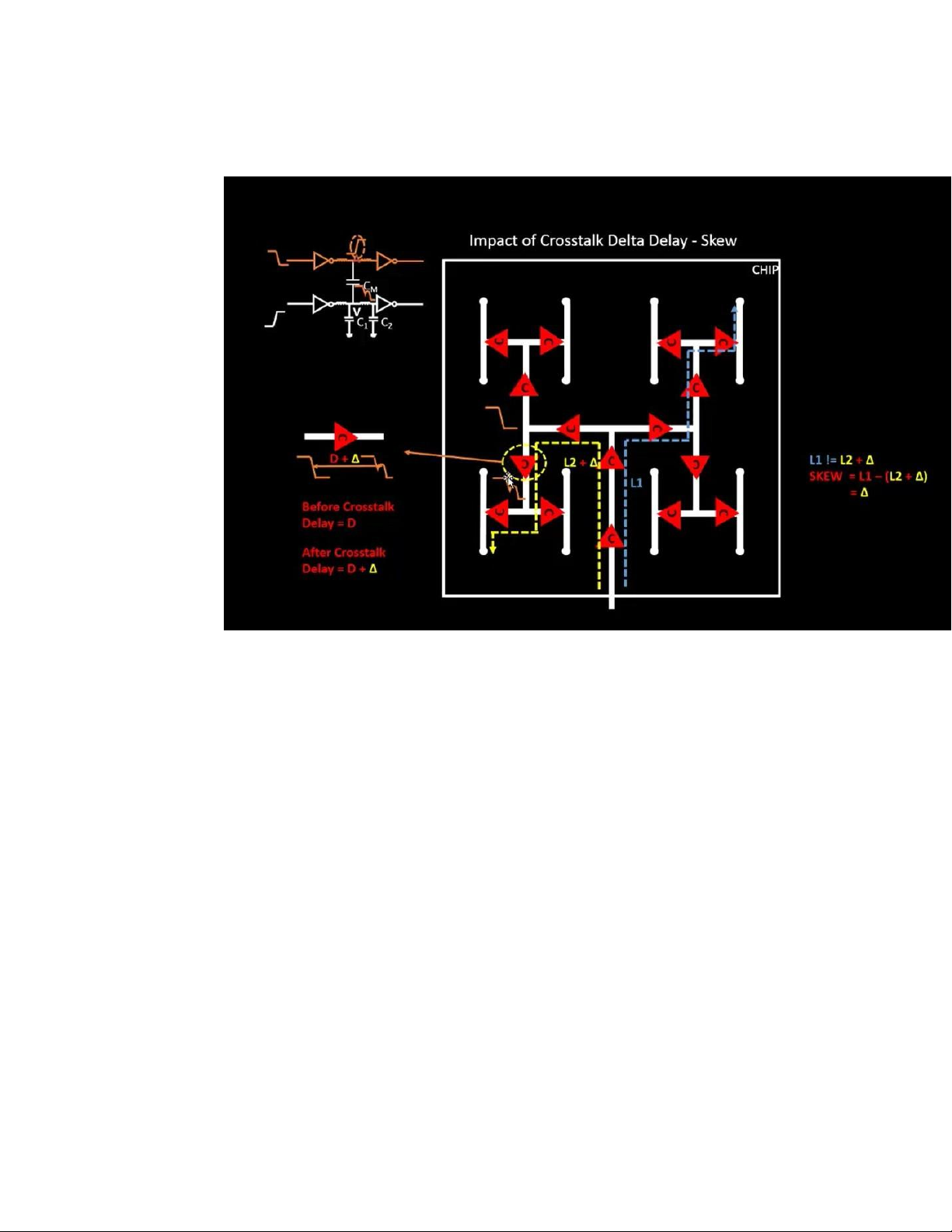

4. Kỹ thuật Shielding (Che chắn) cho tín hiệu đồng hồ

Mục đích của kỹ thuật Shielding:

o Kỹ thuật che chắn được giới thiệu như một phương pháp để bảo vệ các đường dẫn

đồng hồ (clock nets) khỏi ảnh hưởng của các tín hiệu bên ngoài, đặc biệt là hiện

tượng crosstalk (01:25.250 - 01:30.810: "But before that let me give you a brief

brief discussion on Glocke next shooting"). Điều này nhằm đảm bảo tín hiệu đồng

hồ không bị nhiễu, giữ cho độ lệch (skew) và glitch ở mức tối thiểu. o Hội thoại

nhấn mạnh rằng đồng hồ là một "critical net" (đường dẫn quan trọng), nên cần được

bảo vệ như một "ngôi nhà" (01:43.620 - 01:45.560: "It's like we had an absolute

ding this clock needs to be protected from the outside world. It's like a house for the clock").

Cách thực hiện Shielding:

o Che chắn được thực hiện bằng cách đặt các đường dẫn bổ sung (shielding wires)

xung quanh đường dẫn đồng hồ. Những đường dẫn này được kết nối với nguồn

(VDD) hoặc đất (GND) để tạo ra một rào cản (01:37.800 - 01:38.880: "Dig this part

of the clock and shield something like this by shielding what we do with this Glock

next from the outside wall"). o Ý tưởng là ngăn chặn sự tương tác điện dung giữa

tín hiệu đồng hồ (victim) và các tín hiệu khác (aggressor) (04:36.530 - 04:41.930:

"So yes this is the technique We've shielded basically by shielding we're breaking

the coupling capacitance between the actors and the victim").

Cơ chế hoạt động: lOMoAR cPSD| 58778885

o Các đường dẫn che chắn không chuyển đổi trạng thái (switch), do đó chúng không

tạo ra nhiễu bổ sung. Điều này giúp giảm thiểu hiệu ứng ghép điện dung từ các tín

hiệu lân cận (04:50.540 - 05:01.800: "The shields don't switch and if the shields

don't switch that is a very high possibility that the victim will switch").

o Hội thoại giải thích rằng nếu không có che chắn, hoạt động chuyển đổi của các tín

hiệu lân cận có thể gây ra glitch hoặc thay đổi độ trễ, ảnh hưởng đến tín hiệu đồng hồ.

Lợi ích và giới hạn:

o Lợi ích: Che chắn giúp bảo vệ tín hiệu đồng hồ khỏi crosstalk, giảm glitch và skew,

từ đó cải thiện độ tin cậy của hệ thống (04:07.050 - 04:11.480: "So shielding is one

of the techniques that will actually neglected or protect this particular victim").

o Giới hạn: Không thể áp dụng che chắn cho tất cả các đường dẫn do hạn chế về tài

nguyên và không gian trên chip. Hội thoại gợi ý rằng chỉ các đường dẫn quan trọng

như clock nets và một số data nets được ưu tiên (08:36.940 - 08:50.820: "But if

they really don't know which are very critical it is it is it becomes necessary to see

them but it's not always possible to shield all of the all of the next the design because

that might just increase the eroding resources"). •

Cấu trúc vật lý của Shielding:

o Trong thực tế, shielding thường được thực hiện bằng cách đặt các đường dẫn kim

loại (metal lines) ở các lớp khác nhau trên chip, ví dụ: một đường dẫn đồng hồ được

bao quanh bởi hai đường dẫn nối đất (GND) hoặc nguồn (VDD) ở hai bên. Điều

này tạo ra một "hàng rào điện" giảm thiểu ghép điện dung, như được minh họa

trong hình ảnh đầu tiên của bạn. lOMoAR cPSD| 58778885 • Các loại Shielding:

o Single-sided shielding: Chỉ che chắn một bên của đường dẫn đồng hồ, thường được

sử dụng khi không gian hạn chế. o Double-sided shielding: Che chắn cả hai bên,

cung cấp bảo vệ tốt hơn nhưng đòi hỏi nhiều tài nguyên hơn, phù hợp với các clock

nets quan trọng. o Hội thoại tập trung vào double-sided shielding (01:37.800 -

01:43.620), nhưng bạn có thể cân nhắc loại phù hợp tùy thuộc vào thiết kế. •

Tác động đến hiệu suất:

o Mặc dù shielding giúp giảm nhiễu, nó cũng làm tăng điện dung tổng cộng trên chip,

có thể làm chậm tín hiệu hoặc tăng tiêu thụ điện. Điều này giải thích tại sao hội

thoại đề cập đến việc không thể che chắn tất cả các đường dẫn (08:50.820 - 08:52.300). •

Kỹ thuật bổ sung:

o Ngoài shielding, các phương pháp như điều chỉnh khoảng cách giữa các đường dẫn,

sử dụng vật liệu cách điện tốt hơn (low-k dielectrics), hoặc tối ưu hóa tần số đồng

hồ cũng có thể giảm crosstalk. Điều này bổ sung cho ý tưởng trong hội thoại rằng

shielding là một phần của chiến lược tổng thể (08:01.900 - 08:05.770). •

Ứng dụng thực tế:

o Trong các chip hiện đại như CPU hoặc chip AI, shielding được sử dụng rộng rãi cho

các clock nets chính để đảm bảo đồng bộ trong hàng triệu cổng logic. Hội thoại gợi

ý ứng dụng trong chip ô tô (03:35.480 - 03:42.080), nhưng kỹ thuật này còn quan

trọng trong các lĩnh vực như viễn thông hoặc thiết bị y tế, nơi độ tin cậy là tối thượng. lOMoAR cPSD| 58778885 Kết luận

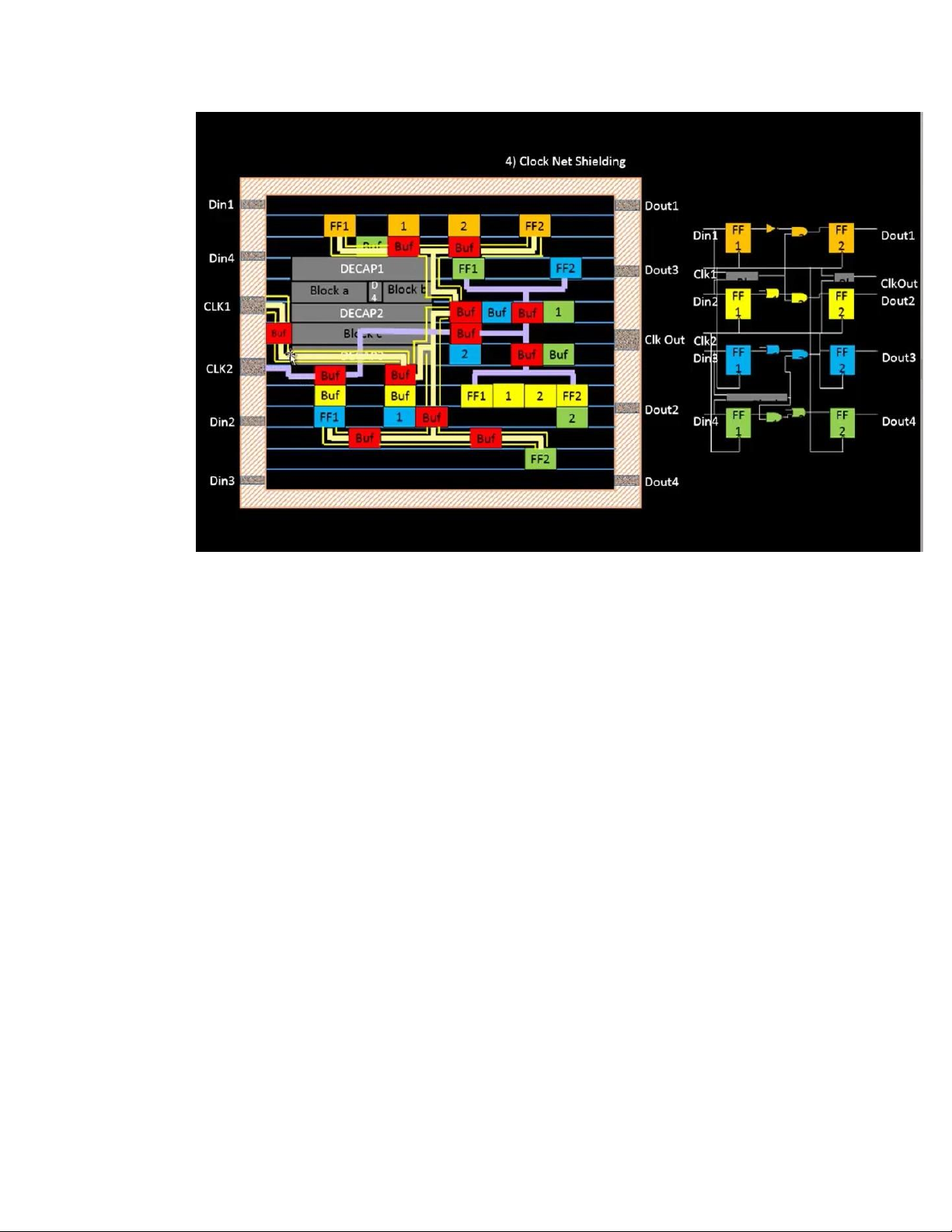

5. Phân tích định thời (Timing Analysis) với tín hiệu đồng hồ thực tế

Mục đích của Phân tích định thời với tín hiệu thực tế:

o Sau khi áp dụng kỹ thuật che chắn (shielding) cho các đường dẫn đồng hồ, cần thực

hiện lại phân tích định thời để đảm bảo thiết kế hoạt động chính xác với tín hiệu

đồng hồ thực tế (09:04.950 - 09:07.630: "So after we have done the diclofenac

shilling the next the next step is to do again a damning analysis with the real plugs

because now we have the clock next"). o Hội thoại nhấn mạnh rằng việc này là một

phần quan trọng trong quy trình thiết kế lý tưởng (flow) để xác minh tính toàn vẹn

của hệ thống (09:16.140 -

09:21.640: "We'll be doing a timing analysis with real clocks and that's the part of

the floor. That's the part of an ideal flow").

Sử dụng tín hiệu đồng hồ thực tế:

o Phân tích được thực hiện với các tín hiệu đồng hồ thực tế (real clocks) thay vì tín

hiệu lý tưởng, vì tín hiệu thực tế bao gồm các yếu tố như độ trễ dây dẫn, nhiễu, và

sai số (09:07.740 - 09:14.280: "And now we have the clock and the children. So

what is the point where we have to do with real plugs. Dorothy the pots are not all

good"). o Điều này phản ánh rằng sau khi che chắn, các đặc tính thực tế của đồng

hồ (bao gồm độ lệch và độ trễ bổ sung) cần được đánh giá lại.

Quy trình và tiêu chí định thời:

o Hội thoại gợi ý rằng phân tích định thời liên quan đến việc xác định các đường dẫn

quan trọng (critical paths) và đảm bảo chúng đáp ứng các yêu cầu thời gian

(09:22.170 - 09:26.070: "So what we'll do is we'll talk about this particular slide in

the next video since I'm older than the lot of them").

o Hình ảnh thứ năm cung cấp một ví dụ cụ thể với công thức định thời:

(Θ+Δ1)<(T+Δ2)−S−SU, trong đó:

Θ : Độ trễ dữ liệu.

Δ1,Δ2: Độ trễ bổ sung do dây dẫn thực tế và bộ đệm. T: Chu kỳ đồng hồ.

S: Độ lệch an toàn (setup margin).

SU: Độ không chắc chắn (uncertainty, được giả định là 90ps trong hình). lOMoAR cPSD| 58778885

o Mục tiêu là đảm bảo rằng tổng độ trễ dữ liệu nhỏ hơn thời gian chu kỳ đồng hồ trừ

đi các yếu tố an toàn và không chắc chắn.

Tầm quan trọng của bước này:

o Phân tích định thời với tín hiệu thực tế giúp phát hiện các lỗi tiềm ẩn (như skew

hoặc timing violation) sau khi áp dụng các kỹ thuật như shielding. Đây là bước cuối

cùng để xác nhận rằng thiết kế đáp ứng yêu cầu hiệu suất (09:14.280 - 09:16.040:

"Dorothy the pots are not all good"). •

Sự khác biệt giữa tín hiệu lý tưởng và thực tế:

o Tín hiệu đồng hồ lý tưởng giả định độ trễ không đổi và không có nhiễu, trong khi

tín hiệu thực tế bao gồm các yếu tố như độ trễ dây dẫn (RC delay), nhiễu crosstalk,

và biến thiên do nhiệt độ hoặc điện áp. Hội thoại đề cập đến "real wire RC delay"

(hình ảnh thứ năm), nhấn mạnh tầm quan trọng của việc mô phỏng thực tế. •

Các loại phân tích định thời:

o Static Timing Analysis (STA): Kiểm tra tất cả các đường dẫn mà không cần mô

phỏng tín hiệu, thường được sử dụng sau khi shielding để xác định các vi phạm định thời.

o Dynamic Timing Analysis: Sử dụng mô phỏng với tín hiệu thực tế, phù hợp để

đánh giá ảnh hưởng của nhiễu hoặc skew động. Hội thoại ám chỉ STA khi đề cập

đến "timing analysis with real clocks". •

Các tham số bổ sung: lOMoAR cPSD| 58778885

o Ngoài S và SU, các yếu tố như hold time (thời gian giữ) và clock uncertainty cũng

cần được xem xét. Ví dụ, nếu SU=90ps (như trong hình), nó phản ánh sai số do

jitter hoặc nhiễu, đòi hỏi thiết kế phải có biên độ an toàn lớn hơn. •

Công cụ và quy trình thực tế:

o Trong thực tế, các công cụ như Synopsys PrimeTime hoặc Cadence Tempus được sử

dụng để thực hiện STA sau khi hoàn thành bố cục (post-layout). Hội thoại gợi ý

rằng đây là bước tiếp theo sau shielding, nhưng không đi sâu vào công cụ, vì vậy

bạn có thể khám phá thêm để áp dụng. •

Tác động đến thiết kế:

o Nếu phân tích định thời phát hiện vi phạm (timing violation), thiết kế có thể cần điều

chỉnh, như thêm bộ đệm (buffer), giảm độ dài đường dẫn, hoặc tối ưu hóa lại

shielding. Điều này bổ sung cho ý tưởng trong hội thoại rằng quy trình là "ideal

flow" (09:20.040 - 09:21.640), đòi hỏi lặp lại nếu cần. •

Ứng dụng thực tế:

o Trong các chip như CPU hoặc chip IoT, phân tích định thời với tín hiệu thực tế đảm

bảo rằng hệ thống hoạt động ổn định ở tần số cao (ví dụ: vài GHz). Sai sót ở bước

này có thể dẫn đến lỗi hệ thống, như được ám chỉ với chip ô tô trong hội thoại trước.

6. Kết luận và ứng dụng •

Che chắn tín hiệu đồng hồ là một kỹ thuật quan trọng để bảo vệ mạch khỏi các lỗi do

crosstalk gây ra, đặc biệt trong các thiết kế đòi hỏi độ tin cậy cao. •

Tuy nhiên, không thể che chắn tất cả các đường dẫn do hạn chế về tài nguyên, vì vậy cần

ưu tiên bảo vệ các đường dẫn đồng hồ và các đường dẫn dữ liệu quan trọng. •

Sau khi áp dụng che chắn, cần thực hiện lại phân tích định thời với tín hiệu đồng hồ thực

tế để đảm bảo thiết kế hoạt động chính xác.

Bài học nhấn mạnh rằng hiểu và kiểm soát glitch, skew, và crosstalk là rất cần thiết trong thiết kế

VLSI, và kỹ thuật shielding là một giải pháp hiệu quả để cải thiện độ tin cậy của hệ thống. Nếu

bạn muốn tìm hiểu thêm, các video về crosstalk được đề cập trong hội thoại có thể cung cấp chi tiết bổ sung.