Preview text:

lOMoAR cPSD| 58737056

BÀI THỰC HÀNH KỸ THUẬT SỐ

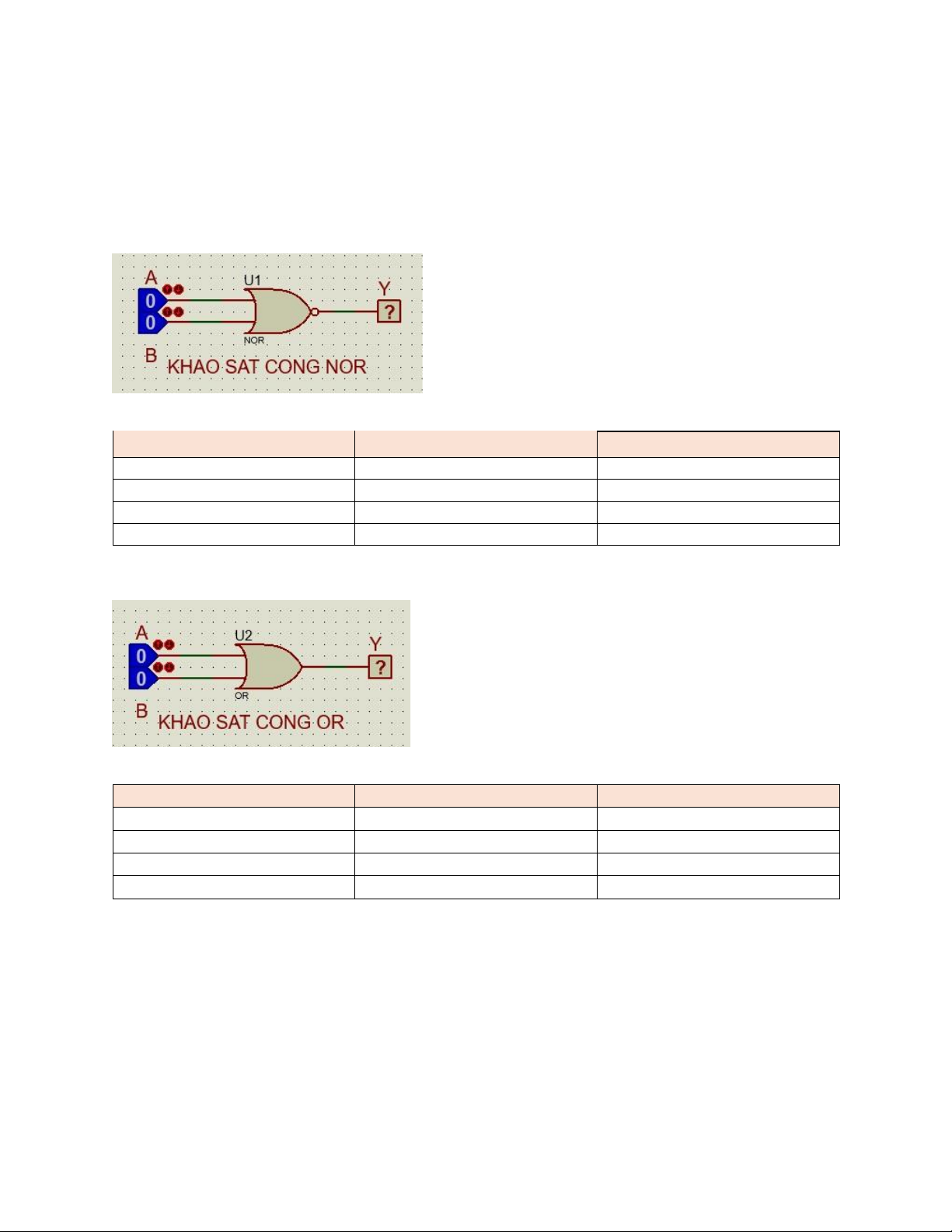

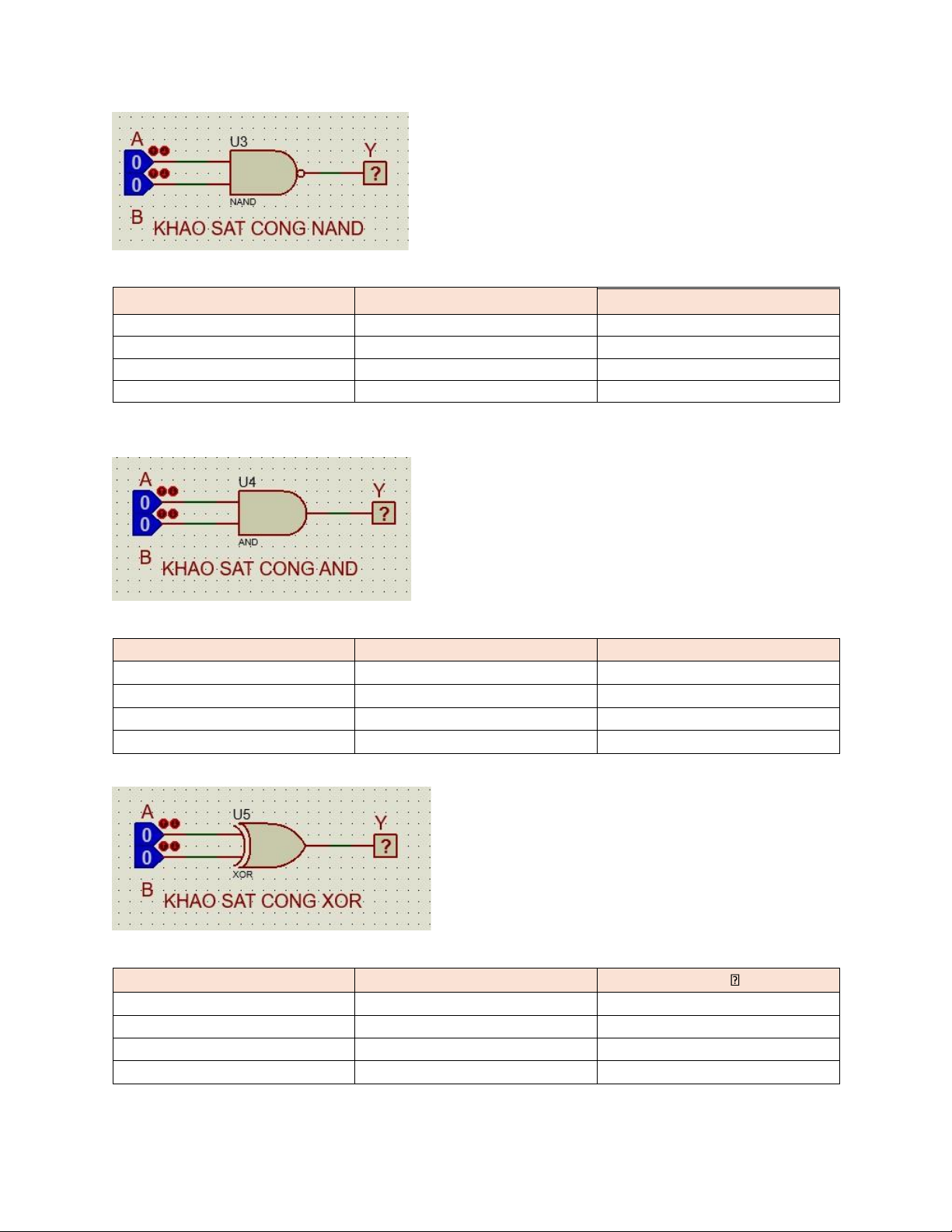

Bài 1: Khảo sát cổng logic

a. Cổng NOR * Sơ đồ * Bảng trạng thái A B Y = A+B 0 0 1 0 1 0 1 0 0 1 1 0

* Nhận xét: Ngõ ra Y bằng 1 khi tất cả ngõ vào bằng 0. b. Cổng OR * Bảng trạng thái A B Y = A + B 0 0 0 0 1 1 1 0 1 1 1 1

* Nhận xét: Ngõ ra Y bằng 0 khi tất cả ngõ vào bằng 0. c. Cổng NAND lOMoAR cPSD| 58737056 * Bảng trạng thái A B Y = A.B 0 0 1 0 1 1 1 0 1 1 1 0

* Nhận xét: Ngõ ra Y bằng 0 khi tất cả ngõ vào bằng 1. d. Cổng AND * Bảng trạng thái A B Y = A . B 0 0 0 0 1 0 1 0 0 1 1 1

* Nhận xét: Ngõ ra Y bằng 1 khi tất cả ngõ vào bằng 1. e. Cổng XOR * Bảng trạng thái A B Y = A B 0 0 0 0 1 1 1 0 1 1 1 0 lOMoAR cPSD| 58737056

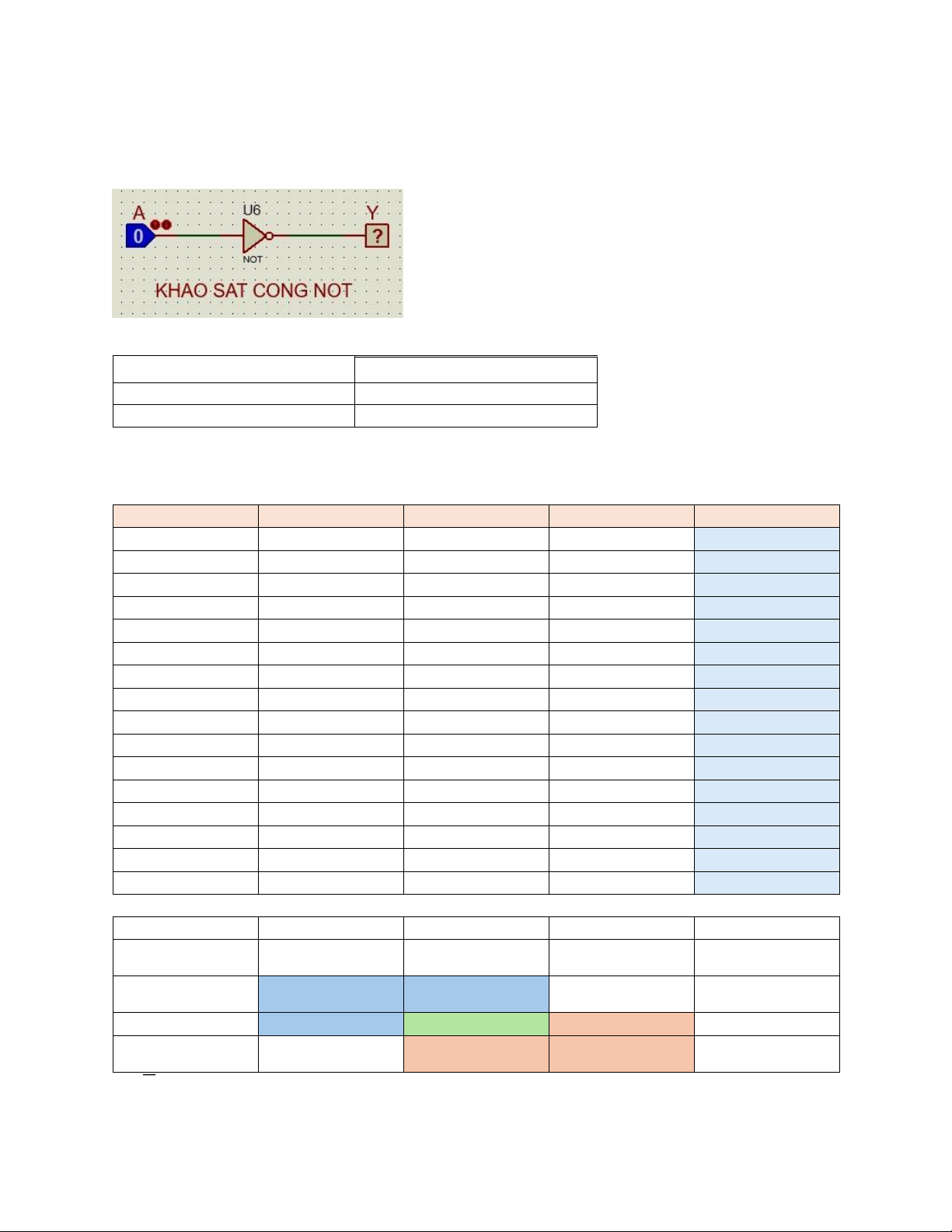

* Nhận xét: Ngõ ra Y bằng 1 khi chỉ có đúng 1 ngõ vào bằng 1 và 1 ngõ vào bằng 0. f. Cổng NOT * Bảng trạng thái A Y = A 0 1 1 0

* Nhận xét: Ngõ ra bằng 1 khi ngõ vào bằng 0 và ngược lại.

Bài 2: Cho hàm: F(A,B,C,D) = ∑(1,3,5,6,7,15) + d(4,9,11,12,14) với A là MSB; D là LSB.

a) Biểu diễn hàm F dưới dạng bảng sự thật. A B C D F 0 0 0 0 0 0 0 0 1 1 0 0 1 0 0 0 0 1 1 1 0 1 0 0 X 0 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 0 0 0 0 1 0 0 1 X 1 0 1 0 0 1 0 1 1 X 1 1 0 0 X 1 1 0 1 0 1 1 1 0 X 1 1 1 1 1

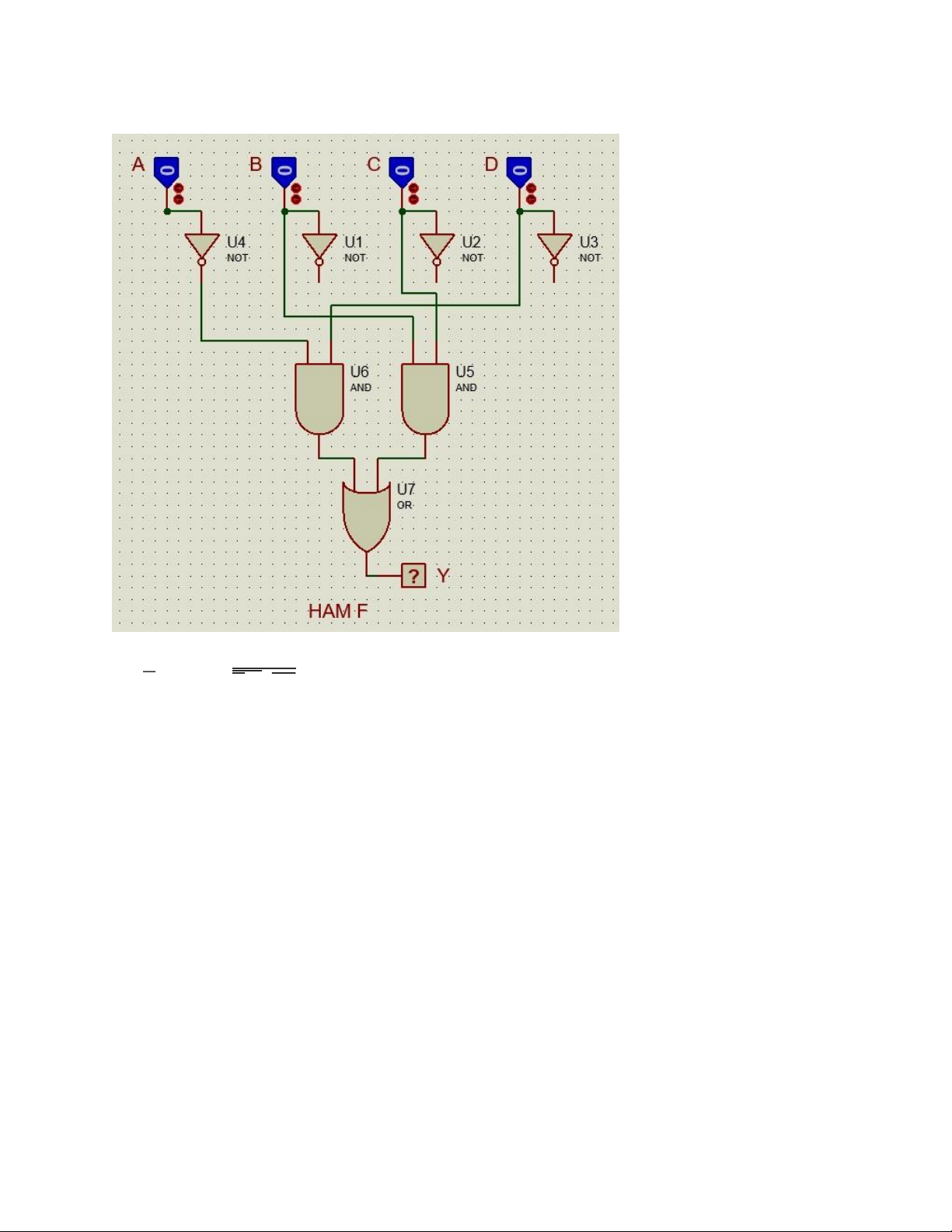

b) Thực hiện hàm F bằng bìa K và rút gọn, vẽ mạch. CD \ AB 00 01 11 10 00 X X 01 1 1 X 11 1 1 1 X 10 1 X F = AD+BC lOMoAR cPSD| 58737056 * Sơ đồ:

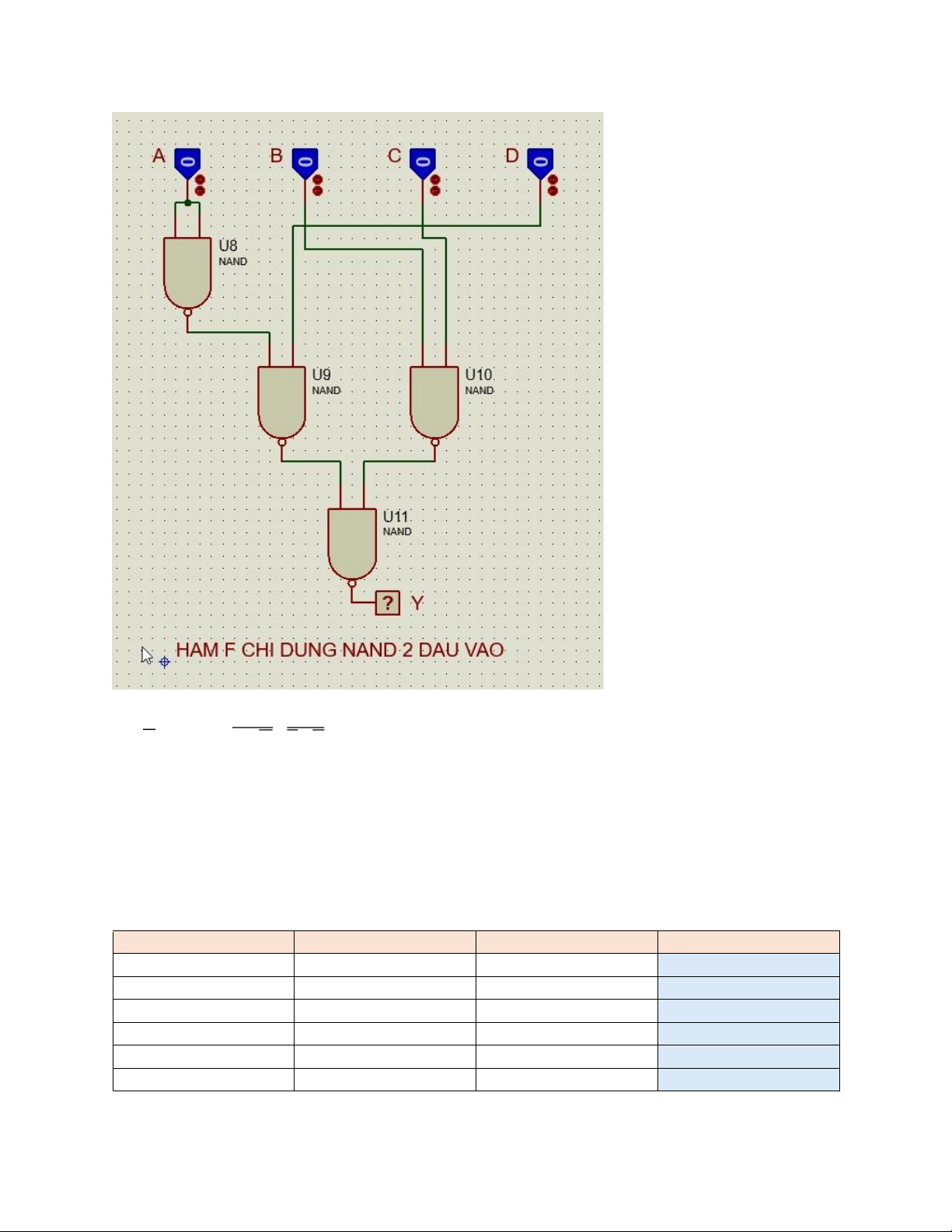

c) Thực hiện hàm F tối ưu bằng một loại cổng NAND 2 ngõ vào, vẽ mạch.

F = AD+BC = A D.BC * Sơ đồ: lOMoAR cPSD| 58737056

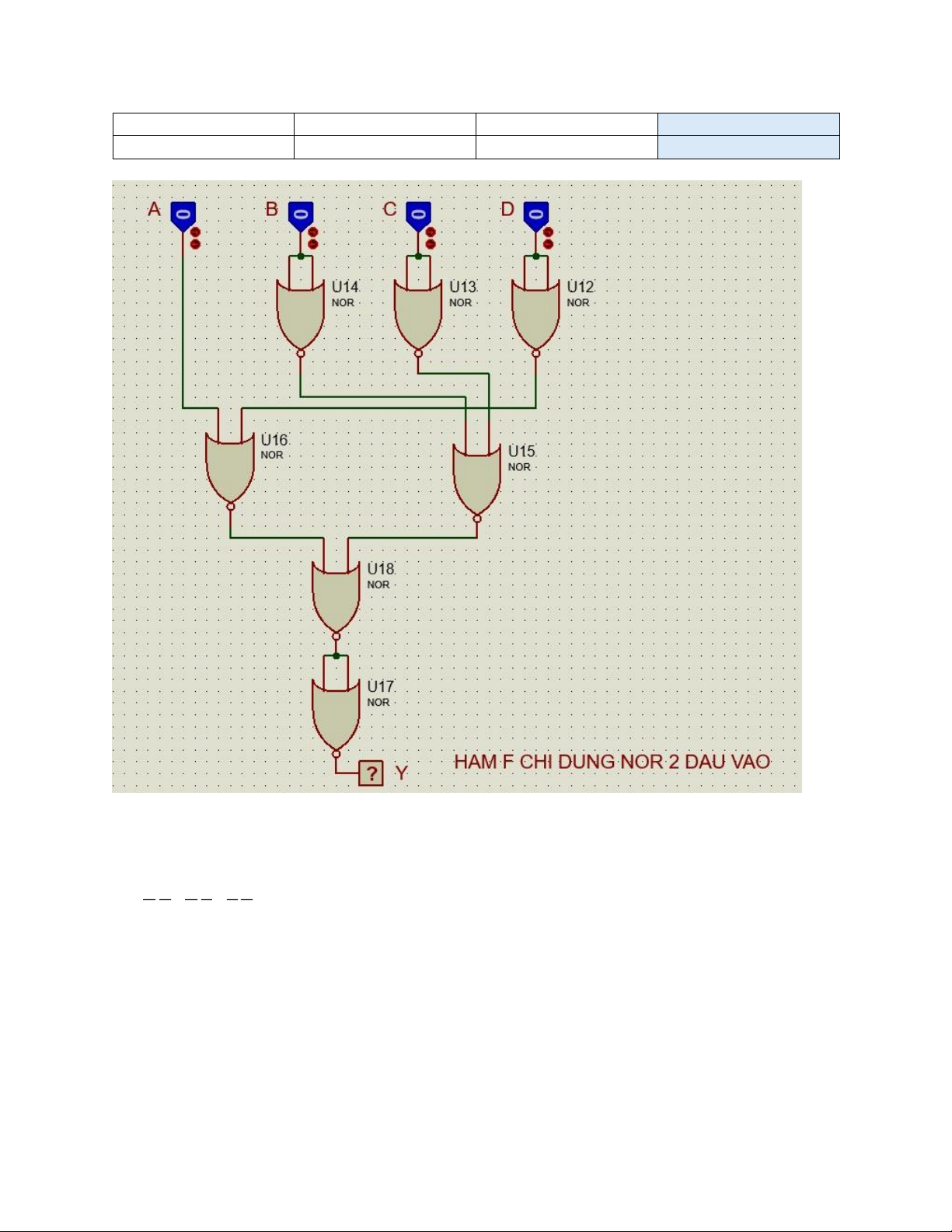

d) Thực hiện hàm F tối ưu bằng một loại cổng NOR 2 ngõ vào, vẽ mạch

F = AD+BC = A+D+B+C A B C Y 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 0 1 0 0 1 1 0 1 0 lOMoAR cPSD| 58737056 1 1 0 0 1 1 1 0 * Sơ đồ:

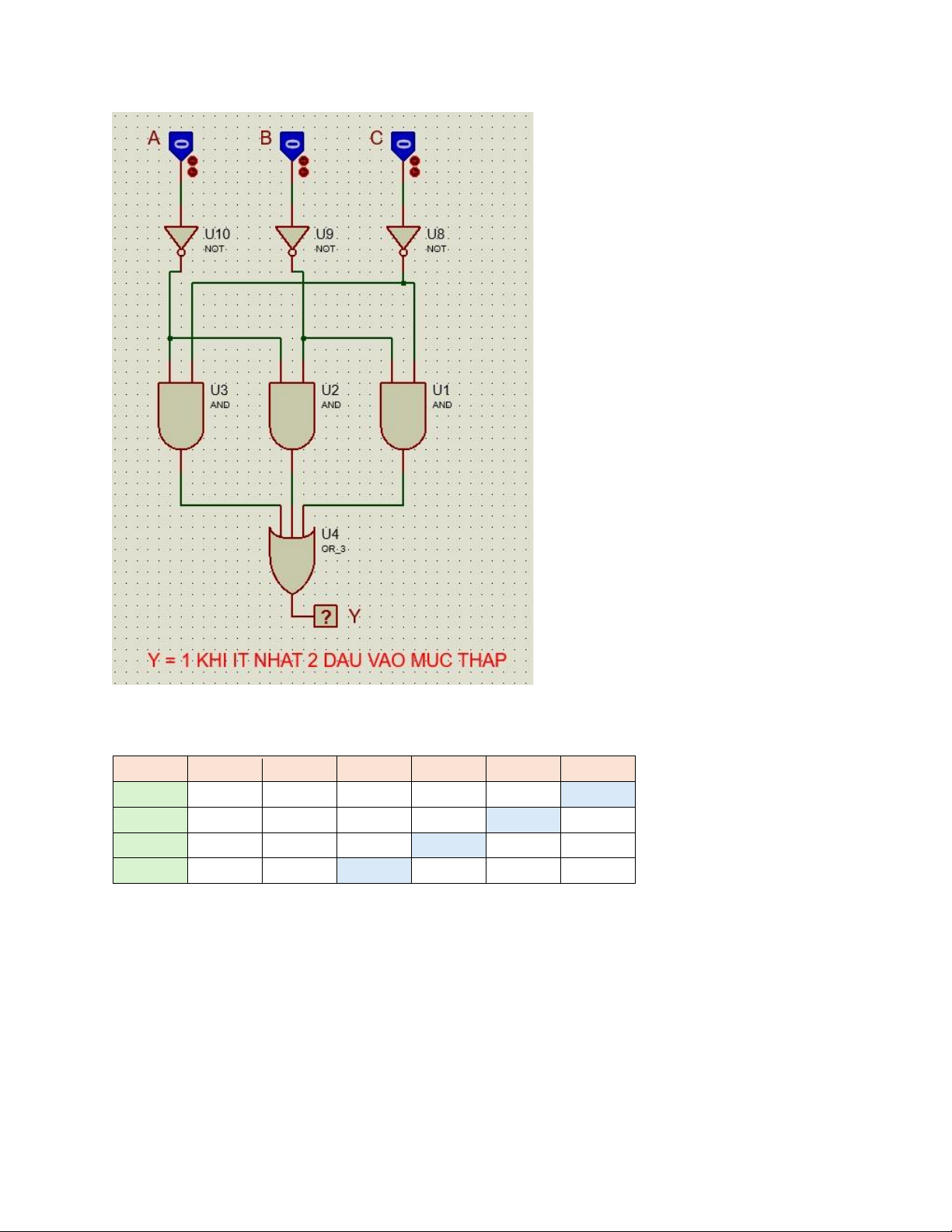

Bài 3: Thiết kế mạch tổ hợp với ngõ ra Y bằng “1” khi đa số ngõ vào A, B, C ở mức thấp, các

trường hợp còn lại ngõ ra Y bằng “0”.

Khi có ít nhất 2 ngõ vào bằng 0, ngõ ra sẽ bằng 1.

F = AC+AB+BC * Sơ đồ: lOMoAR cPSD| 58737056

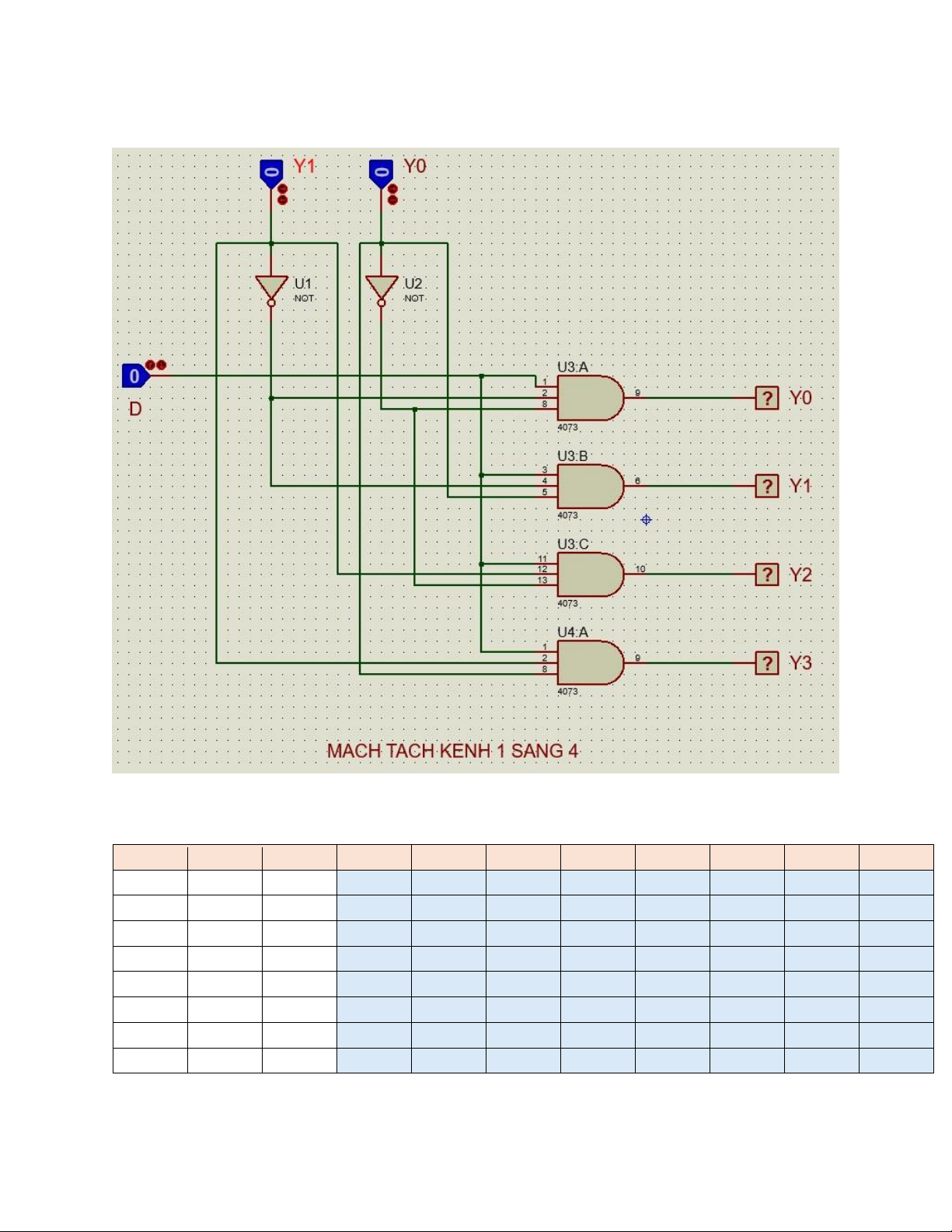

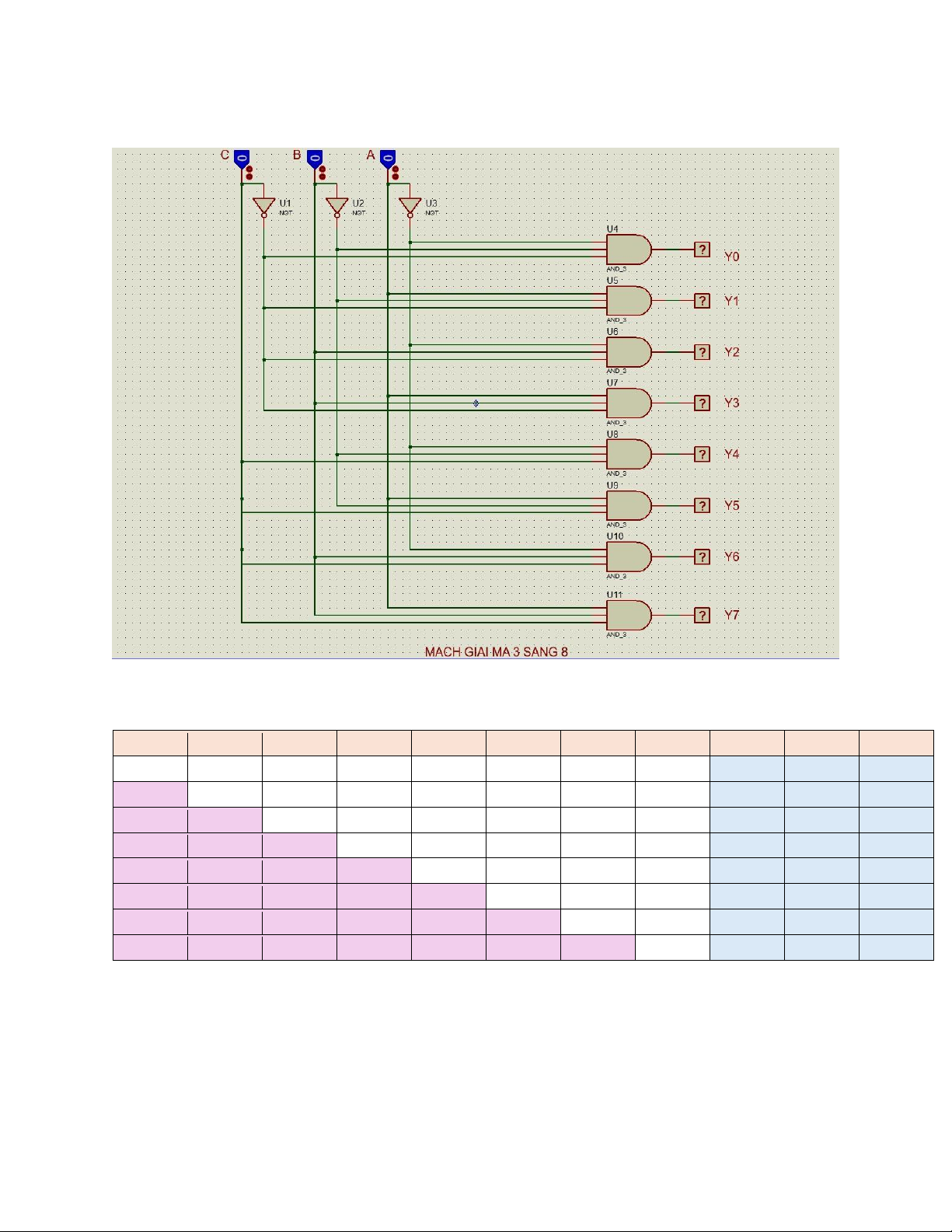

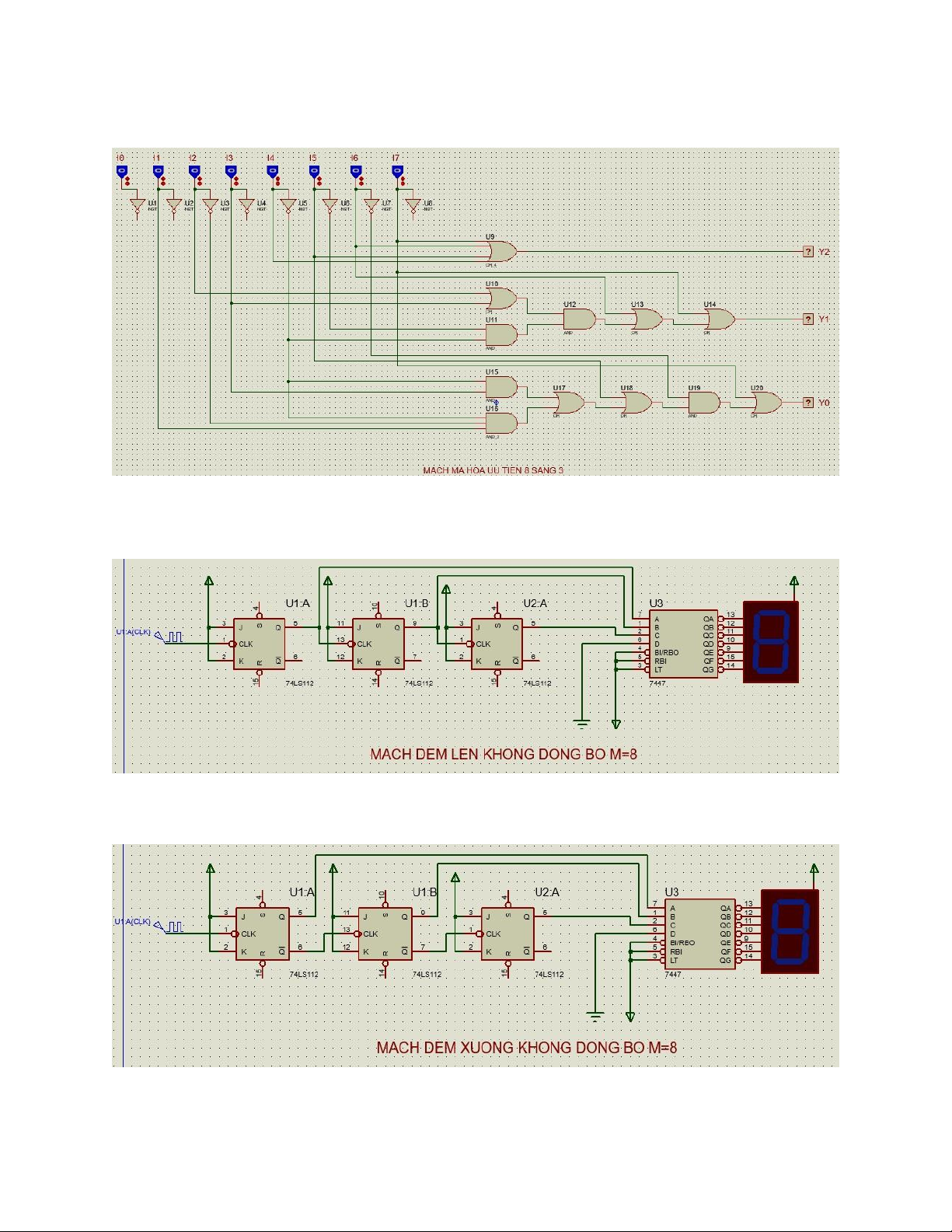

Bài 4: Thiết kế mạch tách kênh 1 sang 4. * Bảng sự thật mi S1 S0 Y3 Y2 Y1 Y0 m0 0 0 0 0 0 D m1 0 1 0 0 D 0 m2 1 0 0 D 0 0 m3 1 1 D 0 0 0 lOMoAR cPSD| 58737056 * Sơ đồ Bài 5: * Bảng sự thật C B A Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 0 0 0 1 0 0 0 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 1 1 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 1 0 1 0 0 0 0 0 1 0 0 1 1 0 0 0 0 0 0 0 1 0 1 1 1 0 0 0 0 0 0 0 1 lOMoAR cPSD| 58737056 * Sơ đồ Bài 6: * Bảng sự thật I0 I1 I2 I3 I4 I5 I6 I7 O2 O1 O0 1 0 0 0 0 0 0 0 0 0 0 X 1 0 0 0 0 0 0 0 0 1 X X 1 0 0 0 0 0 0 1 0 X X X 1 0 0 0 0 0 1 1 X X X X 1 0 0 0 1 0 0 X X X X X 1 0 0 1 0 1 X X X X X X 1 0 1 1 0 X X X X X X X 1 1 1 1 lOMoAR cPSD| 58737056 * Sơ đồ Bài 7: * Sơ đồ Bài 8: * Sơ đồ