Preview text:

lOMoARcPSD| 36991220

HỌC VIỆN CÔNG NGHỆ BƯU CHÍNH VIỄN THÔNG KHOA KỸ THUẬT ĐIỆN TỬ 1 ־־־־־ ־־־־־

BÁO CÁO BÀI TẬP LỚN MÔN THIẾT KẾ LOGIC SỐ Nhóm 17 MỤC LỤC

Câu 1: Viết chương trình điều khiển 8 led sang lan từ giữa sang hai bên. Viết testbench để

kiểm tra hoạt động của mạch.......................3

1. Sơ đồ khối.........................................................................................3

2. Nguyên lý..........................................................................................3

3. Quá trình thực hiện.........................................................................3

4. Kết quả..............................................................................................5

Câu 2:.........................................................................................................6 Phần 1: Phân

tích..................................................................................6

Phần 2: Code VHDL................................................................................9

Câu 3:.......................................................................................................13

Phần 1: Tính mã Gray kế tiếp............................................................13

Phần 2: Hiển thị sử dụng 2 led 7 đoạn Anode chung....................14

Phần 3: Code VHDL..............................................................................15

Câu 4: Viết chương trình mô tả bộ giải mã 3:8, có đầu vào điều khiển hoạt động ở mức thấp,

lối ra hiển thị trên LED đơn. Viết testbench để kiểm tra

hoạt động của mạch..................................................................................18

1. Sơ đồ khối.......................................................................................18 lOMoARcPSD| 36991220

2. Nguyên lý........................................................................................18

3. Quá trình thực hiện.......................................................................18

4. Kết quả............................................................................................22

Câu 5:.......................................................................................................22

Phần 1: Phân tích mạch logic tuần tự..............................................22

Phần 2: Code VHDL..............................................................................23

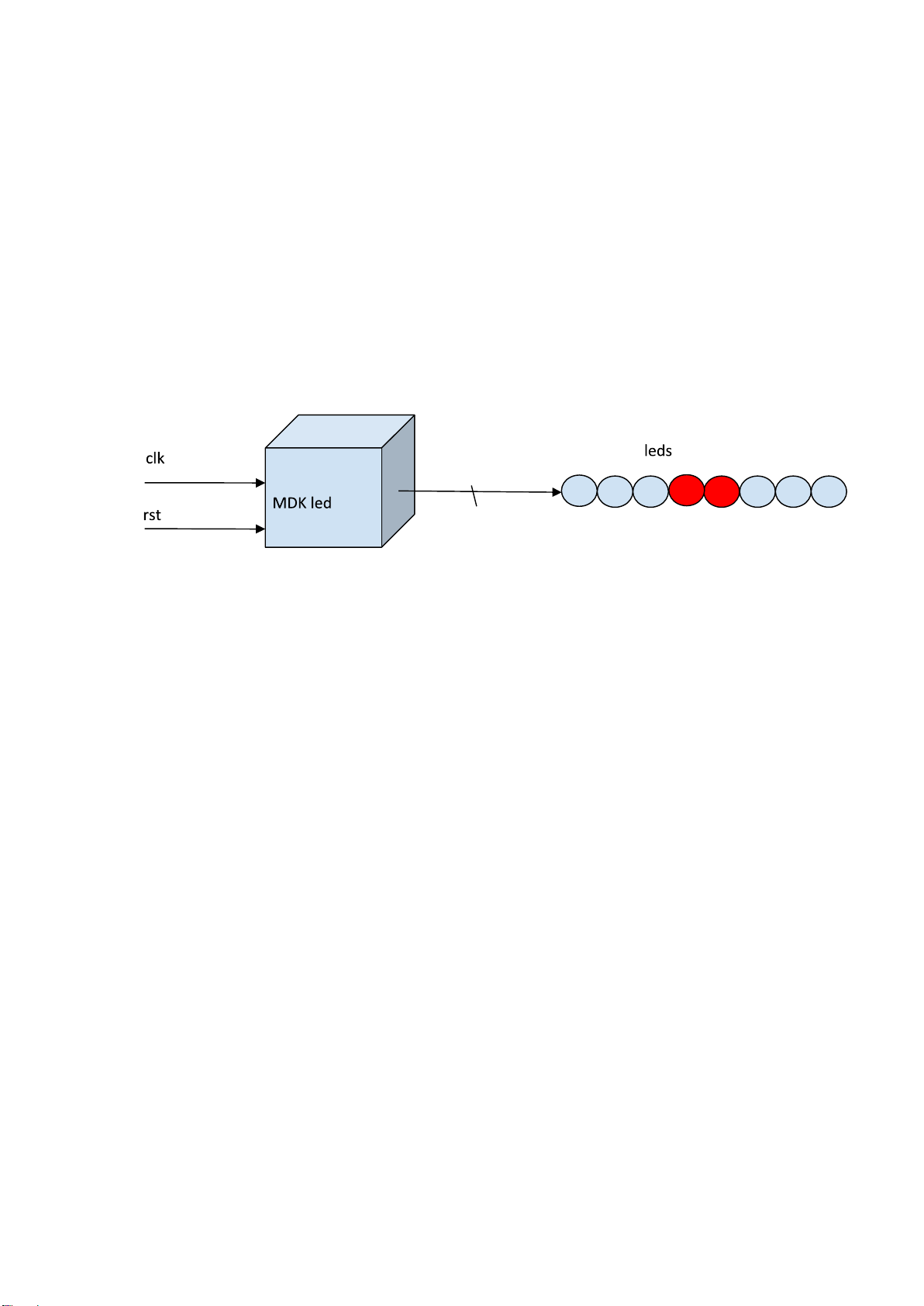

Câu 1: Viết chương trình điều khiển 8 led sang lan từ giữa sang hai bên. Viết

testbench để kiểm tra hoạt động của mạch 1. Sơ đồ khối 8 2. Nguyên lý

+ Mạch điều khiển LED được kích hoạt bởi tín hiệu clk (clock) và tín hiệu reset (đặt lại).

+ Khi tín hiệu reset được kích hoạt (ở mức logic '1'), mạch đặt lại trạng thái ban

đầu ( trang thái ban đầu 00000000 ). Các LED được tắt ( các LED đơn đấu anode chung ).

+ Khi tín hiệu reset không, mạch sẽ hoạt động như sau:

• Nếu trạng thái hiện tại là 00000000 thì trạng thái tiếp theo là 00011000 hai

LED ở giữa được bật, còn lại tất cả các LED khác đều tắt.

• Nếu trạng thái hiện tại là 00011000 thì trạng thái tiếp theo là 00111100 bốn LED ở giữa sáng.

• Nếu trạng thái hiện tại là 00111100 thì trạng thái tiếp theo là 01111110 sáu LED ở giữa sáng.

• Nếu trạng thái hiện tại là 01111110 thì trạng thái tiếp theo là 111111 tám LED sáng.

• Nếu trạng thái hiện tại là 11111111 thì trạng thái tiếp theo là 00000000 tám LED tắt.

3. Quá trình thực hiện - Main lOMoARcPSD| 36991220 library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity dk_8_led_test is

Port ( clock : in std_logic; reset : in std_logic;

led_out : out std_logic_vector(7 downto 0) ); end dk_8_led_test;

architecture Behavioral of dk_8_led_test is signal t :

std_logic_vector(7 downto 0); begin process( clock, reset) begin if (reset = '1') then t <= "00000000";

elsif ( clock'event and clock = '1' ) then case t is when "00000000" => t <=

"00011000"; when "00011000" => t <=

"00111100"; when "00111100" => t <=

"01111110"; when "01111110" => t <=

"11111111"; when "11111111" => t <=

"00000000"; when others => t <= "00000000"; end case; end if; end process; led_out <= t; end Behavioral; lOMoARcPSD| 36991220 - Testbench lOMoARcPSD| 36991220 library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity tb_dk_8_led is -- Port ( );

end tb_dk_8_led; architecture Behavioral of tb_dk_8_led is component dk_8_led_test Port ( clock : in std_logic; reset : in std_logic;

led_out : out std_logic_vector(7 downto 0) ); end component;

signal clock : std_logic := '0'; signal reset : std_logic;-- := '0';

signal led_out : std_logic_vector(7 downto 0); begin

u: dk_8_led_test port map(clock=>clock, reset=>reset, led_out=>led_out);

clock <= not clock after 0.5ns; -- reset <= not reset after 12.5ns; process begin

reset <= '0';-- after 12.5ns;

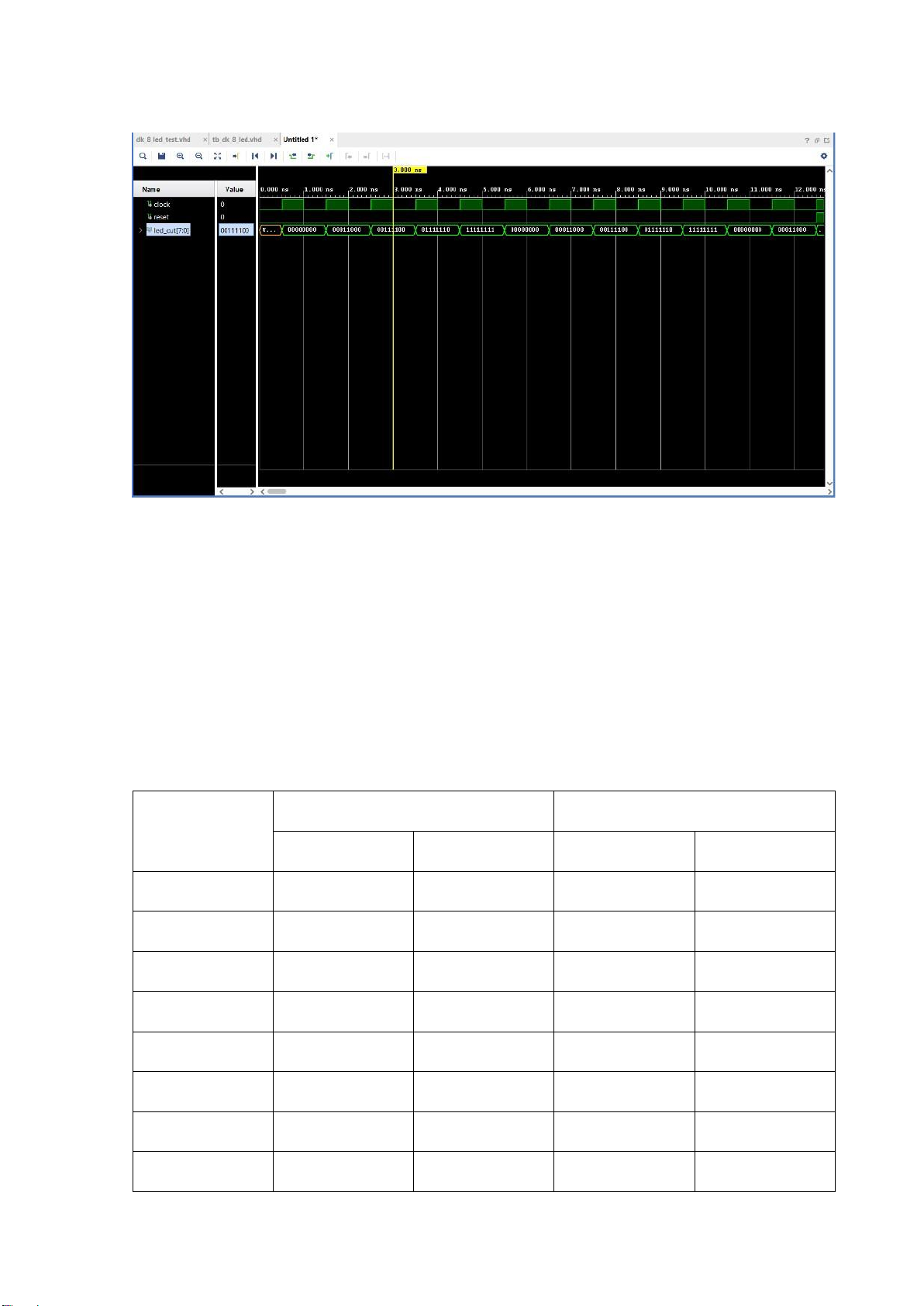

wait for 12.5ns; reset <= '1';-- after 2ns; wait for 2ns; end process; end Behavioral; lOMoARcPSD| 36991220 4. Kết quả Câu 2:

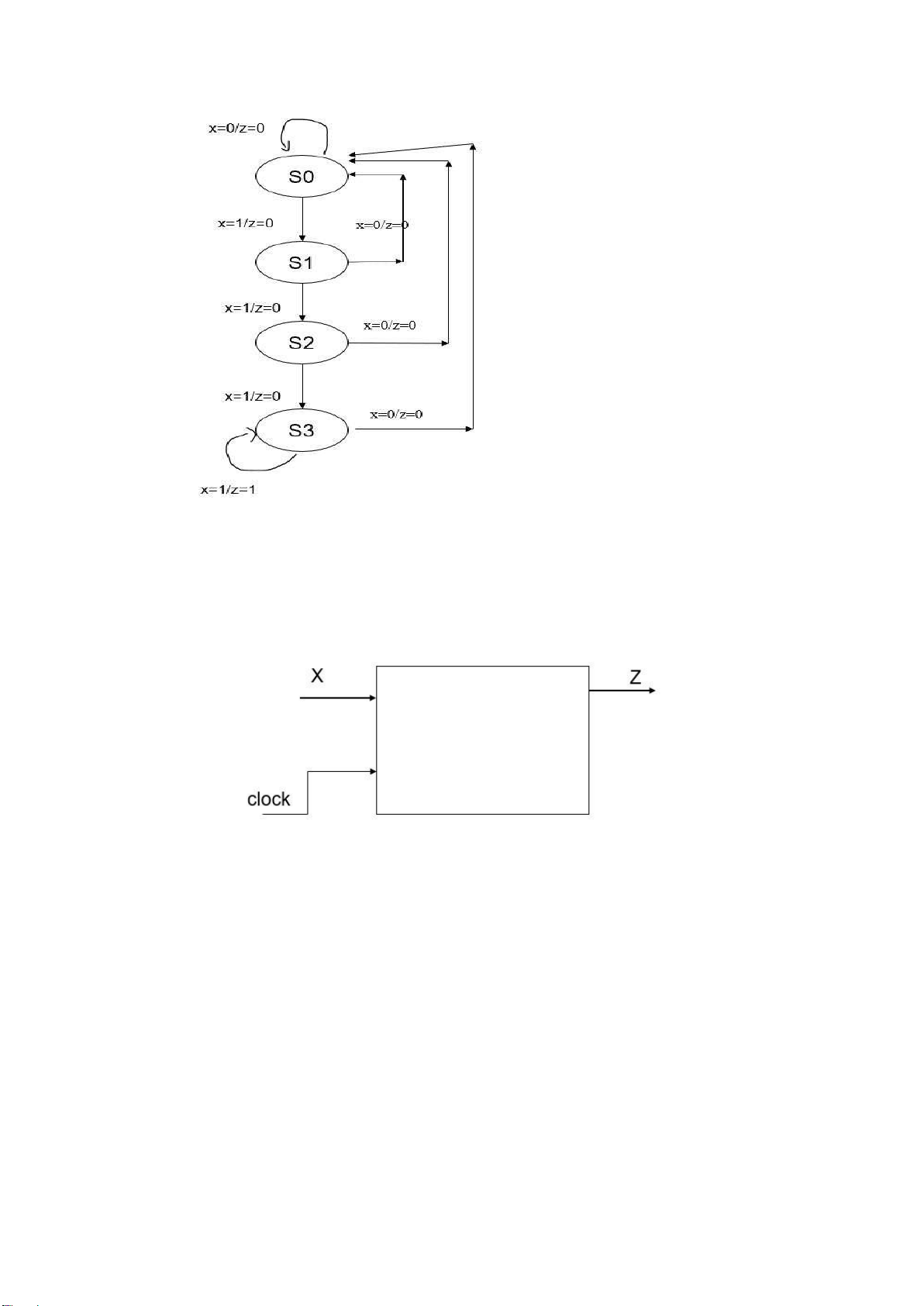

Viết chương trình mô tả mạch phát hiện chuỗi bit nhị phân liên tiếp, đầu ra của nó là 1

khi xuất hiện 4 hoặc nhiều hơn 4 bit 1 liên tục và đầu ra là 0 trong các trường hợp còn

lại. Viết testbench để kiểm tra hoạt động của mạch. Bài làm Phần 1: Phân tích

NX: để phát hiện được 4 bit thì phải nhớ được 3 bit trước đó.

Sn+1 = Q1Q0X (dịch X vào đẩy Q2 ra)

Bảng chuyển đổi trạng thái S Sn+1 Z X=0 X=1 X=0 X=1 Q2Q1Q0 Q2Q1Q0 Q2Q1Q0 Q2Q1Q0 Q2Q1Q0 000 000 001 0 0 001 010 011 0 0 010 100 101 0 0 011 110 111 0 0 100 000 001 0 0 101 010 011 0 0 110 100 101 0 0 lOMoARcPSD| 36991220 111 110 111 0 1 Mã hóa trạng thái S S Sn+1 Z X=0 X=1 X=0 X=1 Q2Q1Q0 Q2Q1Q0 Q2Q1Q0 Q2Q1Q0 000 S0 S0 S1 0 0 001 S1 S2 S3 0 0 010 S2 S4 S5 0 0 011 S3 S6 S7 0 0 100 S4 S0 S1 0 0 101 S5 S2 S3 0 0 110 S6 S4 S5 0 0 111 S7 S6 S7 0 1 lOMoARcPSD| 36991220 Rút gọn

S0 S4 S04, S1 S5 S15, S2 S6 S26 S Sn+1 Z X=0 X=1 X=0 X=1 Q2Q1Q0 Q2Q1Q0 Q2Q1Q0 S04 S04 S15 0 0 S15 S26 S3 0 0 S26 S04 S15 0 0 S3 S26 S7 0 0 S7 S26 S7 0 1 S04 S26 S0426 S Sn+1 Z X=0 X=1 X=0 X=1 Q2Q1Q0 Q2Q1Q0 Q2Q1Q0 S0426 S0426 S15 0 0 S15 S0426 S3 0 0 S3 S0426 S7 0 0 S7 S0426 S7 0 1 Đồ hình trạng thái

Giả sử: S0426 S0, S15 S1, S3 S2, S7 S3 lOMoARcPSD| 36991220

Phần 2: Code VHDL Sơ đồ khối: Code: library IEEE;

use IEEE.STD_LOGIC_1164.ALL; --use IEEE.NUMERIC_STD.ALL; --use

UNISIM.VComponents.all; entity cau_2 is lOMoARcPSD| 36991220 Port ( clock : in std_logic; x : in std_logic; z : out std_logic ); end cau_2;

architecture Behavioral of cau_2 is type th is (s0, s1, s2, s3);--kieu du

lieu liet ke tu DN signal s : th := s0; begin process( clock )

begin if( clock'event and clock = '1' ) then case s is when s0 => if(x='0') then s<=s0; elsif(x='1') then s<=s1; end if;

when s1 => if(x='0') then s<=s0; elsif(x='1') then s<=s2; end if;

when s2 => if(x='0') then s<=s0; elsif(x='1') then s<=s3; end if;

when s3 => if(x='0') then s<=s0; elsif(x='1') then s<=s3; end if; end case; end if; end process; process( clock ) begin

if( clock'event and clock = '1' ) then if(

s=s3 and x='1') then z<='1'; else lOMoARcPSD| 36991220

z<='0'; end if; end if; end process; end Behavioral; Testbench: library IEEE; use

IEEE.STD_LOGIC_1164.ALL; --use IEEE.NUMERIC_STD.ALL; --use

UNISIM.VComponents.all; entity tb_cau_2 is -- Port ( ); end tb_cau_2;

architecture Behavioral of tb_cau_2 is component cau_2 port( clock : in std_logic; x : in std_logic; z : out std_logic );

end component; signal clock :

std_logic := '0'; signal x : std_logic := '0';

signal z : std_logic := '0'; begin

u : cau_2 port map( clock=>clock, x=>x, z=>z); clock <= not

clock after 0.5ns;-- chu ky clock 1ns process begin

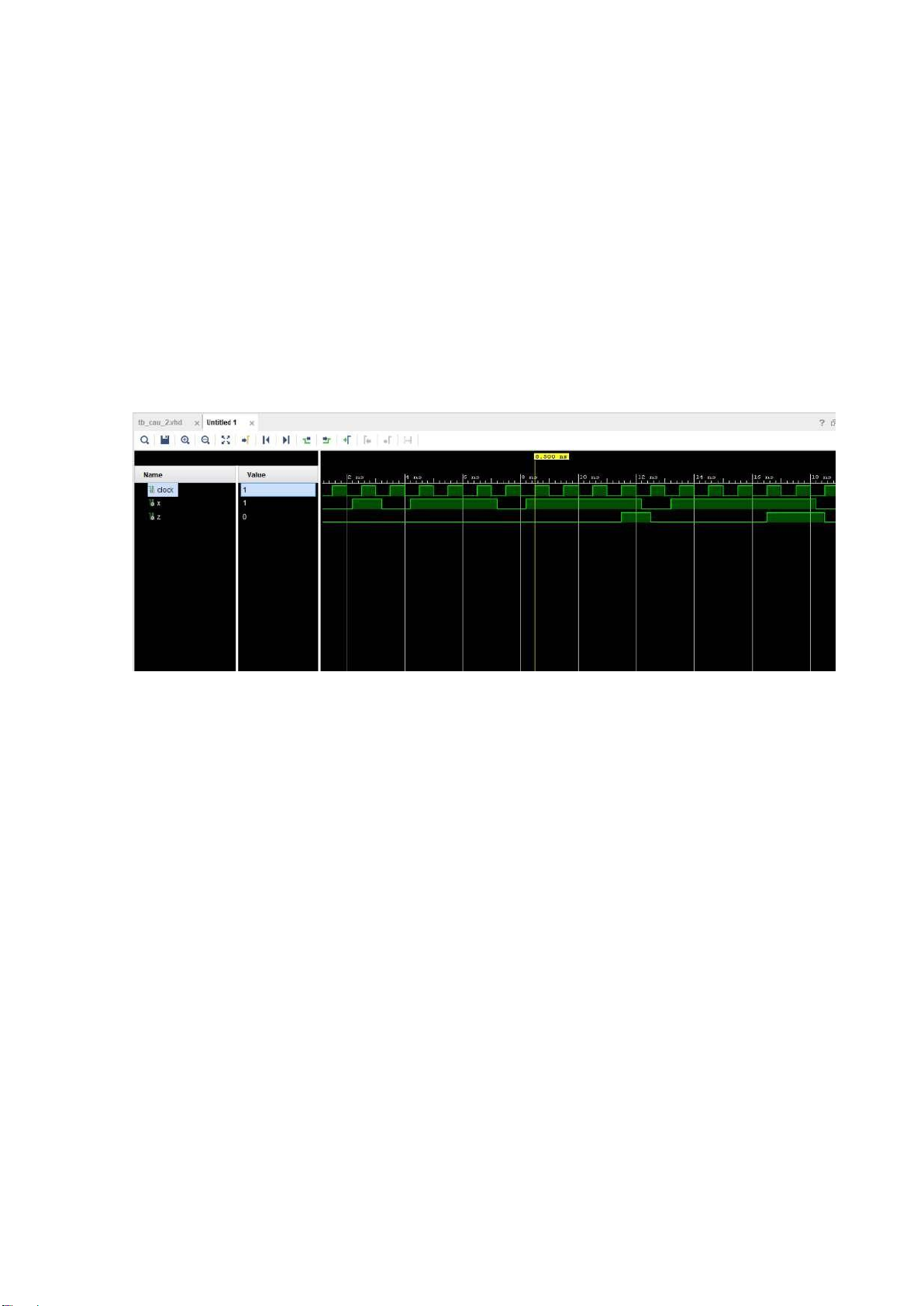

x <= '0'; wait for 0.2ns; x <= '0'; wait for 2ns; x <= '1'; wait for 1ns; x <= '0'; wait for 1ns; x <= '1'; wait for 3ns; x <= '0'; wait for 1ns; x <= lOMoARcPSD| 36991220 '1'; wait for 4ns; x <= '0'; wait for 1ns; x <= '1'; wait for 5ns;

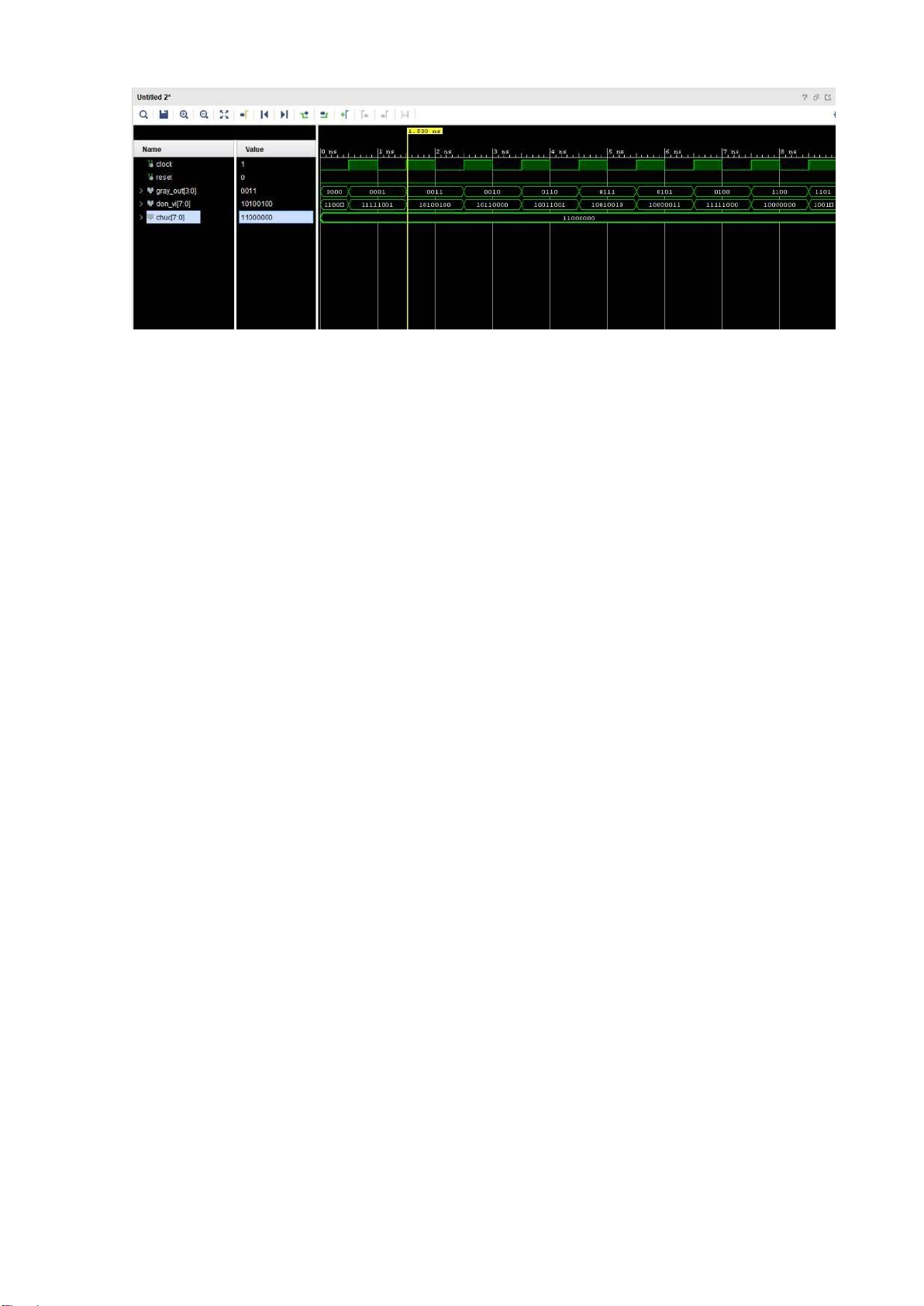

-- x = 001011101111011111 end process; end Behavioral; Run simulation Câu 3:

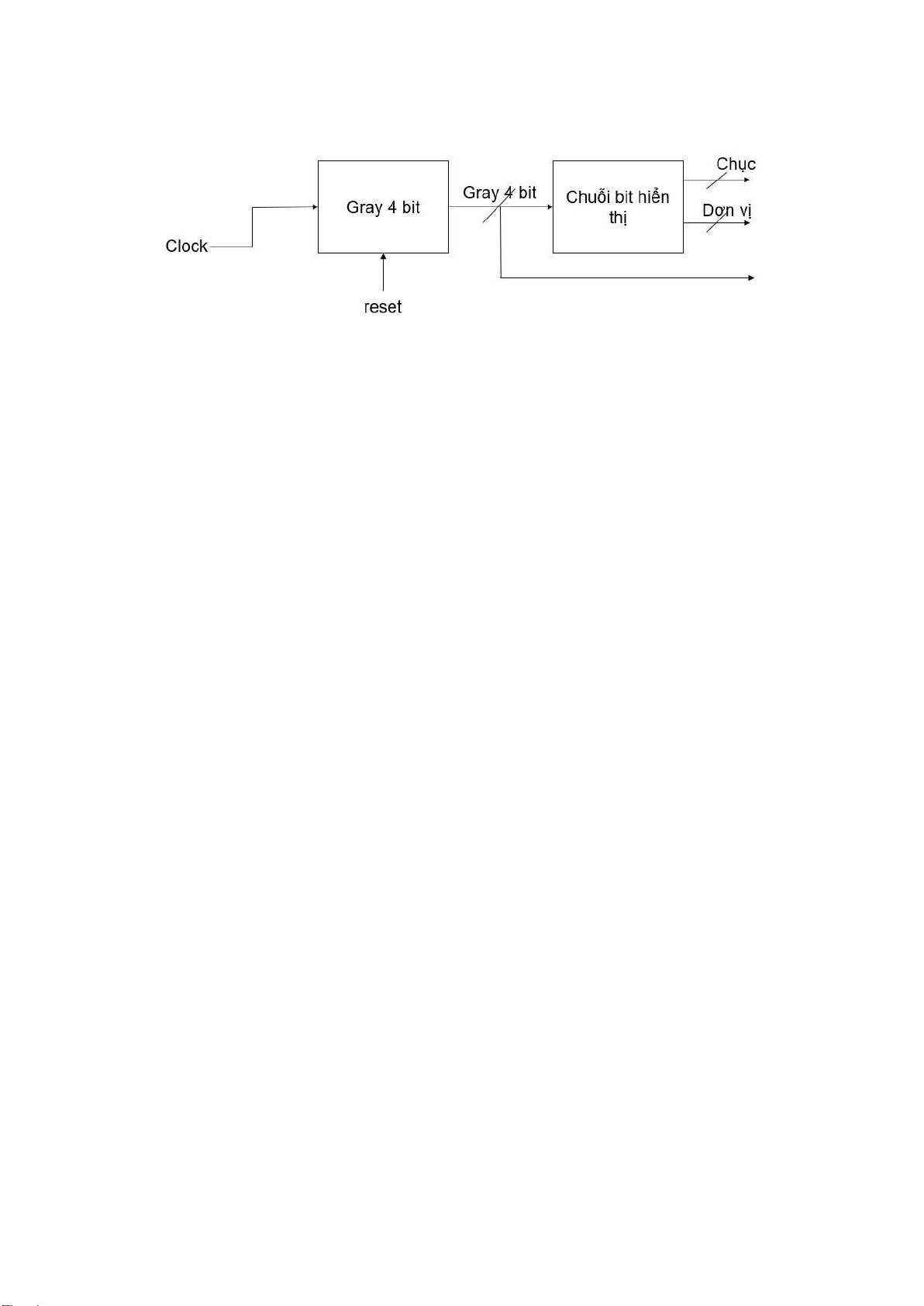

Viết chương trình mô tả bộ đếm Gray 4 bit và hiển thị kết quả dưới dạng thập phân

trên LED 7 thanh. Viết testbench để kiểm tra hoạt động của mạch. Bài làm

Phần 1: Tính mã Gray kế tiếp.

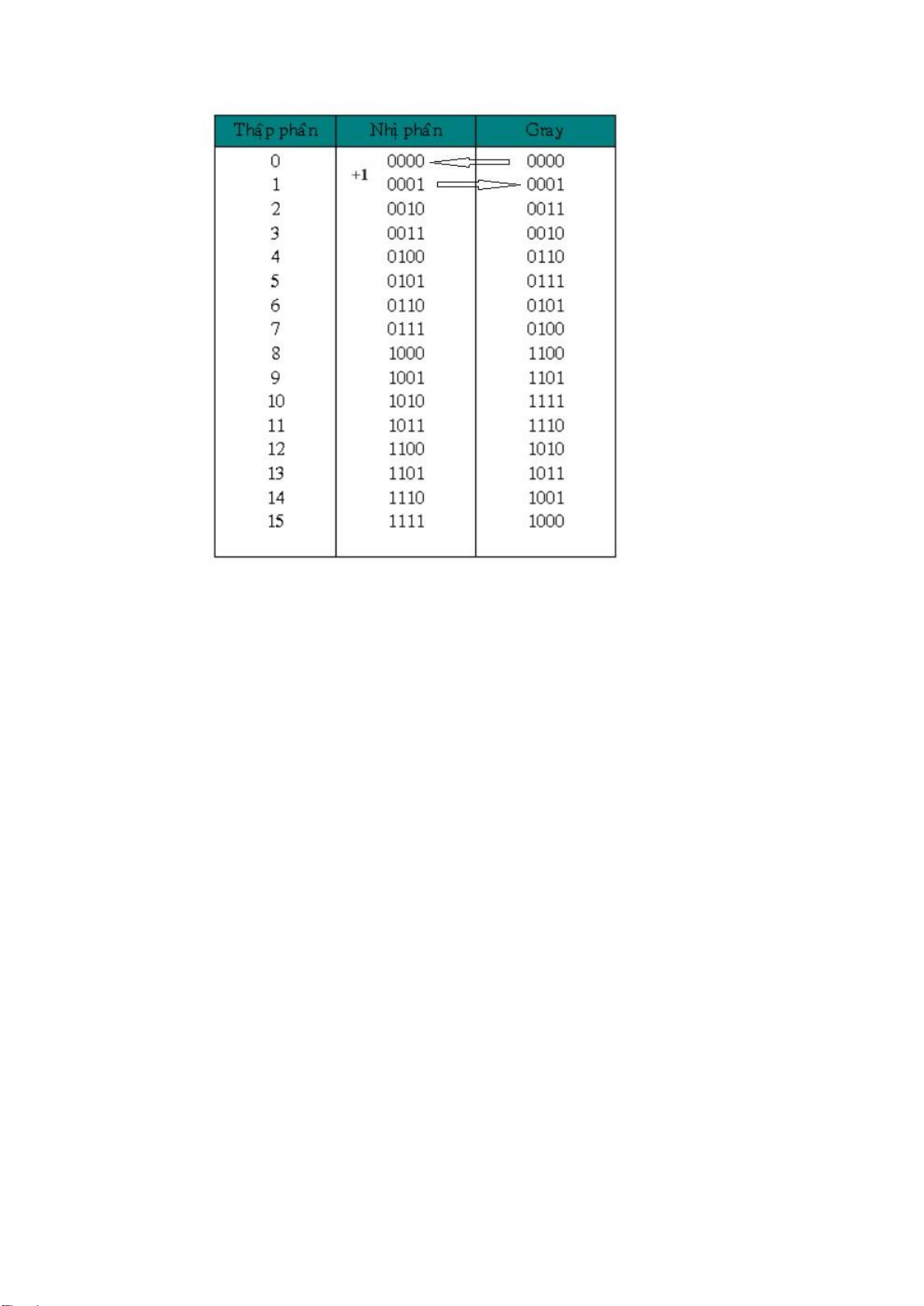

Mã Gray: là mã có 2 từ mã liên tiếp chỉ khác nhau đúng một bit. Để xác định

mã Gray kế tiếp ta sử dụng cách:

Từ mã Gray hiện tai -> BCD tương ứng -> lấy mã BCD đó +1 -> Gray (gray kế tiếp) lOMoARcPSD| 36991220 Từ Gray sang BCD : G3G2G1G0 -> B3B2B1B0 B3 = G3 = 0 xor 0 xor 0 xor G3 B2 = G3 xor G2 = 0 xor 0 xor G3 xor G2 B1 = G3 xor G2 xor G1 = 0 xor G3 xor G2 xor G1 B0 = G3 xor G2 xor G1 xor G0 = G3 xor G2 xor G1xor G0

-> code: B(3 downto 0) = G( 3 downto 0) xor ( ‘0’ & G( 3 downto 1))

xor ( “00” & G(3 downto 2)) xor (“000” & G(3)). Từ BCD sang Gray: B3B2B1B0 -> G3G2G1G0 G3 = 0 xor B3 G2 = B3 xor B2 G1 = B2 xor B1 G0 = B1 xor B0

-> code: G(3 downto 0) = B(3 downto 0) xor ( ‘0’ & B(3 downto lOMoARcPSD| 36991220 1))

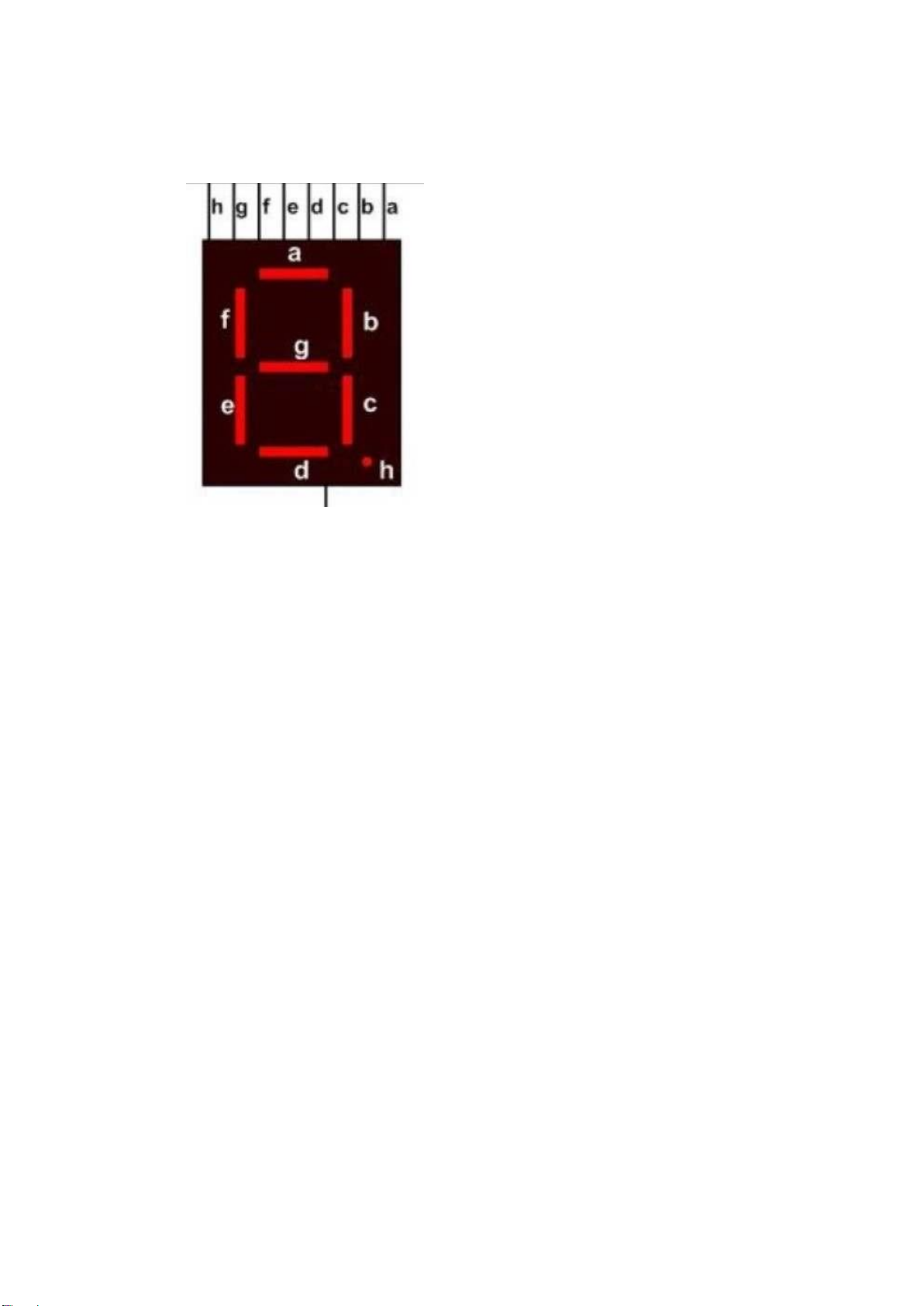

Phần 2: Hiển thị sử dụng 2 led 7 đoạn Anode chung. Led 7 đoạn Anode chung h g f e d c b a

11000000 : số 0 - các thanh từ a-f sáng 11111001 : số 1 10100100 : số 2 10110000 : số 3 10011001 : số 4 10010010 : số 5 10000011 : số 6 11111000 : số 7 10000000 : số 8 10010000 : số 9

Sử dụng 2 chuỗi 8 bit để điều khiển 2 led 7 thanh. Phần 3: Code VHDL Sơ đồ khối: lOMoARcPSD| 36991220 Code: library IEEE;

use IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL; --use UNISIM.VComponents.all; entity cau_3 is

Port ( clock : in std_logic; reset : in std_logic;

gray_out : out std_logic_vector(3 downto 0); don_vi : out std_logic_vector(7 downto 0);

chuc : out std_logic_vector(7 downto 0); ); end cau_3;

architecture Behavioral of cau_3 is signal t_g_chuyen : std_logic_vector(3

downto 0) := "1000"; signal t_b : std_logic_vector(3 downto 0); signal

t_b_1 : std_logic_vector(3 downto 0); signal t_g_out : std_logic_vector(3 downto 0); begin

process( clock, reset) begin if (reset = '1') then

t_g_chuyen <= "1000"; elsif ( clock'event and clock = '1' )

then t_g_chuyen <= t_g_out; end if; end process;

t_b(3 downto 0) <= t_g_chuyen(3 downto 0) xor ( '0' & t_b(3 downto 1));

t_b_1 <= std_logic_vector(unsigned(t_b) + 1);-- IEEE.NUMERIC_STD.ALL

t_g_out(3 downto 0) <= t_b_1(3 downto 0) xor ( '0' & t_b_1(3 downto 1)); lOMoARcPSD| 36991220 gray_out <= t_g_out; process( t_g_out ) begin case t_b_1 is

when "0000" => chuc <= "11000000"; don_vi <= "11000000";-- h g f e d c b a

when "0001" => chuc <= "11000000"; don_vi <= "11111001";-- 01

when "0010" => chuc <= "11000000"; don_vi <= "10100100";-- 02

when "0011" => chuc <= "11000000"; don_vi <= "10110000";-- 03

when "0100" => chuc <= "11000000"; don_vi <= "10011001";-- 04

when "0101" => chuc <= "11000000"; don_vi <= "10010010";-- 05

when "0110" => chuc <= "11000000"; don_vi <= "10000011";-- 06

when "0111" => chuc <= "11000000"; don_vi <= "11111000";-- 07

when "1000" => chuc <= "11000000"; don_vi <= "10000000";-- 08

when "1001" => chuc <= "11000000"; don_vi <= "10010000";-- 09

when "1010" => chuc <= "11111001"; don_vi <= "11000000";-- 10

when "1011" => chuc <= "11111001"; don_vi <= "11111001";-- 11

when "1100" => chuc <= "11111001"; don_vi <= "10100100";-- 12

when "1101" => chuc <= "11111001"; don_vi <= "10110000";-- 13

when "1110" => chuc <= "11111001"; don_vi <= "10011001";-- 14

when "1111" => chuc <= "11111001"; don_vi <= "10010010";-- 15

when others => chuc <= "01111111"; don_vi <= "01111111"; end case; end process; end Behavioral; lOMoARcPSD| 36991220 Testbench: library IEEE; use IEEE.STD_LOGIC_1164.ALL;

--use IEEE.NUMERIC_STD.ALL; --use UNISIM.VComponents.all; entity tb_cau_3 is -- Port ( ); end tb_cau_3;

architecture Behavioral of tb_cau_3 is component cau_3 Port ( clock : in std_logic; reset : in std_logic;

gray_out : out std_logic_vector(3 downto 0); don_vi :

out std_logic_vector(7 downto 0);

chuc : out std_logic_vector(7 downto 0) ); end component;

signal clock : std_logic := '0'; signal reset : std_logic;

signal gray_out : std_logic_vector(3 downto 0); signal don_vi

: std_logic_vector(7 downto 0); signal chuc : std_logic_vector(7 downto 0); begin

u : cau_3 port map(clock=>clock, reset=>reset, gray_out=>gray_out,

don_vi=>don_vi, chuc=>chuc);

clock <= not clock after 0.5ns; process begin reset <= '0'; wait for 20ns; reset <= '1'; wait for 1ns; end process; end Behavioral; Run simulation lOMoARcPSD| 36991220 lOMoARcPSD| 36991220

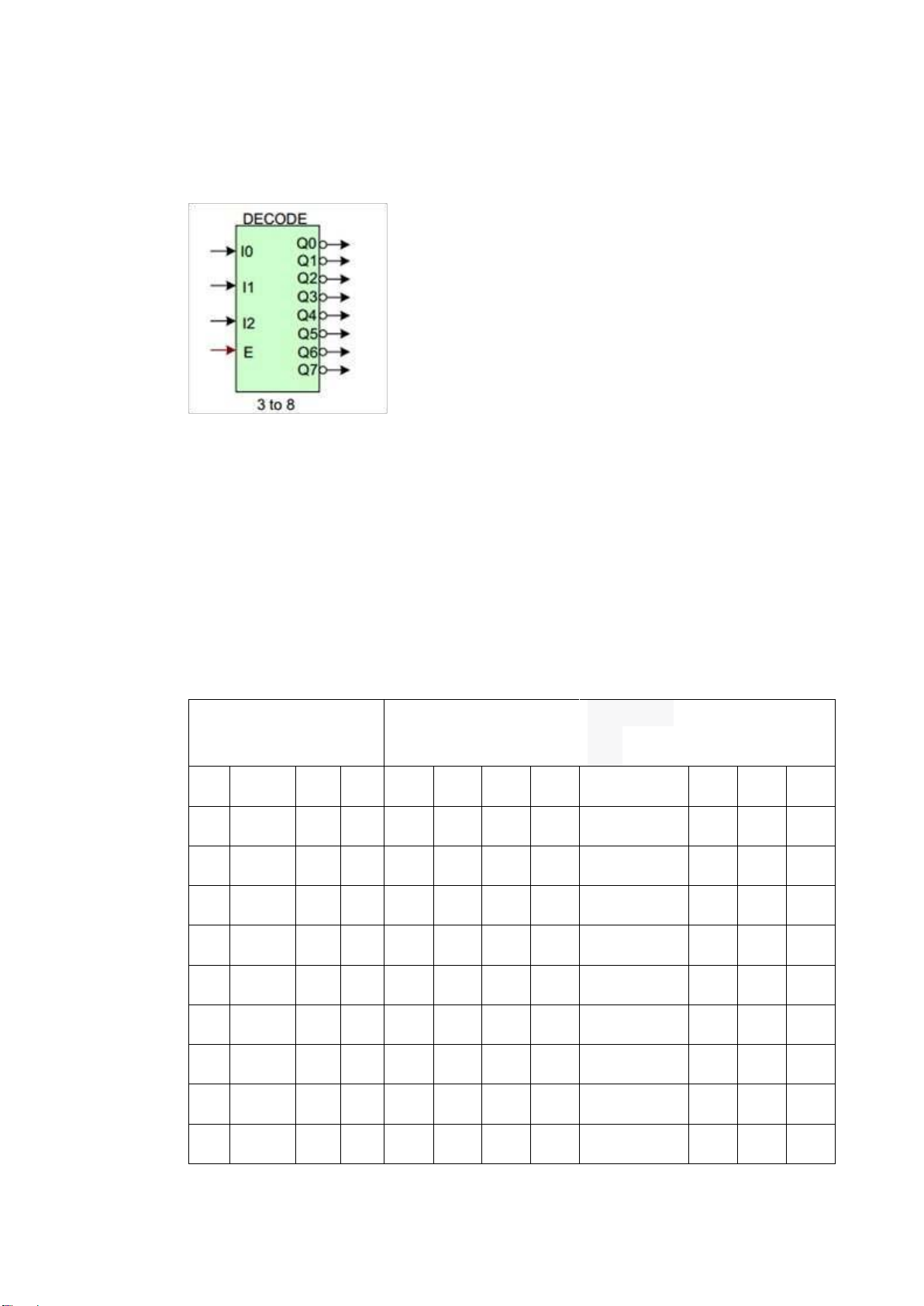

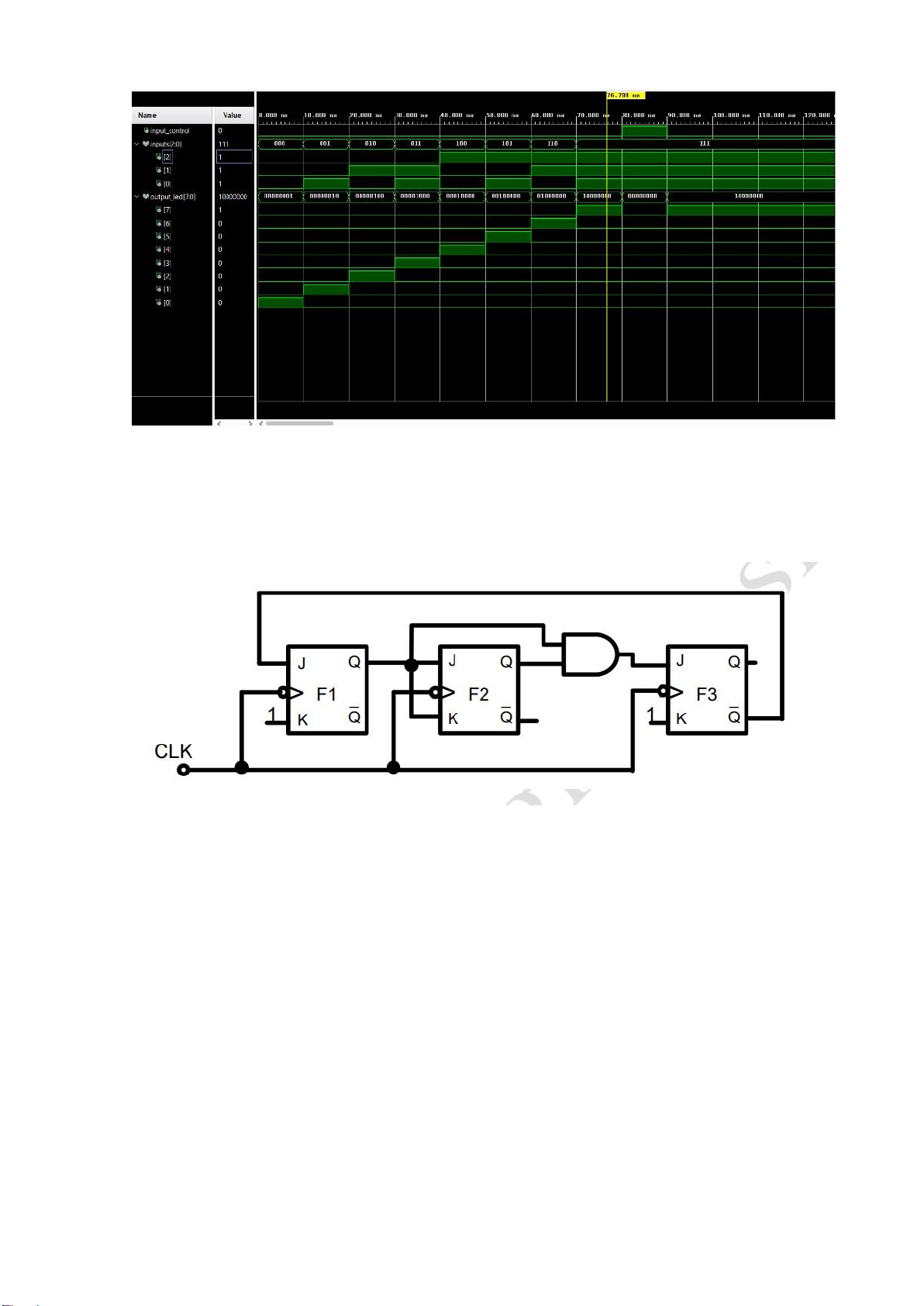

Câu 4: Viết chương trình mô tả bộ giải mã 3:8, có đầu vào điều khiển hoạt động ở

mức thấp, lối ra hiển thị trên LED đơn. Viết testbench để kiểm tra hoạt động của mạch. 1. Sơ đồ khối 2. Nguyên lý •

Mạch này nhận hai đầu vào chính: input_control và inputs. •

input_control là tín hiệu kiểm soát, có 2 trạng thái: '0' và '1'. Khi

input_control là '0', mạch sẽ hoạt động ở chế độ bình thường và sẽ giải mã giá

trị của inputs thành một trong tám đèn LED được bật. •

inputs là một tín hiệu 3 bit, biểu thị một trong tám trạng thái khả dụng.

Mạch này sẽ chọn đèn LED cần bật dựa trên giá trị của inputs. Mỗi giá trị của

inputs tương ứng với một đèn LED. •

Khi input_control là '1', tất cả các đèn

LED sẽ tắt (output_led = "00000000"). inpu ts output_ led E I2 I1 I0 Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0 1 x x x 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 1 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 1 0 1 0 0 1 0 0 0 0 0 0 1 1 0 0 1 0 0 0 0 0 0 0 1 1 1 1 0 0 0 0 0 0 0

3. Quá trình thực hiện lOMoARcPSD| 36991220 - Main lOMoARcPSD| 36991220 library IEEE;

use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Decoder_3to8 is Port (

input_control : in STD_LOGIC; inputs : in

STD_LOGIC_VECTOR(2 downto 0); output_led : out STD_LOGIC_VECTOR(7 downto 0) ); end Decoder_3to8;

architecture Behavioral of Decoder_3to8 is begin

process (inputs, input_control) begin if input_control = '0' then

case inputs is when "000" =>

output_led <= "00000001"; when "001" =>

output_led <= "00000010"; when "010" =>

output_led <= "00000100"; when "011" =>

output_led <= "00001000"; when "100" =>

output_led <= "00010000"; when "101" =>

output_led <= "00100000"; when "110" =>

output_led <= "01000000"; when others =>

output_led <= "10000000"; end case; else

output_led <= (others => '0'); lOMoARcPSD| 36991220 end if; end process; end Behavioral; - Testbench library IEEE;

use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity Decoder_3to8_Testbench is end Decoder_3to8_Testbench;

architecture Behavioral of Decoder_3to8_Testbench is

signal input_control : STD_LOGIC := '0'; signal inputs :

STD_LOGIC_VECTOR(2 downto 0) := "000"; signal output_led : STD_LOGIC_VECTOR(7 downto 0); begin

UUT : entity work.Decoder_3to8 port map (

input_control => input_control, inputs => inputs, output_led => output_led ); process begin input_control <= '0';

inputs <= "000"; wait for 10 ns; inputs <= "001"; wait for 10 ns; lOMoARcPSD| 36991220 inputs <= "010"; wait for 10 ns; inputs <= "011"; wait for 10 ns; inputs <= "100"; wait for 10 ns; inputs <= "101"; wait for 10 ns; inputs <= "110"; wait for 10 ns; inputs <= "111"; wait for 10 ns;

input_control <= '1'; wait for 10 ns; input_control <= '0'; wait; end process; end Behavioral; 4. Kết quả lOMoARcPSD| 36991220 Câu 5:

Viết mô tả VHDL (Entity và Architecture) cho mạch đó. Viết testbench để kiểm tra hoạt động của mạch.

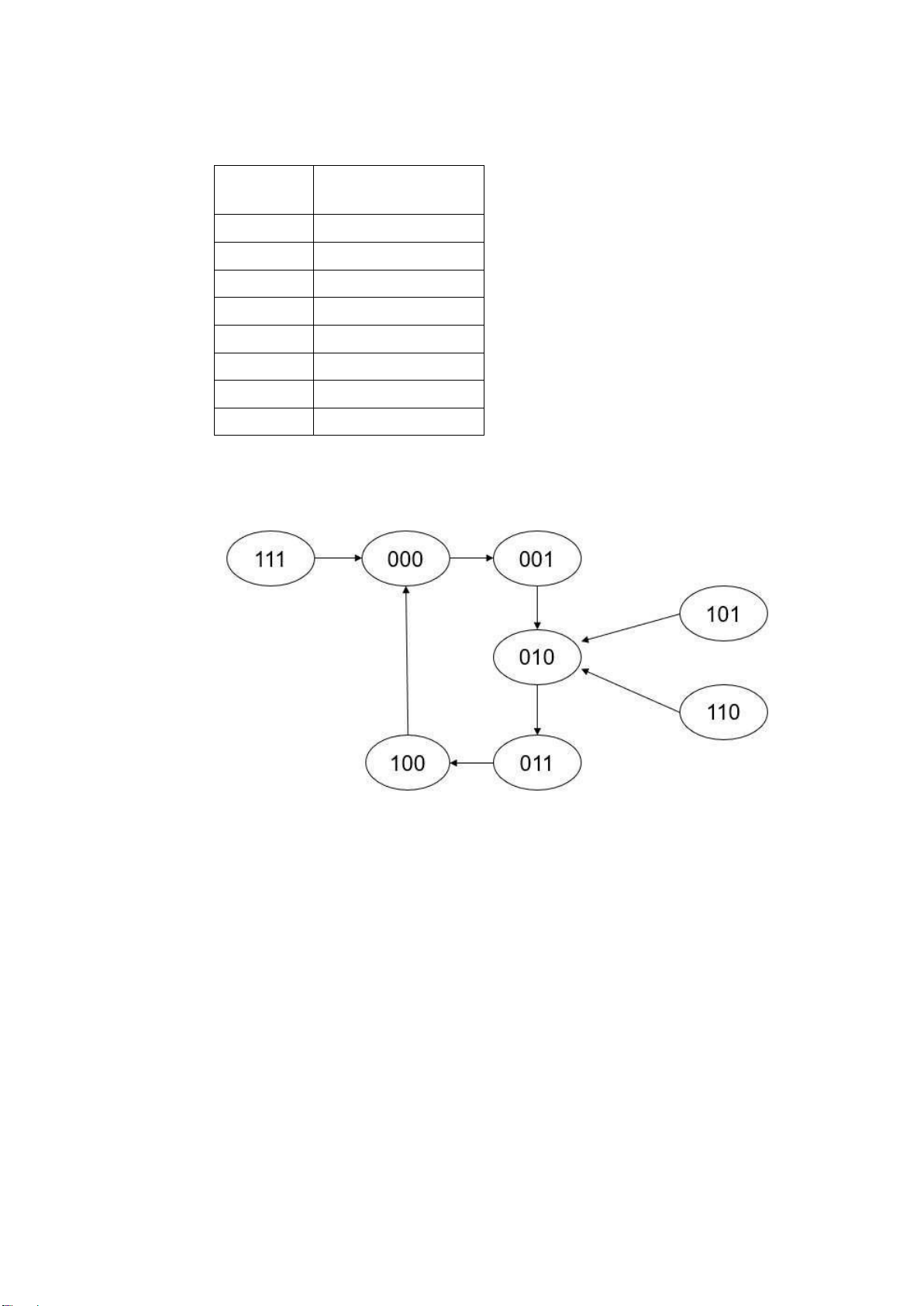

Phần 1: Phân tích mạch logic tuần tự

Phương trình định thời: C = C1 = C2 =C3

Phương trình kích : J1 = not Q3, K1 = 1 J2 = K2 = Q1 J3 = Q1 and Q2, K3 = 1

Phương trình đặc trưng: Qn+1 i = (Ji and (not Qi)) or ((not K) and Qi)

Phương trình chuyển đổi trạng thái:

Qn+1 1 = J1 and (not Q1) or ((not K) and Q1) = (not Q3)and(notQ1) Qn+1 2 = Q1 xor Q2 lOMoARcPSD| 36991220

Qn+1 3 = Q1 and Q2 and (not Q3)

Bảng chuyển đổi trạng thái: Q3Q2Q 1 Qn+13 Qn+12 Qn+11 000 001 001 010 010 011 011 100 100 000 101 010 110 010 111 000 Đồ hình trạng thái:

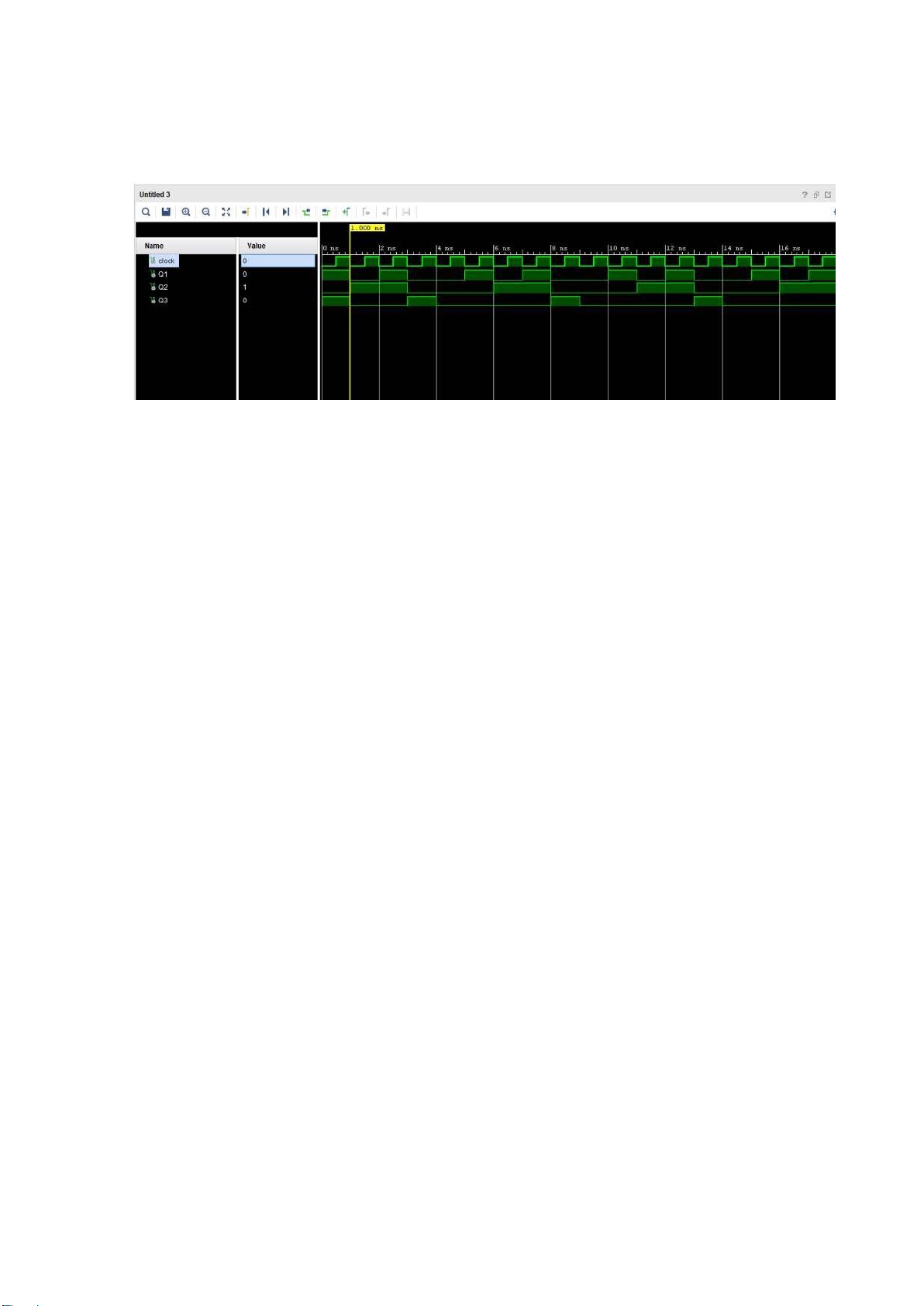

NX: Là bộ đếm mod 5 tự khởi động Phần 2: Code VHDL Code: JK library IEEE;

use IEEE.STD_LOGIC_1164.ALL; --use IEEE.NUMERIC_STD.ALL; --use UNISIM.VComponents.all; entity JK is Port ( lOMoARcPSD| 36991220 clock : in std_logic; reset : in std_logic; J : in std_logic; K : in std_logic; Q : out std_logic; Q_not : out std_logic ); end JK;

architecture Behavioral of JK is signal Q_n: std_logic;

signal Q_n_1: std_logic;-- :='0';-- phai khoi tao neu khong noi component se bi U begin process( clock, reset) begin if(reset='1') then Q_n_1 <= '0';

elsif( clock' event and clock = '1') then

Q_n_1 <= (J and (not Q_n)) or ((not K) and Q_n); end if; end process; Q_n <= Q_n_1; Q <= Q_n_1; Q_not <= not Q_n_1; end Behavioral; Code: khối 1 library IEEE;

use IEEE.STD_LOGIC_1164.ALL; entity JK_1 is Port ( clock : in std_logic; J : in std_logic; K : in std_logic; Q : out std_logic; Q_not : out std_logic ); end JK_1;

architecture Behavioral of JK_1 is signal Q_n: std_logic;

signal Q_n_1: std_logic :='1'; begin lOMoARcPSD| 36991220 process( clock ) begin

if( clock' event and clock = '0') then

Q_n_1 <= (J and (not Q_n)) or ((not K) and Q_n); end if; end process; Q_n <= Q_n_1; Q <= Q_n_1; Q_not <= not Q_n_1; end Behavioral;

NX: khối 2, 4 tương tự khối 1 Code: khối 3 library IEEE; use

IEEE.STD_LOGIC_1164.ALL; entity block_and is Port ( a: in std_logic; b: in std_logic; c : out std_logic );

end block_and; architecture Behavioral of

block_and is begin c<= a and b; end Behavioral; Code: Câu 5 library IEEE; use IEEE.STD_LOGIC_1164.ALL;

--use IEEE.NUMERIC_STD.ALL; --use UNISIM.VComponents.all; entity cau_5 is Port ( clock : in std_logic; Q1 : out std_logic; Q2 : out std_logic; Q3 : out std_logic ); end cau_5;

architecture Behavioral of cau_5 is lOMoARcPSD| 36991220 component JK_1 port( clock : in std_logic; J : in std_logic; K : in std_logic; Q : out std_logic; Q_not : out std_logic ); end component; component JK_2 port( clock : in std_logic; J : in std_logic; K : in std_logic; Q : out std_logic; Q_not : out std_logic ); end component; component JK_3 port( clock : in std_logic; J : in std_logic; K : in std_logic; Q : out std_logic; Q_not : out std_logic ); end component; component block_and Port ( a: in std_logic; b: in std_logic; c : out std_logic ); end component;

signal n_1 : std_logic;-- :='0'; signal

n_2 : std_logic;-- :='1'; signal n_3 :

std_logic;-- :='0'; signal n_4 : std_logic;-- :='0';

signal n_5 : std_logic;-- := '0'; lOMoARcPSD| 36991220 begin

block_1 : JK_1 port map(clock=>clock, J=>n_1, K=>'1', Q=>n_2); block_2 : JK_2 port

map(clock=>clock, J=>n_2, K=>n_2, Q=>n_3); block_3 : block_and port map(a=> n_2, b=>n_3, c=>n_4);

block_4 : JK_3 port map(clock=>clock, J=>n_4, K=>'1', Q_not=>n_1, Q=>n_5); Q1<= n_2; Q2<= n_3; Q3<= n_5; end Behavioral; Testbench: library IEEE; use IEEE.STD_LOGIC_1164.ALL;

--use IEEE.NUMERIC_STD.ALL; --use UNISIM.VComponents.all; entity t_b_cau_5 is -- Port ( ); end t_b_cau_5;

architecture Behavioral of t_b_cau_5 is component cau_5 Port ( clock : in std_logic; Q1 : out std_logic; Q2 : out std_logic; Q3 : out std_logic ); end component;

signal clock : std_logic := '0';-- chu y phai khoi tao clock signal Q1 :

std_logic; signal Q2 : std_logic; signal Q3 : std_logic;

-- chu y de test tu khoi dong tu 101 ve 010 vao cao Jk thay Q_n_1

begin u: cau_5 port map(clock=>clock, Q1=>Q1, Q2=>Q2, Q3=>Q3); lOMoARcPSD| 36991220

clock <= not clock after 0.5ns; end Behavioral; Run simulation