Preview text:

lOMoAR cPSD| 59908026 LỜI MỞ Đ 숃 U

Đứng trước thời đại 4.0 – kỷ nguyên số của toàn nhân loại, những ngành

công nghiệp chế tạo như phần mềm, phần cứng, vật liệu linh kiện bán dẫn đã

đạt được nhiều thành tựu đáng chú ý và góp phần không nhỏ vào sự thay đổi

này. Nhận thấy tầm quan trọng của sự thay đổi có thể quyết định vận mệnh

quốc gia như vậy, những môn liên quan đến phần cứng và phần mềm đã được

tích hợp sâu vào chương trình đào tạo như một phần không thể thiếu của các

trường Cao đẳng, Đại học, đặc biệt là các trường kỹ thuật nhằm đào tạo ra thế

hệ các kỹ sư chất lượng trong tương lai. Qua bộ môn “Kiến trúc máy tính”,

sinh viên sẽ có cái nhìn cụ thể và chi tiết hơn về ngành nghề mình được đào

tạo và qua đó sẽ kích thích sự sáng tạo để cho ra những sản phẩm thiết thực phục vụ đời sống.

Qua bài tập lớn này chúng em có cái nhìn thực tế hơn, sâu sắc hơn về cách

một máy tính đơn giản như máy tính 8-bit hoạt động, qua đó có cái nhìn cụ

thể về cách mà các cổng logic làm việc với nhau.

Với sự hướng dẫn tận tình của thầy Hoàng Anh Dũng, chúng em hy vọng

có thể hoàn thành tốt bài tập lần này.

Chúng em xin chân thành cảm ơn thầy.

CHƯƠNG 1: GIỚI THI 쨃⌀U CHUNG V 쨃 KI 쨃 ĀN

TR 唃 ĀC M䄃ĀY T䤃ĀNH V䄃 H 쨃 ⌀ M䄃ĀY T䤃ĀNH 8-BIT I.

愃 i v 愃 c 愃 愃 i 1. Đề tài

Thiết kế máy tính 8 bit đơn giản, sử dụng cổng logic để thực hiện ph 攃 Āp toán. 2. Các yêu cầu đề ra -

ạt động của máy tính 8 bit

- Tìm hiểu các bộ phận cấ - Hoàn thiện sản phẩm II.

甃 Āc m 愃 Āy t 椃 Ān 1 lOMoAR cPSD| 59908026

Kiến trúc máy tính (Computer Architecture) và Tổ chức máy tính

(Computer Organization) là hai trong số các khái niệm cơ bản của ngành Công

nghệ máy tính (Computer Engineering). Có thể nói kiến trúc máy tính là bức

tranh toàn cảnh về hệ thống máy tính, còn tổ chức máy tính là bức tranh cụ thể

về các thành phần phần cứng của hệ thống máy tính. Kiến trúc máy tính là khoa

học về việc lựa chọn và kết nối các thành phần phần cứng để tạo ra các máy

tính đạt được các yêu cầu về chức năng (functionality), hiệu năng

(performance) và giá thành (cost). Nhờ có sự phát triển rất mạnh mẽ của công

nghệ vi xử lý, các máy tính ngày nay có tính năng phong phú, nhanh hơn và rẻ

hơn so với máy tính các thế hệ trước.

Kiến trúc máy tính còn được xem xét theo khía cạnh mà người lập trình có

thể can thiệp vào mọi mức đặc quyền, bao gồm các thanh ghi, ô nhớ các ngắt

... có thể được thâm nhập thông qua các lệnh. Ngày nay có rất nhiều tiến bộ

trong lĩnh vực Điện tử và nhiều công nghệ tiên tiến đang được phát triển mỗi

ngày, nhưng vi điều khiển 8-bit vẫn có vai trò riêng trong thị trường điện tử kỹ

thuật số thống trị bởi các thiết bị kỹ thuật số 16-bit, 32-bit và 64-bit.

Kiến trúc máy tính bao gồm ít nhất ba phạm trù con chính: -

Kiến trúc tập lệnh (Instruction set architecture), là

hình ảnh trừu tượng của một hệ thống tính toán được nhìn từ góc

độ của một lập trình viên sử dụng ngôn ngữ máy (hay hợp ngữ),

bao gồm tập lệnh, cách đánh địa chỉ bộ nhớ (memory address

modes), các thanh ghi, và các định dạng địa chỉ và dữ liệu. -

Vi kiến trúc (Microarchitecture), còn gọi là Tổ chức

máy tính ( Computer organization) là một mô tả bậc thấp, cụ thể

hơn về hệ thống. Mô tả này nói về các bộ phận cấu thành của hệ

thống được kết nối với nhau như thế nào và chúng hoạt động tương

hỗ như thế nào để thực hiện kiến trúc tập lệnh. Ví dụ, kích thước

bộ đệm cache của một máy tính là một đặc điểm về tổ chức máy

tính mà thường không liên quan đến kiến trúc tập lệnh. -

Thiết kế hệ thống (System Design) bao gồm tất cả các

thành phần phần cứng khác bên trong một hệ thống tính toán chẳng

hạn: Các đường kết nối hệ thống như bus và switch, các bộ điều

khiển bộ nhớ (memory controller) và các cây phả hệ bộ nhớ, các

cơ chế CPU off-load như truy nhập bộ nhớ trực tiếp (direct memory

access), các vấn đề như đa xử lý (multiprocessing). 2 lOMoAR cPSD| 59908026 III.

⌀ m 愃 Āy t 椃 Ānh 8-bit

Trong kiến trúc máy tính, số nguyên 8bit hoặc các đơn vị dữ liệu khác là

những số nguyên có chiều rộng 8-bit (1 octet ). Ngoài ra, kiến trúc CPU và ALU

8-bit là những kiến trúc dựa trên thanh ghi hoặc bus dữ liệu có kích thước đó.

Địa chỉ bộ nhớ (và do đó địa chỉ bus) cho CPU 8-bit thường lớn hơn 8 bit,

thường là 16-bit, trong khi về lý thuyết chúng có thể là 8- bit và trong một số

trường hợp, địa chỉ 8-bit cũng được sử dụng với địa chỉ 16-bit chủ yếu được

sử dụng. '8-bit' cũng là một thế hệ máy vi tính trong đó bộ vi xử lý 8-bit là tiêu

chuẩn. Thuật ngữ '8-bit' cũng được áp dụng cho các bộ ký tự có thể được sử

dụng trên máy tính có byte 8-bit, được biết đến nhiều nhất là các dạng ASCII mở rộ

ỗi ISO / IEC 8859 của các bộ ký tự quốc gia -

đặc biệt là tiếng Latin 1 cho các ngôn ngữ tiếng Anh và Tây Âu.

IBM System / 360 đã giới thiệu bộ nhớ định địa chỉ byte với các byte 8 bit,

trái ngược với bộ nhớ định địa chỉ bằng chữ số hoặc chữ số có địa chỉ bit hoặc

thập phân, mặc dù của nó thanh ghi mục đích chung rộng 32 bit và địa chỉ

được chứa trong 24 bit thấp hơn của các địa chỉ đó. Các mô hình khác nhau

của System / 360 có độ rộng đường dẫn dữ liệu nội bộ khác nhau; IBM System

/ 360 Model 30 (1965) đã triển khai kiến trúc 32-bit System / 360, nhưng có

độ rộng đường dẫn gốc 8 bit và thực hiện số học 32-bit, 8-bit cùng một lúc. Bộ

vi xử lý 8-bit đầu tiên được sử dụng rộng rãi là Intel 8080, được sử dụng trong

nhiều máy tính yêu thích vào cuối những năm 1970 và đầu những năm 1980,

thường chạy CP / Hệ điều hành M; nó có các từ dữ liệu 8 bit và địa chỉ 16 bit.

Zilog Z80 ( tương thích với 8080) và Motorola 6800 cũng được sử dụng trong

các máy tính tương tự. Z80 và MOS Technology 6502 CPU 8bit đã được sử

dụng rộng rãi trong máy tính gia đình và bảng điều khiển trò chơi thế hệ thứ

ba và của những năm 1970 và 1980. Nhiều CPU 8-bit hoặc vi điều khiển là cơ

sở của các hệ thống nhúng phổ biến hiện nay.

Một thanh ghi 8 bit có thể lưu trữ 28 giá trị khác nhau. Phạm vi giá trị số

nguyên có thể được lưu trữ trong 8 bit phụ thuộc vào cách biểu diễn số

nguyên được sử dụng. Với hai cách biểu diễn phổ biến nhất, phạm vi từ 0 đến

255 (28 - 1) để biểu diễn dưới dạng số nhị phân (không dấu) và −128 (−1 ×

27) đến 127 (27 - 1) để biểu diễn dưới dạng phần bù của hai. CPU 8 bit sử dụng

bus dữ liệu 8 bit và do đó có thể truy cập 8 bit dữ liệu trong một lệnh máy duy

nhất. Bus địa chỉ thường rộng một octet k 攃 Āp (16 bit), do các cân nhắc thực

tế và kinh tế. Điều này ngụ ý một không gian địa chỉ trực tiếp là 64 KB (65,536

byte) trên hầu hết các bộ xử lý 8-bit. 3 lOMoAR cPSD| 59908026

IV. Ý NGHĨA KHOA HỌC VÀ THỰC TIỄN CỦA ĐỀ TÀI 1. Ý nghĩa khoa học

- Nắm vững cấu trúc máy tính: Đây là cơ hội để tìm hiểu sâu hơn về cấu

trúc và nguyên lý hoạt động của máy tính, từ các phần tử cơ bản như

bộ xử lý, bộ nhớ, bộ điều khiển đến cách chúng tương tác với nhau.

- Áp dụng kiến thức lý thuyết: Nhóm nghiên cứu có thể thử nghiệm và

áp dụng những kiến thức lý thuyết đã học vào việc thiết kế một hệ

thống máy tính hoàn chỉnh. Điều này giúp củng cố kiến thức và hiểu

sâu hơn về lý thuyết và thực tiễn.

- Nghiên cứu và phát triển: Việc thiết kế máy tính 8 bits có thể dẫn đến

việc nghiên cứu và phát triển các công nghệ mới hoặc cải tiến trong lĩnh vực này. 2. Ý nghĩa thực tiễn

- Học hỏi kỹ năng thiết kế: Việc thiết kế máy tính 8 bits trên phần mềm

Logisim giúp nhóm nghiên cứu phát triển kỹ năng thiết kế mạch điện

tử và logic, kỹ năng quan trọng trong ngành Kỹ thuật Điện tử và Máy tính.

- Ứng dụng vào công việc: Kiến thức và kỹ năng thu được từ đề tài này

có thể được áp dụng trong ngành Công nghệ thông tin, từ việc thiết kế

mạch đến việc hiểu sâu về hoạt động của máy tính.

- Giải quyết vấn đề và sáng tạo: Thông qua việc tìm kiếm cách cải tiến,

tối ưu hóa hoặc mở rộng chức năng của máy tính 8 bits, nhóm nghiên

cứu có cơ hội thể hiện sự sáng tạo và khả năng giải quyết vấn đề.

Điều này không chỉ giúp nhóm nghiên cứu có hiểu biết rộng hơn về khoa

học máy tính mà còn phát triển kỹ năng thiết kế và nghiên cứu, sẵn sàng cho

thị trường lao động yêu cầu kiến thức sâu về CNTT và Kỹ thuật điện tử.

CHƯƠNG II: T 퐃ऀ NG QUAN V 쨃 H 쨃⌀ TH 퐃 ĀNG I. 甃 Āc 4 lOMoAR cPSD| 59908026

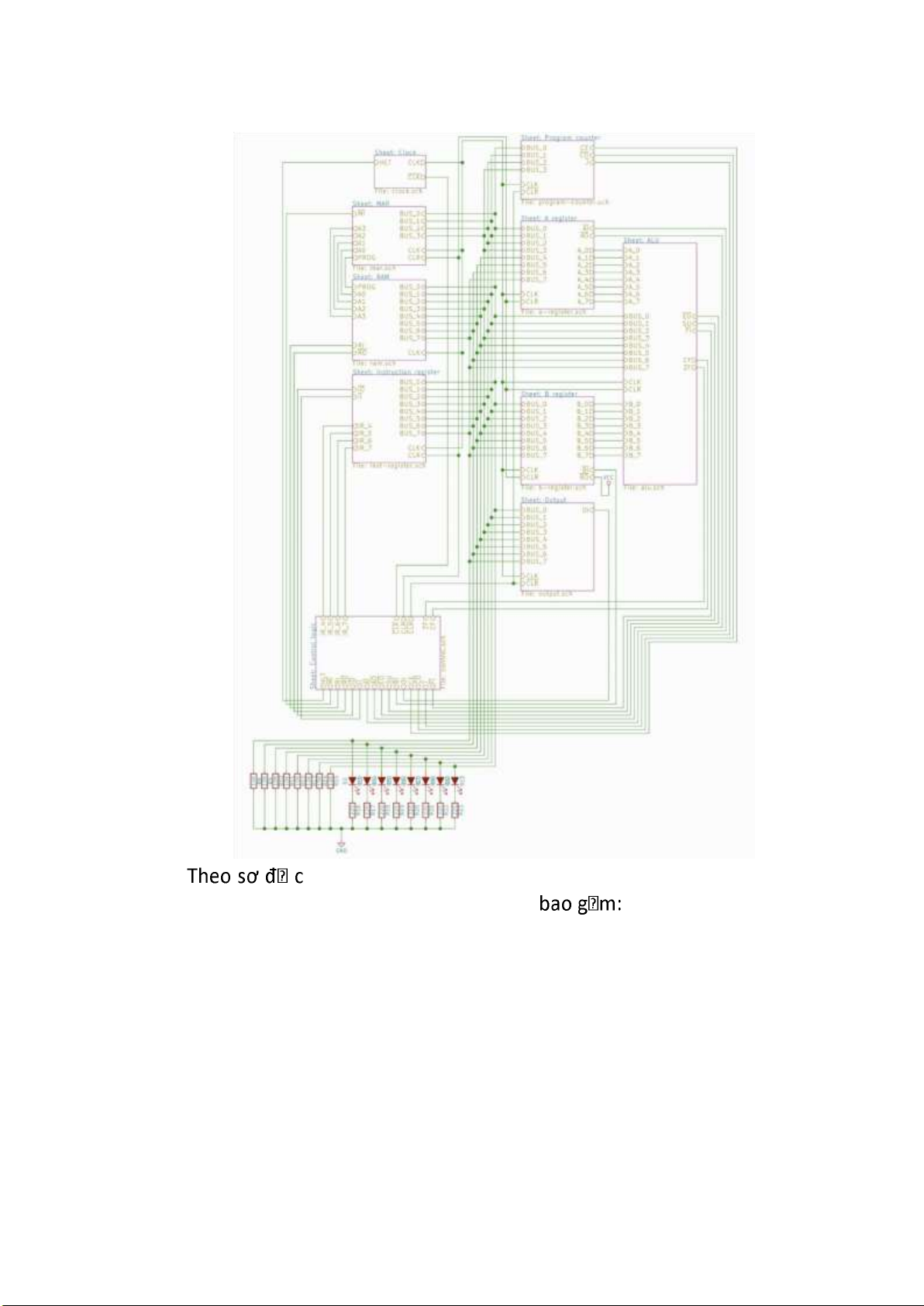

ấu trúc ở bên trên, chúng ta có thể thấy những thành phần

chính quan trọng của một máy tính 8-bit sẽ - Clock - ALU - RAM, ROM - CPU - Thanh ghi - Output

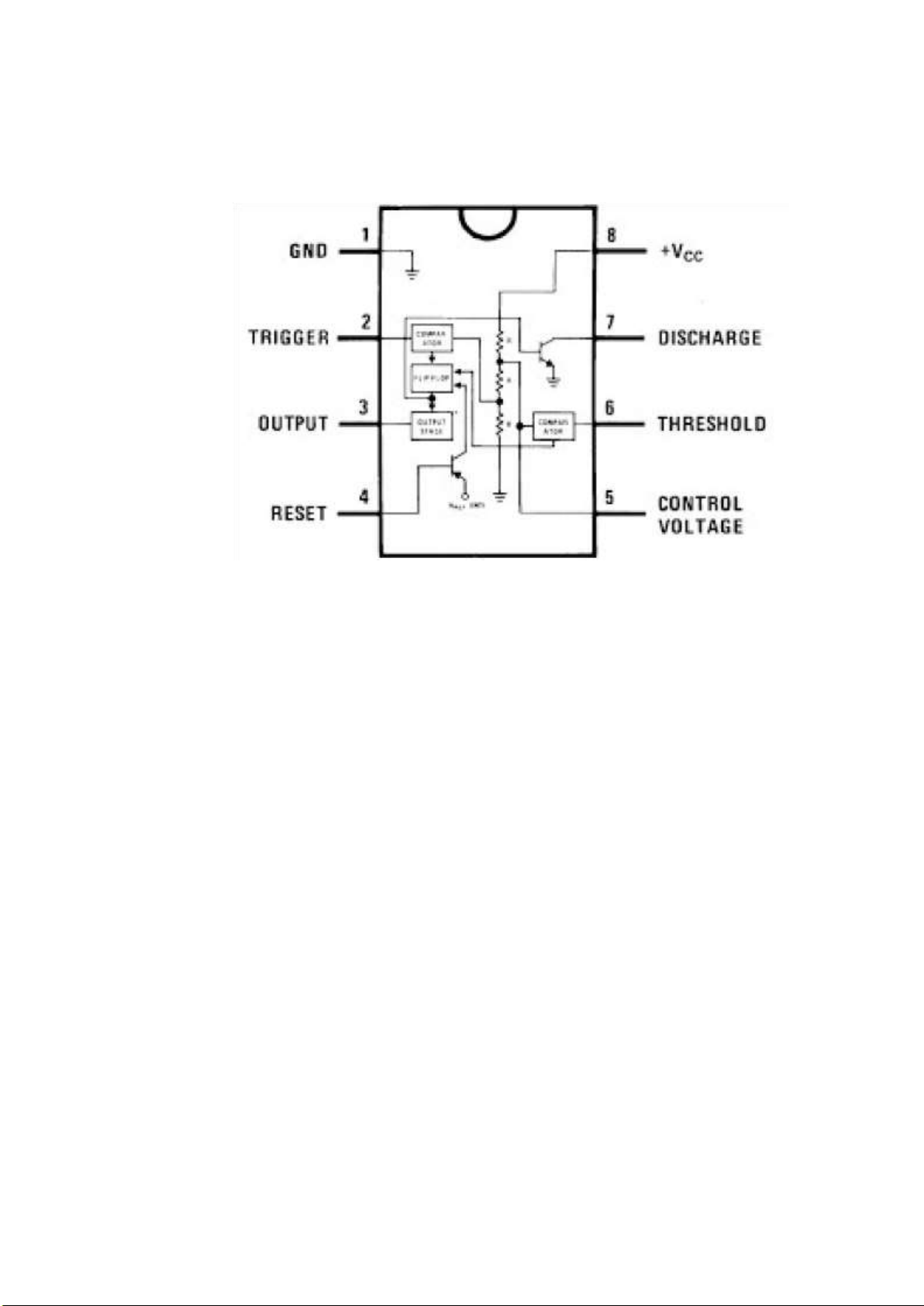

II. Danh s愃Āch linh kiêṇ 1. IC555 5 lOMoAR cPSD| 59908026

IC 555 là một dạng mạch tích hợp kỹ thuật số có thể được sử dụng như một bộ tạo xung nhịp.

Chân 1: “GND” là chân nối đất: Tất cả các mức điên áp đều được sọ

sánh với áp tại đường dây nối đất.

Chân 2: “Trigger” là chân kích: Chân trigger được dùng cung cấp đầu

vào kích cho IC555 hoạt đông ở chế độ đơn ổn. Chân này chuyển trạng thái tự̀

set sang reset của flip flop.

Chân 3: “Output” là chân xuất tín hiêu ra.̣ Chân

4: “reset” là chân reset vi mạch.

Chân 5: “Control voltage” là chân điên áp điều khiển.̣

Chân 6: “Thresohold” là chân ngưỡng: Nó là ng漃̀ vào không đảo của

bô so sánh 1, được so sánh với ng漃̀ vào đảo với điệ n áp tham chiếu là

2/3Vcc,̣ bô so sánh trên chuyển sang +Vsat và đầu ra được đặ t lại. ̣

Chân 7: “discharge” là chân xả điên.̣

Chân 8: “Vcc” là chân cấp nguồn: nguồn cung cấp trong từ 5V đến 18 V. 2. 74 LS 04 6 lOMoAR cPSD| 59908026

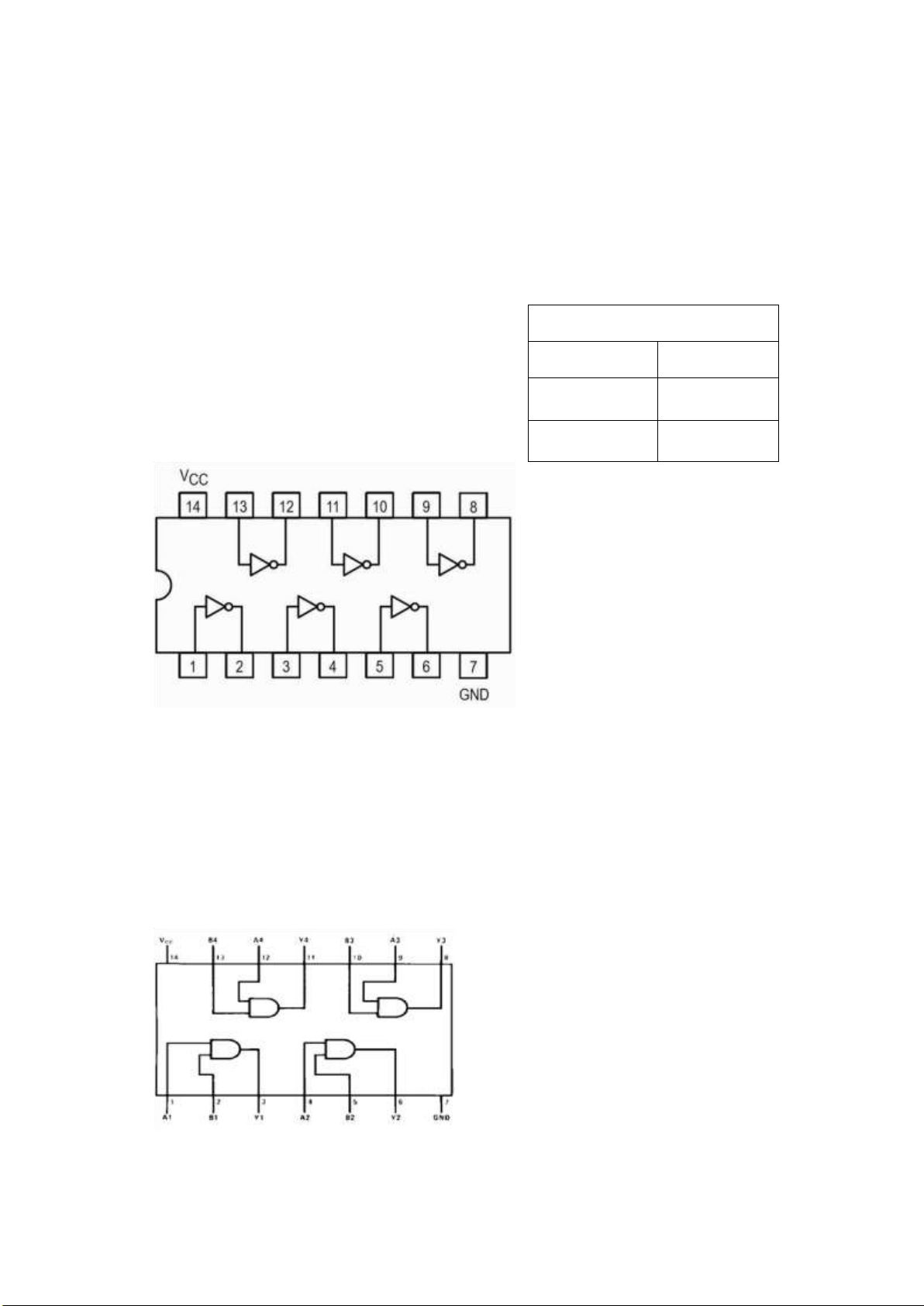

74 LS04 là IC cổng logic NOT 2 đầu vào 4x8bit. Bộ đảo trạng thái logic

là một linh kiện điện tử có chức năng cơ bản là đảo ngược giá trị logic đầu vào ra mức CAO hoặc THẤP. Bảng chân lý Đầu vào A Đầu ra Q 0 1 1 0 3. 74 LS 08

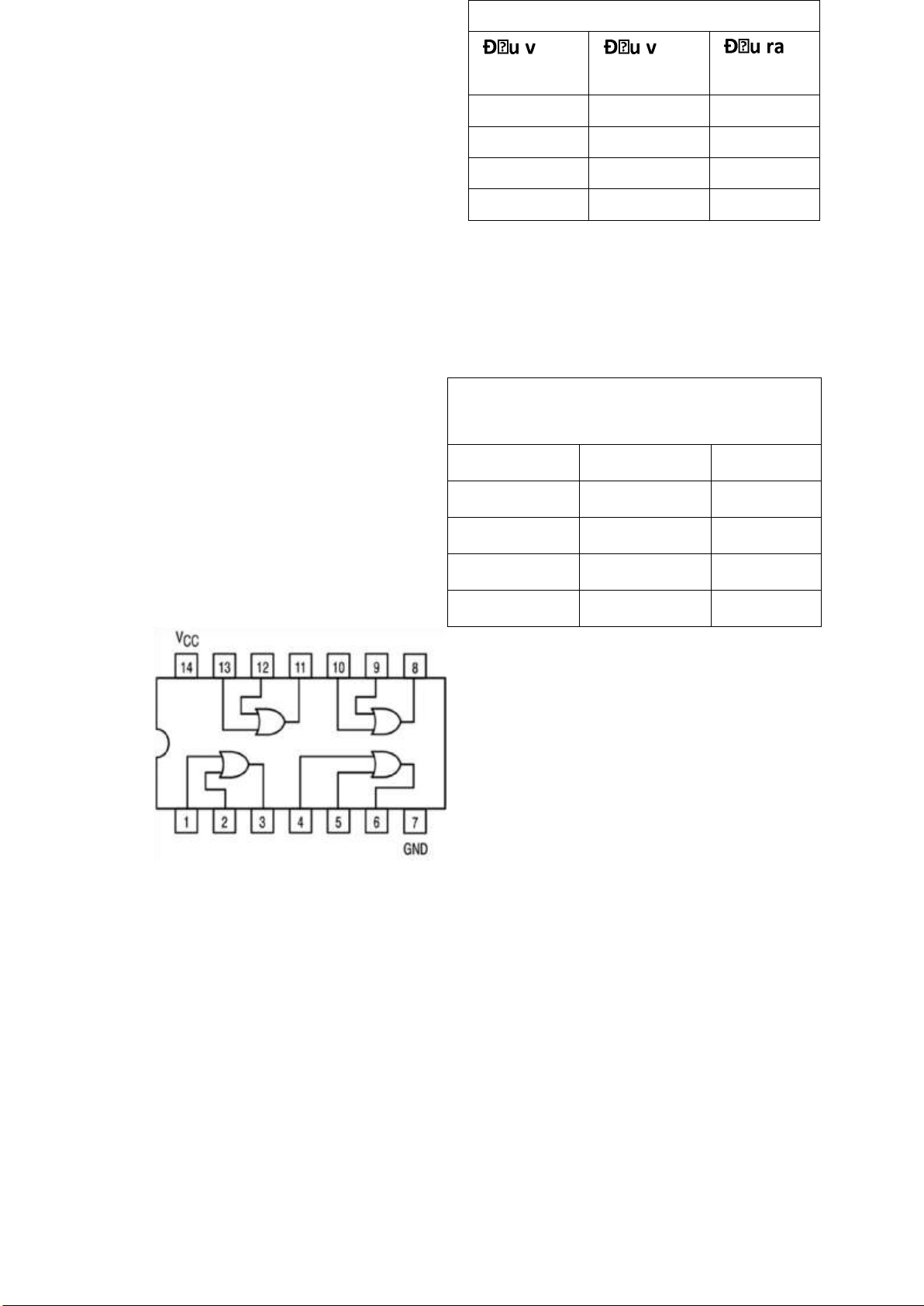

74LS08 là môt vi mạch logic cổ điển được thiết kế để thực hiệ n các ̣

phép toán logic AND với 4 đầu vào. Mỗi đầu vào đều cs thể có giá trị logic là

0 hoăc 1 và đầu ra tương ứng sẽ có giá trị logic 1 nếu cả 4 đậ̀ u vào đều là

logic 1. Ngược lại, nếu bất k礃 đầu vào nào có giá trị logic 0 thì đầu ra sẽ có giá trị logic 0. 7 lOMoAR cPSD| 59908026 Bảng chân lý 愃 o 愃 o A B Q 0 0 0 4. 74 LS 32 0 1 0

74 LS32 là cổng OR đầu vào 1 0 0

kép với gói Quad. Nó chứa bốn cổng 1 1 1

độc lập, mỗi cổng thực hiện chức

năng logic OR. Mỗi cổng có hai đầu vào, đó là lý do tại sao nó được đặt tên là

cổng OR đầu vào kép Quad. Bảng chân lý Đầu vào A Đầu vào B Đầu ra Q 0 0 1 0 1 0 1 0 0 1 1 0 5. 74 LS 245

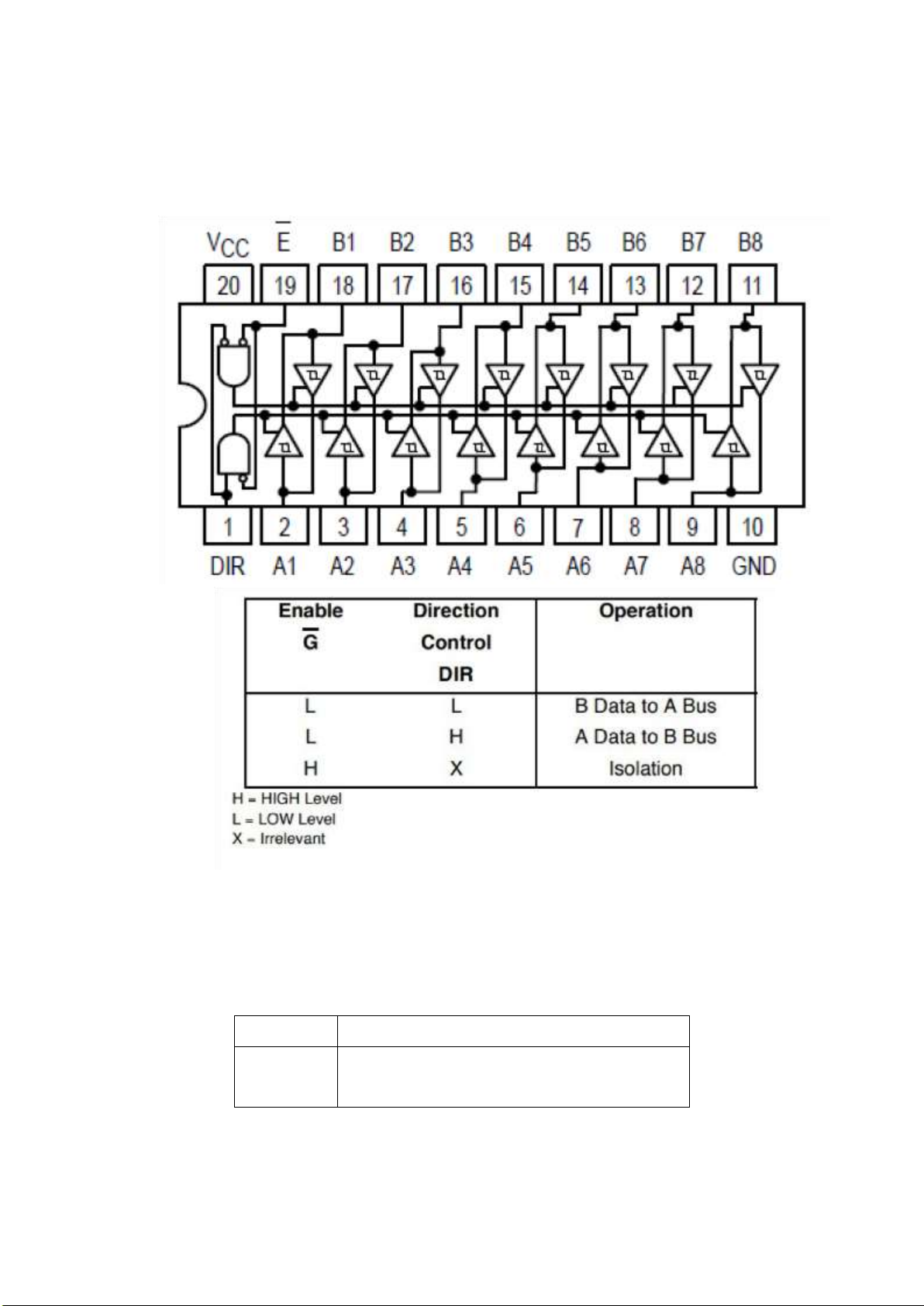

74 LS245 là IC thu phát bus bát phân được thiết kế để liên lạc hai chiều

không đồng bộ giữa các bus dữ liệu Việc triển khai chức năng điều khiển giảm

thiểu các yêu cầu về thời gian bên ngoài.

Thiết bị cho phép truyền dữ liệu từ bus A sang bus B hoặc từ bus B sang

bus A, tùy thuộc vào mức logic ở đầu vào điều khiển hướng (DIR). Đầu vào

kích hoạt đầu ra (OE) có thể vô hiệu hóa thiết bị để các bus được cách ly hiệu quả. 8 lOMoAR cPSD| 59908026

Sơ đồ chân 74LS245 (chân 19 OE Kích hoạt đầu ra thấp đang hoạt

động; Thấp = tất cả các kênh đang hoạt động, Cao = tất cả các kênh bị tắt (trở kháng cao) 6. 74 LS 173

74LS173A là mạch ghi loại D - 4bit tốc độ cao có đầu ra 3 trạng thái để

sử dụng trong các hệ thống được tổ chức bằng bus. Đồng hồ được kích hoạt

hoàn toàn ở cạnh cho phép tải từ đầu vào D hoặc giữ (giữ lại nội dung thanh

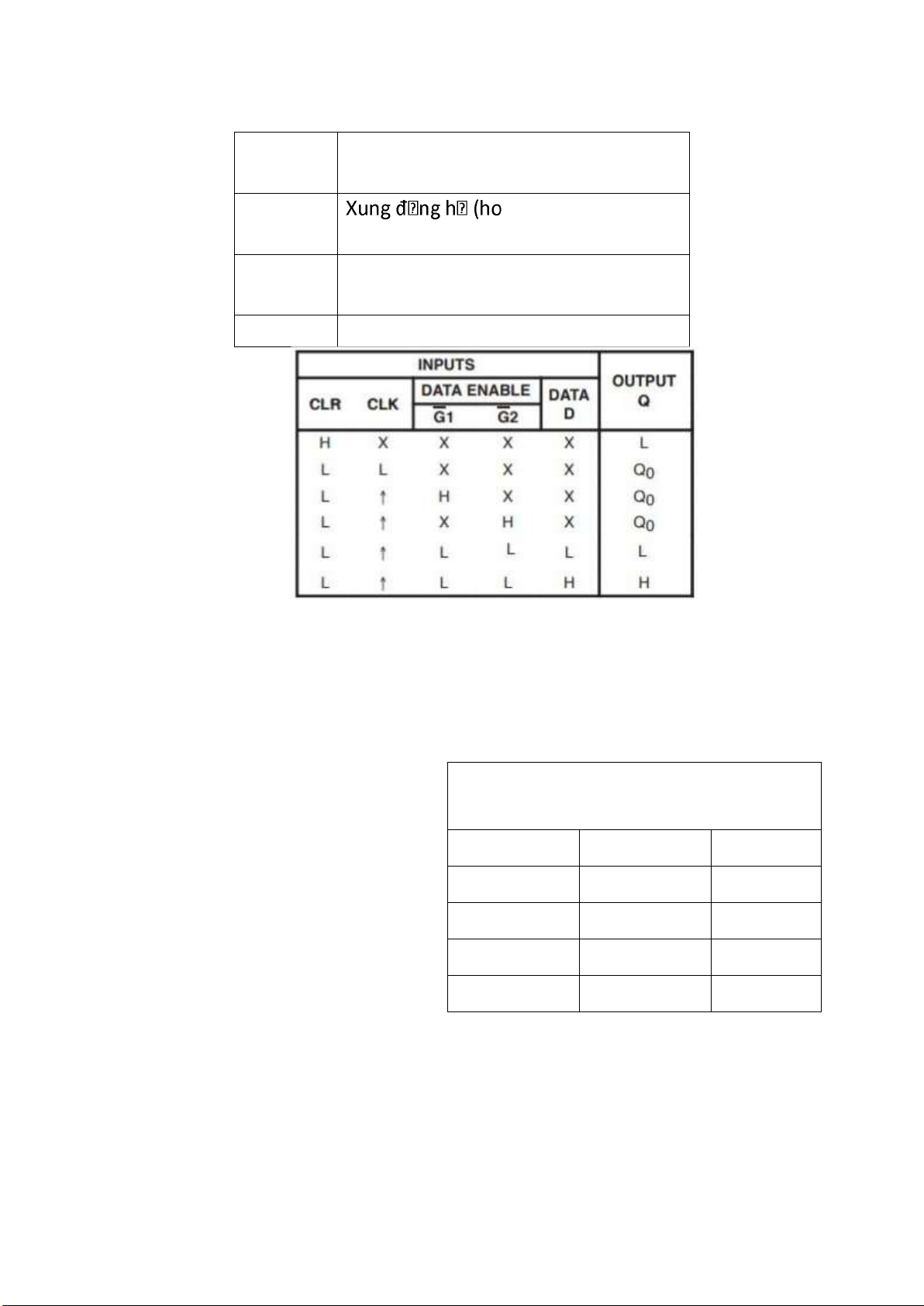

ghi) tùy thuộc vào trạng thái của Đường kích hoạt đầu vào (IE1, IE2). D0-D3 Đầu vào dữ liệu IE1-IE2

Kích hoạt đầu vào( hoạt động thấp) 9 lOMoAR cPSD| 59908026 OE1OE2

Kích hoạt đầu ra (hoạt động thấp) CP ạt động ở cạnh cao) MR

Đầu vào đặt lại chính (hoạt động cao) Q0-Q3 Đầu ra 7. 74 LS 86

74 LS86 tuân theo các cổng logic cơ bản AND, OR và NOT. Các

7486 bao gồm một mạch logic sử dụng hai cổng AND, hai cổng NOT và một

cổng OR. Cổng NOT sẽ được sử dụng tại các chân đầu vào và đồng thời đầu

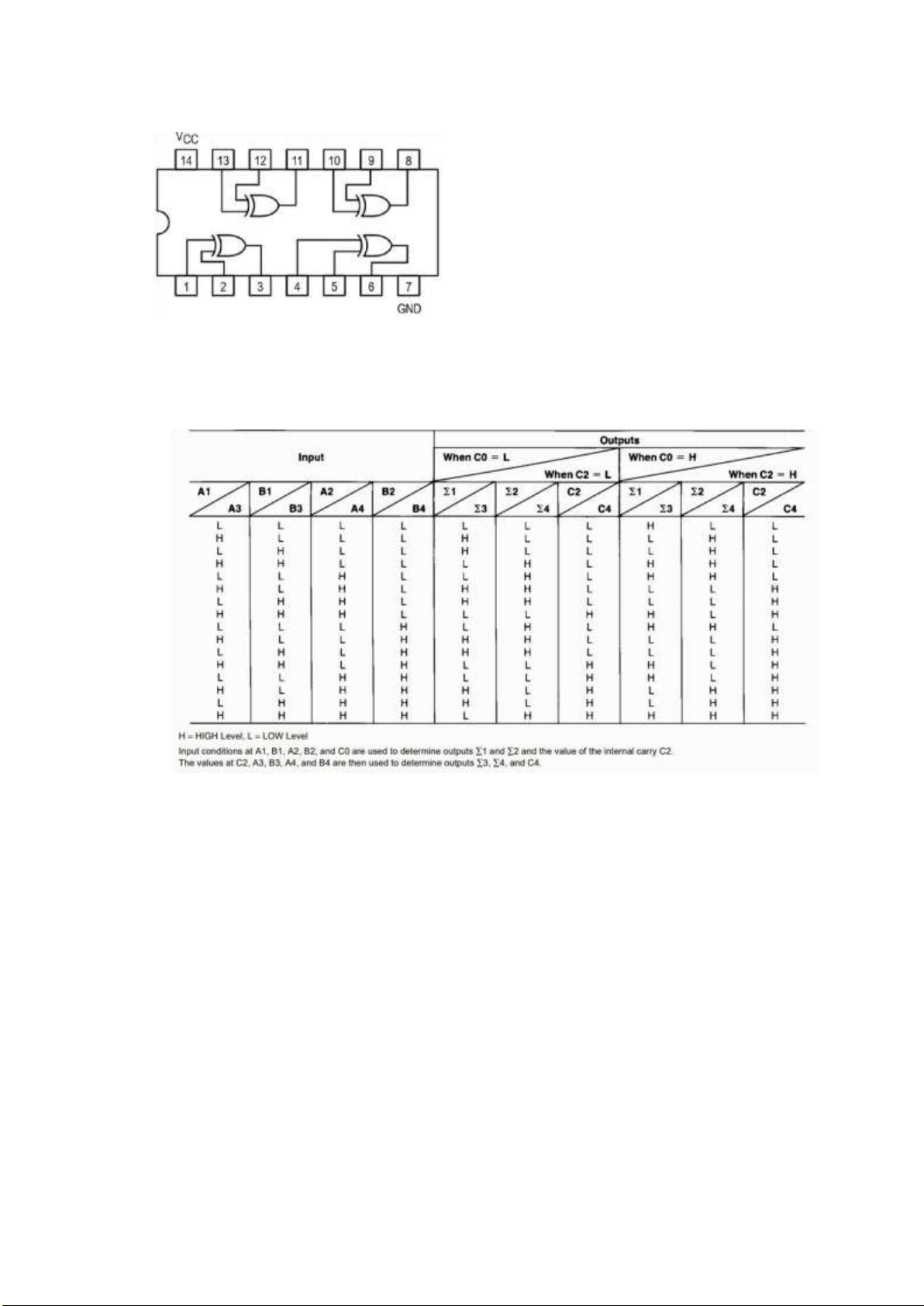

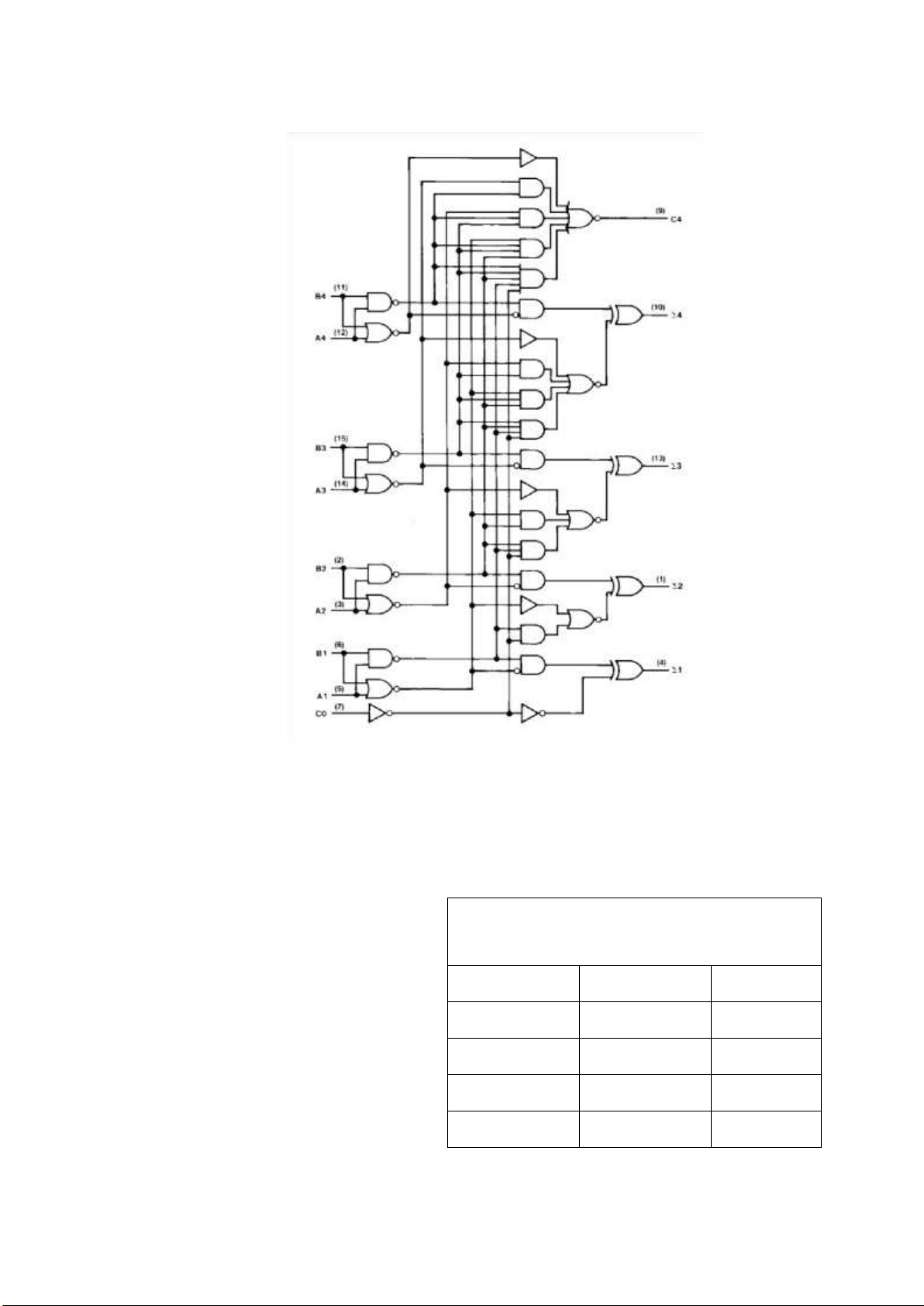

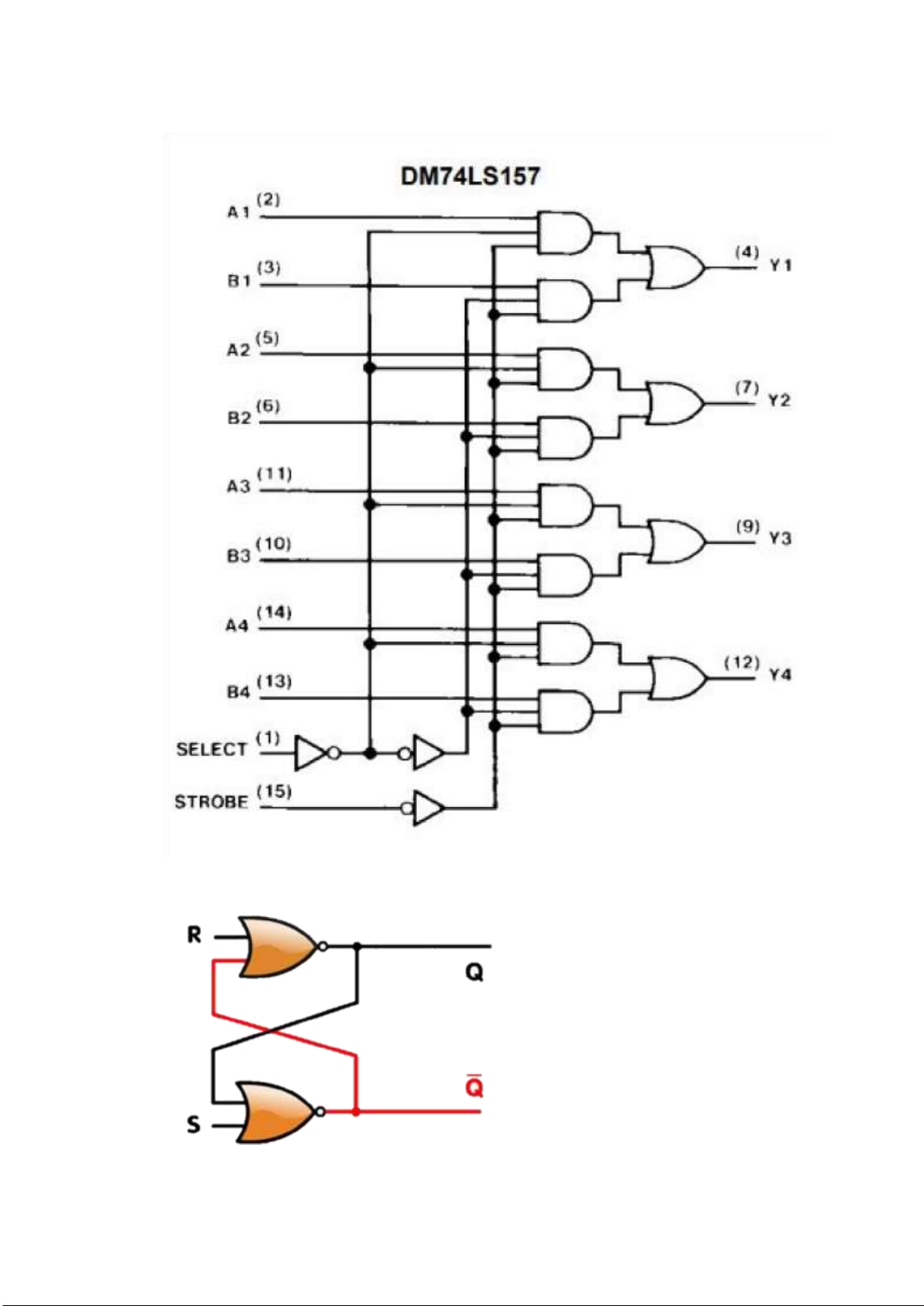

vào sẽ được cấp cho các cổng AND mà không cần đảo ngược. Bảng chân lý Đầu vào A Đầu vào B Đầu ra Q 0 0 0 0 1 1 1 0 1 1 1 0 10 lOMoAR cPSD| 59908026 8. 74 LS 283 11 lOMoAR cPSD| 59908026 9. 74 LS 00

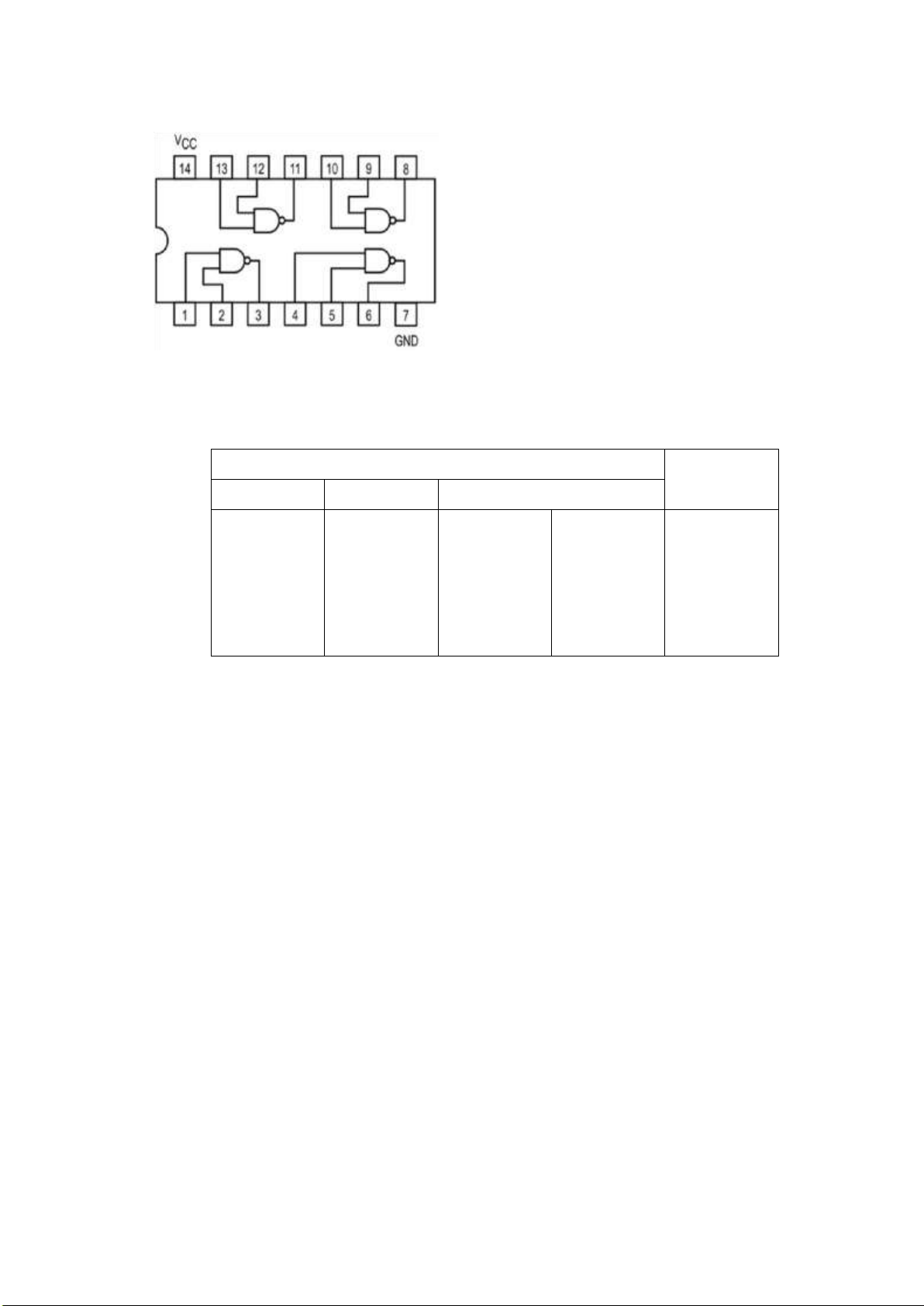

74LS00 là IC dựa trên cổng logic NAND. Nó có 14 chân, tất cả đều

được kết nối với 4 cổng NAND. Do cổng NAND được gọi là cổng đa năng, 74

LS00 có thể được chuyển đổi thành cổng OR và NOT một cách dễ dàng. Bảng chân lý Đầu vào A Đầu vào B Đầu ra Q 0 0 1 0 1 1 1 0 1 1 1 0 12 lOMoAR cPSD| 59908026 10.74 LS 157 In puts Output Strobe Select A B H X X X L L L L X L L L H X H L H X L L L H X H H 13 lOMoAR cPSD| 59908026 11. Flip – Flop D 14 lOMoAR cPSD| 59908026

Flip – Flop D là một thành phần rất đơn giản và dễ sử dụng trong xây

dựng mạch đếm. Với chỉ hai đầu vào (D và Clock) và hai đầu ra (Q và Q̅

), Flip – Flop D giúp giải quyết các vấn đề kỹ thuật một cách hiệu quả

và thuận tiện. Sự linh hoạt của nó cho phép tạo ra các mạch đếm và làm

cho việc tương tác với người dùng trở nên dễ dàng hơn bao giờ hết.

Flip – Flop D có hai đầu vào và hai đầu ra. - Đầu vào:

o D: Đây là đầu vào dữ liệu, nơi mà giá trị dữ liệu sẽ được lưu

trữ và kiểm soát bởi flip-flop.

o Clock (CLK): Đây là đầu vào xung đồng hồ. Khi một xung

clock được đưa vào flip-flop, nó sẽ xảy ra quá trình lưu trữ hoặc truyền dữ liệu. - Đầu ra:

o Q: Đây là đầu ra lưu trữ giá trị của đầu vào D sau khi xung

clock được kích hoạt. Giá trị lưu trữ được duy trì cho đến khi có xung clock tiếp theo.

o Q̅ : Đây là đầu ra đảo của Q, nghĩa là nếu giá trị của Q là 0

thì giá trị của Q̅ là 1 và ngược lại

Với hai đầu vào và hai đầu ra, Flip – Flop D rất phổ biến và được sử dụng

rộng rãi trong các mạch logic để lưu trữ và kiểm soát dữ liệu.

Flip – Flop D là một loại flip-flop đơn giản nhưng rất quan trọng. Nó có hai

đầu vào (D và Clock) và hai đầu ra (Q và Q̅ ) . Đầu vào D là đầu vào dữ

liệu và Clock là xung đồng hồ. Điều quan trọng cần nắm về Flip – Flop D

là khi xung clock tác động, giá trị của đầu vào D sẽ được lưu vào đầu ra Q.

Để làm được điều này, Flip – Flop D sử dụng nguyên tắc lưu trữ dữ liệu

vào một cầu nối khóa (latch).

Công thức hoạt động của Flip – Flop D như sau:

- Khi xung clock là 0, đầu ra của Flip – Flop D không thay đổi.

Khi xung clock là 1, đầu vào D sẽ được lưu vào đầu ra Q của Flip -Flop D

Đây là cách Flip – Flop D hoạt động một cách cơ bản. Nó được sử dụng 15 lOMoAR cPSD| 59908026

trong nhiều ứng dụng, như là một thành phần cơ bản để xây dựng các mạch

đếm và các mạch nhớ trong vi mạch và viễn thông.

CHƯƠNG 3: NGUYÊN LÝ HO愃愃T ĐÔNG CỦA M愃ĀY ̣ T䤃ĀNH 8 BIT I. Bus

BUS được sử dụng để kết nối tất cả các mô-đun bộ xử lý cho phép các

thành phần giao tiếp với nhau.

Thông thường có nhiều hơn 1 bus trong bộ xử lý, như BUS dữ liệu, BUS

địa chỉ, BUS điều khiển, v.v. Đối với phiên bản bộ xử lý đầu tiên, tôi chỉ sử

dụng 2 BUS, một cho dữ liệu và một cho điều khiển. II. 1. Linh kiên sử dụng ̣ - IC555 - 74 LS 04 - 74 LS 08 - 74 LS 32 - Led

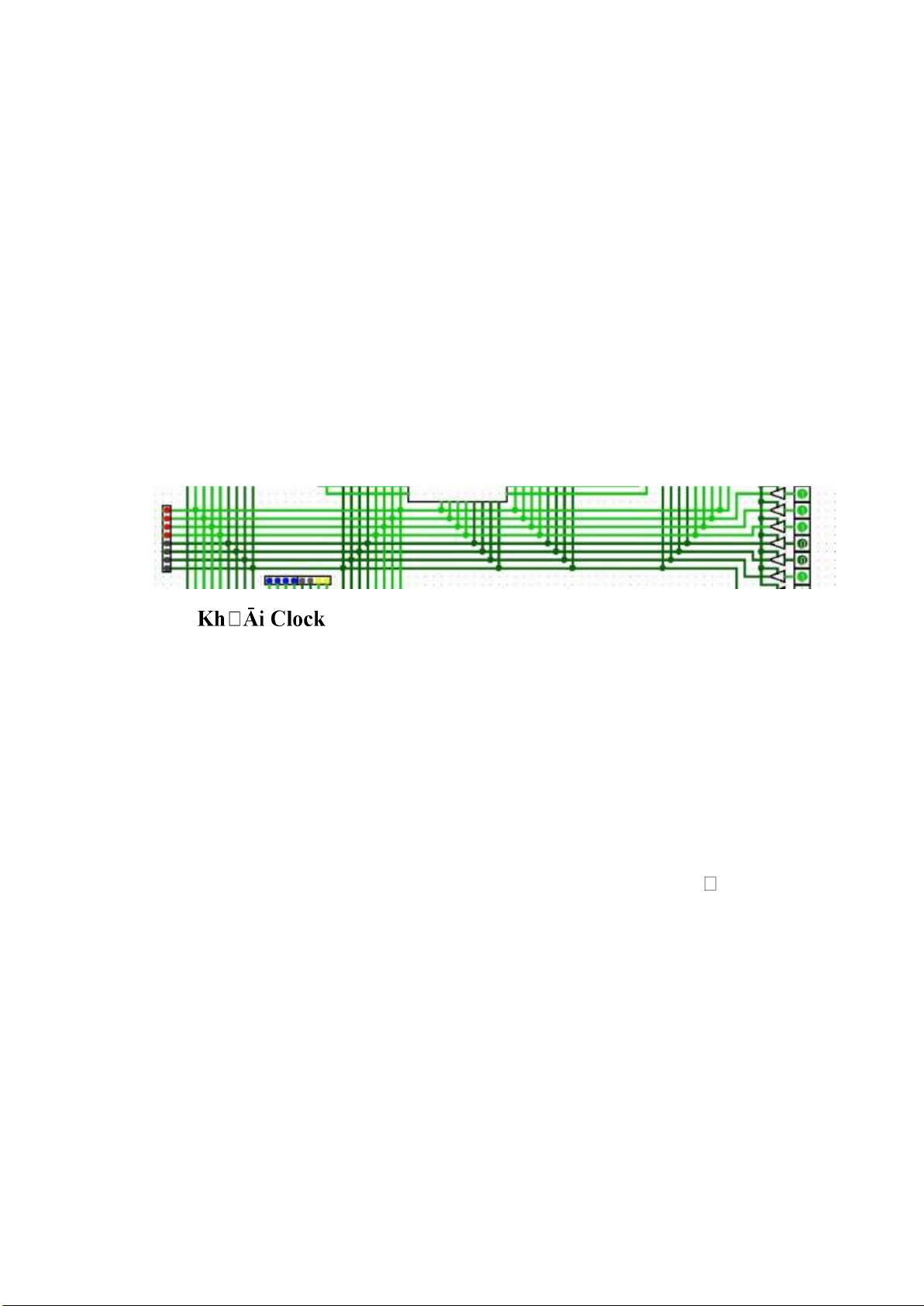

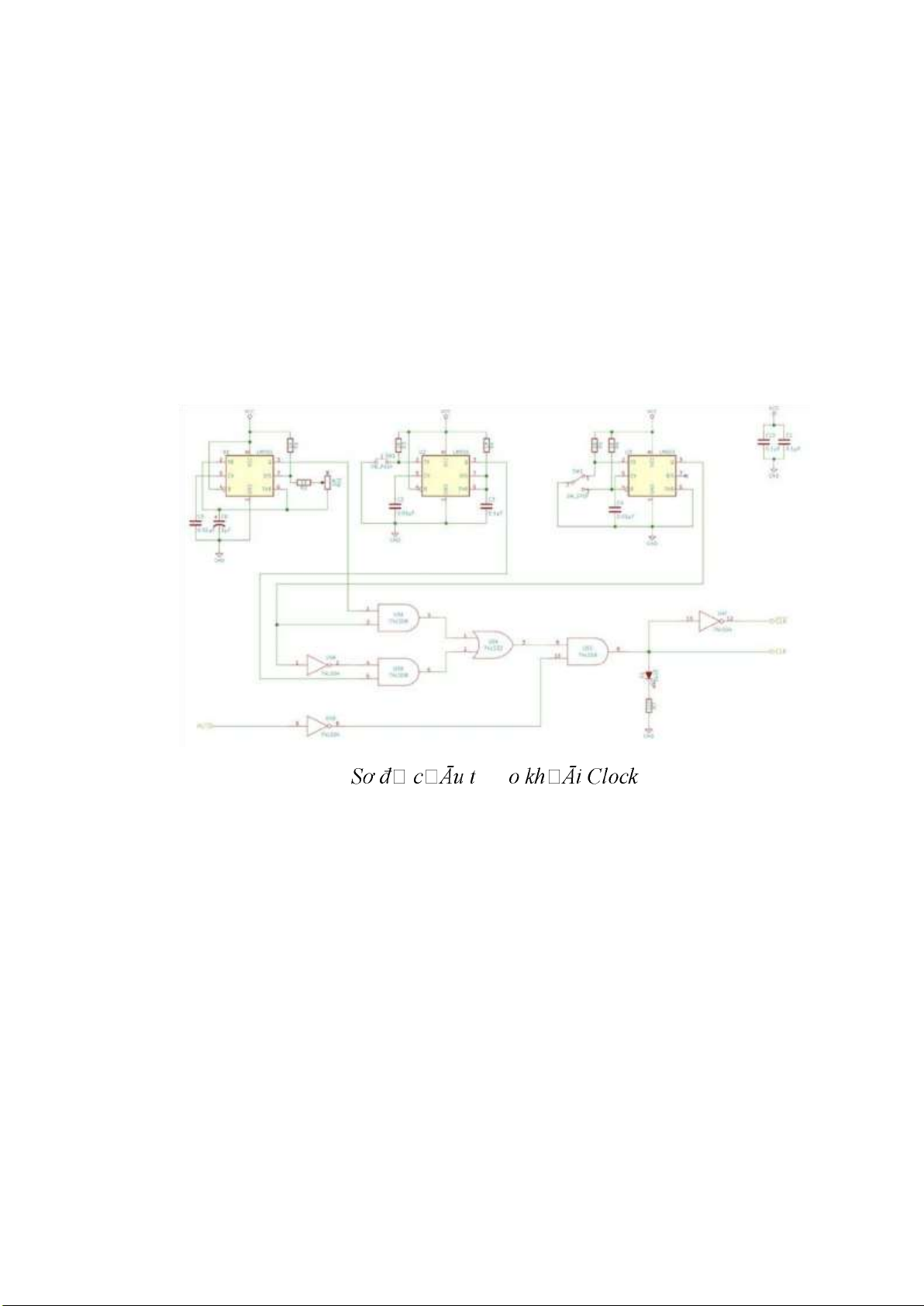

2. Nguyên lý hoạt đông ̣

Để xây dựng mạch clock ổn định, chúng ta cần công tắc nút ấn. Có thể

nhấn nút này và chúng ta nhân được 1 đầu ra logic thoát D chu 漃n và sau đó ̣

xây dựng mạch ổn định. Ta cần kết hợp 3 tín hiêu thành 1 tín hiệ u đầu ra chọ

mạch clock và xuất tín hiêu dao độ ng. Tín hiệ u tạo bằng nút nhấn của chúng ̣

ta tùy thuôc vào việ c chúng ta chọn đ漃n nối với ic nào sáng.̣

Khối clock của máy tính được sử dụng để đồng bộ hóa mọi hoạt

động. Clock được xây dựng dựa trên IC định thời 555. Clock có thể điều

chỉnh tốc độ (từ dưới 1Hz đến vài trăm Hz). Nó cũng có thể được đặt ở

chế độ thủ công trong đó chúng ta có thể nhấn nút để tăng từng chu k漃

đồng hồ. Đây sẽ là một tính năng thực sự hữu ích cho việc gỡ lỗi máy tính sau này. 16 lOMoAR cPSD| 59908026

Chúng em đã xây dựng 1 bô định thời 555 để phát ra xung đồng ̣

thời dao đông này và chúng em đã xây dựng 1 bộ dịnh thời 555 cung ̣

cấp cho công tắc nút nhấn (4 chân) cân bằng D. Nút bấm và chúng em

nhân được 1 đầu ra logic thoát D ổn định. Điều này mang lại cho chúng ̣

em môt đầu ra ổn định việ c gỡ rối cho công tắc bậ t tắt (6 chân) củạ

chúng em bây giờ. Những gì chúng em cần làm là kết hợp 3 tín hiêụ đầu

ra clock và điều chúng em muốn là xuất tín hiêu dao độ ng (xung ̣ vuông)

hoăc tín hiệ u thủ công (0 hoặ c 1) của chúng em tùy thuộ c vàọ lựa chọn

của em. Khi có đầu vào xung ổn định, chúng em ấn nút thủ công thì sẽ

xuất hiên xung thủ công.̣ 愃⌀ III. Thanh ghi 1. Linh kiên sử dụng ̣ - 74 LS 245 - 74 LS 173 - Led - Trở 220Ω - Tụ 0,1µF

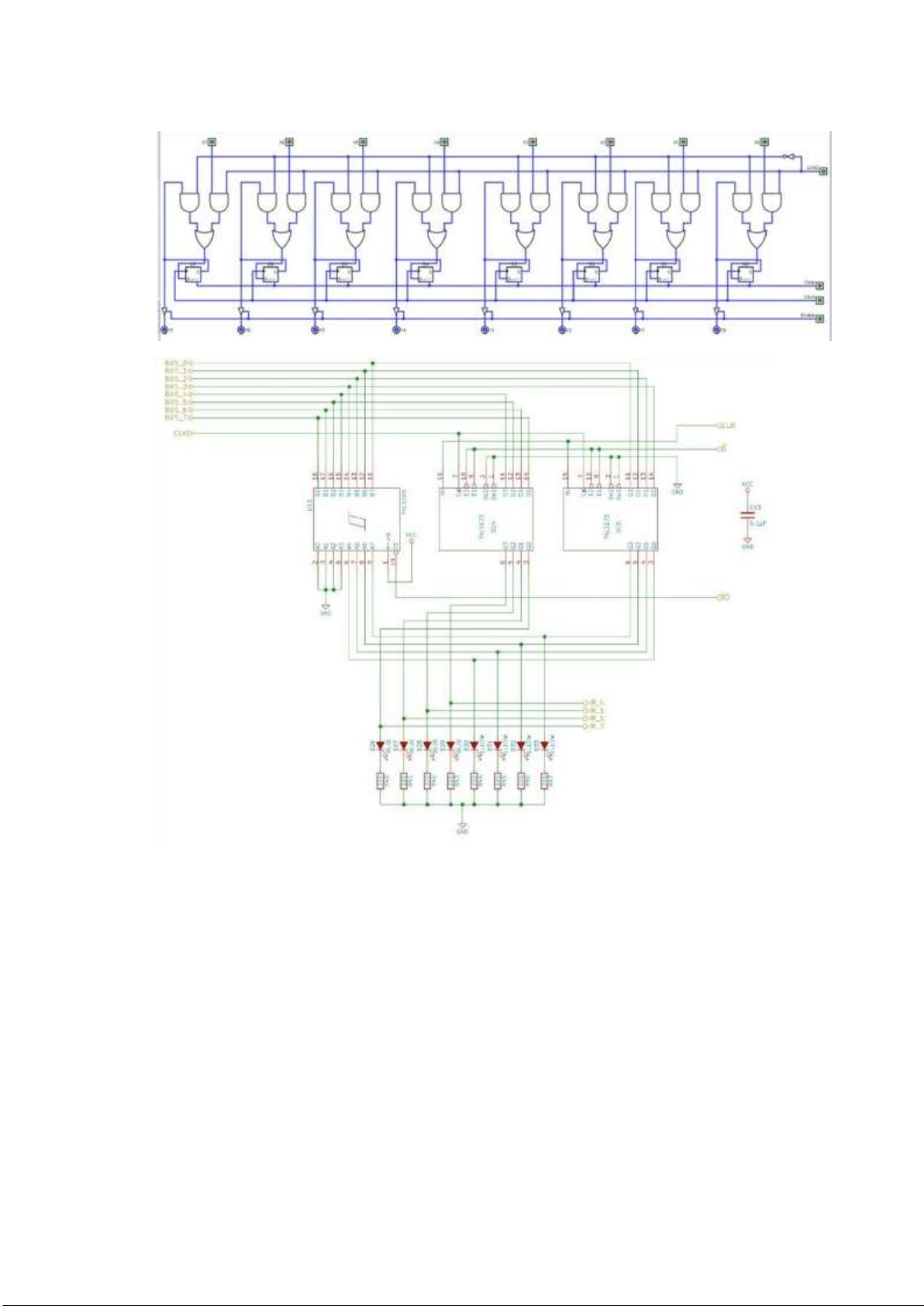

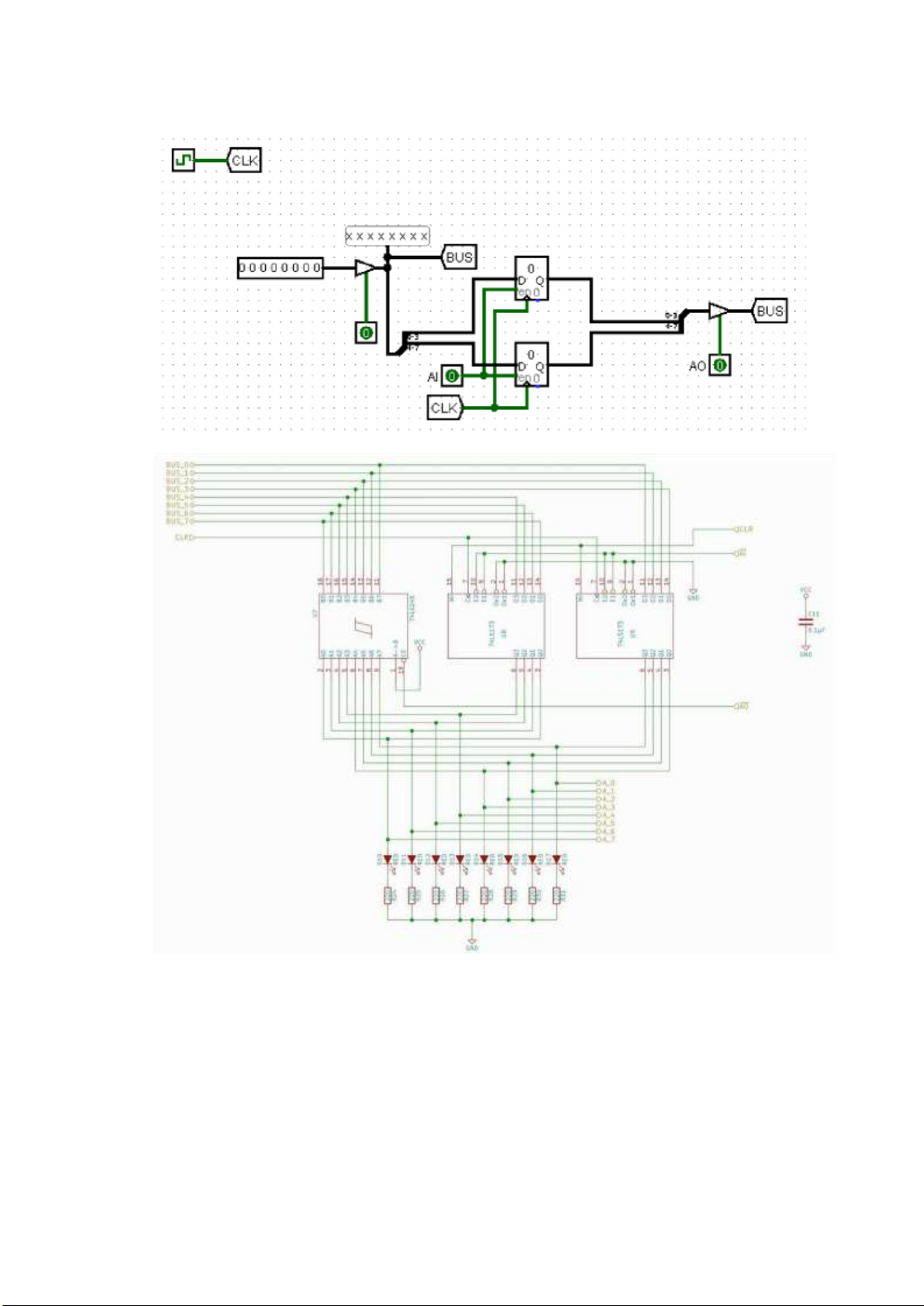

2. Nguyên lý hoạt đông ̣

Thanh ghi là một bộ xử lý có nhiệm vụ lưu trữ thông tin. Trong trường

hợp của chúng tôi, thanh ghi 8 bit sẽ lưu trữ một số 8 bit.

Thanh ghi hoạt động bằng cách sử dụng flip-flop D để lưu trữ một chút.

Mỗi thanh ghi 8 bit sử dụng flip-flop 8 D để lưu trữ một byte (8 bit). 17 lOMoAR cPSD| 59908026

Bộ xử lý này sẽ sử dụng 6 thanh ghi:

- Thanh ghi bộ đếm chương trình (Program Couter)

- Thanh ghi A kết nối với ALU

- Thanh ghi B được kết nối với ALU - Thanh ghi lênh (IR)̣

- Thanh ghi địa chỉ bộ nhớ (MAR)

- Thanh ghi đầu ra (Output Register)

Hầu hết các CPU đều có một số thanh ghi lưu trữ lượng nhỏ dữ liệu mà

CPU đang xử lý. Trong CPU bảng mạch đơn giản của chúng tôi, chúng tôi sẽ

xây dựng ba thanh ghi 8 bit: A, B và IR. Các thanh ghi A và B là các thanh ghi

đa năng. IR (thanh ghi lệnh) hoạt động tương tự, nhưng chúng ta sẽ chỉ sử dụng

nó để lưu trữ lệnh hiện tại đang được thực thi.

Xây dựng thanh ghi 8 đầu vào kết nối với bus có thể lưu trữ 1 giá trị trong

chuỗi số 1 và số 0. Nó được kết nối trong thanh ghi A và nó có thể gửi giá trị

đó ra bus khi đầu vào kích hoạt ở mức thấp do đó, bất k礃 giá trị nào cũng được lưu trữ.

Nếu thấp: bị ngắt kết nối khối nguồn Dòng kích hoạt này lên cao thì bất

k礃 giá trị nào của chuỗi số 1 và số 0 sẽ được lưu trữ trong thanh ghi A và được

xuất ra bus và các thanh ghi còn lại cũng sẽ thấy cùng 1 chuỗi số 1 và số 0. Và

các thanh ghi còn lại có thể chọn lưu giá trị đó vào bô nhớ lưu trữ riêng ̣ của mình.

Khi đầu vào tăng cao tại thời điểm mức thấp lên mức cao thì bất k礃 giá

trị nào trên bus sẽ lưu trữ trong C và sau đó tải có thể xuống mức thấp thì cũng

không làm thay đổi đến bus. Vì những giá trị đó đã được lưu trữ trong thanh

ghi C cho đến khi về cơ bản chúng em đã chuyển giá trị từ A -> C để có thể

nhân 1 giá trị khác. Bus C sẽ ghi nhớ giá trị đó. Sau đó nó có ̣ thể được kích

hoạt để hợp lại giá trị vào bus. Thanh ghi lênḥ 18 lOMoAR cPSD| 59908026 Thanh ghi A và B 19 lOMoAR cPSD| 59908026

IV. Arithmetic logic unit (ALU) 1. Linh kiên sử dụng ̣ - 74 LS 86 - 74 LS 245 - 74 LS 283 20