Preview text:

lOMoAR cPSD| 58493804

TRƯỜNG ĐẠI HỌC CẦN THƠ TRƯỜNG BÁCH KHOA

BÁO CÁO THỰC HÀNH MẠCH XUNG (KC119E)

Đồ án 2: Mạch chống dội bàn phím dùng 2 cổng đảo. Hãy

chứng tỏ rằng khi sử dụng mạch này thì hạn chế được xung

dội contact (dùng IC74164).

Giảng Viên Hướng Dẫn:

Ths.Dương Thái Bình Nhóm sinh viên thực hiện:

Lê Quốc Nam – B2207478

Lê Minh Mẫn – B2207476

Lê Quang Minh – B2207477

Mai Thành Đạt – B2207459

Ngành: Kỹ thuật máy tính – A1 Khóa: 48 lOMoAR cPSD| 58493804

Nội dung báo cáo thực hành Mạch Xung

Đồ án 2: Mạch chống dội bàn phím dùng 2 cổng đảo. Hãy chứng tỏ rằng khi dùng

mạch này hạn chế được xung dội contact (dùng IC74164). lOMoAR cPSD| 58493804

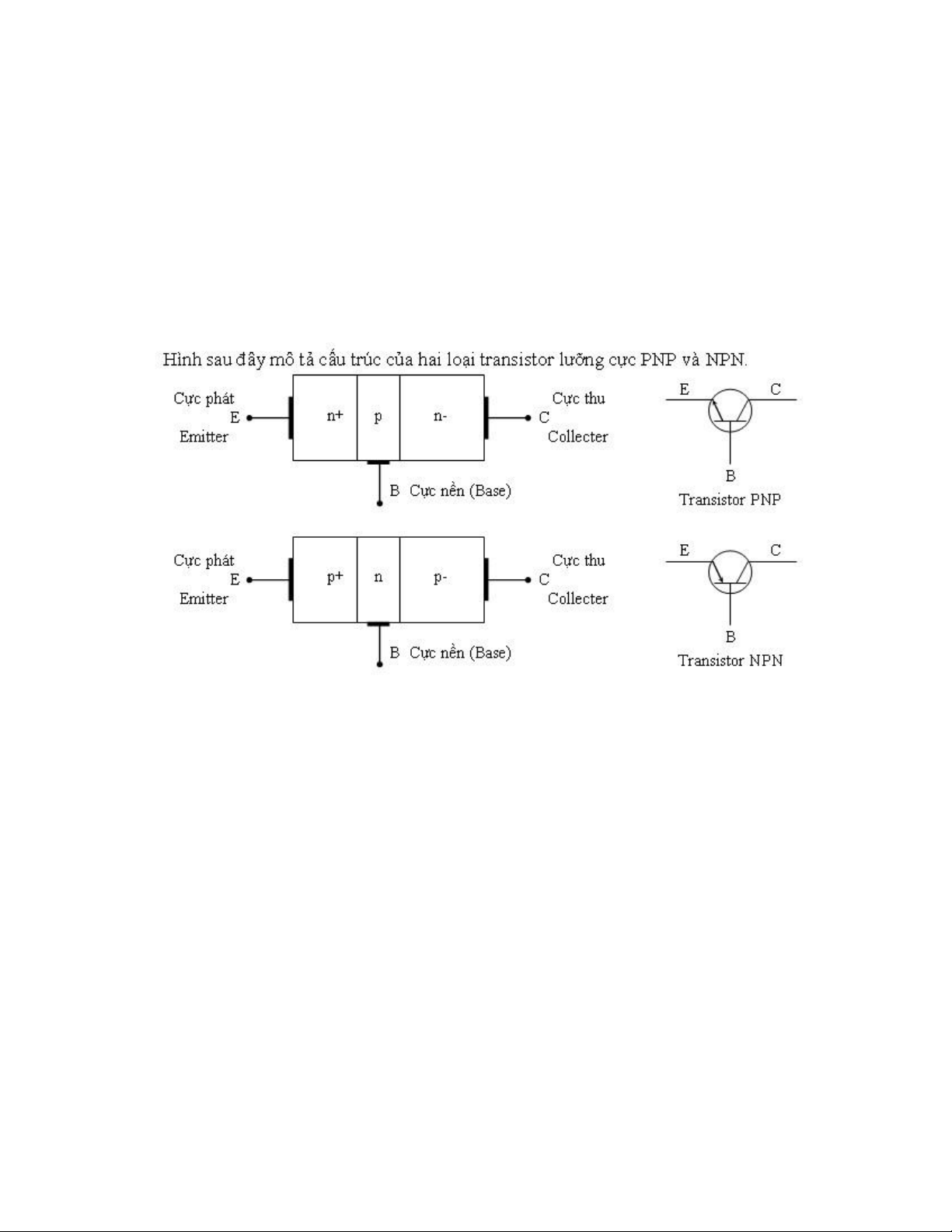

I. Mô phỏng đặc tuyến (V-I) của một transistor lưỡng cực – BJT. (có thể kham

khảo giáo trình linh kiện điện tử, mạch điện tử, linh kiện bán dẫn...). 1.

Cấu tạo cơ bản của Transistor lưỡng cực (BIPOLAR JUNCTION

TRANSISTOR). Transistor lưỡng cực gồm có hai mối P-N nối tiếp nhau, được phát

minh năm 1947 bởi 2 nhà bác học W.H Britain và J.Braden, được cấu tạo trên cùng

một mẫu bán dẫn Germanium hay Silicium.

Transistor gồm 3 lớp bán dẫn loại P và loại N ghép lại với nhau. Do đó có hai loại

transistor là NPN và PNP tương ứng với 2 cách sắp xếp 3 lớp bán dẫn trên. Như

hình vẽ, transistor có 3 cực là B (Base), C (Collector) và E (Emitter) tương ứng với 3 lớp bán dẫn. 2.

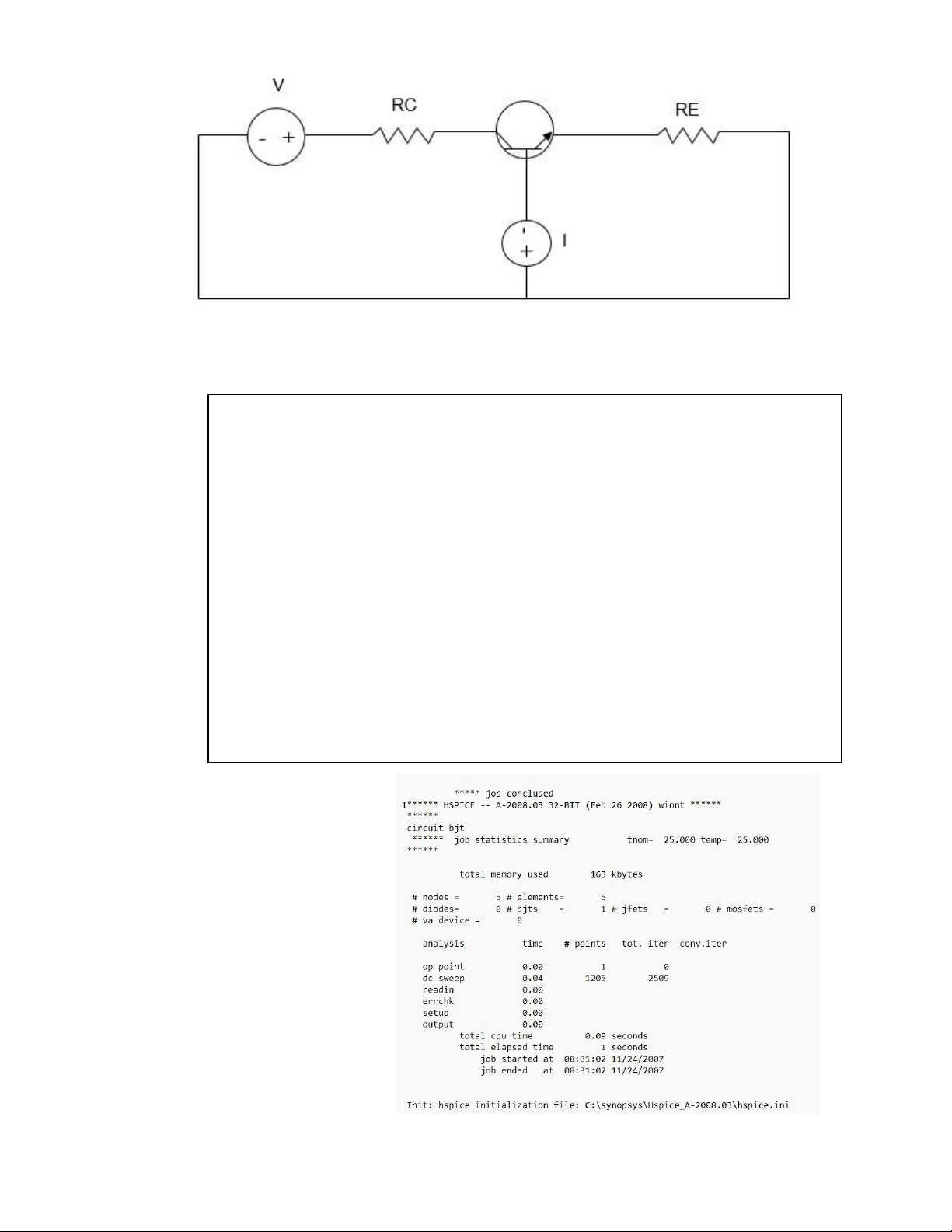

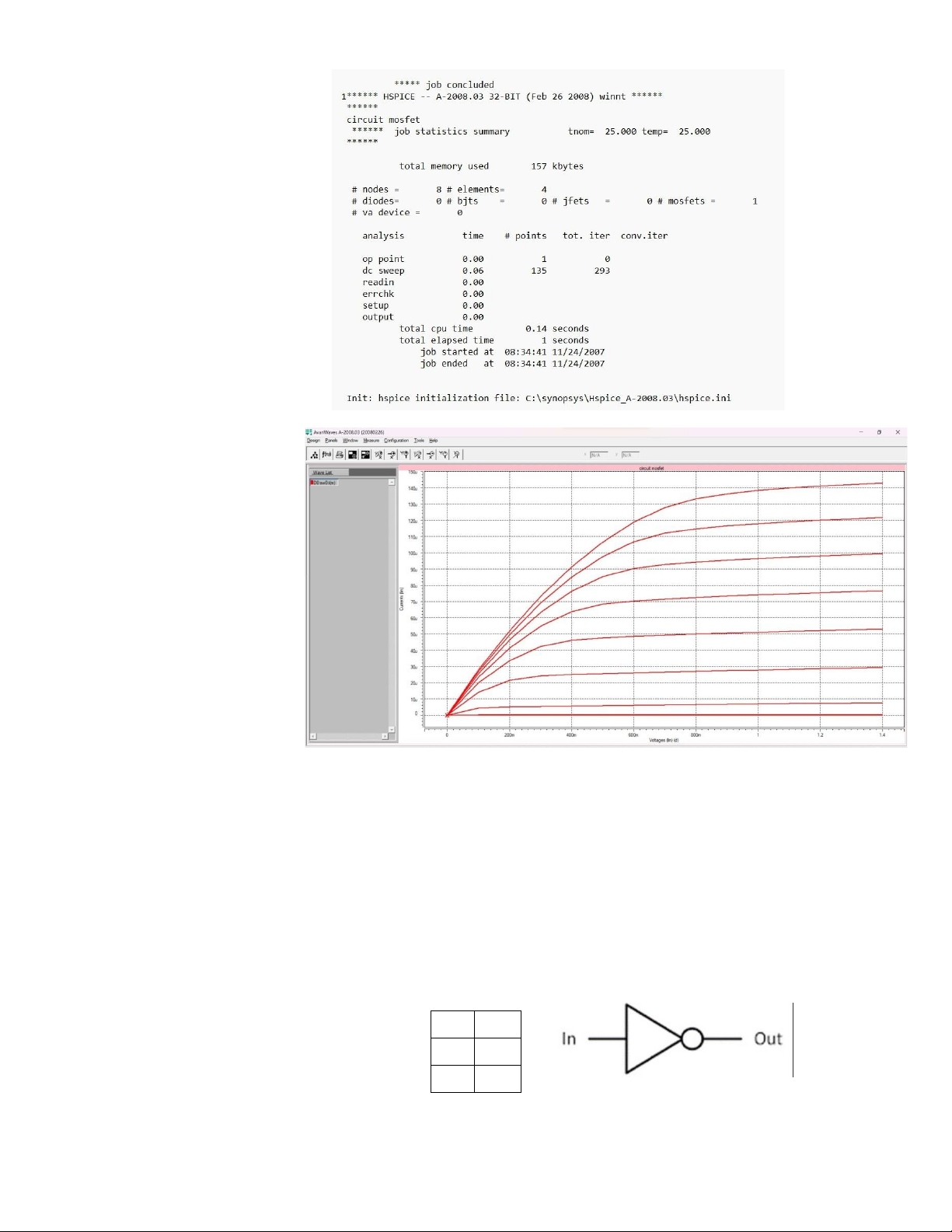

Đặc tuyến V-I của Transistor

Người ta thường chú ý đến 3 loại đặc tuyến của transistor: - Đặc tuyến ngõ vào - Đặc tuyến ngõ ra - Đặc tuyến truyền

Trong đó đặc tuyến ngõ ra mắc kiểu cực phát chung là biểu diễn dòng điện cực

thu IC theo điện thế ngõ ra VC với ngõ vào IB .

Dạng đặc tuyến như sau ( mô phỏng bằng Hsipce): lOMoAR cPSD| 58493804 Ảnh minh họa.

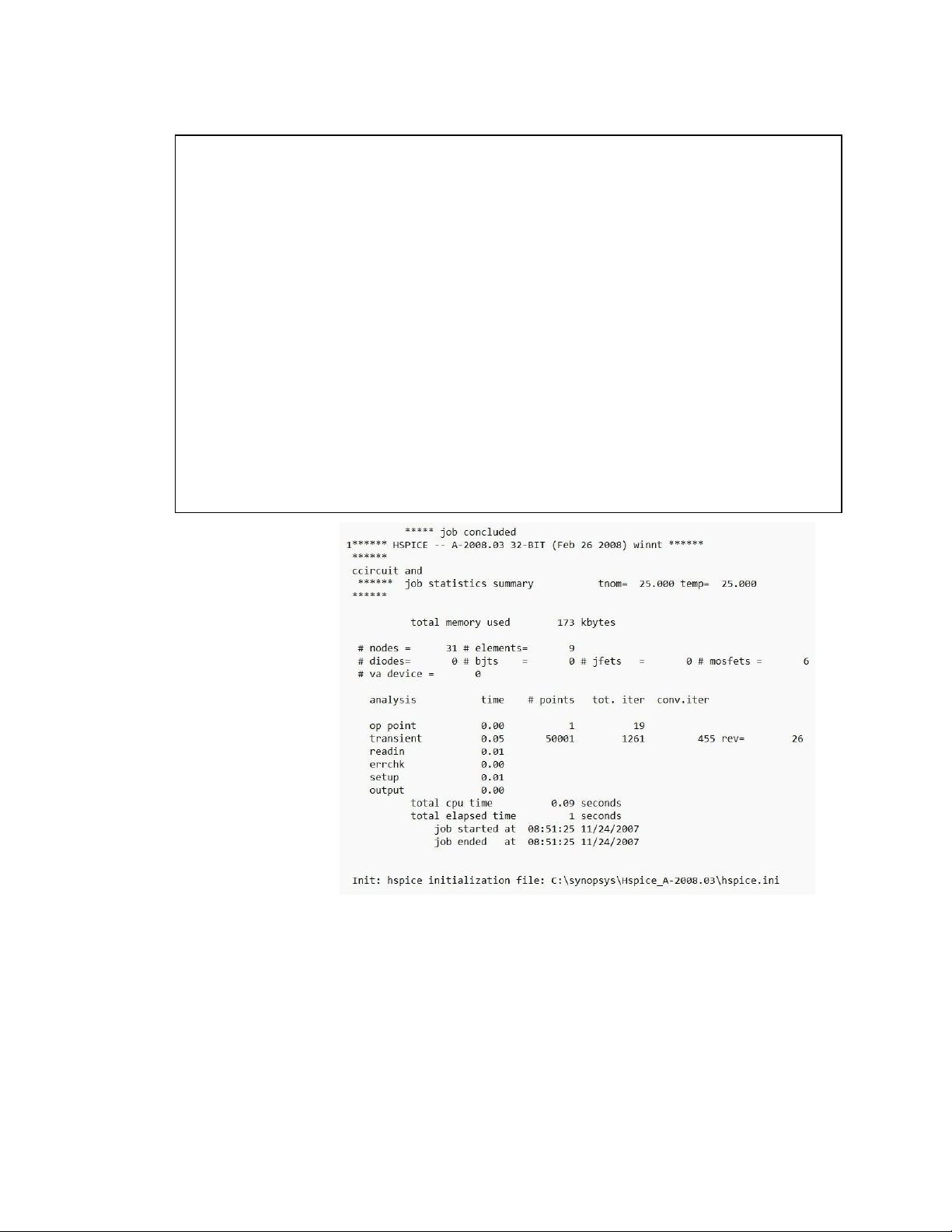

- Chương trình mô phỏng: Circuit BJT .option post V 1 gnd DC RC 1 c 5k Q c b e NPN I gnd b 7.5u RE e gnd 1k .model NPN NPN

.DC V 0 12 0.05 I 1.5u 7.5u 1.5u .plot I(RC), V(c, e) .end - Kết quả mô phỏng: - Tín hiệu mô phỏng: lOMoAR cPSD| 58493804

Ta thấy cũng có 3 vùng hoạt động của transistor: vùng bão hòa, vùng tác động và vùng ngưng.

Khi nối tắt VBE (tức IB = 0) dòng điện thu xấp xĩ dòng điện rĩ ICEO.

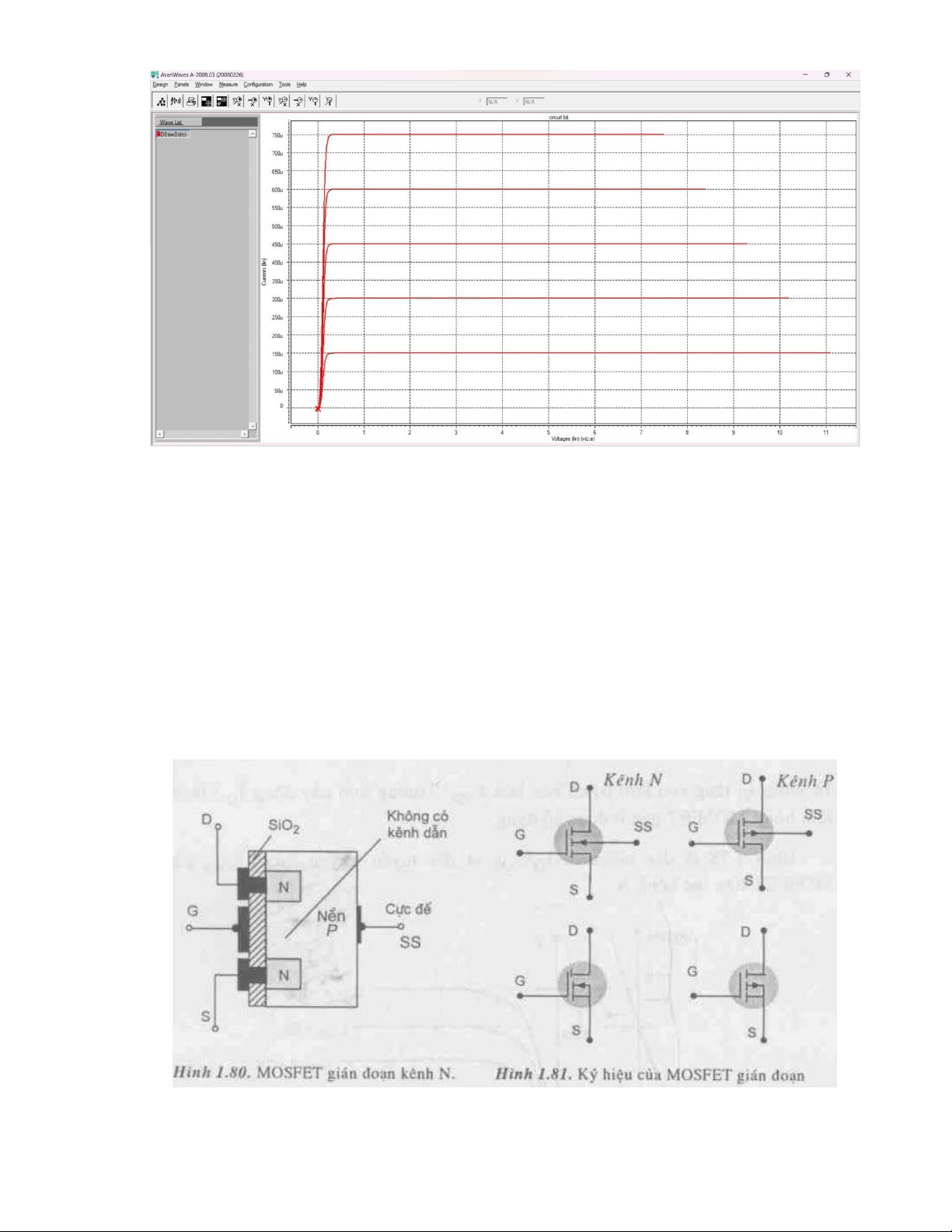

II. Với công nghệ chế tạo tùy chọn (vd: công nghệ 90nm). Mô phỏng đặc tuyến

(V-I) của một transistor MOSFET.

Transistor hiệu ứng trường kim loại - oxit bán dẫn, viết tắt theo tiếng Anh là

MOSFET (metal-oxide-semiconductor field-effect transistor) là thuật ngữ chỉ các

transistor hiệu ứng trường FET được xây dựng dựa trên lớp chuyển tiếp Oxit Kim

loại và bán dẫn (ví dụ Oxit Bạc và bán dẫn Silic) tạo ra lớp cách điện mỏng giữa

cực cổng (gate) kim loại với vùng bán dẫn hoạt động nối giữa cực nguồn (source) và cực máng (drain).

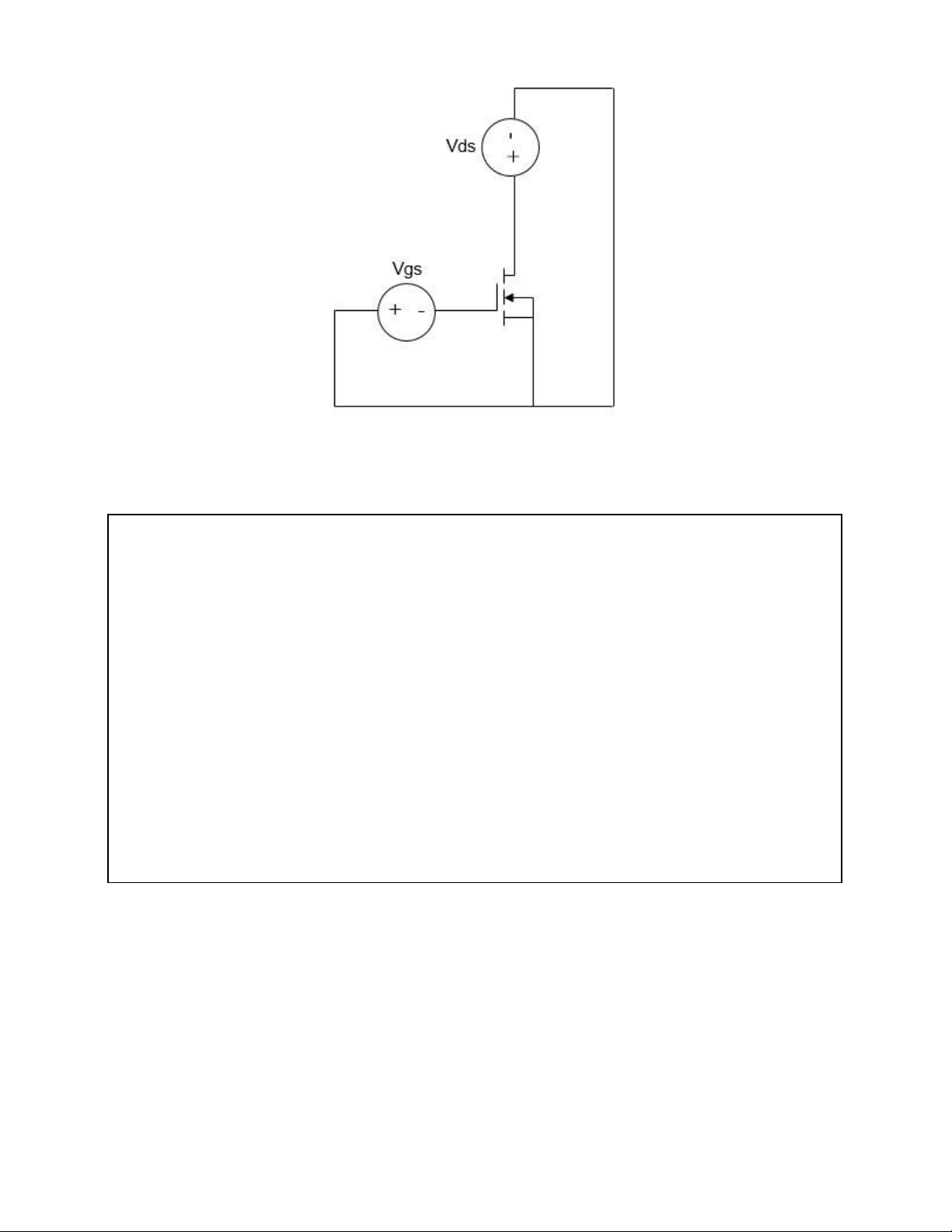

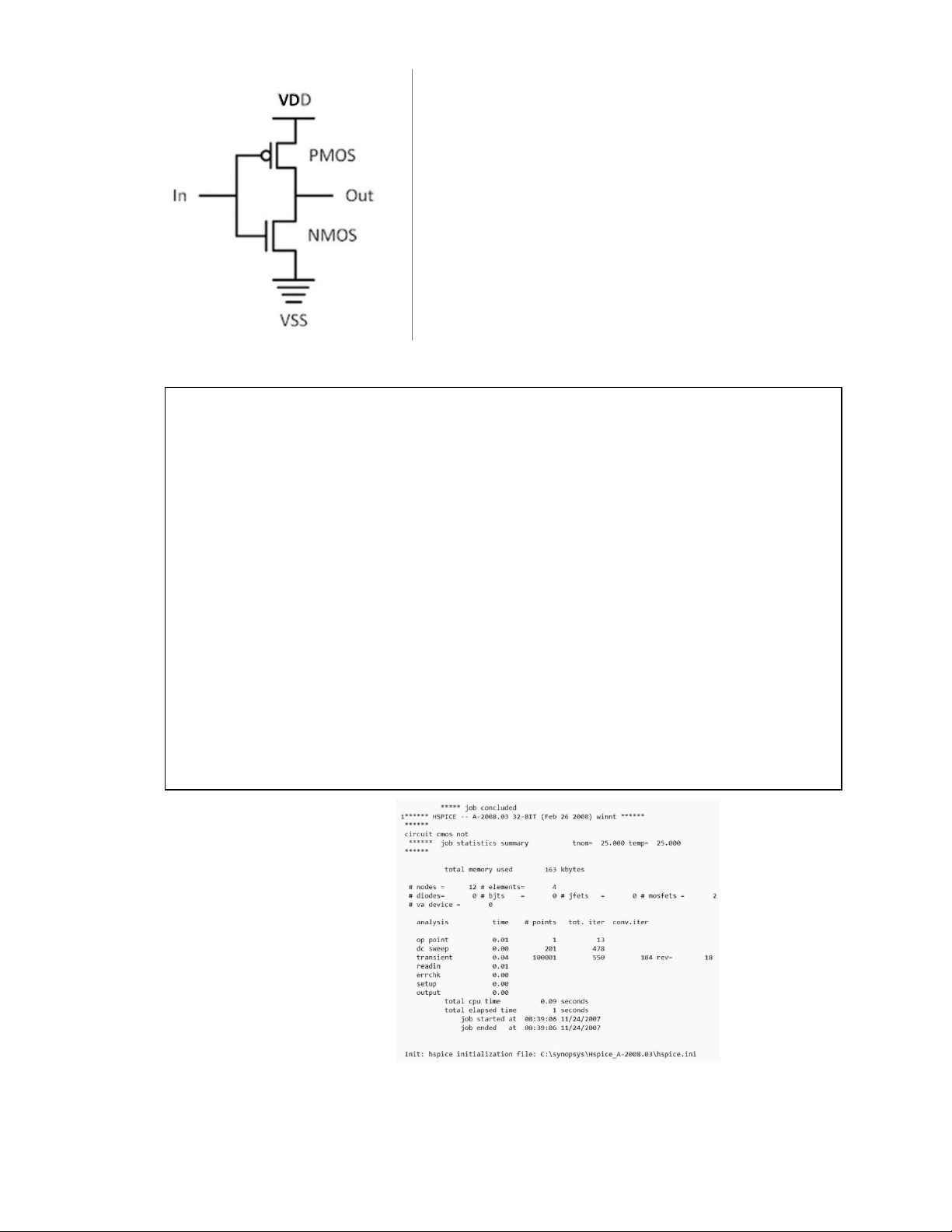

Đặc tuyến (V-I) của một transistor Mosfet (mô phỏng bằng hspice): lOMoAR cPSD| 58493804 Ảnh minh họa.

- Chương trình mô phỏng: Circuit Mosfet .option post .global VDD GND .include'90nm_bulk.pm' .temp 25

M D G gnd gnd nmos L=120n W=90n Vgs G gnd DC Vds D gnd DC

.DC Vds 0 1.4 0.1 SWEEP vgs 2 0 0.25 .plot I(M) .end lOMoAR cPSD| 58493804 - Kết quả mô phỏng: - Tín hiệu mô phỏng: III. Mô phỏng mạch

nguyên lý của một cổng đảo CMOS (sử dụng HSPICE) và vẽ Layout

của nó (dùng Mircowind).

Trong điện tử học, cổng logic (tiếng Anh: logic gate) là mạch điện thực hiện một

hàm Boole lý tưởng hóa. Có nghĩa là, nó thực hiện một phép toán logic trên một hoặc

nhiều logic đầu vào, và tạo ra một kết quả logic ra duy nhất, với thời gian thực hiện lý

tưởng hóa là không có trễ.

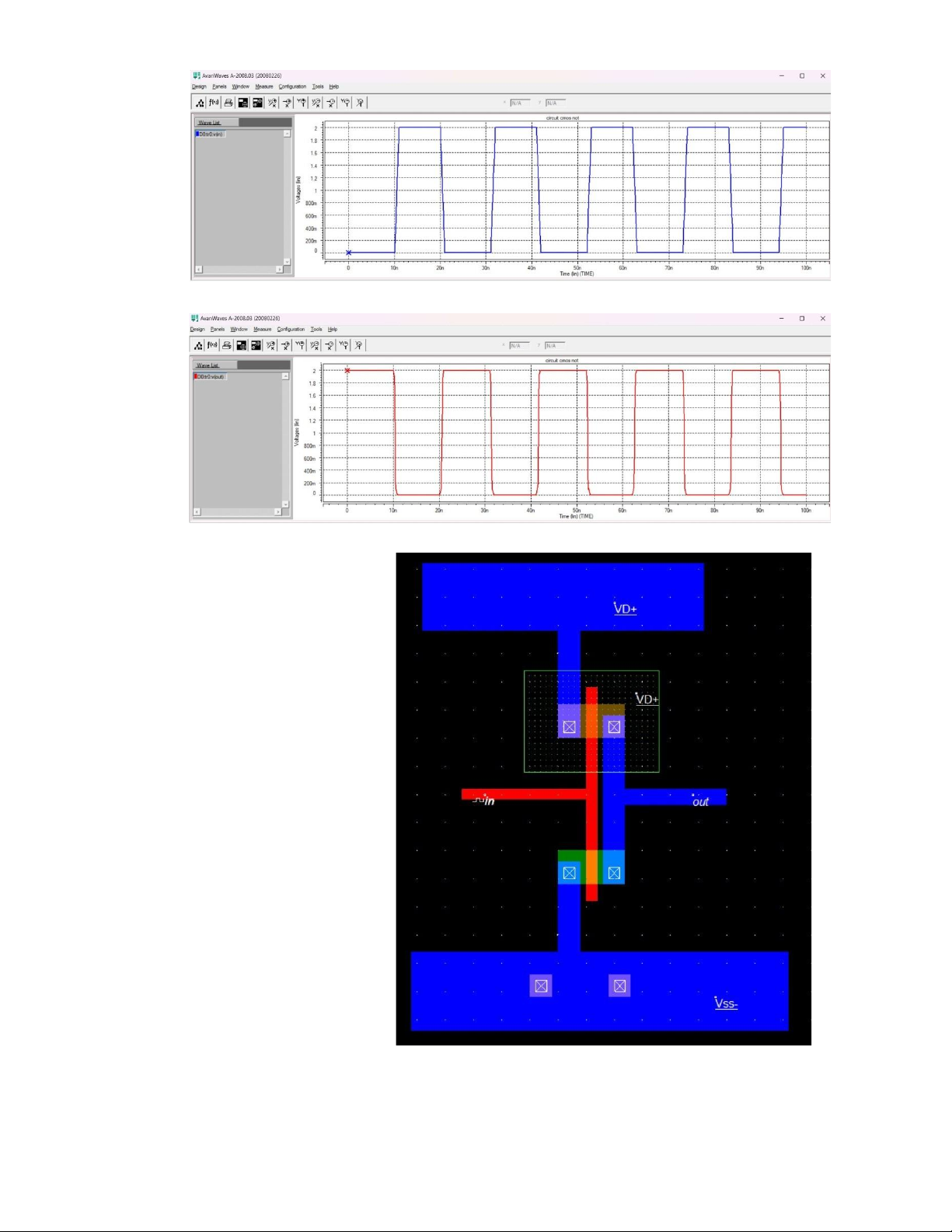

Cổng đảo (not) giống như cái tên của nó thì nó là một linh kiện điện tử có chức năng

cơ bản là đảo ngược giá trị logic đầu vào ra mức cao hoặc thấp. In Out 0 1 Bảng sự thật: 1 0

Mô phỏng cổng đảo cmos bằng Hspice: lOMoAR cPSD| 58493804 Ảnh minh họa.

- Chương trình mô phỏng: Circuit Cmos Not .option post .include '90nm_bulk.pm' .temp 25

VIN in gnd PWL(0n 0,10n 0, 11n 2, 20n 2, 21n 0,R 0) VD 2 gnd DC 2

M1 out in 2 2 pmos w=360n l=90n

M2 out in gnd gnd nmos w=360n l=90n .tran 1ps 100ns .dc VIN 0 2 0.01 .plot .end - Kết quả mô phỏng: - Tín hiệu mô phỏng: + Ngõ vào: lOMoAR cPSD| 58493804 + Ngõ ra:

Sử dụng microwind mô phỏng mạch: - Hình ảnh layout: - Tín hiệu mô phỏng: lOMoAR cPSD| 58493804 + Ngõ vào + Ngõ ra *Nhận xét:

qua tín hiệu trên ta có thể thấy tín hiệu ngõ vào vào tín hiệu ngõ ra ngược nhau. Ngõ

vào mức cao ngõ ra mức thấp và ngược lại.

I. Tùy chọn 2 mạch bất kỳ sử dụng transistor MOSFET (kham khảo giáo trình

linh kiện điện tử, mạch điện tử, linh kiện bán dẫn...), mô phỏng hoạt động

của các mạch sử dụng HSPICE, vẽ Layout các mạch sử dụng Mircowind. 1. Cổng And.

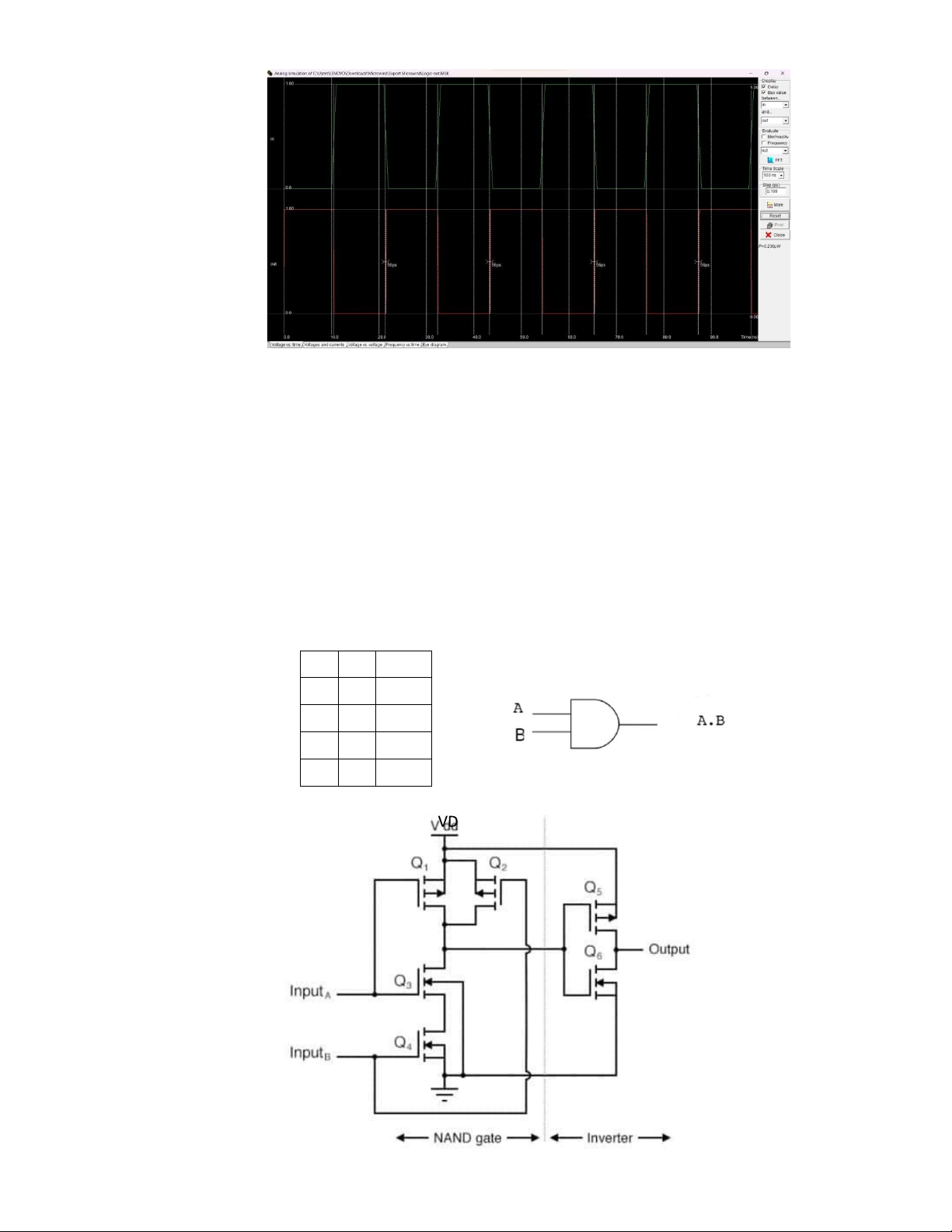

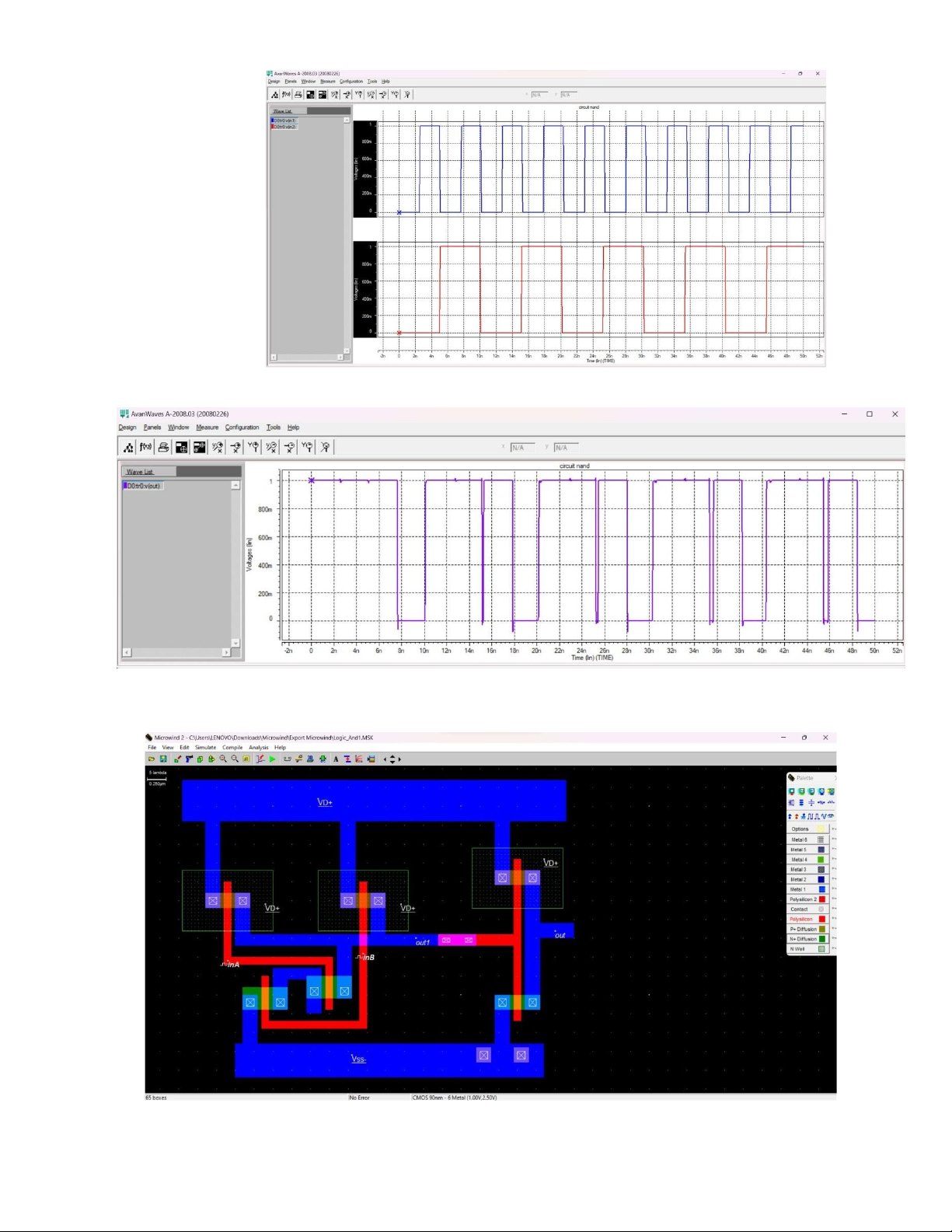

Cổng AND là một cổng logic dùng để thực hiện hàm AND hai hay nhiều biến. Cổng

AND có các ngõ vào tùy thuộc số biến và một ngõ ra. Ngõ ra của cổng là hàm AND của

các biến ngõ vào. Bên phải là bảng chân trị mô tả hoạt động của cổng AND 2 ngõ vào A và B. A B A.B 0 0 0 0 1 0 1 0 0 Bảng sự thật: 1 1 1 Mô phỏng cổng And bằng Hspice: lOMoAR cPSD| 58493804 Ảnh minh họa - Chương trình mô phỏng: Circuit And .option post .include '90nm_bulk.pm' .temp 25

VA in1 gnd PWL(0n 0, 2.5n 0, 2.6n 1, 5n 1, 5.1n 0, R 0)

VB in2 gnd PWL(0n 0, 5n 0, 5.1n 1, 10n 1, 10.1n 0, R 0)

M1 1 in1 D D pmos w=200n l=100n

M2 1 in2 D D pmos w=200n l=100n

M3 1 in1 2 gnd nmos w=300n l=100n

M4 2 in2 gnd gnd nmos w=300n l=100n VD D gnd 1

M5 out 1 D D pmos w=200n l=100n

M6 out 1 gnd gnd nmos w=200n l=100n .tran 1ps 50ns .end - Kết quả mô phỏng: - Tín hiệu mô phỏng: + 2 ngõ vào A và B: lOMoAR cPSD| 58493804 + Ngõ ra:

Sử dụng microwind mô phỏng: - Hình ảnh vẽ layout: - Tín hiệu mô phỏng: lOMoAR cPSD| 58493804 + Ngõ vào A: + Ngõ vào B: + Ngõ ra 2. Mạch cổng Nand.

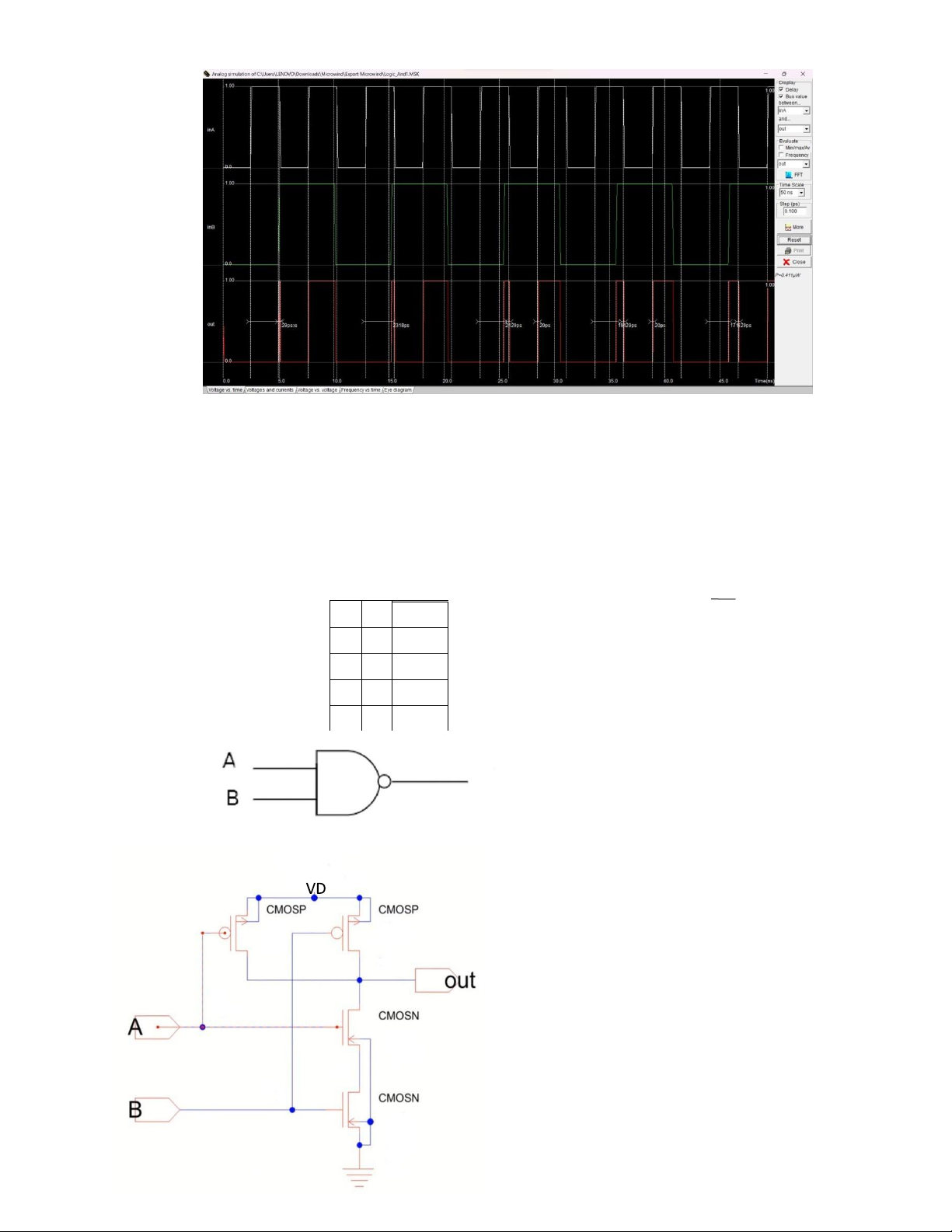

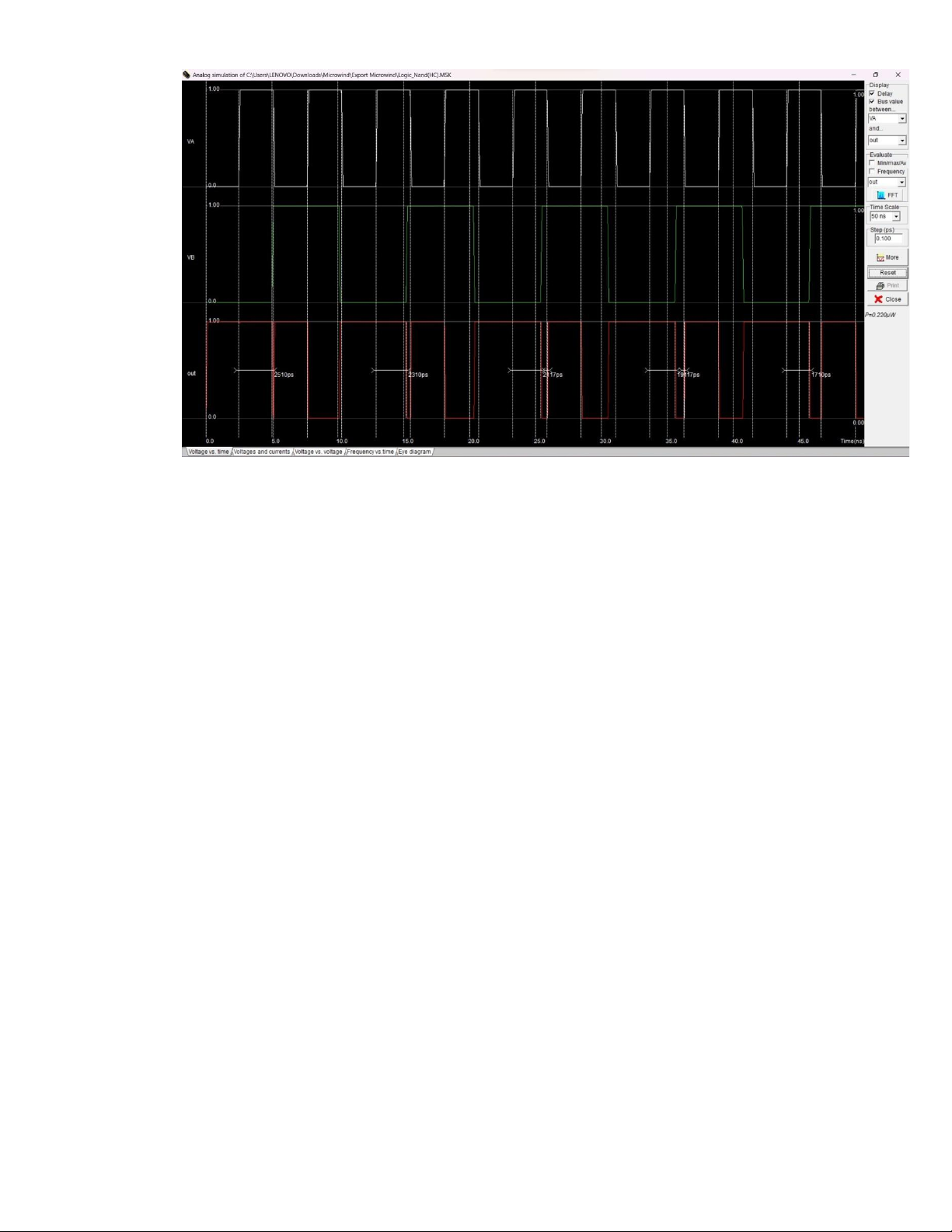

Trong điện tử kỹ thuật số, cổng NAND ( NOT-AND ) là cổng logic tạo ra đầu ra chỉ sai

nếu tất cả các đầu vào của nó là đúng; do đó đầu ra của nó là phần bù cho cổng AND.

Kết quả đầu ra THẤP (0) chỉ cho kết quả nếu tất cả các đầu vào vào cổng là CAO (1);

nếu bất kỳ đầu vào nào là THẤP (0), kết quả đầu ra là CAO (1). A.B Bảng sự thật: A B A.B

Sử dụng Hsipce mô phỏng mạch: 0 0 1 0 1 1 1 0 1 1 1 0 Ảnh minh họa lOMoAR cPSD| 58493804

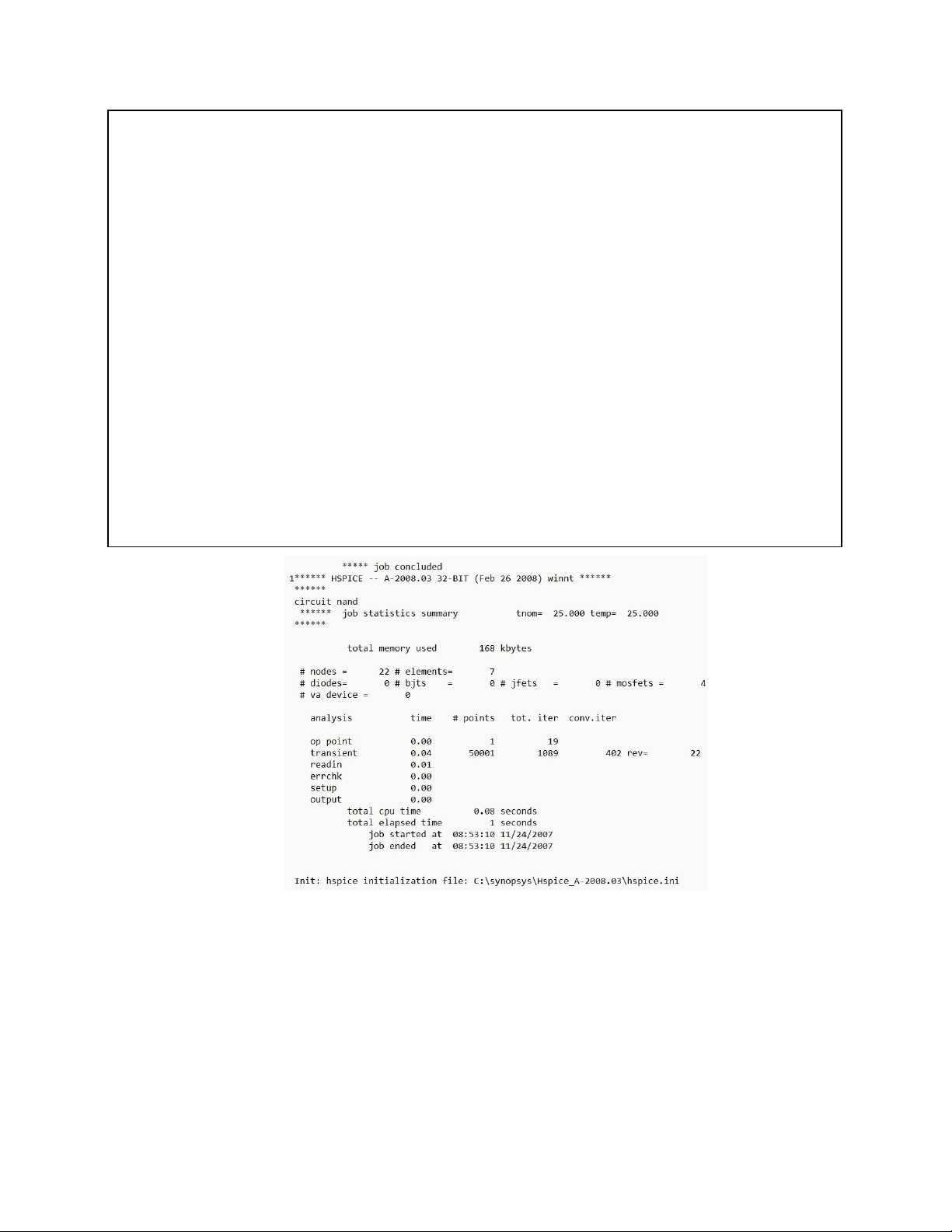

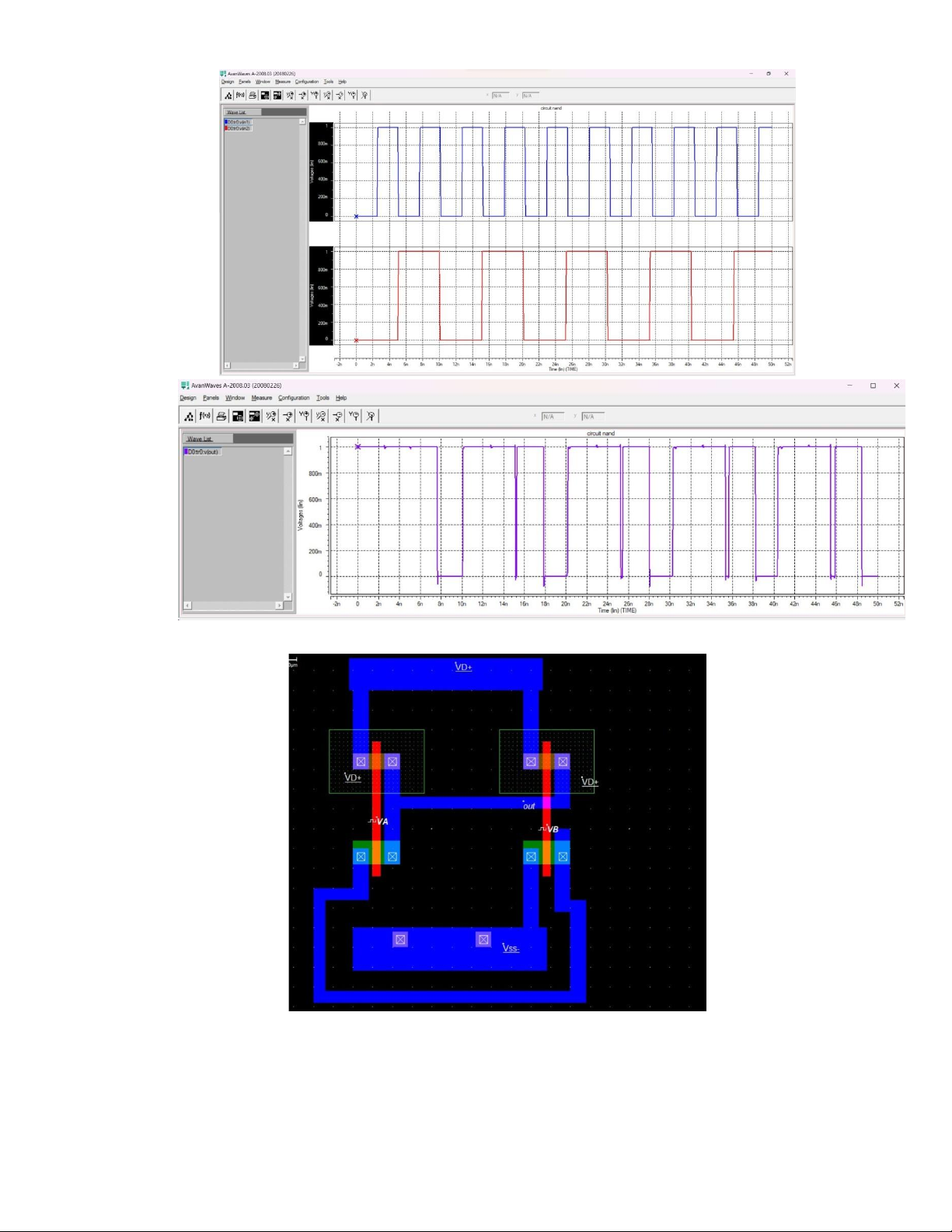

- Chương trình mô phỏng: Circuit Nand .option post .include '90nm_bulk.pm' .temp 25

VA in1 gnd PWL(0n 0, 2.5n 0, 2.6n 1, 5n 1, 5.1n 0, R 0)

VB in2 gnd PWL(0n 0, 5n 0, 5.1n 1, 10n 1, 10.1n 0, R 0)

M1 out in1 D D pmos w=200n l=100n

M2 out in2 D D pmos w=200n l=100n

M3 out in1 2 gnd nmos w=300n l=100n

M4 2 in2 gnd gnd nmos w=300n l=100n VD D gnd 1 .tran 1ps 50ns .end - Kết quả mô phỏng: - Tín hiệu mô phỏng: lOMoAR cPSD| 58493804 + Ngõ vào A: + Ngõ vào B: + Ngõ ra: Sử dụng microwind mô phỏng: - Hình ảnh vẽ layout: - Kết quả mô phỏng: lOMoAR cPSD| 58493804 + Ngõ vào A: + Ngõ vào B: + Ngõ ra: