Preview text:

2 + Chương 4 Bộ nhớ Cache

4.1 Tổng quan Hệ thống bộ nhớ máy tính

Các đặc tính của hệ thống bộ nhớ Phân cấp bộ nhớ

4.2 nguyên tắc Bộ nhớ Cache

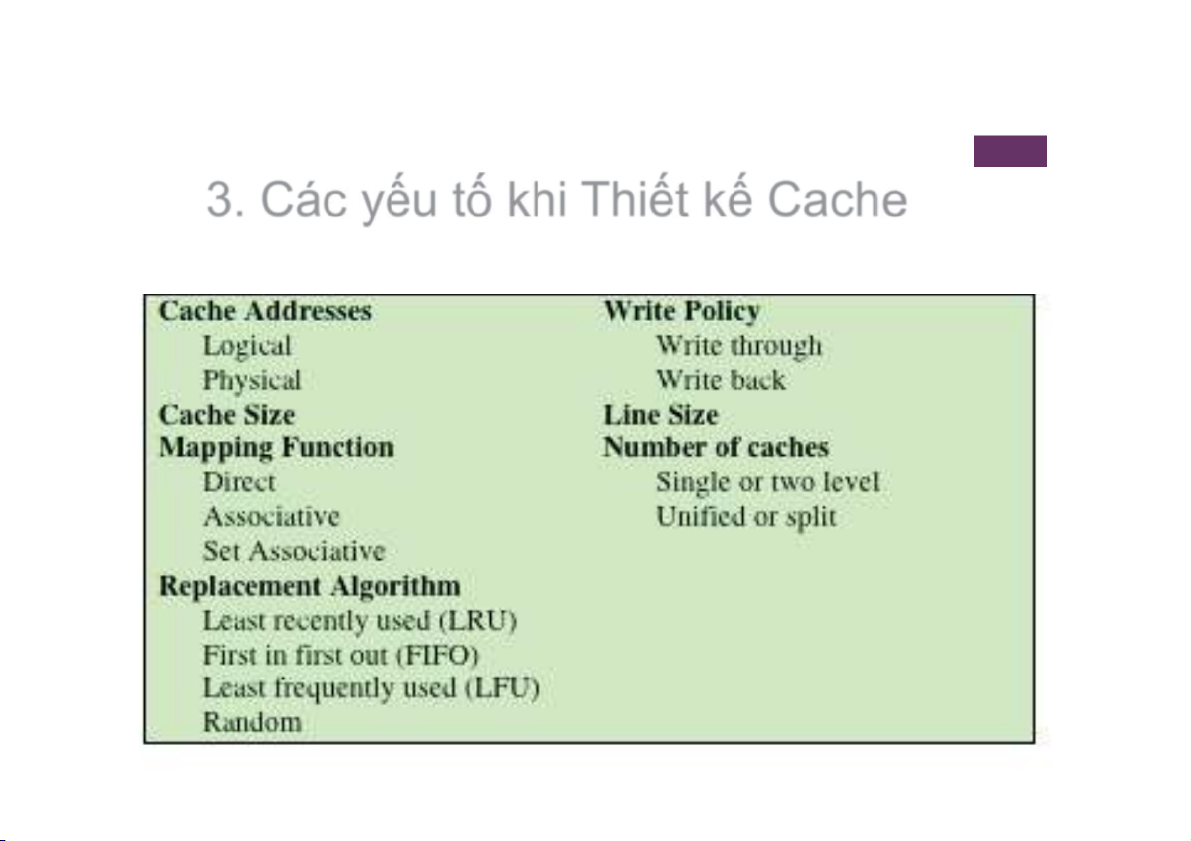

4.3 Các thành phần của Thiết kế Cache Cache Addresses Cache Size + Ánh xạ Chức năng Các thuật toán thay thế Chính sách ghi Kích thước line Số bộ nhớ Cache

4.4 Tổ chức Cache Pentium 4 NỘI DUNG 4

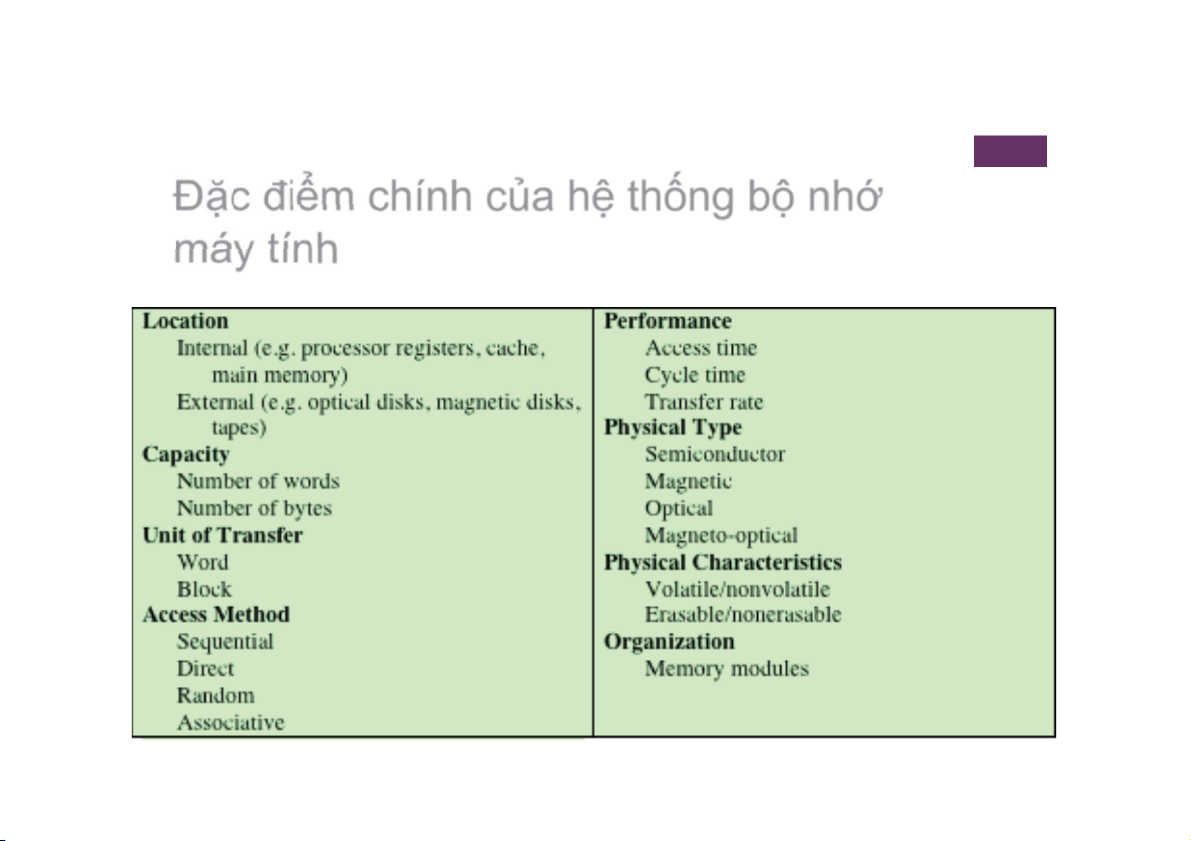

Đặc điểm chính của hệ thống bộ nhớ máy tính

Bảng 4.1 Các đặc điểm chính của hệ thống bộ nhớ máy tính 5 +

Đặc điểm của hệ thống bộ nhớ Vị trí

Bộ nhớ có thể ở trong và ngoài máy tính

Bộ nhớ trong thường tương đương với bộ nhớ chính

Bộ xử lý cần có bộ nhớ cục bộ riêng của nó, dưới dạng thanh ghi

Cache là một dạng khác của bộ nhớ trong

Bộ nhớ ngoài bao gồm các thiết bị lưu trữ ngoại vi có thể truy cập

vào bộ xử lý thông qua bộ điều khiển I / O Dung lượng

Bộ nhớ thường được biểu d ễ i n dưới dạng byte Đơn vị truyền

Đối với bộ nhớ trong, đ

ơn vị truyền bằng số lượng đường dây điện

đi vào và ra khỏi module bộ nhớ

Phương pháp truy cập các khối dữ liệu 6 Truy cập Truy cập Truy cập Kết hợp tuần tự trực tiếp ngẫu nhiên Bộ nhớ được Mỗi vị trí trong 1 từ được lấy ra tổ chức thành Dùng cơ chế bộ nhớ có một dựa trên 1 phần các đơn vị dữ đọc-ghi chia cơ chế định địa nội dung chứ liệu sẻ chỉ - records riêng không dựa trên địa chỉ của nó Thời gian truy Truy cập phải các block cập vào 1 v ị trí mỗi vị trí có cơ thực hiện theo hoặc record nhất định không chế định địa chỉ một dãy tuần có địa chỉ duy đổi, không phụ riêng; thời gian tự thuộc vào chuỗi nhất dựa trên truy cập không vị trí thực tế các truy cập đổi, không phụ trước đó thuộc vị trí hoặc các mẫu truy Thời gian truy 1 vị trí bất kỳ có cập trước cập biến Thời gian truy động thể được lựa cập biến chọn ngẫu nhiên, động đánh địa chỉ và truy cập Bộ nhớ cache trực tiếp có thể sử dụng truy cập kết hợp Bộ nhớ chính và một số hệ thống cache là truy

Dung lượng và Hiệu năng: 7

Hai đặc điểm quan trọng nhất của bộ nhớ

Ba tham số hiệu năng được sử dụng:

Thời gian truy cập

(độ trễ)

Chu kỳ bộ nhớ

Tốc độ truyền tải

• Đối với bộ nhớ truy

• Thời gian truy cập cộng cập ngẫu nhiên, nó

với thời gian cần trước • Tốc độ truyền dữ là thời gian cần để khi truy cập thứ hai có liệu vào hoặc ra thực hiện 1 thao tác thể bắt đầu khỏi bộ nhớ đọc hoặc ghi

• Liên quan đến hệ thống

• Đối với bộ nhớ truy

• Đối với bộ nhớ truy bus, không liên quan cập ngẫu nhiên, cập không ngẫu bộ xử lý tốc độ truyền tải nhiên, nó là thời gian bằng 1/(chu kỳ) cần để đặt cơ chế đọc-ghi đến vị trí mong muốn 8 + Bộ n ớ h

- Các dạng phổ biến n ấ h t: Bộ nhớ bán ẫ d n, Bộ nhớ bề mặt

từ, Bộ nhớ quang, Bộ nhớ quang từ - Với bộ n ớ h truy ậ

c p ngẫu nhiên, vấn đề quan trọng khi

thiết kế là tổ chức hay sự sắp xếp vật lý của các bit để tạo thành các từ word 9 + Bộ n ớ h Một số đ c

ặ điểm vật lý quan trọng của lưu trữ dữ liệu:

Bộ nhớ khả biến (Volatile memory)

Thông tin bị phân rã tự nhiên hoặc bị mất khi nguồn điện ắ t t

Bộ nhớ bất biến (Non-volatile memory)

Thông tin một khi đã được ghi thì ẽ s không bị hư hỏng cho

đến khi được cố tình thay đổi

Không cần cấp điện để giữ lại thông tin

Bộ nhớ bề mặt từ (Magnetic-surface memories) Bất biến

Bộ nhớ bán dẫn (Semiconductor memory)

Khả biến hoặc bất biến

Bộ nhớ không xoá được (Nonerasable memory)

Không thể thay đổi, trừ khi phá hủy các khối lưu trữ 10

+ Phân cấp bộ nhớ

Thiết kế bộ nhớ của máy tính cần trả lời ba câu hỏi:

How much, how fast, how expensive

Cần có sự cân đối giữa dung lượng, thời gian truy cập và chi phí

Thời gian truy cập nhanh hơn, chi phí lớn hơn cho mỗi bit

Dung lượng lớn hơn, chi phí nhỏ hơn cho mỗi bit

Dung lượng lớn hơn, thời gian truy cập chậm hơn

Giải pháp cho tình trạng khó xử khi thiết kế bộ nhớ:

Không dựa vào một thành phần hoặc công nghệ bộ nhớ

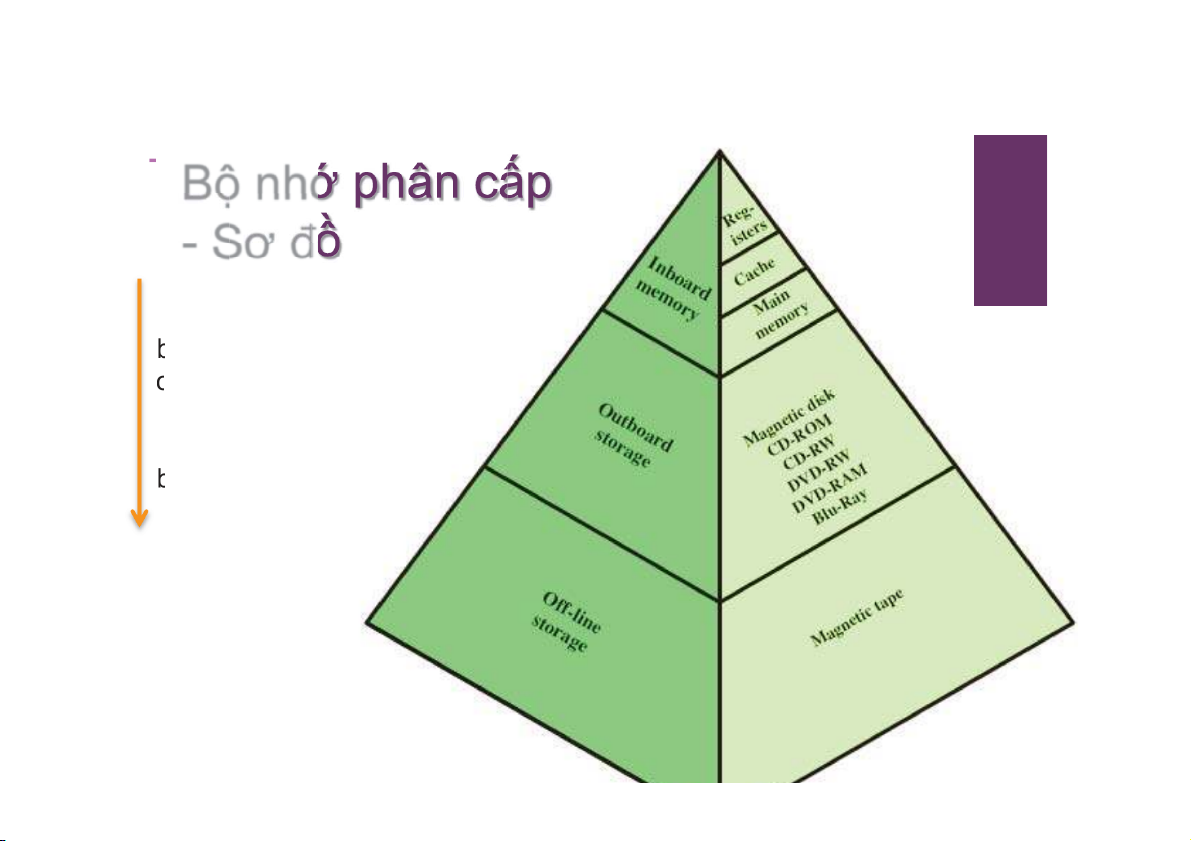

Sử dụng một hệ thống phân cấp bộ nhớ 11 + Bộ nhớ - Sơ đồ

a. Giảm chi phí cho mỗi bit b. Tăng dung lượng

c. Tăng thời gian truy cập dài hơn

d. Giảm tần suất truy cập

bộ nhớ của bộ vi xử lý +

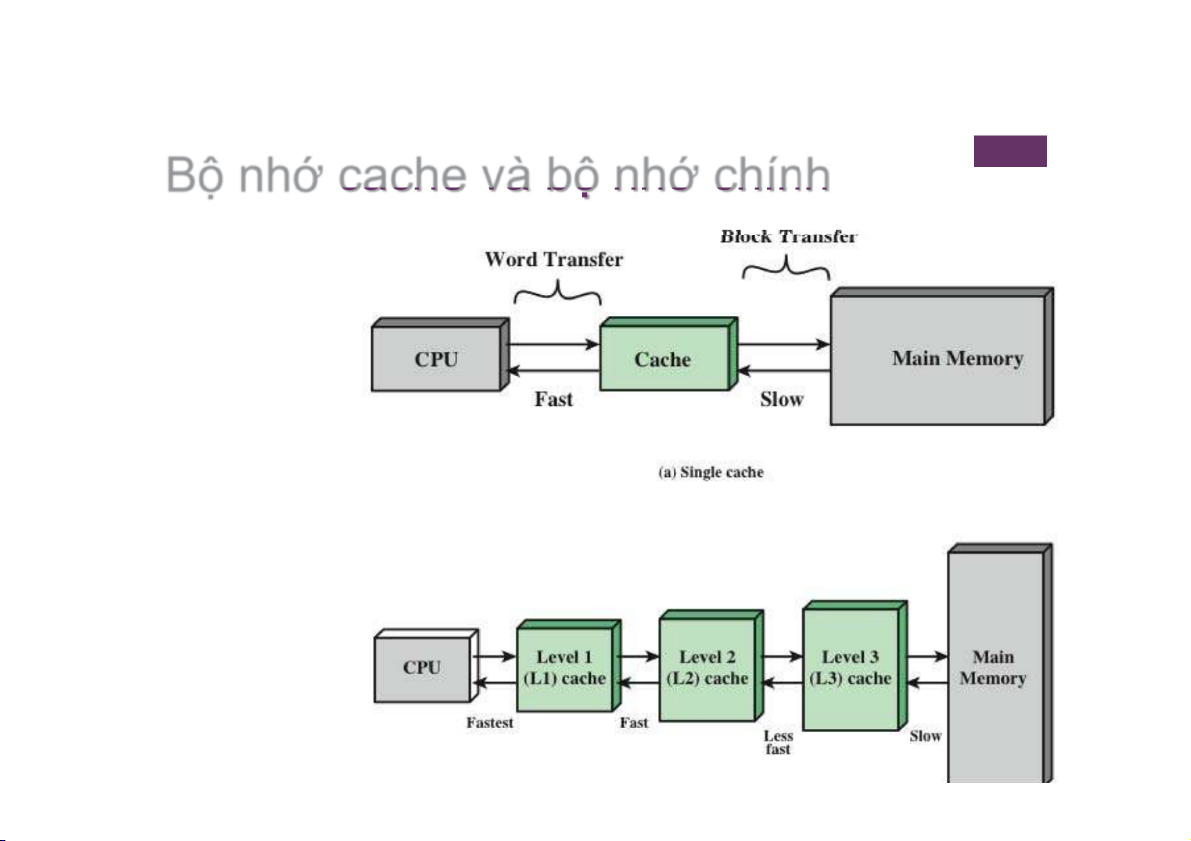

2. NGUYÊN LÝ BỘ NHỚ CACHE

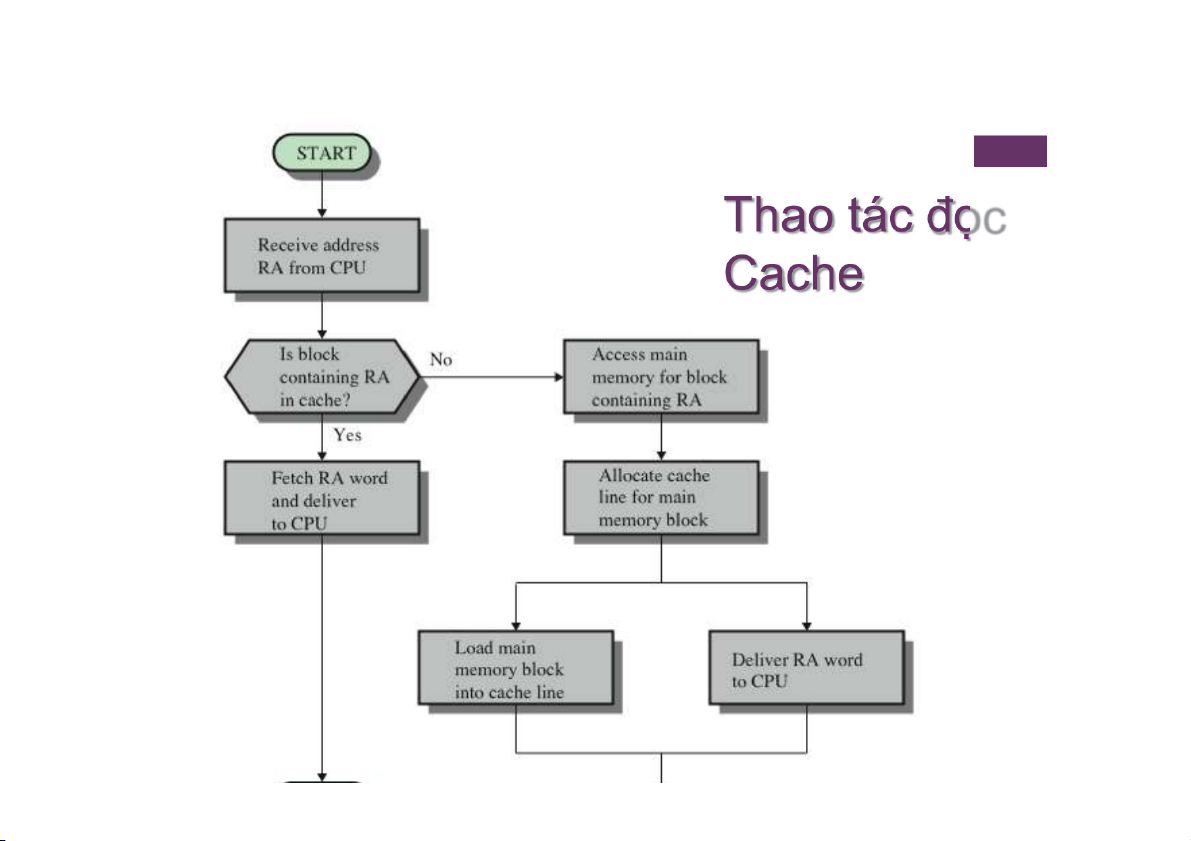

Bộ nhớ cache và bộ nhớ chính 13 BXL kiểm tra xem từ có trong cache hay không: - Nếu có, cache gửi từ này đến BXL (nhanh) - Nếu không, cache đọc 1 block trong bộ nhớ chính, rồi cache gửi word đến BXL

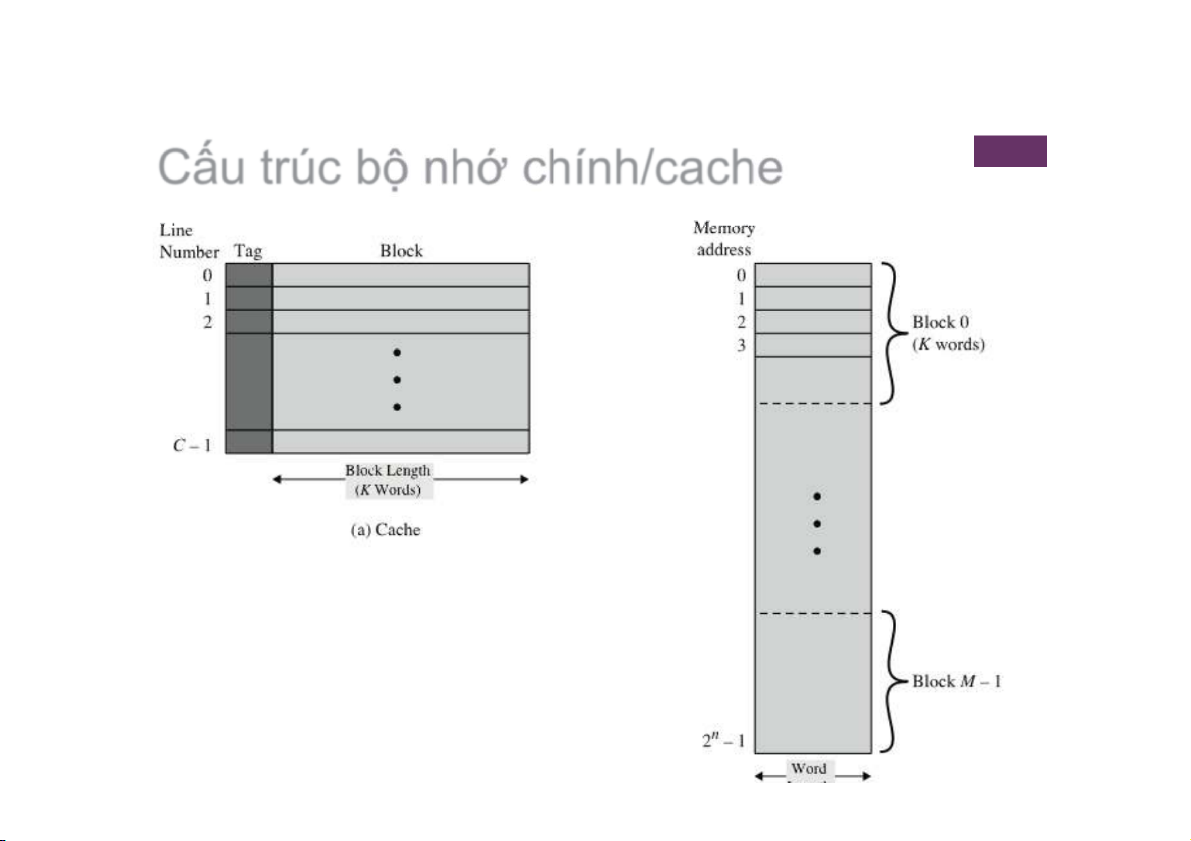

Cấu trúc bộ nhớ chính/cache 14 15 ọc 16

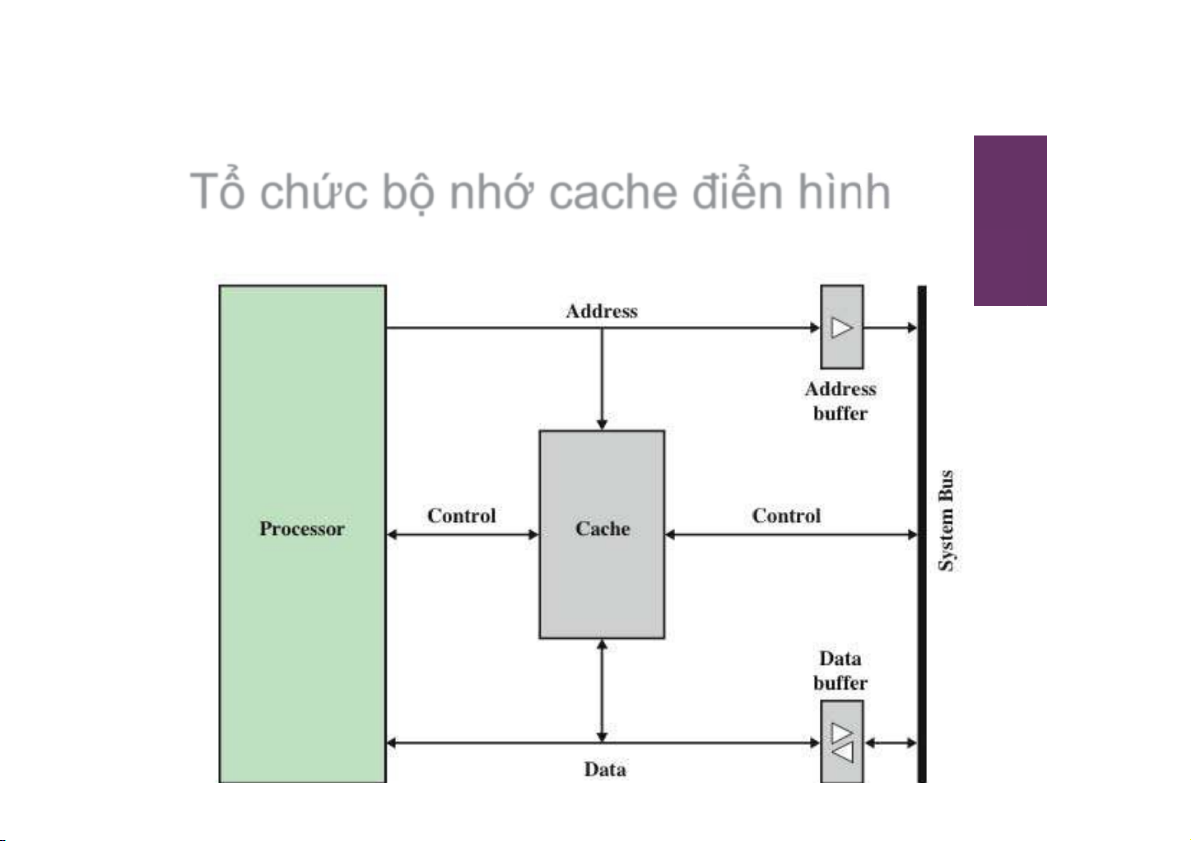

+ Tổ chức bộ nhớ cache điển hình 17 3. Các yếu ố t khi Thiết kế Cache 18

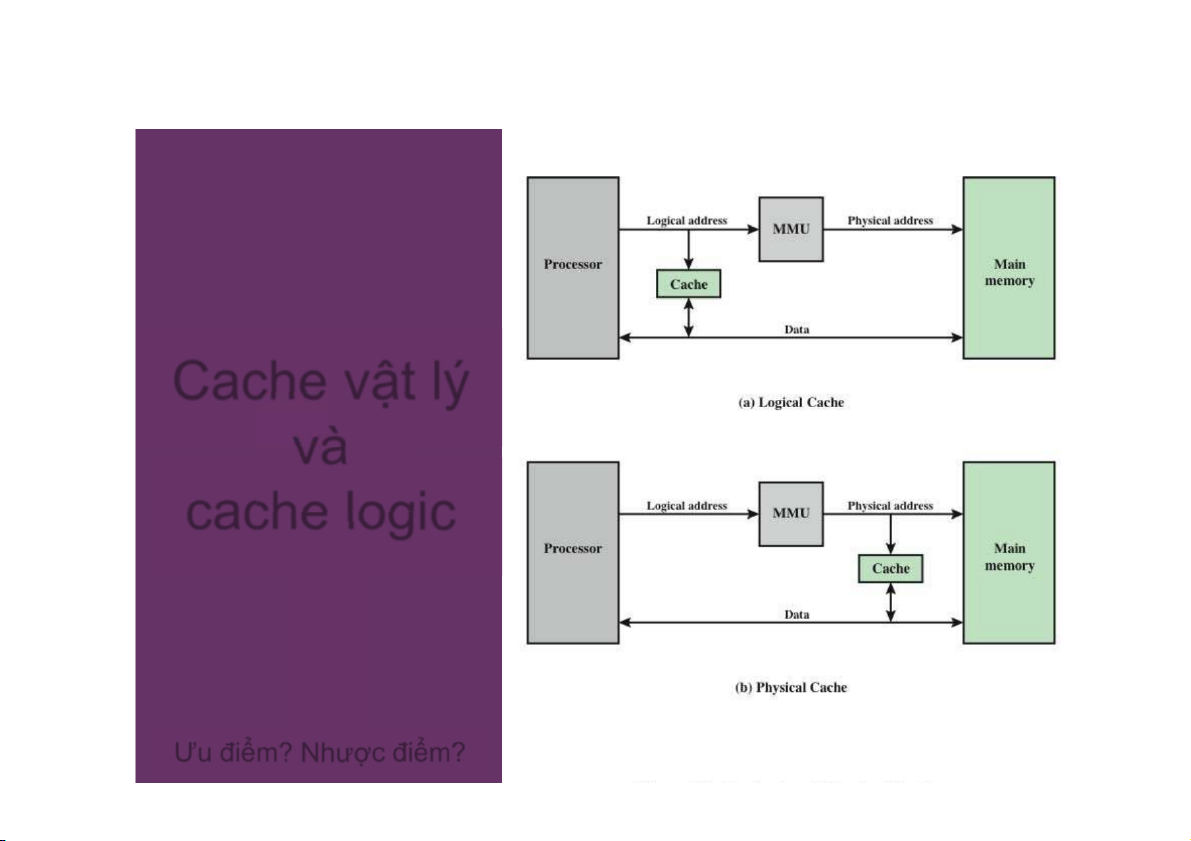

+ Địa chỉ bộ nhớ cache Bộ nhớ ảo

Cơ sở cho phép các chương trình định đ ịa chỉ bộ nhớ theo

quan điểm logic, không liên quan đến số lượng ộ b nhớ chính vật lý có sẵn

Khi bộ nhớ ảo được sử dụng, trường địa chỉ trong lệnh chứa địa chỉ ảo

Để đọc ra và ghi vào bộ nhớ chính, một khối phần cứng

quản lý bộ nhớ (memory management unit - MMU) sẽ

dịch từng địa chỉ ảo sang địa chỉ vật lý trong bộ nhớ chính + Cache vật lý và cache logic

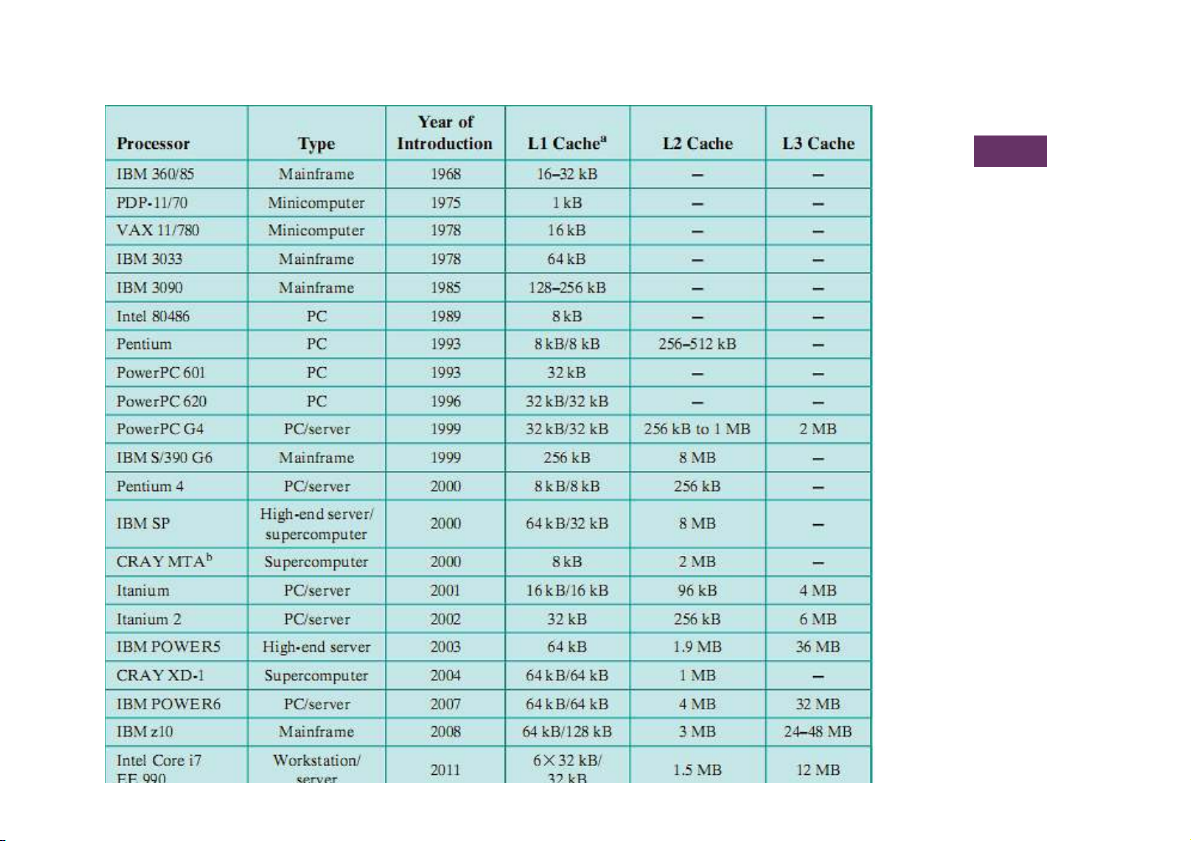

Ưu điểm? Nhược điểm? 20 Bảng 4.3 Kích thước cache trong

một số

bộ xử lý a, Hai giá trị cách nhau bằng dấu / là cache lệnh và cache dữ liệu. b, Cả hai cache đều là cache lệnh; 21 Hàm ánh xạ

Bởi vì số dòng (line) của cache ít hơn số khối (block) bộ nhớ

chính, cần có một thuật toán ánh xạ các khối bộ nhớ chính

vào các dòng bộ nhớ cache

Ba kỹ thuật có thể được sử dụng: Trực tiếp Kết hợp Kết hợp Set

• Cho phép 1 khối bộ nhớ • Thể hiện ưu điểm • Đơn giản nhất

chính được tải vào bất của cả phương pháp kỳ dòng cache nào • Ánh xạ

trực tiếp và kết hợp, mỗi k ố h i ủ c a bộ nhớ chính vào

• Logic điều khiển cache đồng thời giảm một

diễn giải địa chỉ bộ nhớ nhược điểm line cache xác bằng trường Tag và định trường Word

• Để xác định một khối có ở trong cache không, logic điều khiển cache phải cùng lúc kiểm tra