Preview text:

Công nghệ CMOS

(complementary metal-oxide semiconductor)

Lịch sử hình thành và sự ra đời mạch điện tử tích hợp (IC)

• Năm 1947 (năm gốc - năm 0) khi Shockley, Brattain và Bardeen phát minh ra Transistor.

• Năm 1952, đơn tinh thể silicon được sản xuất; khái niệm về mạch

tích hợp (IC) lần đầu tiên được công bố ngày 7 tháng 5 năm 1952 tại

Washington D.C, bởi Geoffrey W.A Dummer, năm 1956 Dummer

không thành công khi thí nghiệm chế tạo IC.

• Năm 1954, các công nghệ xử lý mặt nạ oxit, oxi hoá, quang khắc, ăn

mòn axit, khuyếch tán . . . được phòng thí nghiệm Bell phát triển và

là nền tảng công nghệ sản xuất IC.

• Năm 1955, ra đời transistor hiệu ứng trường đầu tiên.

• Năm 1958, mạch tổ hợp được phát minh. Jack Kilby xây dựng

thành công IC dao động đơn giản gồm 5 linh kiện được tích hợp.

• Năm 1959, công nghệ Planar ra đời, cho phép tích hợp các linh kiện

trên một phiến bán dẫn với tỷ lệ tích hợp cao.

Theo dòng lịch sử, hai công nghệ chế tạo mạch tích hợp phổ biến nhất là

Bipolar và CMOS. Trong một thời gian dài công nghệ Bipolar chiếm ưu thế với họ

IC TTL nổi tiếng. Vào những năm đầu thập niên 70, công nghệ MOS mà điển hình

là dòng sản phẩm DRAMs, các họ chip có khả năng lập trình (vi xử lý) và họ IC

4000 được chế tạo thành công đã bắt đầu cho thời kỳ phát triển theo cấp số nhân về

mật độ tích hợp. Cũng trong thời gian này một số tổ chức đã thiết kế mạch tích hợp

tương tự sử dụng công nghệ MOS. Đầu thập niên 80, công nghệ silicon-gate CMOS

ra đời cho phép kết hợp cả CMOS và Bipolar thành BiCMOS tạo ra công nghệ

mang tính cạnh tranh cao về giá thành và tốc độ. 1

1. Các bước xử lý cơ bản trong công nghệ CMOS

Công nghệ chế tạo bán dẫn dựa trên nền tảng một số bước xử lý như

oxidation (oxi hoá), diffusion (khuếch tán), ion-implantation (cấy ion), etching (ăn

mòn) và photolithography (quang khắc). Tất cả các quá trình này được bắt đầu với

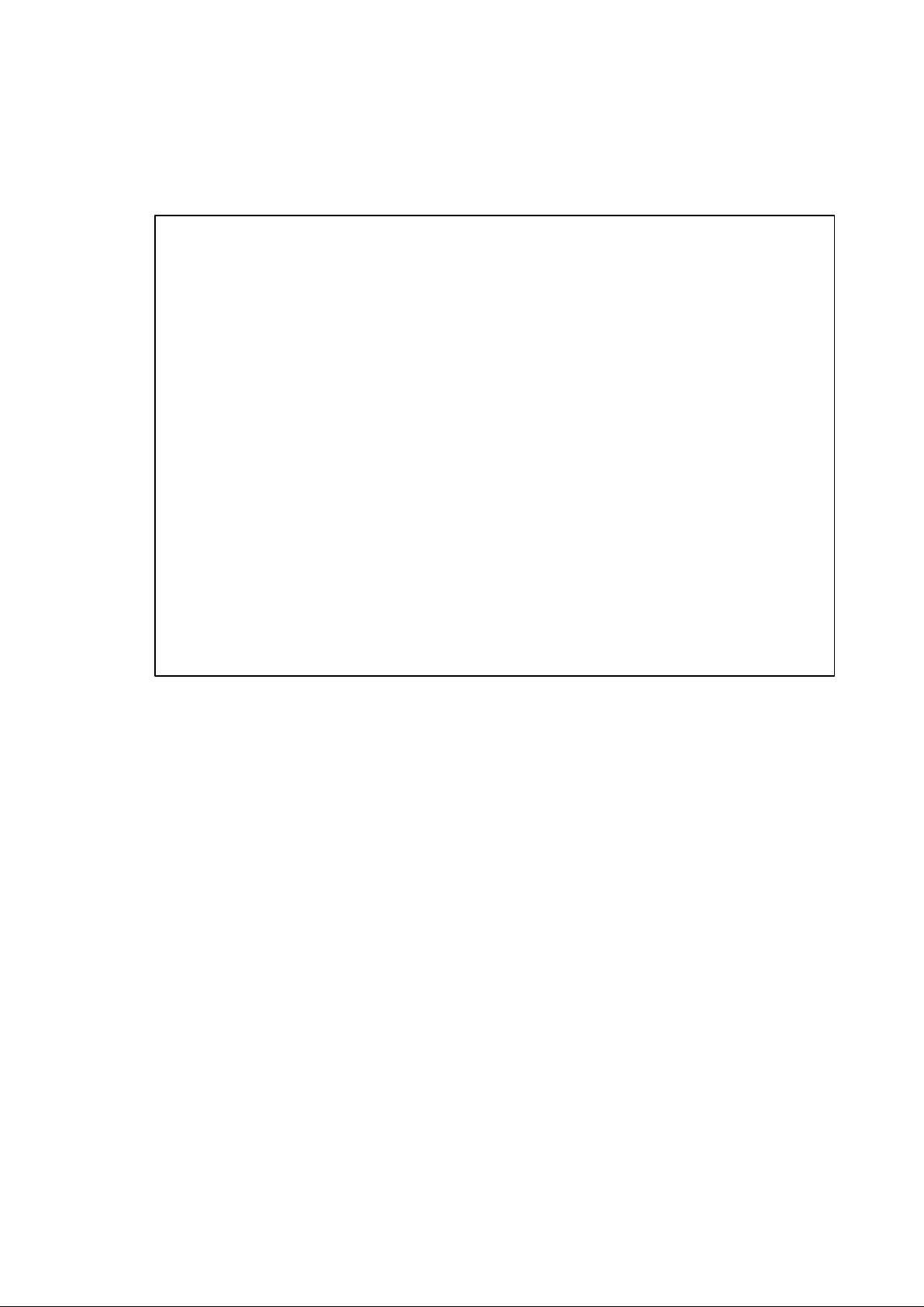

một phiến vật liệu đơn tinh thể silicon. “Thỏi vật liệu đơn tinh thể silicon hình trụ”

được hình thành qua quá trình “kéo đơn tinh thể” thường có đường kính từ 75-300

mm và dài 1m. Trong quá trình chế tạo thỏi đơn tinh thể silicon hình trụ, các nguyên

tố nhóm 3 hoặc nhóm 5 trong bảng tuần hoàn ví dụ như boron hoặc phốt pho được

pha tạp thêm vào thỏi đơn tinh thể để thay đổi tính chất điện hình thành các phiến

đế bán dẫn loại p hoặc loại n tương ứn sau này. Sau đó thỏi đơn tinh thể silicon

được cắt thành từng lát mỏng có bề dày từ 0.5 tới 0.7 mm gọi là wafer (hình 1.1).

Sau đây ta sẽ tìm hiểu các bước cơ bản nhất trong công nghệ chế tạo mạch tích hợp

Hình 1.1: Wafer

1.1 Ôxi hoá (Oxidation)

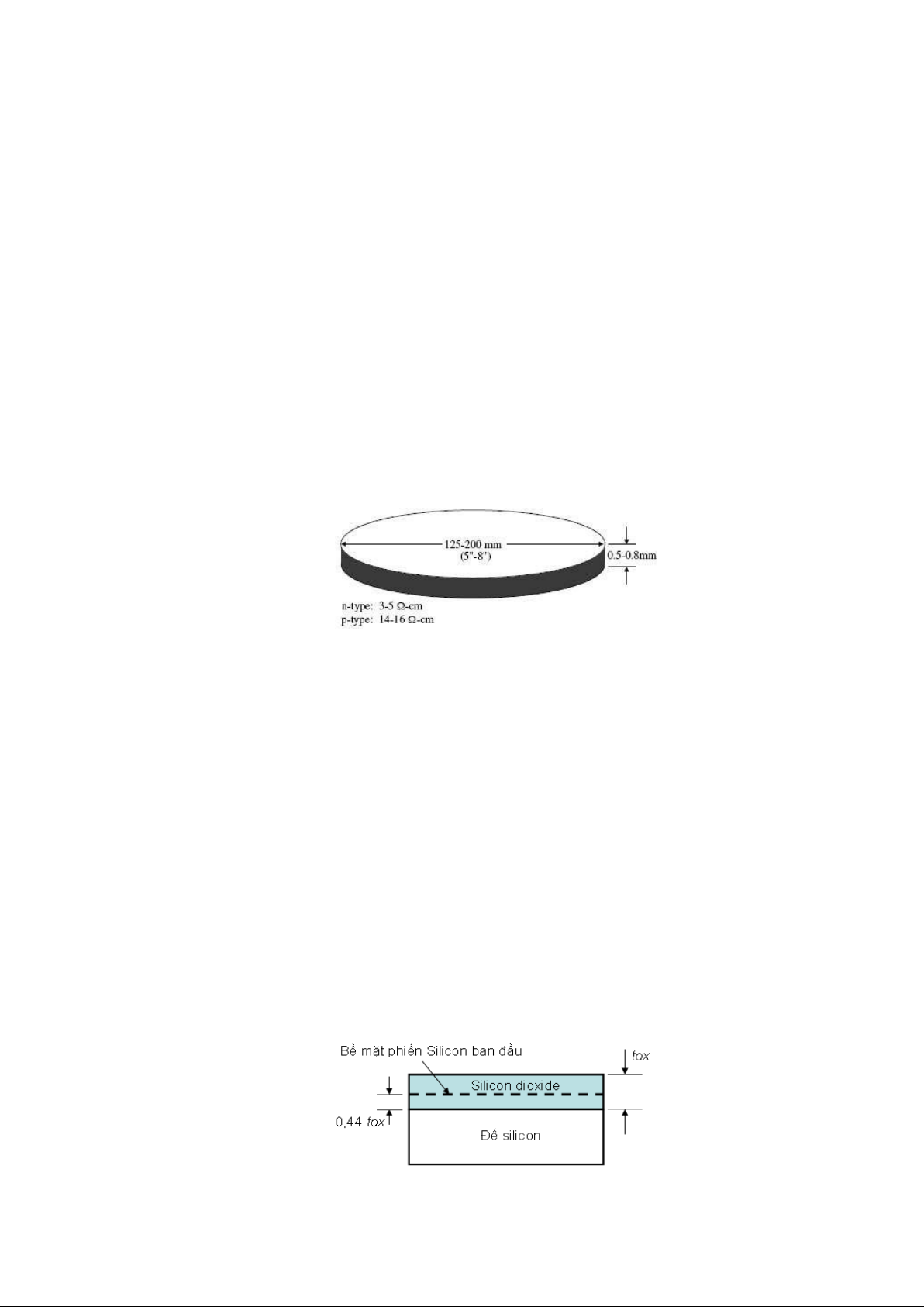

Mục đích của bước này là tạo ra một lớp SiO2 trên bề mặt của wafer, đây là

lớp phủ vững chắc trên bề mặt và có khả năng cách điện cao, chịu nhiệt tốt bảo vệ

cho lớp vật liệu Si trong suốt quá trình khuếch tán. Ngoài ra, SiO2 còn có khả năng

bảo vệ toàn bộ mạch điện khỏi môi trường bên ngoài và chống tác dụng của phóng

xạ. Ngoài ra, một ứng dụng quan trọng khác của lớp oxit này là dùng để làm tụ điện trong mạch tích hợp.

Đây là bước đầu tiên trong quá trình chế tạo sau khi hoàn thành sẽ có một

lớp oxit trên bề mặt của wafer. Tráng màng oxít tốt nếu đạt tỷ lệ 56% bề dày lớp

oxít ở trên bề mặt phiến silicon ban đầu và 44% bề dày lớp oxít ở dưới bề mặt phiến (hình 1.2).

Hình 1.2: Oxi hoá trên bề mặt phiến bán dẫn 2

Thông thường bề dày lớp oxít không cố định, có thể từ 150Å cho các lớp gate

oxide (lớp oxide mỏng dưới cực gate của CMOS hoặc khu vực để chế tạo các linh

kiện tích cực) và hơn 10000Å cho các lớp field oxide (lớp oxide dày để cách ly về

mặt điện giữa các linh kiện.) Sự chuyển tiếp giữa lớp oxide dày và oxide mỏng là

không có sự thay đổi đột ngột về cao độ mà khá mượt mà do đó các lớp vật liệu

khác như dây dẫn kim loại thường được lắng đọng bên trên lớp oxide dày này.

Vùng diện tích cho lớp oxide dày chiếm tỷ trọng khá lớn so với khu vực dành cho

chế tạo các linh kiện tích cực, điều này là tương đối lãng phí không hiệu quả khi nốt

công nghệ ngày càng được thu nhỏ, do đó, hiện nay công nghệ STI được sử dụng để

cách ly về mặt điện giữa các linh kiện thay cho việc chế tạo lớp oxide dày.

Có hai phương pháp Oxihoá là Oxihoá khô, Oxihoá ướt và được tiến hành

trong điều kiện nhiệt độ từ 700 đến 1100 oC.

Si + O2 → SiO2 (Oxihoá khô)

Si + 2H2O → SiO2 + 2H2 (Oxihoá ướt)

1.2 Khuếch tán (Diffusion)

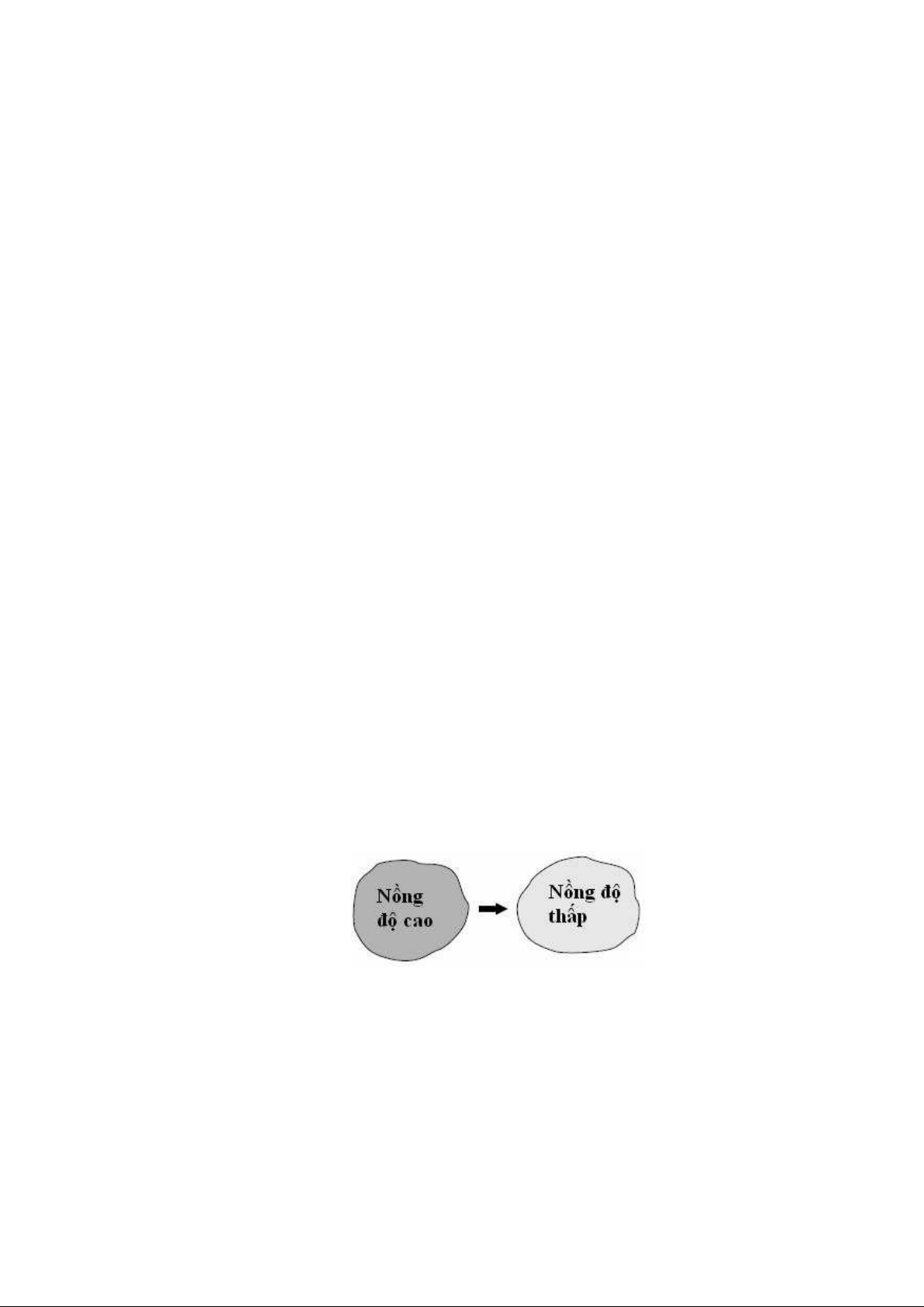

Khuếch tán là một sự dịch chuyển, thường ở nhiệt độ cao, của các nguyên tử

tạp chất từ bề mặt vào sâu phiến đế bằng cách lợi dụng đặc tính chuyển động hỗn

loạn của hạt. Đặc tính này được phát biểu như sau: nếu có một sự chênh lệch về

nồng độ, hạt sẽ chuyển động từ miền có nồng độ cao về miền có nồng độ thấp.

Phương pháp này thường được sử dụng để tạo lớp chuyển tiếp pn dùng cho chế tạo

diode, transistor, tạo vùng nguồn máng của MOSFET hay tạo điện trở và bản cực tụ điện.

Hình 1.3: Quá trình khuếch tán

Trên thực tế, ở dải nhiệt độ từ 800oC tới 1400oC, tùy vào loại tạp chất được

sử dụng trong quá trình khuếch tán, các nguyên tử tạp chất sẽ dần thay thế các

nguyên tử silicon trong mạng đơn tinh thể tạo thành các vùng vật liệu, trong đó tạp

chất loại p đông hơn loại n hoặc tạp chất loại n đông hơn loại p, tương ứng với các

vùng vật liệu có đặc tính dẫn điện loại p hay loại n. 3

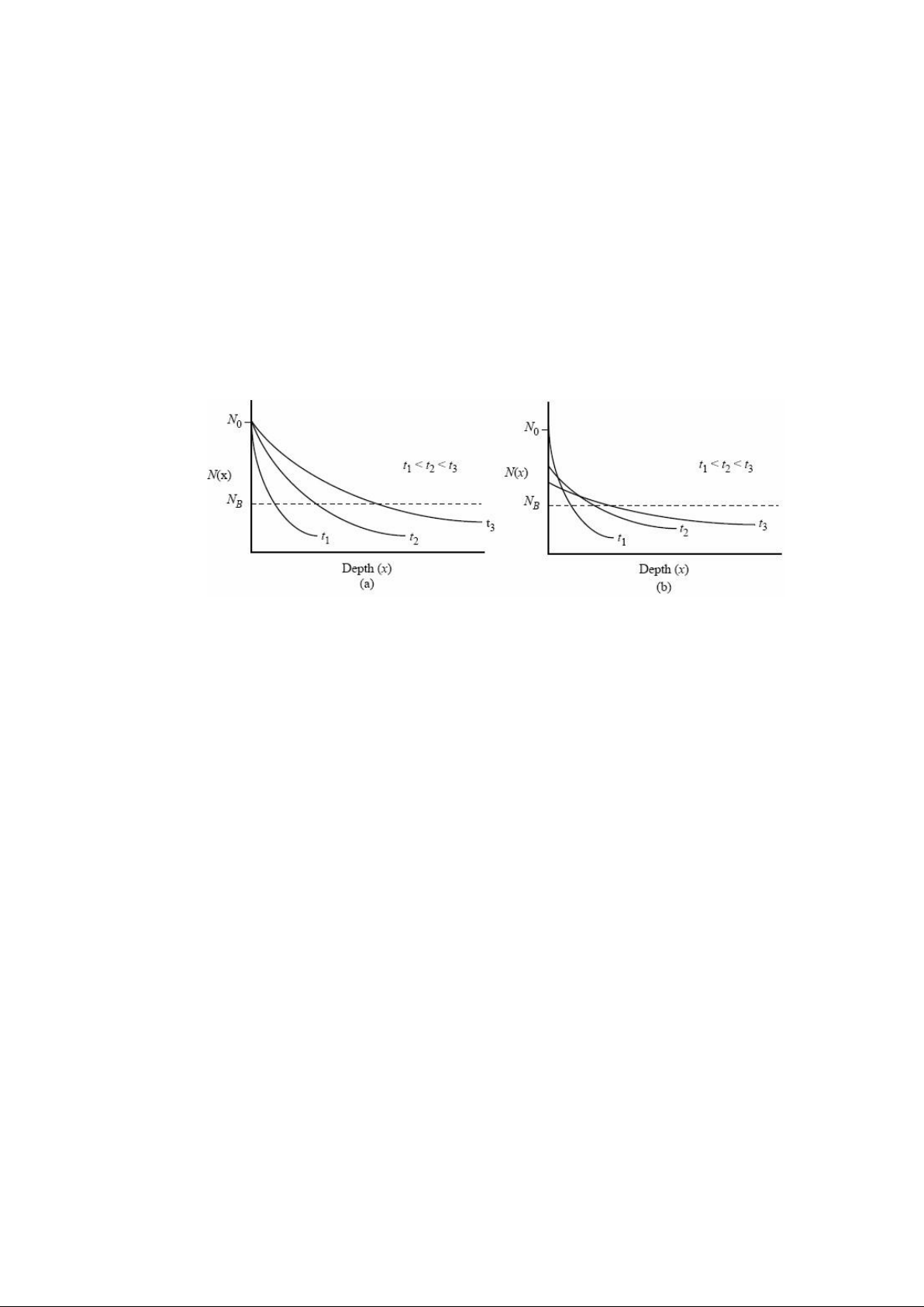

Quá trình khuếch tán tự nhiên được mô tả bởi hai mô hình khuếch tán cơ bản

là: khuếch tán từ nguồn vô hạn và khuếch tán từ nguồn hữu hạn. Khuếch tán từ

nguồn vô hạn là ta giả sử bằng một số kỹ thuật khác nhau sự sắp xếp ban đầu của

các nguyên tử tạp chất lên bề mặt của silicon sao cho nồng độ tạp chất ở bề mặt

khuếch tán là không đổi trong suốt thời gian khuếch tán (N0 cm-3), phân bố nồng độ

tạp chất theo độ sâu khuếch tán là hàm của thời gian (hình 1.4a). Khuếch tán từ

nguồn hữu hạn là nồng độ tạp chất tại bề mặt khuếch tán giảm dần theo thời gian

khuếch tán và phân bố nồng độ tạp chất theo độ sâu khuếch tán cũng là hàm của

thời gian (hình 1.4b).

Hình 1.4: Phần bố nồng độ tạp theo thời gian với

(a) khuếch tán từ nguồn vô hạn, (b) khuếch tán từ nguồn hữu hạn

Trong cả hai mô hình, NB là nồng độ tạp ban đầu của vật liệu bán dẫn.

Chuyển tiếp P-N hình thành khi tạp chất khuếch tán vào khác loại dẫn so với tạp

chất được pha tạp khi chế tạo đế, khoảng cách từ bề mặt khuếch tán tới lớp tiếp giáp

gọi là chiều sâu “chuyển tiếp”. Hai mô hình khuếch tán kể trên là minh họa cho hai

giai đoạn khuếch tán. Giai đoạn đầu tiên gọi là giai đoạn “tạo nguồn” (pre-

deposition) người ta sử dụng mô hình khuếch tán từ nguồn vô hạn để xét cho giai

đoạn này vớí chiều sâu lớp chuyển tiếp thường khoảng 0.1μm. Giai đoạn thứ hai gọi

là giai đoạn khuếch tán “tại chỗ bên trong” (Drive-in diffusion), giai đoạn này

thường diễn ra ở nhiệt độ từ 1050oC tới 1200oC, chúng ta sử dụng mô hình khuếch

tán từ nguồn hữu hạn để xét cho quá trình này với chiều sâu lớp chuyển tiếp thường là 10μm.

Để sử dụng quá trình khuếch tán này chế tạo những linh kiện hữu ích, sự

khuếch tán phải được giới hạn trong một vùng nhỏ trên bề mặt của silicon thay vì là

toàn bộ bề mặt. Giới hạn này được thực hiện bằng kỹ thuật quang khắc. 4

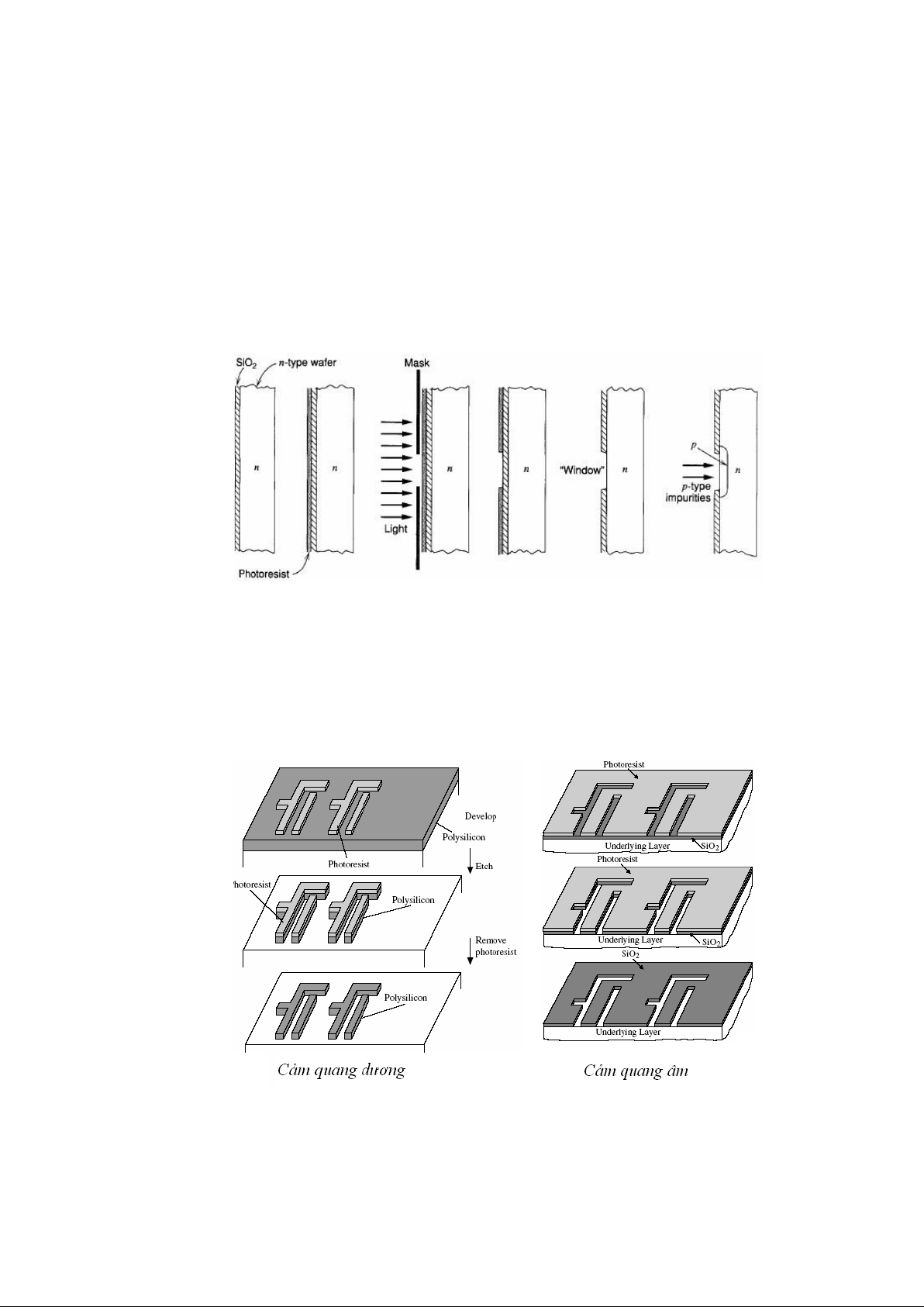

1.3 Quang khắc (lithography)

Quang khắc là kỹ thuật tạo ra các “cửa sổ” trong các công đoạn chế tạo. Ví

dụ để có thể khuếch tán tạp chất tạo cực nguồn, máng, giếng n . . . lên bề mặt phiến

bán dẫn ta phải dùng kỹ thuật quang khắc để tạo ra các cửa sổ dùng để tiến hành

khuếch tán tạp chất hình thành các vùng tích cực. Thông thường phiến tinh thể

Silicon có một lớp oxít mỏng trên bề mặt ngăn cản sự khuếch tán, việc tạo cửa số

khuếch tán sử dụng kỹ thuật quang khắc được minh họa như hình 1.5 dưới đây.

Hình 1.5: Quá trình quang khắc

Trong kỹ thuật quang khắc, trước hết ta phủ một lớp cảm quang lên bề mặt

cần quang khắc. Sau đó đặt mask (mặt nạ quang học) lên trên bề mặt phủ chất cảm

quang rồi tiến hành chiếu sáng với bước sóng cụ thể, phần vật liệu được chiếu sáng

sẽ thay đổi tính chất.

Hình 1.6: Cảm quang dương và cảm quang âm

Cảm quang là hợp chất vật liệu nhậy quang (polymer và dung môi). Cảm

quang dương là trước khi chiếu sáng lớp cảm quang không hoà tan trong dung dịch 5

hiện, sau khi chiếu sáng hấp thụ bức xạ sẽ thay đổi cấu trúc hoá học và hòa tan.

Cảm quang âm là khi được chiếu sáng do hấp thụ năng lượng tạo thành các chuỗi

polymer mà không bị hoà tan trong dung môi. Tiếp theo là hiện hình, với cảm

quang dương phần còn lại sẽ giống hình vẽ trên mask, với cảm quang âm phần còn

lại sẽ ngược với hình vẽ trên mask. Sau khi đã mở ra các vùng SiO2 với hình dạng

thích hợp trên phiến Si bằng lớp cảm quang, ta tiến hành ăn mòn SiO2 bằng HF.

Lớp cảm quang sẽ có vai trò như lớp bảo vệ phần SiO2 còn lại khỏi bị ăn mòn. Sau

khi oxide ở các cửa sổ được ăn mòn phần cảm quang còn lại được loại bỏ bởi hoạt

động tẩy rửa hóa học tiếp theo để lại cửa sổ bề mặt silicon trống như mong muốn.

Ta có thể tiến hành các công đoạn tiếp theo như khuếch tán tạp chất.

Tuỳ từng loại cảm quang mà có các mask khác nhau, thông thường mask

được thiết kế bằng máy tính, dữ liệu về Layout sẽ được dùng để điều khiển máy vẽ

quang hoặc máy vẽ tia điện tử. Thông thường trong chế tạo vi mạch, số lượng mặt

nạ quang học và các bước khuếch tán được sử dụng để tạo thành các cấu trúc phức

tạp như transistor, do đó cần nhiều mask cho các công đoạn khác nhau. Điểm chính

yếu của quang khắc là khả năng định hình một số lượng lớn linh kiện lên bề mặt của

wafer đảm bảo tất cả các linh kiện được chế tạo cùng một mẻ ở cùng một thời điểm.

Khi kích thước cửa sổ ngày càng được thủ nhỏ thì khả năng chế tạo hàng loạt linh

kiện cùng một lúc này chính là chìa khóa nắm giữ, đảm bảo ưu điểm vể tính kinh tế

cho sự phát triển không ngừng của công nghệ vi mạch, đó là giá thành sản xuất tính

trên một đơn vị transistor ngày cảng rẻ. Tuy nhiên khi khích thước cửa sổ ngày càng

bé (số lượng cửa sổ trên cả tấm wafer đạt mức 10xx) thì yêu cầu về độ trùng khớp

các mask, giá thành mặt nạ quang học có thể sẽ làm đảo ngược ưu điểm về tính kinh

tế của công nghệ sản xuất vi mạch được đề cập ở trên.

1.4 Cấy Ion (Ion implantation)

Hình 1.7: Quá trình cấy ion

Đây là phương pháp không sử dụng nhiệt độ để đưa các tạp chất vào phiến

Silicon mà các nguyên tử tạp chất được ion hoá, được gia tốc và đưa đến bề mặt 6

phiến Silicon (hình 1.7,) sau đó các ion với năng lượng cao sẽ đi vào mạng tinh thể,

va chạm với các nguyên tử Si làm cho mất dần năng lượng, cuối cùng sẽ dừng lại.

Phương pháp này có thể cấy ion ở độ sâu 10-600nm dưới bề mặt với ưu điểm

quan trọng nhất là khả năng khống chế chính xác lượng nguyên tử tạp chất, có thể

cấy ion qua lớp oxide và có thể cấy nhiều loại nguyên tố khác nhau (ưu điểm hơn so

với phương pháp khuếch tán).

Cấy ion tiến hành trong chân không nên đạt độ sạch rất cao, thực hiện ở nhiệt

độ phòng nên không ảnh hưởng tới phân bố tạp chất của các công đoạn khuếch tán trước đó.

Các ion năng lượng cao đi vào trong đế va chạm với các nguyên tử, sau mỗi

lần va chạm quỹ đạo di chuyển là ngẫu nhiên do vậy khi xét phân bố nồng độ tạp

chất ta sử dụng quy luật phân bố theo hàm Gauss.

Tuy nhiên, trong quá trình cấy ion, do va chạm nhiều nên nguyên tử đế sẽ bị

đẩy khỏi vị trí nút mạng. Nếu xảy ra với liều lượng lớn sẽ dẫn đến sai hỏng và vật

liệu trở thành vô định hình, để loại trừ sai hỏng và hoạt hoá ion, cần tiến hành ủ

nhiệt trong thời gian nhất định (nhiệt độ từ 400oC tới 600oC). Và để tránh hiện

tượng khuếch tán tiếp tục xảy ra, có thể ủ nhanh bằng tia laser hoặc bằng bức xạ hồng ngoại.

Hiện nay phương pháp cấy ion được sử dụng rộng rãi để pha tạp kênh cho

phép điều khiển mức điện áp ngưỡng, tạo các giếng P hoặc N, tạo vùng nguồn và

máng của MOSFET, cấy ion dễ khống chế nồng độ và phân bố tạp chất, điều này là

rất có ý nghĩa khi muốn thu hẹp kích thước.

1.5 Lắng đọng (Deposition)

Đây là quá trình làm cho một lớp mỏng các vật liệu khác nhau lắng dần

xuống và đọng lại trên bề mặt wafer. Các lớp mỏng vật liệu này có thể được lắng

đọng bằng nhiều kỹ thuật khác nhau như phương pháp bay hơi (evaporation),

phương pháp phún xạ (sputtering) và lắng đọng hơi hoá học (chemical- vapor deposition).

Trong phương pháp bay hơi, một chất liệu rắn được đặt trong một bình chân

không và nung nóng tới khi bay hơi. Hơi vật liệu sẽ được lắng đọng trên wafer có

nhiệt độ thấp hơn, và tạo thành các lớp mỏng trên bề mặt của wafer. Chiều dày lớp

lắng đọng sẽ phụ thuộc vào nhiệt độ và thời gian bay hơi, thông thường thì nó khoảng là 1μm. 7

Phương pháp phún xạ là phương pháp sử dụng các ion dương bắn phá vào

cathode mà trên đó phủ lớp vật liệu cần dùng để lắng đọng. Các nguyên tử của vật

liệu này sẽ bật ra và lắng đọng vào wafer được đặt ở anode. Phương pháp này

thường được tiến hành trong buồng chân không.

Còn phương pháp lắng đọng hơi hoá học là phương pháp tạo ra lớp lắng

đọng bằng các phản ứng hoá học hoặc nhiệt phân ở pha hơi, xảy ra ở bề mặt của

wafer. Phương pháp lắng đọng này thường dùng để lắng đọng polysilicon, silicon

dioxide (SiO2) hay silicon nitride (Si3N4). Thông thường, phương pháp lắng đọng

hơi hoá học thường được thực hiện ở áp suất khí quyển hoặc thực hiện ở áp suất

thấp tại nơi mà sự khuyếch tán có cường độ lớn.

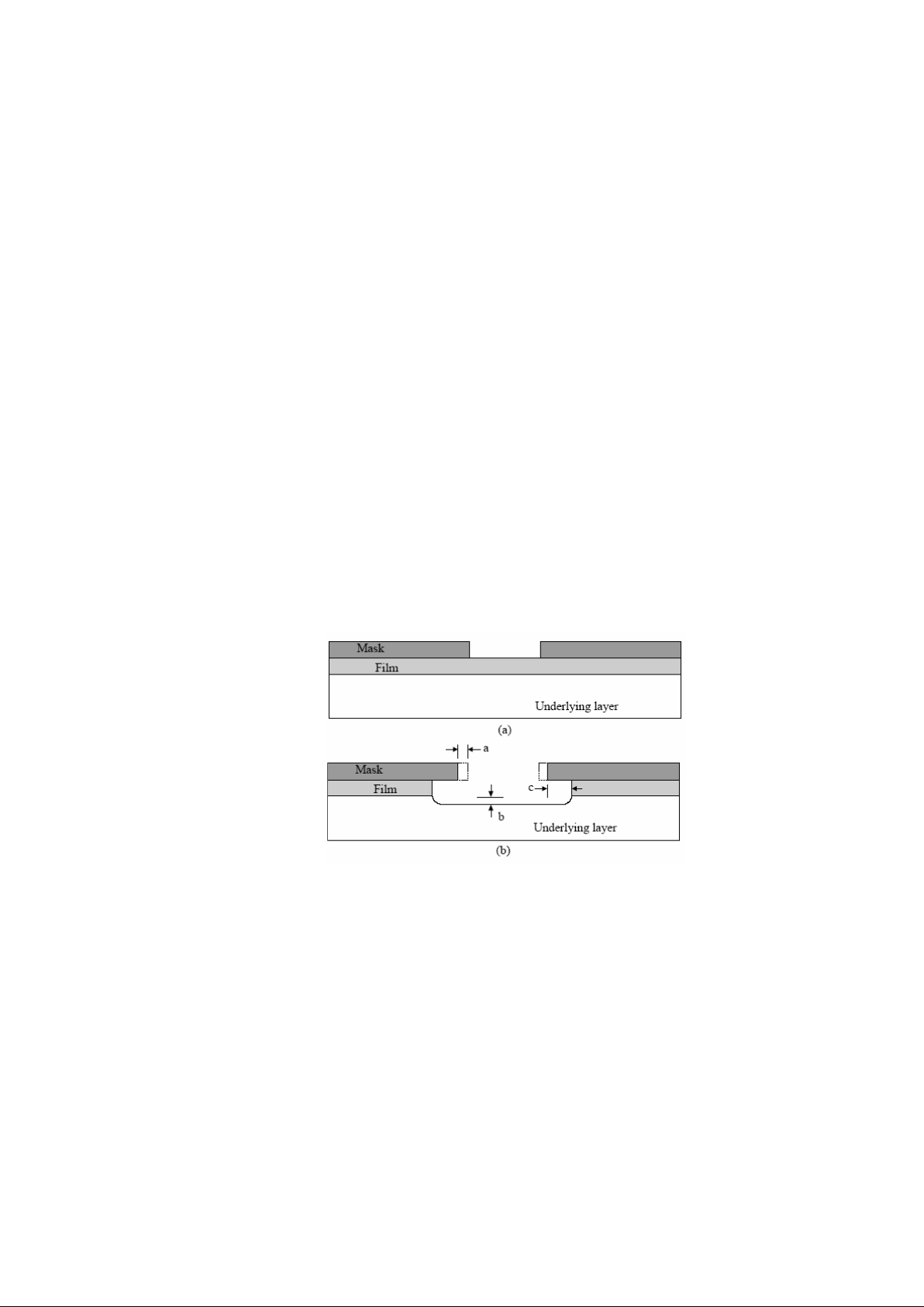

1.6 Ăn mòn (Etching)

Mục tiêu của etching là lấy đi phần thừa của lớp vật liệu nào đó mà ta cần

loại bỏ. Đây là khâu quan trọng cần thiết để mài bóng, làm sạch bề mặt và “mở cửa

sổ” trong vật liệu cách điện.

Minh hoạ quá trình ăn mòn theo hình vẽ (hình 1.8) sau:

Hình 1.8: Quá trình ăn mòn. (a) trước khi ăn mòn, (b) sau khi ăn mòn

Chúng ta có 3 lớp: lớp đế, lớp bảo vệ và lớp cần ăn mòn. Trong quá trình ăn

mòn chúng ta cần tính toán đến 3 sai số. Ăn mòn lớp bảo vệ (a), ăn mòn không

mong muốn lớp cần ăn mòn (c) và ăn mòn bề mặt lớp đế(b).

Có hai dạng ăn mòn chính là ăn mòn đẳng hướng và ăn mòn dị hướng. Ăn

mòn đẳng hướng có tốc độ ăn mòn giống nhau với mọi hướng, còn ăn mòn dị

hướng có tốc độ ăn mòn theo một hướng nào đó trội hơn hẳn

Hai kỹ thuật ăn mòn chính là ăn mòn khô và ăn mòn ướt. Ăn mòn ướt thông

thường là ăn mòn đẳng hướng, sử dụng các dung dịch hoá học như HF để ăn mòn

Silicon dioxide, H3PO4 ăn mòn Silicon Nitride, axit nitric, acetic axít acetic hay axít 8

hydrofluoric để loại bỏ lớp polysilicon, ăn mòn loại này phụ thuộc rất nhiều vào

thời gian và nhiệt độ và phải rất chú ý tới sự an toàn khi sử dụng axít. Ăn mòn khô

là kỹ thuật ăn mòn sử dụng khí gas thổi vào phần cần ăn mòn, đây là phương pháp

dùng để ăn mòn dị hướng. 1.7 Epitaxy

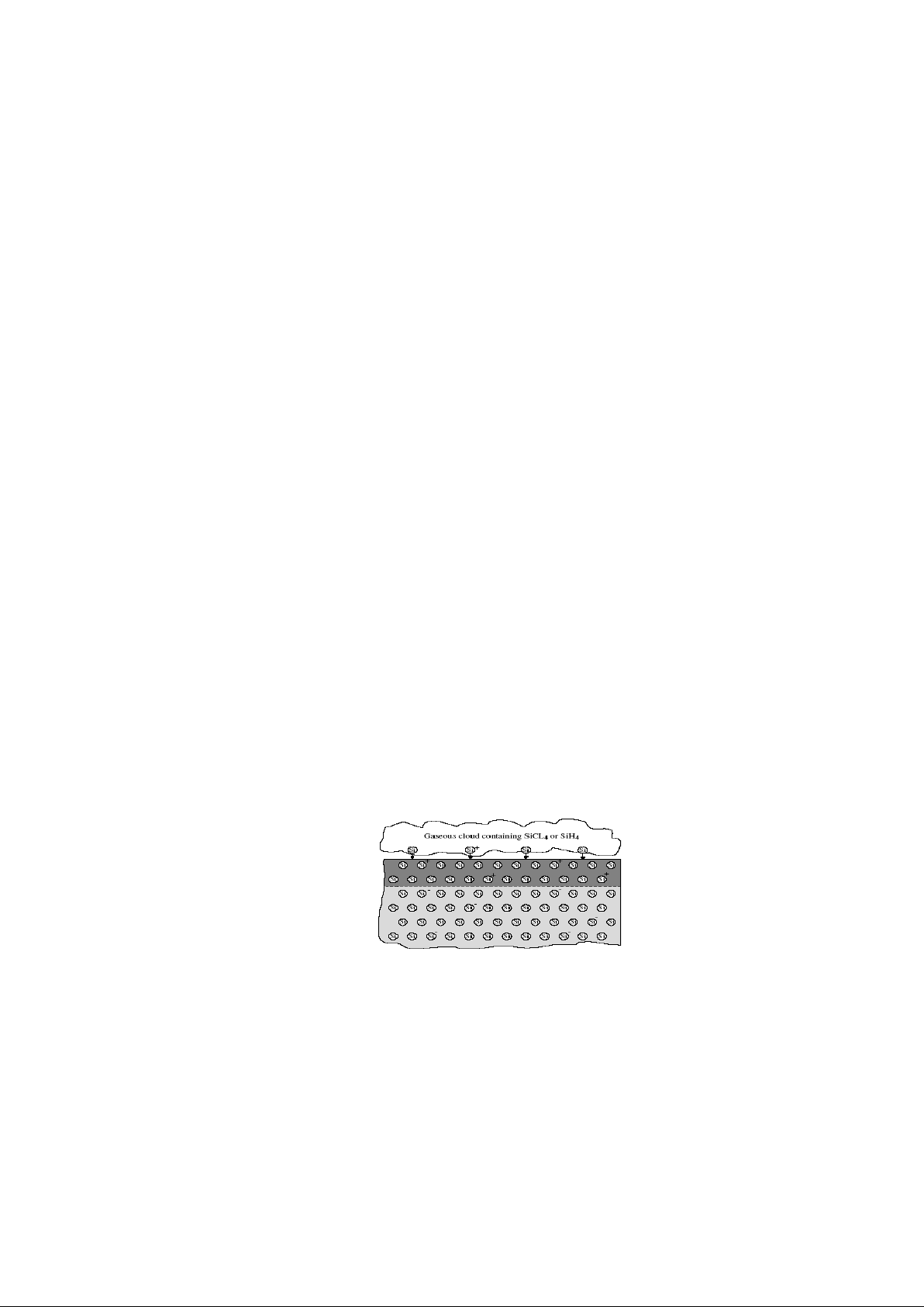

Trong quá trình chế tạo các linh kiện có cấu trúc phức tạp ví dụ như

transistro lưỡng cực (BJT), khuếch tán được sử dụng nhiều lần có nhược điểm là

khó kiểm soát được chính xác nồng độ tạp chất mong muốn ở những vị trí cố định.

Để giải quyết vấn đề này kỹ thuật nuôi cấy epitaxial là cần thiết.

Quá trình epitaxy (hình 1.9) là quá trình tạo một lớp mỏng tinh thể loại này

lên trên bề mặt tinh thể loại khác. Đây là sự kết tinh định hướng trong khi cấy

những màng đơn tinh thể, là quá trình phát triển những lớp tinh thể có mạng tinh thể

định hướng trùng với cấu trúc tinh thể của đế. Nồng độ tạp chất trong lớp epi có thể

được điều khiển độc lập và có thể lớn hơn hay nhỏ hơn so với nồng độ tạp chất

trong vật liệu đế. Thông thường, loại tạp chất trong vùng nuôi cấy epitaxy là loại

đối lập với tạp chất của để và chiều dày của lớp epi trong mạch tích hợp có thể thay

đổi từ 1μm-20μm.

Việc nuôi cấy này được thực hiện khi đặt wafer trong môi trường bao gồm

tetrachloride (SiCl4) hoặc silane (SiH4), ở nhiệt độ cao phản ứng hoá học diễn ra,

các thành phần silicon được lắng đọng lên bề mặt của wafer, kết quả là lớp silicon

mới được kết tinh trên bề mặt wafer.

Hình 1.9 : Epitaxy 9

2. Các phần tử cơ bản trong công nghệ CMOS

Các phần tử cơ bản trong công nghệ CMOS sẽ bao gồm các phần tử tích cực

như Transistor trường (MOSFET), Transistor lưỡng cực (BJT) và các phần tử thụ

động như tụ điện, điện trở. Sau đây chúng ta sẽ lần lượt xem xét các phần tử này ở khía cạnh chế tạo.

2.1 Các phần tử tích cực trong công nghệ CMOS

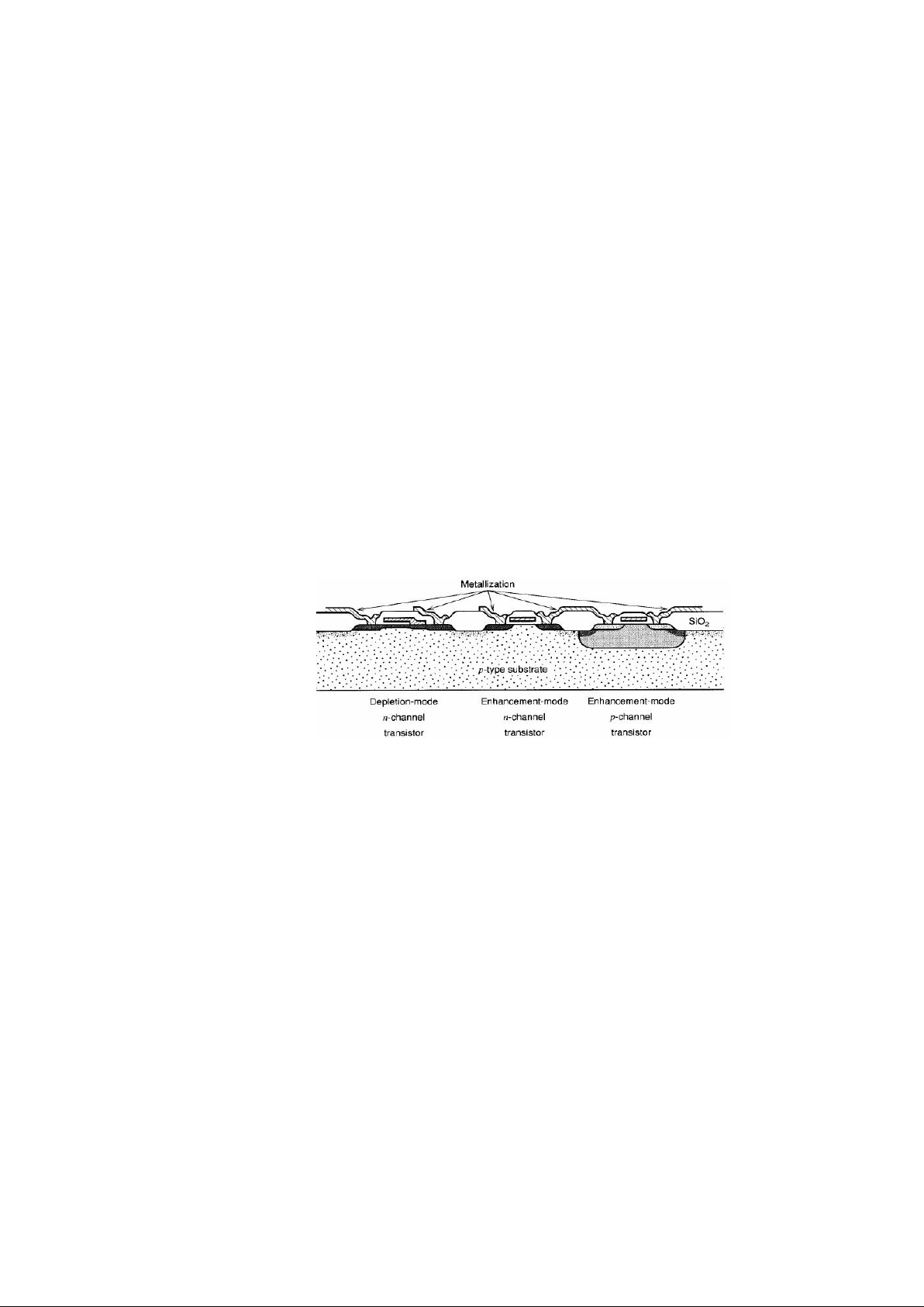

2.1.1 MOSFET (Metal oxide semiconductor field effect transistor)

MOSFET có hai loại là MOSFET “kênh cảm ứng” và MOSFET “kênh tạo sẵn.”

MOSFET kênh tạo sẵn hoạt động theo chế độ làm nghèo hạt dẫn (deleption-mode),

còn MOSFET kênh cảm ứng thì hoạt động theo chế độ làm giàu hạt dẫn

(enhancement-mode). Hiện nay, người ta thường dùng MOSFET loại kênh cảm ứng

để thiết kế IC vì loại này có quá trình chế tạo đơn giản hơn và cho phép linh hoạt

hơn trong việc thiết kế. Dưới đây là các cấu trúc MOSFET cơ bản (hình2.10):

Hình 2.10: Cấu trúc các loại MOSFET

Cực cổng (Gate) được phủ bởi lớp kim loại như nhôm hay polysilicon và

được pha tạp với nồng độ cao. Giữa lớp kim loại này và đế (Substrate) là lớp oxit

SiO2 mỏng, hình thành tụ giữa Gate và đế. Nồng độ hạt dẫn trong kênh dẫn phụ

thuộc vào điện áp VG do đó VG được gọi là điện áp phân cực. Đặc tính quan trọng

nhất của CMOS là dùng điện áp đặt trên gate để điều khiển dòng nguồn-máng cho

phép MOSFET có độ cách ly về điện rất cao giữa gate và nguồn/máng. 10

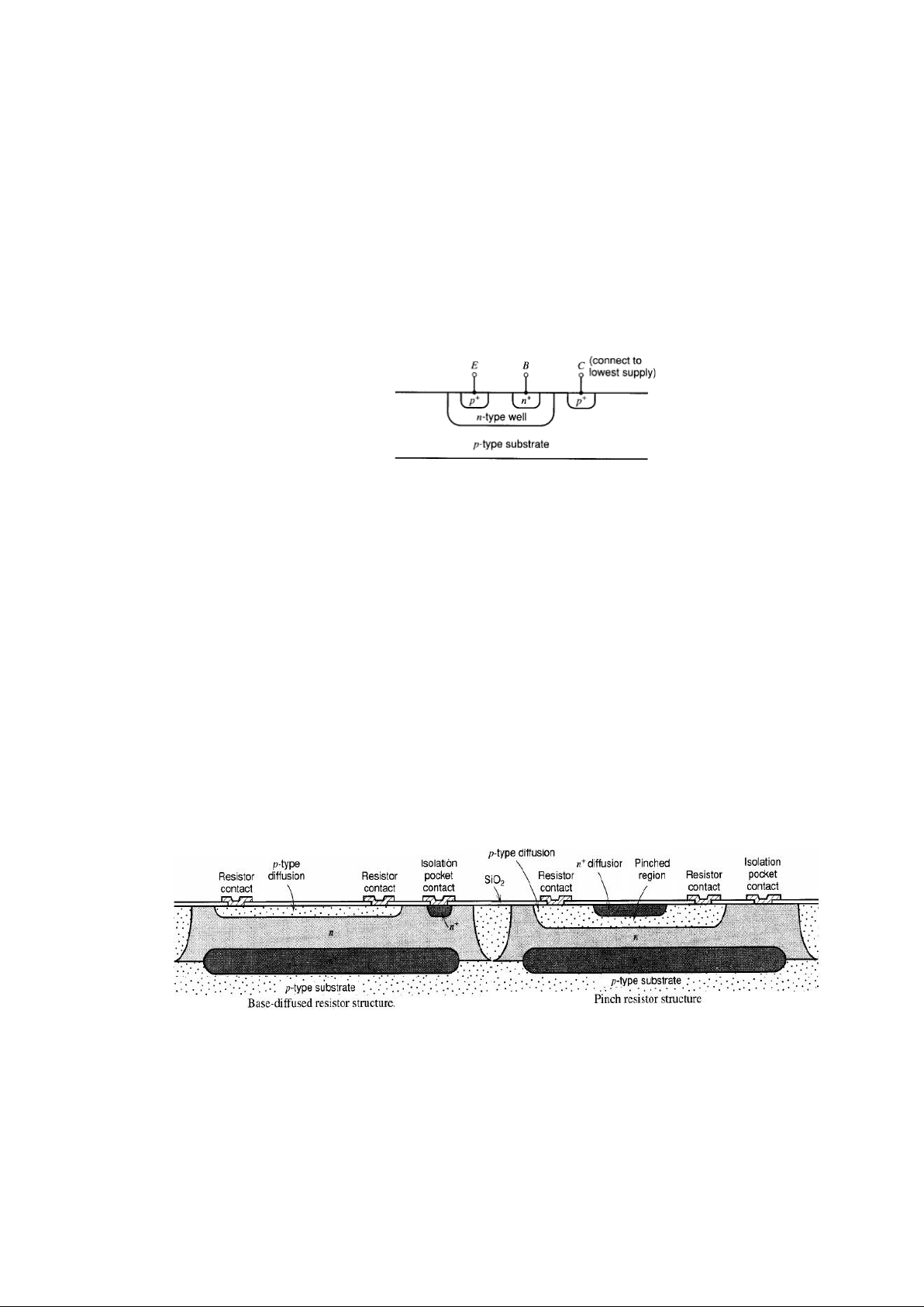

2.1.2 Transitor lưỡng cực (BJT)

Trong công nghệ CMOS, người ta cũng có thể chế tạo được transistor lưỡng

cực với cực collector được gắn với đế. Hình 2.11 chỉ ra cấu trúc của BJT. Vùng

giếng tạo nên cực Base của transistor và vùng khuyếch tán loại p trong giếng tạo

nên cực emitter. Đây là transistor loại pnp và được tạo ra với đế loại p. Nó rất hay

được sử dụng các bộ tạo điện áp tham chiếu (references voltage.)

Hình 2.11: Cấu trúc Transistor lưỡng cực trong công nghệ CMOS

2.2 Các phần tử thụ động sử dụng trên công nghệ MOS

Trong thiết kế IC bên cạnh các linh kiện tích cực là các MOSFET thì các linh

kiện thụ động cũng góp phần rất quan trọng. Các linh kiện thụ động đó là các điện

trở và các tụ điện. Điện trở có nhiều loại bao gồm điện trở khuếch tán, điện trở

poly-silicon, điện trở giếng. Tụ điện gồm có tụ điện được tạo thành bởi hai lớp

poly-poly, metal-poly, silicon-silicon, metal-metal.

2.2.1 Điện trở trong công nghệ CMOS

a) Điện trở khuếch tán (Diffused Resistor): Chúng ta có thể sử dụng các vùng

khuếch tán tạo nguồn và máng để tạo điện trở. Cấu trúc của điện trở này được mô tả

bởi hình vẽ sau (hình 2.12):

Hình 2.12: Cấu trúc điện trở khuếch tán trong công nghệ CMOS

b) Điện trở Polisilicon (Polysilicon Resistor): Trong công nghệ CMOS các cực

Gate thường được tạo ra bằng các lớp polysilicon. Người ta cũng thường sử dụng

lớp này để làm điện trở. Về mặt hình dạng thì điện trở này cũng tương tự như điện trở khuếch tán. 11

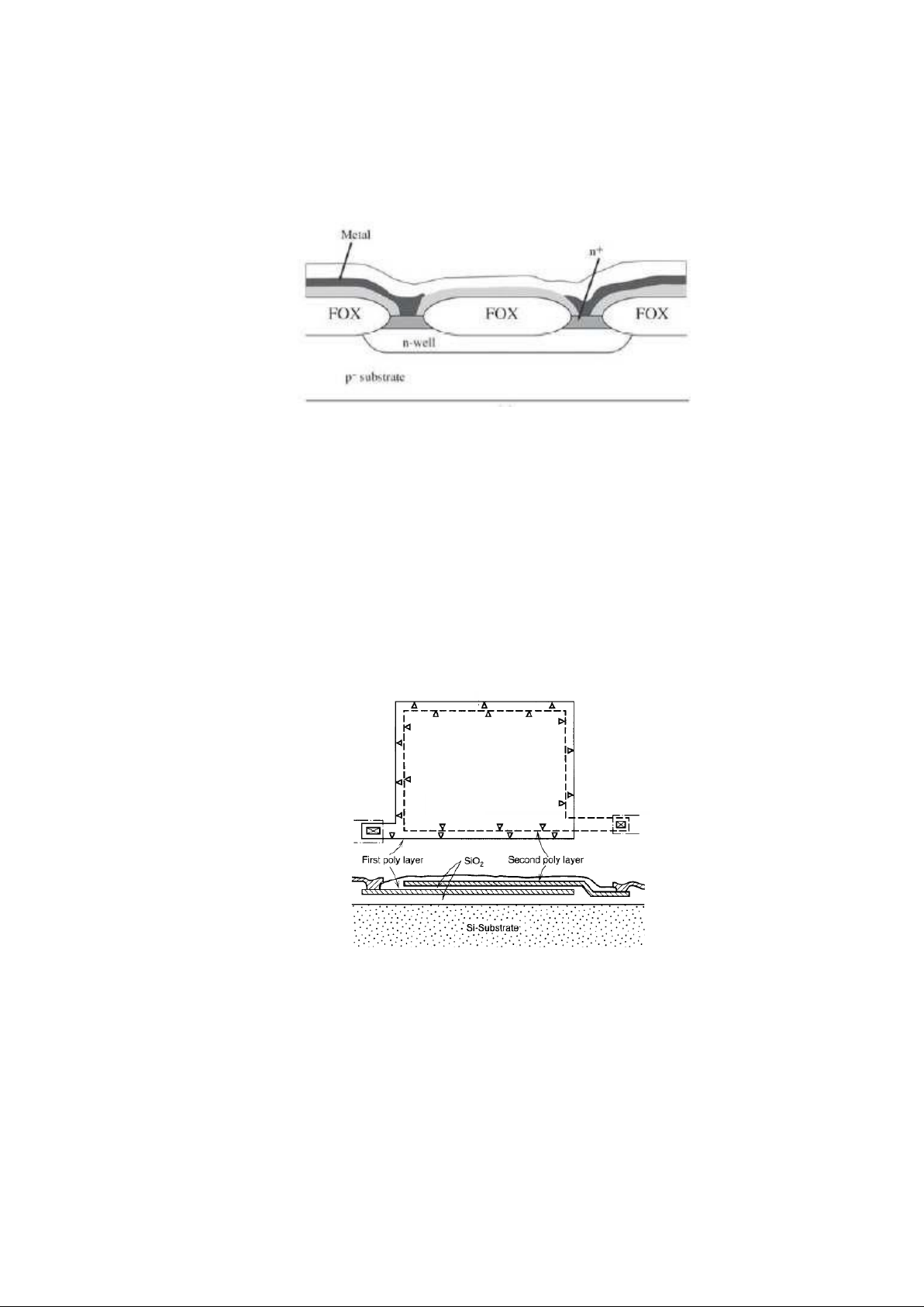

c) Điện trở giếng (Well Resistor): Trong công nghệ CMOS, giếng thường được sử

dụng làm thân của điện trở. Giếng là một vùng có sự pha tạp rất nhỏ và do đó giá trị

điện trở có thể đạt được giá trí khá lớn.

Hình 2.13: Cấu trúc điện trở giếng trong công nghệ CMOS

2.2.2 Tụ điện trong công nghệ MOS

Trong công nghệ CMOS tụ điện đóng vai trò rất quan trọng. Có nhiều loại tụ

điện được sử dụng trong công nghệ CMOS, nhưng thực tế người ta thường sử dụng tụ poly-poly và tụ MOS.

a) Tụ điện poly-poly: Trong công nghệ MOS các lớp poly được sử dụng với rất

nhiều mục đích. Cấu trúc tiêu biểu của tụ điện sử dụng hai lớp poly được mô tả như hình 2.14:

Hình 2.14: Cấu trúc tụ điện poly-poly trong công nghệ CMOS

Khoảng cách giữa hai phiến này thường có thể so sánh với chiều dày lớp oxit

của MOSFET. Trong cấu trúc này điều đáng chú ý là điện dung ký sinh giữa phiến

poly cực đáy với các lớp vật liệu ở phía dưới. Điện dung này có giá trị tuỳ theo diện

tích của cực đáy, thường có giá trị từ 10% đến 30% điện dung của chính tụ poly-

poly. Các khía cạnh khác cần quan tâm với cấu trúc tụ này là sai số, hệ số phụ thuộc

của điện dung vào nhiệt độ và điện áp. Các hệ số phụ thuộc này phụ thuộc rất nhiều 12

vào mức độ pha tạp trong các phiến tạo thành các cực của tụ và hằng số điện môi.

Cụ thể là khi ta tăng độ pha tạp lên thì hệ số phụ thuộc điện áp sẽ giảm. Với nồng

độ tạp chất thông thường thì hệ số phụ thuộc vào điện áp khoảng 50ppm/V, còn hệ

số nhiệt là 50ppm/0C.

b) Sử dụng transistor MOS làm tụ: Chúng ta có thể sử dụng trực tiếp transistor

MOS như là một tụ điện khi ta phân cực cho nó làm việc trong vùng triode. Với

cách sử dụng này thì Gate sẽ là một mặt cực, các cực còn lại của mosfet sẽ được nối

với nhau tạo thành mặt cực còn lại của tụ điện. Nhược điểm của cấu trúc này là khi

điện áp đặt vào cực Gate thay đổi sẽ gây ra một sự thay đổi lớn trên bề mặt của cực

còn lại. Điều này làm cho hệ số phụ thuộc điện áp của tụ điện rất lớn. Tuy nhiên

trong những ứng dụng không quá nhạy cảm với giá trị của tụ điện thì cấu trúc tụ này

có thể sử dụng rất hiệu quả.

Ngoài ra, còn có cấu trúc tụ sandwich là kết hợp của hai cấu trúc trên, cụ thể là sử

dụng MOSFET làm tụ, đồng thời tận dụng ngay lớp poly gate của tụ mosfet làm

thành một bản cực của một tụ poly-poly khác, lớp poly làm bản cực còn lại của tụ

poly-poly sẽ được nối với cực còn lại của tụ mosfet. Như vậy ta sẽ tạo ra một tụ

điện có giá trị lớn trong khi diện tích sẽ nhỏ hơn so với một tụ mosfet hay tụ poly-

poly có giá trị tương đương. 13

Tóm lại, để có một cái nhìn tổng quan về toàn bộ quá trình chế tạo, ta xem xét các

công đoạn chế tạo linh kiện PMOS và NMOS trên phiến wafer loại P như sau (hình 2.15):

Hình 2.15: Các bước chế tạo cơ bản trong công nghệ CMOS

Đầu tiên là một lớp silicon dioxide được hình thành trên bề mặt phiến đế loại

p. Sau đó một lớp cảm quang được lắng đọng lên trên bể mặt lớp oxide, vùng giếng

n được hiện hình sau khi chiếu sáng, tiếp đó tạp chất loại n bắt đầu được pha tạp

bằng phương pháp cấy ion (hình a). Tiếp theo lớp cảm quang được loại bỏ và quá

trình oxidation được tiến hành trong điều kiện nhiệt độ cao đồng thời tạp chất loại n

được khuếch tán sâu vào trong đế, Si3N4 được lắng đọng phủ trên lớp oxide bảo vệ

lớp oxide mỏng cho vùng gate của MOS (hình b, c). Tiếp đó các quá trình phủ lớp

poly tạo cực gate và tạo source-drain cho PMOS và NMOS được tiến hành (tạo

drain-source cho PMOS và NMOS phải được tiến hành lần lượt vì tạp chất ở cực

drain-soure của hai transistor này là khác loại). Cuối cùng ta tạo các vùng contact để

nối dây kim loại (metal). 14 Tác giả

Nguyễn Thanh Yên, Tốt nghiệp đại học bách khoa Hà Nội, chuyên

ngành điện tử viễn thông năm 2005, và nhận bằng thạc sỹ khoa học,

chuyên nghành kỹ thuật vi mạch, đại học quốc gia Singapore năm

2012. Trước khi đảm nhận vị trí tổng giám đốc tại công ty CoAsia

SEMI Vietnam hiện tại, anh Yên sáng lập đơn vị LSI cung cấp dịch

vụ thiết kế chip vi mạch cho các khách hàng quốc tế tại FPT

Software, tại đây anh Yên đã thành công thiết lập, quản lý, vận hành

và phát triển đội ngũ 130 kỹ sư thiết kế vi mạch chỉ trong 3 năm từ

con số không ban đầu. Từ năm 2008 tới năm 2014, anh Yên làm

việc cho công ty Infineon Technologies, phụ trách thiết kế các mạch điện tương tự cho sản

phẩm biến đổi nguồn và vi điều khiển 32 bit sử dụng trong các ứng dụng cho ô tô. Trước

năm 2008, anh Yên làm việc cho công ty Active-Semi, nay là công ty Qorvo Việt Nam với

vai trò là kỹ sư thiết kế vi mạch tương tự cho các sản phẩm quản lý nguồn. Anh Yên còn là

thành viên quản trị cộng đồng kỹ sư vi mạch Việt Nam với hơn 26,000 thành viên. Anh

Yên rất tích cực tham gia vào các hoạt động phát triển cộng đồng vi mạch Việt Nam, bao

gồm: viết bài, thực hiện tổ chức các hội thảo trực tuyến, trực tiếp và các khóa đào tạo miễn

phí về “Thiết kế chip” cho các bạn sinh viên muốn củng cố kiến thức nền tảng liên quan

đến thiết kế chip vi mạch ./.

Tài liệu tham khảo

1. Paul R. Gray, Paul J. Hurst, Stephen H. Lewis, Robert G. Meyer, “Analysis and

Design of Analog Integrated Circuits,” Wiley Publishers, 2001.

2. Nguyễn Đức Chiến, “Giáo trình Kỹ thuật Vi điện tử”, Đại học Bách khoa Hà Nội, 2002.

3. Phùng Hồ, “Giáo Trình Vật Lý Điện Tử”, NXB Khoa học và Kỹ thuật, 2007.

4. Nguyễn Thanh Yên, “Công Nghệ CMOS và thiết kế mạch IC tương tự”, Đồ án

tốt nghiệp, K45, ĐHBKHN, 2005. 15