Preview text:

ĐỀ CƯƠNG ÔN TẬP

1.Trình bày định nghĩa IC màng mỏng? Nêu ưu nhược điểm của hai phương pháp được

dùng trong chế tạo IC màng mỏng là: phún xạ và bay hơi trong chân không.

2. Tiêu chí quan trọng đánh giá mức độ phòng sạch trong quang khắc là gì? Có bao

nhiêu hệ xác định phòng sạch? Nêu ý nghĩa của từng hệ?

3. Trình bày định nghĩa quang khắc trong công nghệ vi điện tử. Nêu các bước thực hiện

quá trình truyền hình ảnh trong quang khắc?

4. Kể tên các phương pháp chiếu sáng được dùng trong quang khắc? Trình bày ưu,

nhược điểm của từng phương pháp?

5. Để chế tạo chuyển tiếp P-N người ta thường sử dụng công nghệ nào? Nêu ưu, nhược

điểm của phương pháp pha tạp bằng cấy ion.

6. Khuếch tán là gì? Nêu vai trò của khuếch tán trong công nghệ chế tạo IC. Kể tên một

số cơ chế khuếch tán thông dụng.

7. Thông số quan trọng nhất của MOSFET là gì? Ý nghĩa của thông số? Nêu các giai

đoạn của quá trình chế tạo CMOS.

8. Ứng dụng của oxy hóa nhiệt là gì? Có mấy phương pháp oxy hóa nhiệt? Ý nghĩa của

mô hình Deal- Grove? Mô hình được áp dụng trong giai đoạn nào của quá trình oxy hóa?

9. Nêu khái niệm phương pháp epitaxy? Kể tên các phương pháp epitaxy.

10. Nêu các thông số xác định chất lượng công cụ chiếu sáng được sử dụng trong quá

trình truyền hình ảnh? Trình bày ý nghĩa của từng thông số? Bài 1

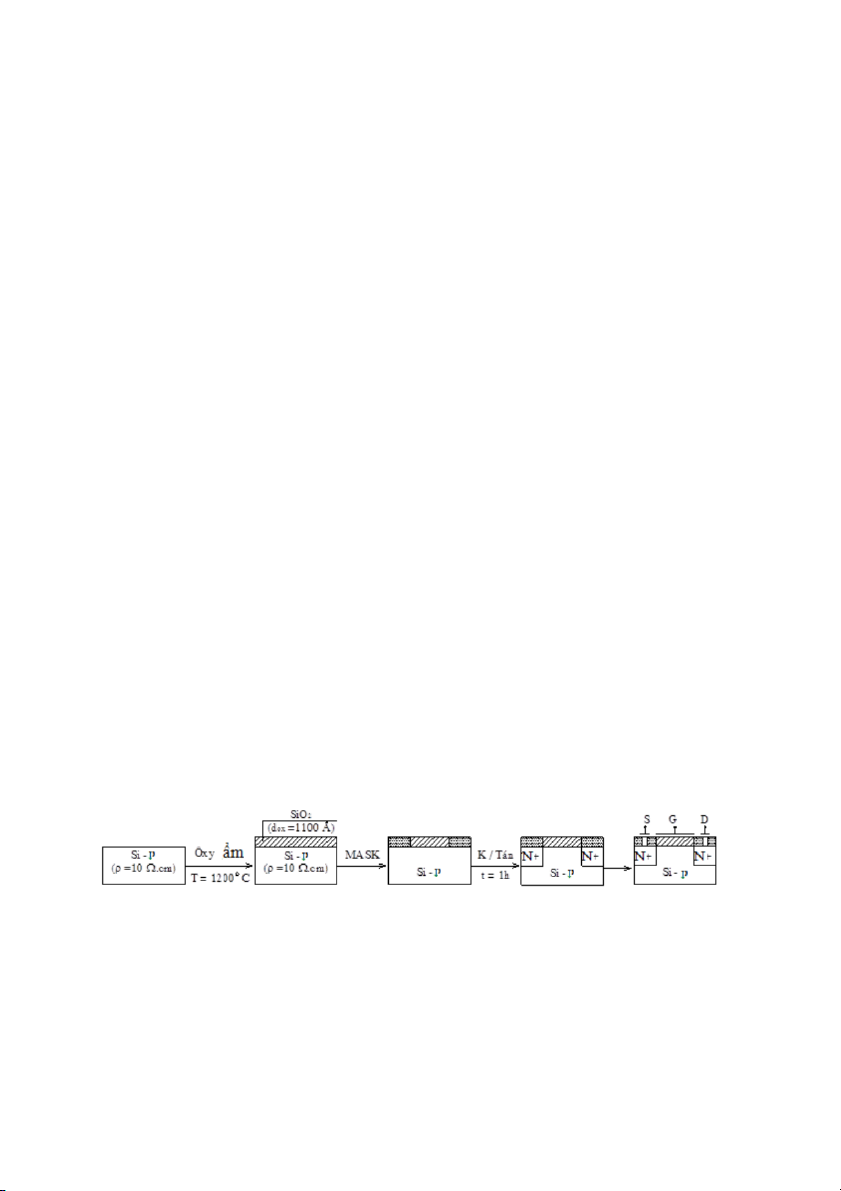

Một IC MOS được chế tạo theo quy trình công nghệ sau:

1. Hãy xác định thời gian cần thiết để nhận được lớp SiO 0 2 có chiều dày 1100A .

2. a) Xác định nhiệt độ cần thiết để tiến hành khuếch tán tạp chất để nhận được lớp khuếch

tán có chiều sâu xj = 1,7µm. Biết rằng khuếch tán được tiến hành từ nguồn hữu hạn với

nồng độ tạp chất bề mặt phiến Si là 1,2.1020cm-3

b) Xác định lượng nguyên tử tạp chất Phospho khuếch tán vào phiến Si trên một đơn vị diện tích bề mặt.

3. Giả sử mật độ điện tích bề mặt Si/SiO 10 Φ 2 là: Qox = 3.10

q.cm-2; Hiệu công thoát kim loại là ms

= -0,6V; εSi =11,7; εox =3,9; εo =8,85.10-12 F/m; n -3

i= 1,5.1010 cm . Xác định điện áp ngưỡng của transistor MOS. Bài 2

1. Để tiến hành khuếch tán Bo từ một nguồn tạp chất vô hạn vào Si loại n có nồng độ tạp bề mặt là N 20 0 S= 1,5.10

cm-3 tại nhiệt độ là T= 1200 C trong thời gian là 1giờ, xác định

gradient nồng độ tạp chất ở bề mặt phiến Si và ở tọa độ x -3 j cho biết NB=1,2.1015 cm

2. Cho một Tranzitor MOS kênh n với các thông số sau: Chiều dày lớp oxide d 15 -3 Φ

0x=80nm. Nồng độ pha tạp đế NA= 5.10 cm . Hiệu công thoát ms =

0,6V. Mật độ điện tích bề mặt: Q -2 ε ox/q=5.1010 cm ;

o =8,85.10-12 F/m; ε Si =11,7; εox =3,9; ni= 1,5.1010 cm-3

Tính điện áp ngưỡng của tranzitor MOS. Bài 3

1 Người ta cần lớp oxide cổng dày 1000A0 theo hai bước. Đầu tiên nhận lớp oxide dày

450A0, sau đó phiến được oxy hoá lại để được chiều dày tổng cộng là 1000A0. Nếu oxy hoá

được tiến hành tại 11000C trong hơi nước, hãy tính thời gian cho mỗi lần oxy hoá

2. Cho MOSFET kênh n với các thông số:

Chiều dài kênh L = 1,5 µm; chiều rộng kênh W= 10 µm; chiều dày lớp oxide d Φ

ox = 50nm; nồng độ pha tạp đế NA = 1.1015cm-3; hiệu công thoát

ms = -0,6V; mật độ điện tích bề mặt: Q 10 ε 10 -3 o/q= 5.10

cm-2; o =8,85.10-12 F/m ; εox =3,9; εSi =11,7; ni= 1,5.10 cm ; độ linh động

của điện tử μ =450 cm2/V.s; của lỗ trống μ = 200 cm2/V.s

Tính điện áp ngưỡng, độ hỗ dẫn gm tại UGS = 2,5V Bài 4

Cho IC MOS được chế tạo trên đế Si-p có điện trở suất là ρ = 5Ω.cm

1. Để chế tạo vùng Si loại n người ta tiến hành khuếch tán tạp P từ một nguồn hữu hạn trong

môi trường nhiệt độ là T= 12000C trong thời gian 3,5 giờ. Tính chiều sâu khuếch tán của

chuyển tiếp p-n tạo thành, biết nồng độ tạp trên bề mặt phiến Si là 3,5.1017 cm-3

2. Hãy xác định thời gian cần thiết để nhận được lớp SiO 0

2 dưới cực cửa có chiều dày 500A ,

biết rằng quá trình oxy hóa được tiến hành trong môi trường oxy hóa khô ở nhiệt độ 11000C.

3. Xác định điện áp ngưỡng của transistor N-MOS trước khi cấy ion điều chỉnh, biết Qox =

3.1010q.cm-2; hiệu công thoát Φ 10

ms =- 0.6V; ε o =8,86.10-12 F/m; ε ox =3,9; ε Si =11,7; ni= 1,5.10 cm-3 Bài 5

1. Giả sử ion Bor (B) được cấy vào đế silic có đường kính 200mm với năng lượng

100KeV trong thời gian 1 phút. Tính nồng độ tạp chất cực đại và dòng ion cần dùng.

2. MOSFET kênh n sau khi chế tạo có các thông số sau: Chiều dày lớp SiO2 là 40nm, điện

áp ngưỡng VT = 0,5V. Người ta muốn có một MOSFET kênh n với VT = 1,5V; vậy phải làm gì và

làm như thế nào? Biết εo =8,85.10-12 F/m; εox =3,9; εSi =11,7; n -3 i= 1,5.1010 cm .

3. Một IC MOS được chế tạo trên đế Si-p có điện trở suất là ρ = 5Ω.cm.

Để tạo vùng Si loại n người ta tiến hành khuếch tán tạp P từ một nguồn hữu hạn trong môi

trường nhiệt độ là T= 10500C trong thời gian 4h. Tính chiều sâu khuếch tán của chuyển tiếp p-

n tạo thành, biết nồng độ tạp trên bề mặt phiến Si là 4.1017cm-3. Bài 6

1, Người ta tiến hành oxy hóa để tạo lớp SiO 0

2 trên đế Si trong hơi nước ở nhiệt độ 1200 C

trong thời gian 90 phút. Tính chiều dày lớp oxide? Tính thời gian để tạo lớp oxide cùng chiều

dày nếu oxy hóa trong môi trường O2 khô.

2, Giả sử phiến Silic có đường kính 300mm được pha tạp bởi phương pháp cấy ion từ nguồn

Bo có năng lượng 80KeV, liều cấy là 5.1014ion/cm .

2 Tính nồng độ lớn nhất của Bo biết độ lệch

chuẩn ∆Rp = 64nm. Giả sử thời gian cấy 10 phút, tính dòng ion.

3. MOFET sử dụng trong mạch tích hợp có Al làm cực cửa trên đế Si-n với các kích thước như

sau: L= 0,6 μ m; W=15 μ m; μ =230 cm /V.s; C 2 2

ox=3.10-8 F/cm ; điện áp ngưỡng VT= -2V.

Tính dòng máng bão hòa IDS khi VG = -5V. Bài 7

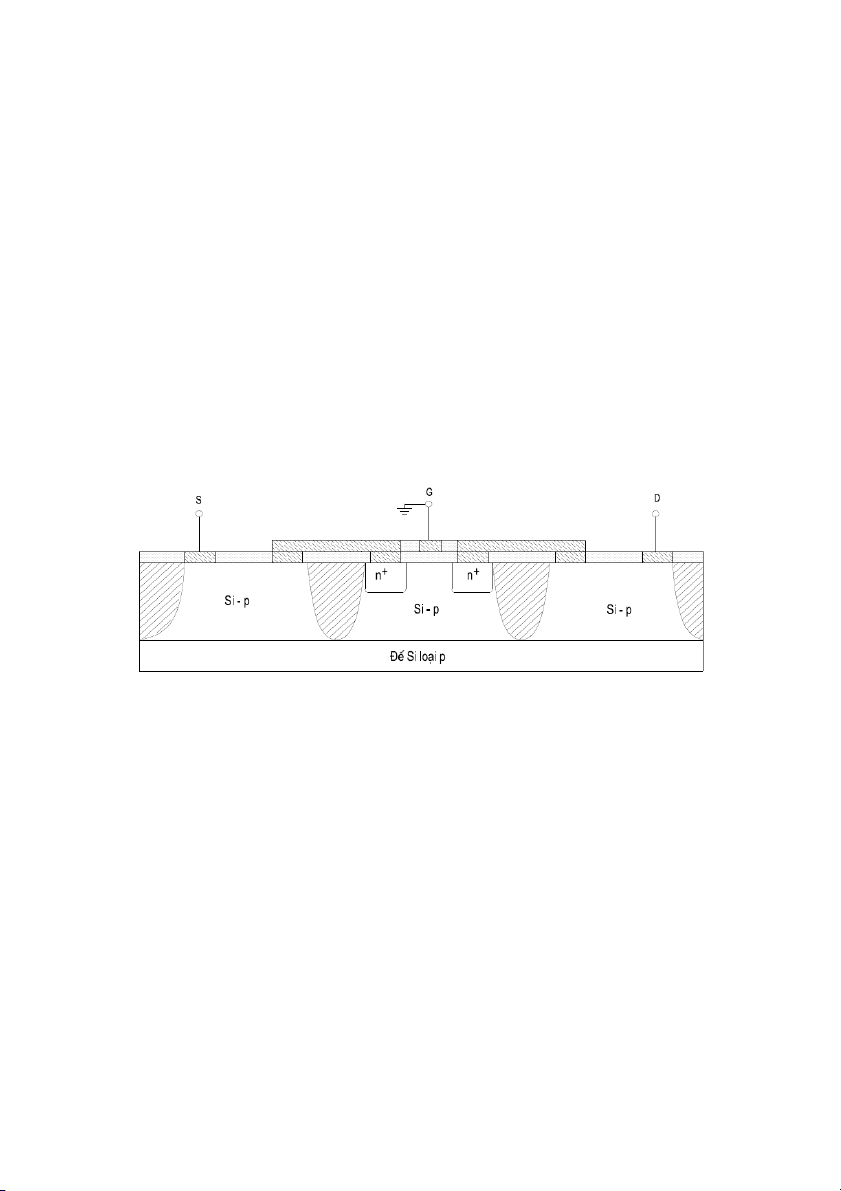

Cho một IC có cấu trúc như hình vẽ dưới đây

IC được chế tạo trên đế Si-p có điện trở suất ρ=10 Ω. cm

1. Hãy xác định chiều sâu khuếch tán của các vùng nguồn và máng của transistor, tính lượng

tạp chất nguyên tử Bo khuếch tán vào phiến silic trên một đơn vị diện tích, biết rằng chúng

được khuếch tán bằng tạp phosphorus với nồng độ bề mặt 2,1.1020cm-3 từ nguồn vô tận ở

nhiệt độ T=10500C trong thời gian 90 phút.

2. Hãy xác định thời gian cần thiết để nhận được lớp SiO 0

2 dưới cực cửa có chiều dày 900 A ,

biết rằng quá trình ôxy hoá tiến hành trong môi trường ôxy khô ở nhiệt độ T= 12000C.

3. a) Xác định điện áp ngưỡng của MOS, biết rằng Q -2 ε

ox/q=5.1010cm ; Si =11,7; ε ox =3,9; ε o =8,85.10-12 F/m; n -3 Φ i= 1,5.1010 cm ; ms = -0,6V.

b) Nếu dòng máng cho bởi công thức I 2 2

DS= ½.K(VGS-VT) . Tính gm tại VGS = 2V biết K = 1mA/V . Bài 8

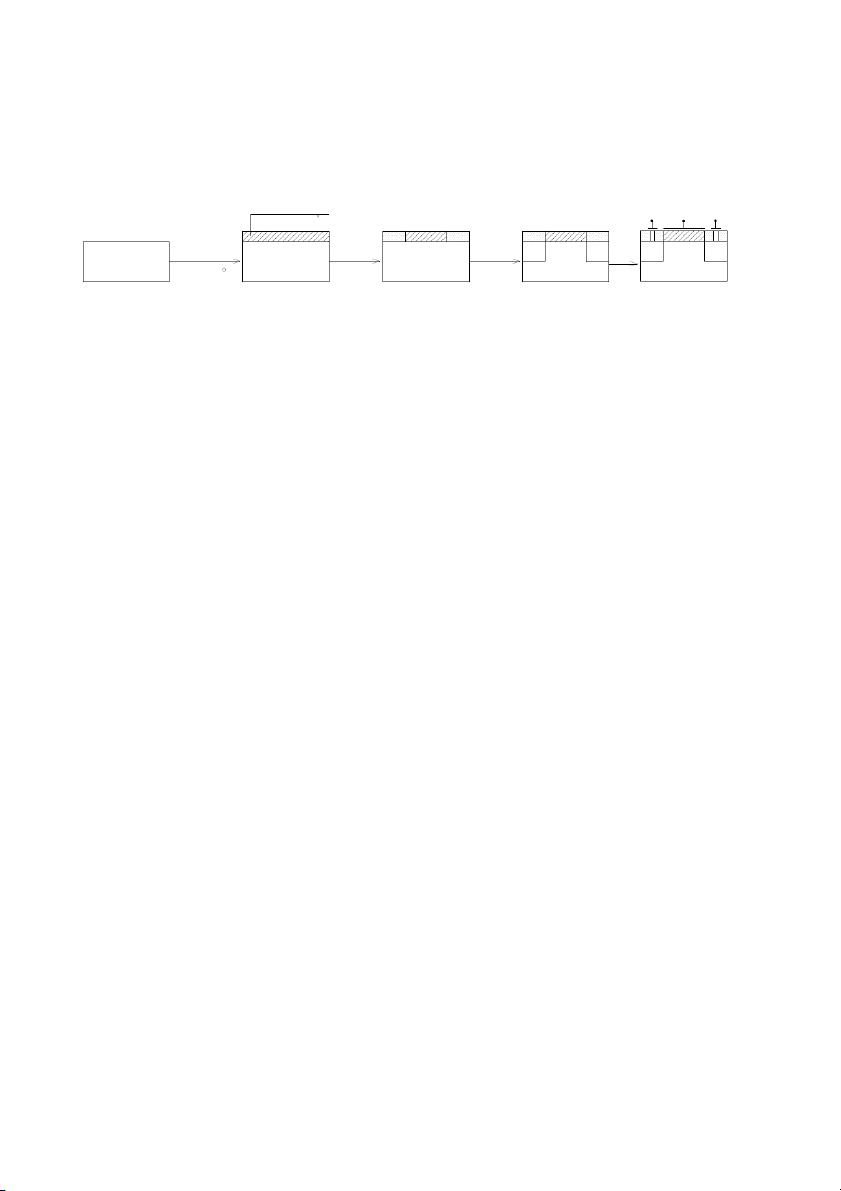

Một phần tử ICMOS được chế tạo theo sơ đồ quy trình công nghệ sau đây: SiO 2 S G D (dox =1100 A) Si - n ¤xy kh« Si - n MASK K / T¸n P+ P+ P+ P+ (10 Ωcm) (10Ωcm) T = 1200 C Si - n t = 1h Si - n Si - n

1. Hãy xác định thời gian cần thiết để nhận được lớp SiO2 có chiều dày là dox=1100A0.

2. Hãy xác định nhiệt độ cần thiết để tiến hành quá trình khuếch tán có chiều sâu Xj=2,1 μ m.

Xác định lượng tạp chất nguyên tử Bo khuếch tán vào phiến Si trên một đơn vị diện tích.

Vẽ phân bố nồng độ tạp chất

Biết rằng quá trình khuếch tán được tiến hành với nguồn hữu hạn, nồng độ tạp chất bề mặt là NS= 1,6.1020cm-3

3. a) Xác định điện áp ngưỡng của MOS. Biết rằng Q -2 ε

ox/q=5.1010cm ; Si =11,7; ε ox =3,9; ε o =8,85.10-12 F/m; n -3

i= 1,5.1010 cm ; hiệu công thoát kim loại là Φ ms = -0,2V.

b) Nếu dòng máng cho bởi công thức I 2 2

DS= ½.K(VGS-VT) với K = 1mA/V , tính dòng cực máng tại VGS= -5V Bài 9

1. Một mẫu chất Silic được phủ một lớp Oxide dầy 0,3 μ m. Cần thêm một thời gian

bao lâu để tạo được một lớp oxide mới dầy 0,1 μ m trong ôxy khô ở nhiệt độ 11000C ?

2. Để chế tạo một linh kiện Silic người ta cần cấy Bo với nồng độ cực đại là 10 18 cm-3 tại chiều sâu 4000Ao.

a. Hãy xác định năng lượng ion và liều cấy cần thiết.

b. Tìm chiều sâu chuyển tiếp ngay sau khi cấy ion nếu đế Silic loại n có nồng độ tạp là 1015 cm-3.

3. Cho một PMOS có các thông số sau: L= 6 μ m; W=30 μ m; VT= -3V; d0x=100nm; μ

=230cm2/V.s; εSi =11,7; εox =3,9; εo =8,85.10-12F/m; n 10 i=1,5.10 cm-3.

Xác định IDS, gm khi VGS =- 5V. Bài 10

1. Để chế tạo vùng Base của transistor lưỡng cực người ta tiến hành khuếch tán tạp Bo

từ một nguồn hữu hạn trong môi trường nhiệt độ là T=1200 C 0

trong thời gian 180 phút. Tính

độ sau khuếch tán của chuyển tiếp p-n tạo thành, biết đế là Si-n có nồng độ tạp là ND = 1,4.10 cm 15

-3. Nồng độ tạp Bo đo được trên bề mặt phiến sau khi khuếch tán là N 17 -3 0=3,5.10 cm ,

năng lượng hoạt hóa của Bo là Ea=3,59eV, hằng số khuếch tán là D 2 0=3,17cm /s

2. Giả sử phiến silic có đường kính 200mm được pha tạp bởi phương pháp cấy ion từ

nguồn Bo có năng lượng 80KeV, liều cấy là 5.1014ion/cm2. Tính nồng độ lớn nhất của tạp Bo.

Giả sử thời gian cấy 15 phút, tính dòng ion

3. Cho MOS transistor sử dụng Al làm cực cửa trên đế Si-n có nồng độ tạp Nd= 2,5.10 cm 15

-3. Chiều dày lớp oxit cực cửa dox = 70nm. Mật độ điện tích bề mặt Si-SiO 2 là QS =5.10 cm 11 -2 Tính .

điện áp ngưỡng của transistor. Biết: n 10 -3 ε

i= 1,5.10 cm ; Si =11,7; ε ox =3,9; ε o =8,86.10-12 F/m; hiệu công thoát kim loại là Φ ms = -0,2V.