Preview text:

Giáo trình Verilog HDL

Verilog Hardware Description Language NI DUNG

Chương1. Dn nhp thit k h thng s vi Verilog

Khi kích thưc và ñ phc tp ca h thng thit k ngày càng tăng,

nhiu công c h tr thit k trên máy tính (CAD) ñưc s dng vào quá

trình thit k phn cng. Thi kì ñu, nhng công c mô phng và to ra

phn cng ñã ñưa ra phương pháp thit k, kim tra, phân tích, tng hp và

t ñng to ra phn cng mt cách phc tp. S phát trin không ngng

ca nhng công c thit k mt cách t ñng là do s phát trin ca nhng

ngôn ng mô t phn cng (HDLs) và nhng phương pháp thit k da trên

nhng ngôn ng này. Da trên nhng ngôn ng mô t phn cng (HDLs),

nhng công c CAD trong thit k h thng s ñưc phát trin và s dng

rng rãi bi nhng kĩ sư thit k phn cng. Hin ti, ngưi ta vn ñang

tip tc nghiên cu ñ tìm ra nhng ngôn ng mô t phn cng tt hơn và

tru tưng hơn. Mt trong nhng ngôn ng mô t phn cng ñưc s dng

rng rãi nht ñó là ngôn ng Verilog HDL. Do ñưc chp nhn rng rãi

trong ngành công nghip thit k s, Verilog ñã tr thành mt kin thc

ñưc ñòi hi phi bit ñi vi nhng kĩ sư cũng như sinh viên làm vic và

h!c tp trong lĩnh vc phn cng máy tính.

Trong chương này, ta s" trình bày nhng công c và môi trưng làm

vic có s#n tương thích vi ngôn ng Verilog mà mt kĩ sư thit k có th

s dng trong qui trình thit k t ñng ca mình ñ giúp ñ$y nhanh tin ñ

thit k. Chúng ta s" tho lun tng bưc v thit k phân cp, thit k mc

cao t vic mô t thit k b%ng ngôn ng Verilog ñn vic to ra phn cng

ca thit k ñó. Nhng qui trình và nhng t khóa chuyên môn cũng s"

ñưc minh h!a phn này. K tip, chúng ta cũng s" tho lun nhng công Lâm Đc Khi

University of Information Technology Page 1

Verilog Hardware Description Language

c CAD hin có tương thích vi Verilog và chc năng ca nó trong môi

trưng thit k t ñng. Phn cui cùng ca chương này s" nói v mt s

ñ&c tính ca Verilog khin nó tr thành mt ngôn ng ñưc nhiu kĩ sư

thit k phn cng la ch!n.

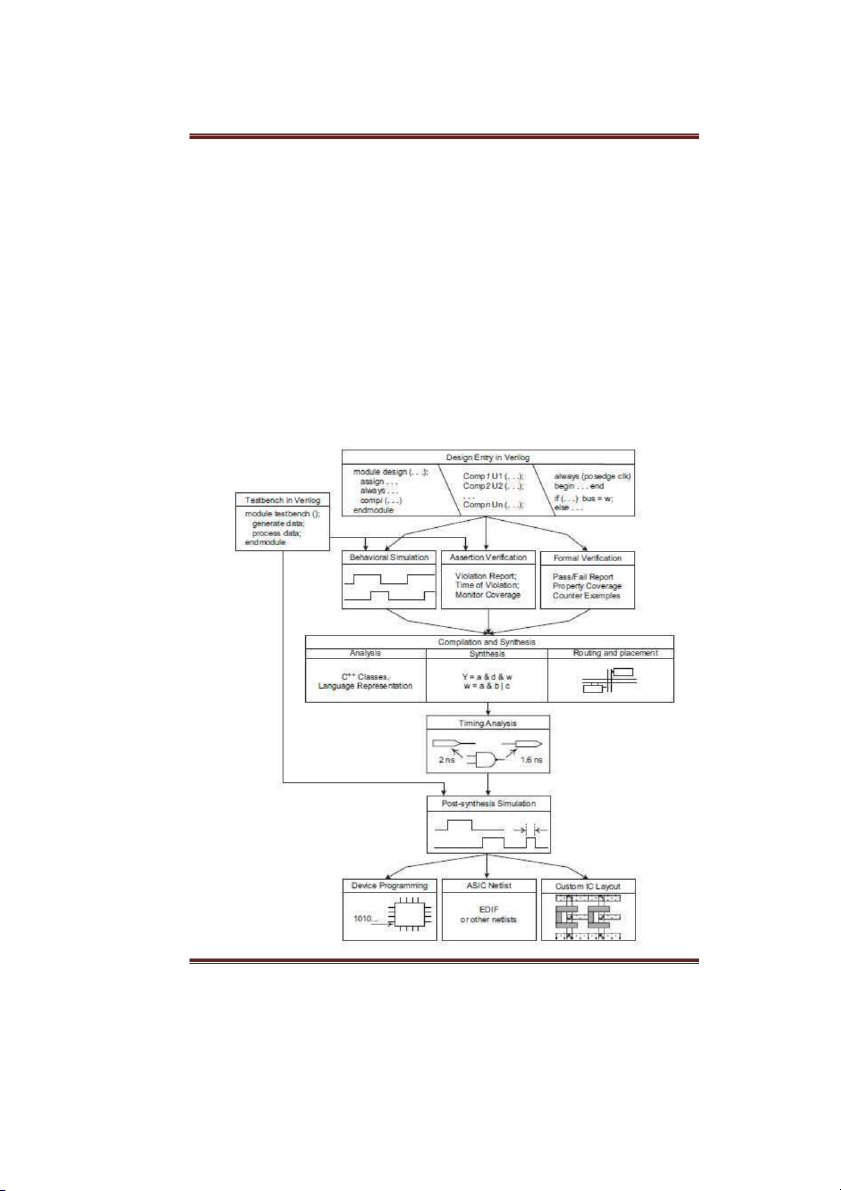

1.1 Qui trình thit k s

Trong thit k mt h thng s s dng môi trưng thit k t ñng,

qui trình thit k b't ñu b%ng vic mô t thit k ti nhiu mc ñ tru

tưng khác nhau và kt thúc b%ng vic to ra danh sách các linh kin cũng

như các ñưng kt ni gia các linh kin vi nhau ( netlist) cho mt mch

tích hp vi ng dng c th (ASIC), mch in ( layout) cho mt mch tích

hp theo yêu cu khách hàng ( custom IC), ho&c mt chương trình cho mt

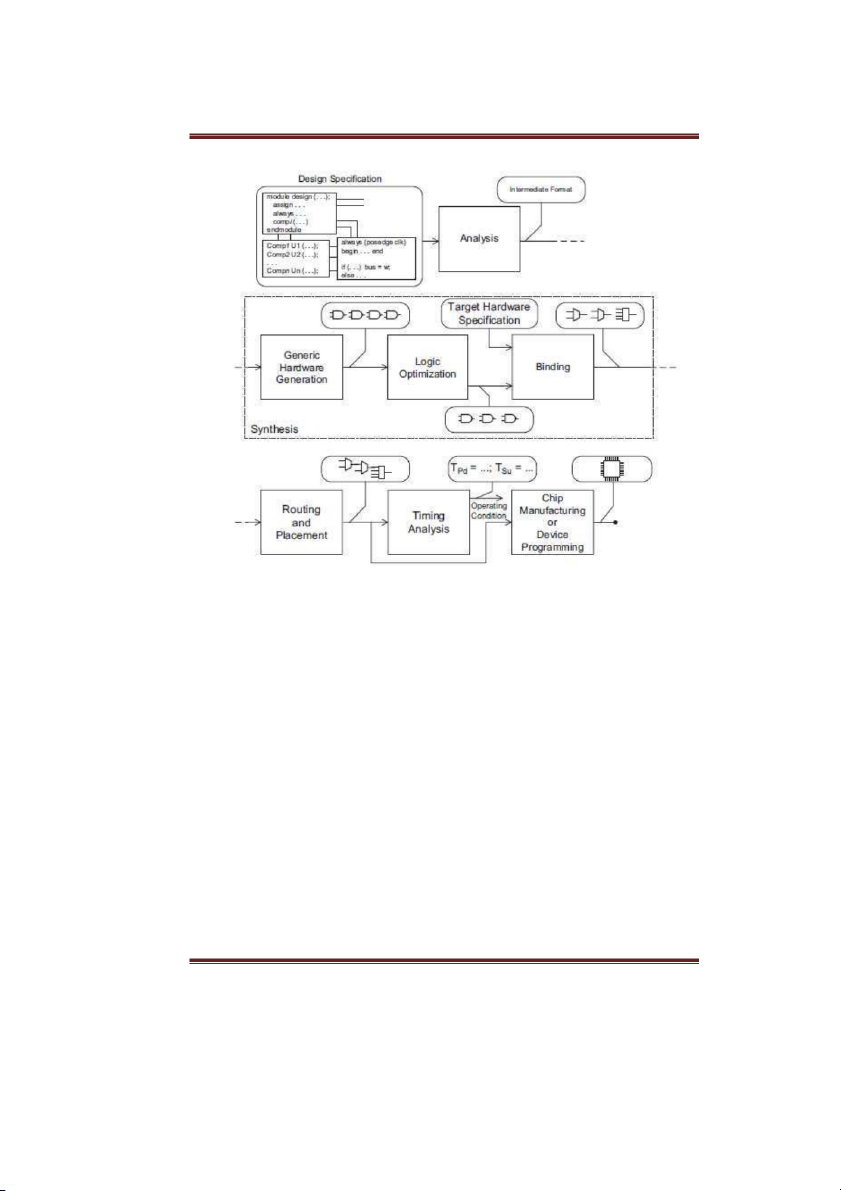

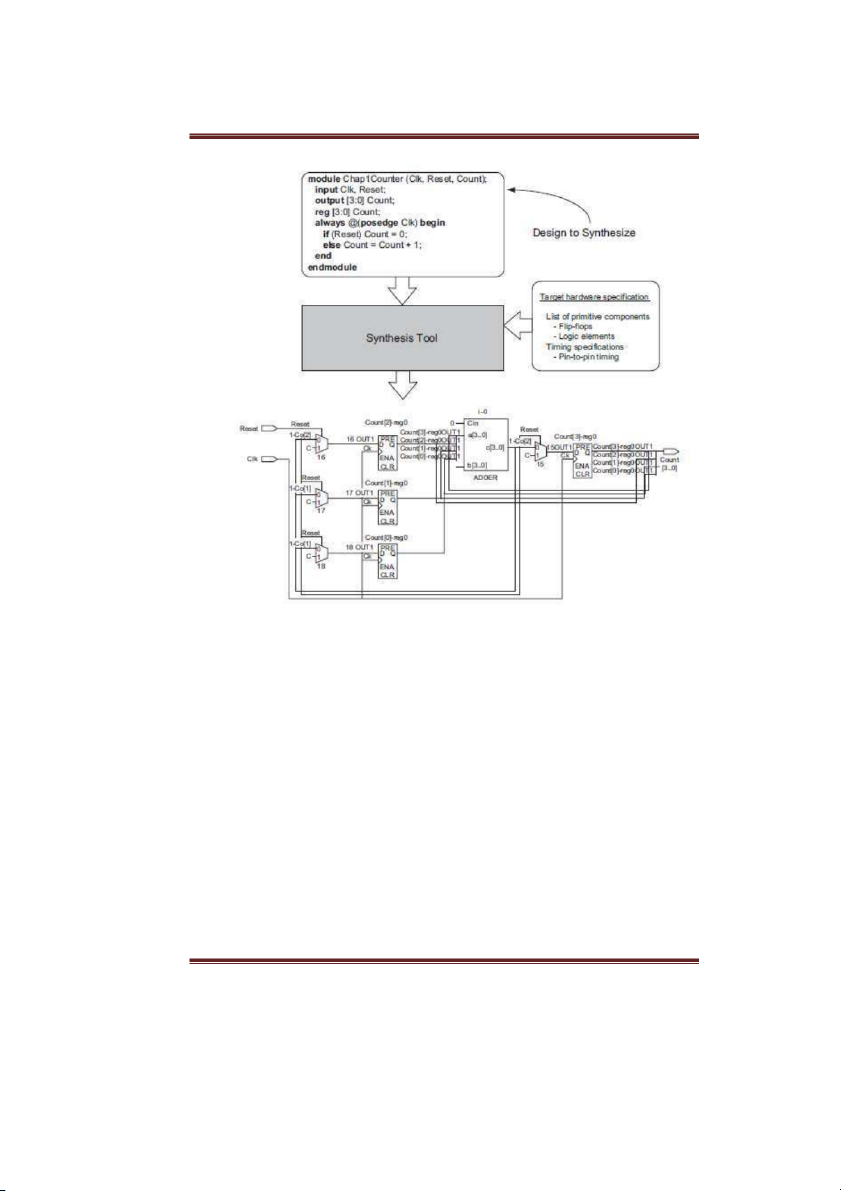

thit b( logic có kh năng lp trình ñưc (PLD). Hình 1.1 mô t tng bưc

trong qui trình thit k này.

Bưc ñu ca thit k, mt thit k s" ñưc mô t bi s hn hp

gia mô t mc ñ hành vi (behavioural) Verilog, s dng nhng gói

(module) thit k Verilog ñã ñưc thit k s#n, và vic gán h thng các

bus và wire ñ liên kt các gói thit k này thành mt h thng hoàn ch)nh.

Kĩ sư thit k cũng phi có trách nhim to ra d liu ñ kim tra

(testbench) xem thit k ñúng chc năng hay chưa cũng như dùng ñ kim

tra thit k sau khi tng hp. Vic kim tra thit k có th thc hin ñưc

b%ng vic mô phng, chèn nhng kĩ thut kim tra, kim tra thông thưng

ho&c kt hp c ba phương pháp trên. Sau bưc kim tra ñánh giá thit k (

bưc này ñưc g!i là kim tra tin tng hp (presynthesis verification)),

thit k s" ñưc tip tc b%ng vic tng hp ñ to ra phn cng thc s

cho h thng thit k cui cùng (ASIC, custom IC or FPLD,…). Nu h

thng thit k là ASIC, thit k s" s" ñưc sn xut bi nhà sn xut khác; Lâm Đc Khi

University of Information Technology Page 2

Verilog Hardware Description Language

nu là custom IC, thit k s" ñưc sn xut trc tip; nu là FPLD, thit k

s" ñưc np lên thit b( lp trình ñưc. Sau bưc tng hp và trưc khi

phn cng thc s ñưc to ra, mt quá trình mô phng khác (hu tng hp

(postsynthesis)) phi ñưc thc hin. Vic mô phng này, ta có th s dng

testbench tương t testbench ñã s dng trong mô phng tin tng hp

(presynthesis). B%ng phương pháp này, mô hình thit k mc ñ hành vi

và mô hình phn cng ca thit k ñưc kim tra vi cùng d liu ngõ vào.

S khác nhau gia mô phng tin tng hp và hu tng hp ñó là mc ñ

chi tit có th ñt ñưc t mi loi mô phng. Lâm Đc Khi

University of Information Technology Page 3

Verilog Hardware Description Language

Nhng phn tip theo s" mô t t) m) v mi khi trong hình 1.1.

1.1.1 Dn nhp thit k

Bưc ñu tiên trong thit k h thng s là bưc dn nhp thit k.

Trong bưc này, thit k ñưc mô t b%ng Verilog theo phong cách phân

cp t cao xung thp (top-down). Mt thit k hoàn ch)nh có th bao g*m

nhng linh kin mc cng ho&c mc transistor, nhng khi (module)

phn cng có chc năng phc tp hơn ñưc mô t mc ñ hành vi, ho&c

nhng linh kin ñưc lit kê bi cu trúc bus.

Do nhng thit k Verilog mc cao thưng ñưc mô t mc ñ

mà ti ñó nó mô t h thng nhng thanh ghi và s truyn d liu gia

nhng thanh ghi này thông qua h thng bus, vic mô t h thng thit k

mc ñ này ñưc xem như là mc ñ truyn d liu gia các thanh ghi

(RTL). Mt thit k hoàn ch)nh ñưc mô t như vy s" to ra ñưc phn

cng tương ng thc s rõ ràng. Nhng cu trúc thit k Verilog mc ñ

RTL s dng nhng phát biu qui trình (producedural statements), phép

gán liên tc (continuous assignments), và nhng phát biu g!i s dng khi

(module) ñã xây dng s#n.

Nhng phát biu qui trình Verilog (procedural statements) ñưc

dùng ñ mô t mc ñ hành vi mc cao. Mt h thng ho&c mt linh kin

ñưc mô t mc ñ hành vi thì tương t vi vic mô t trong ngôn ng

phn mm. Ví d, chúng ta có th mô t mt linh kin b%ng vic kim tra

ñiu kin ngõ vào ca nó, bt c hiu, ch cho ñn khi có s kin nào ñó

xy ra, quan sát nhng tín hiu b't tay và to ra ngõ ra. Mô t h thng mt

cách qui trình như vy, cu trúc if-else, case ca Verilog cũng như nhng

ngôn ng phn mm khác ñu s dng như nhau. Lâm Đc Khi

University of Information Technology Page 4

Verilog Hardware Description Language

Nhng phép gán liên tc (continuous assignment) trong Verilog là

nhng phép gán cho vic th hin chc năng nhng khi logic, nhng phép

gán bus, và mô t vic kt ni gia h thng bus và các chân ngõ vào và

ngõ ra. Kt hp vi nhng hàm Boolean và nhng biu thc có ñiu kin,

nhng cu trúc ngôn ng này có th ñưc ñ mô t nhng linh kin và h

thng theo nhng phép gán thanh ghi và bus ca chúng.

Nhng phát biu g!i s dng khi Verilog ñã ñưc thit k s#n

(instantiantion statements) ñưc dùng cho nhng linh kin mc thp trong

mt thit k mc ñ cao hơn. Thay vi mô t mc ñ hành vi, chc

năng, ho&c bus ca mt h thng, chúng ta có th mô t mt h thng b%ng

Verilog b%ng cách kt ni nhng linh kin mc ñ thp hơn. Nhng linh

kin này có th nh như là mc cng hay transistor, ho&c có th ln như là

mt b vi x lí hoàn ch)nh.

1.1.2 Testbench trong Verilog

Mt h thng ñưc thit k dùng Verilog phi ñưc mô phng và

kim tra xem thit k ñã ñúng chc năng chưa trưc khi to ra phn cng.

Trong quá trình chy mô phng này, nhng li thit k và s không tương

thích gia nhng linh kin dùng trong thit k có th ñưc phát hin. Chy

mô phng mt thit k ñòi hi vic to ra mt d liu ngõ vào kim tra và

quá trình quan sát kt qu sau khi chy mô phng, d liu dùng ñ kim tra

này ñưc g!i là testbench. Mt testbench s dng cu trúc mc cao ca

Verilog ñ to ra d liu kim tra, quan sát ñáp ng ngõ ra, và c vic b't

tay gia nhng tín hiu trong thit k. Bên trong testbench, h thng thit

k cn chy mô phng s" ñưc g!i ra (instantiate) trong testbench. D liu

testbench cùng vi h thng thit k s" to ra mt mô hình mô phng mà s"

ñưc s dng bi mt công c mô phng Verilog. Lâm Đc Khi

University of Information Technology Page 5

Verilog Hardware Description Language

1.1.3 Đánh giá thit k

Mt nhiêm v quan tr!ng trong bt kì thit k s nào cũng cn ñó là

ñánh giá thit k. Đánh giá thit k là quá trình mà ngưi thit k s" kim

tra thit k ca h! có sai sót nào có th xy ra trong sut quá trình thit k

hay không. Mt sai sót thit k có th xy ra do s mô t thit k mơ h*, do

sai sót ca ngưi thit k, ho&c s dng không ñúng nhng khi trong thit

k. Đánh giá thit k có th thc hin b%ng mô phng, b%ng vic chèn

nhng kĩ thut kim tra, ho&c kim tra thông thưng. 1.1.3.1 Mô phng

Chy mô phng dùng trong vic ñánh giá thit k ñưc thc hin

trưc khi thit k ñưc tng hp. Bưc chy mô phng này ñưc hiu như

mô phng mc ñ hành vi, mc ñ RTL hay tin tng hp. , mc ñ

RTL, mt thit k bao g*m xung thi gian clock nhưng không bao g*m trí

hoãn thi gian trên cng và dây kt ni (wire). Chy mô phng mc ñ

này s" chính xác theo xung clock. Thi gian ca vic chy mô phng

mc ñ RTL là theo tín hiu xung clock, không quan tâm ñn nhng nguy

him tim $n có th khin thit k b( li (hazards, glitch), hin tưng chy

ñua không kim soát gia nhng tín hiu (race conditions), nhng vi phm

v thi gian setup và hold ca tín hiu ngõ vào, và nhng vn ñ liên quan

ñn ñ(nh thi khác. Ưu ñim ca vic mô phng này là tc ñ chy mô

phng nhanh so vi chy mô phng mc cng ho&c mc transistor.

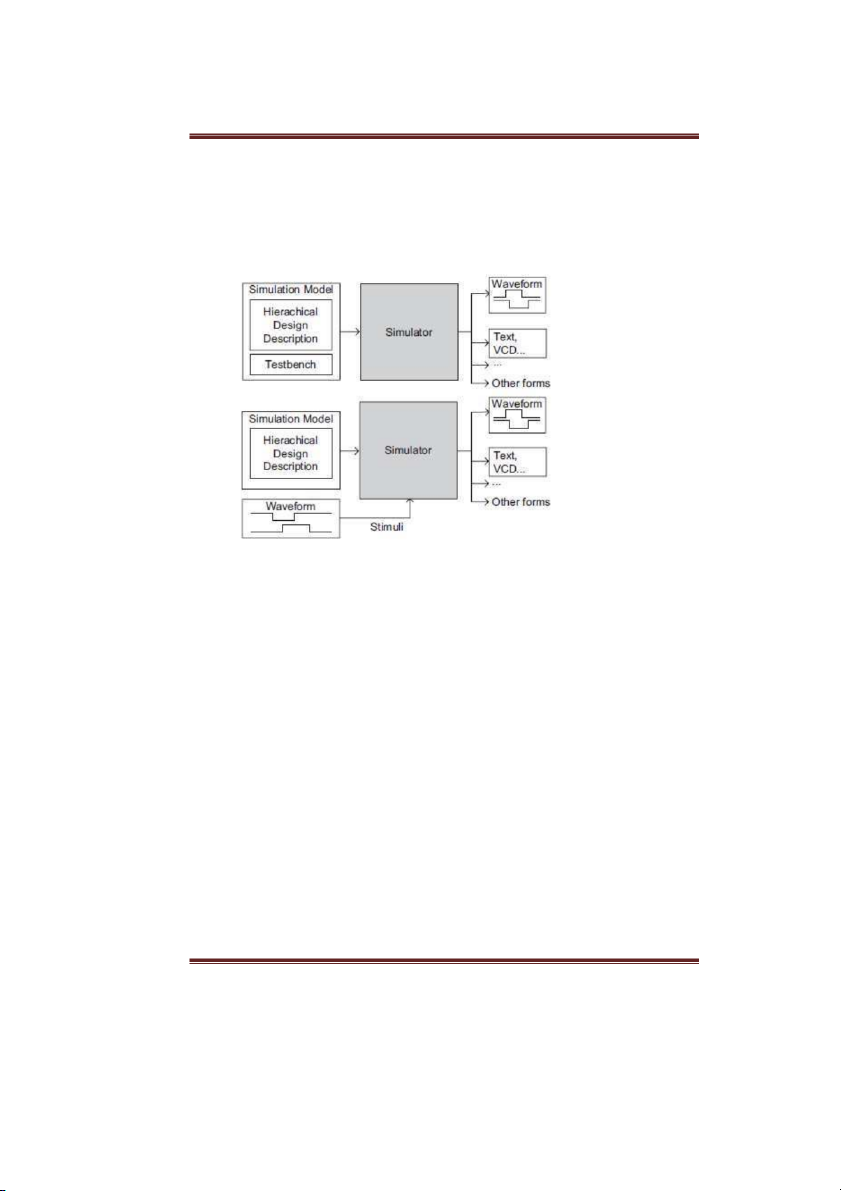

Chy mô phng cho mt thit k ñòi hi d liu kim tra, thông

thưng trong môi trưng mô phng Verilog s" cung cp nhiu phương

pháp khác nhau ñ ñưa d liu kim tra này vào thit k ñ kim tra. D

liu kim tra có th ñưc to ra b%ng ñ* h!a s dng nhng công c son

tho dng sóng, ho&c b%ng testbench. Hình 1.2 mô t hai cách khác nhau ñ Lâm Đc Khi

University of Information Technology Page 6

Verilog Hardware Description Language

ñ(nh nghĩa d liu kim tra ngõ vào ca mt công c mô phng. Nhng

ngõ ra ca công c mô phng là nhng dng sóng ngõ ra ( có th quan sát trc quan).

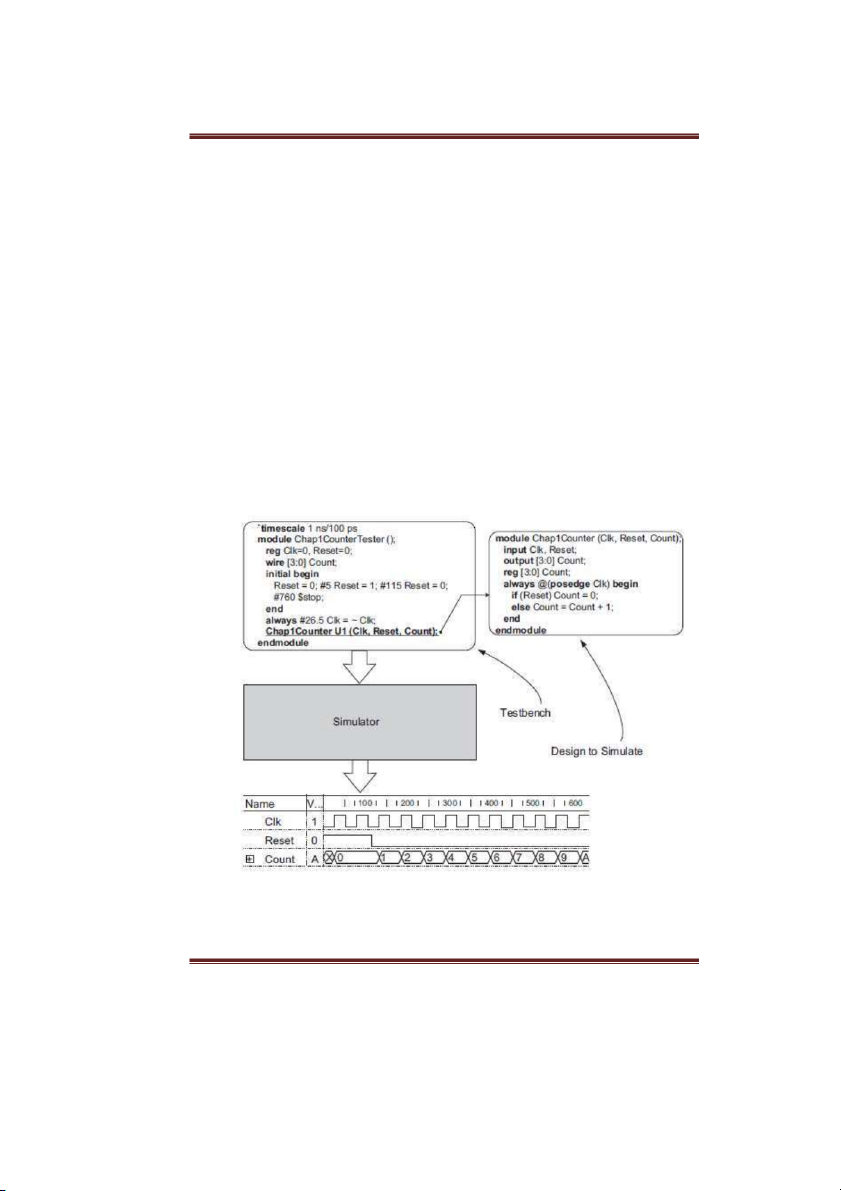

Đ chy mô phng vi Verilog testbench, trong testbench s" g!i h

thng thit k ra ñ kim tra, lúc này h thng thit k ñưc xem như là

mt phn ca testbench, testbench s" cung cp d liu kim tra ñn ngõ vào

ca h thng thit k. Hình 1.3 mô t mt ñon code ca mt mch ñm,

testbench ca nó, cũng như kt qu chy mô phng ca nó dưi dng sóng

ngõ ra. Quan sát hình ta thy vic chy mô phng s" ñánh giá chc năng

ca mch ñm. Vi mi xung clock thì ngõ ra b ñm s" tăng lên 1. Chú ý

r%ng, theo biu ñ* thi gian thì ngõ ra b ñm thay ñi ti cnh lên xung

clock và không có thi gian trì hoãn do cng cũng như trì hoãn trên ñưng

truyn. Kt qu chy mô phng ch) ra r%ng chc năng ca mch ñm là

chính xác mà không cn quan tâm ñn tn s xung clock.

Hin nhiên, nhng linh kin phn cng thc s s" có ñáp ng khác

nhau. Da trên ñ(nh thi và thi gian trì hoãn ca nhng khi ñưc s Lâm Đc Khi

University of Information Technology Page 7

Verilog Hardware Description Language

dng, thi gian t cnh lên xung clock ñn ngõ ra ca b ñm s" có ñ trì

hoãn khác không. Hơn na, nu tn s xung clock ñưc cp vào mch thc

s quá nhanh so vi tc ñ truyn tín hiu bên trong các cng và transistor

ca thit k thì ngõ ra ca thit k s" không th bit ñưc.

Vic mô phng này không cung cp chi tit v các vn ñ ñ(nh thi

ca h thng thit k ñưc mô phng. Do ñó, nhng vn ñ tim $n v ñ(nh

thi ca phn cng do trì hoãn trên cng s" không th phát hin ñưc. Đây

là vn ñ ñin hình ca quá tr)nh mô phng tin tng hp ho&c mô phng

mc ñ hnh vi. Điu bit ñưc trong hình 1.3 ñó là b ñm ca ta ñm s

nhi phân. Thit k hot ñng nhanh chm th nào, hot ñông ñưc tn s

nào ch) có th bit ñưc b%ng vic kim tra thit k sau tng hp. Lâm Đc Khi

University of Information Technology Page 8

Verilog Hardware Description Language

1.1.3.2 Kĩ thut chèn kim tra (assertion)

Thay vì phi dò theo kt qu mô phng b%ng m't hay to nhng d

liu kim tra testbench phc tp, kĩ thut chèn thit b( giám sát có th ñưc

s dng ñ kim tra tun t nhng ñ&c tính ca thit k trong sut quá trình

mô phng. Thit b( giám sát ñưc ñ&t bên trong h thng thit k ñưc mô

phng bi ngưi thit k. Ngưi thit k s" quyt ñ(nh xem chc năng ca

thit k ñúng hay sai, nhng ñiu kin nào thit k cn phi tha mãn.

Nhng ñiu kin này phi tuân theo nhng ñ&c tính thit k, và thit b(

giám sát ñưc chèn vào h thng thit k ñ ñm bo nhng ñ&c tính này

không b( vi phm. Chui thit b( giám sát này s" sai nu mt ñ&c tính nào

ñó ñưc ñ&t vào bi ngưi thit k b( vi phm. Nó s" cnh báo ngưi thit

k r%ng thit k ñã không ñúng chc năng như mong ñi. Thư vin OVL (

Open Verification Library) cung cp mt chui nhng thit b( giám sát ñ

chèn vào h thng thit k ñ giám sát nhng ñ&c tính thông thưng ca

thit k. Ngưi thit k có th dùng nhng kĩ thut giám sát ca riêng mình

ñ chèn vào thit k và dùng chúng kt hp vi testbench trong vic kim tra ñánh giá thit k.

1.1.3.3 Kim tra thông th n ư g

Kim tra thông thưng là quá trình kim tra nhng ñ&c tính bt kì

ca thit k. Khi mt thit k hoàn thành, ngưi thit k s" xây dng mt

chui nhng ñ&c tính tương ng vi hành vi ca thit k. Công c kim tra

thông thưng s" kim tra thit k ñ ñm bo r%ng nhng ñ&c tính ñưc mô

t ñáp ng ñưc tt c nhng ñiu kin. Nu có mt ñ&c tính ñưc phát

hin là không ñáp ng ñúng, ñ&c tính ñó ñưc xem như vi phm. Đ&c tính

ñ bao ph (coverage) ch) ra bao nhiêu phn trăm ñ&c tính ca thit k ñã ñưc kim tra. Lâm Đc Khi

University of Information Technology Page 9

Verilog Hardware Description Language

1.1.4 Biên dch và tng hp thit k

Tng hp là quá trình to ra phn cng t ñng t mt mô t thit k

phn cng tương ng rõ ràng. Mt mô t phn cng Verilog dùng ñ tng

hp không th bao g*m tín hiu và mô t ñ(nh thi mc cng, và nhng

cu trúc ngôn ng khác mà không d(ch sang nhng phương trình logic tun

t ho&c t hp. Hơn th na, nhng mô t phân cng Verilog dùng cho

tng hp phi tuân theo nhng phong cách vit code mt cách nht ñ(nh

cho mch t hp cũng như mch tun t. Nhng phong cách này và cu

trúc Verilog tương ng ca chúng ñưc ñ(nh nghĩa trong vic tng hp RTL.

Trong qui trình thit k, sau khi mt thit k ñưc mô t hoàn thành

và kt qu mô phng tin tng hp ca nó ñưc kim tra bi ngưi thit k,

nó phi ñưc biên d(ch ñ nó tin gn hơn ñn vic to thành phn cng

thc s trên silicon. Bưc thit k này ñòi hi vic mô t phn cng ca

thit k phi ñưc nhn ra. Ví d, chúng ta phi ch) ñn mt ASIC c th,

ho&c mt FPGA c th như là thit b( phn cng mc ñích ca thit k. Khi

thit b( mc ñích ñưc ch) ra, nhng tp tin mô t v công ngh

(technology files) ca phn cng ( ASIC, FPGA, ho&c custom IC) s" cung

cp chi tit nhng thông tin v ñ(nh thi và mô t chc năng cho quá trình

biên d(ch. Quá trình biên d(ch s" chuyn ñi nhng phn khác nhau ca

thit k ra mt ñ(nh dng trung gian ( bưc phân tích), kt ni tt c các

phn li vi nhau, to ra mc logic tương ng ( bưc tng hp), s'p xp và

kt ni ( place and route ) nhng linh kin trong thit b( phn cng mc

ñích li vi nhau ñ thc hiên chc năng như thit k mong mun và to ra

thông tin chi tit v ñ(nh thi trong thit k. Lâm Đc Khi

University of Information Technology Page 10

Verilog Hardware Description Language

Hình 1.4 mô t quá trình biên d(ch và mô t hình nh kt qu ngõ ra

ca mi bưc biên d(ch. Như trên hình, ngõ vào ca bưc này là mt mô t

phn cng bao g*m nhng mc ñ mô t khác nhau ca Verilog, và kt qu

ngõ ra ca nó là mt phn cng chi tit cho thit b( phn cng mc ñích

như FPLD hay ñ sn xut chip ASIC. 1.1.4.1 Phân tích

Mt thit k hoàn ch)nh ñưc mô t dùng Verilog có th bao g*m mô

t nhiu mc ñ khác nhau như mc ñ hành vi, h thng bus và dây kt

ni vi nhng linh kin Verilog khác. Trưc khi mt thit k hoàn ch)nh

to ra phn cng, thit k phi ñưc phân tích và to ra mt ñ(nh dng ñ*ng

nht cho tt c các phn trong thit k. Bưc này cũng kim tra cú pháp và

ng nghĩa ca mã ngõ vào Verilog.

1.1.4.2 To phn cng

Sau khi to ñưc mt d liu thit k có ñ(nh dng ñ*ng nht cho tt

c các linh kin trong thit k, bưc tng hp s" b't ñu b%ng chuyn ñi

d liu thit k trên sang nhng ñ(nh dng phn cng thông thưng như

mt chui nhng biu thc Boolean hay mt netlist nhng cng cơ bn. Lâm Đc Khi

University of Information Technology Page 11

Verilog Hardware Description Language

1.1.4.3 Ti ưu logic

Bưc k tip ca quá trình tng hp, sau khi mt thit k ñưc

chuyn ñi sang mt chui nhng biu thc Boolean, bưc ti ưu logic

ñưc thc hin. Bưc này nh%m mc ñích làm gim nhng biu thc vi

ngõ vào không ñi, loi b nhng biu thc lp li, ti thiu hai mc, ti thiu nhiu mc.

Đây là quá trình tính toán rt hao tn thi gian và công sc, mt s

công c cho phép ngưi thit k quyt ñ(nh mc ñ ti ưu. Kt qu ngõ ra

ca bưc này cũng dưi dng nhng biu thc Boolean, mô t logic dưi

dng bng, ho&c netlist g*m nhng cng cơ bn. Lâm Đc Khi

University of Information Technology Page 12

Verilog Hardware Description Language 1.1.4.4 Binding

Sau bưc ti ưu logic, quá trình tng hp s dng thông tin t thit

b( phn cng mc ñích ñ quyt ñ(nh chính xác linh kin logic nào và thit

b( nào cn ñ hin thc mch thit k. Quá trình này ñưc g!i là binding và

kt qu ngõ ra ca nó ñưc ch) ñ(nh c th s dng cho FPLD, ASIC, hay custom IC.

1.1.4.5 Sp xp và ñi dây liên kt

Bưc s'p xp và ñi dây lien kt s" quyt ñ(nh vic ñ&t v( trí ca các

linh kin trên thit b( phn cng mc ñích. Vic kt ni các ngõ vào và ngõ

ra ca nhng linh kin này dùng h thng dây liên kt và vùng chuyn

mch trên thit b( phn cng mc ñích ñưc quyt ñ(nh bi bưc s'p xp

và ñi dây liên kt này. Kt qu ngõ ra ca bưc này ñưc ñưa ti thit b(

phn cng mc ñích, như np lên FPLD, hay dùng ñ sn xut ASIC.

Mt ví d minh h!a v quá trình tng hp ñưc ch) ra trên hình 1.5.

Trong hình này, mch ñm mà ñã ñưc dùng chy mô phng trong hình 1.3

ñưc tng hp. Ngoài vic mô t phn cng thit k dùng Verilog, công c

tng hp ñòi hi nhng thông tin mô t thit b( phn cng ñích ñ tin hành

quá trình tng hp ca mình. Kt qu ngõ ra ca công c tng hp là danh

sách các cng và flip-flop có s#n trong thit b( phn cng ñích và h thng

dây kt ni gia chúng. Hình 5 cũng ch) ra mt kt qu ngõ ra mang tính

trc quan mà ñã ñưc to ra t ñng b%ng công c tng hp ca Altera Quartus II. Lâm Đc Khi

University of Information Technology Page 13

Verilog Hardware Description Language

1.1.5 Mô phng sau khi tng hp thit k

Sau khi quá trình tng hp hoàn thành, công c tng hp s" to ra

mt netlist hoàn ch)nh cha nhng linh kin ca thit b( phn cng ñích và

các giá tr( ñ(nh thi ca nó. Nhng thông tin chi tit v các cng ñưc dùng

ñ hin thc thit k cũng ñưc mô t trong netlist này. Netlist này cũng

bao g*m nhng thông tin v ñ trì hoãn trên ñưng dây và nhng tác ñng

ca ti lên các cng dùng trong quá trình hu tng hp. Có nhiu ñ(nh dng

netlist ngõ ra có th ñưc to ra bao g*m c ñ(nh dng Verilog. Mt netlist

như vy có th ñưc dùng ñ mô phng, và mô phng này ñưc g!i là mô

phng hu tng hp. Nhng vn ñ v ñ(nh thi, v tn s xung clock, v

hin tưng chy ñua không kim soát, nhng nguy him tim $n ca thit Lâm Đc Khi

University of Information Technology Page 14

Verilog Hardware Description Language

k ch) có th kim tra b%ng mô phng hu tng hp thc hin sau khi thit

k ñưc tng hp. Như trên hình 1.1, ta có th s dng d liu kim tra mà

ñã dùng cho quá trình mô phng tin tng hp ñ dùng cho quá trình mô phng hu tng hp.

Do ñ trì hoãn trên ñưng dây và các cng, ñáp ng ca thit k sau

khi chy mô phng hu tng hp s" khác vi ñáp ng ca thit k mà

ngưi thit k mong mun. Trong trưng hp này, ngưi thit k phi sa

li thit k và c g'ng tránh nhng sai sót v ñ(nh thi và hin tưng chy

ñua gia nhng tín hiu mà không th kim soát.

1.1.6 Phân tích thi gian

Quan sát trên h)nh 1.1, bưc phân tích thi gian là mt phn trong

quá trình biên d(ch, ho&c trong mt s công c thì bưc phân tích thi gian

này ñưc thc hin sau quá trình biên d(ch. Bưc này s" to ra kh năng

xu nht v ñ trì hoãn , tc ñ xung clock, ñ trì hoãn t cng này ñn

cng khác, cũng như thi gian cho vic thit lp và gi tín hiu. Kt qu

ca bưc phân tích thi gian ñưc th hin dưi dng bng ho&c biu ñ*.

Ngưi thit k s dng nhng thông tin này ñ xác ñ(nh tc ñ xung clock,

hay nói cách khác là xác ñ(nh tc ñ hot ñng ca mch thit k.

1.1.7 To linh kin phn cng

Bưc cui cùng trong qui trình thit k t ñng da trên Verilog ñó

là to ra phn cng thc s cho thit k. Bưc này có th to ra mt netlist

dùng ñ sn xut ASIC, mt chương trình ñ np vào FPLD, hay mt mch in cho mch IC. Lâm Đc Khi

University of Information Technology Page 15

Verilog Hardware Description Language

1.2 Ngôn ng phn cng Verilog ( Verilog HDL)

Trong phn trưc, ta ñã trình bày tng bưc thit k mc ñ RTL

t mt mô t thit k Verilog cho ñn vic hin thc ra mt phn cng thc

s. Qui trình thit k này ch) có th thc hin ñưc khi ngôn ng Verilog

có th hiu ñưc bi ngưi thit k h thng, ngưi thit k mc ñ RTL,

ngưi kim tra, công c mô phng, công c tng hp, và các máy móc liên

quan. Bi vì tm quan tr!ng ca nó trong qui trình thit k, Verilog ñã tr

thành mt chu$n quc t IEEE. Chu$n này ñưc s dng bi ngưi thit k

cũng như ngưi xây dng công c thit k.

1.2.1 Quá trình phát trin Verilog

Verilog ñưc ra ñi vào ñu năm 1984 bi Gateway Design

Automation. Khi ñu, ngôn ng ñu tiên ñưc dùng như là mt công c

mô phng và kim tra. Sau thi gian ñu ngôn ng này ñưc chp nhn bi

ngành công nghip ñin t, mt công c mô phng, mt công c phân tích

thi gian, và sau này vào năm 1987, công c tng hp ñã ñưc xây dng và

phát trin da vào ngôn ng này. Gateway Design Automation và nhng

công c da trên Verilog ca hang sau này ñưc mua bi Cadence Design

System. T sau ñó, Cadence ñóng vai trò ht sc quan tr!ng trong vic phát

trin cũng như ph bin ngôn ng mô t phn cng Verilog.

Vào năm 1987, VHDL tr thành mt chu$n ngôn ng mô t phn

cng ca IEEE. Bi do s h tr ca B quc phòng (DoD), VHDL ñưc

s dng nhiu trong nhng d án ln ca chính ph M.. Trong n lc ph

bin Verilog, vào năm 1990, OVI ( Open Verilog International) ñưc thành

lp và Verilog chim ưu th trong lĩnh vc công nghip. Điu này ñã to ra

mt s quan tâm khá ln t ngưi dùng và các nhà cung cp EDA ti Verilog. Lâm Đc Khi

University of Information Technology Page 16

Verilog Hardware Description Language

Vào năm 1993, nhng n lc nh%m chu$n hóa ngôn ng Verilog

ñưc b't ñu. Verilog tr thành chu$n IEEE, IEEE Std 1364-1995, vào

năm 1995. Vi nhng công c mô phng, công c tng hp, công c phân

tích thi gian, và nhng công c thit k da trên Verilog ñã có s#n, chu$n

Verilog IEEE này nhanh chóng ñưc chp nhn sâu rng trong cng ñ*ng thit k ñin t.

Mt phiên bn mi ca Verilog ñưc chp nhn bi IEEE vào năm

2001. Phiên bn mi này ñưc xem như chu$n Verilog-2001 và ñưc dùng

bi hu ht ngưi s dng và ngưi phát trin công c. Nhng ñ&c ñim

mi trong phiên bn mi ñó là nó cho phép bên ngoài có kh năng ñ!c và

ghi d liu, qun lí thư vin, xây dng cu hình thit k, h tr nhng cu

trúc có mc ñ tru tưng cao hơn, nhng cu trúc mô t s l&p li, cũng

như thêm mt s ñ&c tính vào phiên bn này. Quá trình ci tin chu$n này

vn ñang ñưc tip tc vi s tài tr ca IEEE.

1.2.2 Nhng ñc tính ca Verilog

Verilog là mt ngôn ng mô t phn cng dùng ñ ñ&c t phn cng

t mc transistor ñn mc hành vi. Ngôn ng này h tr nhng cu trúc

ñ(nh thi cho vic mô phng ñ(nh thi mc ñ chuyn mch và tc thi,

nó cũng có kh năng mô t phn cng ti mc ñ thut toán tru tưng.

Mt mô t thit k Verilog có th bao g*m s trn ln gia nhng khi

(module) có mc ñ tru tưng khác nhau vi s khác nhau v mc ñ chi tit. Lâm Đc Khi

University of Information Technology Page 17

Verilog Hardware Description Language

1.2.2.1 Mc ñ chuyn mch

Nhng ñ&c ñim ca ngôn ng này khin nó tr nên lí tưng trong

vic mô hình hóa và mô phng mc ñ chuyn mch bao g*m kh năng

chuyn mch mt chiu cũng như hai chiu vi nhng thông s v ñ trì

hoãn và lưu tr ñin tích. Nhng trì hoãn mch ñin có th ñưc mô hình

hóa như là trì hoãn ñưng truyn, trì hoãn t thp lên cao hay t cao xung

thp. Đ&c ñim lưu tr ñin tích mc ñ tru tưng trong Verilog khin

nó có kh năng mô t nhng mch ñin vi linh kin ñng như là CMOS hay MOS.

1.2.2.2 Mc ñ cng

Nhng cng cơ bn vi nhng thông s ñưc ñ(nh nghĩa trưc s"

cung cp mt kh năng thun tin trong vic th hin netlist và mô phng

mc cng. Đi vi vic mô phng mc cng vi mc ñích chi tit và ñ&c

bit, nhng linh kin cng có th ñưc ñ(nh nghĩa mc ñ hành vi.

Verilog cũng cung cp nhng công c cho vic ñ(nh nghĩa nhng phn t

cơ bn vi nhng chc năng ñ&c bit. Mt h thng s logic 4 giá tr( ñơn

gin (0,1,x,z) ñưc s dng trong Verilog ñ th hin giá tr( cho tín hiu.

Tuy nhien, ñ mô hình mc logic chính xác hơn, nhng tín hiu Verilog

g*m 16 mc giá tr( v ñ mnh ñưc thêm vào 4 giá tr( ñơn gin trên.

1.2.2.3 Đ trì hoãn gia pin ñn pin

Mt tin ích trong vic mô t ñ(nh thi cho các linh kin ti ngõ vào

và ngõ ra cũng ñưc cung cp trong Verilog. Tin ích này có th ñưc dùng

ñ truy vn li thông tin v ñ(nh thi trong mô t tin thit k ban ñu. Hơn

na, tin ích này cũng cho phép ngưi vit mô hình hóa tinh ch)nh hành vi

ñ(nh thi ca mô hình da trên hin thc phn cng. Lâm Đc Khi

University of Information Technology Page 18

Verilog Hardware Description Language 1.2.2.4 Mô t Bus

Nhng tin ích v mô hình bus và thanh ghi cũng ñưc cung cp bi

Verilog. Đi vi nhiu cu trúc bus khác nhau, Verilog h tr chc năng

phân gii bus và wire vi h thng logic 4 giá tr( (0,1,x,z). Vi s kt hp

gia chc năng bus logic và chc năng phân gii, nó cho phép mô hình hóa

ñưc hu ht các loi bus. Đi vi vic mô hình hóa thanh ghi, vic mô t

xung clock mc cao và nhưng cu trúc ñiu khin ñ(nh thi có th ñưc s

dng ñ mô t thanh ghi vi nhng tín hiu xung clock và tín hiu reset khác nhau.

1.2.2.5 Mc ñ hành vi

Nhng khi qui trình ( procedural blocks) ca Verilog cho phép mô

t thut toán ca nhng cu trúc phn cng. Nhng cu trúc này tương t

vi ngôn ng lp trình phn mm nhưng có kh năng mô t phn cng.

1.2.2.6 Nhng tin ích h thng

Nhng tác v h thng trong Verilog cung cp cho ngưi thit k

nhng công c trong vic to ra d liu kim tra testbench, tp tin truy xut

ñ!c, ghi, x lí d liu, to d liu, và mô hình hóa nhng phn cng

chuyên dng. Nhng tin ích h thng dùng cho b nh ñ!c và thit b(

logic lp trình ñưc (PLA) cung cp nhng phương pháp thun tin cho

vic mô hình hóa nhng thit b( này. Nhng tác v hin th( và I/O có th

ñưc s dng ñ kim soát tt c nhng ngõ vào và ngõ ra d liu ca ng

dng và mô phng. Verilog cho phép vic truy xut ñ!c và ghi ngu nhiên ñn các tp tin. Lâm Đc Khi

University of Information Technology Page 19