Preview text:

KIỂM TRA GIỮA KÌ – ĐỀ 6

Học phần: Hệ thống nhúng IoT Họ và tên: Mã SV: Nhóm LT:

1. Hệ thống nhúng được định nghĩa:

A. Là hệ thống mà tác vụ xử lý thông tin được nhúng vào các sản phẩm.

B. Là các thiết bị điện tử gia dụng có phần mềm điều khiển. C. Là các máy tính.

D. Là các thiết bị vật lý thông thường được gắn thêm bộ xử lý.

2. Lấy 3 ví dụ về hệ thống nhúng.

3. Lấy 3 ví dụ về hệ thống nhúng IoT.

4. Các thành phần phần cứng cơ bản của một hệ thống nhúng IoT là

A. Bộ xử lý trung tâm, bộ nhớ hệ thống và kiến trúc tập lệnh

B. Bộ xử lý trung tâm, bộ nhớ hệ thống và tập các cổng vào/ ra

C. Bộ vi xử lý, các thiết bị ngoại vi và bộ cài thiết bị

D. Bộ vi xử lý, các thiết bị ngoại vi và ngắt

5. ISA trong các hệ thống nhúng IoT được hiểu là

A. Là tập lệnh chung cho tất các các chip có sẵn trên thị trường.

B. Là tập lệnh riêng mà mỗi nhà sản xuất sản xuất chip tự phát triển.

C. Là tập lệnh mà bộ vi xử lý/ vi điều khiển cần thực thi và có ràng buộc cấu trúc nhất

định mà tất cả các chip phải tuân thủ.

D. Là mẩu silicon do nhà sản xuất chất bán dẫn cũng cấp để tích hợp bộ vi điều khiển trên đó.

6. Nhận định nào sau đây là SAI đối với xử lý song song trong hệ thống nhúng IoT

A. Một chương trình tính toán được cho là xử lý song song nếu các thành phần của

chương trình được thực thi cùng một lúc về mặt khái niệm.

B. Một chương trình tính toán được cho là xử lý song song nếu các thành phần của

chương trình được thực thi cùng một lúc về mặt vật lý trên một phần cứng xác định.

C. Có thể thực thi các lệnh theo cơ chế song song khác với trình tự của chương trình

mà vẫn thu được kết quả tương tự như trường hợp thực hiện theo trình tự chính xác.

D. Cơ chế xử lý song song ảnh hưởng tới thời gian thực thi một chương trình. Về

nguyên tắc, cho phép rút ngắn thời gian thực hiện.

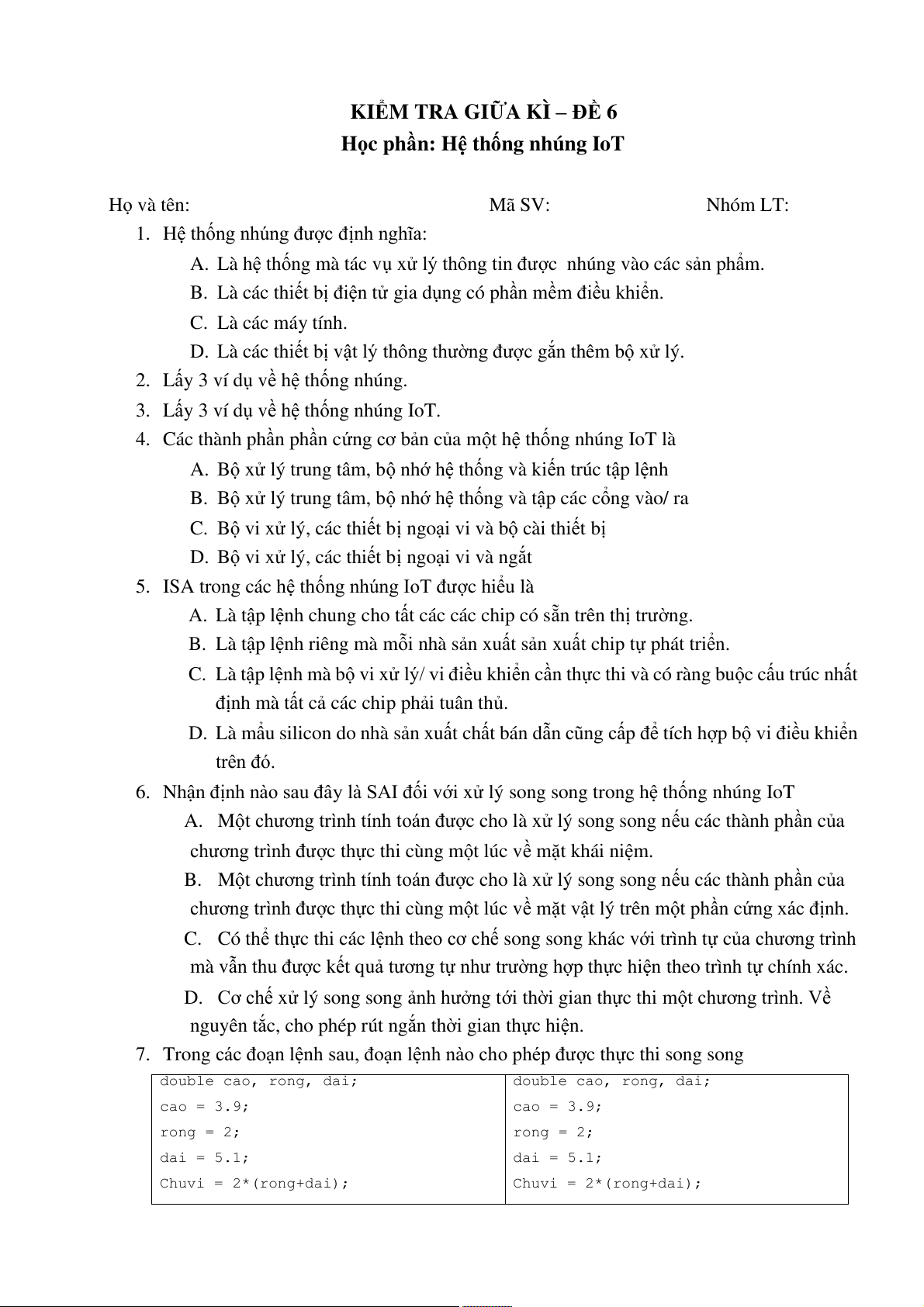

7. Trong các đoạn lệnh sau, đoạn lệnh nào cho phép được thực thi song song double cao, rong, dai; double cao, rong, dai; cao = 3.9; cao = 3.9; rong = 2; rong = 2; dai = 5.1; dai = 5.1; Chuvi = 2*(rong+dai); Chuvi = 2*(rong+dai); Sday = rong*dai; Sday = rong*dai; Sxq = 2*cao*(rong+dai); Sxq = 2*cao*(rong+dai); Stp = Sxq + 2*Sday;

Stp = 2*cao*(rong+dai) + 2*rong*dai; Đoạn 1 Đoạn 2 double cao, rong, dai; double cao, rong, dai; rong = 2; cao = 3.9; dai = 5.1; rong = 2; Sday = rong*dai; dai = 5.1; Chuvi = 2*(rong+dai);

Stp = 2*cao*(rong+dai)+ 2*rong*dai; cao = 3.9; Sday = rong*dai;

Stp = 2*cao*(rong+dai) + 2*rong*dai; Chuvi = 2*(rong+dai); Sxq = 2*cao*(rong+dai); Sxq = cao*Chuvi; Đoạn 3 Đoạn 4 A. Đoạn 1 và đoạn 2 B. Đoạn 4 và đoạn 3 C. Đoạn 2 và đoạn 4 D. Đoạn 3 và đoạn 2

8. Kích thước của bộ vi xử lý nào sau đây là đúng A. Bộ vi xử lý 32 byte B. Bộ vi xử lý 4 byte

C. Bộ vi xử lý 4 từ (word) D. Bộ vi xử lý 32 bit

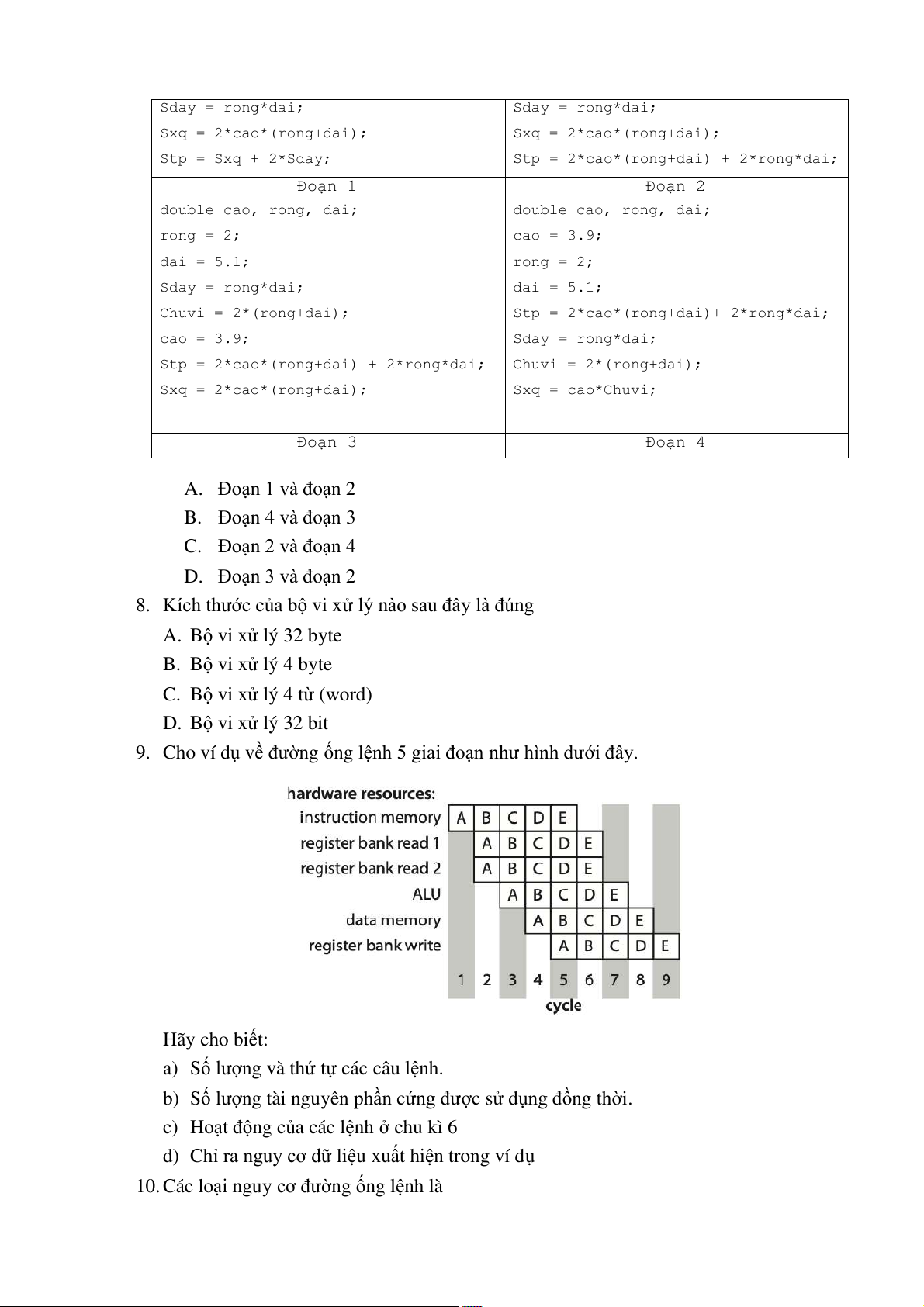

9. Cho ví dụ về đường ống lệnh 5 giai đoạn như hình dưới đây. Hãy cho biết:

a) Số lượng và thứ tự các câu lệnh.

b) Số lượng tài nguyên phần cứng được sử dụng đồng thời.

c) Hoạt động của các lệnh ở chu kì 6

d) Chỉ ra nguy cơ dữ liệu xuất hiện trong ví dụ

10. Các loại nguy cơ đường ống lệnh là

A. Nguy cơ cấu trúc, nguy cơ bộ nhớ, nguy cơ dữ liệu

B. Nguy cơ bộ nhớ, nguy cơ dữ liệu, nguy cơ điều khiển

C. Nguy cơ cấu trúc, nguy cơ dữ liệu, nguy cơ điều khiển

D. Nguy cơ điều khiển, nguy cơ bộ nhớ, nguy cơ cấu trúc.

11. Các bộ nhớ không bay hơi, tức là dữ liệu không bị mất khi mất nguồn, là A. ROM, EEPROM B. Flash C. RAM, SRAM, DRAM D. SSD, HDD

Chú ý: có thể lựa chọn nhiều hơn một đáp án

12. Định nghĩa về kiến trúc Harvard và kiến trúc Neumann là

A. Kiến trúc Harvard phân biệt địa chỉ dành cho bộ nhớ chương trình và bộ nhớ dành

cho dữ liệu; kiến trúc Neumann sử dụng cùng một bộ nhớ để lưu chương trình và dữ liệu.

B. Kiến trúc Neumann phân biệt địa chỉ dành cho bộ nhớ chương trình và bộ nhớ dành

cho dữ liệu; kiến trúc Harvard sử dụng cùng một bộ nhớ để lưu chương trình và dữ liệu.

C. Kiến trúc Neumann sử dụng bộ nhớ ROM để lưu chương trình trong khi kiến trúc

Harvard sử dụng bộ nhớ RAM để lưu chương trình.

D. Kiến trúc Harvard sử dụng bộ nhớ ROM để lưu chương trình trong khi kiến trúc

Neumann sử dụng bộ nhớ RAM để lưu chương trình.

13. Một kiến trúc bộ xử lý 64 bit có địa chỉ thanh ghi đầu tiên là 00000000. Mỗi từ lệnh của

ISA cần ít nhất 56 bit cho chạy chương trình. Hãy tính số lượng thanh ghi tối đa và địa

chỉ của từng thanh ghi trong bộ xử lý.

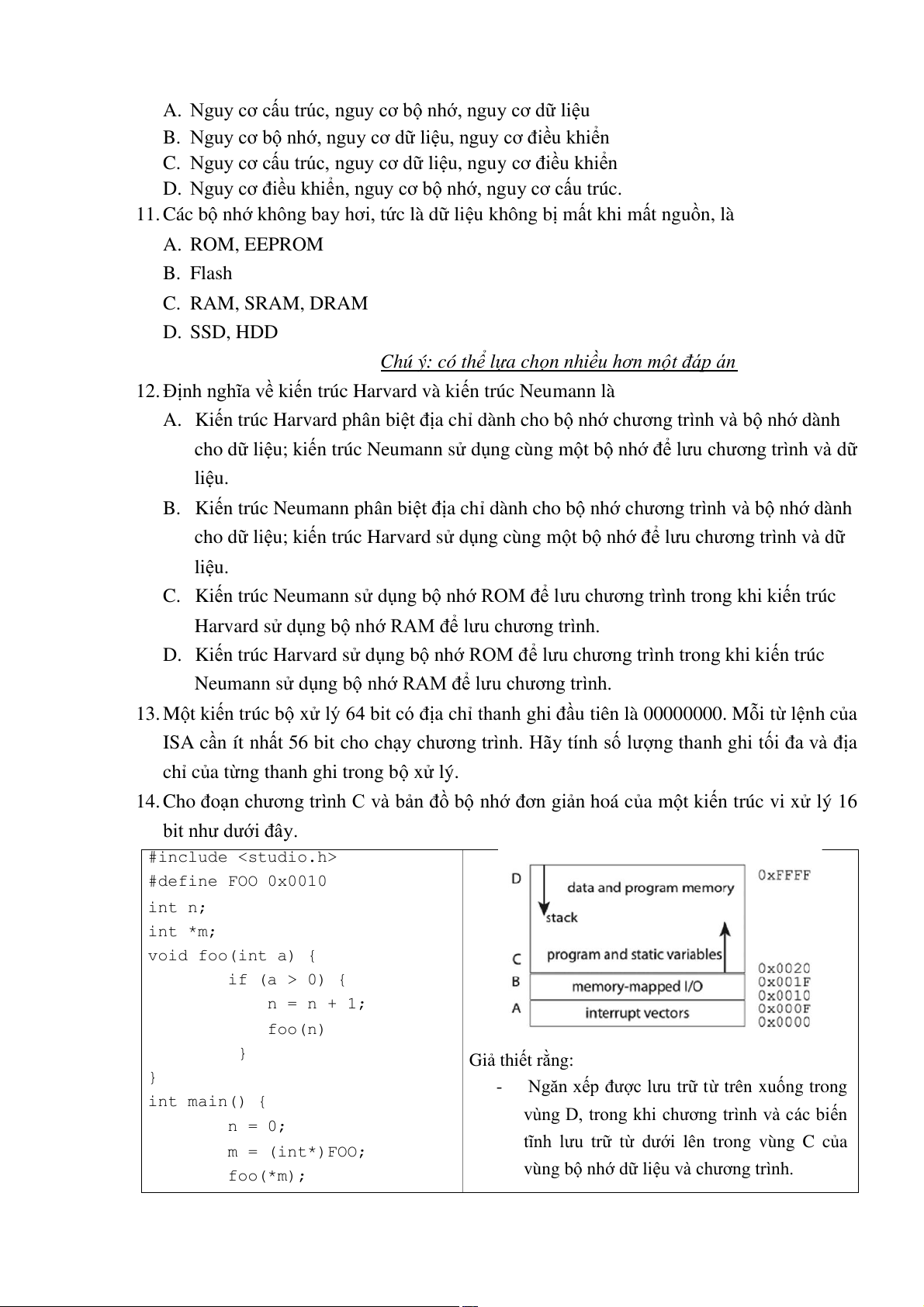

14. Cho đoạn chương trình C và bản đồ bộ nhớ đơn giản hoá của một kiến trúc vi xử lý 16 bit như dưới đây. #include #define FOO 0x0010 int n; int *m; void foo(int a) { if (a > 0) { n = n + 1; foo(n) } Giả thiết rằng: }

- Ngăn xếp được lưu trữ từ trên xuống trong int main() {

vùng D, trong khi chương trình và các biến n = 0;

tĩnh lưu trữ từ dưới lên trong vùng C của m = (int*)FOO; vùng b nh ộ ớ dữ li ệu và chương trình. foo(*m); printf(“n = %d\n”, n );

- Toàn bộ không gian địa chỉ đều ánh xạ được } đế ộ n b nhớ ậ v t lý của hệ thống.

Giả thiết rằng trong hệ thống, int là một số 16 bit, hệ thống không có hệ điều hành và bảo

vệ bộ nhớ, và chương trình được biên dịch và nạp vào vùng C của bộ nhớ. Hãy cho biết:

a) Vị trị các biến n, m và a được lưu trữ trong bộ nhớ (vùng A, B, C hay D).

b) Chương trình thực hiện như thế nào nếu nội dung tại địa chỉ 0x0010 là 0 khi nhập.

15. Với kích thước bộ vi xử lý là 64 bit, kích thước của một từ (word) chứa trong mỗi thanh ghi của tệp thanh ghi là A. 8 bit B. 16 bit C. 32 bit D. 64 bit

16. Các giao diện nối tiếp được chuẩn hoá trong phần cứng hệ thống nhúng IoT là

A. RS-232, UART, USB, JTAG, I2C, PCI

B. RS-232, UART, I2C, IEEE-1284, BUS

C. RS-232, JTAG, I2C, PCI, IEEE-1284

D. RS-232, JTAG, I2C, BUS, IEEE-1284

17. Thứ tự các bước khi phần cứng quyết định phục vụ một ngắt:

A. Kích hoạt ngắt – Đẩy bộ đếm chương trình hiện thời và thanh ghi trạng thái bộ xử lý

vào ngăn xếp – Chuyển tới địa chỉ chứa bước nhảy tới ISR – Lưu trữ vào ngăn xếp

các giá trị trong thanh ghi hiện thời – Khôi phục chương trình ban đầu, vô hiệu hoá ngắt.

B. Đẩy bộ đếm chương trình hiện thời và thanh ghi trạng thái bộ xử lý vào ngăn xếp –

Kích hoạt ngắt – Chuyển tới ị

đ a chỉ chứa bước nhảy tới ISR – Lưu trữ vào ngăn xếp

các giá trị trong thanh ghi hiện thời – Khôi phục chương trình ban đầu, vô hiệu hoá ngắt.

C. Đẩy bộ đếm chương trình hiện thời và thanh ghi trạng thái bộ xử lý vào ngăn xếp –

Chuyển tới địa chỉ chứa bước nhảy tới ISR – Lưu trữ vào ngăn xếp các giá trị trong

thanh ghi hiện thời – Khôi phục chương trình ban đầu.

D. Kích hoạt ngắt – Đẩy bộ đếm chương trình hiện thời và thanh ghi trạng thái bộ xử lý

vào ngăn xếp, vô hiệu hoá ngắt – Chuyển tới địa chỉ chứa bước nhảy tới ISR – ISR

lưu trữ vào ngăn xếp các giá trị hiện thời trong thanh ghi nó sử dụng, kích hoạt ngắt

– Khôi phục chương trình ban đầu tại vị trí bị dừng, vô hiệu hoá ngắt.