Preview text:

TR ƯƠ NG CÔNG HOÀNG VI Ệ T

MỤ C LỤ C ▪ MODULE 3 ▪

THIỆ T KỆ MẠ CH TỔ HƠ P VƠ I ASSIGN 4 ▪

THIỆ T KỆ MẠ CH BẠ NG PRIMITIVES 6 ▪

THIỆ T KỆ MẠ CH TỔ HƠ P VƠ I ALWAYS 7 ▪ VERILOG REGISTER 8 ▪

THIỆ T KỆ MẠ CH TỔ HƠ P BẠ NG PHƯƠNG PHÁP KỆ T HƠ P 9 ASSIGN VÀ ALWAYS ▪

THIỆ T KỆ MẠ CH TỔ HƠ P SƯ DỤ NG CASE 10 ▪

CÁC LƯU Ý KHI THIỆ T KỆ MẠ CH TỔ HƠ P 11 ▪

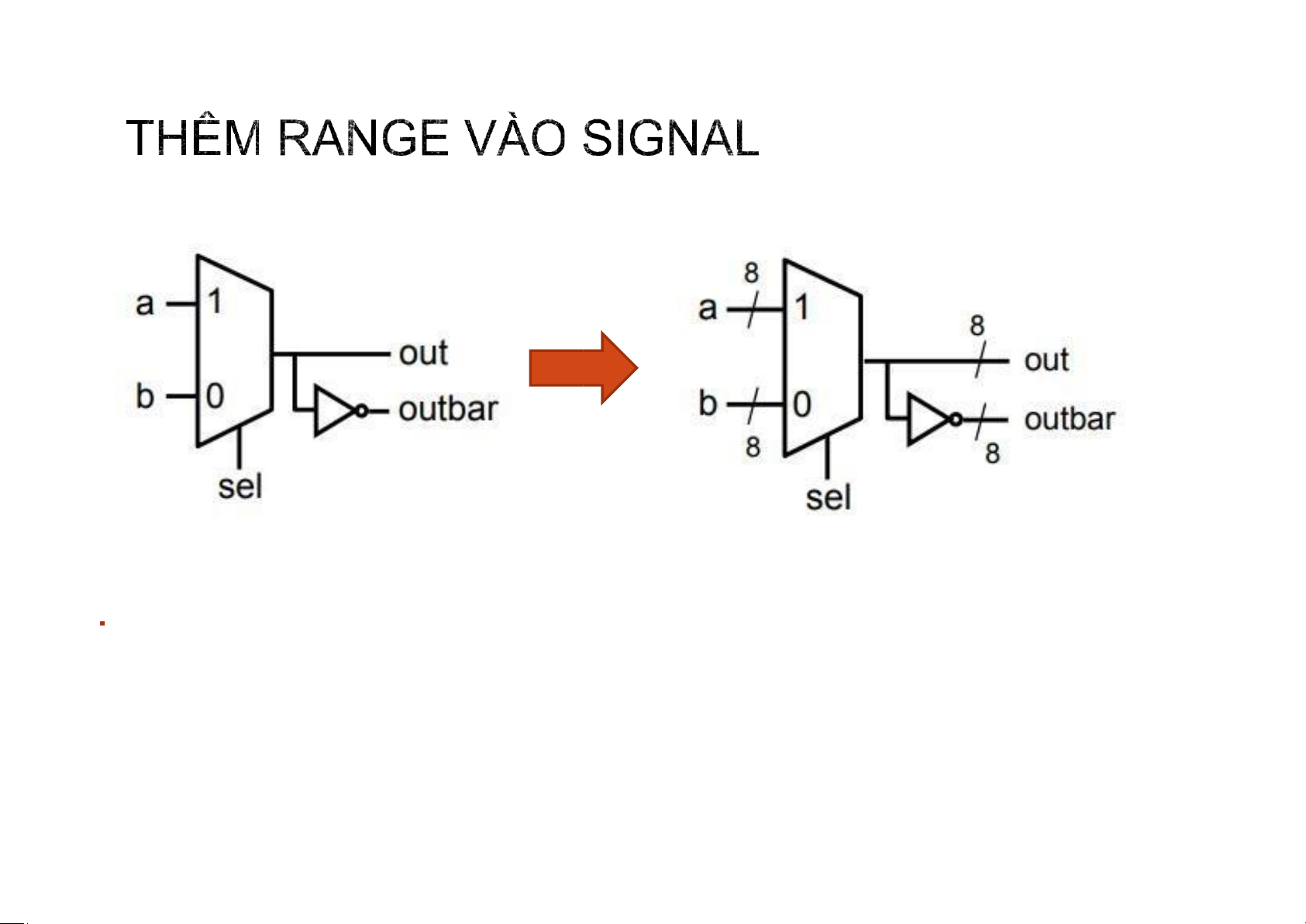

MẠ CH TẠ O LATCH SƯ DỤ NG IF 16 ▪ THÊM RANGE VÀO SIGNAL 17 ▪

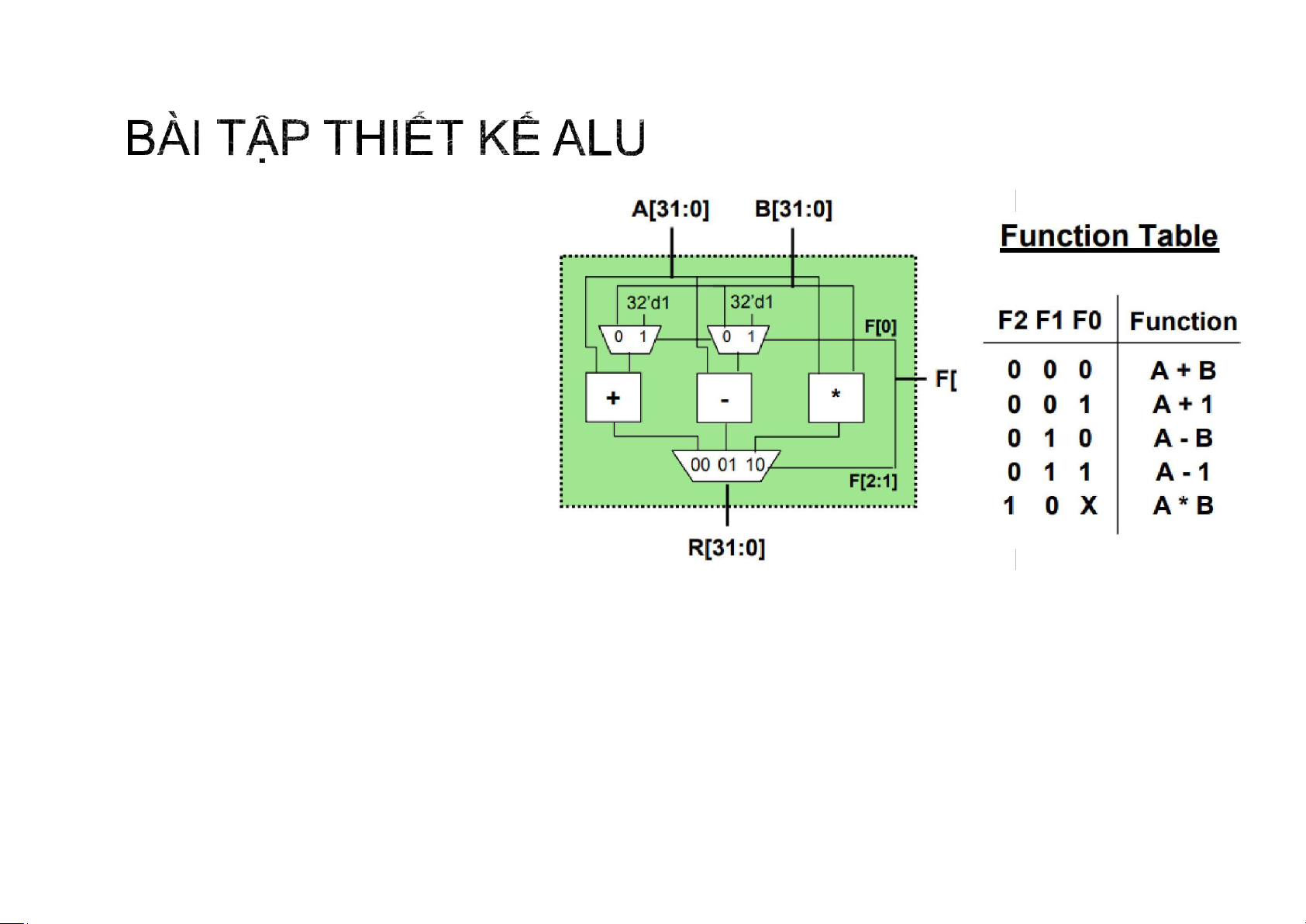

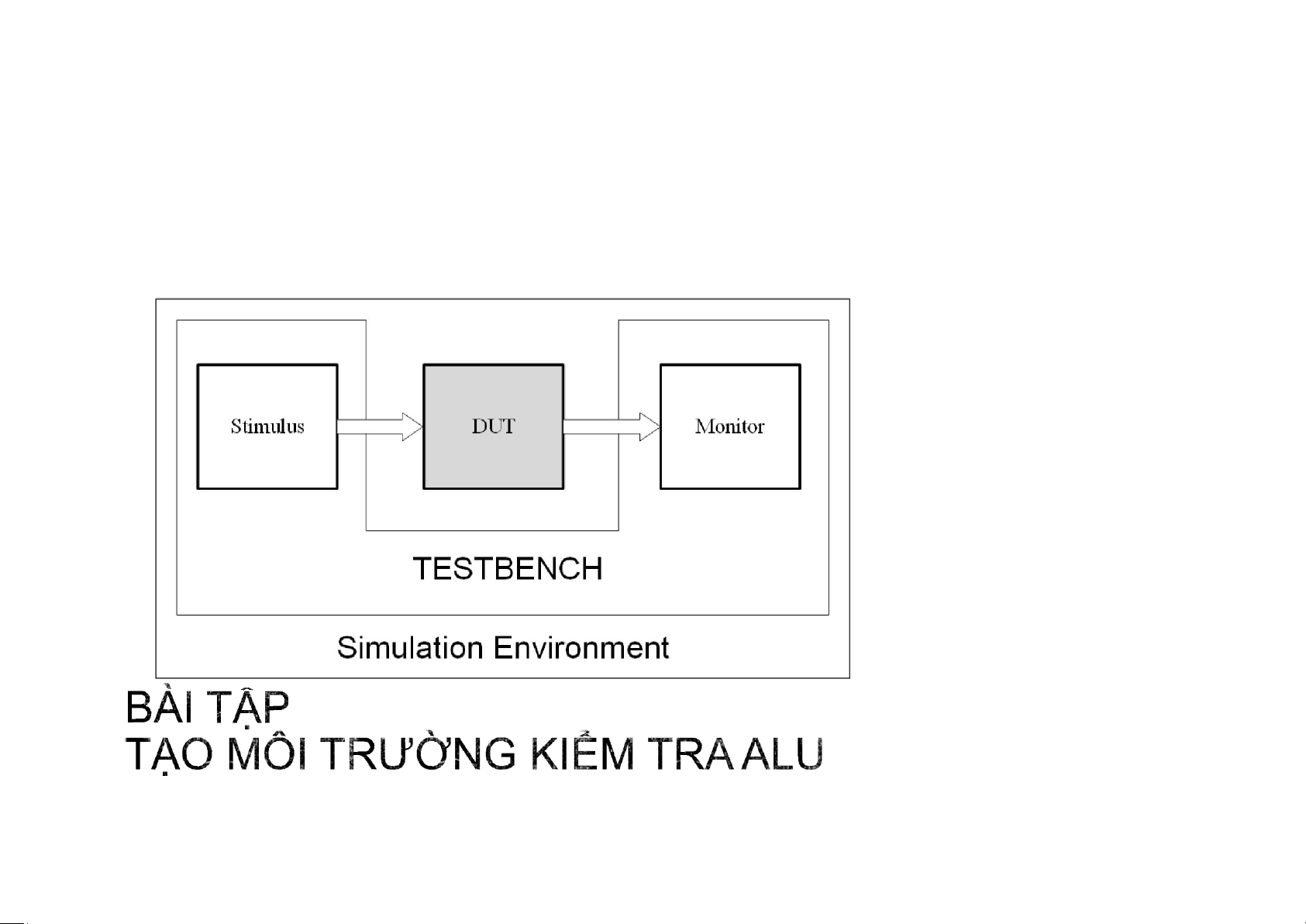

BÀI TẠ P THIỆ T KỆ ALU, TẠ O MÔI TRƯƠ NG KIỆ M TRA 19 ALU

TRƯƠNG CÔNG HOÀNG

Downloaded by Uc Lan (uehbsaxac464@gmail.com) •

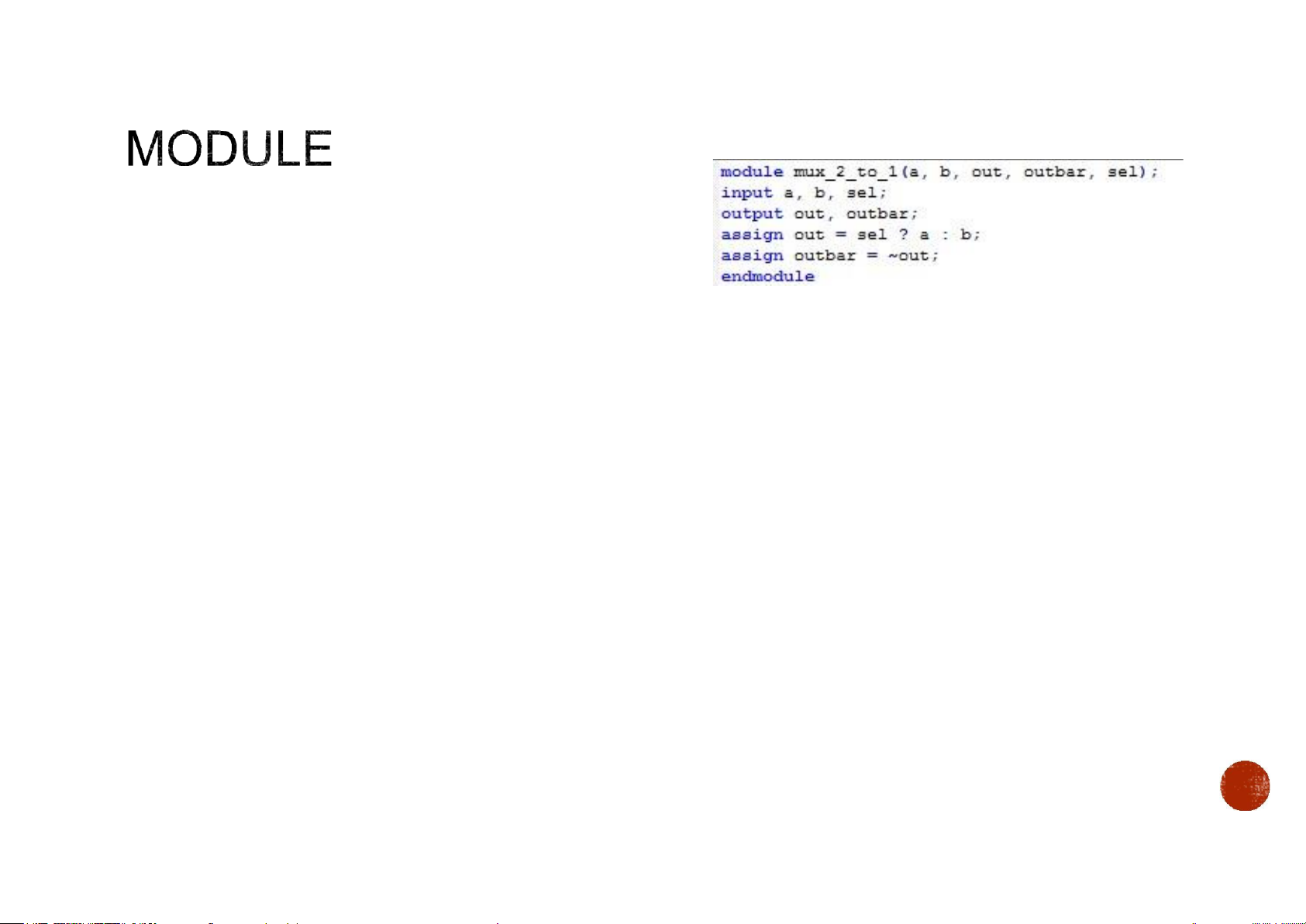

Một thiết kế bao gồm nhiều module liên kết ▪ Ví dụ với nhau •

Module có thể là một thành phần hoặc bao gồm

các khối thiết kế nhỏ hơn ▪

Khai báo tên module cùng với danh sách port và dấu ; theo sau ▪

Dấu comment ‘//’ dùng để ghi chú ▪ Khai báo input output ▪

net thể hiện connection giữa các phần tử, được khai báo là wire ▪

Mô tả hành vi, mỗi statement sẽ được thực thi song song, thứ tự không quan trọng ▪

Kết thúc module bằng endmodule

TRƯƠNG CÔNG HOÀNG

Downloaded by Uc Lan (uehbsaxac464@gmail.com)

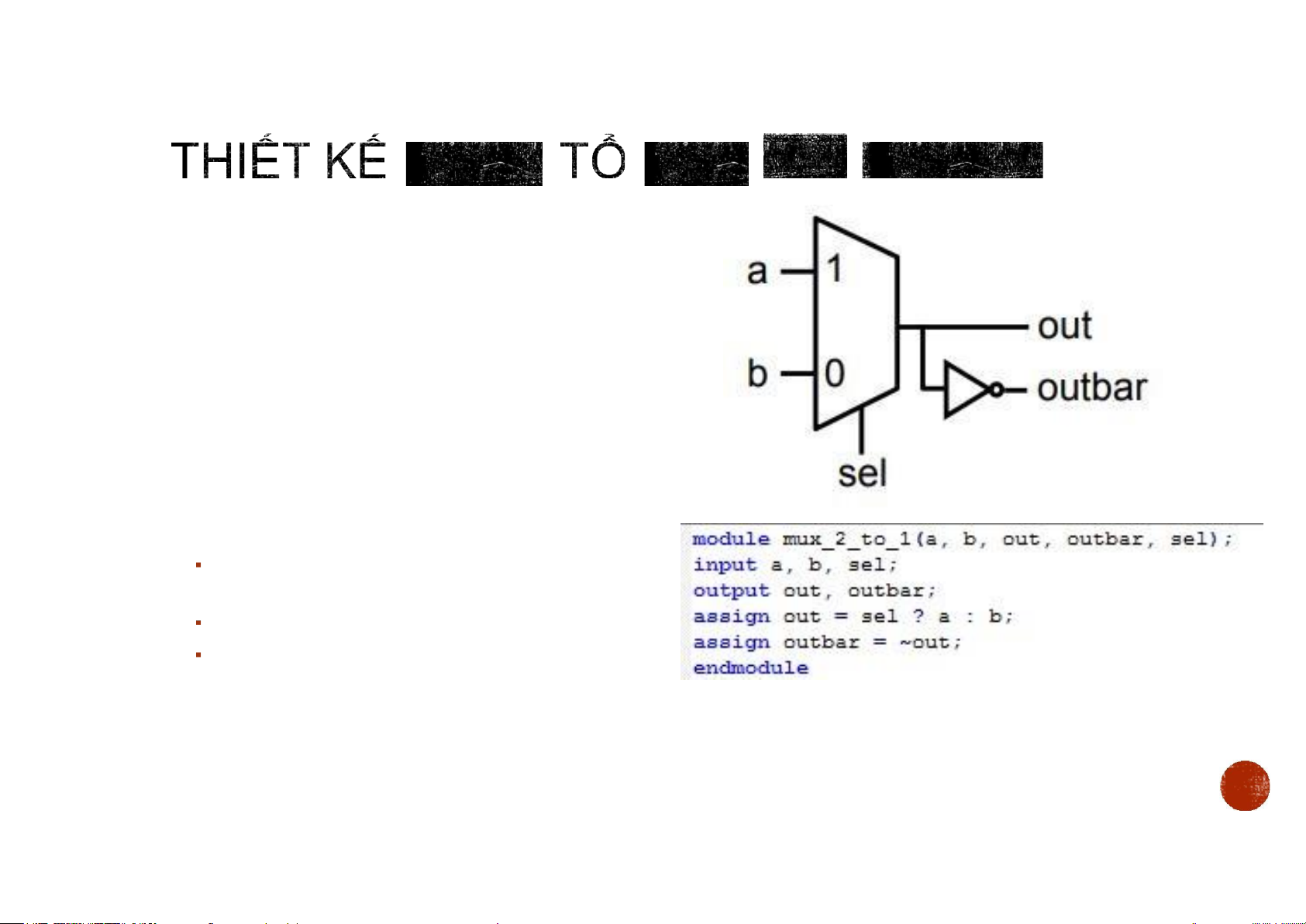

Phép gán liên tục sử dụng lệnh assign

Giá trị RHS liên tục được tính toán mối khi

giá trị input thay đổi và gán cho LHS

Đối tượng của phép gán liên tục là net được

lái “drive” bởi mạch tổ hợp

LHS phải có kiểu dữ liện là “scalar” hoặc

“vector” net. RHS có thể là net hoặc register

Operator cho phép gán liện tục:

Gán có điều kiện: (conditional_expression)

? (value - if - true) : (value - if - false);

Logic nhị phân: ~, &, | Logic số học: +, -, ▪ ▪

TRƯƠNG CÔNG HOÀNG

Downloaded by Uc Lan (uehbsaxac464@gmail.com) ▪ ▪ ▪

TRƯƠNG CÔNG HOÀNG

Downloaded by Uc Lan (uehbsaxac464@gmail.com)

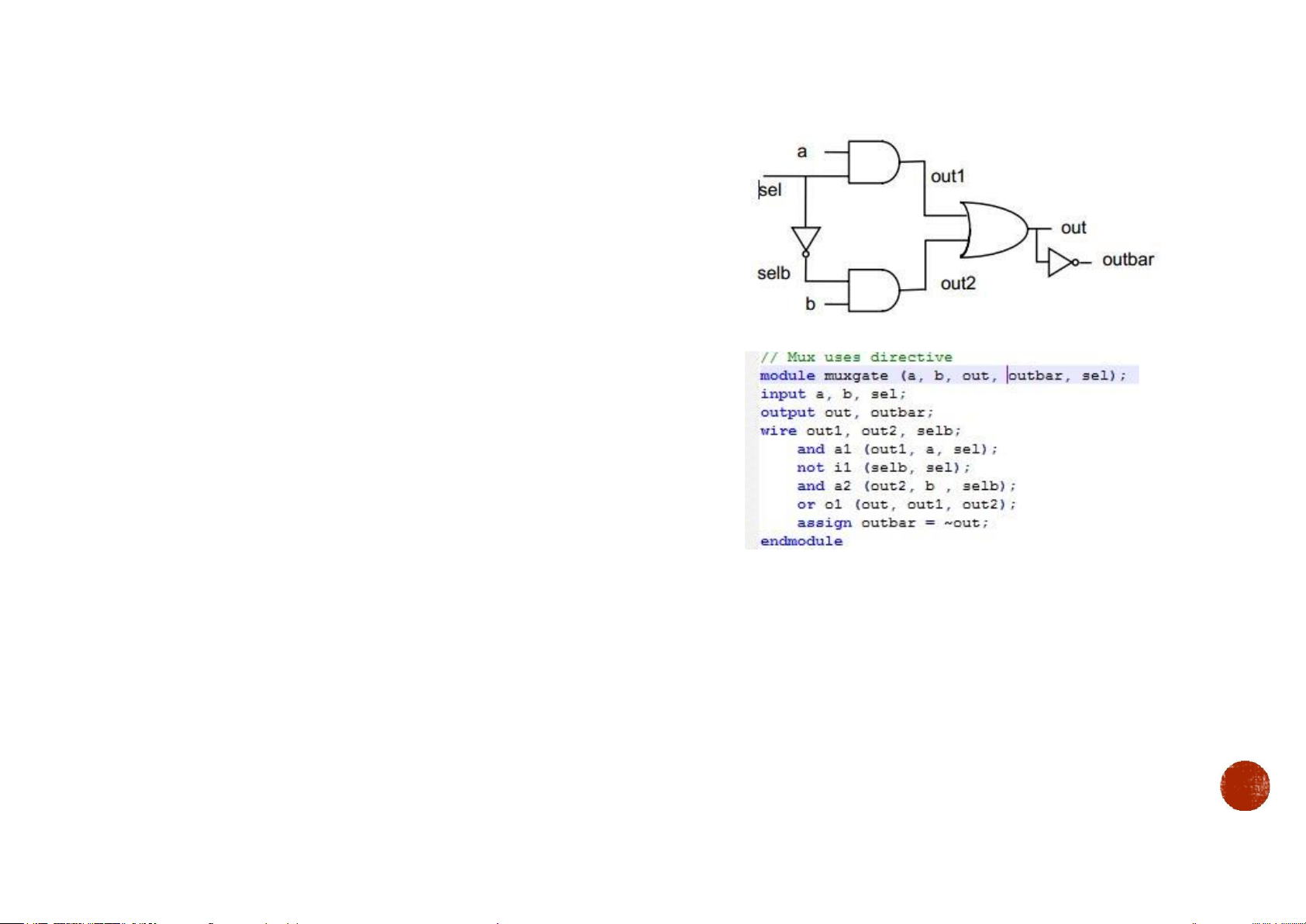

▪ Verilog hỗ trợ style code bằng cổng logic cơ bản

được gọi là “primitives”. “Primitives là những dòng lệnh thường để

hướng dẫn tool xử lý data theo ý của người dùng ▪

and, nand, or, nor, xor, xnor, not, buf

▪ Có thể được mở rộng thành cổng có nhiều input, ví

dụ nand nand3in (out,in1,in2,in3); ▪

Bufif1 and bufif0 là tri-state buffers

TRƯƠNG CÔNG HOÀNG

Downloaded by Uc Lan (uehbsaxac464@gmail.com)

Phép gán thủ tục có 2 cấu trúc là Initial và always

Hỗ trợ những statement if, for, while,case

Sử dụng phép gán thủ tục

Biến được gán trong always phải được khai báo là reg always @(), always được

thực thi khi 1 trong các giá trị trong sensitive list thay đỏi

Những lệnh được sử dụng trong always,

được thực hiện một cách tuần tự

Always bắt đầu bằng begin và kết thúc bằng end ▪

TRƯƠNG CÔNG HOÀNG

Downloaded by Uc Lan (uehbsaxac464@gmail.com) ▪

“Digital register” thể hiện là một bộ nhớ

▪ “Digital register” cần clock để hoạt động và cập nhật giá trị ở một thời điểm nhất định hoặc cạnh clock ▪

Register trong verilog không phải là thanh ghi khi nhắc đến phần cứng ▪

Register khai báo là reg trong verilog chỉ đơn giản là một biến có thể giữ giá trị ▪

Register trong verilog không cần clock để hoạt động, cũng không cần đươc lái như 1 net

▪ Giá trị của register có thể được thay đổi khi mô phỏng khi có một giá trị mới được gán vào register VIỆ Tc

TRƯƠNG CÔNG HOÀNG

Downloaded by Uc Lan (uehbsaxac464@gmail.com)

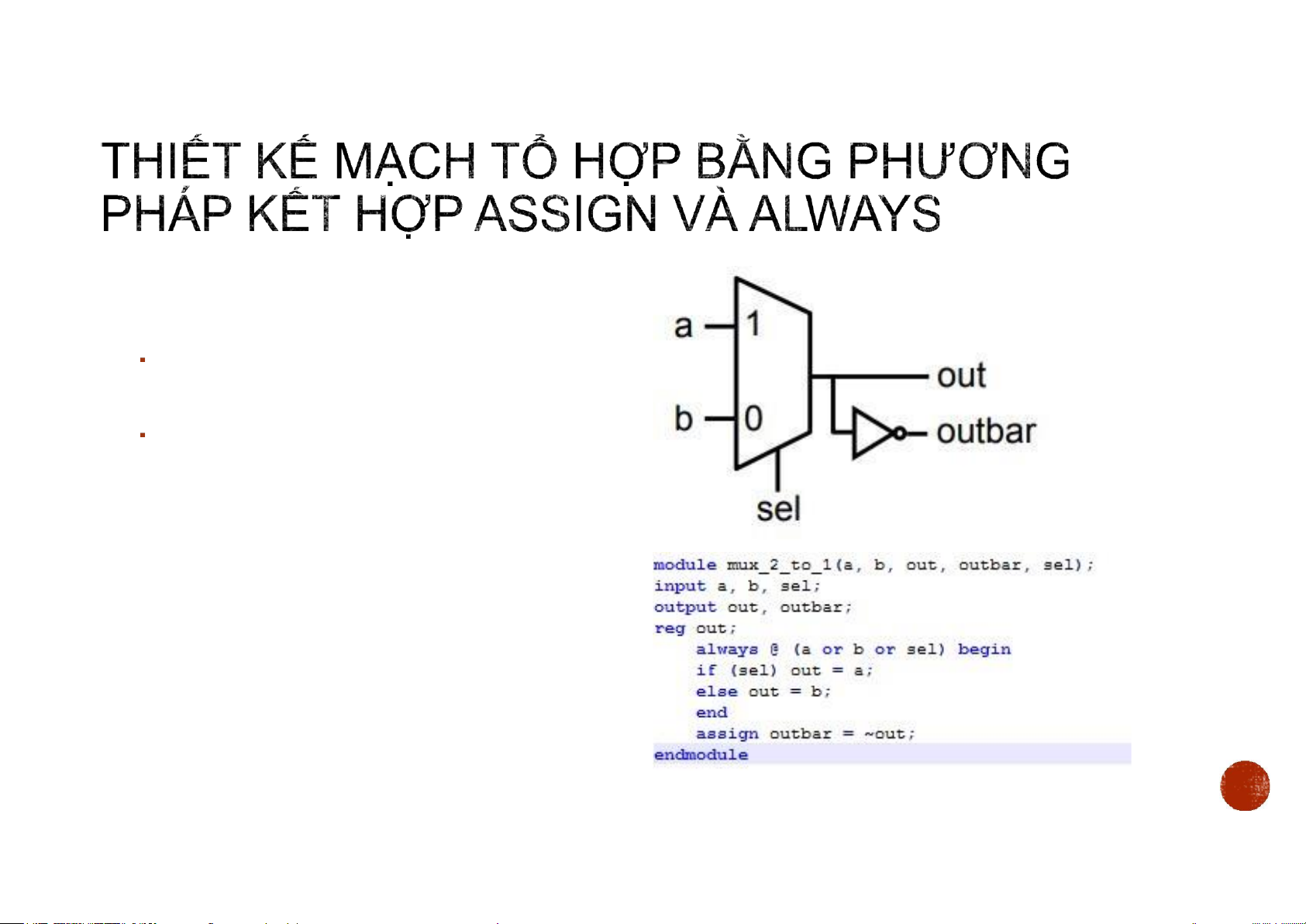

Kết hợp phép gán tuần tự và phép gán liên

tục trong cùng một module

Phép gán thủ tục sẽ cập nhật giá trị cho reg

out, giá trị sẽ không đổi cho đến khi một

phép gán thủ tục khác cập nhật lại giá trị cho biến đó .

TRƯƠNG CÔNG HOÀNG

Downloaded by Uc Lan (uehbsaxac464@gmail.com) VIỆ T c ▪

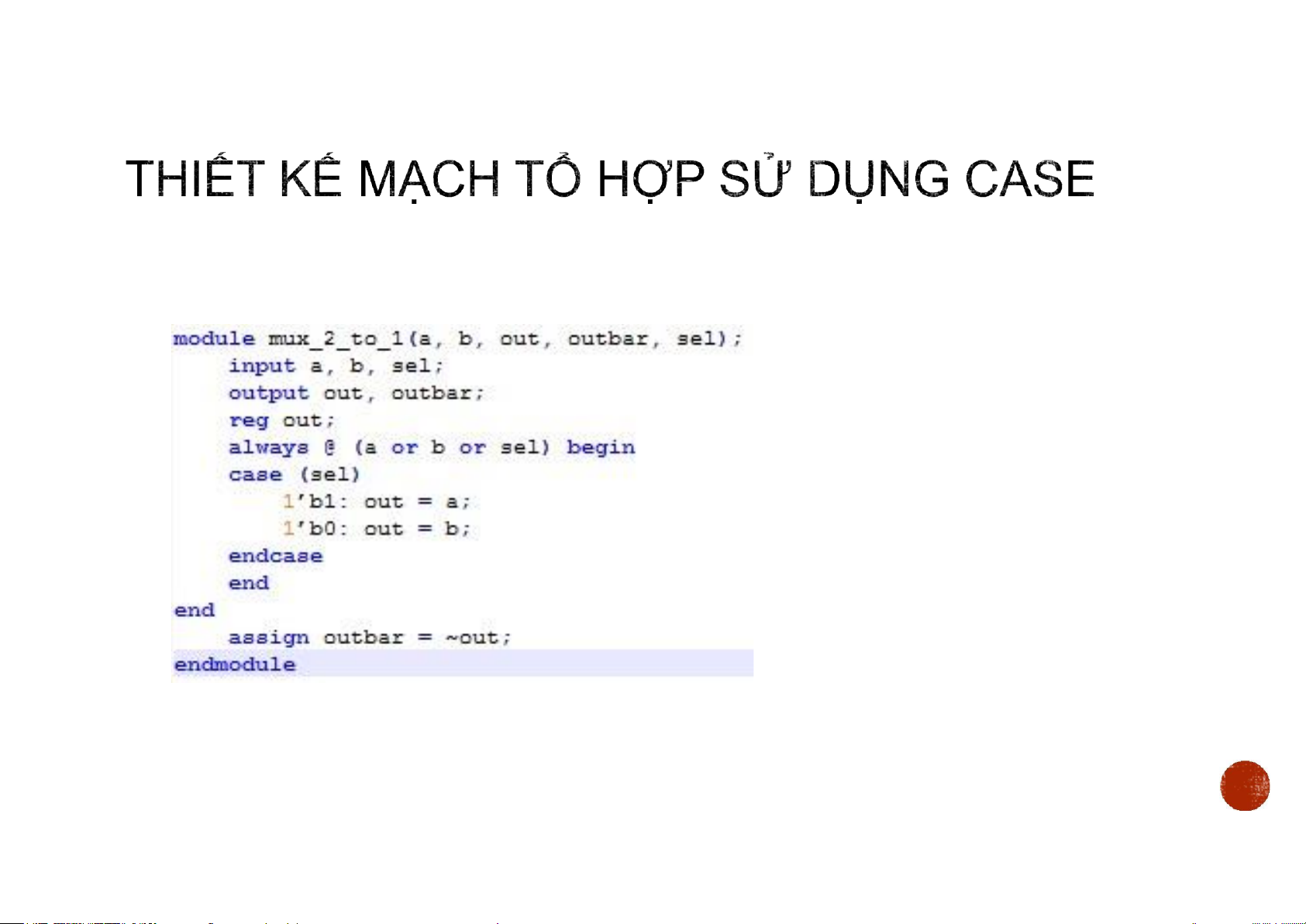

Case và if có thể được hoán đổi cho nhau trong always ▪

Case dễ đọc và ngắn gọn hơn

TRƯƠNG CÔNG HOÀNG

Downloaded by Uc Lan (uehbsaxac464@gmail.com) lOMoAR cPSD| 59671932

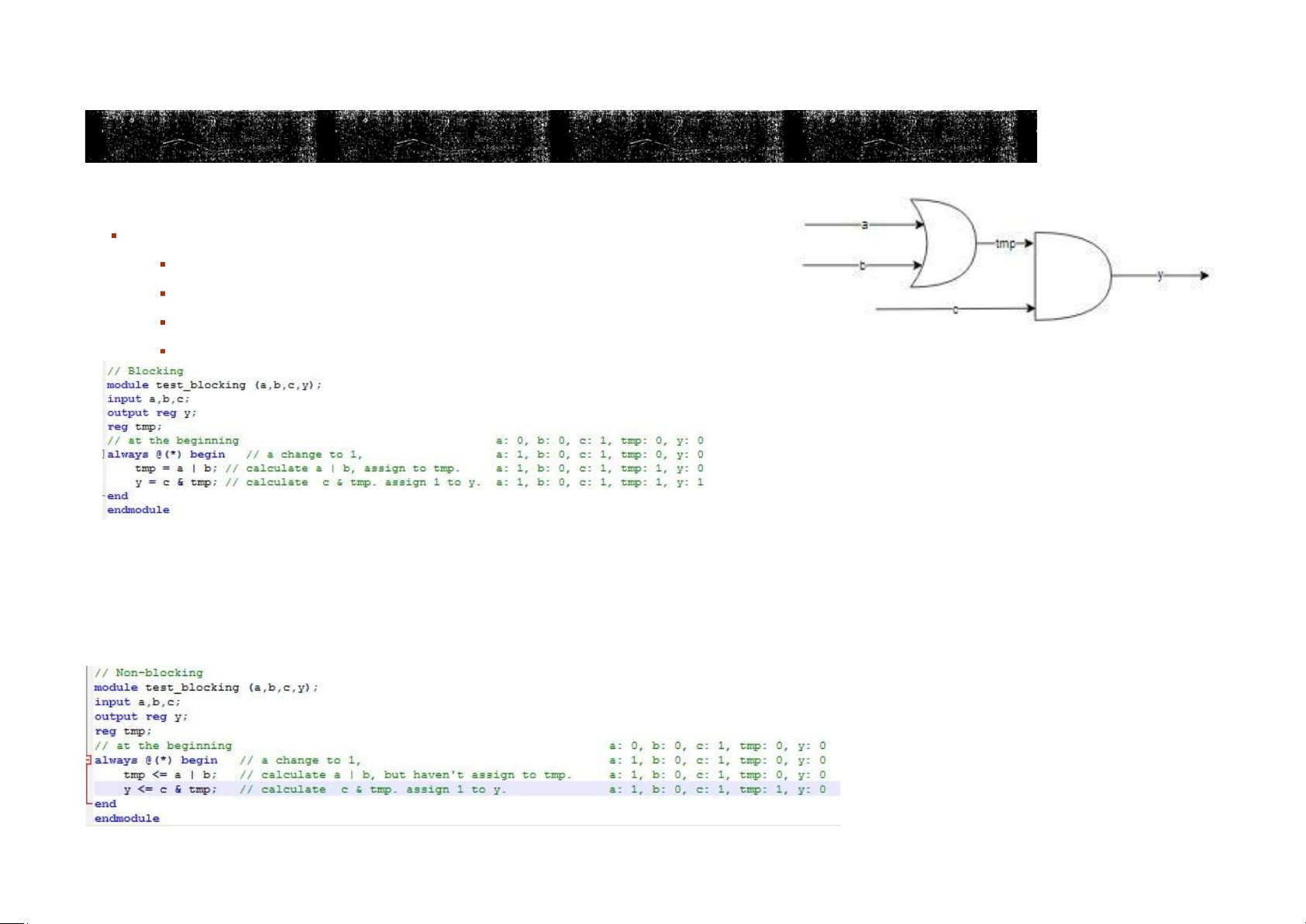

▪ Sử dụng phép gán blocking

▪ Mô tả đúng thứ tự phép gán ▪ Tránh tạo latch lOMoAR cPSD| 59671932

Sử dụng phép gán blocking để mô tả mạch tổ hợp

Ví dụ sử dụng blocking để mô tả mạch tổ hợp

a : 0, b: 0, c: 1, tmp : 0, y: 0, giá trị ban đầu

a : 1, b: 0, c: 1, tmp : 0, y: 0, a thay đổi giá trị sang 1

a : 1, b: 0, c: 1, tmp : 1, y: 0, tính toán a | b và gán cho tmp

a : 1, b: 0, c: 1, tmp : 1, y: 1, tính toán c & tmp và gán 1 cho y ▪

Ví dụ khi sử dụng non-blocking để mô tả mạch tổ hợp ▪

a: 0, b: 0, c: 1, tmp: 0, y: 0, giá trị ban đầu ▪

a: 1, b: 0, c: 1, tmp: 0, y: 0, a thay đổi giá trị sang 1 ▪

a: 1, b: 0, c: 1, tmp: 0, y: 0, tính toán a | b nhưng chưa gán cho tmp ▪

a: 1, b: 0, c: 1, tmp: 1, y: 0, tính toán c & tmp và gán 1 cho y lOMoAR cPSD| 59671932

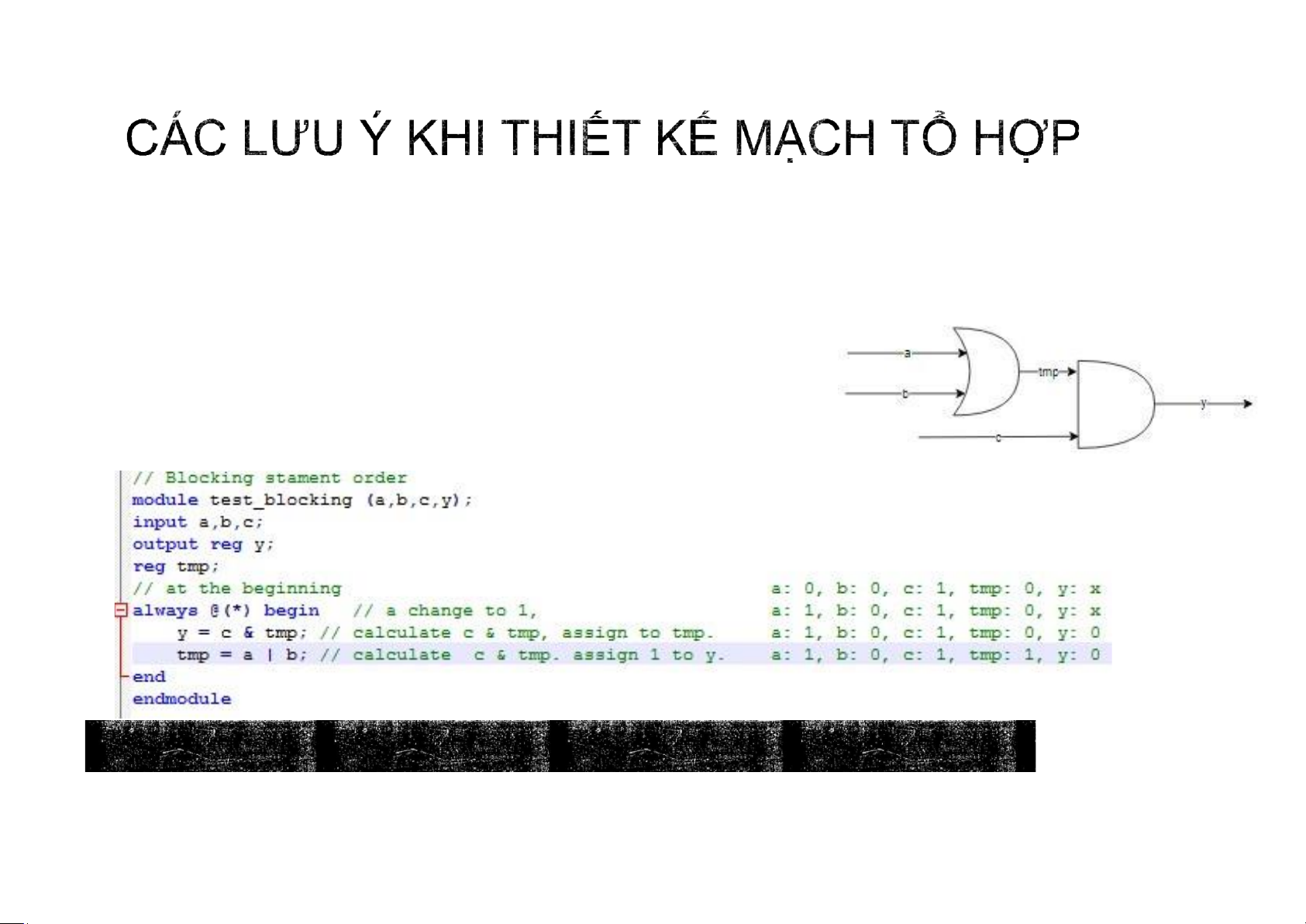

Mô tả đúng thứ tự phép gán

▪ Ví dụ về thứ tự phép gán không đúng

▪ a: 0, b: 0, c: 1, tmp: 0, y: 0, giá trị ban đầu

▪ a: 1, b: 0, c: 1, tmp: 0, y: 0, a thay đổi giá trị sang 1

▪ a: 1, b: 0, c: 1, tmp: 1, y: 0, tính toán c & tmp và gán cho y

▪ a: 1, b: 0, c: 1, tmp: 1, y: 1, tính toán c & tmp và gán 1 cho y lOMoAR cPSD| 59671932 Tránh tạo latch ▪

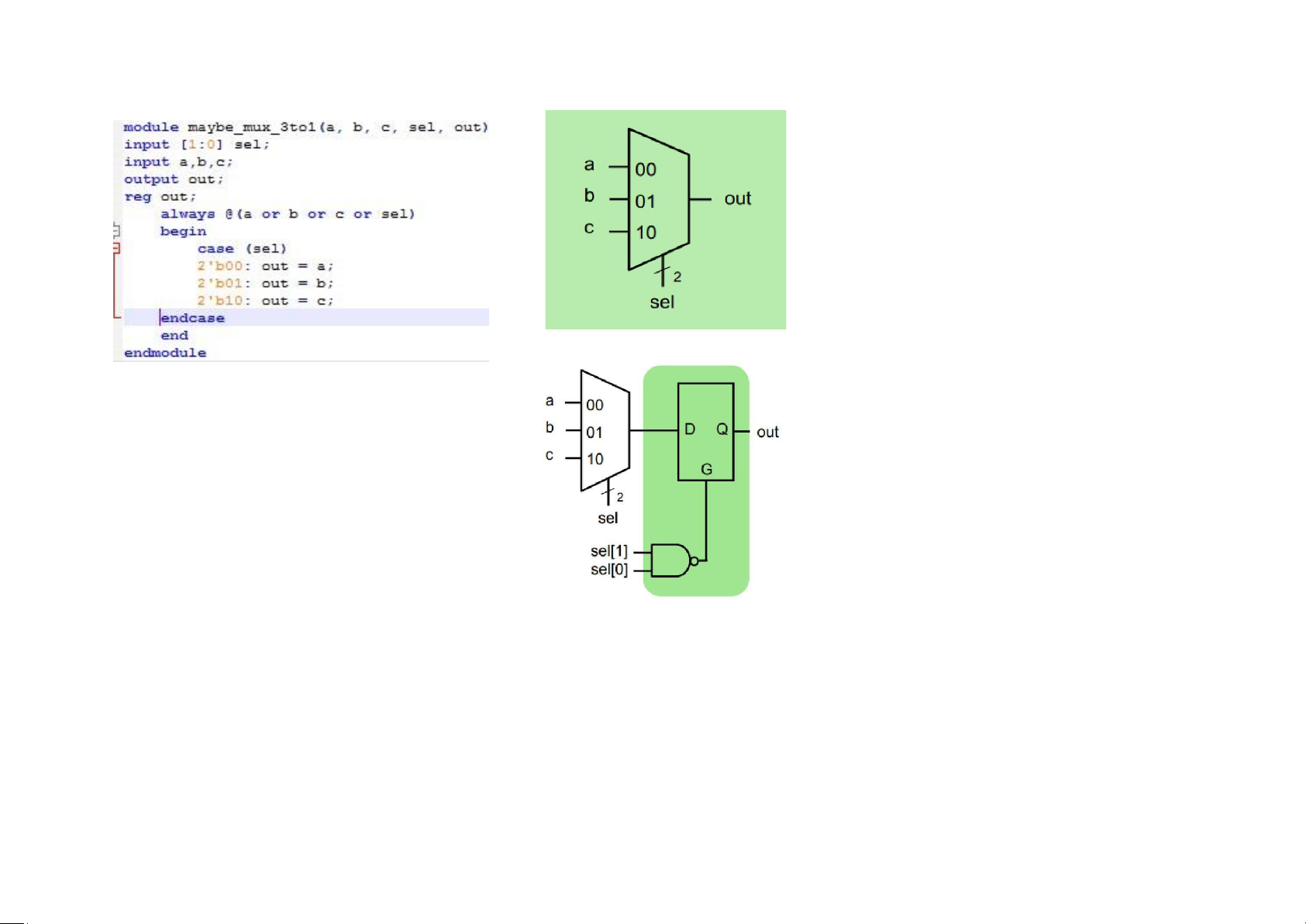

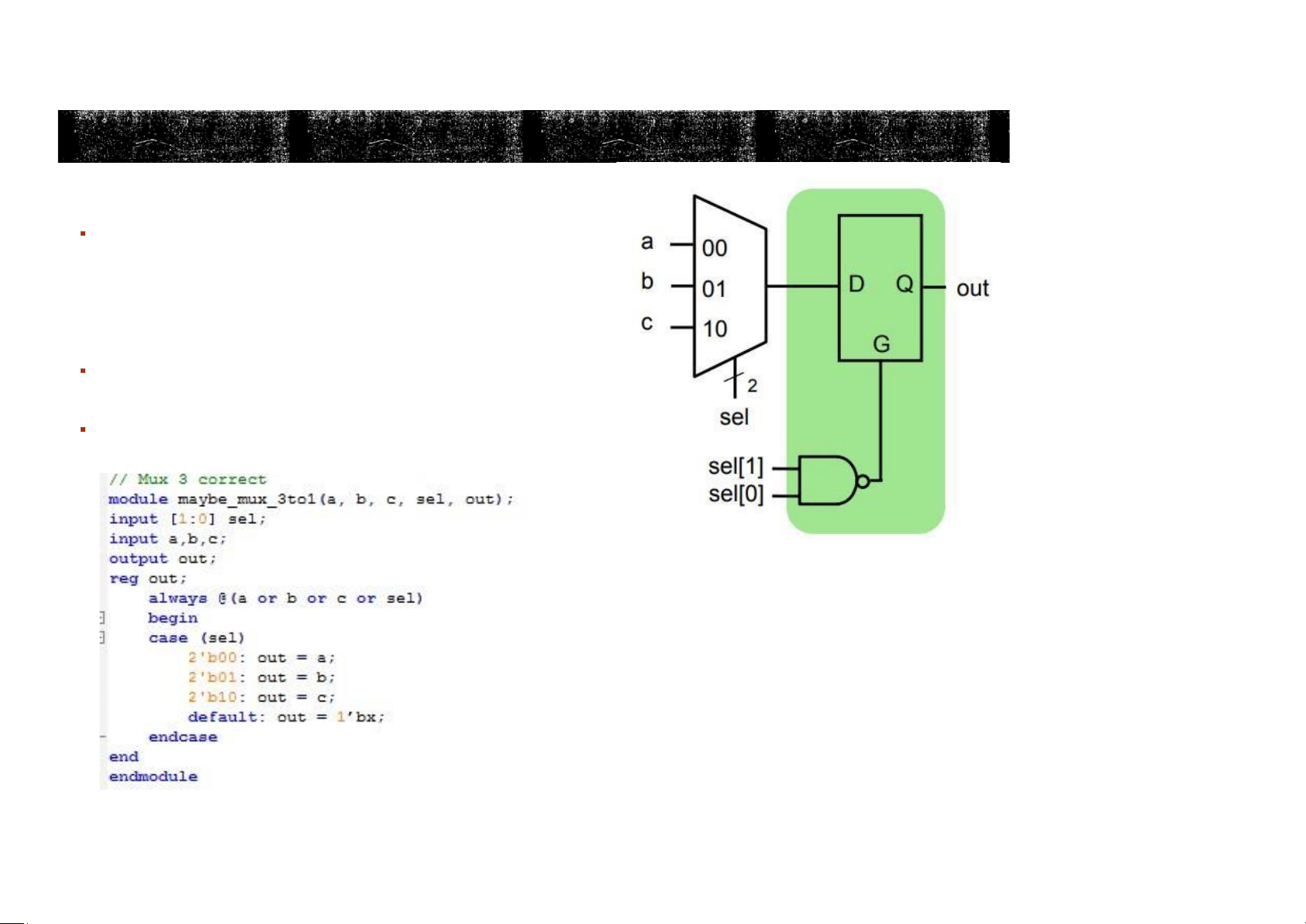

Sử dụng phát biểu case để mô tả mux3-1 lOMoAR cPSD| 59671932

Kết quả tổng hợp thực tế ▪ ▪ lOMoAR cPSD| 59671932 Tránh tạo latch

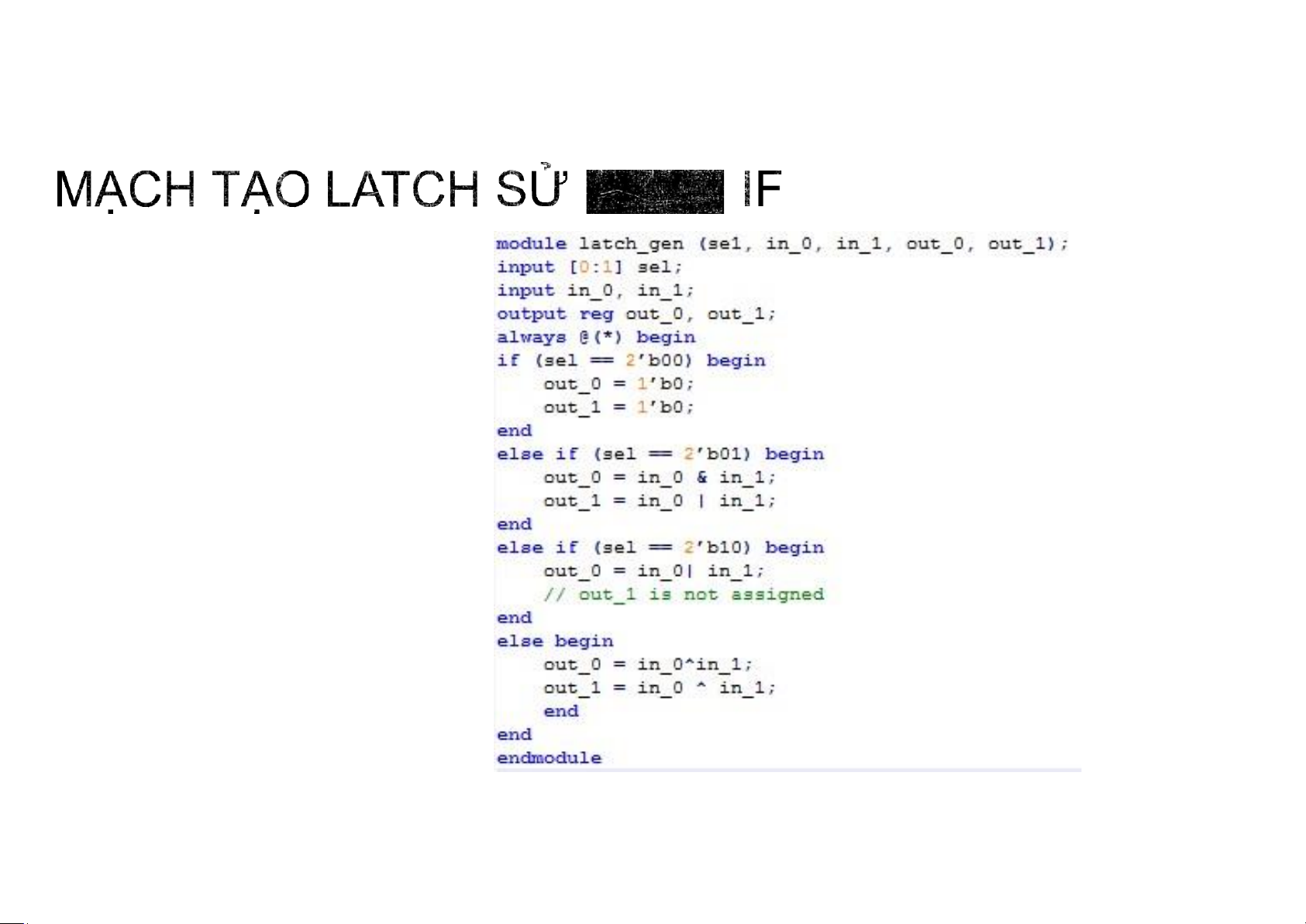

Trong những điều kiện mà biến “out” không được

assign giá trị khi vong always được thực thi thì giá

trị của out sẽ được giữ lại giá trị trước đó => latch

sinh ra trong khi sel = 2’b11. G = 0, latch sẽ giữ

lại giá trị trước đó

Thông thường trong thiết kế, người thiết kế không mong muốn điều này

Thêm default vào case để không xuất hiện latch ngoài ý muốn: lOMoAR cPSD| 59671932 ▪

Latch sẽ được sinh ra để giữ

giá trị của “out_1” khi sel = 2 ’b 10 lOMoAR cPSD| 59671932

Làm như thế nào trong RTL code? lOMoAR cPSD| 59671932 ▪ ▪ ▪ ▪ Input F[2:0] lựa chọn phép tính Input A[31;0], số hạng A Input B[31;0], số hạng B Viết testbench lOMoAR cPSD| 59671932 TESTBENCH CƠ BẠ N