Preview text:

lOMoAR cPSD| 59908026

Bài 5. Các phương pháp vào ra lOMoAR cPSD| 59908026 Nội dung

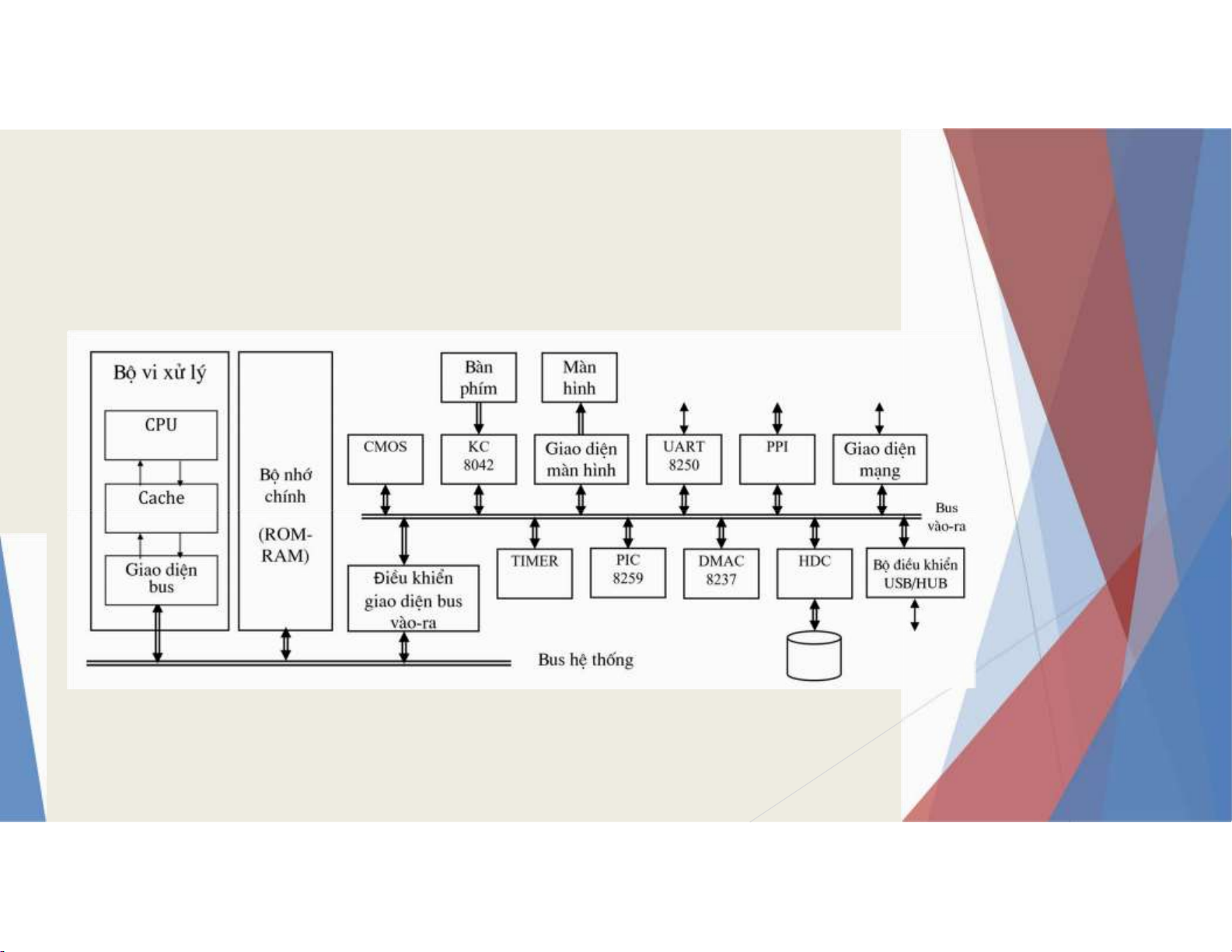

Phương pháp vào – ra dữ liệu Bộ iều khiển vào ra Kiến trúc máy vi tính PC

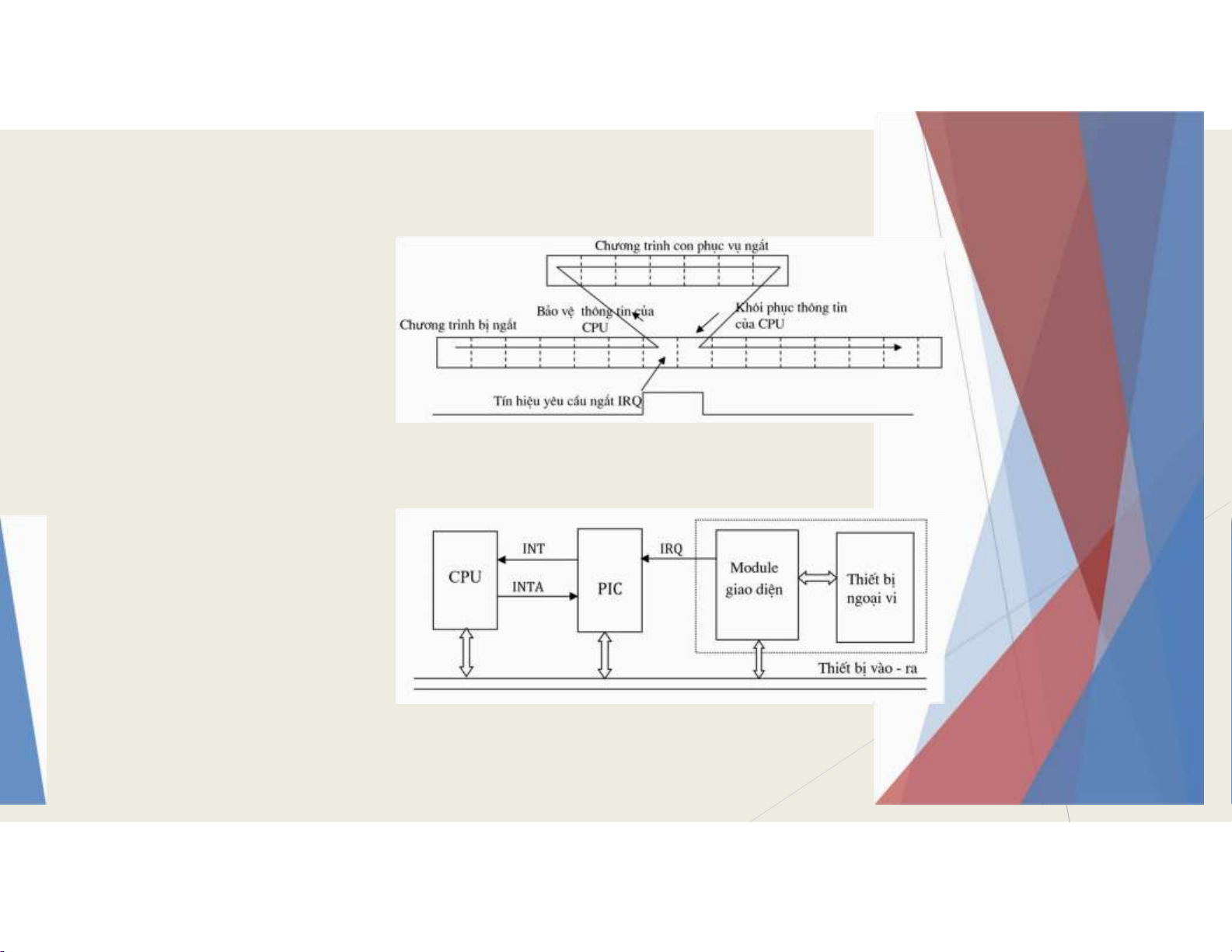

Tập lệnh trên máy vi tính PC lOMoAR cPSD| 59908026 Phương pháp vào-ra theo ngắt

• Cấu trúc của hệ thống vào

ra dữ liệu theo ngắt cứng

• Số ngắt-> Địa chỉ • Bảng véc tơ ngắt lOMoAR cPSD| 59908026

Phương pháp vào-ra theo ngắt

Quá trình phục vụ ngắt và vào/ra dữ liệu theo phương pháp ngắt cứng :

- CPU ang thực hiện chưương trình hiện hành.

- Thiết bị vào-ra có yêu cầu phục vụ phát ra tín hiệu IRQ cho PIC.

- Thiết bị PIC phát ra tín hiệu INT cho CPU, òi CPU phục vụ.

- CPU hoàn thành nốt lệnh ang thực hiện.

- CPU phát tín hiệu INTA (Interrupt Acknowledge) trả lời PIC, báo sẵn sàng phục vụ

quá trỡnh ngắt. Bit cờ IF trong thanh ghi trạng thái PSW ược ặt xuống 0 khi ngắt ược phục vụ.

Phương pháp vào-ra theo ngắt

Quá trình phục vụ ngắt và vào/ra dữ liệu theo phương pháp ngắt cứng : lOMoAR cPSD| 59908026

- CPU cất giữ nội dung con trỏ lệnh PC và nội dung thanh ghi trạng thái PSW vào

ngăn xếp ( ể còn khôi phục lại khi rời khỏi chưương trỡnh phục vụ ngắt ).

- PIC phát ra ịa chỉ (hoặc số ngắt ại diện cho ịa chỉ) của chưương trỡnh con phục vụ

ngắt tưương ứng với tín hiệu IRQ, cho CPU .

- Dựa trên ịa chỉ hoặc số ngắt này CPU nạp giá trị mới cho con trỏ lệnh PC và bắt ầu

thực hiện chưương trỡnh con phục vụ ngắt, thực hiện vào/ra dữ liệu với thiết bị vào-ra.

- Chưương trỡnh con phục vụ ngắt ưưîc kết thúc bằng lệnh IRET. Khi CPU nhập và

thực hiện lệnh IRET, CPU khôi phục lại nội dung con trỏ lệnh PC và thanh ghi trạng thái PSW.

Bằng cách ó CPU quay lại tiếp tục thực hiện chưương trỡnh bị ngắt. lOMoAR cPSD| 59908026

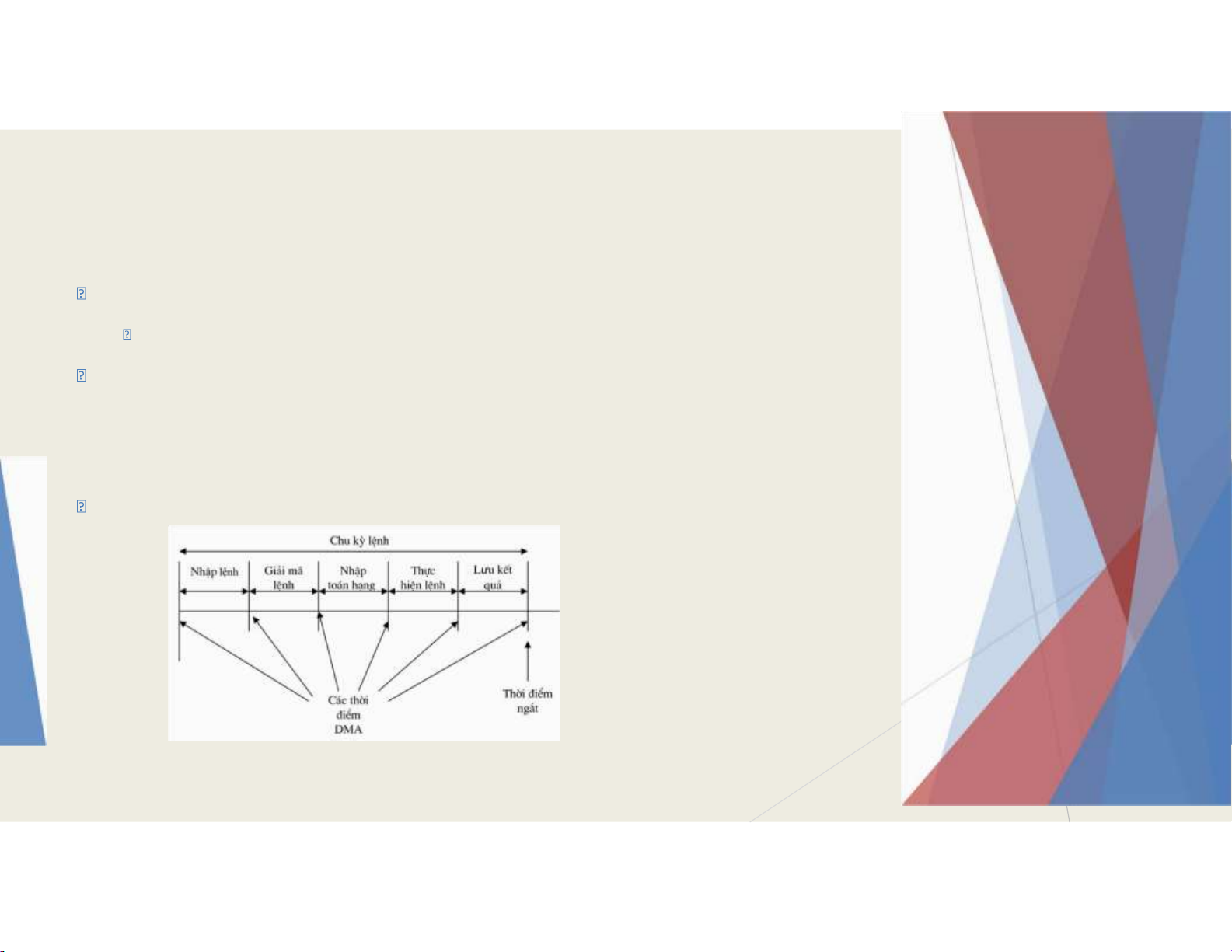

Phưương pháp vào-ra kiểu truy nhập trực tiếp bộ nhớ

Phương pháp DMA- Direct Memory Access

Quá trình vào/ra dữ liệu trực tiếp giữa bộ nhớ và thiết bị ngoại vi không qua CPU.

Trong quá trình DMA việc chuyển dữ liệu ưưîc iều khiển bởi một thiết bị phần cứng

là bộ iều khiển DMAC (Direct Memory Access Controller). Thiết bị DMAC thay thế

CPU óng vai trò chủ bus, iều khiển quá trỡnh chuyển dữ liệu trực tiếp giữa thiết bị

vào-ra và bộ nhớ chính qua bus hệ thống.

Những thời iểm CPU có thể trao quyền sử dụng bus cho DMAC trong một chu kỳ lệnh

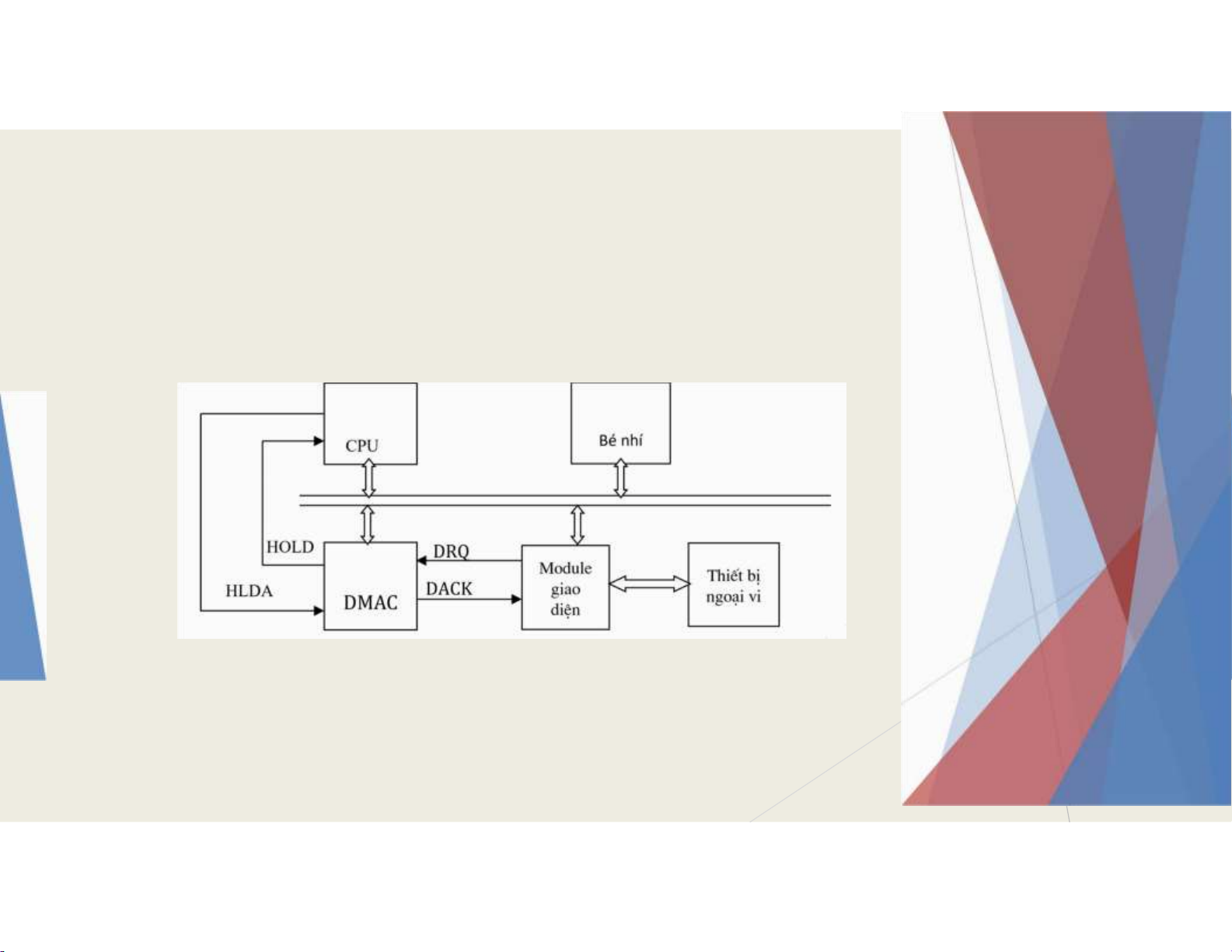

Cấu trúc hệ thống vào-ra dữ liệu theo kiểu lOMoAR cPSD| 59908026 DMA.

Quá trình DMA ưîc thực hiện nhưư sau : -

CPU thực hiện các lệnh vào-ra nạp các giá trị ban ầu cho hai thanh ghi AR và DC, ồng thời

xác ịnh hưướng truyền dữ liệu giữa bộ nhớ và thiết bị vào-ra cho DMAC. DMAC sẵn sàng

iều khiển truyền dữ liệu. -

Thiết bị vào-ra phát tín hiệu DRQ cho DMAC. -

DMAC phát tín hiệu HOLD = 1 cho CPU, òi CPU áp ứng. -

CPU thực hiện nốt chu kỳ máy. -

CPU phát tín hiệu HLDA trả lời cho DMAC và tự tách ra khỏi hệ thống bus. Quyền iều

khiển hệ thống bus thuộc về DMAC. -

DMAC phát tín hiệu DACK trả lời thiết bị yêu cầu, phát iạ chỉ ô nhớ lên bus ịa chỉ, phát

các tín hiệu iều khiển ghi/ọc thiết bị vào-ra và phát tín hiệu iều khiển ọc/ghi bộ nhớ, qua

ó iều khiển quá trỡnh chuyển dữ liệu trực tiếp giữa thiết bị vào-ra và bộ nhớ. Sau mỗi

từ dữ liệu ưưîc truyền, giá trị của AR tăng lên và giá trị của DC giảm i.

Cấu trúc hệ thống vào-ra dữ liệu theo kiểu lOMoAR cPSD| 59908026 DMA. -

Nếu DC còn chưưa giảm về 0 và thiết bị vào-ra chưa sẵn sàng gửi hoặc nhận dữ liệu tiếp theo,

DMAC trả lại quyền iều khiển bus cho CPU bằng cách ặt HOLD = 0. CPU nắm lại quyền iều khiển bus. -

Khi DC giảm về 0, DMAC kết thúc quá trỡnh DMA bằng việc phát tín hiệu HOLD = 0 cho CPU,

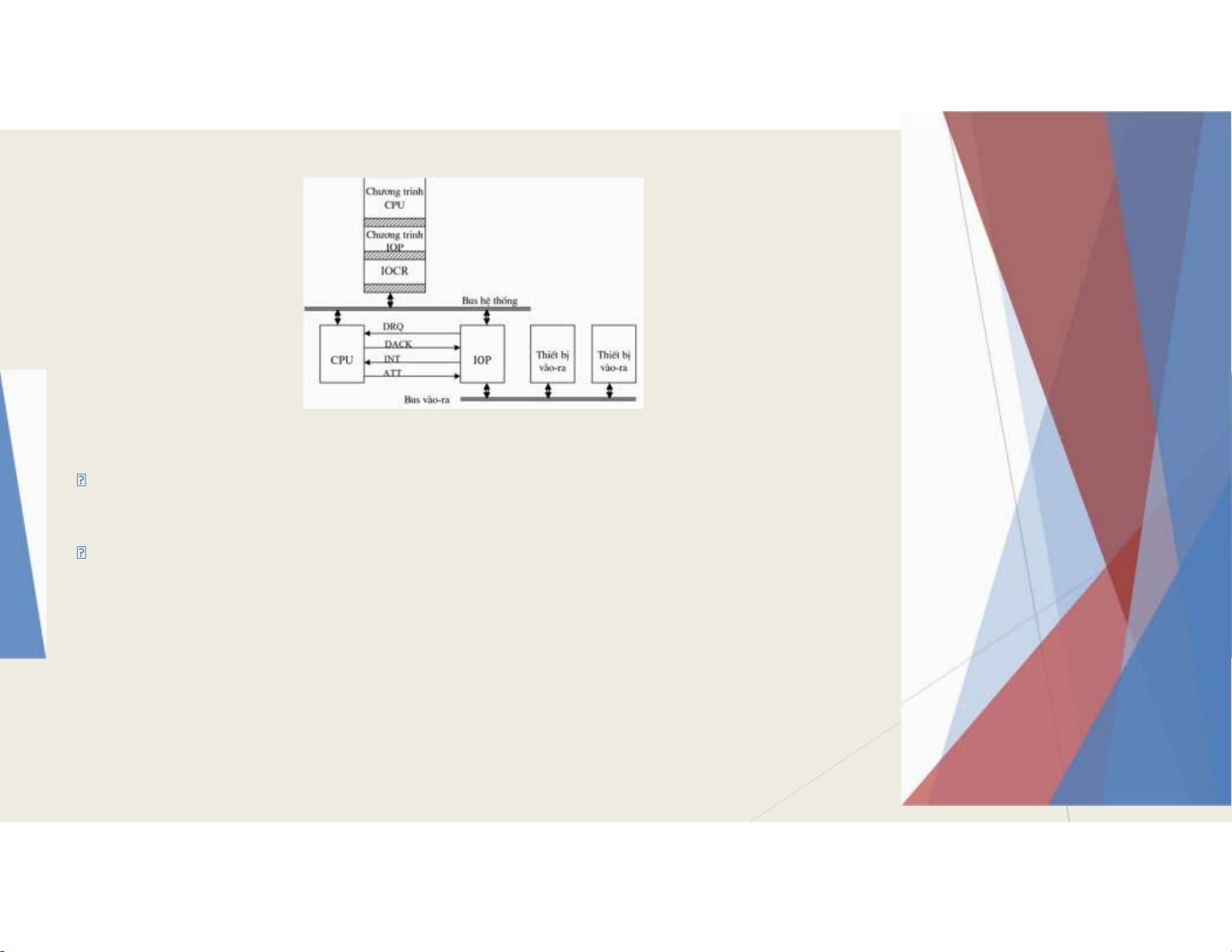

trả quyền iều khiển bus cho CPU. CPU nắm lại quyền iều khiển bus và tiếp tục làm việc bình thường. lOMoAR cPSD| 59908026 Bộ xử lý vào-ra

Bộ xử lý vào-ra IOP (Input-Output Processor) là một dạng mở rộng của các phưương

pháp iều khiển vào-ra dữ liệu.

Một phát triển logic tiếp theo của các phưương pháp iều khiển vào-ra là : module

giao diện trở thành bộ xử lý vào-ra với một tập các chỉ thị chuyên biệt cho iều khiển vào-ra dữ liệu.

CPU ra lệnh cho bộ xử lý vào-ra thực hiện chưương trỡnh iều khiển vào-ra.

Bộ xử lý vào-ra nhập và thực hiện lệnh của

chưương trỡnh iều khiển vào-ra, không cần ến sự can thiệp của CPU. CPU chỉ thực

hiện vài lệnh cho phép và kết thúc hoạt ộng của IOP. lOMoAR cPSD| 59908026

• Cấu trúc của hệ thống máy tính có IOP:

IOCR (Input Output Communication Region) : vựng nhớ truyền thụng, dựng ể

truyền thụng iệp giữa hai bộ xử lý.

(VD : ịa chỉ của chưương trỡnh iều khiển vào-ra cần thực hiện, ịa chỉ của thiết bị vàora ưược sử dụng CÂU HỎI CHƯƠNG 5

1)Tại sao khi thực hiện vào/ra (nhập/xuất) dữ liệu với các thiết bị ngoại vi của máy

tính phải áp dụng một trong các phương pháp vào-ra dữ liệu? lOMoAR cPSD| 59908026

2)Trong phương pháp vào-ra theo thăm dò, biện pháp nào ược sử dụng ể ơn vị xử lý

trung tâm bắt nhịp ược với hoạt ộng của thiết bị ngoại vi ?

3)Cơ chế ể ơn vị xử lý trung tâm bắt nhịp ược với hoạt ộng của thiết bị ngoại vi ở

phương pháp vào-ra theo ngắt cứng là gì ?

4) Điều kiện ể có thể thực hiện vào ra dữ liệu theo phương pháp ngắt cứng là gì ? lOMoAR cPSD| 59908026 Chương 6 Kiến

trúc máy vi tính PC và ơn vị xử lý trung tâm lOMoAR cPSD| 59908026 Kiến trúc máy vi tính PC lOMoAR cPSD| 59908026

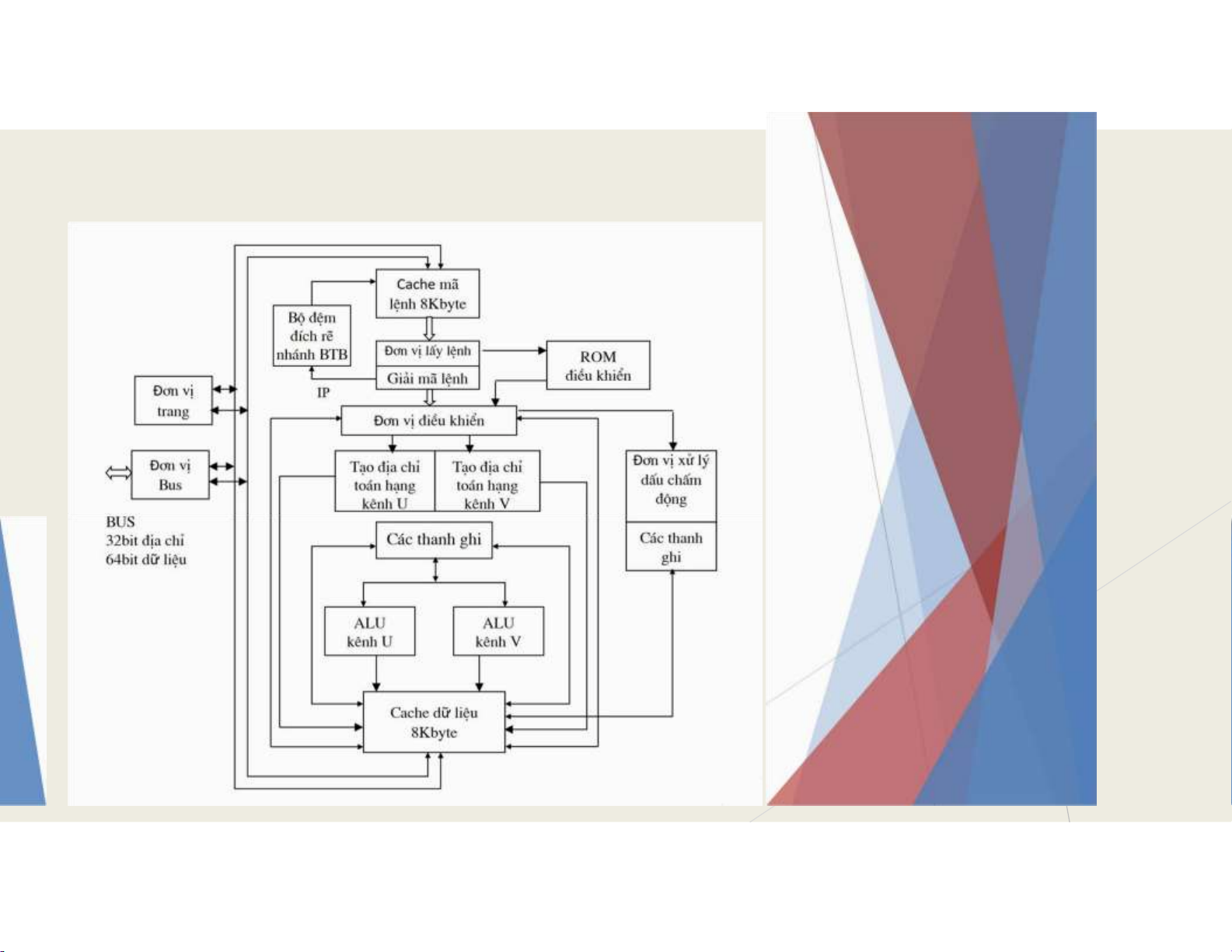

Đơn vị xử lý trung tâm Pentium lOMoAR cPSD| 59908026

Đơn vị xử lý trung tâm

Đường ống thực hiện lệnh của Pentium gồm 5 giai oạn :

1- Nhập lệnh. Lệnh ưưîc nhập từ cache và ưưa vào vùng ệm trưước giải mã.

2- Giải mã 1. Lệnh ưưîc giải mã ể tạo ra từ iều khiển. Từ iều khiển ơn giản sẽ gây ra

việc thực hiện trực tiếp lệnh. Từ iều khiển phức tạp sẽ ưưîc xử lý tiếp. Dự báo rẽ

nhánh cũng ưưîc thực hiện trong giai oạn này)

3- Giải mã 2. Từ iều khiển phức tạp ưîc giải mã tiếp ể tạo ra các vi mã thao tác (micro-

ops) dùng cho giai oạn thực thi lệnh (Địa chỉ toán hạng cũng ưưîc tạo ra ở giai oạn này.)

4- Thực thi lệnh. Lệnh ược thực thi ở ALU. (Nếu cần, cache dữ liệu cũng ược truy nhập ở giai oạn này.)

5- Ghi kết quả. Kết quả tính toán ược ghi trở lại vào các thanh ghi CPU lOMoAR cPSD| 59908026

Đơn vị xử lý trung tâm

• Điều kiện cơ bản ể thực hiện ồng thời hai lệnh trong Pentium là cả hai lệnh phải là loại ơn giản.

• Các lệnh ơn giản là các lệnh: chuyển dữ liệu tức thời từ thanh ghi hoặc từ bộ nhớ

tới thanh ghi, chuyển giá trị tức thời từ thanh ghi tới bộ nhớ, lệnh số học nguyên,

lệnh tăng giảm, lệnh bảo vệ và khôi phục thanh ghi từ ngăn xếp, lệnh nhảy không

iều kiện và nhảy gần có iều kiện, lệnh gọi chưương trình con, lệnh lấy ịa chỉ hiệu dụng v.v.

• Với các lệnh dấu chấm ộng, hai giai oạn ầu tiên nhập và giải mã lệnh ưîc thực hiện

trên kênh U, sau ó ược chuyển sang FPU. Không lệnh dấu chấm ộng nào ược thực hiện song song. lOMoAR cPSD| 59908026

Đơn vị xử lý trung tâm

• Quá trình xử lý song song mức lệnh thể hiện qua thuật toán sau :

Giải mã ồng thời hai lệnh I1 và I2 lOMoAR cPSD| 59908026

Nếu những iều sau úng :

I1 và I2 là các lệnh ơn giản

I1 không phải là lệnh nhảy

Đích của I1 không phải là nguồn của I2

Đích của I1 không phải là ích của I2 thì ưa I1 vào kênh U và I2 vào kênh V

Các trưường hợp khác thỡ ưưa I1 vào kênh U

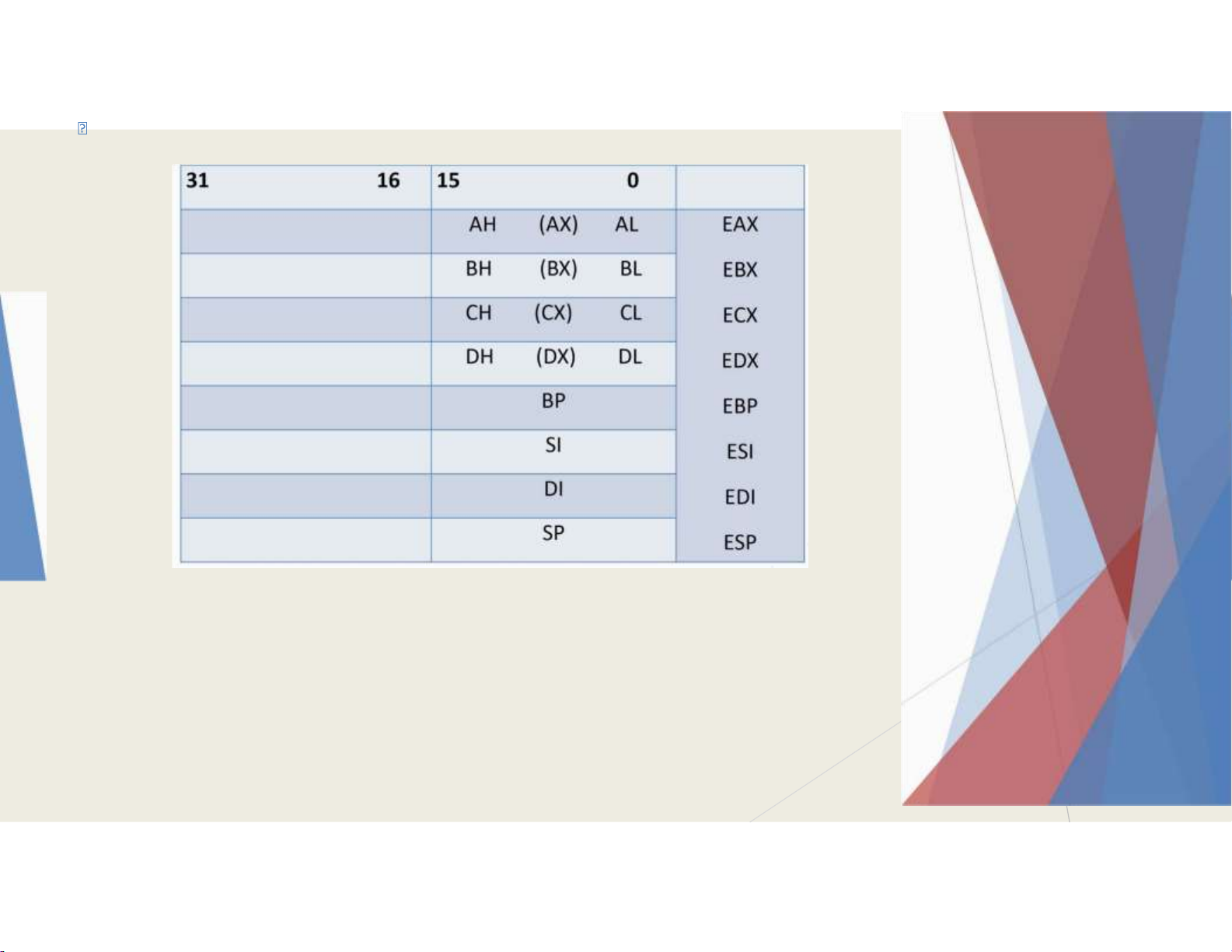

Tập các thanh ghi cơ bản lOMoAR cPSD| 59908026

Các thanh ghi a năng EAX, EBX, ECX, EDX , EBP, ESI, EDI, ESP lOMoAR cPSD| 59908026

• Con trỏ lệnh EIP (Instruction Pointer). EIP là một thanh ghi 32 bit. EIP chứa ịa chỉ offset

của ô nhớ chứa lệnh tiếp theo trong oạn mã lệnh.

• Thanh ghi cờ trạng thái EFLAGS. EFLAGS là thanh ghi 32 bit. Thanh ghi trạng thái EFLAGS

chứa các bit mang thông tin phản ảnh trạng thái của bộ xử lý và một số bit iều khiển.

• Các thanh ghi iều khiển 32 bit CR0, CR1, CR2, CR3, CR4

CR0 iều khiển và chỉ thị hệ thống (VD : bit PE-Protect Enable,

bit PG-Paging Enable, bit TS-Task chuyển nhiệm vụ)

CR1: chưa sử dụng , CR2 ghi nhớ ịa chỉ trang vật lý chưa ược nạp, CR3 là thanh ghi nền thư

mục trang PDR, CR4 cho phộp mở rộng kiến trỳc của CPU (mở rộng trang ến 4 Mb)

Các thanh ghi quản lý bộ nhớ GDTR, LDTR, TR, IDTR