Report tài liệu

Chia sẻ tài liệu

Thiết kế mạch giải mã và địa chỉ kết nối dữ liệu cho hệ thống môn Kỹ thuật lập trình mạng | Đại học Bách Khoa, Đại học Đà Nẵng

Thiết kế mạch giải mã và địa chỉ kết nối dữ liệu cho hệ thống môn Kỹ thuật lập trình mạng | Đại học Bách Khoa, Đại học Đà Nẵng giúp sinh viên tham khảo, ôn luyện và phục vụ nhu cầu học tập của mình cụ thể là có định hướng, ôn tập, nắm vững kiến thức môn học và làm bài tốt trong những bài kiểm tra, bài tiểu luận, bài tập kết thúc học phần, từ đó học tập tốt và có kết quả cao cũng như có thể vận dụng tốt những kiến thức mình đã học

Môn: Kỹ thuật lập trình(KTLT) 35 tài liệu

Trường: Trường Đại học Bách khoa, Đại học Đà Nẵng 1.7 K tài liệu

Tác giả:

Tài liệu khác của Trường Đại học Bách khoa, Đại học Đà Nẵng

Preview text:

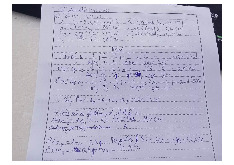

1. Thi t k m ch gi i m đ a ch và k t nối dữ liệu cho hệ thống (8-bit đ a ch

A0; 8-bit dữ liệu D7-D0; RD, WR trên 2 chân riêng biệt) k t nối với các module

bên dưới. Ghi rõ k t nối chân CS, WR, RD tới các module và đ a ch bắt đầu, đ a

ch k t thúc của các module (không gi i m đ a ch các kênh):

1/ Module 1: 8 kênh ADC 16-bit

4/ Module 4: 4 kênh Digital Input 8-bit

2/ Module 2: 16 kênh Encoder 32-bit 5/ Module 5: 2 kênh Digital Output 8-bit

3/ Module 3: 16 kênh PWM 10-bit

2. Vi t hàm xuất giá tr ra kênh PWM theo cấu trúc như sau:

void pwm (int channel, int pwm_value); - Trong đó

channel: thứ tự kênh có giá tr từ 1-16

pwm_value: giá tr điều rộng có giá tr từ 0-1000

Tài liệu liên quan:

-

Thiết kế hệ thống sấy thóc quy mô hộ gia đình năng suất 1tấn/mẻ sử dụng môn Kỹ thuật lập trình | Trường Đại học Bách Khoa, Đại học Đà Nẵng

34 17 -

Bài tập môn Kỹ thuật lập trình | Trường Đại học Bách Khoa, Đại học Đà Nẵng

34 17 -

Lab15 Owasp Zap để kiểm thử bảo mật cho Web Application và API Tài liệu ôn thi Vstep Speaking | Đại học Bách Khoa, Đại học Đà Nẵng

523 262 -

Bài tập: Viết ứng dụng quản lý có menu thực hiện các phương thức trong lớp List môn Kỹ thuật máy tính | Đại học Bách Khoa, Đại học Đà Nẵng

294 147