Preview text:

lOMoAR cPSD| 59908026

PHIẾU GHI KẾT QUẢ QUAN SÁT

BÀI THỰC HÀNH SỐ 2

Họ và tên sinh viên: Đào Thành Hả Lớp: 64CNTT1

LAB 2.1: KIỂM TRA TÍNH CỤC BỘ (LÂN CẬN) CỦA CÁC CHƯƠNG TRÌNH KHÁC NHAU

1. Thực hiện: Cấu hình một hệ thống với các đặc tính kiến trúc như sau:

- Số lượng bộ xử lý - Processors in SMP = 1.

- Giao thức liên kết cache - Cache coherence protocol = MESI.

- Phương pháp phân xử Bus - Scheme for bus arbitration = Random.

- Kích thước word - Word wide (bits) = 16.

- Số word trong một block - Words by block = 16 (block size = 32 bytes).

- Số block trong bộ nhớ chính - Blocks in main memory = 8192. Kích thước bộ nhớ

chính bằng bao nhiêu? - Số blocks trong cache – Blocks in cache: 32 - Ánh

xạ - Mapping = Fully-Associative.

- Chính sách thay thế - Replacement policy = LRU

2. Quan sát miss rate (tỷ lệ truy xuất cache không thành công) với các memory traces:

Hydro, Nasa7, Cexp, Mdljd, Ear, Comp, Wave, Swm và Ucomp và ghi vào file MS Excel: Memory Traces Miss Rate Hydro 18.195 % Nasa7 17.035 % Cexp 0.77 % Ear 16.993 % Comp 18.661 % Swm 21.985 % 1 lOMoAR cPSD| 59908026 Ucomp 17.892 % 3. Phân tích kết quả:

- Theo kết quả khảo sát được, trả lời các câu hỏi sau:

1) Liệu các chương trình có cùng mức độ cục bộ? Chương trình nào có tính

cục bộ tốt nhất? Chương trình nào có tính cục bộ kém nhất?

Các chương trình không có cùng mức độ cục bộ

• Cexp có mức độ cục bộ tốt nhất

• Swm có mức độ cục bộ kém nhất

2) Liệu cấu hình trên có khai thác được tính cục bộ của các chương trình

này và tăng hiệu suất hệ thống không? Tại sao?

• Cấu hình trên đã khai thác được mức độ cục bộ của các chương trình, tuy

nhiêu hiệu suất chưa cao (miss rate > 10% với hầu hết các chương trình)

3) Trong quá trình chương trình thực hiện, nếu quan sát dưới dạng đồ thị, tỷ

lệ miss rate giảm dần, nguyên nhân tại sao?

Trong quá trình một chương trình chạy, miss rate sẽ giảm dần vì:

• Khi bắt đầu chạy chương trình, bộ nhớ cache chưa có dữ liệu. Các

truy xuất bộ nhớ của CPU phải truy xuất đến RAM (cache miss) - > Miss rate lớn

• Sau khi các khối được ánh xạ nhiều trong bộ nhớ Do tính cục

bộ của chương trình, các câu lệnh và dữ liệu có thể được truy xuất

trực tiếp từ Cache (cache hit) -> Miss rate giảm dần.

LAB 2.2: ẢNH HƯỞNG CỦA KÍCH THƯỚC CACHE ĐẾN HIỆU SUẤT HỆ THỐNG

Nhiệm vụ của sinh viên:

1. Thiết lập cấu hình của hệ thống với các đặc tính kiến trúc sau:

- Số lượng bộ xử lý - Processors in SMP = 1.

- Giao thức liên kết cache - Cache coherence protocol = MESI.

- Phương pháp phân xử Bus - Scheme for bus arbitration = Random. 2 lOMoAR cPSD| 59908026

- Kích thước word - Word wide (bits) = 16.

- Số word trong một block - Words by block = 16 (block size = 32 bytes).

- Số block trong bộ nhớ chính - Blocks in main memory = 8192. Kích thước bộ nhớ chính bằng bao nhiêu?

- Ánh xạ - Mapping = Fully-Associative.

- Chính sách thay thế - Replacement policy = LRU.

- Thiết lập cache với kích thước như sau (số block trong cache): 1, 2, 4, 8, 16, 32 , 64, 128, 256 và 512.

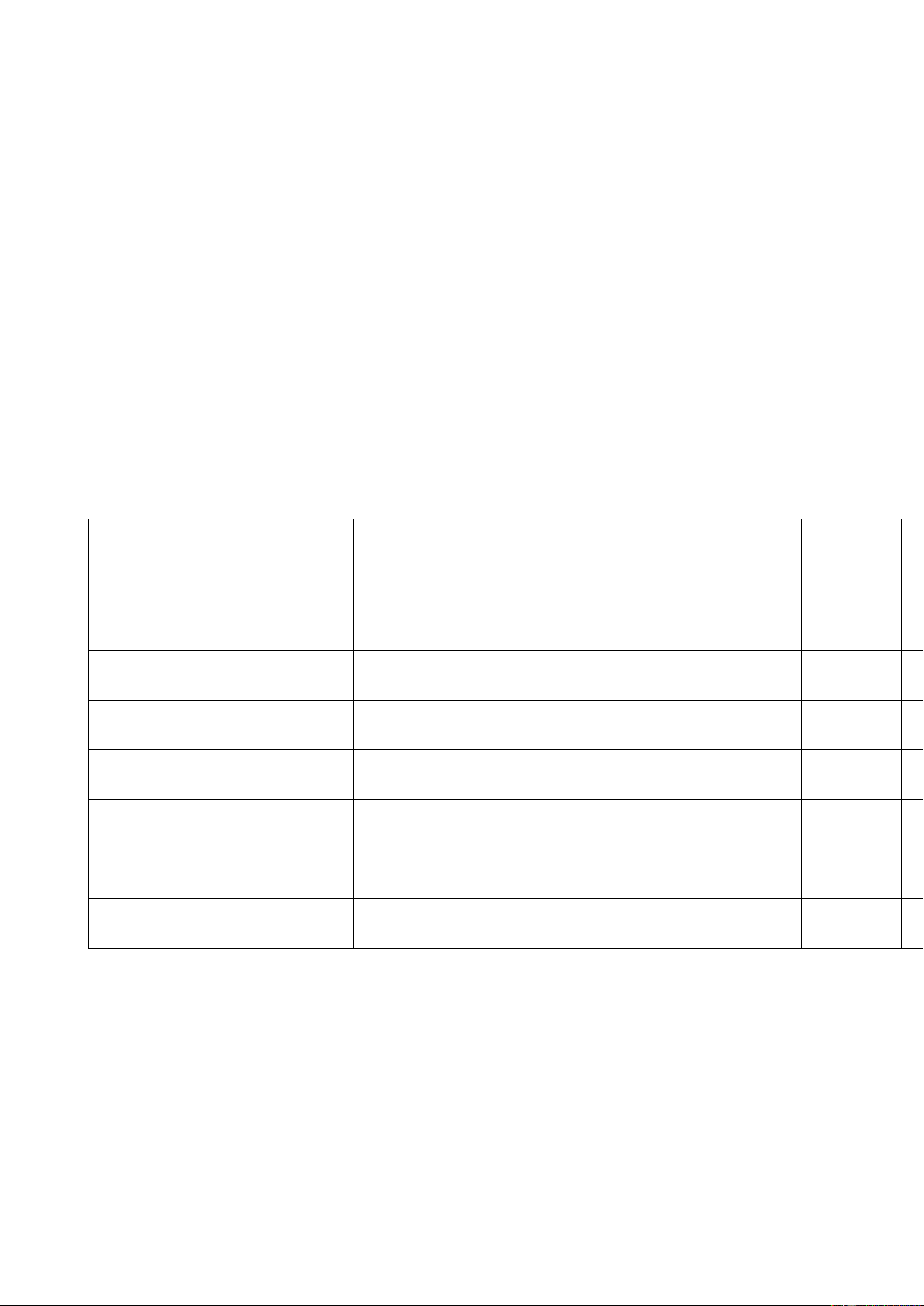

2. Với mỗi thông số trên, thiết lập các memory traces: Hydro, Nasa7, Cexp, Mdljd, Ear, Comp,

Wave, Swm và Ucomp, chạy mô phỏng và ghi lại các miss rate ra file MS Excel: U Cache Hydro Nasa7 Cexp Mdljd Ear Comp Wave Swm size 1 66.197% 66.577% 52.920% 63.055% 59.947% 65.689% 66.355% 60.108% 2 42.360% 41.024% 43.900% 42.565% 42.144% 37.797% 42.136% 41.380% 4 32.111% 29.650% 43.145% 29.820% 37.622% 25.396% 31.293% 30.835% 8 28.068% 25.822% 40.065% 21.575% 27.769% 23.257% 29.093% 26.085% 16 25.012% 23.235% 1.540% 19.715% 18.218% 21.355% 26.875% 23.875% 32 18.195% 17.035% 0.770% 17.885% 16.933% 18.661% 21.564% 21.985% 64 15.468% 16.065% 0.745% 16.040% 15.674% 18.185% 18.354% 20.815% 6 3 2 2 2 1 3 lOMoAR cPSD| 59908026 128 14.810% 15.364% 0.740% 14.780% 10.098% 17.908% 17.479% 19.630% 256 14.386% 14.987% 0.740% 13.235% 6.707% 17.908% 16.808% 18.285% 512 14.386% 14.987% 0.740% 11.225% 6.707% 17.274% 15.320% 16.060% 1 1 1 1 3. Phân tích kết quả:

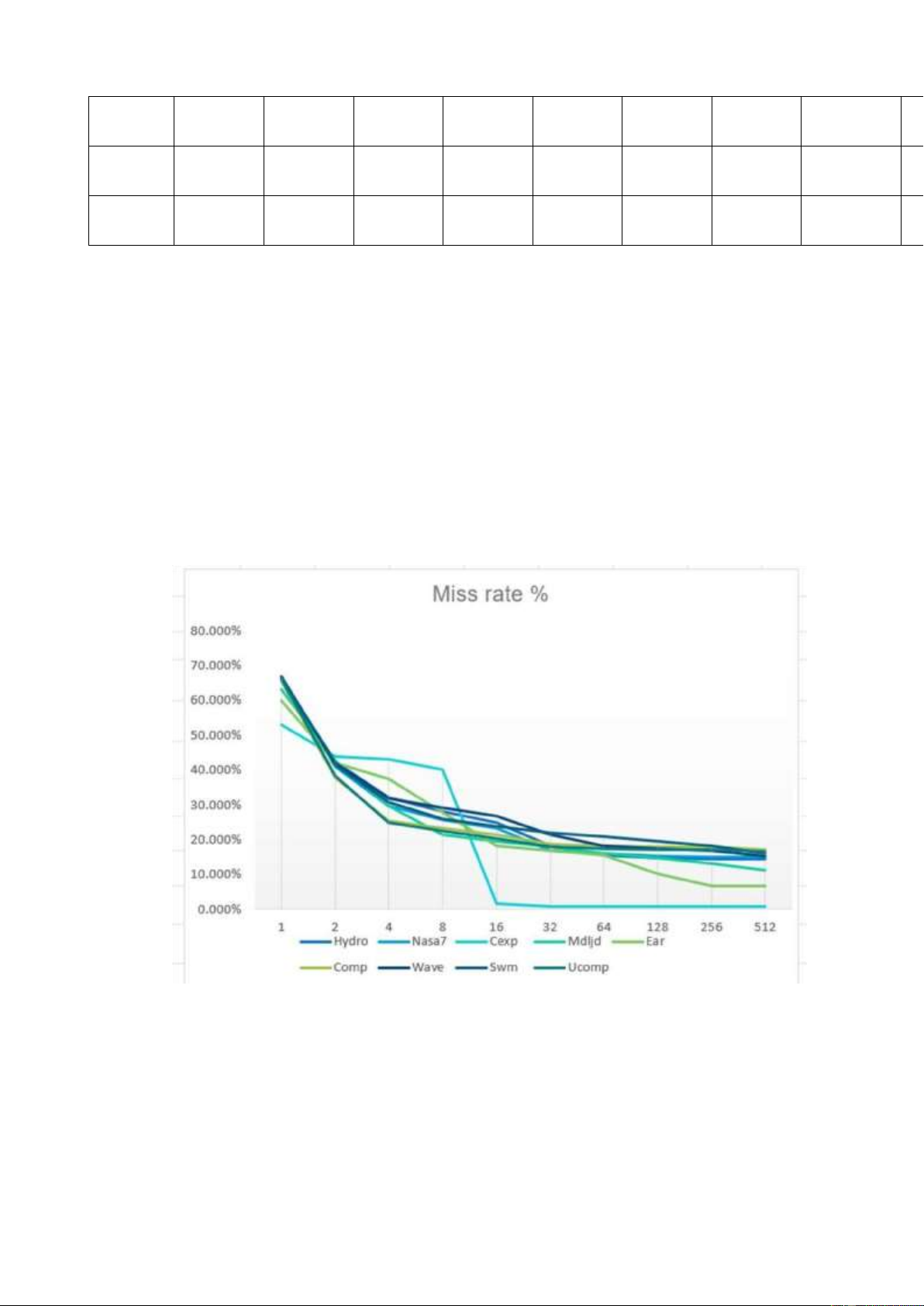

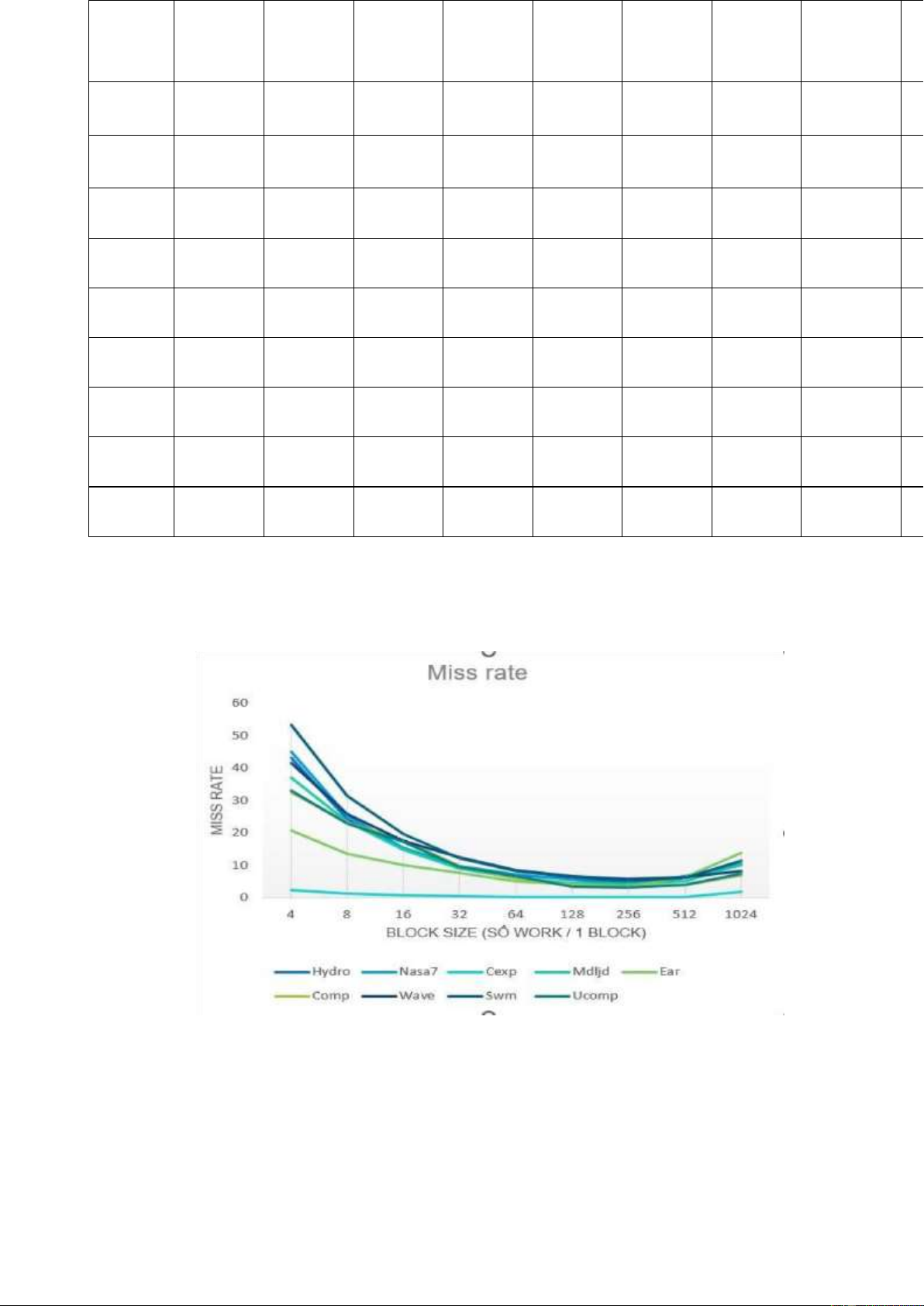

- Vẽ các biểu đồ tương ứng từ file Excel. Ví dụ biểu đồ:

- Phân tích và đánh giá kết quả theo các câu hỏi sau:

o Miss rate như thế nào khi kích thước cache tăng? Giải thích. –

Miss rate sẽ giảm khi kích thước cache tang vì:

• Kích thước cache lớn hơn có thể chứa nhiều dữ liệu hơn, làm

giảm tỉ lệ truy cập vào bộ nhớ chính, từ đó giảm khả năng xảy 4 lOMoAR cPSD| 59908026

ra misses do không đủ dung lượng để lưu trữ dữ liệu khi cần thiết.

o Liệu việc tăng kích thước cache có giúp cải thiện hiệu suất của hệ thống không?

Tăng kích thước cache cải thiện hiệu suất hệ thống trong một số

trường hợp, hưng cũng cần xem xét để đảm bảo việc tăng kích thước cache có lợi:

• Ưu điểm: Giảm miss rate, Cải thiện thời gian truy cập, …

• Nhược điểm: Chi phí chế tạo và duy trì cao hơn, Độ

trễ tăng lên, khả năng dặt cache trên chip. 5 lOMoAR cPSD| 59908026

LAB 2.3: ẢNH HƯỞNG CỦA KÍCH THƯỚC BLOCK ĐẾN HIỆU SUẤT HỆ THỐNG

Nhiệm vụ của sinh viên:

1. Thiết lập cấu hình của hệ thống với các đặc tính kiến trúc sau:

- Số lượng bộ xử lý - Processors in SMP = 1.

- Giao thức liên kết cache - Cache coherence protocol = MESI.

- Phương pháp phân xử Bus - Scheme for bus arbitration = Random.

- Kích thước word - Word wide (bits) = 16.

- Kích thước bộ nhớ RAM = 256 KB (số lượng block trong bộ nhớ sẽ thay đổi)

- Kích thước cache = 4 KB (số line –block trong cace thay đổi) - Ánh xạ - Mapping = Fully-Associative.

- Chính sách thay thế - Replacement policy = LRU.

- Cấu hình kích thước Block (số word/1 block) như sau: 4, 8, 16, 32, 64, 128, 256 , 512, 1024.

2. Với mỗi cấu hình trên, thiết lập các memory traces: Hydro, Nasa7, Cexp, Mdljd, Ear, Comp,

Wave, Swm và Ucomp, chạy mô phỏng và ghi lại các miss rate ra file MS Excel: U 3 2 1 6 3 3 3 6 lOMoAR cPSD| 59908026 Block Hydro Nasa7 Cexp Mdljd Ear Comp Wave Swm size 4 43.112% 44.96% 2.435% 37.005% 20.836% 32.448% 41.436% 53.245% 8 24.307% 25.391% 1.305% 23.285% 13.583% 23.098% 25.883% 31.405% 16 14.81% 15.364% 0.74% 14.78% 10.098% 17.098% 17.479% 19.63% 32 9.403% 9.757% 0.455% 9.075% 7.649% 9.905% 12.606% 12.115 % 64 6.958% 7.062% 0.295% 6.005% 5.124% 5.903% 8.433% 8.13% 128 5.689% 5.499% 0.215% 4.595% 4.107% 3.566% 6.624% 6.215% 256 4.607% 3.881% 0.15% 4.18% 3.429% 3.288% 5.69% 5.27% 512 6.723% 5.984% 0.185% 5.065% 6.274% 4.041% 6.449% 6.045% 7 1024 10.625% 10.081% 1.78% 10.31% 13.922% 6.933% 8.2% 11.495% 3. Phân tích kết quả:

- Vẽ các biểu đồ tương ứng từ file Excel. Ví dụ biểu đồ:

- Phân tích và đánh giá kết quả theo các câu hỏi sau:

o Khi kích thước block tăng thì miss rate tăng hay giảm? Tại sao?

Kích thước block tăng thí miss rate có thể tăng hoặc giảm: 7 lOMoAR cPSD| 59908026

- Miss rate có thể giảm do cache có thể lưu trữ nhiều dữ liệu liên quan đến một lần truy cập

- Miss rate có thể tăng do kích thước block lớn có thể dẫn đến các

xung dột khi nhiều phần của chương trình truy cập cùng một block

- Miss rate có thể tăng do mỗi block chỉ chứa một lượng nhỏ dữ liệu

mới làm tăng khả năng xảy ra lỗi không đủ dung lượng khi cache

không đủ lưu trữ toàn bộ block

o Kích thước Block nào cho hiệu suất hệ thống cao nhất đối với cả các chương trình?

- Theo bảng trên thì khi kích thước block là 256 sẽ cho hệ thống có

hiệu suất cao nhất đối với các chương trình. 8