Preview text:

lOMoAR cPSD| 59703641

TRƯỜNG ĐẠI HỌC BÁCH KHOA HÀ NỘI

VIỆN ĐIỆN TỬ VIỄN THÔNG BÀI TẬP LỚN MÔN THIẾT KẾ VLSI

ĐỀ TÀI: THIẾT KẾ ĐỒNG HỒ SỐ

Giảng viên hướng dẫn : Ts Nguyễn Vũ Thắng

Nhóm sinh viên thực hiện:

Nguyễn Văn Thoan - 20092602 - ĐTVT06

Nguyễn Hà Giang - 20090860 - ĐTVT11

Phùng Mạnh Hưng - 20093902 -ĐTVT12 Nguyễn Xuân Thắng Hà Nội 3/2013 MỤC LỤC

MỤC LỤC..................................................3 A.

MÔ TẢ CHI TIẾT THIẾT KẾ.........................................................3

2.3 Sơ đồ nối dây bên trong.........................................................................5

2.4 Mô tả chức năng từng khối....................................................................6 B.

PHẦN MỀM SYNOPSYS................................................................13

6. ICC.........................................................................................................................................41

......................................................................................55

KẾT LUẬN....................................................................................................55

TÀI LIỆU THAM KHẢO............................................................................56

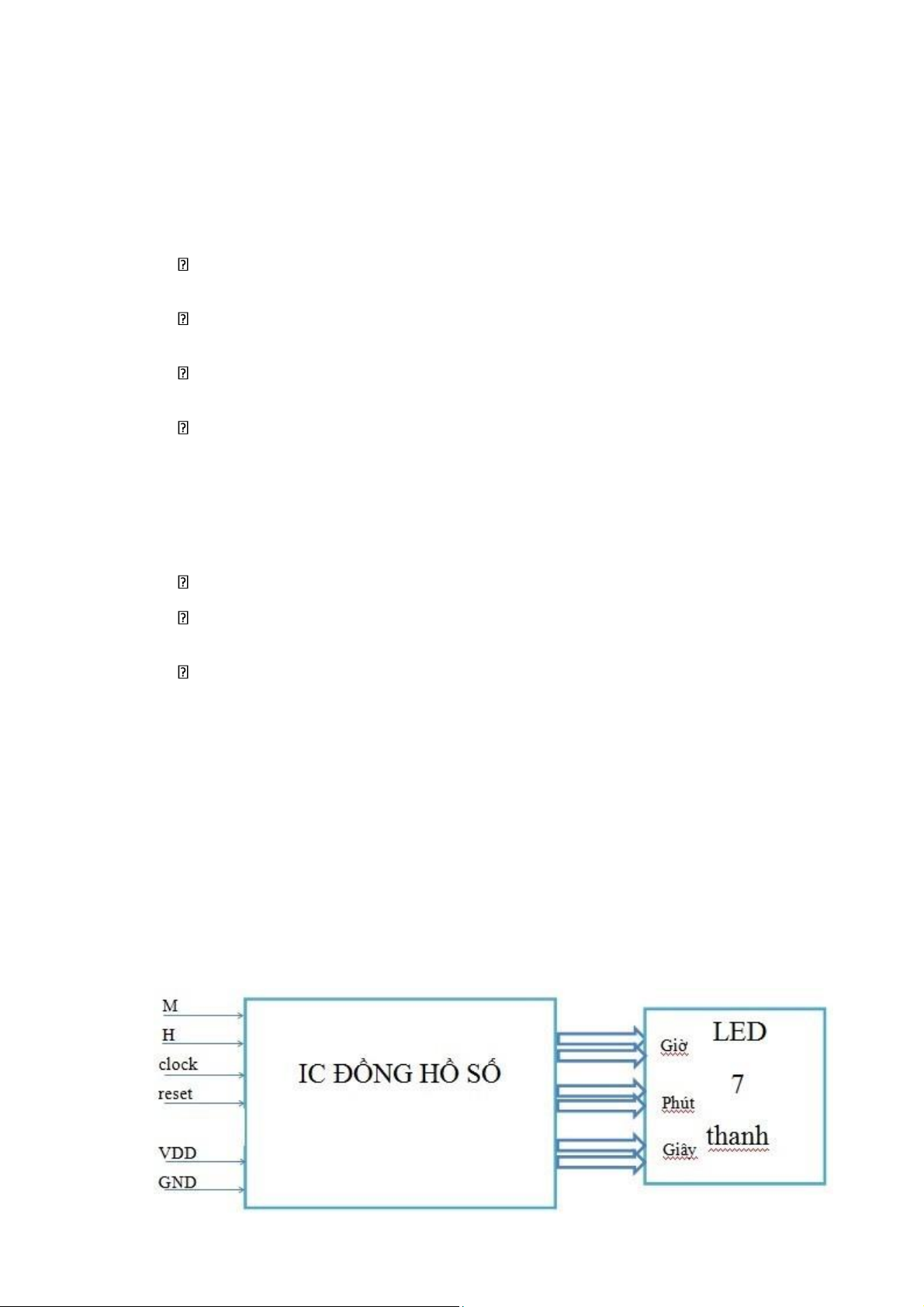

A. MÔ TẢ CHI TIẾT THIẾT KẾ 1. Tổng quan 1.1. Yêu cầu chức năng

IC đồng hồ số có chức năng đếm từ 00:00:00 đến 23:59:59

Có hai nút bấm (M,H) điều chỉnh giờ, phút, giây.

Đầu ra hiển thị trực tiếp lên led 7 thanh

Có chân reset không đồng bộ, chân enable đồng bộ

1.2. Yêu cầu phi chức năng

Mô tả thiết kế sử dụng ngôn ngữ Verilog

Tổng hợp thiết kế, mô phỏng và layout sử dụng phần mềm synopsys

Hoàn thiện thiết kế trong thời gian 8 tuần

2. Sơ đồ khối

2.1. Sơ đồ khối tổng quát Tên chân Chức năng Clock

Cấp tín hiệu xung clock cho IC Reset

Reset đồng hồ về trạng thái khởi tạo ban đầu Output

Các tín hiệu đầu ra để đưa đến led 7 thanh VDD,GND

Chân cấp nguồn cho IC hoạt động H,M

Điều chỉnh thời gian giờ, phút, giây

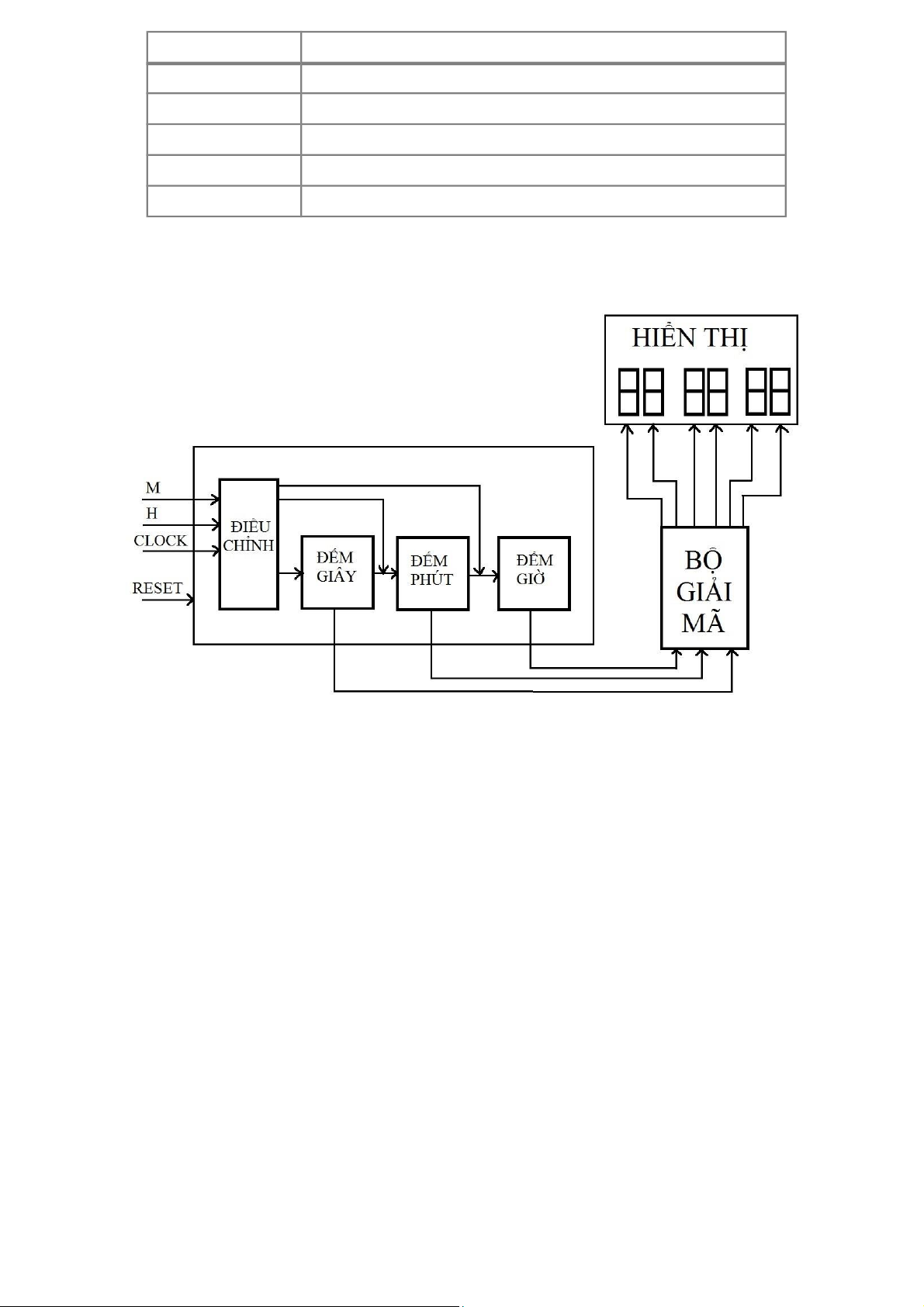

2.2 Sơ đồ khối chi tiết

2.3 Sơ đồ nối dây bên trong

2.4 Mô tả chức năng từng khối

Bộ điều chỉnh: có nhiệm vụ điều chỉnh giờ, phút, giây

Bộ đếm: có nhiệm vụ đếm thời gian, đầu ra đưa vào bộ giải mã

Bộ giải mã: Giải mã tín hiệu ra của bộ đếm để đưa ra hiển thị trên led 7 thanh.

LED 7 thanh : Hiển thị giá trị giờ, phút, giây.

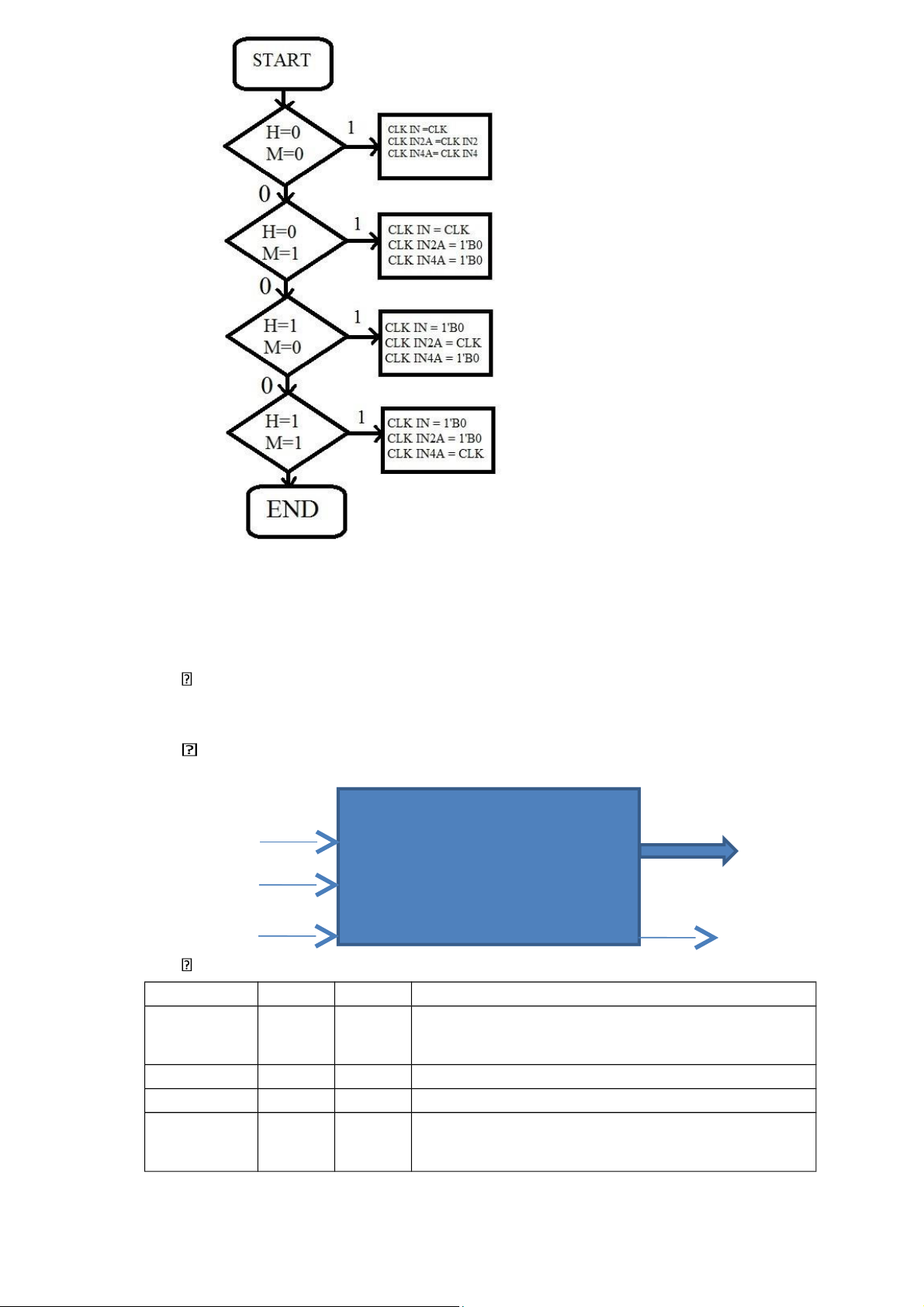

3. Thiết kế chi tiết từng khối 3.1 Khối điều chỉnh

Khối điều chỉnh có nhiệm vụ điều chỉnh thời gian,có 2 nút bấm M và H để điều chỉnh.

• M = 0 và H = 0 các bộ đếm giờ, phút, giây hoạt động bình thường theo

xung clock.(Couter giây hoạt động theo clock ngoài, counter phút hoạt

động theo clock_out của counter giây, counter giờ hoạt động theo clock_out của counter phút).

• M = 0 và H = 1 lúc đó đếm giây sẽ tự tăng theo xung clock còn phút và giờ

không thay đổi ( lúc này chân clock vào của counter đơn vị phút và giờ

bằng 0. Clock_in của giây bằng với clock ngoài 1 giây tăng 1 đơn vị)

• M = 1 và H = 0 lúc đó đếm phút sẽ tự tăng theo xung clock còn giây và giờ

không thay đổi (lúc này chân clock vào của counter đơn vị giây và giờ bằng

0. Clock_in của counter phút bằng với clock ngoài 1 giây tăng 1 đơn vị)

• M = 1 và H =1 lúc đó đếm giờ sẽ tự tăng theo xung clock còn giây và phút

không thay đổi.( lúc này chân clock vào của counter đơn vị giây và phút

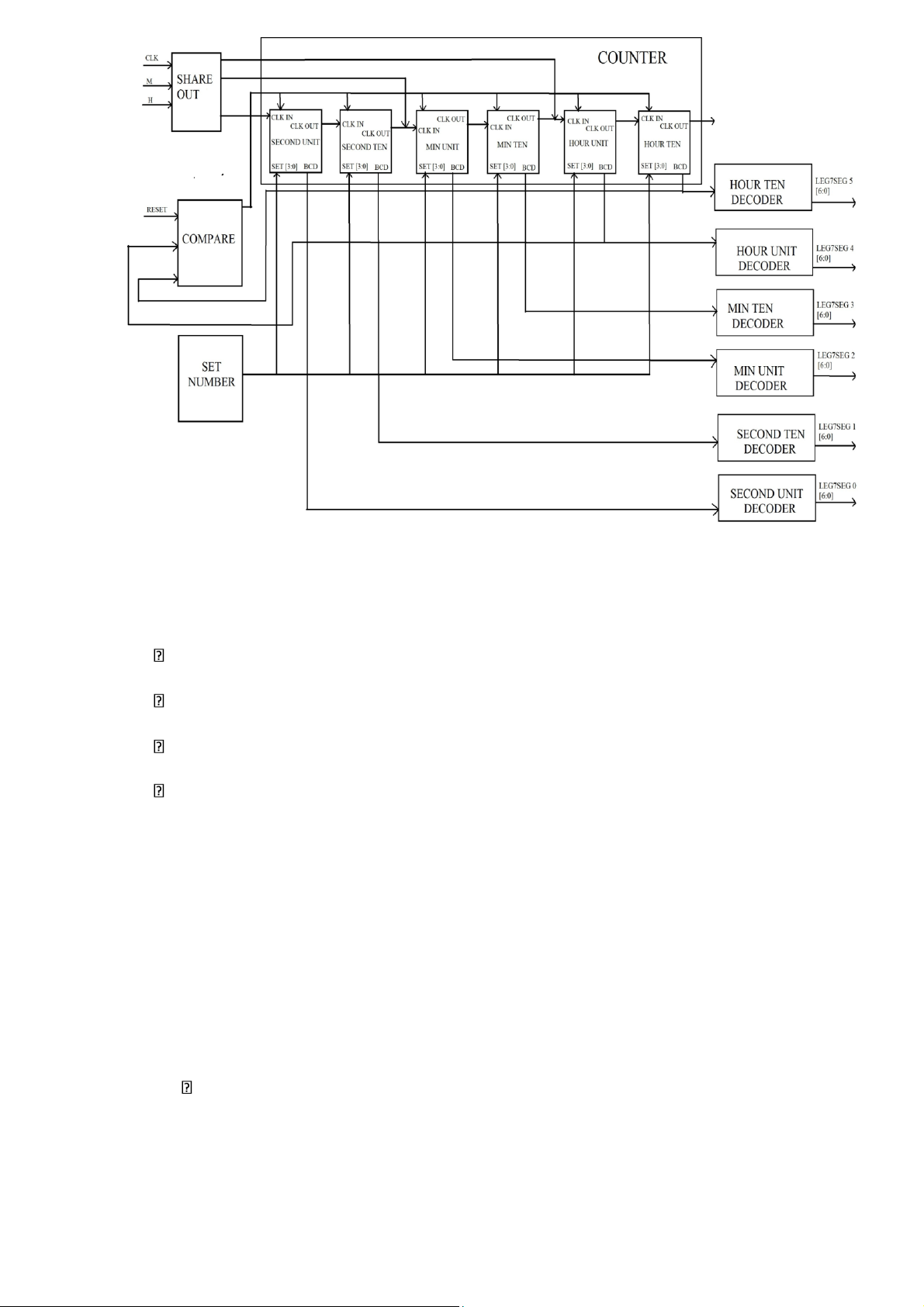

bằng 0. Clock_in của giờ bằng với clock ngoài 1 giây tăng 1 đơn vị. ) Sơ đồ thuật toán 3.2 Khối Counter

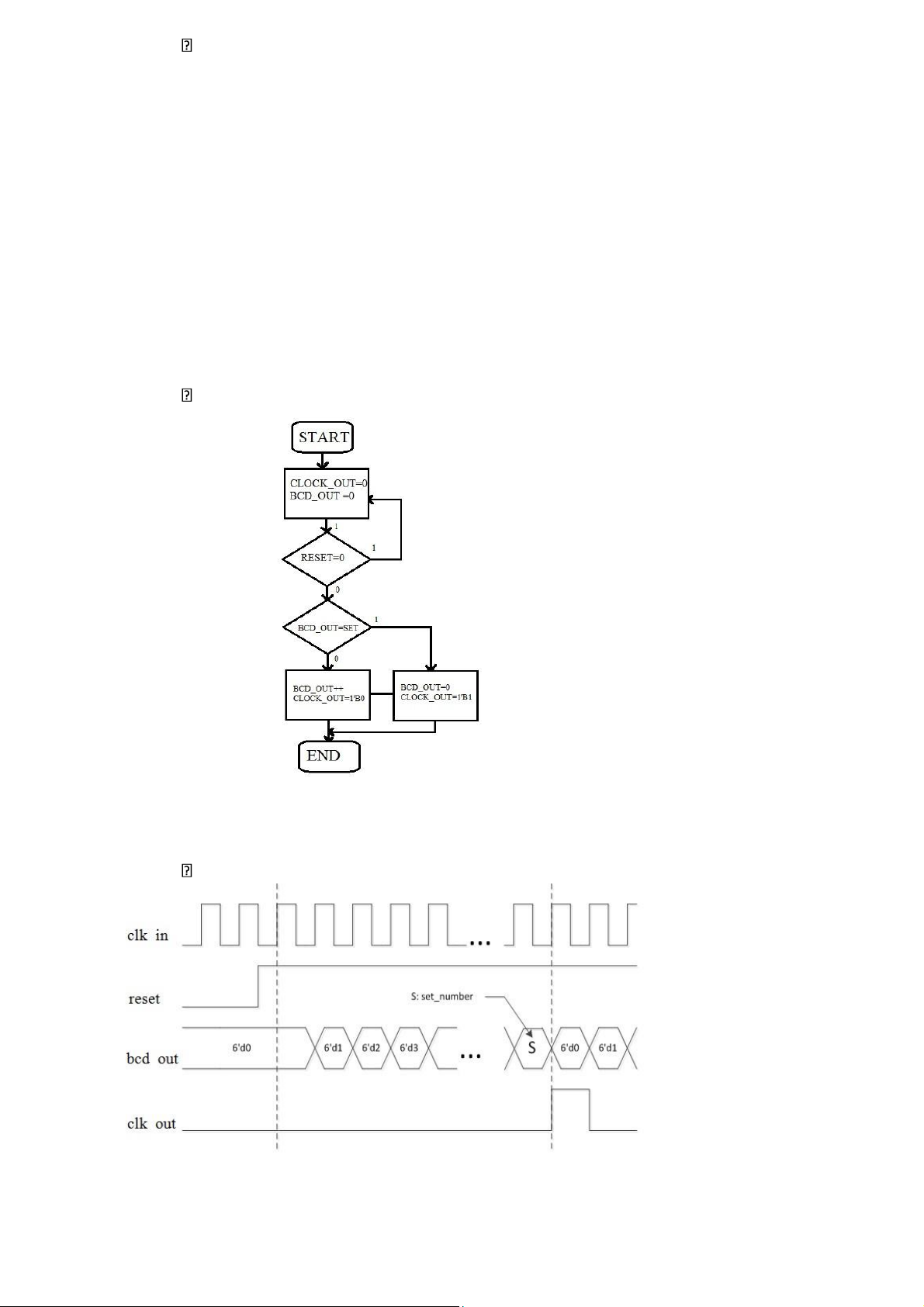

Khối counter thực hiện chức năng đếm: tăng giá trị output lên 1 khi có sườn

xuống của xung clock. Khi có tín hiệu reset thì output được gán bằng 0 Sơ đồ khối clk_in bcd_out COUNTER set reset clk_out Các đầu vào đầu ra Tên chân I/O Số bit Nhiệm vụ

clk_in I 1 Sườn lên của tín hiệu là điều kiện để thực hiện chức năng đếm set I 1

Thiết lập giới hạn cho bộ đếm

reset I 1 Thiết lập lại các giá trị của bộ đếm bcd_out O 4 Đầu ra là mã BCD,

tăng lên 1 đơn vị khi có sườn lên của xung clock

Để thực hiện chức năng đếm giờ thì ta cần 6 bộ đếm cho các giá trị giờ, phút giây :

• Đầu vào của bộ đếm hàng đơn vị giây là xung clock 1 Hz tức là cứ 1

xung thì tăng giá trị lên 1 khi output= “1001” thì reset về “0000”, bit

output[3] được đưa vào làm đầu vào cho clock bộ đếm hàng chục giây

khi output=”0101” thì reset về “0000”.

• Tương tự với các bộ đếm phút.

• Bộ đếm giờ : tương tự như trên thêm 1 trạng thái reset khi 23:59:59 Sơ đồ thuật toán

Mô phỏng tín hiệu của bộ đếm (Counter)

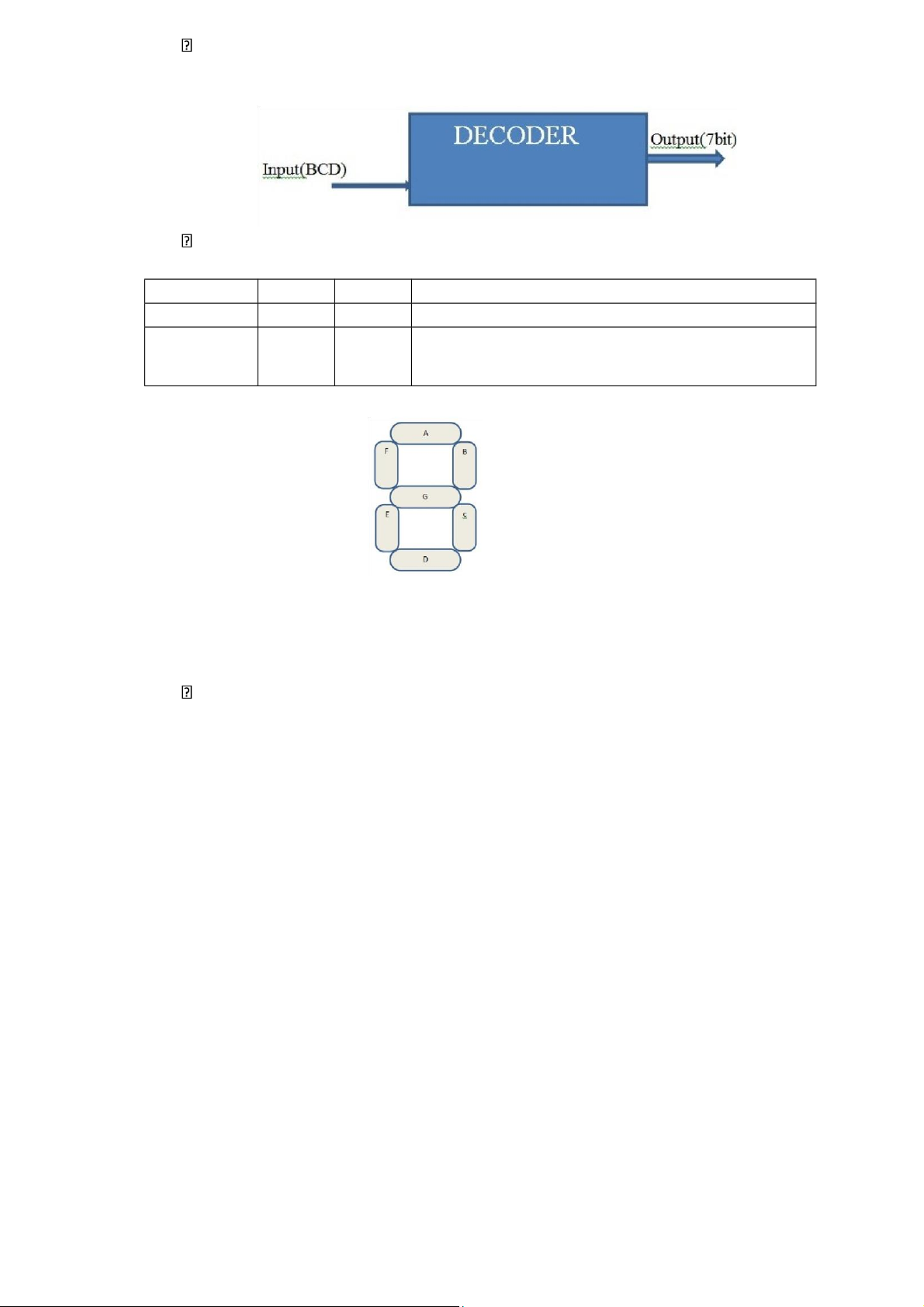

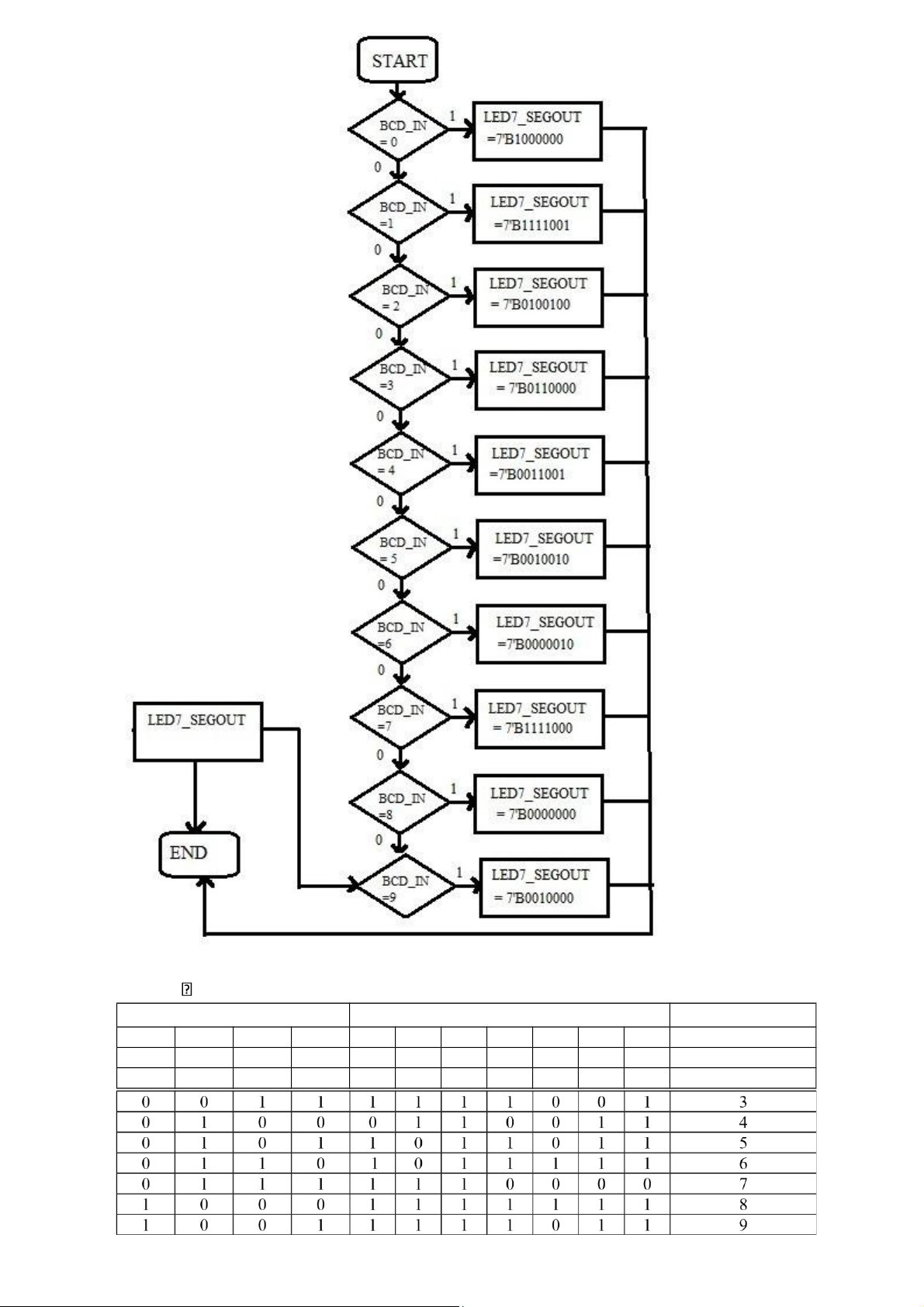

3.3 Khối giải mã LED 7 thanh

Thực hiện chức năng giải mã : Đầu vào là mã BCD của bộ đếm, đầu ra là

tín hiệu điều khiển led 7 thanh Các đầu vào đầu ra Tên chân I/O Số bit Nhiệm vụ Input I 4

Mã BCD lấy từ bộ đếm Output O 7

Đầu ra tương ứng mã BCD để điều khiển led 7 thanh Sơ đồ thuật toán Bảng giá trị Đầu vào Đầu ra Giá trị hiển thị 0 0 0 0 1 1 1 1 1 1 0 0 0 0 0 1 0 1 1 0 0 0 0 1 0 0 1 0 1 1 0 1 1 0 1 2 B. PHẦN MỀM SYNOPSYS

1. Check leda và mô phỏng timing

Leda là công cụ khá đơn giản trong các phần mềm synopsys giúp người dùng có thể

kiểm tra khả năng tổ hợp của các code RTL của mình Dưới đây là hướng dẫn sử dụng công cụ này :

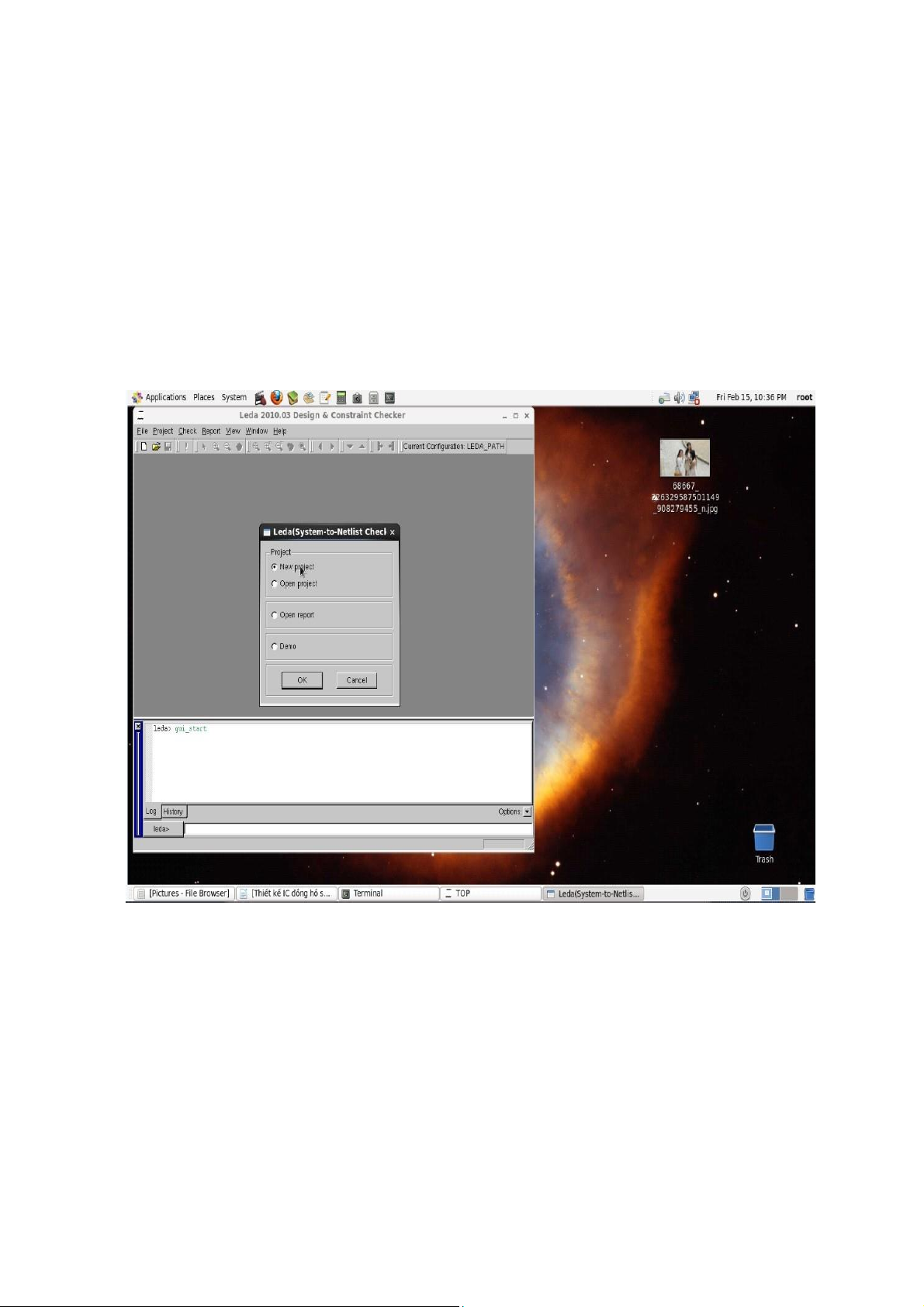

• Đầu tiên khởi chạy phần mềm synopsys trên terminal sau đó chạy leda bằng

câu lệnh “leda” màn hình chương trình chạy lên chọn New project → ok.

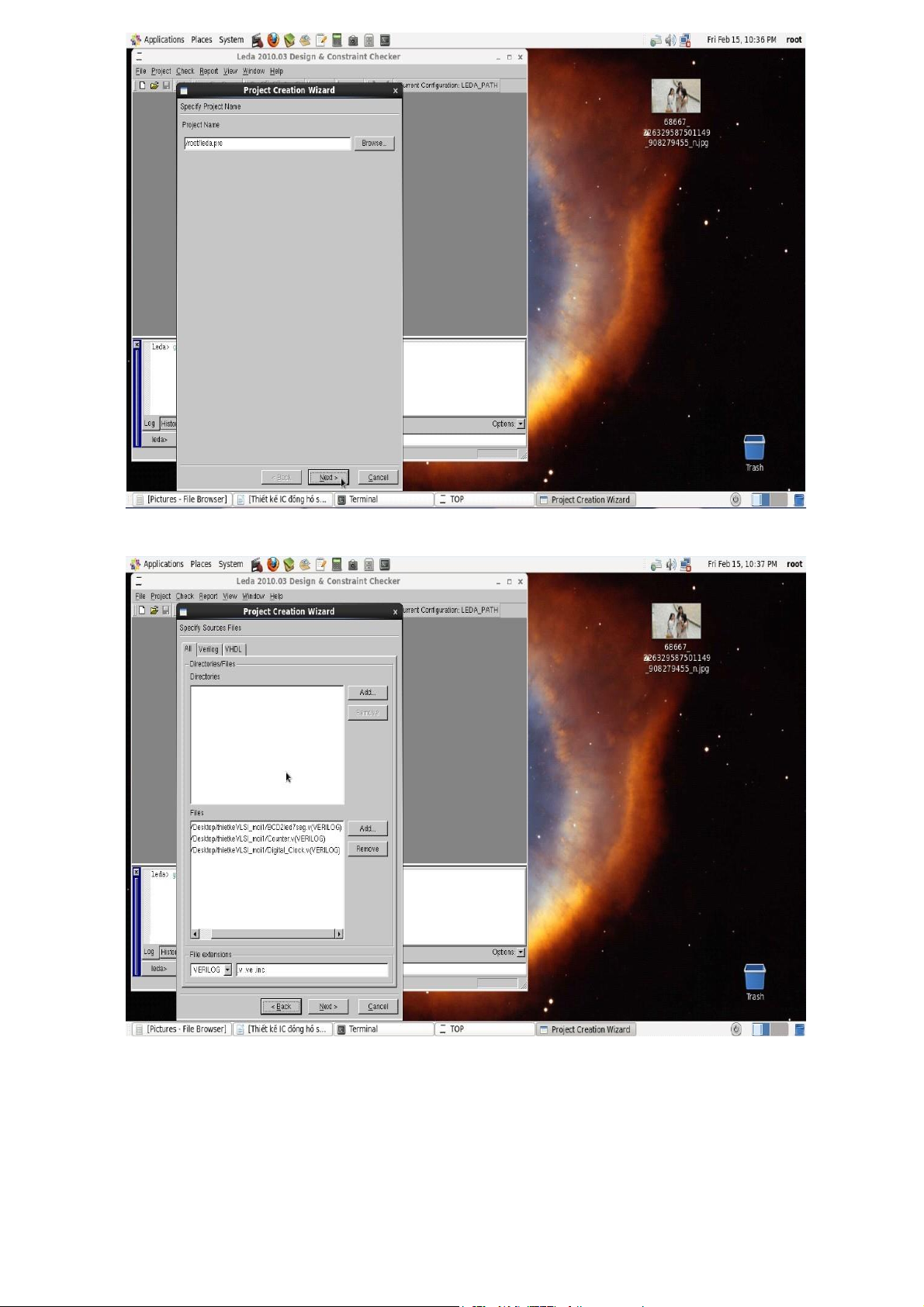

• Khi các cửa sổ khác hiện lên chọn next ,click chọn năm 2001,chọn next tới khi

chương trình hỏi add file chúng ta sẽ add tất cả các file code RTL của thiết kế

vào (trừ file tesbench) → ok

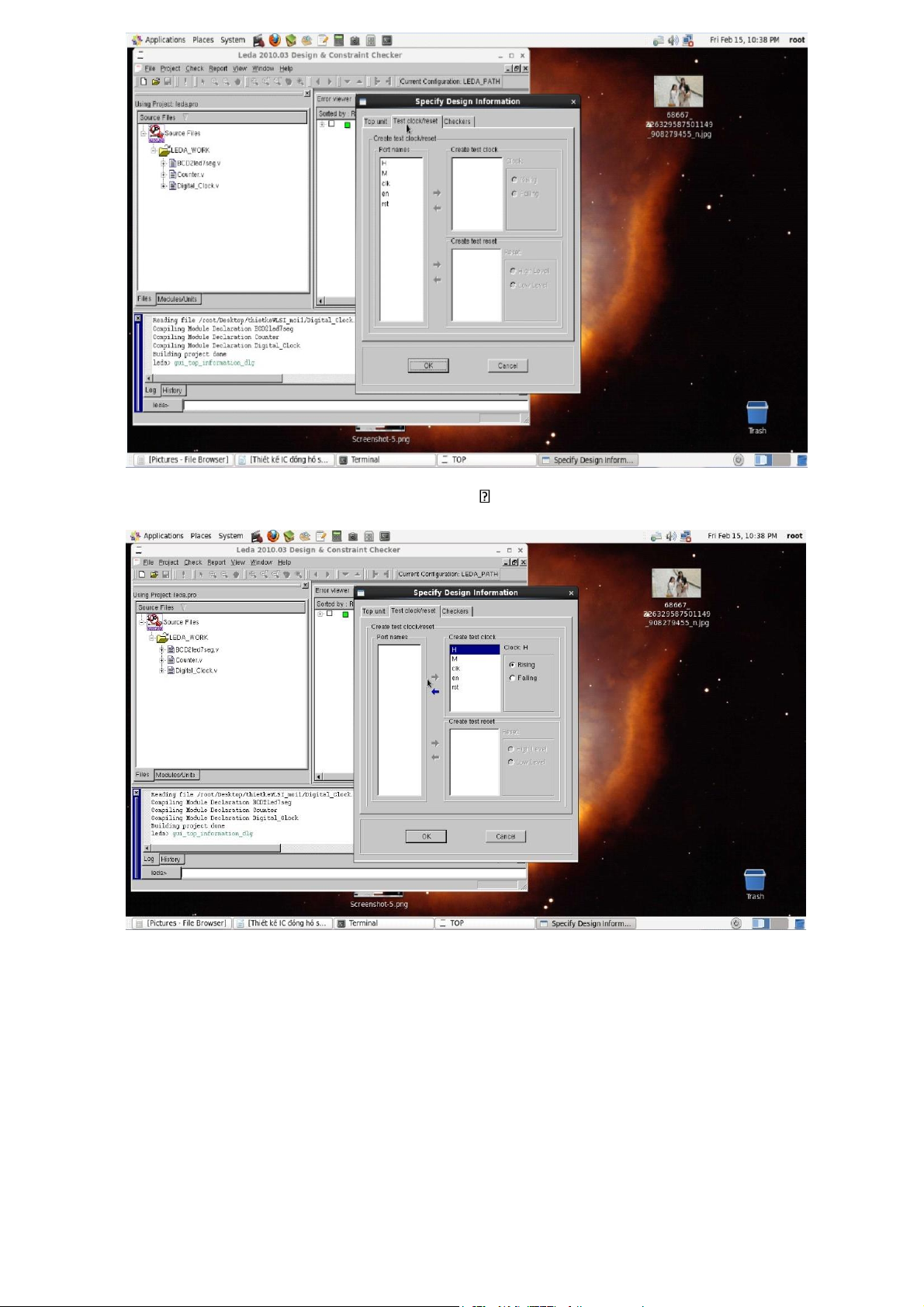

• Tại cửa sổ unit name ta chọn module mà muốn test sau đó chọn Tesclock/reset

• Sau đó chọn chân tín hiệu muốn test click vào mũi tên như hình dưới

• Chọn ok để bắt đầu kiểm tra.

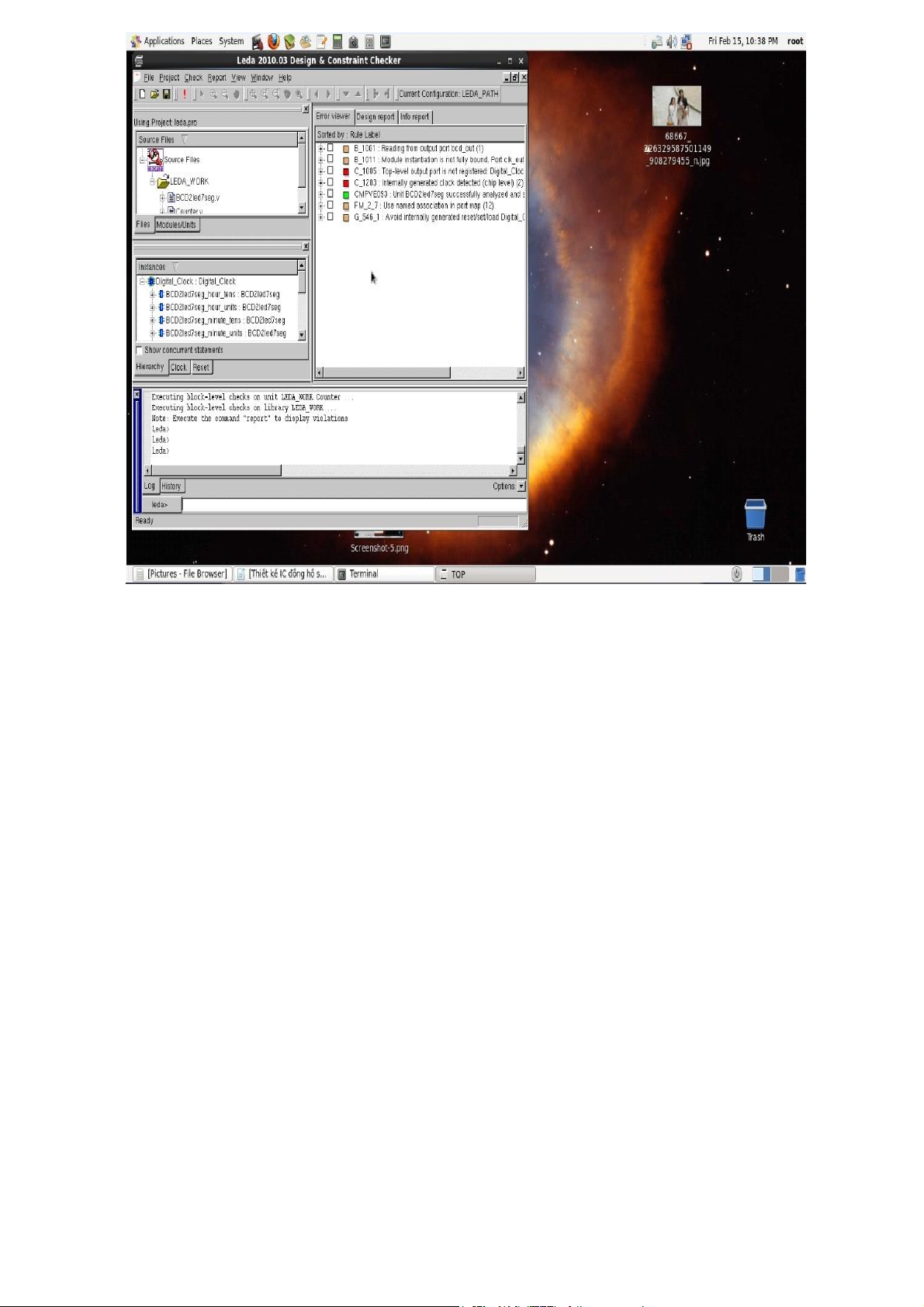

Hình dưới là kết quả kiểm tra :

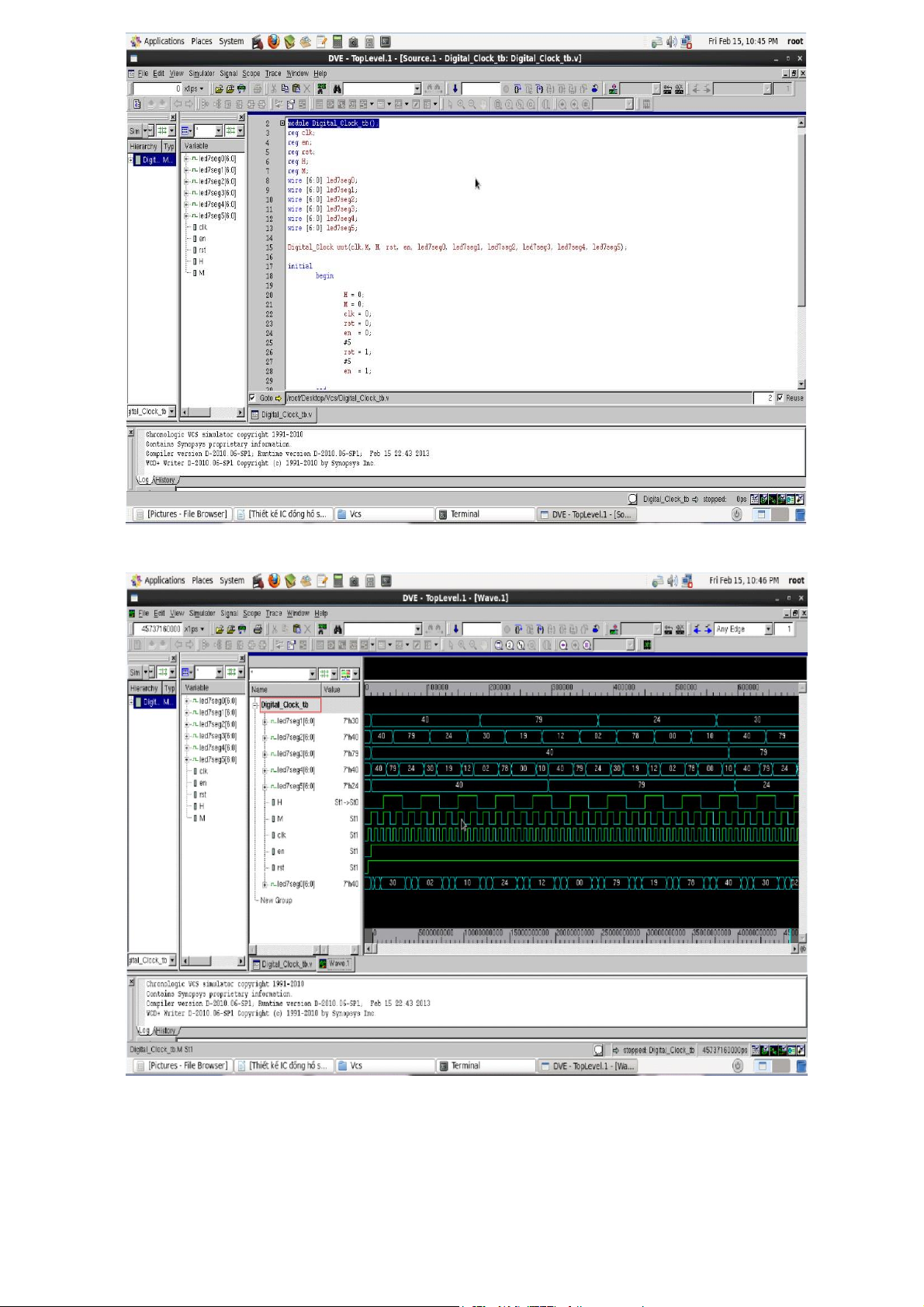

• Chúng ta có thể chuyển sang phần tiếp theo là mô phỏng timing của code

RTL xem có đúng chức năng không

• Chúng ta sẽ tạo một foder chứa tất cả file code RTL sau đó mở terminal ở foder

đó rồi gõ lệnh vcs –debug +v2k *.v

Sau khi debug sẽ tạo ra file simv là file mô phỏng timing của mạch ,chúng ta

mở file simv bằng lệnh : ./simv –gui

Kết quả mô phỏng như sau :

2. Design Compile DC dùng để thực hiện tổ hợp mạch logic mức cổng và tối ưu mạch logic mức cổng

Tạo foder DC sau đó bật terminal tại forder đó

Bước1: (chạy chương trình)

Gõ lệnh dc_shell –gui để chạy DC như hình dưới

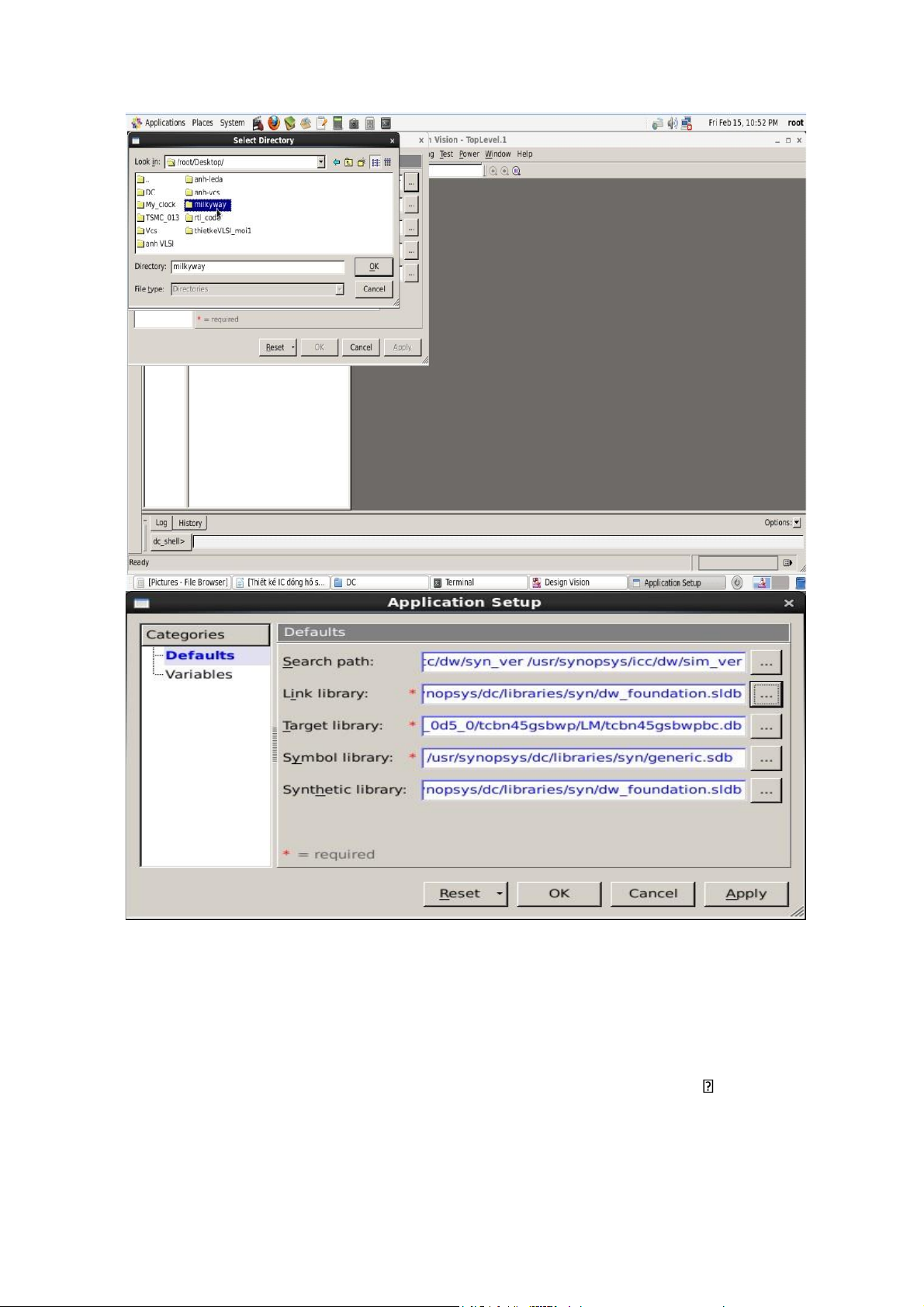

Bước2 (cài đặt thư viện)

Trên giao diện click vào setup → sau đó chọn các đường dẫn các file thư viện theo chỉ dẫn

- search path /home/hoangbinh/milkyway -targetlib

/home/hoangbinh/milkyway/tcbn45gsbwp_120a/frame_only_HVH_0d5_0/tcbn45gs

bwp/LM/tcbn45gsbwpbc.db

- symbol lib /usr/synopsys/dc/libraries/syn/generic.sdb

- synthetic lib /usr/synopsys/dc/libraries/syn/dw_foundation.sldb

- link lib bao gồm taget voi synthetic

Sau khi setup thư viện chúng ta chạy lệnh Set_svf top.svf vào

file chọn read → chọn file Digital_Clock

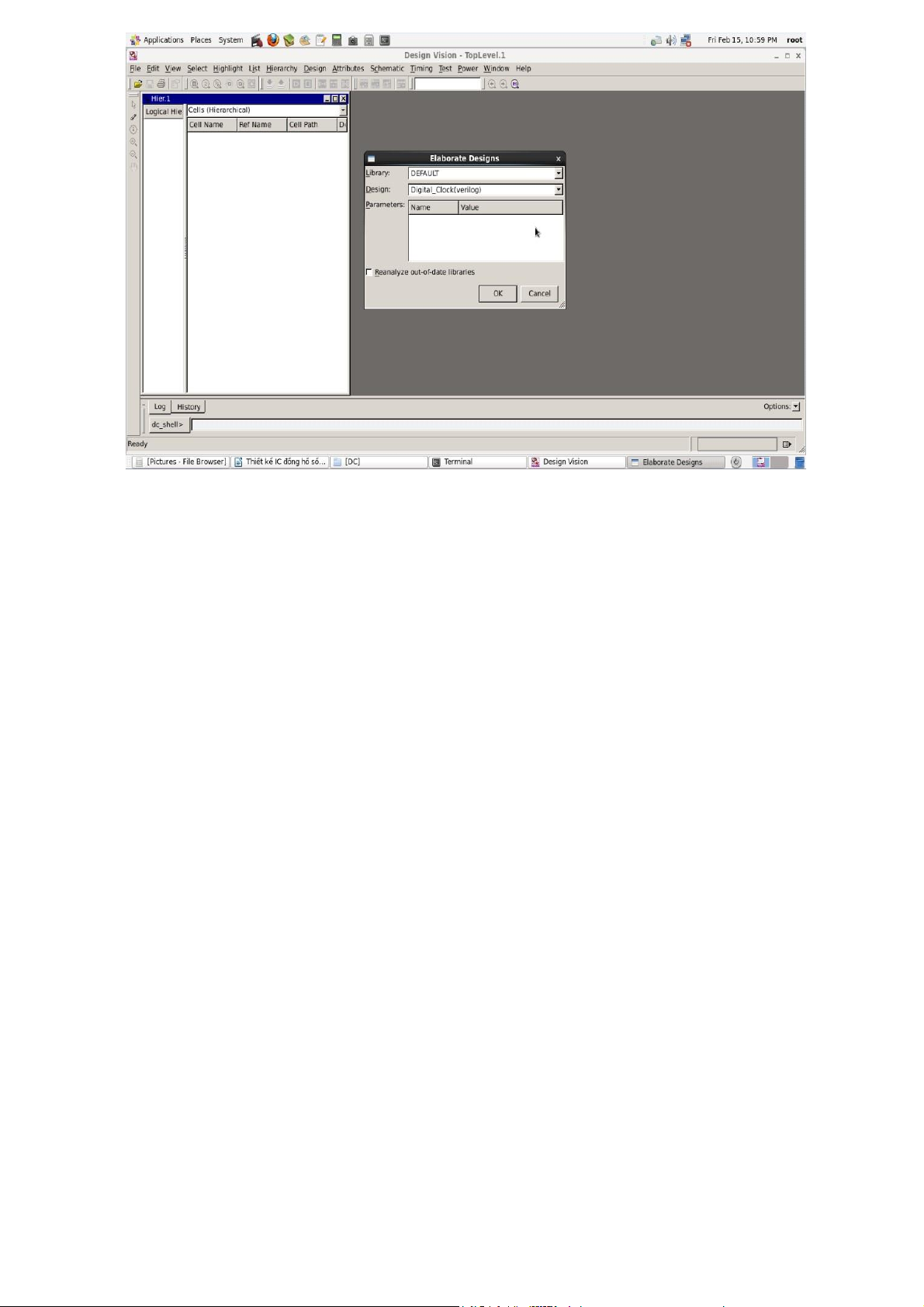

Bước 3 (analyze code RTL)

Trên giao diện DC click chọn analyze sau đó đến đường dẫn và chọn các file code

RTL (trừ file tesbench) → ok

Tiếp theo chọn file → elaborate, trên thanh design chọn Digital_Clock ok

Bước 4: contrain

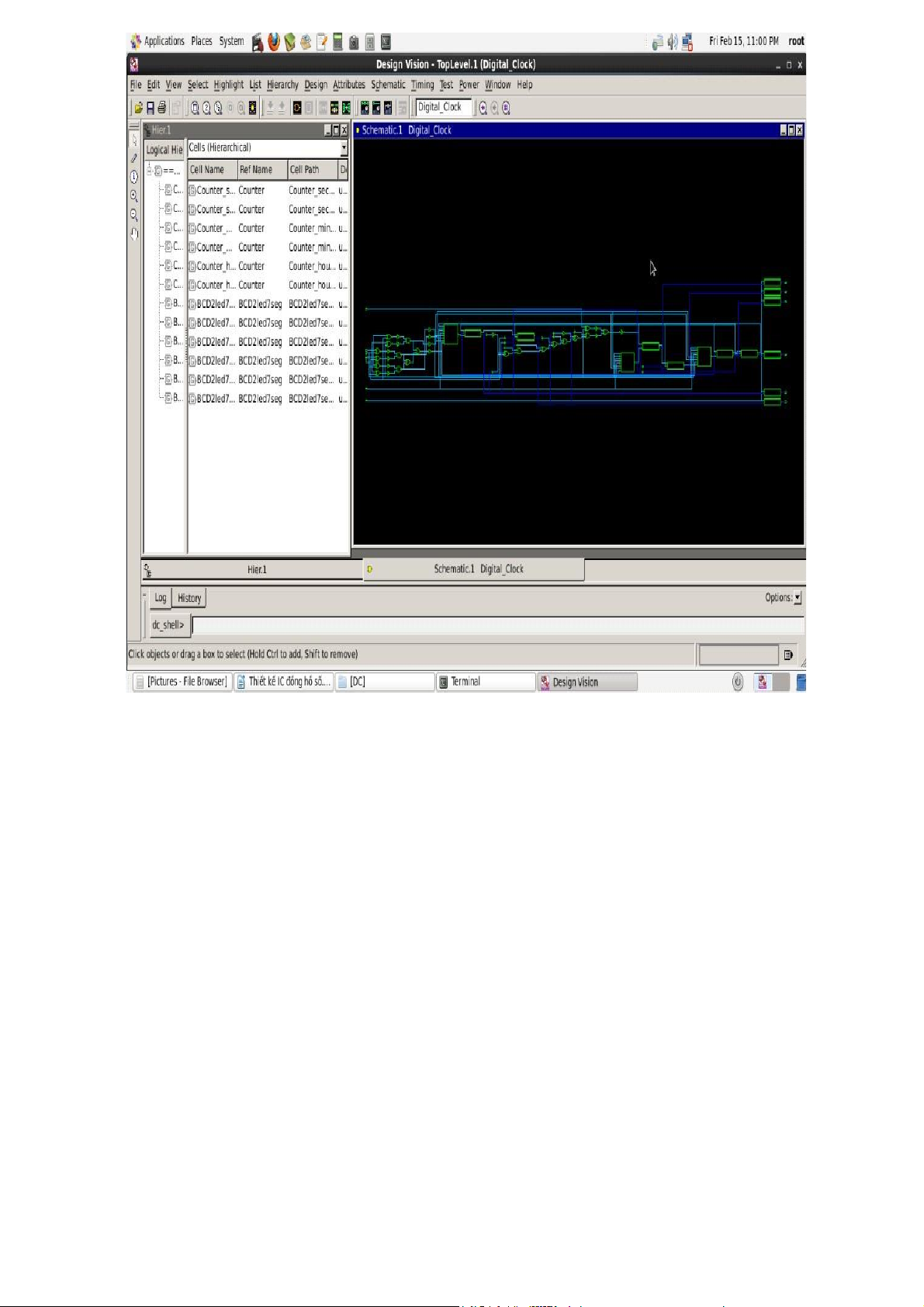

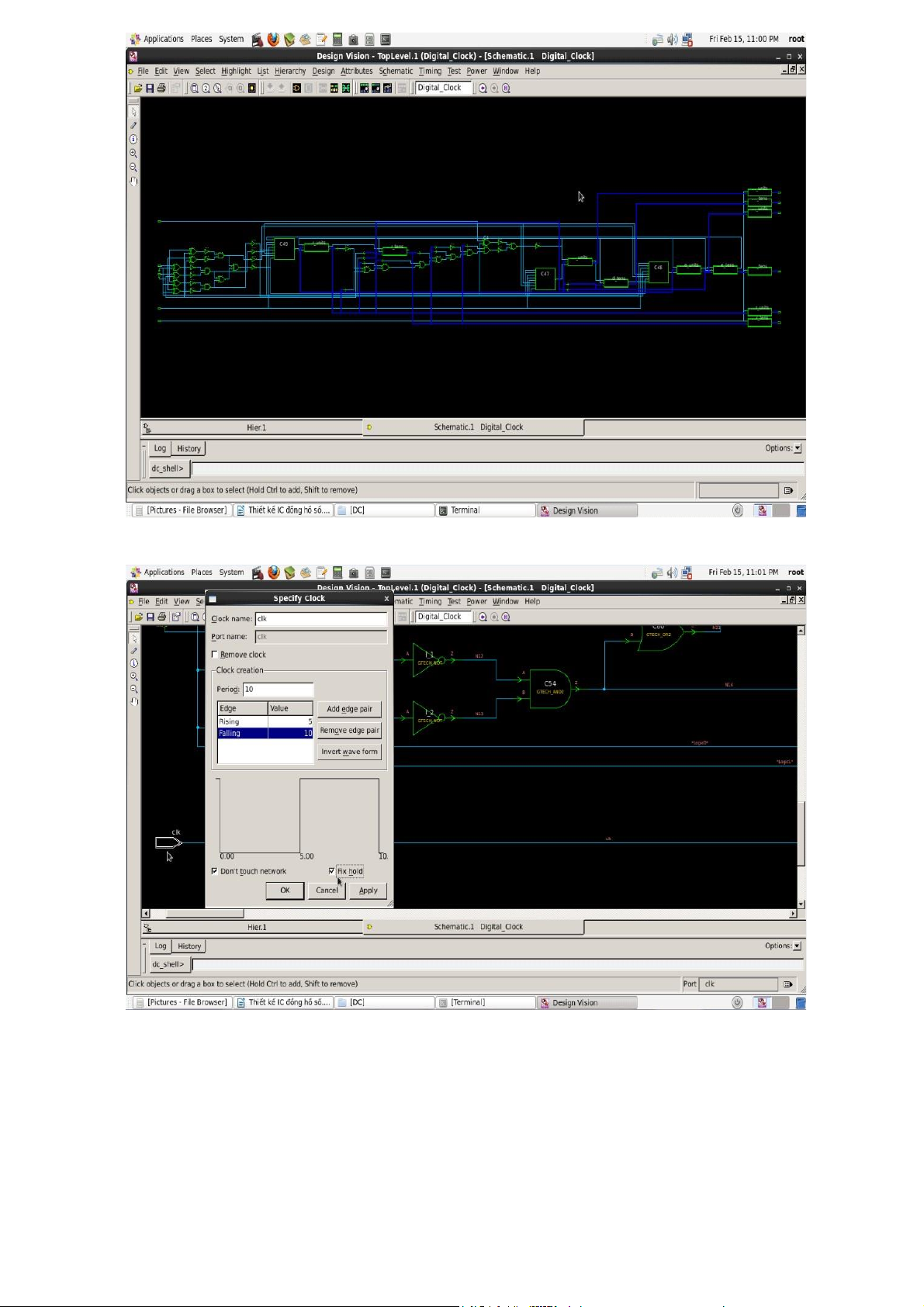

Trước tiên click vào biểu tượng logich trên tool để tạo ra hình vẽ các khối như hình dưới đây Constrains clk

-click vào chân clk trên hình → chọn attributes → chọn specify clock ở các ô

clock name,rising,falling chọn thong số phù hợp có thể như hình dưới

Constrains input (en,reset) Click cả hai chân input → chọn attributes → chọn input

delay rồi cấu hình như hình dưới