Preview text:

lOMoAR cPSD| 59703641

ĐẠI HỌC BÁCH KHOA HÀ NỘI TRƯỜNG ĐIỆN - ĐIỆN TỬ

BÁO CÁO THIẾT KẾ VLSI

Synchronous FIFO with RAM from RTL to GDS

Giảng viên hướng dẫn: TS. Nguyễn Vũ Thắng

Nhóm SV thực hiện: Nguyễn Minh Quân 20214061 Hoàng Ngọc Minh 20213999 Hà Nội, 1/2025

CHƯƠNG I. TỔNG QUAN VLSI I.

Giới thiệu về VLSI

Thiết kế VLSI là một lĩnh vực công nghệ cao tập trung vào việc thiết kế và sản xuất

các mạch tích hợp (IC) với quy mô cực lớn. Ưu điểm nổi bật của VLSI là khả năng

tích hợp hàng tỷ transistor lên một chip duy nhất, tạo ra các thiết bị điện tử nhỏ

gọn, hiệu năng cao và tiêu thụ điện năng thấp.

● Tích hợp cao: VLSI cho phép tích hợp nhiều thành phần điện tử lên một chip duy

nhất, giúp giảm kích thước và tăng độ phức tạp của các thiết bị.

● Hiệu năng cao: Nhờ quy mô lớn và công nghệ tiên tiến, các mạch VLSI hoạt động

nhanh hơn, xử lý thông tin hiệu quả hơn so với các mạch truyền thống.

● Tiêu thụ điện năng thấp: Các kỹ thuật thiết kế hiện đại giúp giảm thiểu tiêu thụ

điện năng của các mạch VLSI, tăng tuổi thọ pin của các thiết bị di động.

● Đa dạng ứng dụng: VLSI được ứng dụng rộng rãi trong nhiều lĩnh vực, từ vi xử lý,

bộ nhớ, cảm biến cho đến các hệ thống nhúng và trí tuệ nhân tạo.

Tuy nhiên, thiết kế VLSI cũng đòi hỏi kiến thức chuyên sâu và các công cụ thiết kế

phức tạp. Các kỹ sư thiết kế VLSI cần phải cân nhắc nhiều yếu tố như hiệu suất,

diện tích chip, tiêu thụ điện năng, độ tin cậy và chi phí sản xuất.

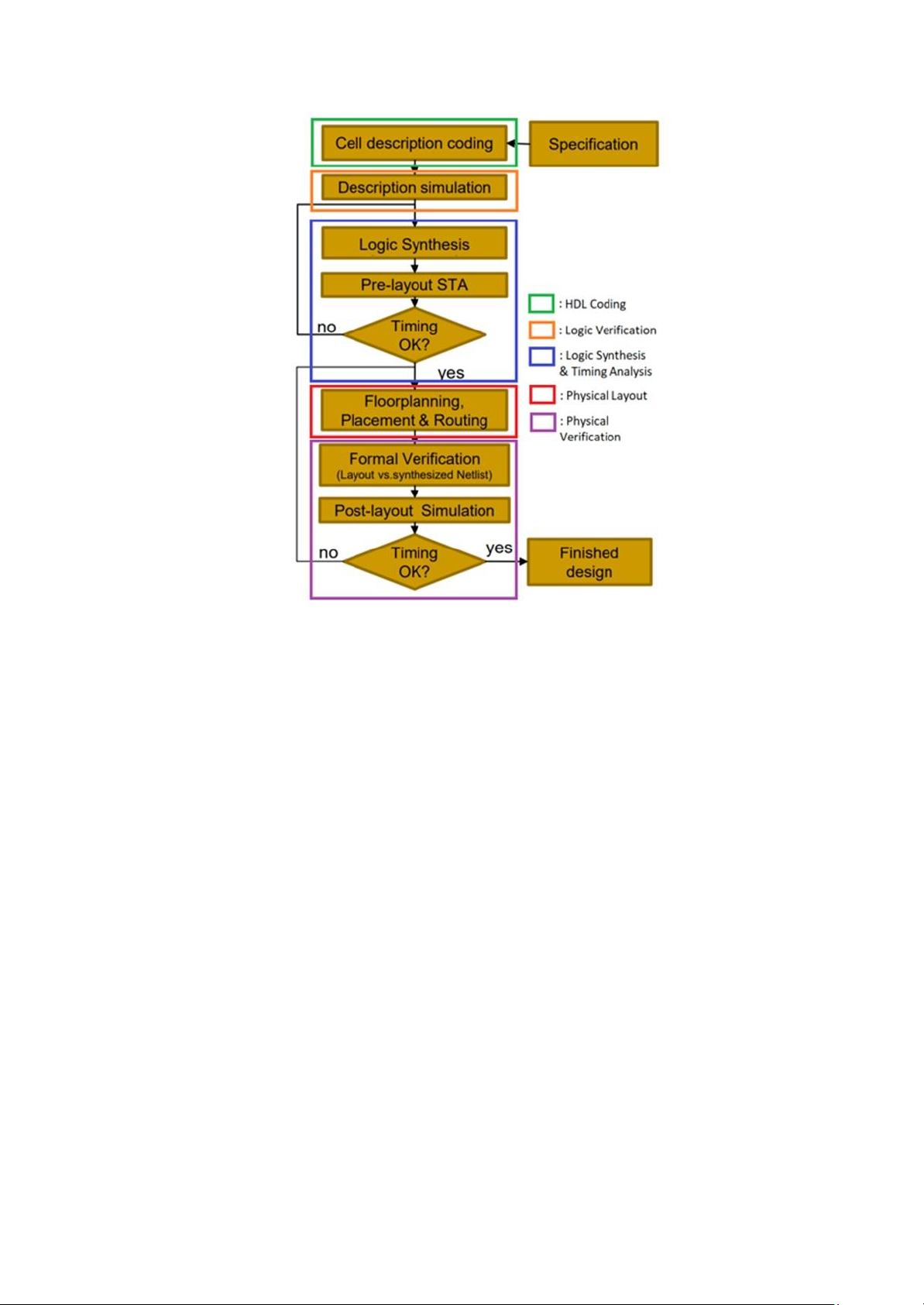

II. Quy trình thiết kế VLSI

Quy trình thiết kế VLSI có thể được biểu diễn bởi 5 bước cơ bản, bao hàm các thao

tác cần thực hiện để có thể đưa ra bản vẽ kĩ thuật cho mạch, gồm:

● HDL Coding - Lập trình mô tả phần cứng.

○ Mạch điện tử số có thể được mô tả thông qua lập trình, dựa trên chức năng/hành

vi của mạch (behavioral), cấu trúc (structural), đặc điểm luồng dữ liệu (data-flow).

○ Sử dụng các ngôn ngữ mô tả phần cứng (HDL) như Verilog, VHDL,

SystemVerilog, v.v.. ● Logic Verification – Kiểm thử logic.

○ Được sử dụng để kiểm tra logic của phần cứng được thiết kế trên HDL, đảm bảo tính

hoạt động đúng đắn của mạch khi được thiết kế.

● Logic Synthesis & Timing Analysis – Tổng hợp logic & Phân tích hiệu năng thời gian.

○ Dựa trên kết quả lập trình HDL đã đúng logic, tiến hành chuyển đổi mô tả của mạch

dưới dạng chức năng/cấu trúc sang tập các cổng logic thực tế & liên kết giữa các

cổng cần thiết để tạo ra mạch thật.

○ Phân tích hoạt động của mạch về mặt thời gian (timing analysis) để xác định hiệu

năng hoạt động, từ đó tạo các ràng buộc/giới hạn cho thiết kế.

● Physical Layout – Tạo bản vẽ vật lý.

○ Dựa vào thiết kế đã được dịch sang tập các cổng logic & liên kết, cùng với thư viện

công nghệ & các ràng buộc thiết kế (hiệu năng thời gian, diện tích, năng lượng, …),

tiến hành tạo bản vẽ vật lý của mạch

● Physical Verification & Sign-off – Kiểm thử vật lý & Hoàn thiện. Physical Verification:

o Kiểm tra bản vẽ của mạch, dựa trên các bộ quy định (design rule) được cung cấp

từ phía nhà sản xuất (foundry). Bản vẽ phải đảm bảo không có lỗi so với bộ quy

định trên Design Rule Check (DRC)

o Kiểm tra độ trùng khớp giữa sơ đồ nguyên lý (schematic) so với bản vẽ (layout). Về

mặt logic, sơ đồ nguyên lý & bản vẽ phải tương đồng. Layout Vs Schematic (LVS)

Post-Timing Analysis: Kiểm tra hiệu năng thời gian sau khi đã có bản vẽ. Thiết kế với

bản vẽ thu được phải đảm bảo các đường dữ liệu hoạt động theo đúng giới hạn

thời gian, không phát sinh trạng thái không xác định trên toàn mạch.

III. Ngôn ngữ mô tả phần cứng Verilog

Verilog là một ngôn ngữ mô tả phần cứng (HDL - Hardware Description Language)

được sử dụng để mô phỏng, thiết kế và xác định các hệ thống kỹ thuật số. Được

phát triển vào những năm 1980, Verilog đã trở thành một trong những ngôn ngữ

phổ biến nhất trong lĩnh vực thiết kế vi mạch.

Verilog được sử dụng để mô tả hành vi và cấu trúc của các mạch kỹ thuật số, từ

mạch đơn giản như cổng logic cho đến mạch phức tạp như vi xử lý. Ngôn ngữ này

cung cấp cú pháp và cấu trúc cho việc mô phỏng và thiết kế hệ thống số thông qua

việc sử dụng các module, tín hiệu, biến, và các câu lệnh điều khiển.

Verilog cung cấp một cách để mô phỏng hoặc tạo ra một mô hình của hệ thống kỹ

thuật số và cho phép kiểm tra và xác minh tính đúng đắn của nó trước khi triển

khai vào phần cứng thực tế. Nó cũng được sử dụng trong quá trình thiết kế vi mạch,

từ việc mô phỏng và kiểm tra đơn giản cho đến tổ chức và xác định các mạch phức tạp hơn.

Trên thực tế, Verilog đã trở thành một ngôn ngữ chuẩn trong lĩnh vực thiết kế mạch

tích hợp và thường được sử dụng trong các công cụ thiết kế như Xilinx ISE, Altera

Quartus, và Cadence Design Systems. 1. Module

Trong Verilog, một module là một đơn vị cơ bản để mô tả một phần của hệ thống

kỹ thuật số. Nó được sử dụng để định nghĩa các thành phần riêng lẻ của mạch và

xác định cách chúng tương tác với nhau. Mỗi module trong Verilog có thể được

xem như một "khối xây dựng" trong thiết kế phần cứng.

Một module trong Verilog bao gồm các phần chính sau:

● Tên module: Mỗi module được đặt tên duy nhất để xác định nó trong thiết kế.

● Khối chứa: Module có thể chứa các khối khác như input, output, wire, reg, và các

module con khác. Các khối này đại diện cho tín hiệu, biến và các thành phần khác trong mạch.

● Cổng vào và cổng ra: Module có thể có các cổng vào (input) và cổng ra (output) để

tương tác với các module khác hoặc với môi trường bên ngoài.

● Internal logic: Module có thể chứa các khối logic và câu lệnh điều khiển để thiết lập hành vi bên trong.

● Instantiation: Module có thể được sử dụng như một thành phần trong các module

khác bằng cách sử dụng cú pháp instantiation. Điều này cho phép tái sử dụng và

phân cấp các module để xây dựng mạch phức tạp hơn.

Module trong Verilog cung cấp một cách để tạo ra các phần tử mạch đơn giản và

kết hợp chúng thành mạch phức tạp hơn. Nó giúp tăng tính tái sử dụng, hiệu suất

và khả năng mô phỏng của quá trình thiết kế vi mạch.

Dưới đây là một ví dụ đơn giản về mô tả module cho cổng AND 2 bit đầu vào:

module AND_gate(input a, input b, output y); assign y = a & b; endmodule

Trong ví dụ này, chúng ta định nghĩa một module có tên là "AND_gate". Module

này có hai cổng vào (input) là "a" và "b", và một cổng ra (output) là "y". Các cổng

vào và cổng ra được khai báo bằng từ khóa "input" và "output".

Dòng "assign y = a & b;" xác định rằng giá trị của cổng ra "y" là kết quả của phép

AND logic giữa cổng vào "a" và "b". Dấu "&" đại diện cho phép AND logic trong

Verilog. Module "AND_gate" này có chức năng thực hiện phép AND logic giữa hai

tín hiệu đầu vào và đưa ra kết quả qua cổng ra. 2. Kiểu dữ liệu

Trong Verilog, có nhiều kiểu dữ liệu (data types) khác nhau để đại diện cho các loại

giá trị và tín hiệu trong mạch kỹ thuật số. Dưới đây là một số kiểu dữ liệu phổ biến trong Verilog:

● Bit và logic: Kiểu dữ liệu 'bit' và 'logic' đại diện cho một bit duy nhất có giá trị logic

0 hoặc 1. Cả hai kiểu dữ liệu này có thể được sử dụng để biểu diễn các tín hiệu logic đơn giản.

● Integer: Kiểu dữ liệu 'integer' đại diện cho một số nguyên có dấu trong khoảng từ

-2^31 đến 2^31-1. Nó được sử dụng để biểu diễn các giá trị số nguyên trong mạch.

● Reg: Kiểu dữ liệu 'reg' đại diện cho một thanh ghi (register). Nó được sử dụng để

lưu trữ các giá trị tạm thời trong quá trình thực hiện mạch kỹ thuật số.

● Wire: Kiểu dữ liệu 'wire' đại diện cho một tín hiệu không đồng bộ (asynchronous

signal) hoặc một liên kết điểm (net). Nó được sử dụng để kết nối các thành phần

trong mạch và truyền giá trị giữa chúng.

● Reg và wire vector: Verilog cũng hỗ trợ các kiểu dữ liệu vectơ, bao gồm 'reg [n:0]'

và 'wire [n:0]', trong đó n là số bit của vectơ.

Các kiểu dữ liệu vectơ này cho phép lưu trữ và xử lý các tín hiệu có độ rộng lớn hơn một bit.

● Struct và Union: Verilog cung cấp cú pháp để định nghĩa các kiểu dữ liệu struct và

union tương tự như trong ngôn ngữ lập trình. Các kiểu dữ liệu này cho phép nhóm

các thành phần dữ liệu có cấu trúc hoặc không liên quan vào một đối tượng đơn.

Ngoài ra, Verilog còn hỗ trợ các kiểu dữ liệu khác như 'real' (đại diện cho số thực)

và các kiểu dữ liệu tùy chỉnh được định nghĩa bởi người dùng. Các kiểu dữ liệu này

cung cấp linh hoạt trong việc mô phỏng và biểu diễn các giá trị và tín hiệu trong mạch kỹ thuật số. 3. Block quan trọng

Trong Verilog, các phép gán dùng để gán giá trị cho một biến hoặc một tín hiệu. Nó

cho phép ta thiết lập giá trị của một biến dựa trên giá trị của các biến khác, hoặc

thiết lập giá trị của một tín hiệu dựa trên các điều kiện và logic khác. Có 3 kiểu cơ bản: always @ (condition)

Luôn thực thi khi thỏa mãn điều kiện (condition) initial

Chỉ thực thi một lần kể từ lúc mô phỏng assign [LHS] = [RHS]

Giá trị LHS luôn được cập nhật khi RHS thay đổi Một số lưu ý:

● reg chỉ có thể được gán trong các khối initial và always

● wire chỉ có thể được gán thông qua câu lệnh assign

● Nếu như có nhiều dòng lệnh trong khối initial/always, cần phải đưa vào trong cặp begin .. end Hierarchy

Hierarchy trong Verilog là khả năng tổ chức mô hình thiết kế thành các cấu trúc

phân cấp và nhóm các module lại với nhau. Điều này cho phép xây dựng mạch

phức tạp từ các thành phần nhỏ hơn và giúp quản lý và tái sử dụng mã nguồn một cách hiệu quả.

Trong Verilog, hierarchy cho phép định nghĩa các module con bên trong module

chính, và các module con có thể chứa các module con khác. Bằng cách sử dụng cú

pháp ".tên_module_con(tên_tín_hiệu)", chúng ta có thể kết nối các module con

với nhau và với các tín hiệu ở mức cao hơn. Dưới đây là một ví dụ:

Trong ví dụ này, chúng ta có module TopLevel là module cấp cao nhất trong mô hình

thiết kế. Nó chứa hai module con là sub_module1 và sub_module2. Các tín hiệu a,

b, c, d và result được khai báo ở mức topLevel và được sử dụng trong các module con.

Mỗi module con (sub_module1 và sub_module2) có cấu trúc và logic của riêng nó.

Chúng được gắn kết với các tín hiệu a, b, c và d tương ứng thông qua cú pháp đã đề cập ở trên.

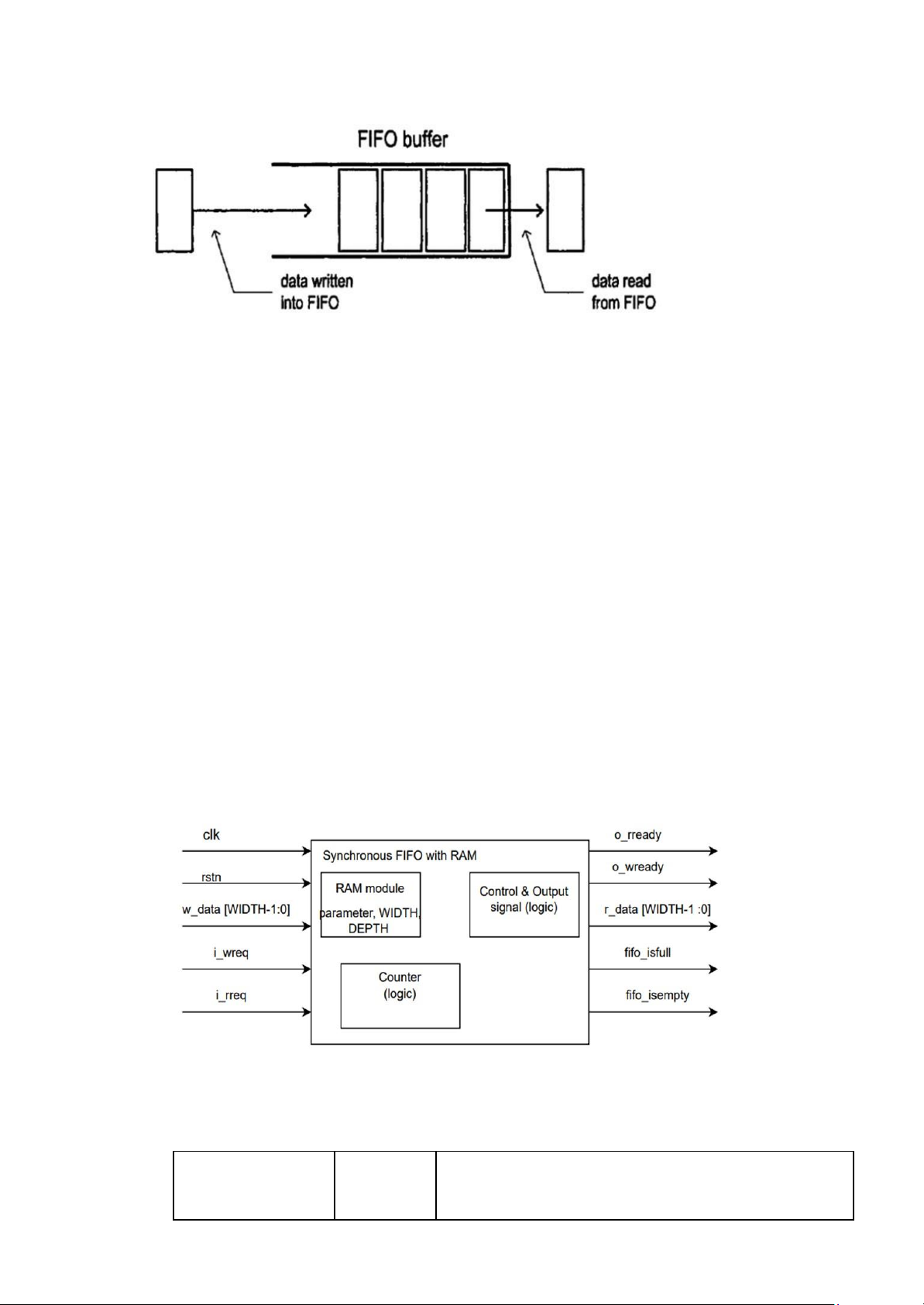

CHƯƠNG II. THIẾT KẾ VÀ TRIỂN KHAI SYNCHRONOUS WITH RAM I. Khái niệm về FIFO

FIFO (First in- First out) là một cấu trúc bộ đệm vòng trong đó dữ liệu được ghi vào

trước sẽ được đọc ra trước. FIFO thường được dùng làm bộ đệm (buffer) trung

gian để lưu trữ tạm thời dữ liệu và truyền dữ liệu giữa hai hệ thống mà có sự khác

biệt về tần số xung nhịp giữa bên truyền và nhận dữ liệu. Vì thế, FIFO gồm hai miền

tín hiệu write và read độc lập. Trong FIFO đồng bộ (synchronous), các thao tác đọc

và ghi dữ liệu sử dụng cùng tần số clock. Thông thường, chúng được sử

dụng với tần số cao để hỗ trợ các hệ thống tốc độ cao.

FIFO được đặc trưng bởi hai thông số:

● DATA_WIDTH: độ rộng của dữ liệu, tương đương với kích thước của dữ liệu của

một phần tử dữ liệu có thể write/read trong một chu kỳ write/read.

● FIFO_DEPTH: chiều sâu của FIFO, tương đương với số phần tử dữ liệu tối đa mà FIFO có thể lưu trữ.

II. Mô tả thiết kế

Đề tài: Thiết kế khối FIFO đồng bộ sử dụng RAM module (Synchronous FIFO with

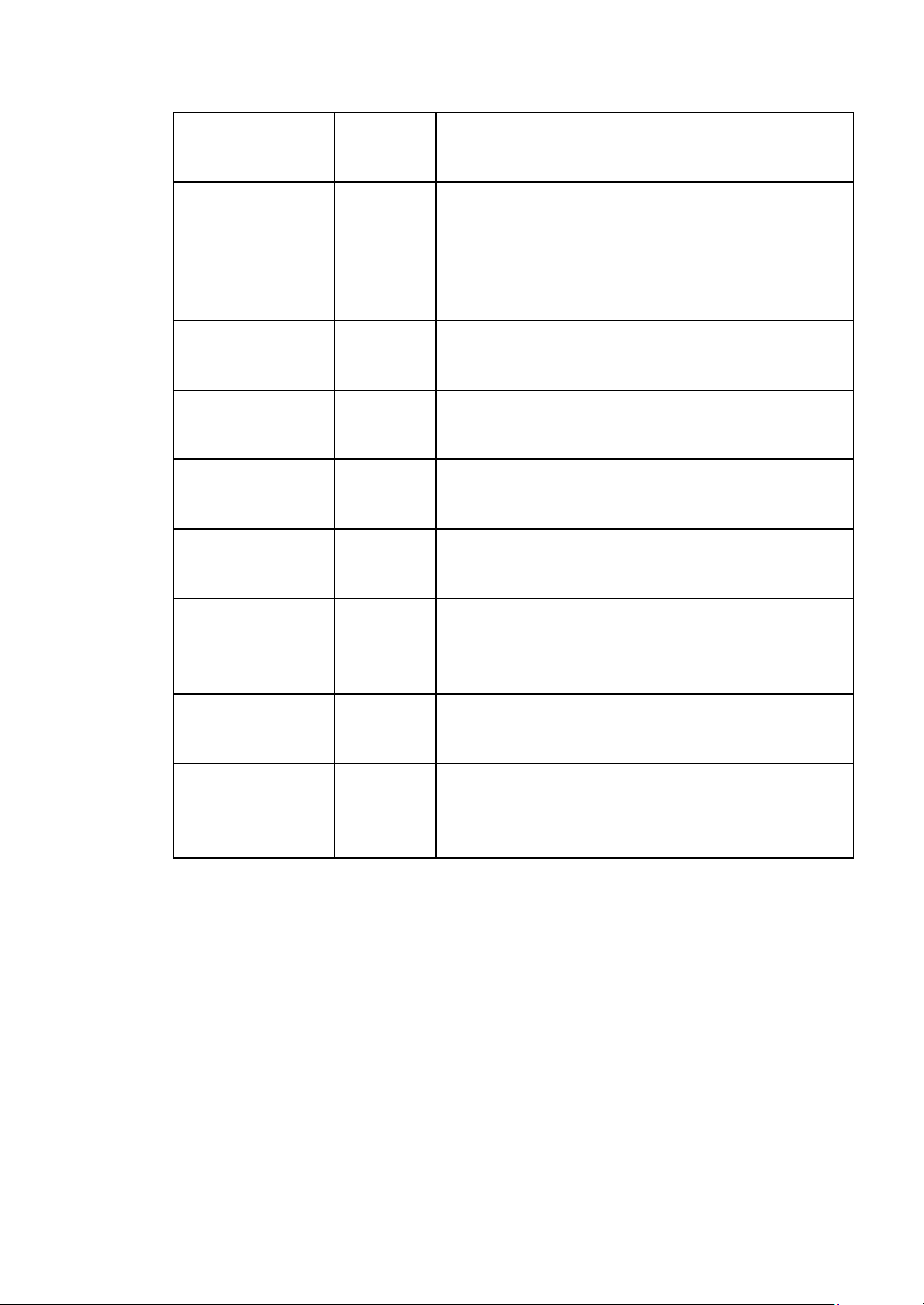

RAM), thực hiện từ lập trình mô tả phần cứng (RTL coding) cho tới tạo bản thiết kế (layout). ● Yêu cầu I/O: Tên tín hiệu Hướng Chức năng clk I

Xung đồng hồ, điều khiển hoạt động của khối sFIFO rstn I

Tín hiệu reset, tích cực mức thấp wdata [WIDTH-

Dữ liệu đưa vào sFIFO (viết vào RAM), rộng WIDTH 1:0] I bit i_wreq I

Tín hiệu thông báo đầu vào tới (yêu cầu ghi dữ liệu) i_rreq I

Tín hiệu yêu cầu đọc dữ liệu o_wready O

Thông báo sFIFO sẵn sàng nhận dữ liệu tiếp theo o_rready O

Thông báo có thể đọc dữ liệu ra từ sFIFO hay không rdata [WIDTH- O 1:0]

Dữ liệu đọc ra từ sFIFO (đọc ra từ RAM), rộng WIDTH bit

Thông báo trạng thái của sFIFO, sFIFO đã đầy hay fifo_isfull O chưa fifo_isempty O

Thông báo trạng thái của sFIFO, sFIFO có rỗng hay không ● Yêu cầu tham số:

○ WIDTH (W) Độ rộng dữ liệu đưa vào sFIFO (word width)

○ DEPTH (D) Độ sâu của RAM module – số lượng word có thể lưu trữ trong

RAM ● Yêu cầu chức năng:

○ Dữ liệu tới sFIFO được lưu vào trong RAM module. Dữ liệu được đọc ra từ RAM

module. Quá trình viết/đọc hoạt động theo cơ chế First-In-First-Out (FIFO).

○ sFIFO hoạt động đồng bộ, theo xung clock (clk)

○ Tín hiệu reset không đồng bộ, tích cực ở mức thấp (resetn)

○ Tín hiệu i_wreq thông báo có dữ liệu mới đến sFIFO & yêu cầu viết. Chỉ khi tín hiệu

i_wreq & tín hiệu o_wready cùng ở mức 1 (yêu cầu ghi & sFIFO sẵn sàng nhận dữ

liệu mới), dữliệu mới được ghi vào trong sFIFO.

○ Tín hiệu i_rreq thể hiện yêu cầu đọc dữ liệu ra từ sFIFO. Chỉ khi tín hiệu i_rreq & tín

hiệu o_rready cùng ở mức 1 (yêu cầu đọc & sFIFO sẵn sàng đọc ra dữ liệu), dữ liệu

mới được đọc ra từ sFIFO.

○ Thông báo trạng thái của sFIFO:

■ fifo_isfull: Đưa lên 1 nếu bộ nhớ (RAM) trong FIFO đã đầy, không nhận thêm dữ liệu

mới cho đến khi được đọc ra

■ fifo_isempty: Đưa lên 1 nếu bộ nhớ (RAM) trong FIFO đã rỗng, không thể đọc dữ

liệu ra cho đến khi dữ liệu mới được ghi vào. ● Ghi chú:

○ Các tham số WIDTH, DEPTH được sử dụng để quy định loại RAM module sẽ được

sử dụng trong thiết kế.

○ RAM module được cung cấp sẵn, không yêu cầu lập trình & tạo layout trong quá trình sử dụng

III. Triển khai thiết kế RTL bằng Verilog và SystemVerilog

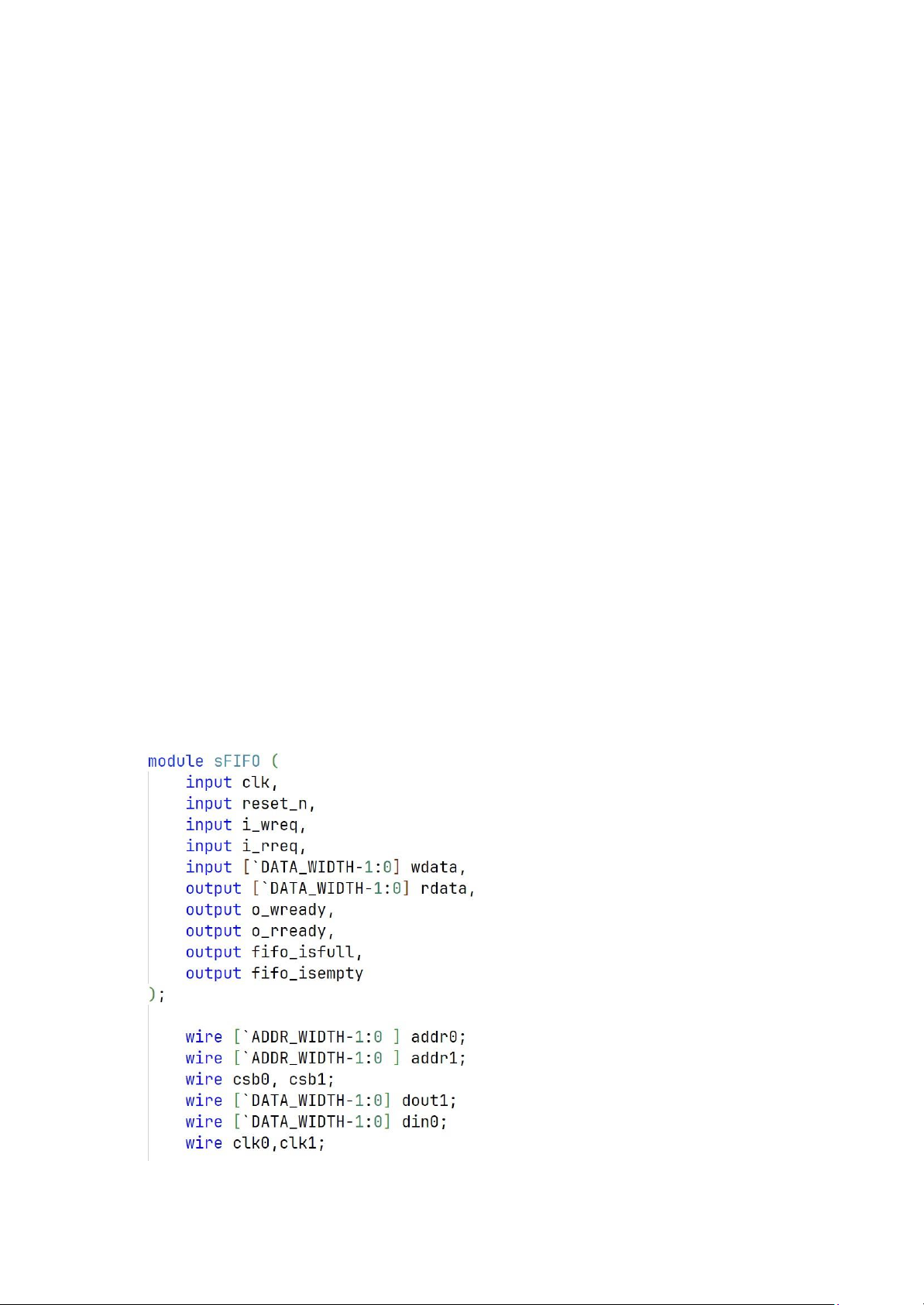

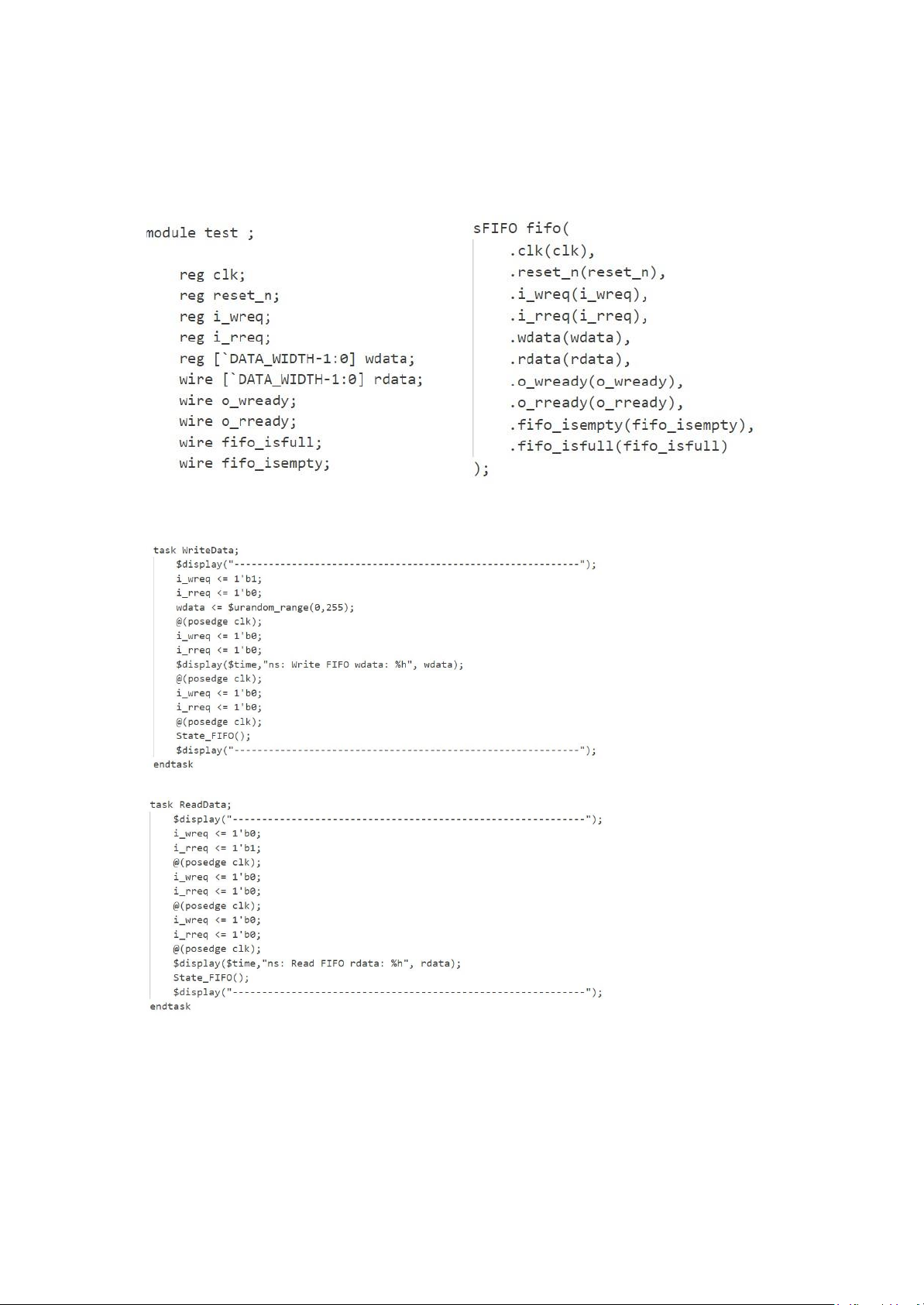

Đoạn code khai báo khởi tạo module FIFO top với các thong số đầu vào, ra

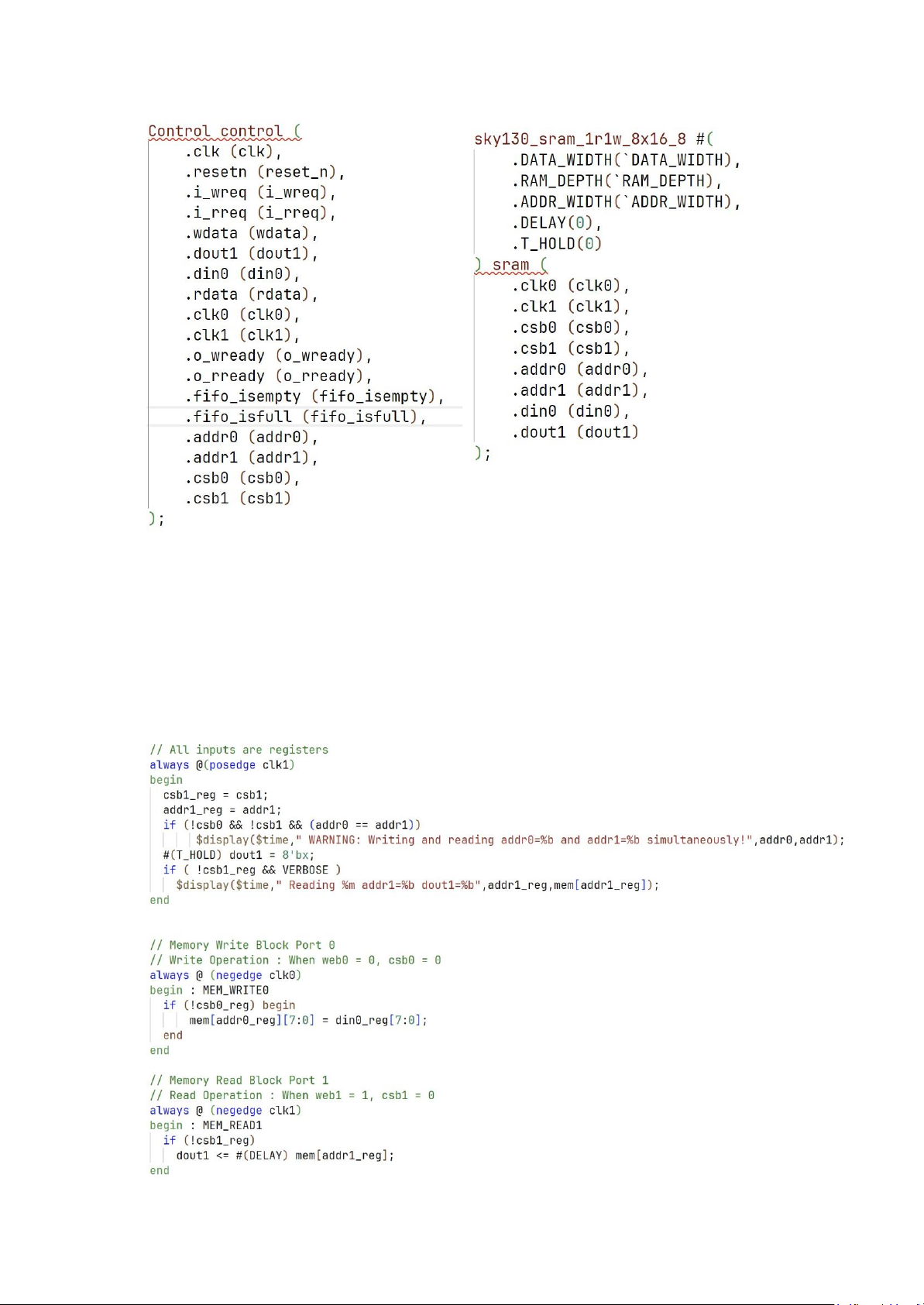

Module top gồm 2 sub module là Control và RAM, module RAM được

được CoAsia cấp, là thư viện OpenRAM được tạo dựa trên thư viện PDK

SKY130nm, ta chỉ cần thiết kế khối Control để điều khiển đọc, ghi trên RAM

Module RAM thực hiện nhận dữ liệu đầu vào là data và địa chỉ ở sườn dương, và

thực hiện đọc ghi tại sườn âm của clk

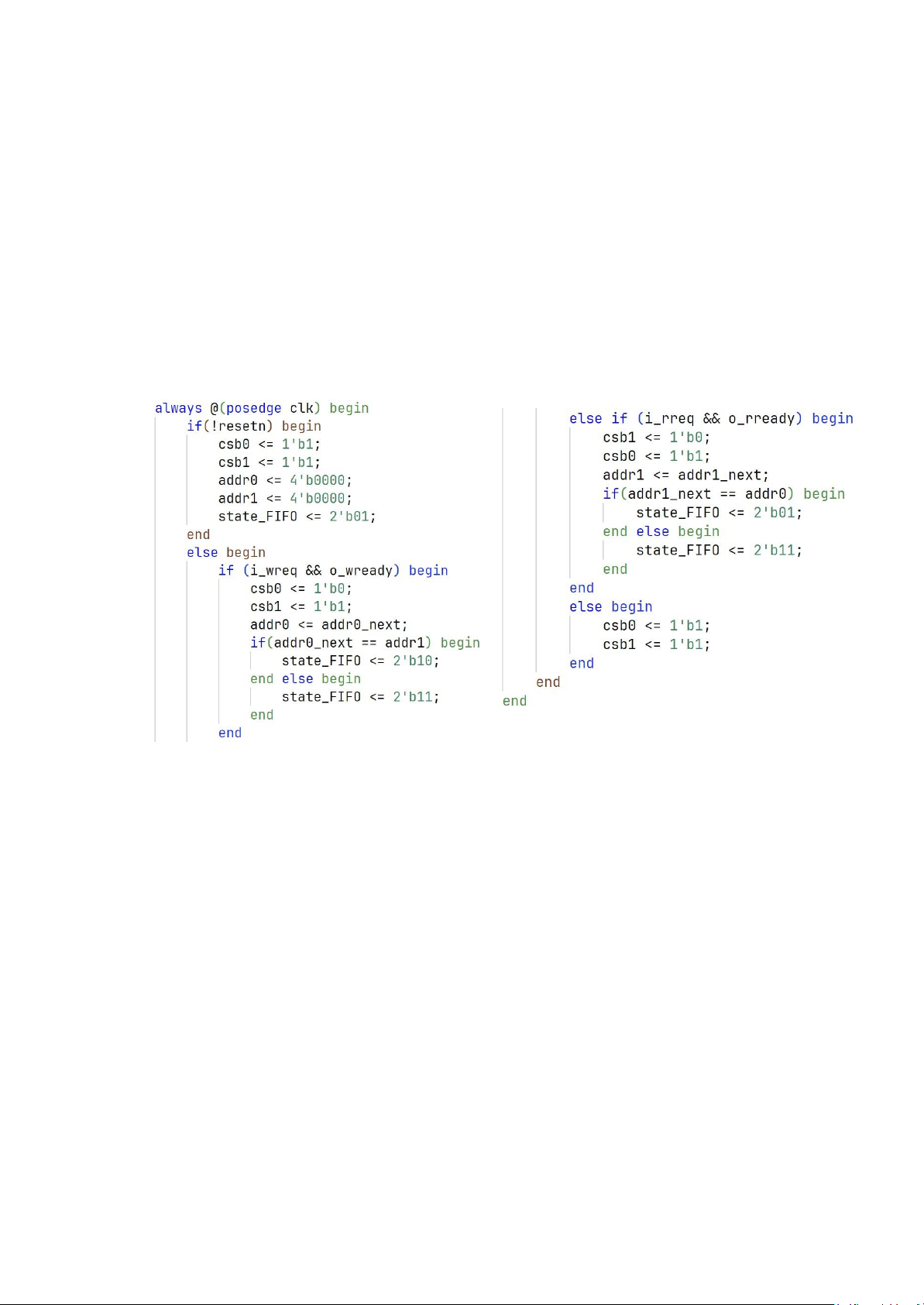

Module Control xậy dựng các khối sequential điều khiển và tính toán trạng thái

FIFO và giá trị địa chỉ để đưa cho RAM,

● Sau khi reset, FIFO sẽ xóa dữ liệu về trạng thái empty

● Tín hiệu điều khiển ghi vào RAM khi tín hiệu i_wreq và o_wready đều bằng I

● Tín hiệu điều khiển đọc vào RAM khi tín hiệu i_rreq và o_rready đều bằng I

● Khối Control sẽ gửi tín hiệu csb để điều khiển và addr để chỉ ô nhớ được đọc,ghi

dữ liệu, trên 2 port0 (ghi) và port1 (đọc) của RAM,

● Cập nhật trạng thái của FIFO trên mỗi sườn dương của clk

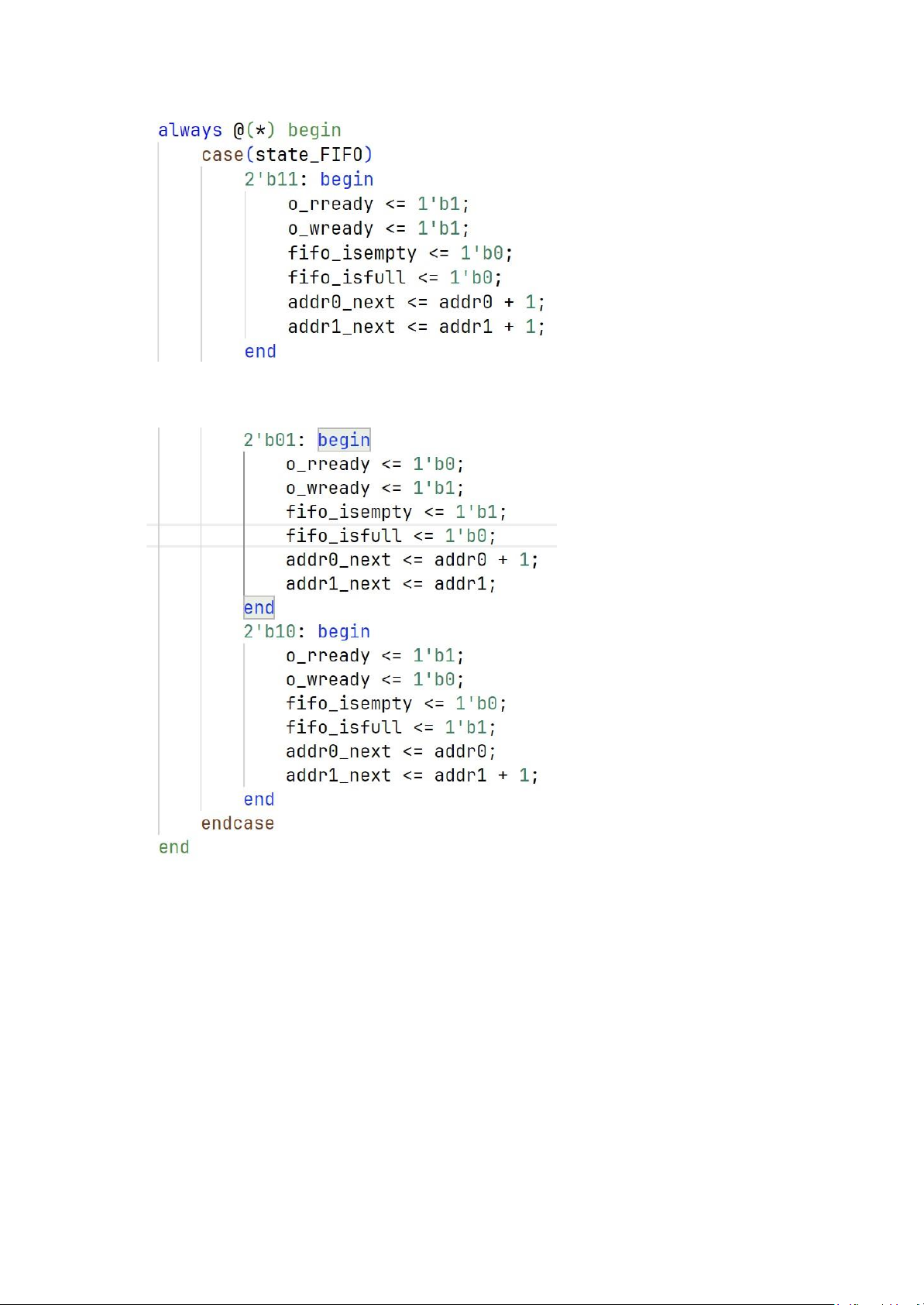

Trạng thái của FIFO gồm 3 state:

● FIFO_DONE: FIFO có thể đọc và ghi, các tín hiệu fifo_empty = fifo_full = 0, 0_wready

= o_rready = 1, các địa chỉ lưu data là địa chỉ ngay sau ô nhớ vừa thực hiện cùng chức năng addr = addr + 1;

● FIFO_EMPTY: FIFO chỉ có thể ghi, các tín hiệu fifo_empty = 1, fifo_full = 0, 0_wready =1, o_rready = 0,

● FIFO_FULL: FIFO chỉ có thể ghi, các tín hiệu fifo_empty =o, fifo_full =1, 0_wready = 0 , o_rready = 1,

IV. KIỂM THỬ CHỨC NĂNG

Kiểm thử thiết kế số là quá trình kiểm tra và đánh giá sự đúng đắn và chức năng

của hệ thống hoặc thiết kế số trước khi được triển khai và đưa ra sử dụng. Đây là

một khâu thiết yếu trong quá trình phát triển và các hệ thống số và đóng vai trò

quan trọng trong việc đảm bảo hệ thống đó đáp ứng được các yêu cầu thiết kế

(specification) và các tiêu chuẩn về thiết kế.

Mục tiêu của quá trình kiểm thử thiết kế số nhằm phát hiện cũng như loại bỏ các

lỗi phát sinh trong quá trình thiết kế, đảm bảo hệ thống thực hiện được theo đúng

yêu cầu, chức năng ở các trường hợp và điều kiện khác nhau. Quá trình đó bao

gồm việc tạo ra một môi trường kiểm thử có thể mô phỏng các trường hợp khác

nhau và kiểm tra được hoạt động của hệ thống ở các điều kiện khác nhau.

Các pha trong kiểm thử thiết kế số

Các pha khác nhau trong kiểm thử thiết kế có thể khác nhau, phụ thuộc vào việc sử

dụng phương pháp hay luồng kiểm thử cụ thể nào đó. Tuy nhiên, các pha trong

kiểm thử đều có những điểm chung, có thể kể đến:

● Lên kế hoạch kiểm thử (Planning): Ở pha này, các mục tiêu hay phạm vi kiểm thử

được xác định và kế hoạch kiểm thử được phát triển.

● Phát triển testbench (Testbench development): Pha này cung cấp việc phát triển

một môi trường kiểm thử có thể mô phỏng được thiết kế cũng như cung cấp các

đầu vào phù hợp cho việc kiểm thử.

● Tạo kiểm thử (Test creation): Trong giai đoạn này, các thử nghiệm được tạo dựa

trên các yêu cầu và kịch bản được chỉ ra trong kế hoạch kiểm thử.

● Thực hiện kiểm thử (Test execution): Các kiểm thử được tạo ở giai đoạn trước được

thực hiện trên thiết kế và kết quả sau đó được phân tích.

● Gỡ lỗi (Debugging): Giai đoạn này liên quan đến việc xác định và giải quyết mọi vấn

đề về thiết kế hoặc lỗi được phát hiện trong các giai đoạn trước.

Xây dựng testplan cho thiết kế

● Kiểm tra đọc ghi dữ liệu chung

○ Thực hiện ghi dữ liệu 5 lần liên tiếp

○ Thưc hiện đọc dữ liệu 3 lần liên tiếp

○ Kiểm tra 3 data đọc có khớp với ghi hay không

● Kiểm tra hoạt động của mạch khi reset ○ Đọc và ghi 1 lần ○ Reset mạch

○ Kiểm tra mạch có empty không, dữ liệu đã xoas chưa

● Kiểm tra trạng thái full của FIFO

○ Thực hiện ghi 16 lần liên tiếp

○ Kiểm tra mạch có full không,

○ Thực hiện ghi tiếp xem trạng thái mạch như thế nào

● Kiểm tra trạng thái empty của FIFO ○ Thưc hiện ghi 3 lần

○ Thực hiện đọc 3 lần

○ Kiểm tra mạch có empty không

○ Thực hiện đọc tiếp để xem trạng thái mạch

● Kiểm tra random để check khả năng lưu lâu dài

○ Thực hiện random tín hiệu điều khiển đọc ghi nhiều lần để check trạng thái mạch

trong hoạt động trong nhiều chu kỳ

Xây dựng testbench

Testbench gen tín hiệu clk, tạo các tín hiệu đầu vào cho dut và quan sát kết quả

đầu ra để kiểm tra bằng waveform và transcript

Tiến hành viết hàm điều khiển đọc ghi cho testbench

Viết task tạo sequence theo testplan và tạo xung clk cho mạch

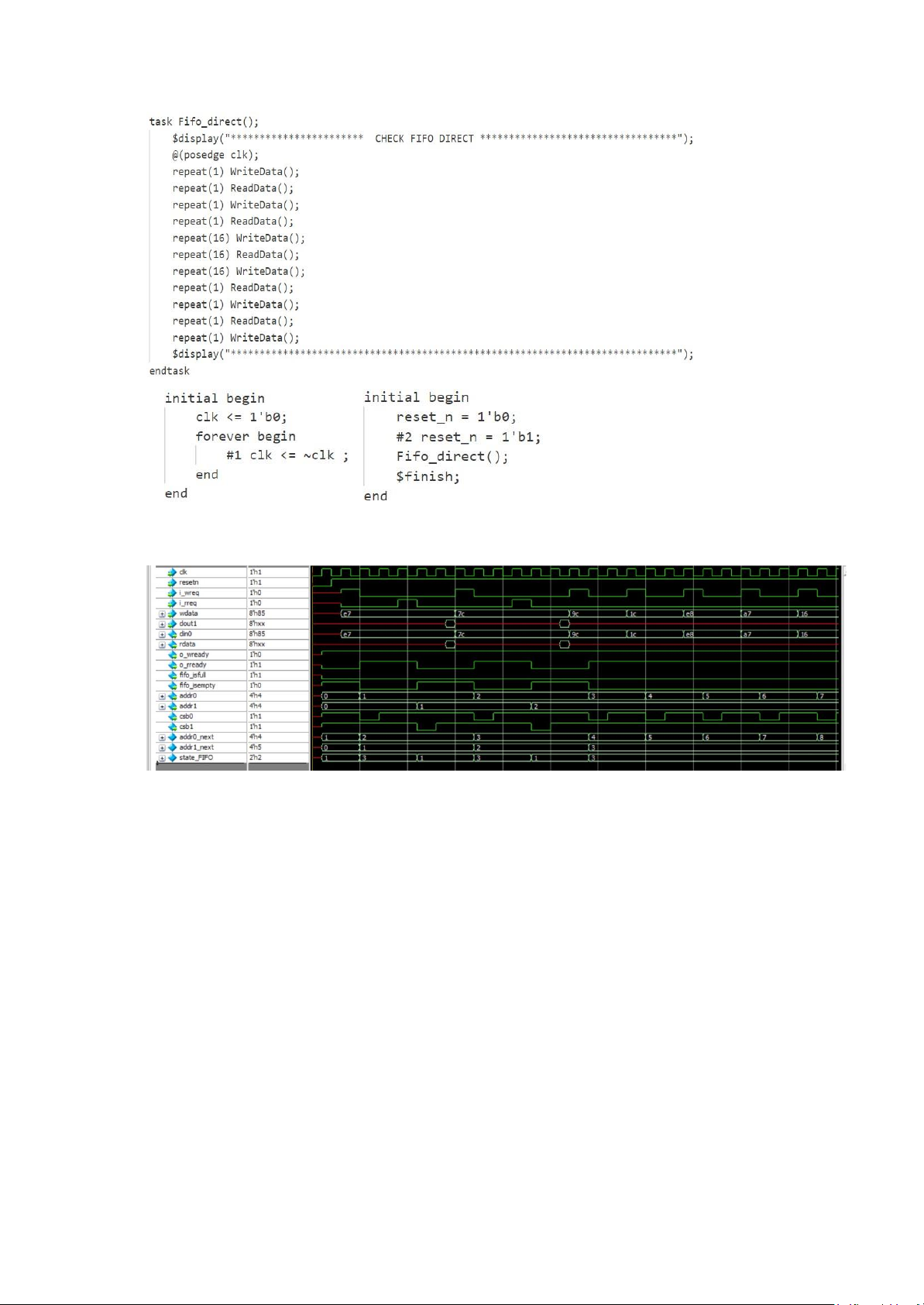

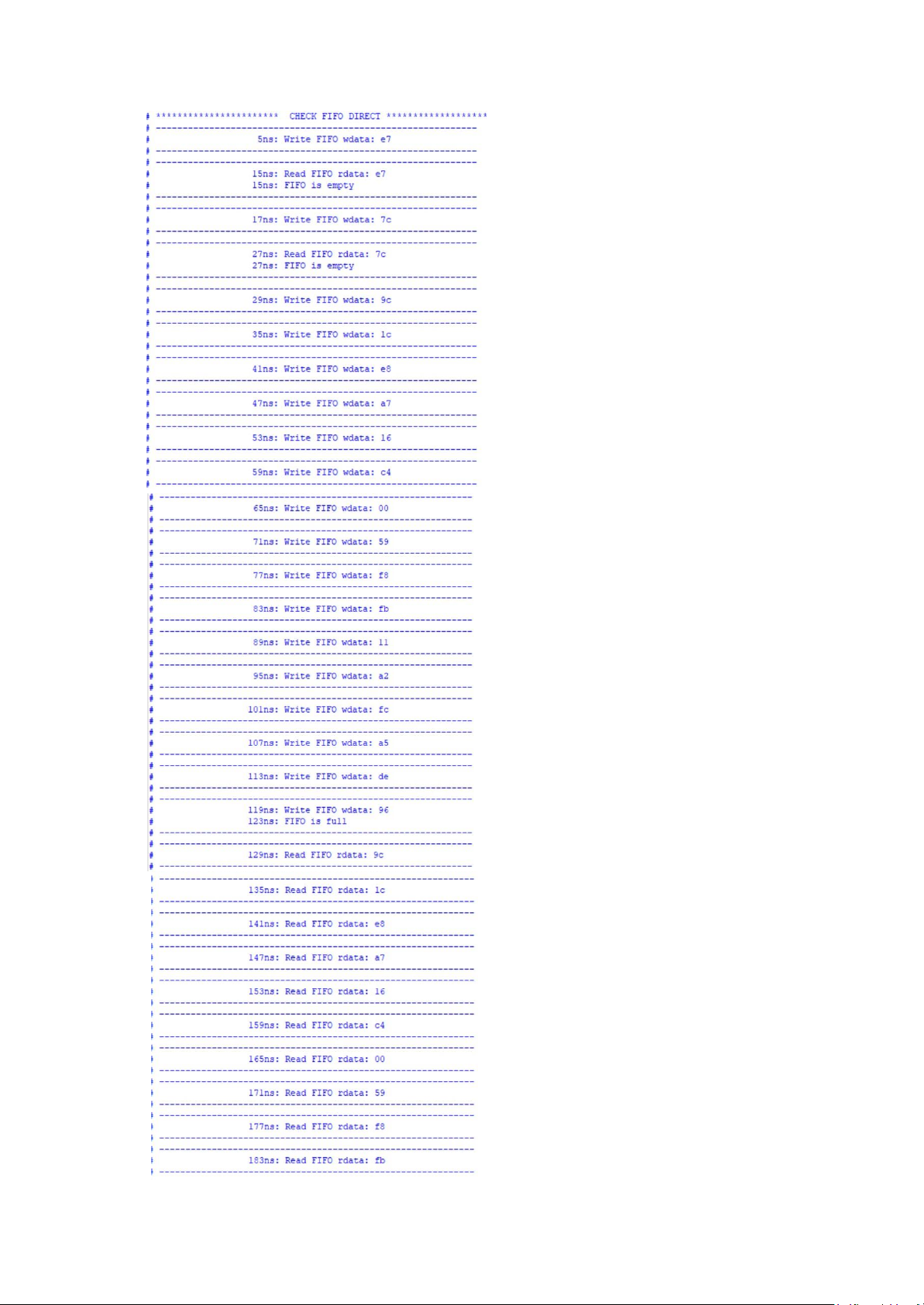

Kết quả đạt được khi chạy mô phỏng trên QuestaSim

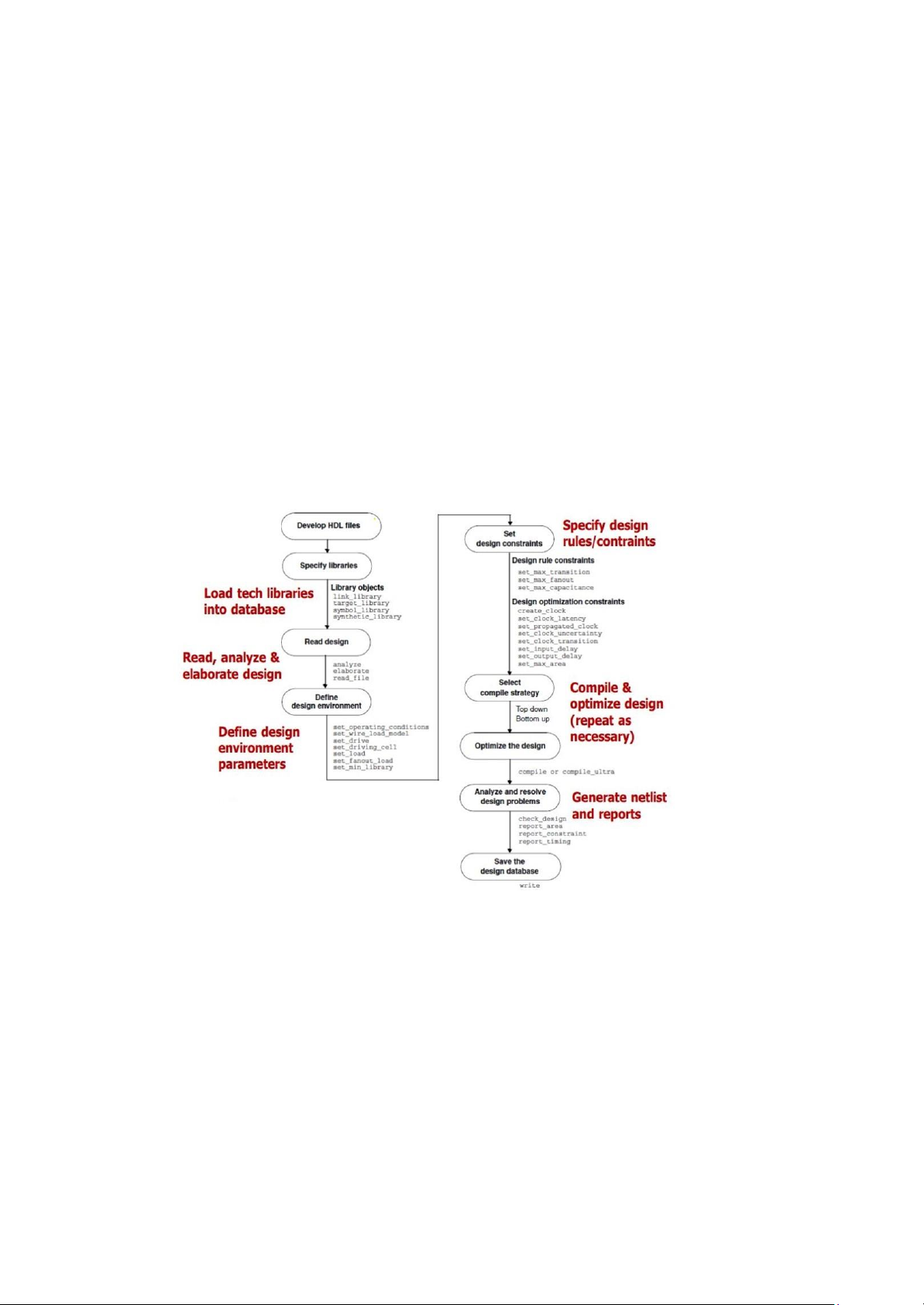

IV. Triển khai flow back_end cho thiết kế

Systhesis - Static Time Analyst

Tổng hợp logic là quá trình chuyển đổi code RTL thành dạng code ở mức thấp

hơn. Cụ thể là chuyển code về các cổng logic được thiết kế sẵn.

● Mục tiêu của tổng hợp logic ○ Tạo ra được Gate-level Nestlist.

○ Chèn cổng logic để tối ưu về mặt năng lượng, chặn tín hiệu clock đi vào 1 module

○ Tối ưu về mặt logic: tối giản các mạch logic để mạch nhỏ hơn, giảm cổng logic để tăng tốc độ xử lý.

○ Chèn DFT logic: chèn thêm mạch test sau khi con chip được sản xuất ra sau khi sản

xuất không thể mô phỏng để test trên chip được mà phải test trực tiếp trên con

chip. Việc chèn con chip DFT có thể giúp test con chip sau khi sản xuất.

● Quy trình tổng hợp diễn ra theo các bước sau:

● Đầu vào của Synthesis

○ Code RTL (các file HDL) ○ Library ○ Constraints ○ UPF

● Đầu ra của Synthesis ○ Net list

○ Reports (Area, Timing etc. )

○ UPF: Unified Power Format ● Các chiến lược tối ưu.

● Biên dịch từ dưới lên: Các thiết kế riêng lẻ được biên dịch riêng biệt, bắt dầu từ

phần dưới cùng của phân cấp hệ thống và tiếp tục đi lên qua các cấp độ của phân

cấp hệ thống cho đến khi thiết kế cấp cao được biên dịch tốt nhất.

● Biên dịch hợp nhất: Chiến lược từ trên xuống hoặc từ dưới lên, tùy chọn nào phù

hợp nhất được áp dụng cho các thiết kế riêng lẻ.

Phân tích thời gian tĩnh là một kĩ thuật kiểm tra trong mạch số. Nó sẽ xác minh bản

thiết kế có thể hoạt động ở mức thời gian hạn chế mà mình đã đặt ra hay không

● Các bước chính trong STA

○ B1. Chia thiết kế thành các thời gian tập hợp các đường dẫn.

○ B2. Tính toán từng đường dẫn

○ B3. Kiểm tra tốc độ của đường dẫn để xem liệu các dữ liệu rõ ràng về thời gian đã

chọn phải là meta không. ● Dữ liệu vào: ○ Gate-level Netlist ○ Libraries ● Dữ liệu ra ○ SDF ○ Parasitics ○ Design constraints Physical Design

Đây là quá trình chuyển đổi mô tả logic ở mức trừu tượng thành một mô tả hình

thức của mạch điện tử. Quá trình này tập trung vào việc đặt và kết nối các thành

phần logic trên một chip dể đảm bảo hiệu suất , độ tin cậy của mạch.

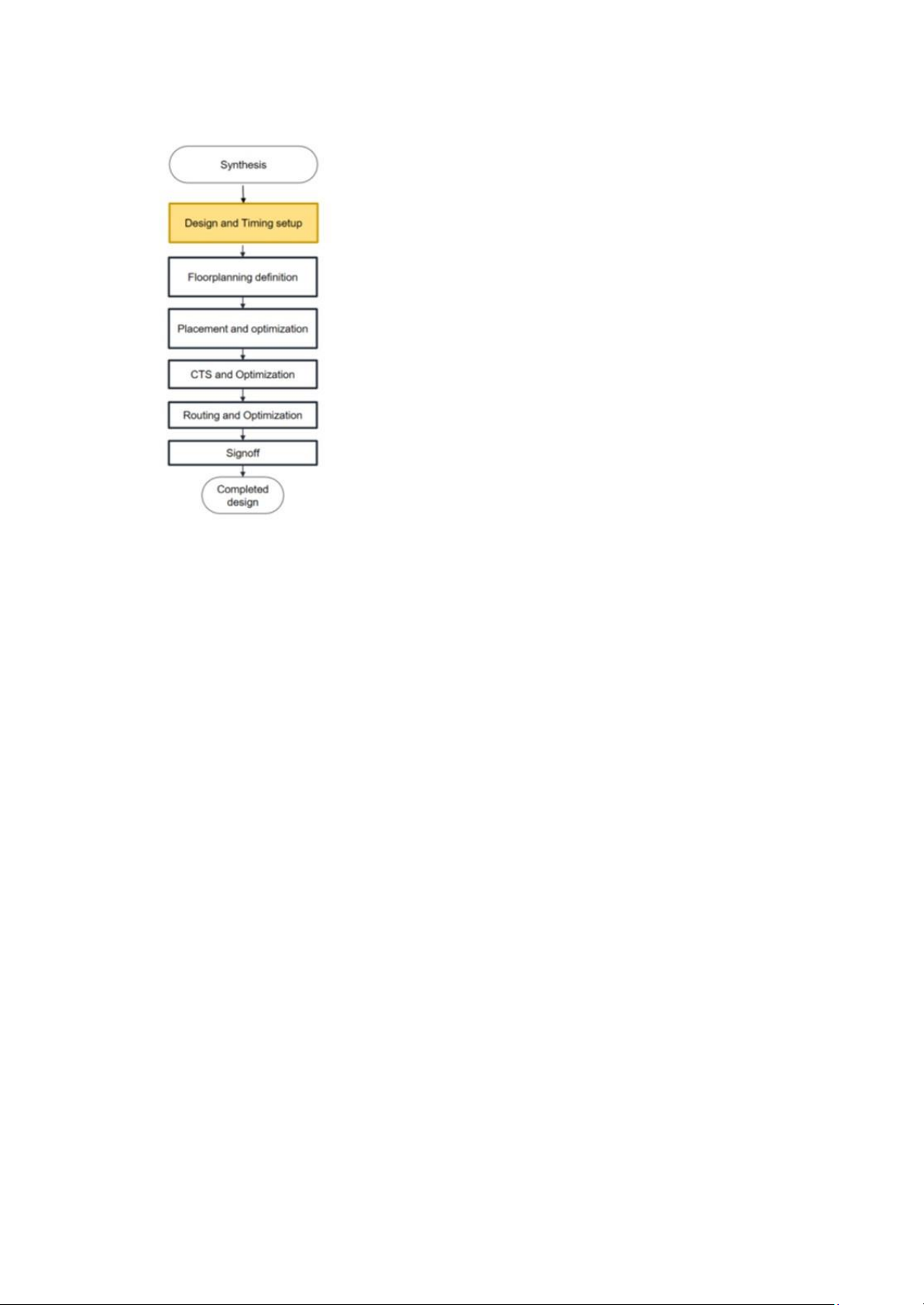

Quy trình bản vẽ vật lý

B1. Design and Timing setup

Trước khi tạo bản vẽ vật lý ta cần chuẩn bị: ● Gate level design

● Logical & Physical libraries ● Timing constraints

● Physical Design constraints.

B2. Floorplanning & Powerplanning

Xác định vị trí và kích thước của các khối logic trên chip để tối ưu hóa diện tích và

đáp ứng các yêu cầu về đường dây và nguồn năng lượng. Đầu vào Floorplan: ● Netlist (.v), Physical library, logical/Timing libraries,.. ● Timing constraints (.sdc)

● Power requirements: Value – PG net structure ● Control parameters: Values, Power spec