Preview text:

lOMoAR cPSD| 58675420 lOMoAR cPSD| 58675420 MỤC LỤC

CHƯƠNG 1. CƠ SỞ LÝ THUYẾT ................................................................... 1

1.1. Giới thiệu phần mềm Vivado ....................................................................... 1

1.2. Thiết kế hệ thống nhúng sử dụng IP Integrator ........................................... 1

1.3. Tạo Accelerator Phần cứng IP-XACT ......................................................... 3

1.3.1 Tạo các bộ chuyển đổi IP-XACT ........................................................... 3

1.3.2 Thêm bộ điều hợp ................................................................................... 4

1.3.3 Tích hợp Bộ điều hợp IP-XACT trong Hệ thống AXI ........................... 5

CHƯƠNG 2: THIẾT KẾ BỘ XỬ LÝ BẰNG IP-XACT ADAPTER VÀ IP

INTEGRTOR ....................................................................................................... 5

2.1. Tạo một project mới ..................................................................................... 6

2.2 Chạy mô phỏng C ....................................................................................... 14

2.3. Tổng hợp thiết kế ....................................................................................... 15

2.4. Chạy RTL/C Co-simulation ....................................................................... 19

2.5. Cấu hình Bộ chuyển đổi IP-XACT ............................................................ 20

2.6. Tạo Bộ chuyển đổi IP-XACT Adapter ...................................................... 25

2.7. Tạo Vivado Project .................................................................................... 27

2.7.1. Tạo hệ thống ban đầu cho Zedboard ................................................... 27

2.7.2. Thêm IP HLS vào danh sách IP ........................................................... 28

2.7.3. Khởi tạo core fir_top ........................................................................... 29

2.7.4. Mở các cổng PS-PL Interrupt .............................................................. 29

2.7.5. Kiểm tra địa chỉ và đánh giá thiết kế ................................................... 32

2.8. Xuất thiết kế phần cứng sang SDK và tạo Application Project ................. 34

2.8.1. Xuất thiết kế phần cứng với bitstream đã tạo sang phần mềm SDK... 34

2.9. Kiểm tra thiết kế trong phần cứng ............................................................. 36 lOMoAR cPSD| 58675420

CHƯƠNG 1. CƠ SỞ LÝ THUYẾT

1.1. Giới thiệu phần mềm Vivado.

Vivado là một phần mềm của Xilinx, được sử dụng để thiết kế và triển khai

hệ thống số trên các vi mạch lập trình được (FPGA) và hệ thống trình tự tùy chỉnh

(SoC). Đây là một công cụ mạnh mẽ cho việc phát triển phần cứng số từ các khối

logic cơ bản cho đến hệ thống nhúng phức tạp.

Vivado cung cấp một loạt các tính năng và công cụ để hỗ trợ quy trình thiết

kế FPGA và SoC. Nó bao gồm các công cụ tổng hợp, triển khai, tối ưu và kiểm tra

để tạo ra bitstream hoặc hệ thống nhúng hoàn chỉnh. Vivado hỗ trợ các ngôn ngữ

mô tả phần cứng phổ biến như VHDL và Verilog, cho phép người dùng mô phỏng,

kiểm tra và xác minh thiết kế trước khi triển khai thực tế.

Một trong những tính năng nổi bật của Vivado là IP Integrator, cho phép

người dùng thiết kế hệ thống nhúng bằng cách kết hợp các IP (Intellectual

Property) có sẵn và tạo ra một hệ thống hoàn chỉnh. Nó cung cấp giao diện đồ họa

và công cụ trực quan để kết nối, cấu hình và kiểm soát các thành phần trong hệ thống.

Vivado cũng hỗ trợ các công nghệ tiên tiến như High-Level Synthesis

(HLS), cho phép người dùng viết mã mô phỏng trên mức cao hơn và tự động tạo

ra mã RTL tương ứng. Điều này giúp tăng hiệu suất và giảm thời gian phát triển

cho các thiết kế phức tạp.

Ngoài ra, Vivado cũng cung cấp một loạt các công cụ phân tích và gỡ lỗi, cho

phép người dùng theo dõi và xác minh hoạt động của hệ thống.

Vivado là một công cụ phát triển hàng đầu trong lĩnh vực thiết kế FPGA và

SoC, được sử dụng rộng rãi trong các lĩnh vực như điện tử, viễn thông, ô tô, hàng

không vũ trụ và nhiều lĩnh vực công nghiệp khác.

1.2. Thiết kế hệ thống nhúng sử dụng IP Integrator

Chúng ta sẽ sử dụng IP Integrator để tạo thiết kế dựa trên hệ thống xử lý bao gồm:

- Bộ xử lý và thiết bị ngoại vi:

• Bộ xử lý ARM ® Cortex ™ A9 kép của Zynq 7000 AP SoC. • Mạch kết nối AXI.

• Thiết bị ngoại vi AXI. lOMoAR cPSD| 58675420

• Cổng reset, xung nhịp, gỡ lỗi.

- Nền tảng phần mềm cho hệ thống xử lý:

• Hệ điều hành độc lập. • Hỗ trợ ngôn ngữ C.

• Dịch vụ bộ xử lý.

• Các trình điều khiển C cho phần cứng.

- Ứng dụng cho người dùng:

• Các hàm dịch vụ ngắt (tùy chọn).

Về kiến trúc Zynq 7000 AP SoC bao gồm hai phần chính: - PS: Hệ thống xử lý

• Dựa trên hai bộ xử lý ARM Cortex A9 (có phiên bản đơn lõi có sẵn).

• Nhiều thiết bị ngoại vi. • Lõi nhân tạo cứng.

- PL: Hệ thống logic có thể lập trình

• Sử dụng cùng logic lập trình của dòng 7 series.

• Thiết bị dựa trên Artix: Z 7010, Z 7015 và Z 7020 (chỉ hỗ trợ các ngân hàng I/O dải cao).

• Phiên bản đơn lõi: Z 7017S, Z 7012S và Z 7014S.

• Thiết bị dựa trên Kintex: Z 7030, Z 7035, Z 7045 và Z 7100 (kết hợp các ngân

hàng I/O dải cao và hiệu suất cao).

Vivado, IP Integrator và SDK là những công cụ được sử dụng trong thiết kế FPGA

của Xilinx và phát triển hệ thống nhúng:

• Vivado là bộ công cụ cho thiết kế FPGA của Xilinx và bao gồm khả năng thiết kế hệ thống nhúng.

• IP Integrator là một phần của Vivado và cho phép thiết kế cấp block cho phần

cứng của một hệ thống nhúng.

• Nó được tích hợp vào Vivado và bao gồm tất cả các công cụ, IP và tài liệu cần

thiết cho việc thiết kế hệ thống với nhân cứng Zynq 7000 AP SoC và/hoặc bộ

xử lý mềm MicroBlaze của Xilinx. lOMoAR cPSD| 58675420

• Vivado + IPI thay thế cho ISE/EDK.

Vivado là quản lý dự án chung và được sử dụng để phát triển phần cứng không nhúng

và triển khai hệ thống nhúng.

• Quy trình Vivado/IP Integrator được khuyến nghị cho việc phát triển hệ thống nhúng Zynq.

SDK là một môi trường thiết kế phần mềm dựa trên Eclipse.

• Nó cho phép tích hợp các thành phần phần cứng và phần mềm. • Liên kết từ Vivado.

1.3. Tạo Accelerator Phần cứng IP-XACT

1.3.1 Tạo các bộ chuyển đổi IP-XACT

Danh sách các bộ chuyển đổi có thể tham khảo Type Core Name Description AX14 AX14M AX14 Master Interface AX14Stream AX14 Stream Interface AX14LiteS AX14Lite Slave Interface Trong đó: -

AX14M: Được chỉ định trên mảng và con trỏ (và tham chiếu trong C++) mà

thôi. Chúng ta có thể nhóm nhiều đối số vào cùng một giao diện AXI4 Lite bằng

cách sử dụng tùy chọn bundle. -

AX14Stream: Được chỉ định trên đối số đầu vào hoặc đầu ra, không được

chỉ định trên đối số đầu vào/đầu ra. -

AX14LiteS: Được chỉ định trên bất kỳ loại đối số nào trừ mảng. Chúng ta

có thể nhóm nhiều đối số vào cùng một giao diện AXI4 Lite bằng cách sử dụng tùy chọn bundle.

Khi mảng là một đối số của hàm cấp cao:

• Mảng/RAM nằm "ngoài chip".

• Loại tài nguyên xác định các cổng IO cấp cao.

Thêm bộ chuyển đổi vào RTL và tạo giao diện bus: lOMoAR cPSD| 58675420

• Nguyên tắc là tương tự.

• Chúng ta định nghĩa một tài nguyên cho cổng.

• Ngoài ra còn một số tùy chọn khác chúng ta sẽ trình bày.

1.3.2 Thêm bộ điều hợp

1.3.2.1 Kiểm tra RTL & C IO

Bước đầu tiên trong việc thêm một bộ chuyển đổi:

- Đảm bảo bạn có một cổng phù hợp trên RTL. - Ví dụ:

• Nếu bạn muốn có một giao diện AXI Stream → cổng phải có ap_fifo trên RTL.

• Nếu cần ap_fifo trên RTL → truyền con trỏ biến, mảng hoặc biến tham chiếu

(trong, ra, nhưng không phải trong/ra).

1.3.2.2 Gắn Adapter Core cho mỗi Port Sau

khi biết được I/O adapter:

• Thêm core như một tài nguyên vào cổng RTL.

Các core được liệt kê trong Hướng dẫn Thư viện Vivado HLS:

• Và có sẵn từ menu trong giao diện đồ họa (GUI).

1.3.2.3 Tùy chọn nhóm và đổi tên các bus Nhóm bus metadata.

• Cho phép nhóm các bus với tên mới.

• Nhiều tài nguyên có thể có cùng tên.

• Sẽ được nhóm vào cùng một bus. Ánh xạ tên cổng.

• Tùy chọn, cổng có thể được ánh xạ tên trong trường port map. o {{output}

{output_hs_vld, output_ap_ack}}

• Tên cổng RTL được đổi tên trên giao diện bộ chuyển đổi.

1.3.2.4 Tạo bộ chuyển đổi

• Chọn Solution > Export RTL. lOMoAR cPSD| 58675420

• Chọn IP Catalog, System Generator for Vivado hoặc PCore for EDK.

• Nhấp vào Configuration... nếu bạn muốn thay đổi số phiên bản hoặc thông tin khác.

o Phiên bản mặc định là v1_00_a. • Nhấp vào OK.

o Thư mục (ip) sẽ được tạo ra dưới thư mục impl trong thư mục dự án

hiện tại và giải pháp hiện tại.

o Chỉ mã RTL trong Verilog sẽ được tạo ra, ngay cả khi bạn chọn ngôn ngữ VHDL.

1.3.3 Tích hợp Bộ điều hợp IP-XACT trong Hệ thống AXI

• Tạo một dự án Vivado mới hoặc mở một dự án đã có.

• Thiết lập cài đặt IP để trỏ đến IP được xuất bằng Cài đặt Dự án.

• Kích hoạt IP Integrator.

• Xây dựng hoặc sửa đổi phần cứng của thiết kế nhúng bằng cách thêm adapter

IP-XACT đã tạo trong Vivado HLS.

• Tạo (Cập nhật) wrapper HDL cấp cao nhất.

• Tổng hợp và triển khai trong Vivado.

• Xuất mô tả phần cứng và khởi chạy SDK.

• Cài đặt kho phần mềm để trỏ đến IP đã tạo nếu cần thiết.

• Tạo một gói hỗ trợ bo mạch phần mềm mới [hoặc cập nhật một gói đã tồn tại]

để bao gồm trình điều khiển cho IP.

• Tạo một dự án ứng dụng trong SDK.

• Biên dịch phần mềm bằng trình biên dịch chéo GNU trong SDK.

• Tải xuống bitstream đã hoàn thành của logic có thể lập trình.

• Sử dụng SDK để tải chương trình (tệp ELF).

CHƯƠNG 2: THIẾT KẾ BỘ XỬ LÝ BẰNG IP-XACT ADAPTER VÀ IP INTEGRTOR

Thiết kế được sử dụng trong bài báo cáo này bao gồm bộ lọc FIR được dùng để

lọc âm có cao độ 4 KHz được thêm vào âm nhạc chất lượng CD. Đặc tính của bộ lọc như sau: lOMoAR cPSD| 58675420 - FS=48000 Hz - FPASS1=2000 Hz - FSTOP1=3800 Hz - FSTOP2=4200 Hz - FPASS2=6000 Hz - APASS1=APASS2=1 dB - ASTOP=60 dB

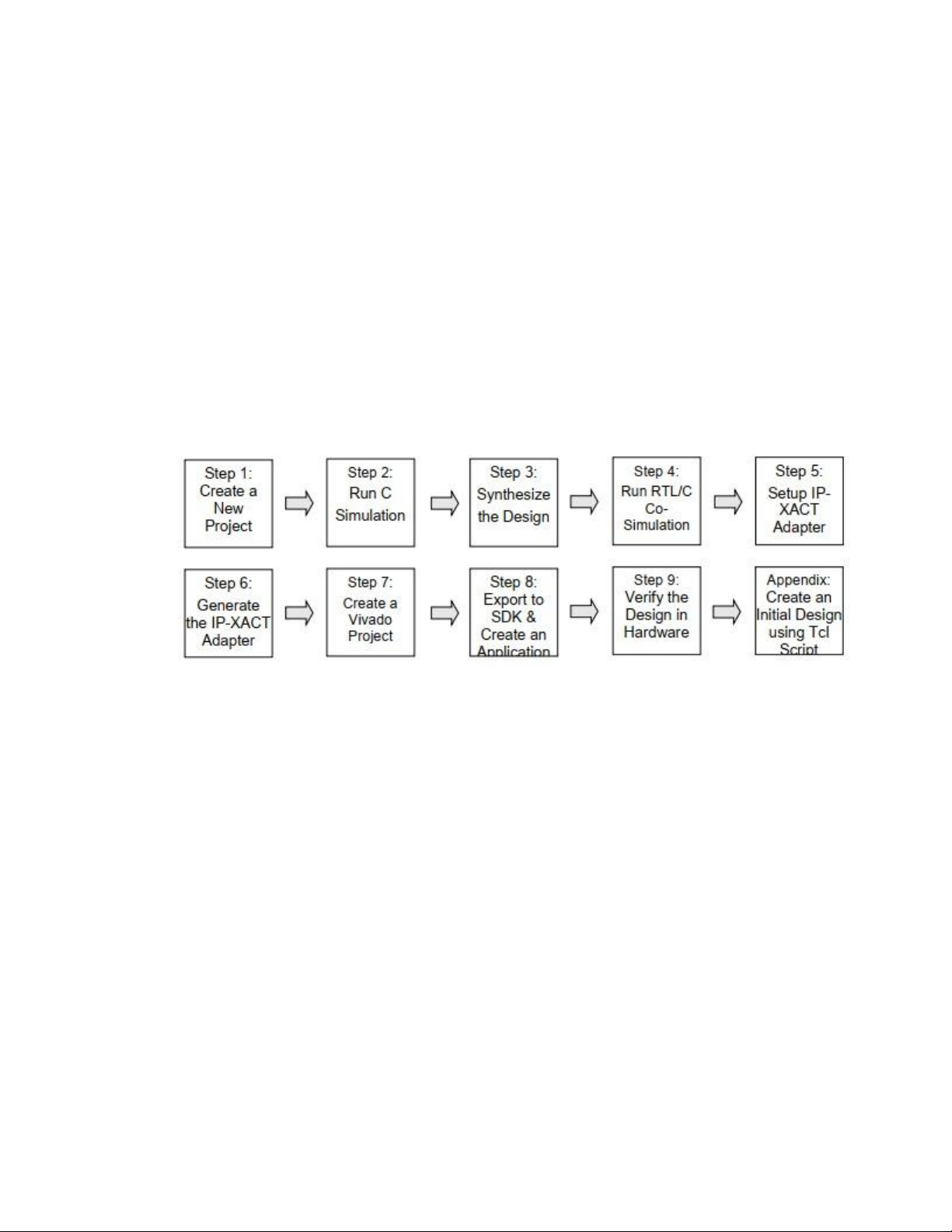

Sơ đồ tổng quan các bước thực hiện project với ZedBoard:

Hình 2.1 Sơ đồ tổng quan

2.1. Tạo một project mới

Bước 1: Tạo một project mới trong Vivado HLS sử dụng XC7Z020CLG484-1 (ZedBoard).

Bước 2: Khởi chạy Vivado HLS: Chọn Start > All Programs > Xilinx Design Tools

> Vivado 2017.4 > Vivado HLS > Vivado HLS 2017.4

Giao diện Getting Started sẽ xuất hiện. lOMoAR cPSD| 58675420

Hình 2.2. Vivado HLS Welcome Page

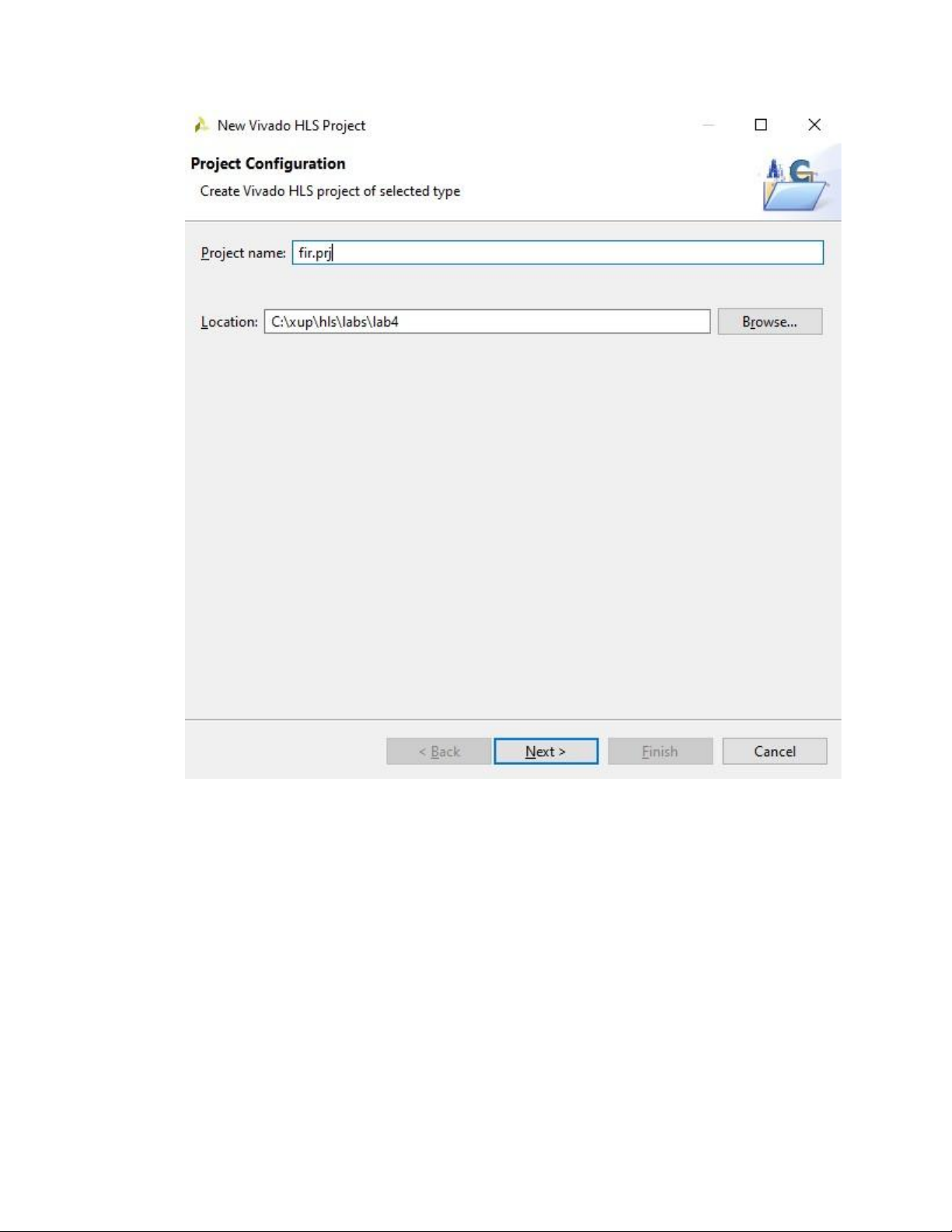

Bước 3: Trong phần Getting Started, nhấp vào Create New Project. Cửa sổ New

Vivado HLS Project wizard sẽ mở ra.

Bước 4: Nhấp vào nút Browse... của trường Location, duyệt đến thư mục

c:\xup\hls\labs\lab4, sau đó nhấp vào OK. Bước 5: Đối với Project Name, gõ fir.prj lOMoAR cPSD| 58675420

Hình 2.3. Cửa sổ New Vivado HLS Project Bước 6: Nhấp vào Next.

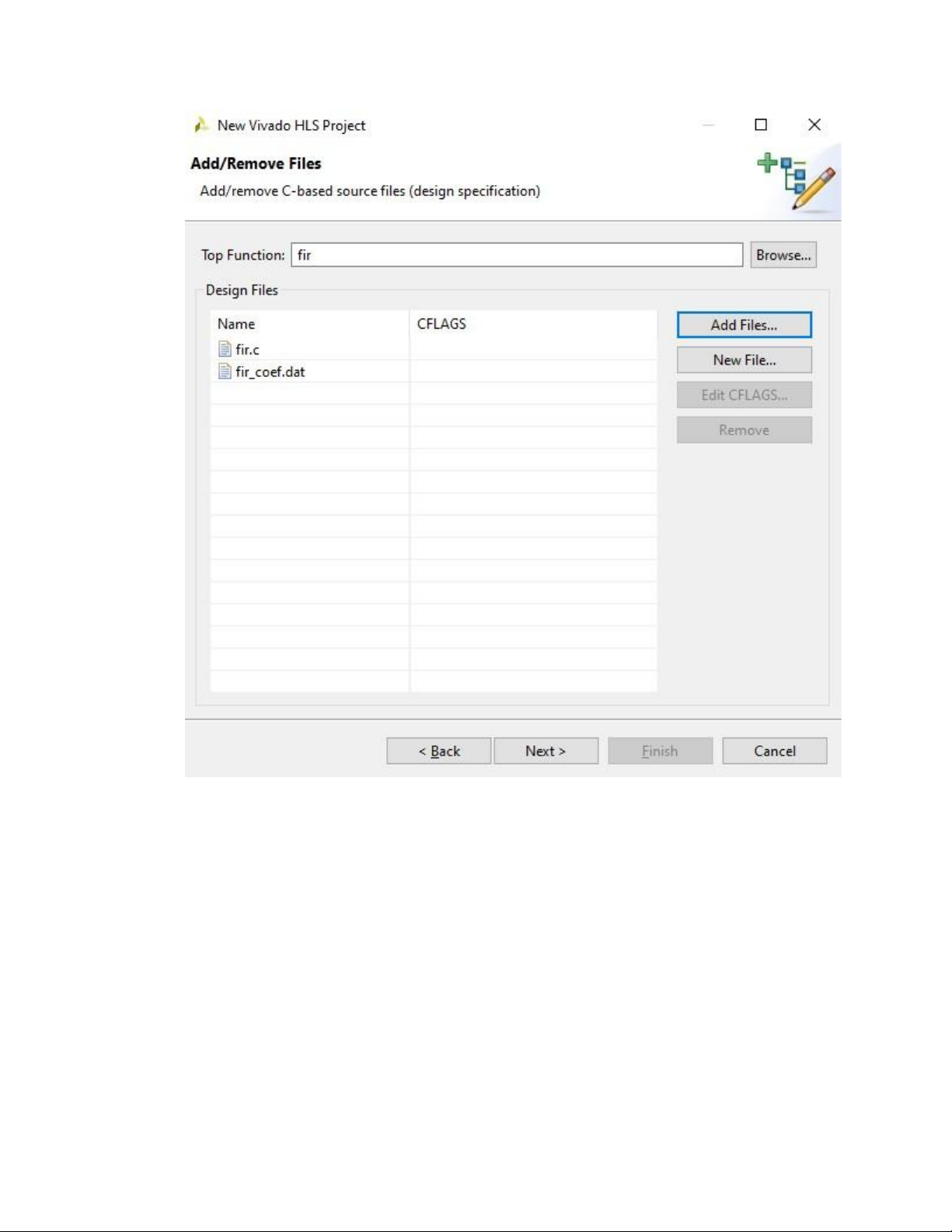

Bước 7: Trong mục Add/Remove Files cho các tệp nguồn, gõ fir là tên hàm

Bước 8: Nhấp vào nút Add Files..., chọn tệp fir.c và fir_coef.dat từ thư mục

c:\xup\hls\labs\lab4, sau đó nhấp Open. lOMoAR cPSD| 58675420

Hình 2.4. Add/Remove Files cho các Source file Bước 9: Nhấp vào Next.

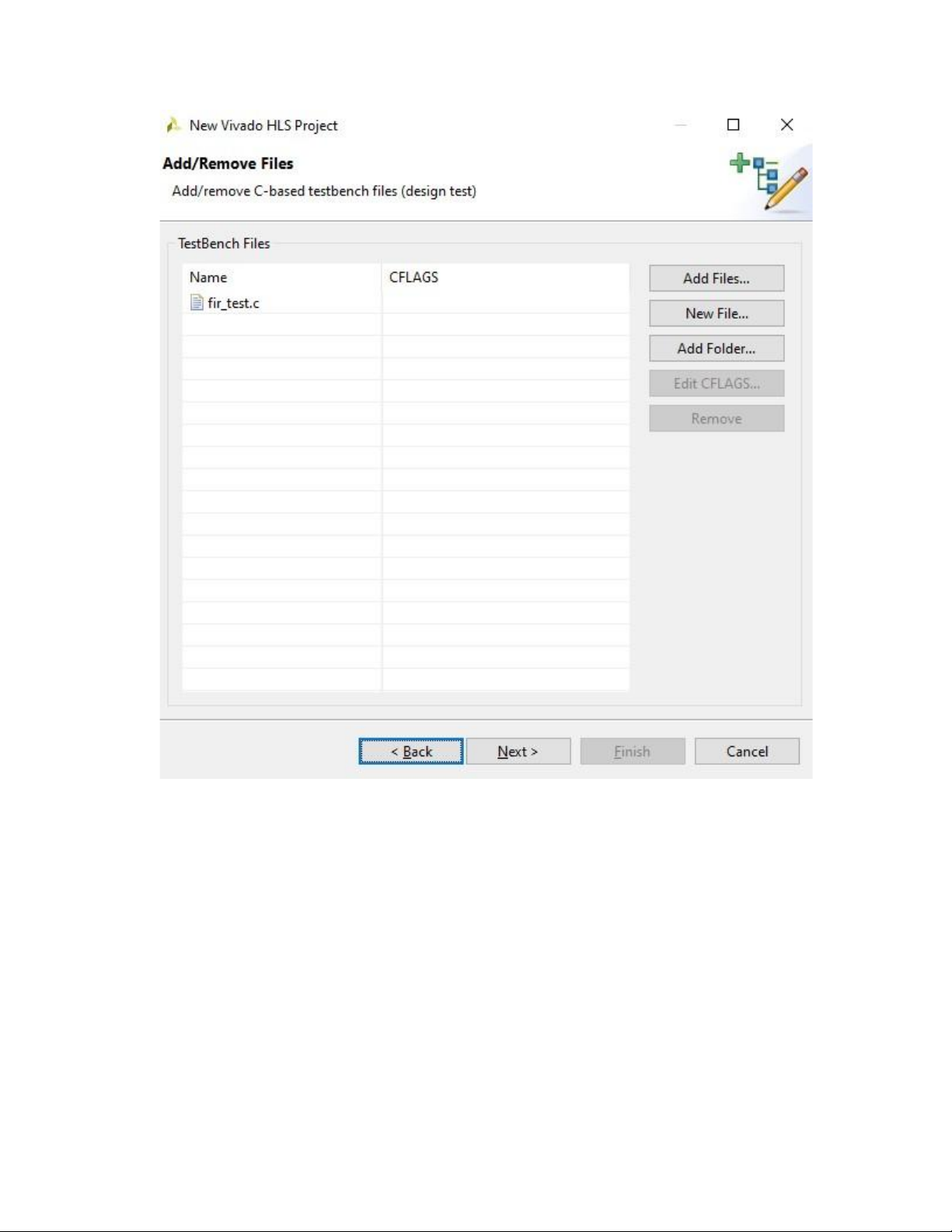

Bước 10: Trong mục Add/Remove Files cho testbench, nhấp vào nút Add Files...,

chọn tệp fir_test.c từ thư mục c:\xup\hls\labs\lab4 và nhấp Open. lOMoAR cPSD| 58675420

Hình 2.5. Add/Remove Files cho Testbench Bước 11: Nhấp vào Next.

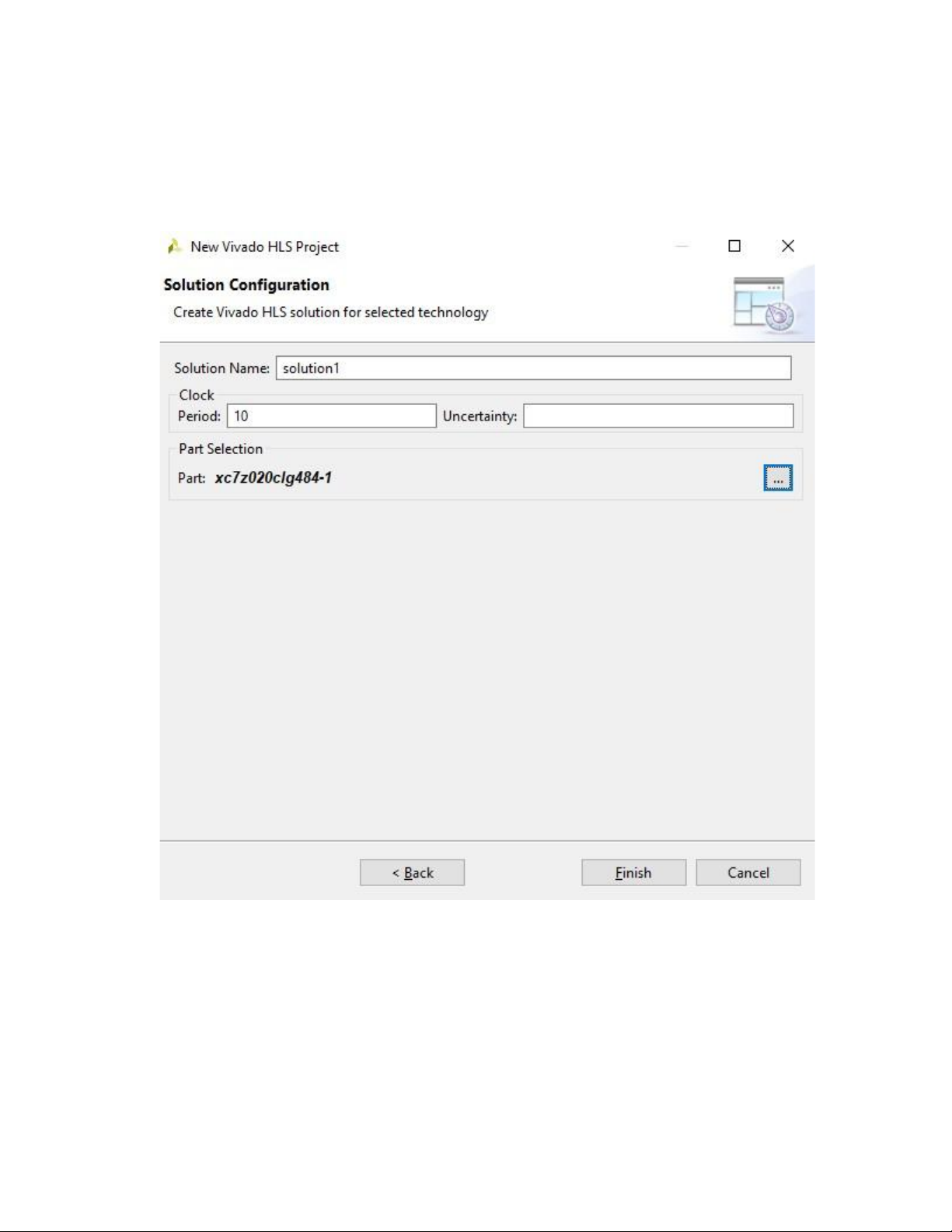

Bước 12: Trong trang Solution Configuration, để trường Solution Name là

solution1 và đặt chu kỳ clock là 10 cho ZedBoard. Để trường Uncertainty trống vì

nó sẽ lấy giá trị mặc định là 1.25 cho ZedBoard.

Bước 13: Nhấp vào nút Browse của Part và chọn các bộ lọc sau đây, sử dụng tùy chọn

Parts Specify, để chọn xc7z020clg484 sau đó nhấp vào OK: Family: Zynq lOMoAR cPSD| 58675420 Sub-Family: Zynq

Package: clg484 (ZedBoard) hoặc clg400 (Zybo) Speed Grade: -1

Hình 2.6. Cấu hình solution

Bước 14: Nhấp vào Finish.

Ta sẽ thấy project đã được tạo trong chế độ xem Explorer. Mở rộng các thư mục con

khác nhau để xem các mục trong từng thư mục con. lOMoAR cPSD| 58675420

Hình 2.7. Cửa sổ làm việc Vivado HLS

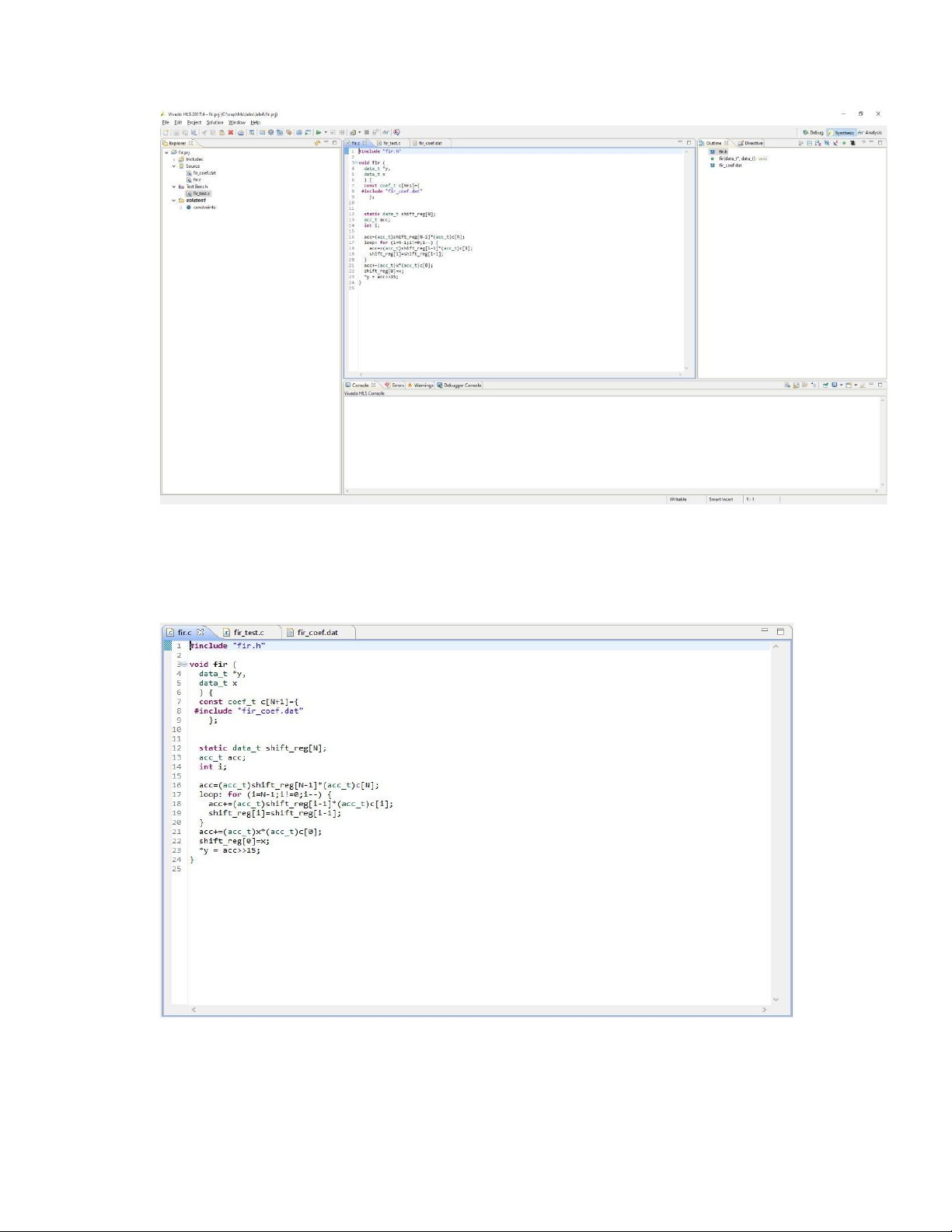

Bước 15: Nhấp đúp vào tệp fir.c trong thư mục nguồn để mở nội dung của nó trong bảng thông tin.

Hình 2.8. Thiết kế của bộ lọc FIR được sử dụng lOMoAR cPSD| 58675420

Bộ lọc FIR mong đợi đầu vào x là một mẫu và con trỏ đến mẫu đã tính toán là

sample out. Cả hai đều được xác định kiểu dữ liệu data_t. Các hệ số được tải vào

mảng c có kiểu dữ liệu coef_t từ tệp được gọi là fir_coef.dat nằm trong thư mục

hiện tại. Thuật toán tuần tự được áp dụng và giá trị tích lũy (sample out) được tính

toán trong biến acc có kiểu dữ liệu acc_t.

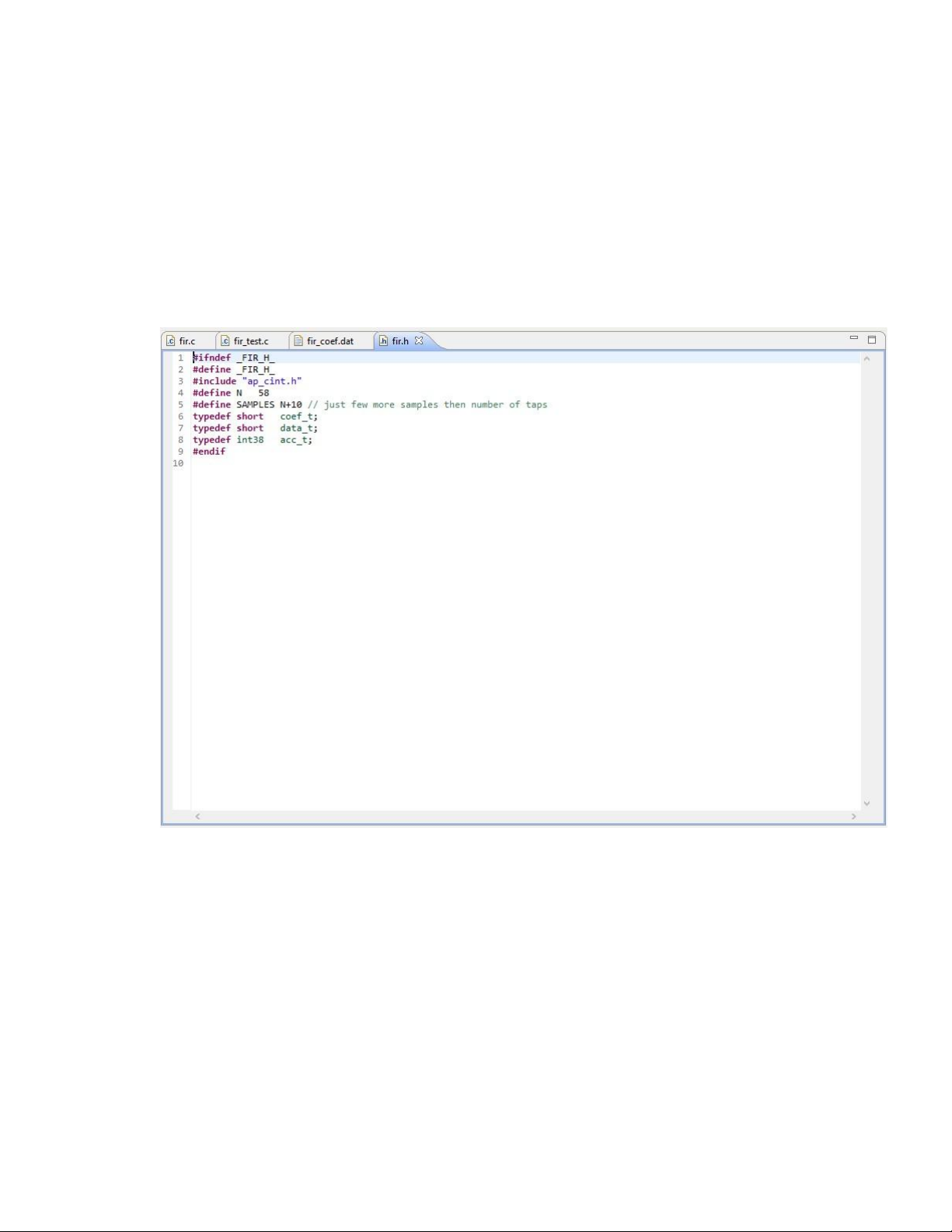

Bước 16: Nhấp đúp vào fir.h trong tab đại diện để mở nội dung của nó trong bảng thông tin. Hình 2.9. File header

Tệp tiêu đề bao gồm ap_cint.h để có thể sử dụng độ rộng dữ liệu do người dùng xác

định (có độ chính xác tùy ý).

Nó cũng xác định số lượng taps (N), số lượng mẫu được tạo ra (trong testbench),

và các kiểu dữ liệu coef_t, data_t và acc_t. Kiểu dữ liệu coef_t và data_t là ngắn

(16 bit). Vì thuật toán lặp lại (nhân và tích lũy) qua 59 taps, có khả năng tăng số

bit lên 6 bit và do đó acc_t được xác định là int38. Vì acc_t lớn hơn độ rộng mẫu lOMoAR cPSD| 58675420

và hệ số, chúng phải được chuyển đổi trước khi sử dụng (như trong dòng 16, 18 và 21 của fir.c).

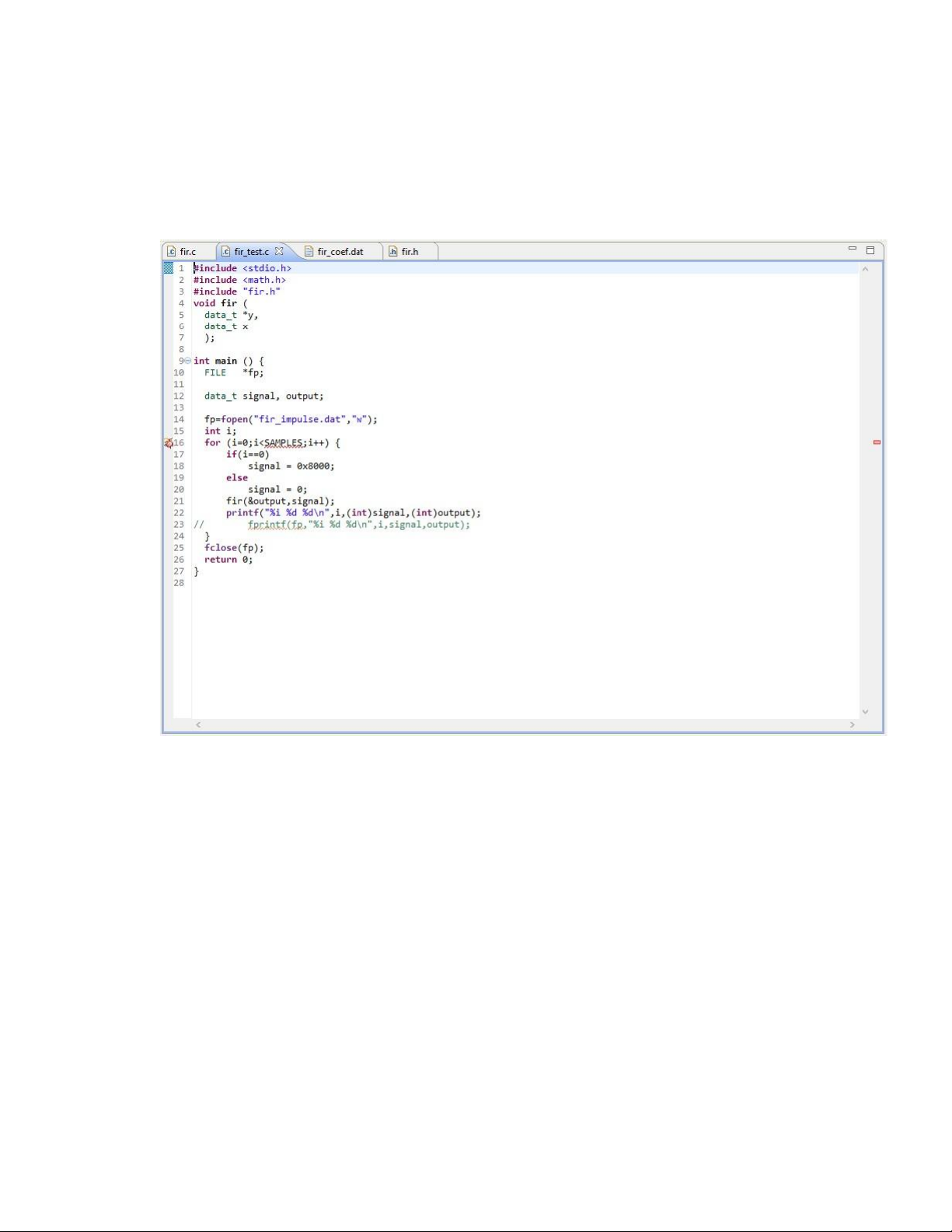

Bước 17: Nhấp đúp vào tệp fir_test.c trong thư mục testbench để mở nội dung của nó trong bảng thông tin.

Hình 2.10. Nội dung file testbench

Lưu ý rằng testbench mở fir_impulse.dat ở chế độ ghi và gửi một xung (mẫu đầu tiên là 0x8000). 2.2 Chạy mô phỏng C

Chạy mô phỏng C để quan sát đầu ra dự kiến.

Bước 1: Chọn Project > Run C Simulation hoặc nhấp vào nút từ thanh công cụ và

nhấp OK trong cửa sổ C Simulation Dialog.

Testbench sẽ được biên dịch bằng trình biên dịch apcc và tệp csim.exe sẽ được tạo

ra. Sau đó, csim.exe sẽ được thực thi và đầu ra sẽ được hiển thị trong cửa sổ console view. lOMoAR cPSD| 58675420

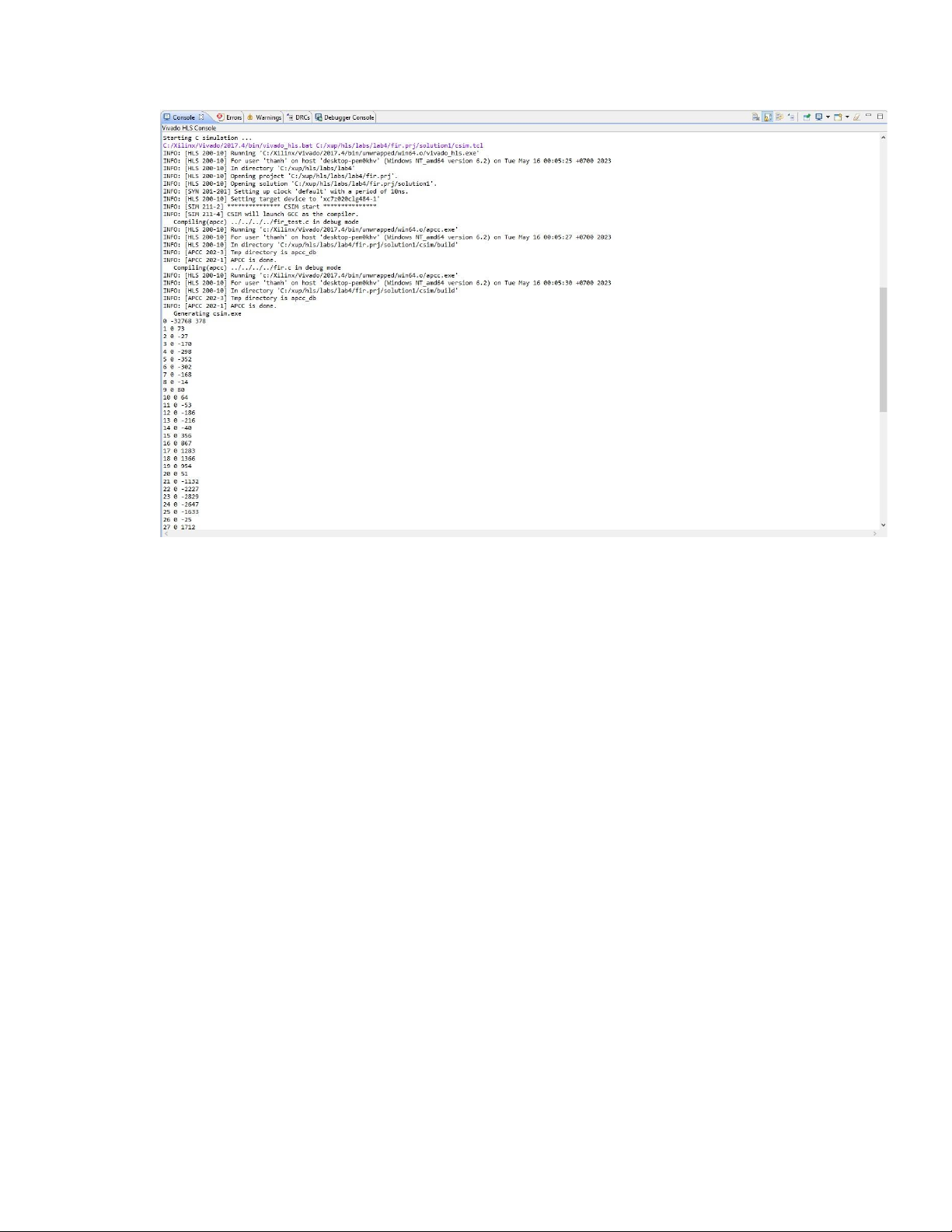

Hình 2.11. Kết quả testbench được tạo ra trong chế độ xem Console

Ta sẽ thấy các hệ số bộ lọc đang được tính toán.

2.3. Tổng hợp thiết kế

Tổng hợp thiết kế với các giá trị mặc định. Xem kết quả tổng hợp và trả lời câu hỏi

được liệt kê trong phần chi tiết của bước này.

Bước 1: Chọn Solution > Run C Synthesis > Active Solution để bắt đầu quá trình tổng hợp.

Bước 2: Khi tổng hợp hoàn thành, một số tệp báo cáo sẽ trở nên truy cập được và Kết

quả Tổng hợp sẽ được hiển thị trong bảng thông tin.

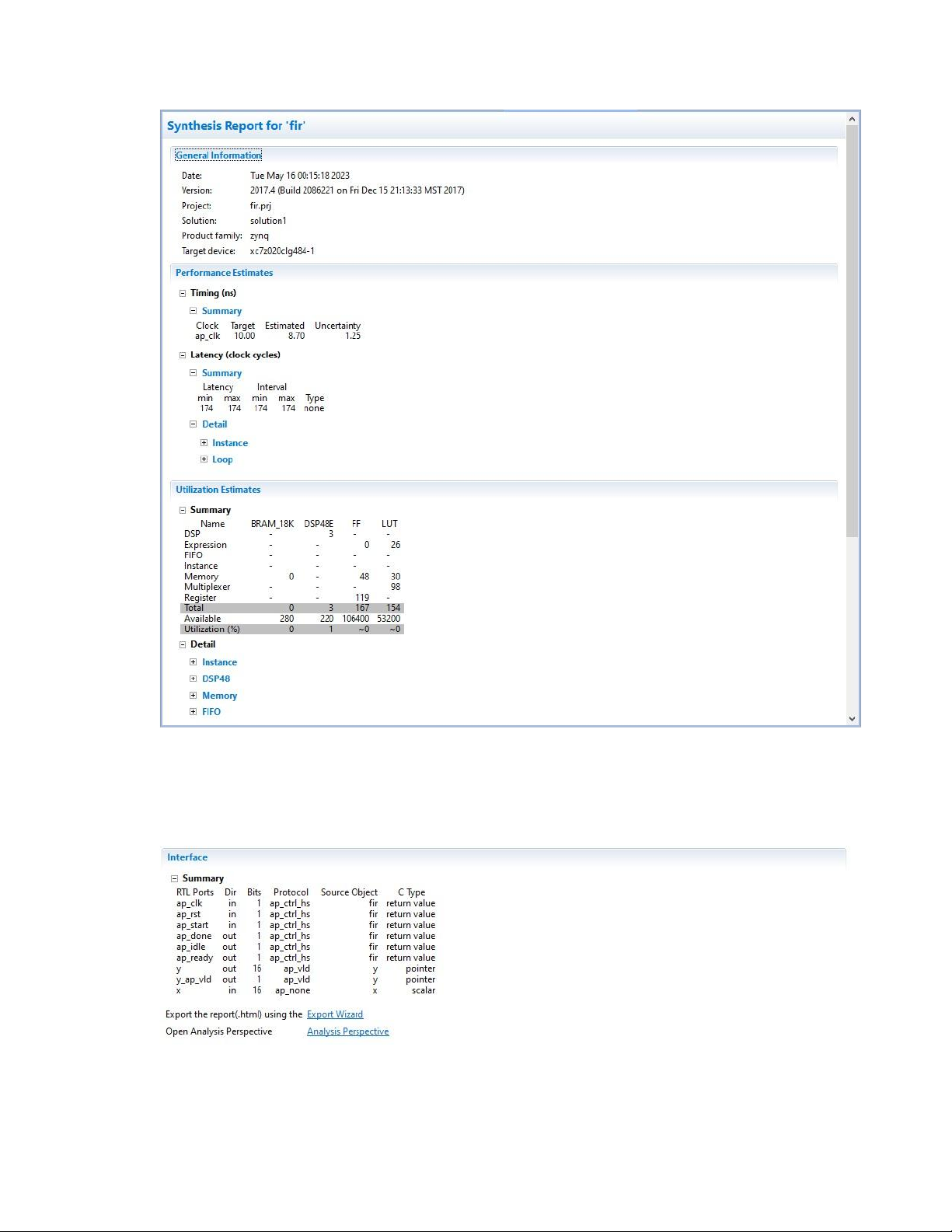

Bước 3: Báo cáo Tổng hợp hiển thị ước tính hiệu suất và tài nguyên cũng như độ trễ

ước tính trong thiết kế. lOMoAR cPSD| 58675420 Hình 2.12. Synthesis Report

Bước 4: Báo cáo cũng hiển thị các tín hiệu interface cấp cao được tạo ra bởi các công cụ.

Hình 2.13. Các tín hiệu interface được tạo ra lOMoAR cPSD| 58675420

Ta có thể thấy thiết kế mong đợi đầu vào x dưới dạng scalar 16-bit và đầu ra y

thông qua con trỏ của dữ liệu 16-bit. Nó cũng có tín hiệu ap_vld để chỉ ra khi kết quả hợp lệ.

Thêm chỉ thị PIPELINE vào vòng lặp và tổng hợp lại thiết kế. Xem kết quả tổng hợp.

Bước 1: Đảm bảo rằng tệp fir.c được mở trong chế độ xem thông tin.

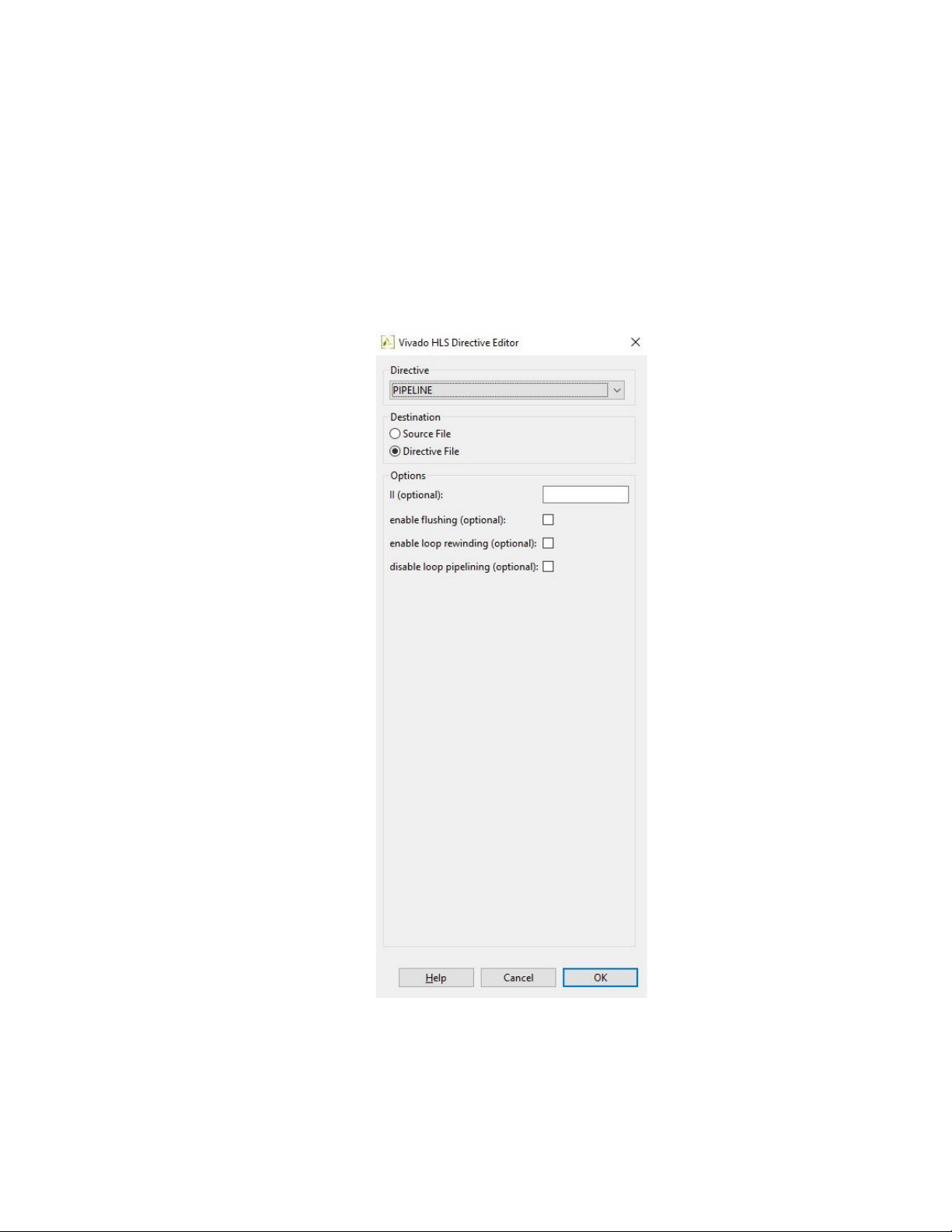

Bước 2: Chọn tab Directive và áp dụng chỉ thị PIPELINE vào vòng lặp.

Hình 2.14. Áp dụng PIPELINE vào vòng lặp lOMoAR cPSD| 58675420

Bước 3: Chọn Solution > Run C Synthesis > Active Solution để bắt đầu quá trình tổng hợp.

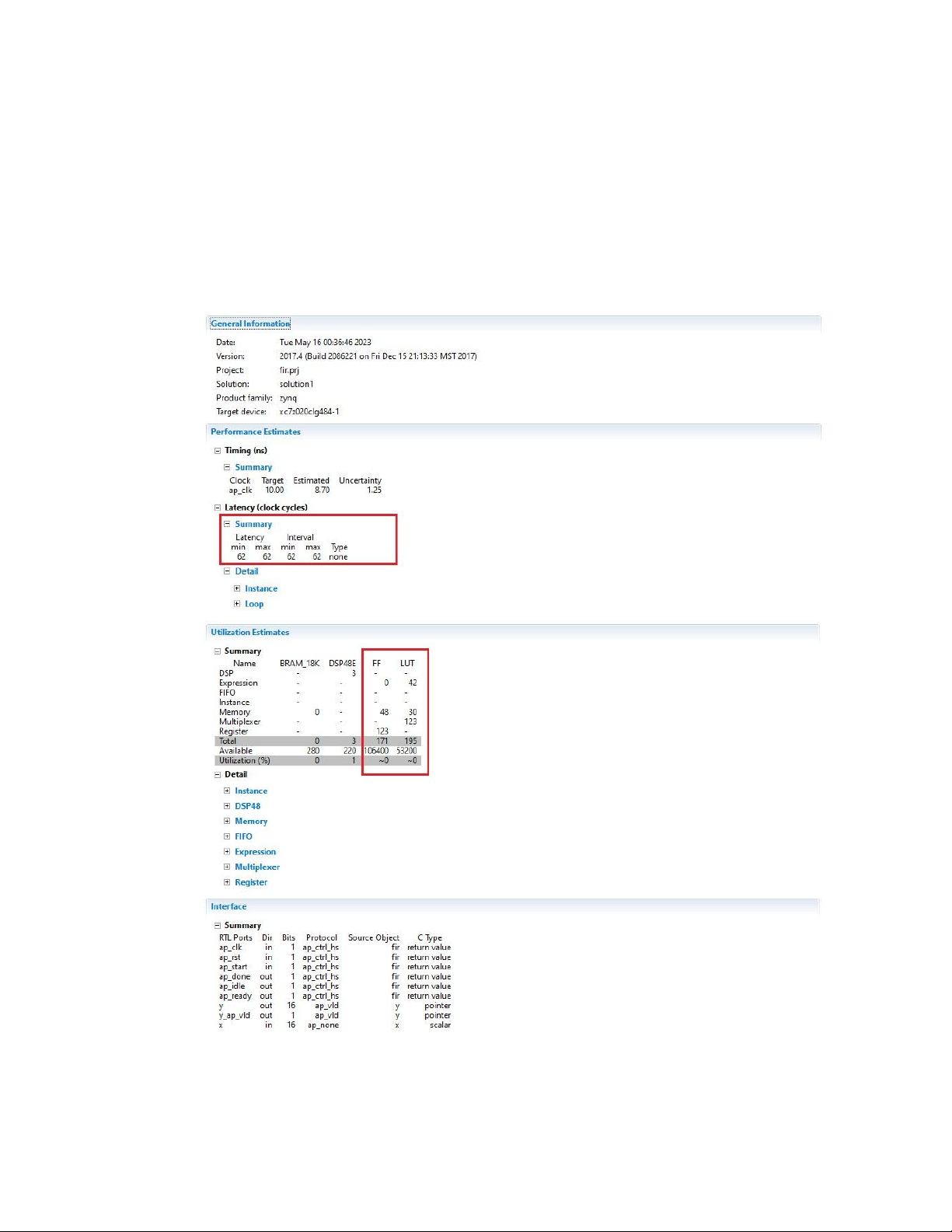

Bước 4: Khi tổng hợp hoàn thành, Kết quả Tổng hợp sẽ được hiển thị trong bảng thông tin.

Bước 5: Lưu ý rằng độ trễ đã giảm xuống 62 hoặc 63 chu kỳ xung. Tiêu thụ DSP48

và BRAM vẫn giữ nguyên; tuy nhiên, tiêu thụ LUT và FF tăng một chút.

Hình 2.15. Synthesis Report saukhitheem PIPELINE vào vòng lặp