Preview text:

lOMoAR cPSD| 58675420

TRƯỜNG ĐẠI HỌC SƯ PHẠM KỸ THUẬT

Ngành đào tạo: CNKT Máy Tính TP. HỒ CHÍ MINH

Chương trình: CNKT Máy Tính KHOA ĐIỆN – ĐIỆN TỬ

Trình độ đào tạo: Đại học

Đề cương chi tiết môn học

1. Tên học phần: Thiết kế kết hợp HW/SW

Mã học phần: HSCD446164

2. Tên Tiếng Anh: Hardware/Software Codesign

3. Số tín chỉ: 4 tín chỉ (3/1/6) (3 tín chỉ lý thuyết, 1 tín chỉ thực hành/thí nghiệm) Phân bố thời

gian: 16 tuần [(4 tiết lý thuyết + 6 tiết tự học)/ tuần]

4. Giảng viên phụ trách 1. PGS. TS. Phan Văn Ca 2. TS. Trương Ngọc Sơn 3. ThS. Trương Quang Phúc

5. Điều kiện tham gia học tập học phần

a. Môn học tiên quyết: Không

b. Môn học trước: Hệ thống nhúng

6. Mô tả học phần (Course Description)

Trong các hệ thống nhúng (embedded system) thực hiện các chức năng thời gian thực trong các hệ

thống điện gia dụng, hệ thống giám sát, hệ thống viễn thống, hệ thống điều khiển. Thông thường,

các hệ thống này được thiết kế riêng biệt giữa phần cứng và phần mềm, chính việc này dẫn đến sự

không đồng nhất giữa phần cứng và phần mềm. Trong học phần này trang bị cho người học kiến

thức cơ bản về phần cứng (HW), phần mềm (SW) và thiết kế kêt hợp HW/SW. Các mô hình thiết

kế luồng dữ liệu (data-flow) luồng điều khiển (control-flow) và quá trình thực hiện các mô hình.

Các phương pháp phân tích đánh giá hiệu năng thiết kế. Các đường dữ liệu (Datapath) với máy

trạng thái hữu hạn(FSM). Phân tích các kiến trúc vi lập trình, các lõi nhúng đã chức năng và hệ

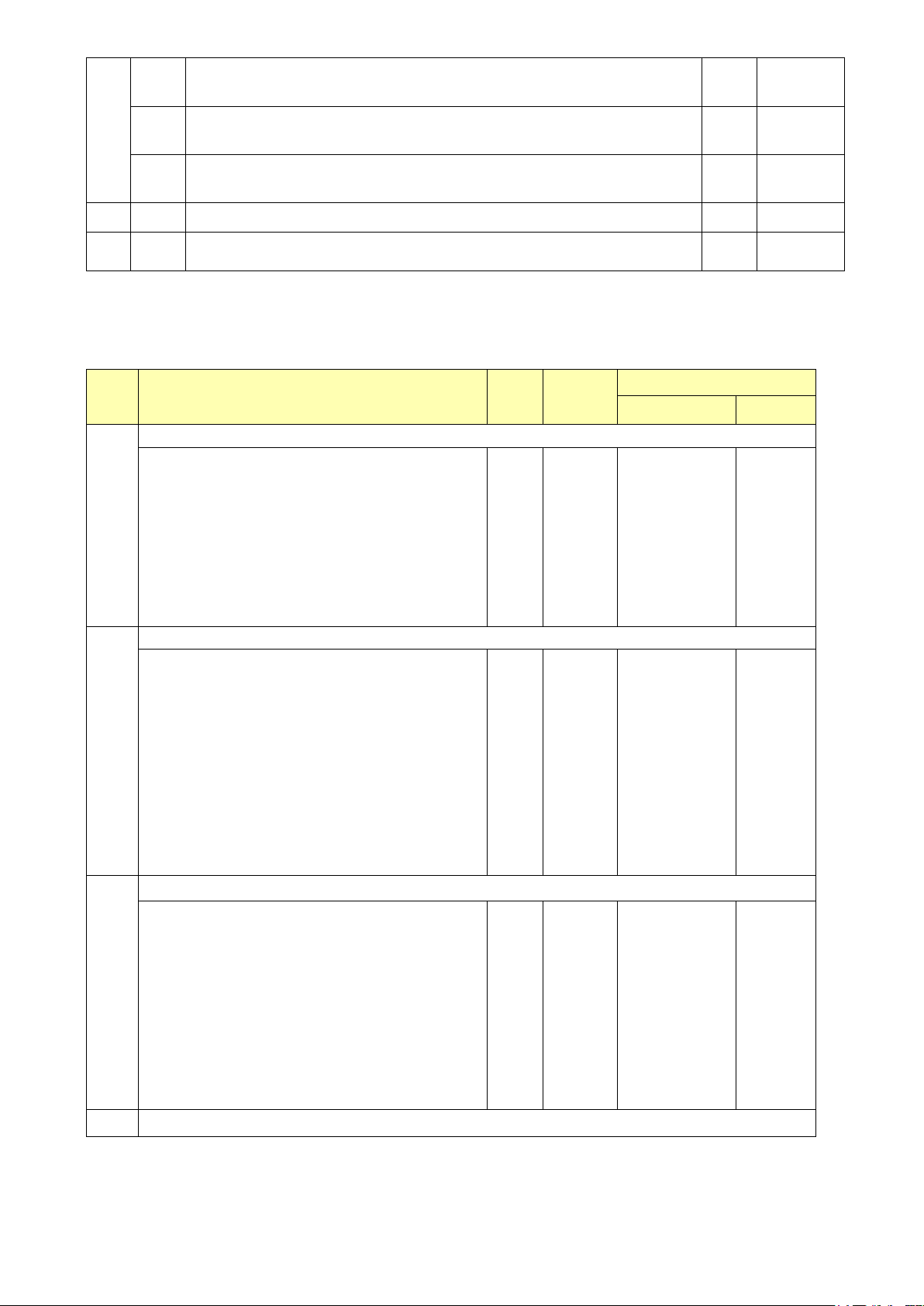

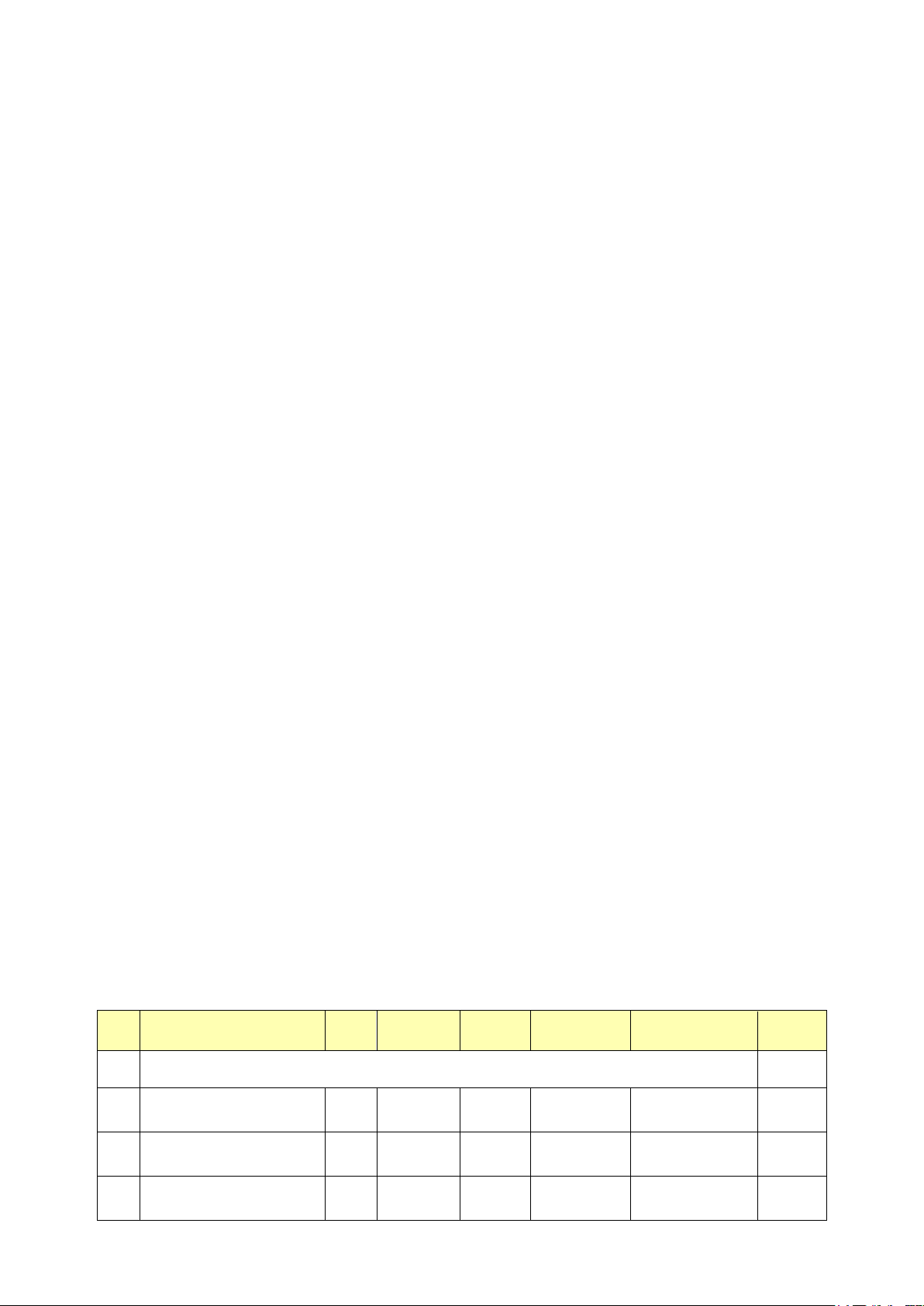

thống trên chip (SoC) cũng được phân tích trong nội dung môn học. 7. Mục tiêu học phần (Course Goals) Mục tiêu Mô tả (Goals)

(Goal description) ELO Trình độ năng lực

Các kiến thức về nền tảng về phần cứng, phần mềm và thiết kế kết hợp, G1

phân tích và giải thích được các chương trình phần mềm và mô tả phần 1-2 5 cứng dựa trên chu kỳ.

Khả năng khảo sát, phân tích đánh giá các thiết kế kết hợp trong các ứng

dụng khác nhau, có xét đến đánh đổi giữa các yếu tố. Dựa trên các mô G2 4-5-7 4

hình phần mềm và các mô tả phần cứng dựa trên chu kỳ, thực hiện các dự án theo nhóm.

Khả năng thiết kế phần cứng và phần mềm, lựa chọn phân vùng thích hợp G3

với các thành phần phần cứng, phần mềm và tạo ra các giao tiếp phần 6 5

cứng và phần mềm tương ứng phản ánh đúng phân vùng đã lựa chọn.

8. Chuẩn đầu ra của học phần CLO Mô tả

(Sau khi học xong môn học này, người học có thể:) ELO Trình độ năng lực

G1.1 Giải thích các khái niệm nền tảng về HW, SW, SoC 1.4 5 G1

G1.2 Mô tả nguyên lý thiết kế và phát triển thiết kế kết hơp HW-SW 2.1 5 lOMoAR cPSD| 58675420

Khả năng phân tích và biến đổi các chương trình phần mềm đơn giản sang 4.5 4

G2.1 mô tả phần cứng dựa trên chu kỳ với các mô tả tương đương

Khả năng làm việc theo nhóm để giải quyết bài toán thiết kế theo yêu cầu 5.3 4 G2 G2.2

Khả năng phân tích, đánh giá các kết quả thiết kế kết hợp đã được thực 7.4 G2.3 hiện và công bố. G3

G3.1 Khả năng sử dụng phần mềm để đồng mô phỏng các chương trình phần 6.4 5

mềm với các mô tả phần cứng dựa trên chu kỳ

9. Đạo đức khoa học

Các nội dung kiểm tra phải được thực hiện từ chính bản thân sinh viên. Nếu bị phát hiện có sao

chép hoặc có hành vi gian lận thì sinh viên có liên quan phải nhận điểm 0 (không) cho môn học.

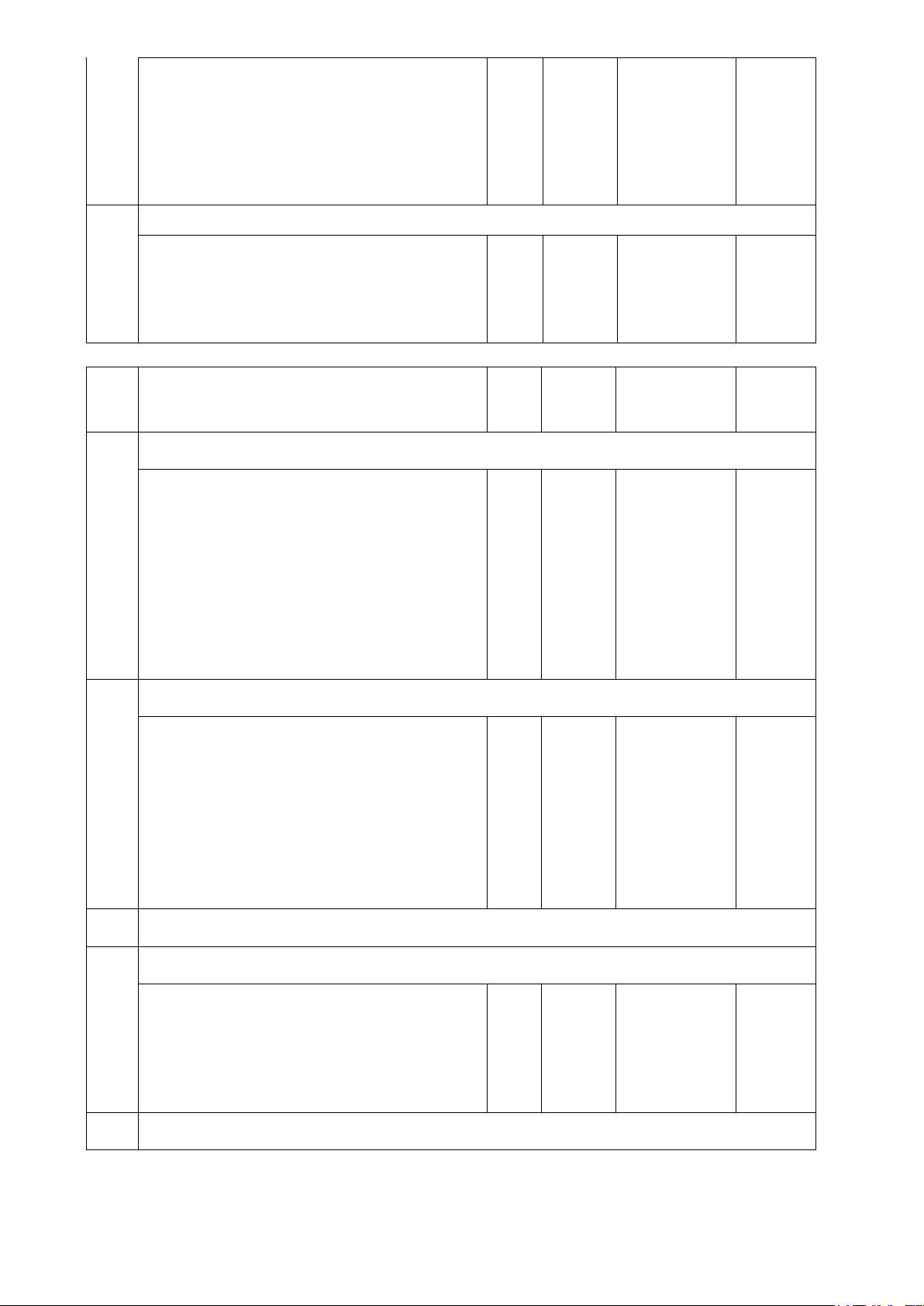

10. Nội dung chi tiết học phần: Trình độ Phương pháp Tuần Nội dung CLO năng lực Dạy học Đánh giá

Chương 1. Giới thiệu thiết kế kết hợp (3/0/6)

Nội dung giảng dạy trên lớp: (3) 1.

Giới thiệu về môn học 2. Phần cứng 1 3. Phần mềm G1.1 5 Thuyết giảng 4.

Không gian thiết kế 5. Hiệu G1.2 5 Thảo luận Q,M,F

Các nội dung tự học: (6)

+ Mức độ tổng quát của mô hình + Chương 1: trong [1]

Chương 2. Mô hình luồng dữ liệu (3/0/6)

Nội dung giảng dạy trên lớp: (3) 1. Giới thiệu sơ đồ 2. Tokens, Actors and Queues 3. SDF 2 4.

Phân tích sơ đồ luồng dữ liệu đồng bộ G1.1 5 Thuyết giảng 5.

Mô hình luồng điều khiển và các hạn chế G1.2 5 Thảo luận Q,M,F

của mô hình luồng dữ liệu 6. Các phép biến đổi

Các nội dung tự học: (6)

+ Phân tích ví dụ thiết kế PAM trong tài liệu [1]

Chương 3. Phân tích luồng dữ liệu và luồng điều khiển (3/0/6)

Nội dung giảng dạy trên lớp: (3) 1. Thực hiện phần mềm SW 2.

Thực hiện phần cứng HW 3. Thực hiện HW/SW 3 4.

Phân tích thiết kế Control flow và Data 5 Thuyết giảng G1.2

flow5. Thực hiện biên dịch ngôn ngữ C cho phần 5 Thảo luận Q,M,F cứng

Các nội dung tự học: (6)

+ Phân tích ví dụ FFT 4 điểm + Bài tập chương 3 4

Chương 4. Mô hình máy trạng thái cho đường dữ liệu (3/0/6) lOMoAR cPSD| 58675420

Nội dung giảng dạy trên lớp: (3) 1.

Mô hình máy trạng thái hữu hạn (FSM) 2. Datapath G1.2 5 Thuyết giảng 3.

Mô hình máy trạng thái hữu hạn cho G2.1 5 Thảo luận Q,M,F đường dữliệu

Các nội dung tự học: (6) + Wires and Registers 5

Chương 4. Mô hình máy trạng thái cho đường dữ liệu (TT)(3/0/6)

Nội dung giảng dạy trên lớp: (3) G1.2 4 Thuyết giảng Q,M,F 4. Mô hình G2.1 4 Thảo luận

5. Thực hiện (Implementation) 6. Ví dụ thiết kế FSMD 7. Bài tập

Các nội dung tự học: (6)

+ Phân tích ví dụ ánh xạ các thiết kế sử dụng Verilog và SystemC

Chương 5. Các kiến trúc vi lập trình (3/0/6)

Nội dung giảng dạy trên lớp: (3) 1.

Các hạn chế của mô hình máy trạng thái hữu hạn 2.

Điều khiển vi lập trình 6 3. Mã hóa vi lệnh G1.1 5 Thuyết giảng 4.

Đường dữ liệu (Datapath) vi lập trình G2.1 4 Thảo luận Q,M,F 5.

Đường ống (Pipelining) vi lập trình 6.

Vi lập trình cho vi điều khiển

Các nội dung tự học: (6) + Bài tập về nhà

Chương 6. Các lõi nhúng đa chức năng (3/0/6)

Nội dung giảng dạy trên lớp: (3) 1. Các bộ vi xử lý 2. RISC Pipeline 7

3. Tổ chức chương trình G1.2 5 Thuyết giảng

4. Các công cụ biên dịch G2.1 5 Thảo luận Q,M,F

5. Phân tích chương trình mức thấp 6. Mô phỏng bộ xử lý

Các nội dung tự học: (6)

+ Đọc thêm tổ chức bộ nhớ 8

Ôn tập và kiểm tra giữ kỳ

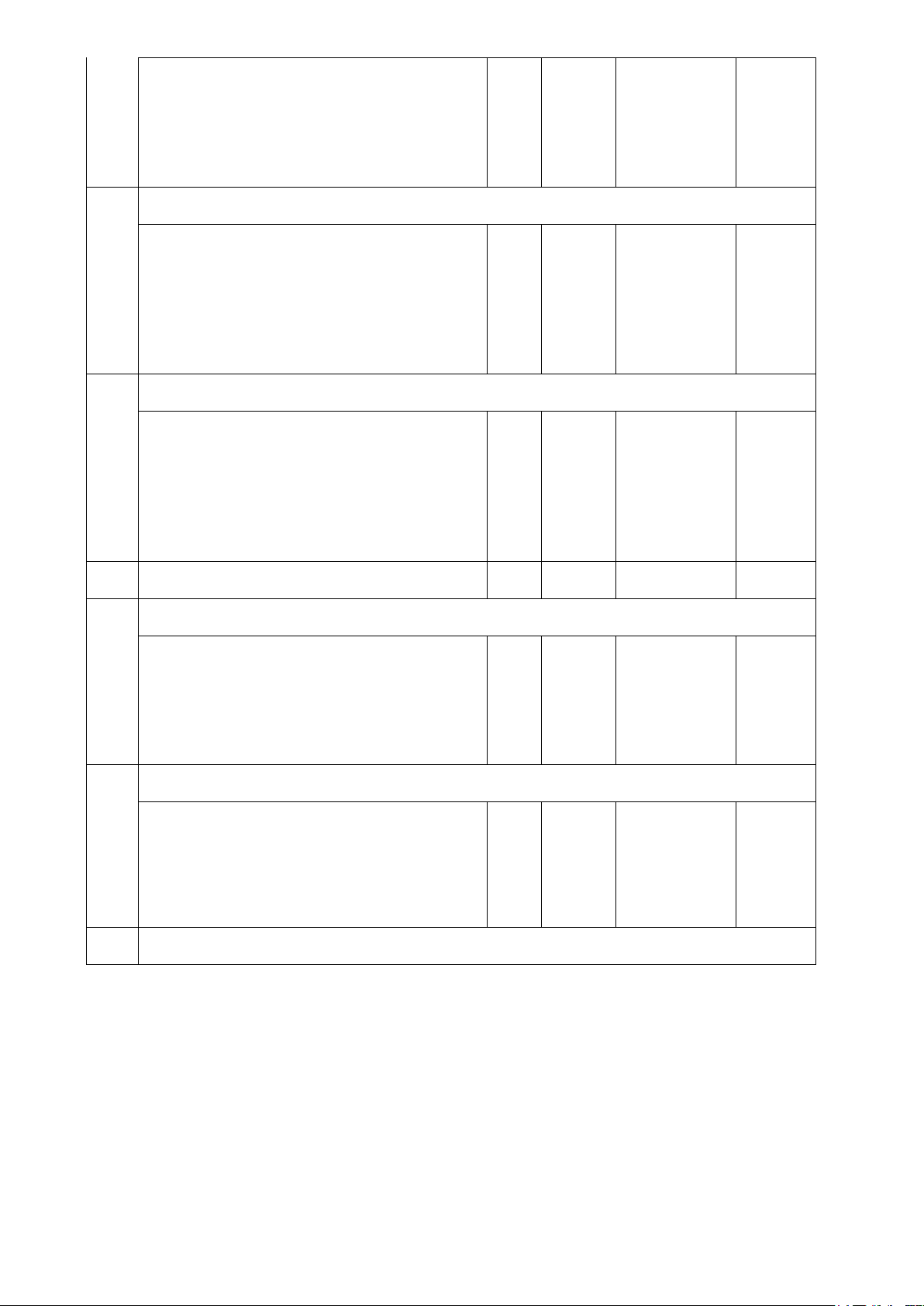

Chương 7. Hệ thống trên Chip SoC (3/0/6)

Nội dung giảng dạy trên lớp: (3) G1.2 1. Khái niệm 9

2. Nguyên tắc thiết kế trong kiến trúc SoC 5 Thuyết giảng 3. Mô hình SoC 5 Thảo luận Q,F

Các nội dung tự học: (6) 3. Bài tập về nhà

10 Chương 8. SystemC (3/0/6) lOMoAR cPSD| 58675420

Nội dung giảng dạy trên lớp: (3)

1. Giới thiệu thư viện SystemC 2. Kiểu dữ liệu G1.1 5 Thuyết giảng 3. Modules Thảo luận Q,F

Các nội dung tự học: (6)

+ Cài đặt thử viện SystemC trên VS

Chương 8. SystemC (TT) (3/0/6)

Nội dung giảng dạy trên lớp: (3) 4. Process 11 5. Port and Signals G1.1 5 Thuyết giảng 6. Channels G3.1 5 Thảo luận Q,P,F 7. TLM

Các nội dung tự học: (6) + SystemC Quick Reference

12 Chương 9. Mô hình hóa (3/0/6)

Nội dung giảng dạy trên lớp: (3) G2.2 5 Thuyết giảng Q,P,F 1. Mô hình tính toán G1.2 Thảo luận

2. Các ngôn ngữ thiết kế hệ thống 3. Mô hình hệ thống 4. Mô hình bộ xử lý 5. Mô hình truyền thông

Các nội dung tự học: (6) + Mô hình hệ thống

Chương 10. Tổng hợp hệ thống (3/0/6)

Nội dung giảng dạy trên lớp: (3)

1. Xu hướng thiết kế hệ thống

13 2. Thiết kế dựa trên TLM G2.1 5 Thuyết giảng 3. Tổng hợp nền tảng G3.1 4 Thảo luận Q,P,F

Các nội dung tự học: (6)

+ Tạo TLM và Mapping tự động

Chương 11. Verification (3/0/6)

Nội dung giảng dạy trên lớp: (3) G3.1 1.

Các phương pháp dựa trên mô phỏng 14 5 2.

Các phương pháp dựa trên xác thực Thuyết giảng 5 thông thường Thảo luận Q,P,F

Các nội dung tự học: (6) 5 + So sánh, phân tích

15-16 Ôn tập và Báo cáo tiểu luận

11. Tài liệu học tập: - Giáo trình chính:

[1] Patrick R. Schaumont, A Practical Introduction to Hardware/Software Codesign, Springer

Science & Business Media, 2nd Edition, 2010 - Tài liệu tham khảo:

[1] João M. P. Cardoso, Michael Hübner, João M. P. Cardoso, Michael Hübner,Reconfigurable

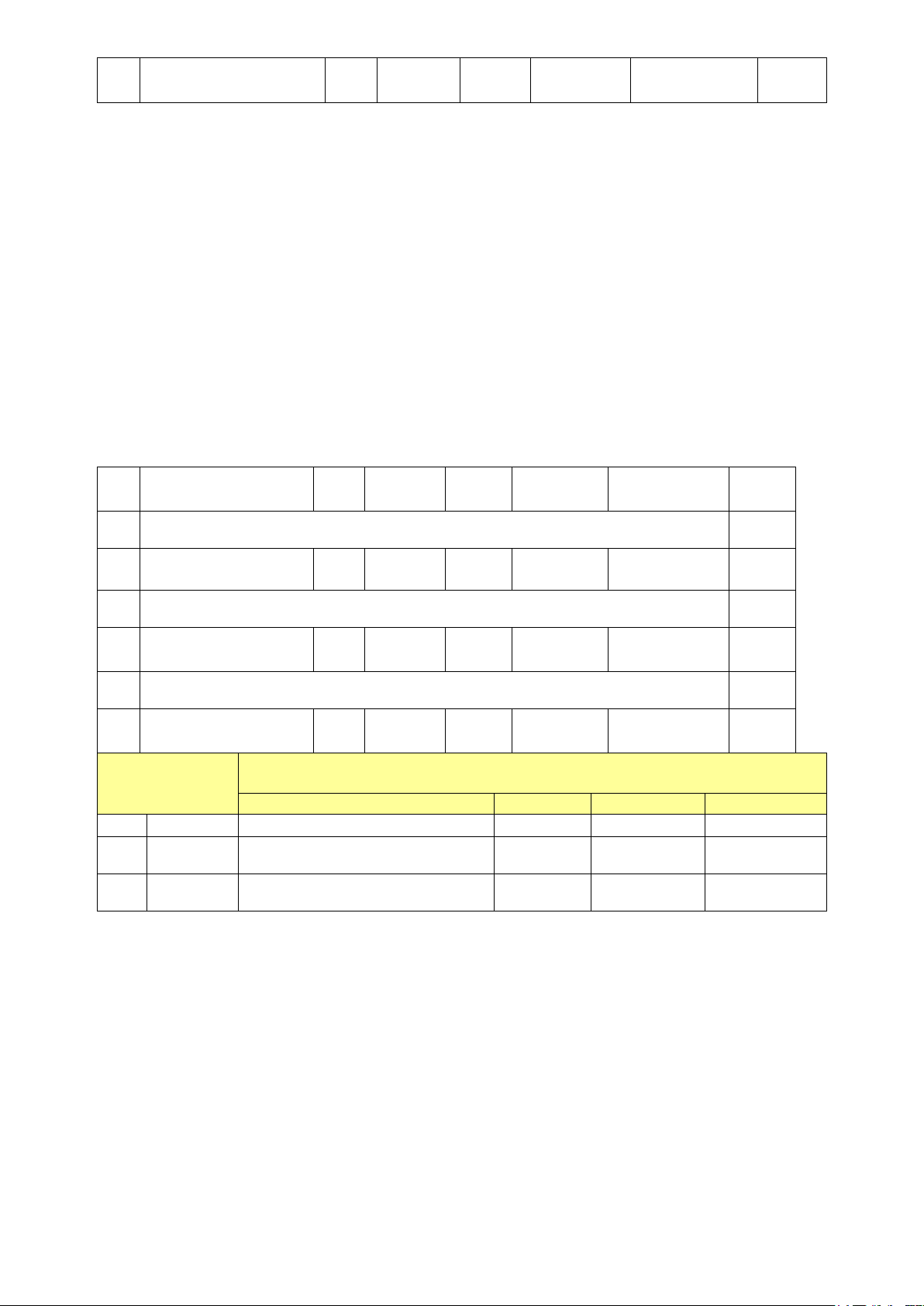

Computing: From FPGAs to Hardware/Software Codesign, Springer-Verlag New York, 2011. lOMoAR cPSD| 58675420 Phương TT Nội dung Tuần CLO Trình độ năng lực pháp Công cụ Tỉ lệ (%)

Q Câu hỏi (Quizzes) 10 4 Kiểm tra

Q1 Kiến thức chương 1 -2 3 G1.1 G1.2 4 trên lớp Câu hỏi tự luận 2 4 Kiểm tra Q2 Kiến thức chương 3-4 6 G1.2 G2.1 4 trên lớp Câu hỏi tự luận 2 4 Kiểm tra Q3 Kiến thức chương 5-6 9 G1.3 G2.1 4 trên lớp Câu hỏi tự luận 2 lOMoAR cPSD| 58675420 Q4 Kiến thức chương 7-8 12 G1.2 4 Kiểm tra trên lớp Câu hỏi tự luận 2

[2] Sanjaya Kumar, James H. Aylor, Barry W. Johnson, WM. A. Wulf, The Codesign of

Embedded Systems: A Unified Hardware/Software Representation, Springer US, 1996

[3] Jørgen Staunstrup, Wayne Wolf, Hardware/Software Co-Design: Principles and Practice,

Springer Science & Business Media, 1997

[4] F. Balarin, Paolo Giusto, Attila Jurecska, Claudio Passerone, Hardware-Software CoDesign

of Embedded Systems The POLIS Approach, Springer Science & Business Media, 2012

[5] Louise H. Crockett, Ross A. Elliot, Martin A. Enderwitz, Robert W. Stewart, The Zynq

Book: Embedded Processing with the Arm Cortex-A9 on the Xilinx Zynq-7000 All Programmable

Soc, Strathclyde Academic Media, 2014

12. Đánh giá kết quả học tập - Thang điểm: 10

- Kế hoạch kiểm tra như sau: Câu hỏi tự Q5 Kiến thức chương 9- 11 15 G1.1 4 Kiểm tra trên lớp luận 2 P Dự án (Projects) 20 P Dự án làm theo nhóm 5 G2.1 5 Thiết kế Báo cáo 5

M Kiểm tra giữa kỳ (Midterm Exam) 20 M Kiến thức chương 1 - 7 8 G1.1-2 4 Kiểm tra trên lớp Tự luận 20 F

Thi cuối kỳ (Final Exam) 50 Tuầ Toàn bộ F Tất cả các kiến thức đã học n thi CLO 4 Thi Tự luận 50

Hì nh thức kiểm a CLO tr Câu hỏi Bài tập lớn Thi giữa kỳ Thi cuối kỳ G1 G1.1-6 x x x x G2 G2.1 x x G3 G2.1-4 x x lOMoAR cPSD| 58675420

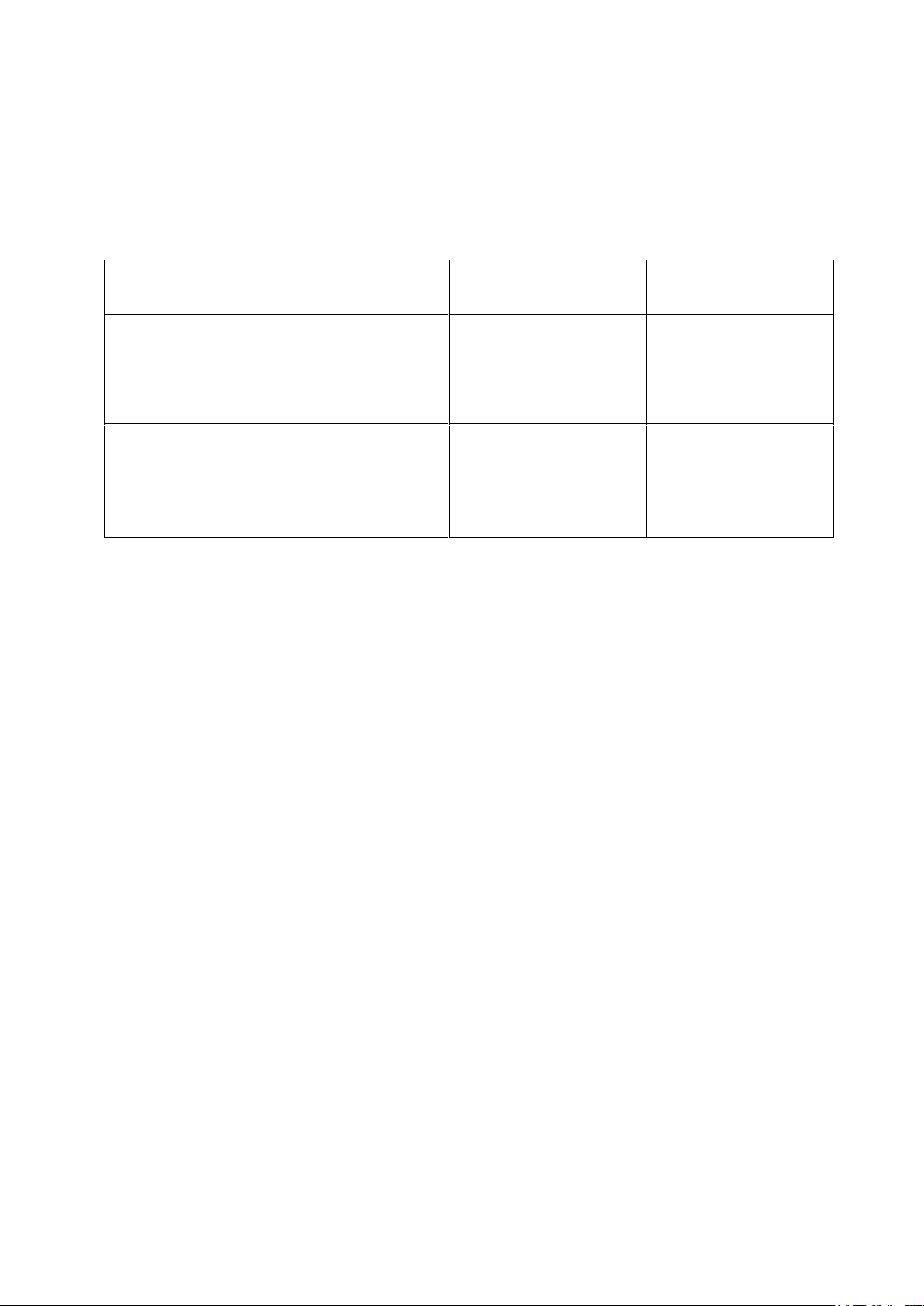

13. Ngày phê duyệt lần đầu: 15/01/2014

14. Cấp phê duyệt: Trưởng khoa Trưởng BM Nhóm biên soạn TS. Nguyễn Minh Tâm TS. Võ Minh Huân TS. Phan Văn Ca

15. Tiến trình cập nhật ĐCCT Bộ môn duyệt

Nôi dụng cập nhật

Giảng viên cập nhật (Ký tên) (Ký tên)

Ngày cập nhật lần 1: 15/01/2016 TS. Phan Văn Ca TS. Phan Văn Ca

Nội dung cập nhật:

Ngày cập nhật lần 2: 15/05/2018 PGS.TS. Phan Văn Ca PGS.TS. Phan Văn Ca

Nội dung cập nhật: