Preview text:

lOMoAR cPSD| 58833082

Báo cáo thực hành môn thiết kế số và vi xử lý Buổi 1 và 2

Họ và tên: Trần Duy Long Mã sinh viên: 22029071 1) Buổi 1:

- Cài đặt ứng dụng Quartus cùng với cách sử dụng ứng dụng cùng với đó là tải ứng dụng

ModelSim và file MAX 10 DEVICE tích hợp vào trong ứng dụng Quartus. Học về cách tạo

1 project và thể hiện biểu thức logic đại số XNOR vào trong Quartus dưới dạng ngôn ngữ

SystemVerilog. Học về các chân của STEP MAX 10 board dựa vào bảng chi tiết và cách chọn

gắn input, output vào các chân của nó. Cuối cùng là cách thể hiện biểu thức đại số XNOR trên STEP MAX 10 board. 2) Buổi 2:

- Giới thiệu về ngôn ngữ mô tả phần cứng. Đầu tiên học về luồng thiết kế gồm những

bước nào kể từ khi lập được bảng chân lý cho đến khi thể hiện nó được trên STEP

MAX 10 board. Học về định nghĩa của mô phòng và tổng hợp là gì ? Tiếp theo ta biết lOMoAR cPSD| 58833082

được định nghĩa về ngôn ngữ mô tả phần cứng, mục đích sử dụng để làm gì. Định

nghĩa về Module, cú pháp, khai báo, portlist, và logic nội bộ của nó thể hiện trong

việc lập trình. Sau đó ta có bảng các kiểu dữ liệu cơ bản và giá trị của 1 biến. Tiếp đó

là học thêm về các toán tử và mức độ ưu tiên của chúng trong Quartus. Định nghĩa

và cú pháp của gán liên tục và gán có điều kiện. Biết thêm được cách thể hiện biểu

thức logic đại số NOT dưới dạng ngôn ngữ SystemVerilog. Biết được testbench là gì,

các bước thực hiện cùng với đó là cấu trúc của 1 testbench và ví dụ về nó. Cuối cùng

là cách chạy mô phỏng trên Quartus và thử nghiệm việc thiết kế module trên STEP MAX 10 board.

- Bài tập về nhà buổi 2:

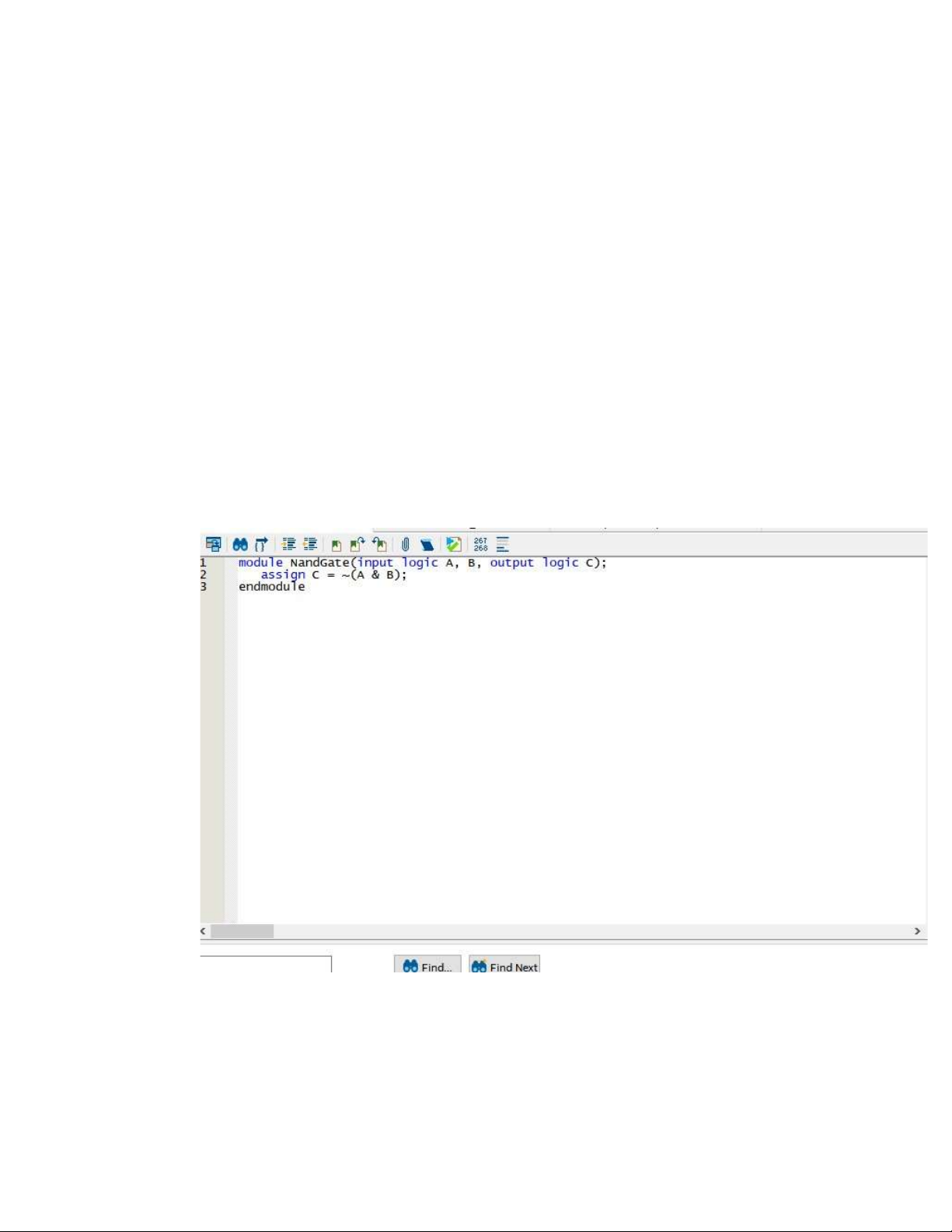

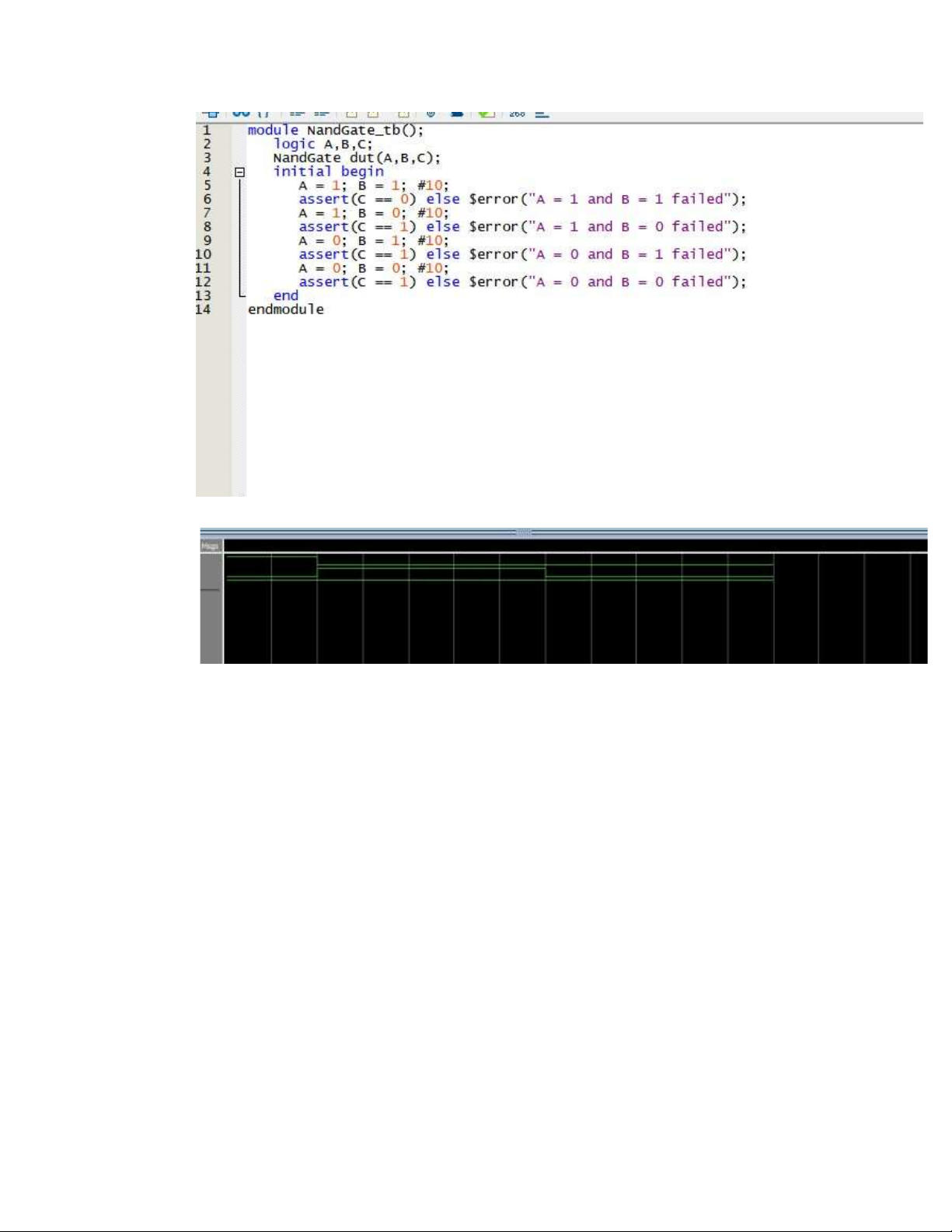

Bài 1: Design a NAND gate using SystemVerilog, simulate on ModelSim and test

operations of design in STEP MAX-10 board

Đoạn code sử dụng ngôn ngữ SystemVerilog để thiết kế 1 cổng NAND Testbench của nó lOMoAR cPSD| 58833082

Kết quả chạy mô phỏng như hình dưới đây

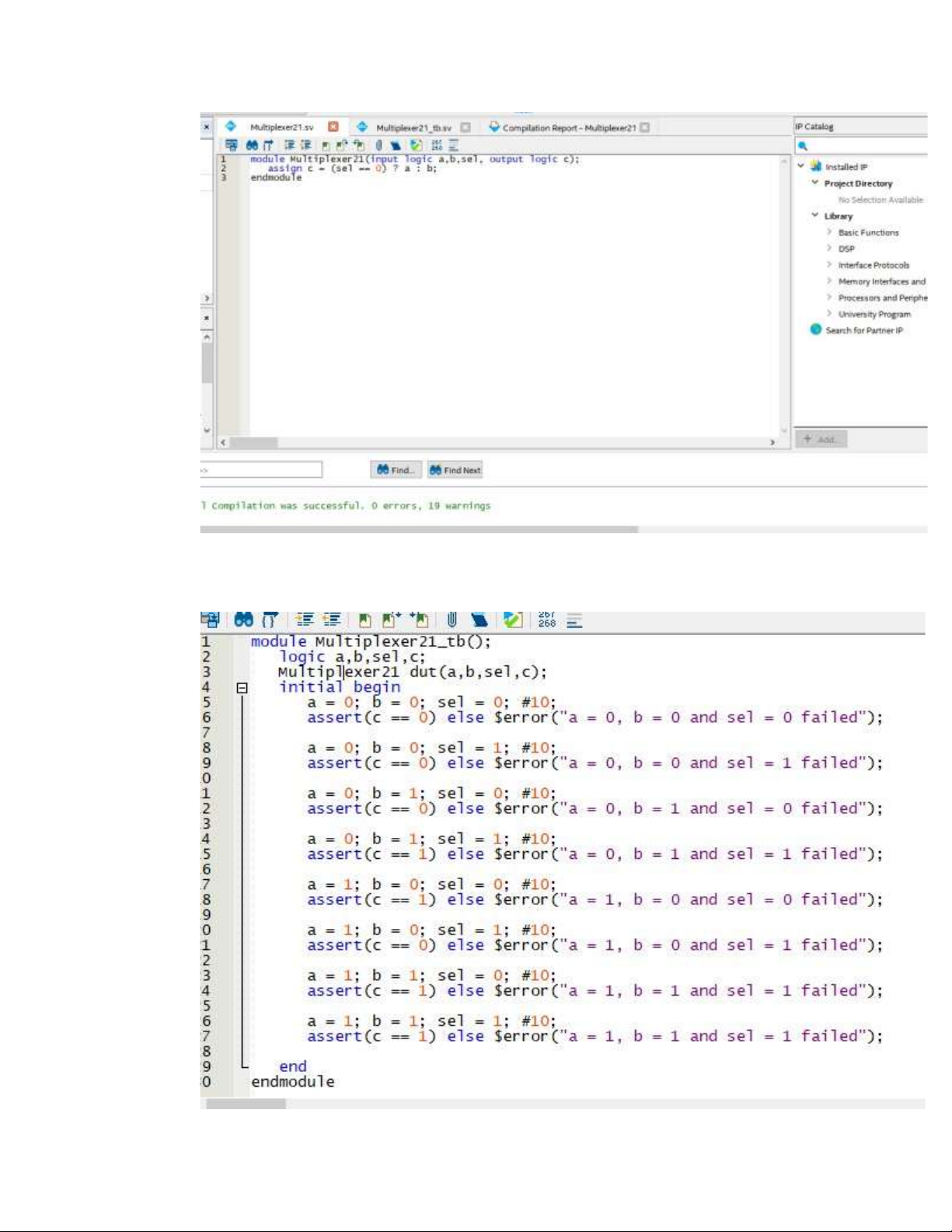

Bài 2: Design a 2:1 multiplexer using SystemVerilog, simulate on ModelSim and test operations

of design in STEP MAX-10 board. (Using conditional operator)

Đoạn code sử dụng ngôn ngữ SystemVerilog để thiết kế 1 bộ ghép kênh 2:1 lOMoAR cPSD| 58833082 Testbench của nó lOMoAR cPSD| 58833082

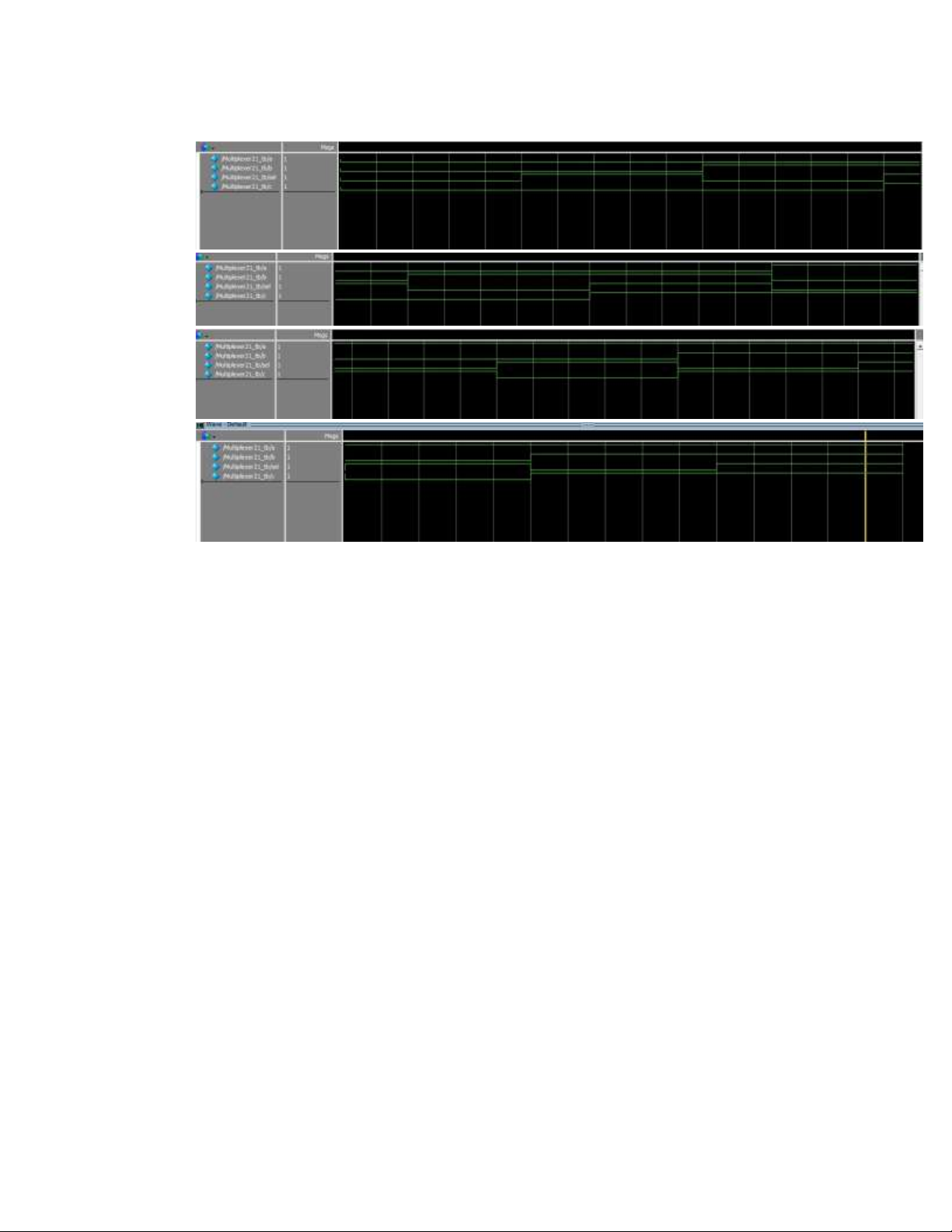

Kết quả chạy mô phỏng như hình dưới đây

Bài 3: Design a 4:1 multiplexer using SystemVerilog, simulate on ModelSim and test operations

of design in STEP MAX-10 board. (Using conditional operator)

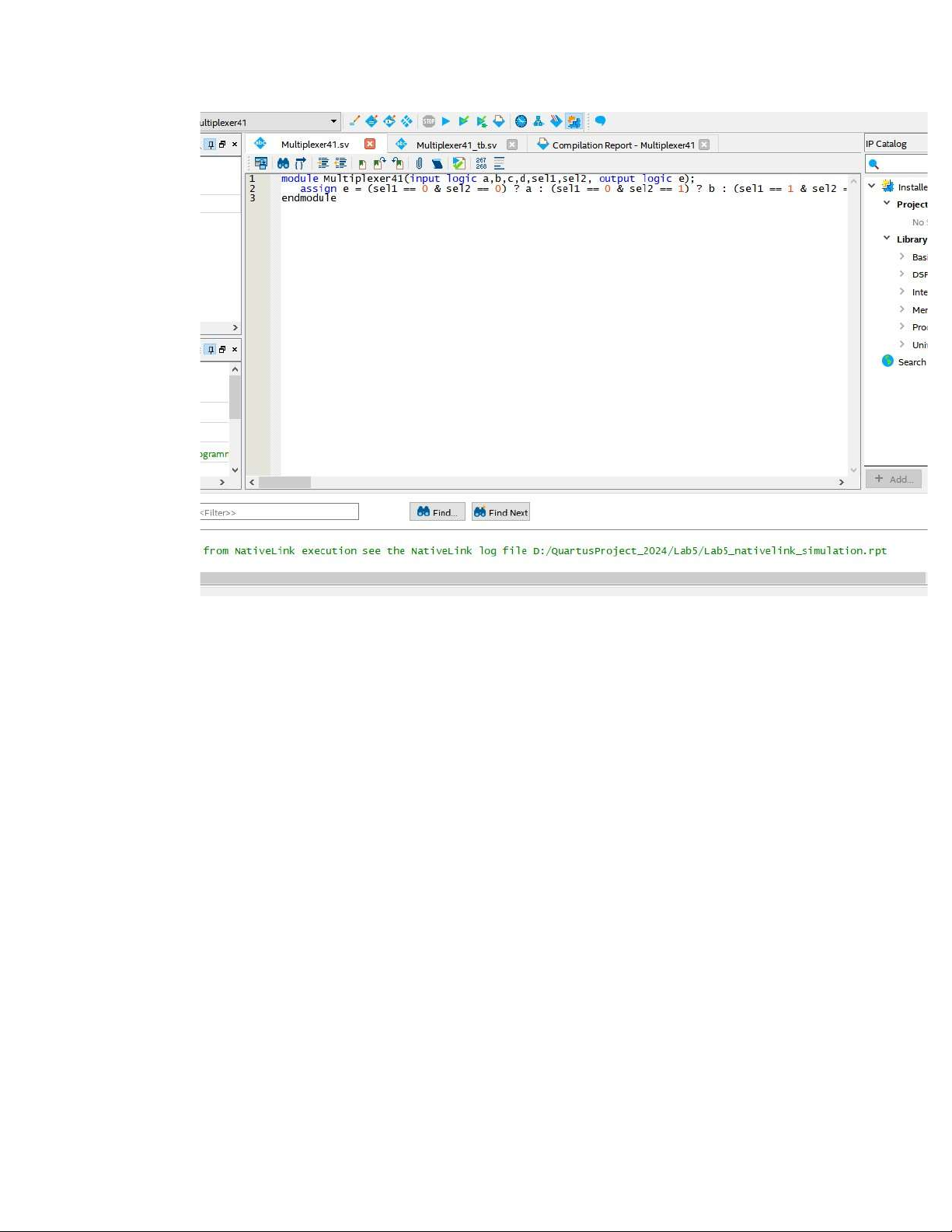

Đoạn code sử dụng ngôn ngữ SystemVerilog để thiết kế 1 bộ ghép kênh 4:1 lOMoAR cPSD| 58833082

module Multiplexer41(input logic a,b,c,d,sel1,sel2, output logic e); assign e = (sel1 == 0 & sel2 == 0) ?

a : (sel1 == 0 & sel2 == 1) ? b : (sel1 == 1 & sel2 == 0) ? c : d; endmodule Testbench của nó lOMoAR cPSD| 58833082

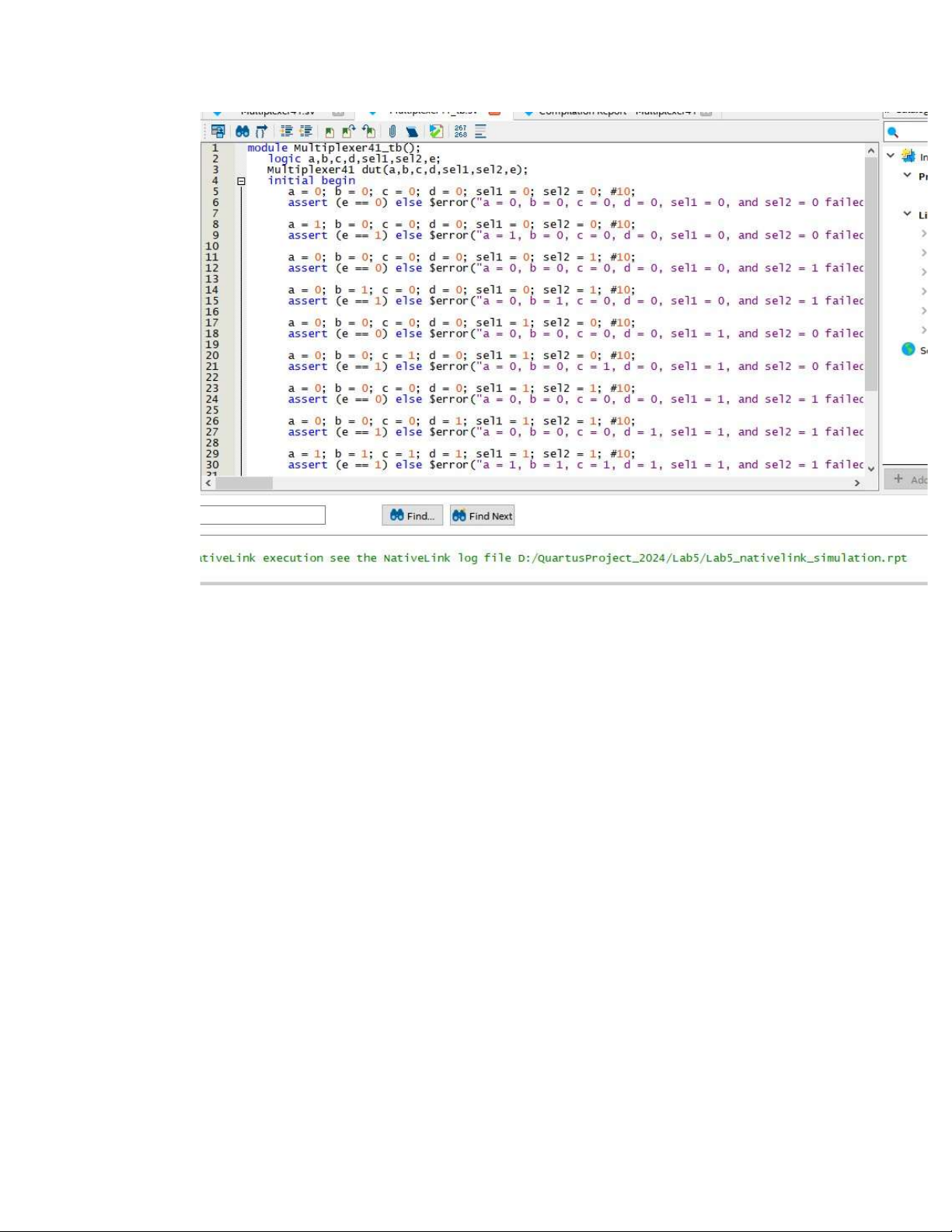

module Multiplexer41_tb(); logic a,b,c,d,sel1,sel2,e;

Multiplexer41 dut(a,b,c,d,sel1,sel2,e); initial begin a = 0; b = 0; c = 0; d = 0; sel1 =

0; sel2 = 0; #10; assert (e == 0) else $error("a = 0, b = 0, c = 0, d = 0, sel1 = 0, and sel2 = 0 failed");

a = 1; b = 0; c = 0; d = 0; sel1 = 0; sel2 = 0; #10; assert (e == 1) else $error("a = 1,

b = 0, c = 0, d = 0, sel1 = 0, and sel2 = 0 failed");

a = 0; b = 0; c = 0; d = 0; sel1 = 0; sel2 = 1; #10; assert (e == 0) else $error("a = 0,

b = 0, c = 0, d = 0, sel1 = 0, and sel2 = 1 failed");

a = 0; b = 1; c = 0; d = 0; sel1 = 0; sel2 = 1; #10; assert (e == 1) else $error("a = 0,

b = 1, c = 0, d = 0, sel1 = 0, and sel2 = 1 failed");

a = 0; b = 0; c = 0; d = 0; sel1 = 1; sel2 = 0; #10; assert (e == 0) else $error("a = 0,

b = 0, c = 0, d = 0, sel1 = 1, and sel2 = 0 failed"); a = 0; b = 0; c = 1; d = 0; sel1 = 1;

sel2 = 0; #10; assert (e == 1) else $error("a = 0, b = 0, c = 1, d = 0, sel1 = 1, and sel2 = 0 failed"); lOMoAR cPSD| 58833082

a = 0; b = 0; c = 0; d = 0; sel1 = 1; sel2 = 1; #10; assert (e == 0) else $error("a = 0,

b = 0, c = 0, d = 0, sel1 = 1, and sel2 = 1 failed");

a = 0; b = 0; c = 0; d = 1; sel1 = 1; sel2 = 1; #10; assert (e == 1) else $error("a = 0,

b = 0, c = 0, d = 1, sel1 = 1, and sel2 = 1 failed");

a = 1; b = 1; c = 1; d = 1; sel1 = 1; sel2 = 1; #10; assert (e == 1) else $error("a = 1,

b = 1, c = 1, d = 1, sel1 = 1, and sel2 = 1 failed");

a = 1; b = 0; c = 1; d = 0; sel1 = 1; sel2 = 0; #10; assert (e == 1) else $error("a = 1,

b = 0, c = 0, d = 1, sel1 = 1, and sel2 = 0 failed");

a = 0; b = 1; c = 0; d = 1; sel1 = 1; sel2 = 0; #10; assert (e == 0) else $error("a = 0,

b = 1, c = 0, d = 1, sel1 = 1, and sel2 = 0 failed"); end endmodule

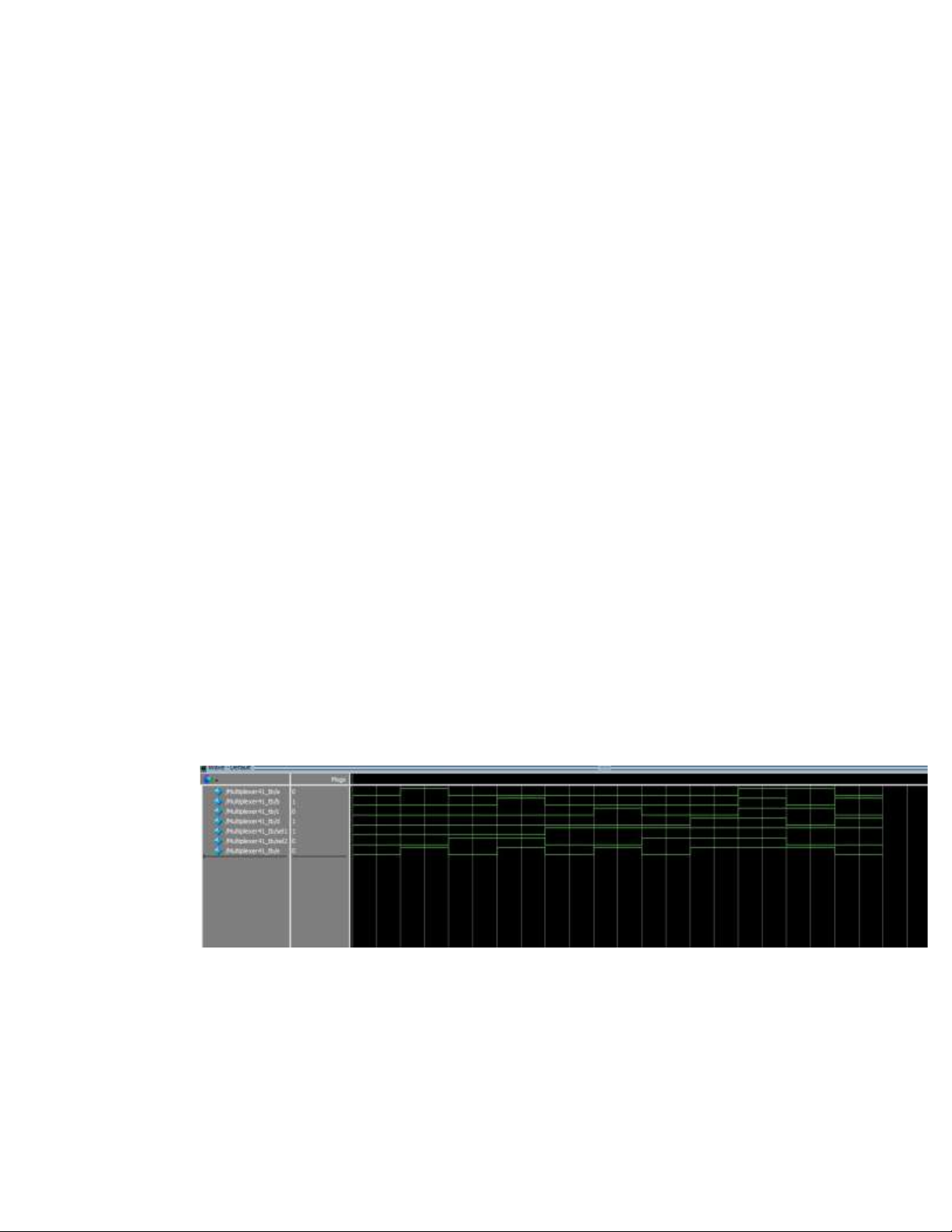

Kết quả chạy mô phỏng như hình dưới đây