Preview text:

ĐẠI HỌC BÁCH KHOA HÀ NỘI

TRƯỜNG ĐIỆN – ĐIỆN TỬ

────────────────────────

BÁO CÁO THỰC TẬP CƠ BẢN

MẠCH ĐẾM THUẬN

Sinh viên thực hiện: Trần Phi Anh Nhật 20234029 Vũ Thế Phong 20234031 Mã lớp: 748517

Hà Nội, ngày 06 tháng 12 năm 2024 1 Mục Lục

I. Các IC và Led 7 thanh. ................................................................................................. 3

1. IC đếm 74LS90. ....................................................................................................... 3

2. IC SN7447. ............................................................................................................... 5

3. IC SN7400. ............................................................................................................... 7

4. Led 7 thanh. .............................................................................................................. 9

II. Tín hiệu số................................................................................................................. 11

III. Các cổng locgic cơ bản. ........................................................................................... 13

1. Cổng NOT. ............................................................................................................. 13

2. Cổng AND. ............................................................................................................ 13

3. Cổng OR. ................................................................................................................ 14

4. Cổng BUFFER. ...................................................................................................... 15

5. Cổng NAND. .......................................................................................................... 15

6. Cổng NOR. ............................................................................................................. 16

7. Cổng EX-OR. ......................................................................................................... 16

8. Cổng EX-NOR. ...................................................................................................... 17

9. Cổng phức AOI (AND-OR-INVERTER). ............................................................. 17

IV. Kết luận. .................................................................................................................. 17 2 I. Các IC và Led 7 thanh. 1. IC đếm 74LS90.

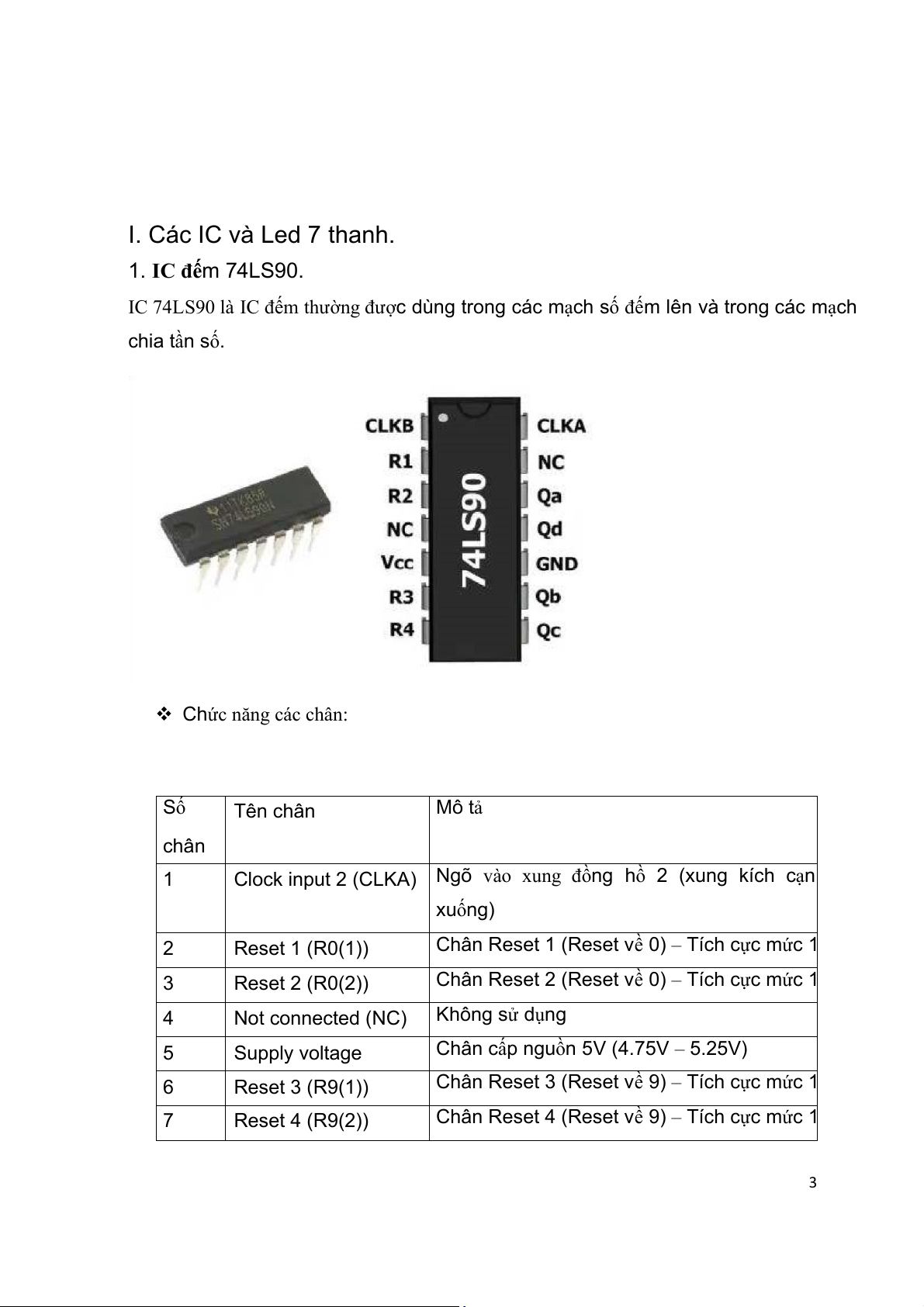

IC 74LS90 là IC đếm thường được dùng trong các mạch số đếm lên và trong các mạch chia tần số. ❖ Chức năng các chân: Số Tên chân Mô tả chân 1

Clock input 2 (CLKA) Ngõ vào xung đồng hồ 2 (xung kích cạn xuống) 2 Reset 1 (R0(1))

Chân Reset 1 (Reset về 0) – Tích cực mức 1 3 Reset 2 (R0(2))

Chân Reset 2 (Reset về 0) – Tích cực mức 1 4 Not connected (NC) Không sử dụng 5 Supply voltage

Chân cấp nguồn 5V (4.75V – 5.25V) 6 Reset 3 (R9(1))

Chân Reset 3 (Reset về 9) – Tích cực mức 1 7 Reset 4 (R9(2))

Chân Reset 4 (Reset về 9) – Tích cực mức 1 3 8 Output 3 (QC) Ngõ ra 3 9 Output 2 (QB) Ngõ ra 2 10 Ground (0V) Chân nối đất 11 Output 4 (QD) Ngõ ra 4 12 Output 1 (QA) Ngõ ra 1 13 Not connected Không sử dụng 14

Clock input 1 (CLKA) Ngõ vào xung đồng hồ 1 (xung kích cạnh xuống)

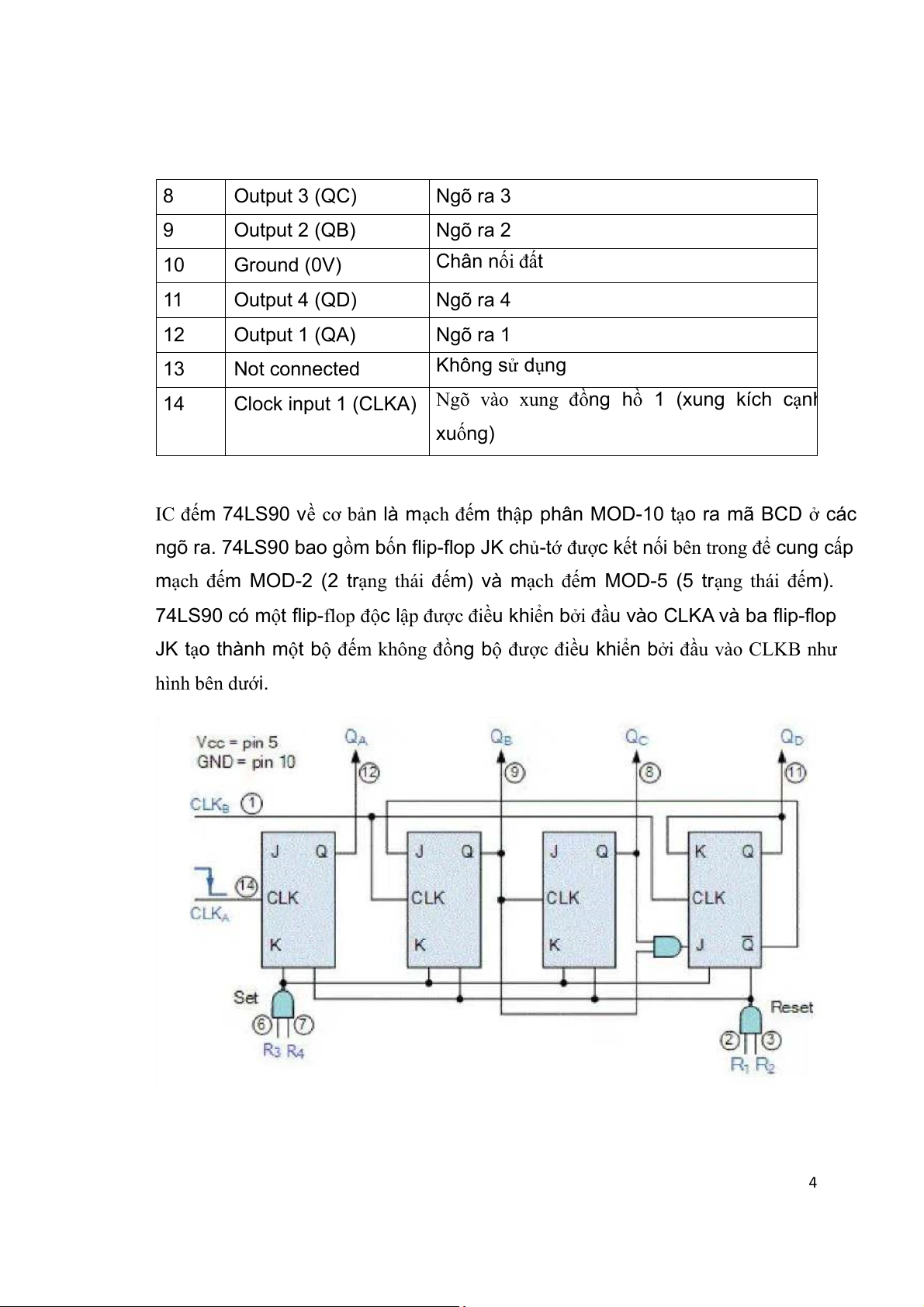

IC đếm 74LS90 về cơ bản là mạch đếm thập phân MOD-10 tạo ra mã BCD ở các

ngõ ra. 74LS90 bao gồm bốn flip-flop JK chủ-tớ được kết nối bên trong để cung cấp

mạch đếm MOD-2 (2 trạng thái đếm) và mạch đếm MOD-5 (5 trạng thái đếm).

74LS90 có một flip-flop độc lập được điều khiển bởi đầu vào CLKA và ba flip-flop

JK tạo thành một bộ đếm không đồng bộ được điều khiển bởi đầu vào CLKB như hình bên dưới. 4

Bốn ngõ ra của IC được ký hiệu là QA, QB, QC và QD. Thứ tự đếm của 74LS90

được kích hoạt bởi cạnh xuống của tín hiệu xung đồng hồ, tức là khi tín hiệu xung

đồng hồ CLK chuyển từ logic 1 (mức CAO) sang logic 0 (mức THẤP) thì xem như

có xung đồng hồ tác động vào mạch đếm.

Các chân ngõ vào bổ sung R1, R2, R3 và R4 là các chân RESET. Khi các ngõ vào

RESET R1 và R2 được kết nối với logic 1, thì mạch đếm sẽ bị RESET trở về 0 (0000)

còn khi các ngõ vào R3 và R4 được kết nối với logic 1, thì mạch đếm được RESET

về số 9 (1001) bất kể số đếm hoặc vị trị đếm hiện tại.

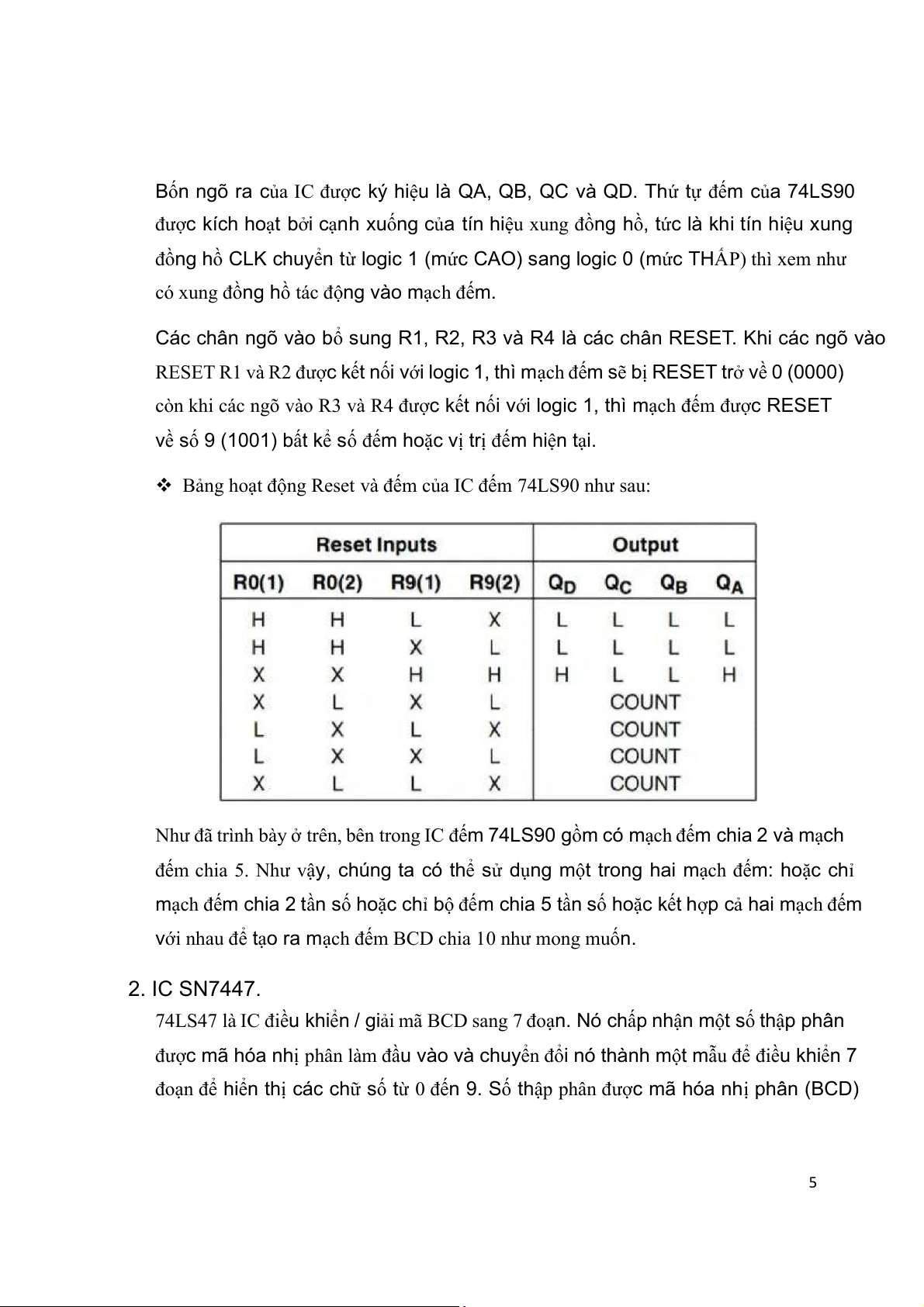

❖ Bảng hoạt động Reset và đếm của IC đếm 74LS90 như sau:

Như đã trình bày ở trên, bên trong IC đếm 74LS90 gồm có mạch đếm chia 2 và mạch

đếm chia 5. Như vậy, chúng ta có thể sử dụng một trong hai mạch đếm: hoặc chỉ

mạch đếm chia 2 tần số hoặc chỉ bộ đếm chia 5 tần số hoặc kết hợp cả hai mạch đếm

với nhau để tạo ra mạch đếm BCD chia 10 như mong muốn. 2. IC SN7447.

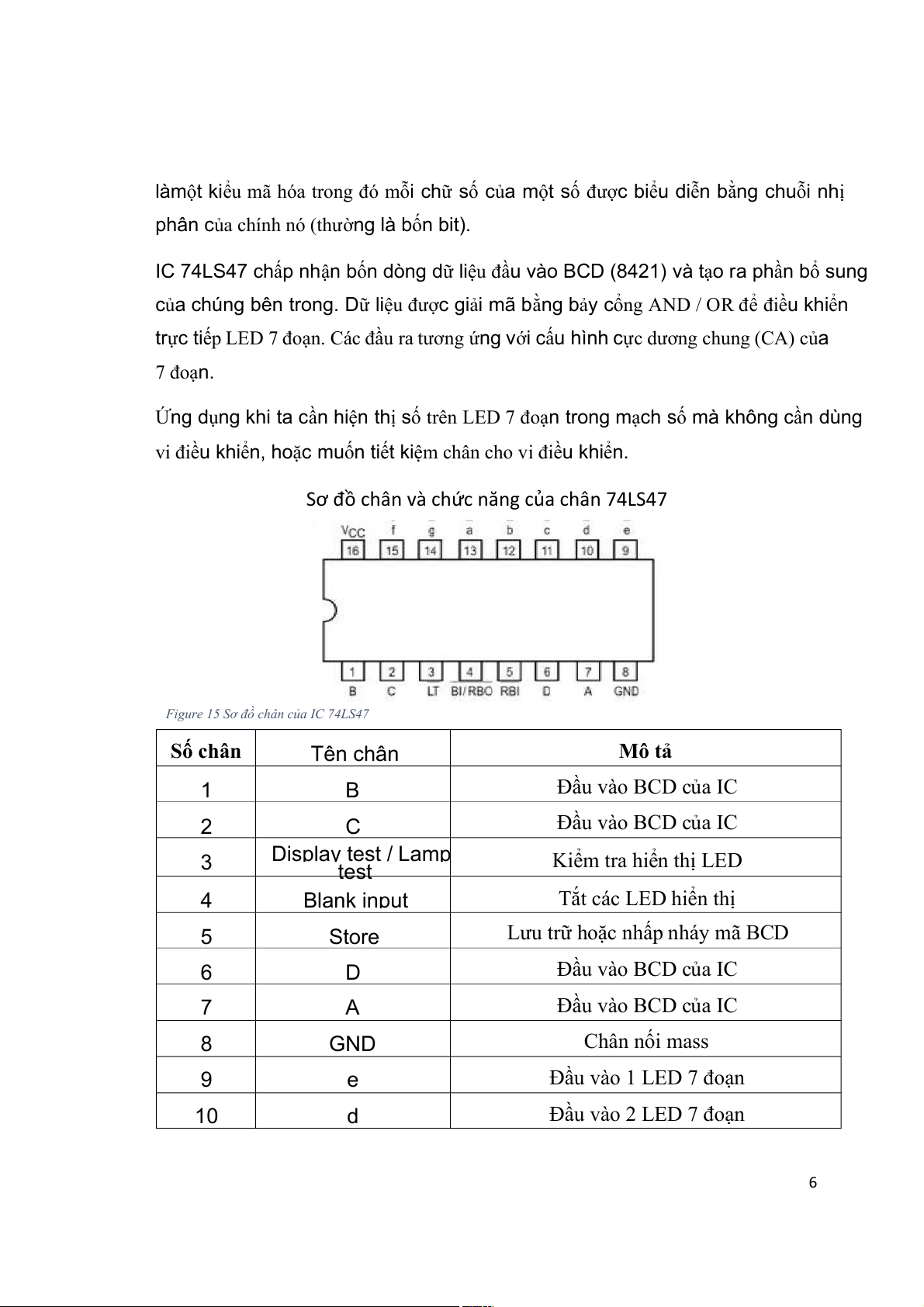

74LS47 là IC điều khiển / giải mã BCD sang 7 đoạn. Nó chấp nhận một số thập phân

được mã hóa nhị phân làm đầu vào và chuyển đổi nó thành một mẫu để điều khiển 7

đoạn để hiển thị các chữ số từ 0 đến 9. Số thập phân được mã hóa nhị phân (BCD) 5

làmột kiểu mã hóa trong đó mỗi chữ số của một số được biểu diễn bằng chuỗi nhị

phân của chính nó (thường là bốn bit).

IC 74LS47 chấp nhận bốn dòng dữ liệu đầu vào BCD (8421) và tạo ra phần bổ sung

của chúng bên trong. Dữ liệu được giải mã bằng bảy cổng AND / OR để điều khiển

trực tiếp LED 7 đoạn. Các đầu ra tương ứng với cấu hình cực dương chung (CA) của 7 đoạn.

Ứng dụng khi ta cần hiện thị số trên LED 7 đoạn trong mạch số mà không cần dùng

vi điều khiển, hoặc muốn tiết kiệm chân cho vi đ ề i u khiển.

Sơ đồ chân và chức năng của chân 74LS47

Figure 15 Sơ đồ chân của IC 74LS47 Số chân Tên chân Mô tả 1 B Đầu vào BCD của IC 2 Đầu vào BCD của IC C 3 Display test / Lamp test Kiểm tra hiển thị LED 4 Blank input Tắt các LED hiển thị

Lưu trữ hoặc nhấp nháy mã BCD 5 Store 6 D Đầu vào BCD của IC 7 A Đầu vào BCD của IC 8 GND Chân nối mass 9 e Đầu vào 1 LED 7 đoạn 10 d Đầu vào 2 LED 7 đoạn 6

IC 74LS47 thường được sử dụng ở 4 chế độ hoạt động:

• Sáng bình thường đủ các trạng thái từ 0 ÷ 9 (thường dùng nhất). Chân BI/RBO

phải bỏ trống hoặc nối lên mức cao, chân RBI phải bỏ trống hoặc nối lên mức

cao, chân LT phải bỏ trống hoặc nối lên mức cao.

• Chân BI/RBO nối xuống mức thấp thì tất các các đoạn của LED đều không

sáng bất chấp trạng thái của các ngõ vào còn lại.

• Bỏ trạng thái số 0 (khi giá trị BCD tại ngõ vào bằng 0 thì tất cả các đoạn của

LED 7 đoạn đều tắt). Chân RBI ở mức thấp và chân BI/RBO phải bỏ trống

(và nó đóng vai trò là ngõ ra).

• Chân BI/RBO phải bỏ trống hoặc nối lên mức cao và chân LT phải nối xuống

mức thấp. Tất cả các thanh của LED 7 đoạn đều sáng, bất chấp các ngõ vào

BCD. Dùng để Kiểm tra các đoạn của LED 7 đoạn (còn sáng hay đã chết). 3. IC SN7400.

IC SN7400 là họ logic phổ biến nhất trong mạch tích hợp, có thể được xây dựng với một

số thiết bị, cung cấp tất cả các cổng logic cơ bản, FF (dép xỏ ngón), bộ đếm ALU, và bộ

thu phát xe buýt. Họ IC số mở rộng là IC 7400 series. Dòng IC này chủ yếu bao gồm các

chip logic kín đáo khác nhau như cổng logic cùng với các thanh ghi, bộ nhớ RAM và bộ giải mã khác nhau.

IC 7400 là một chip 14 chân và nó bao gồm bốn cổng NAND 2 đầu vào. Mỗi cổng đều

sử dụng chân 2 đầu vào & chân 1 đầu ra, bởi 2 chân còn lại là nguồn và đất. Con chip

này được tạo ra với các gói khác nhau như giá đỡ bề mặt và lỗ xuyên qua, bao gồm gói

gốm (hoặc) nhựa kép trong dòng và gói phẳng.

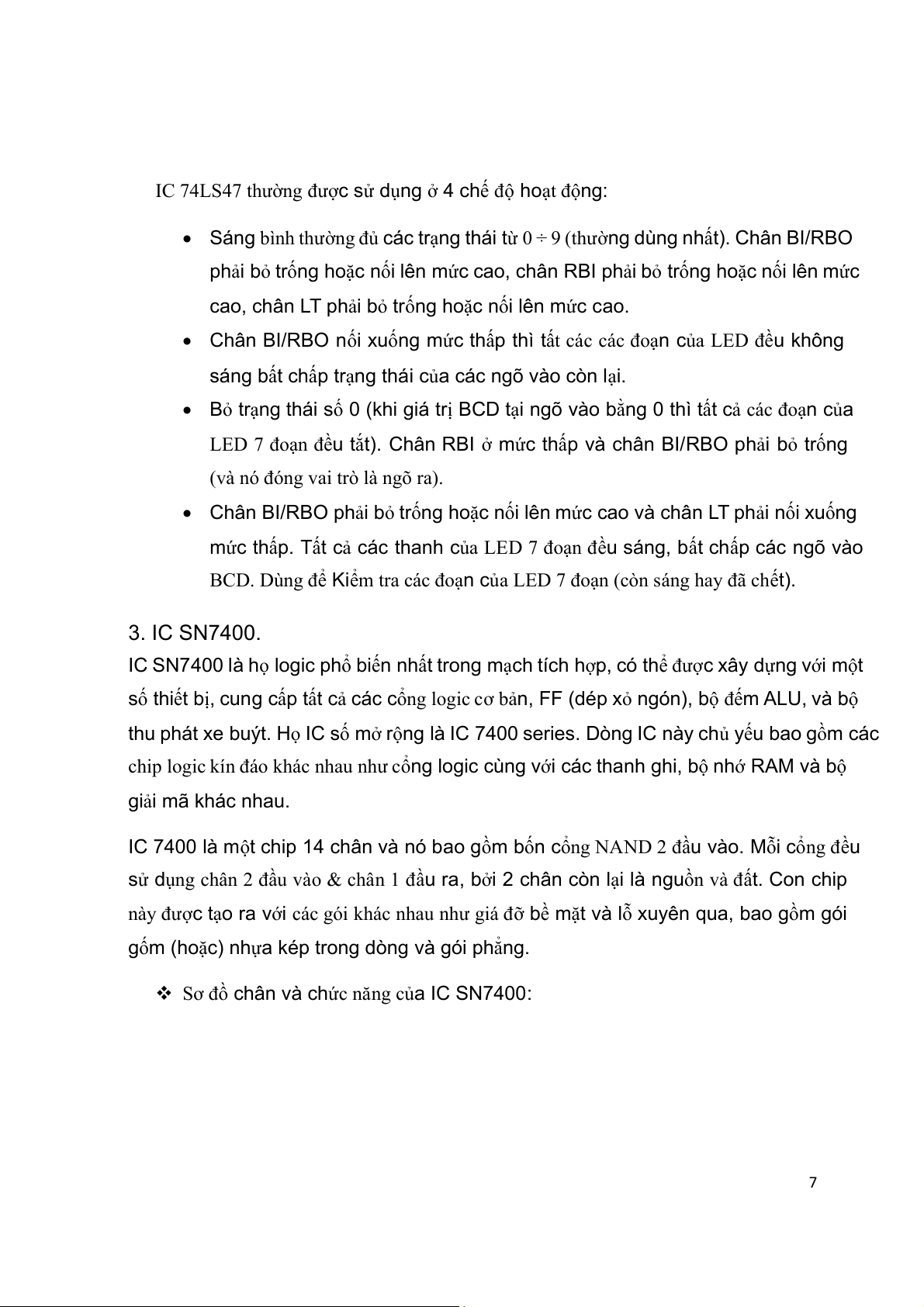

❖ Sơ đồ chân và chức năng của IC SN7400: 7

Figure 16 Sơ đồ chân của IC SN7400 Số chân Tên chân Mô tả 1 1 A Đây là cổng A-input-1 2 1 B Cổng vào B-1 3 1 Y Cổng ra Y-1 4 2 A Cổng A-input-2 5 2 B Cổng đầu vào B-2 6 2 Y Cổng ra Y-2 7 GND

Thiết bị đầu cuối GND 8 3 Y Cổng ra Y-3 9 3 A Cổng A-input-3 10 3 B Cổng đầu vào B-3 8 11 4 Y Cổng đầu ra Y-4 4. Led 7 thanh.

LED 7 thanh hay còn được gọi là LED 7 đoạn, bao gồm 7 đoạn đèn LED được xếp lại

với nhau thành hình chữ nhật. Khi các đoạn lập trình để chiếu sáng thì sẽ hiển thị chữ số

của hệ thập phân hoặc thập lục phân. Đôi khi LED số 8 được hiển thị dấu thập phân khi

có nhiều LED 7 thanh được nối với nhau để có thể hiển thị được các số lớn hơn 2 chữ số.

Với các đoạn LED trong màn hình đều được nối với các chân kết nối để đưa ra ngoài.

Các chân này được gán các ký tự từ a đến g, chúng đại diện cho từng LED riêng lẻ. Các

chân được kết nối với nhau để có thể tạo thành một chân chung.

Chân Pin chung hiển thị thường được sử dụng để có thể xác định loại màn hình LED 7

thanh đó là loại nào. Có 2 loại LED 7 thanh được sử dụng đó là Cathode chung (CC) và Anode chung (CA):

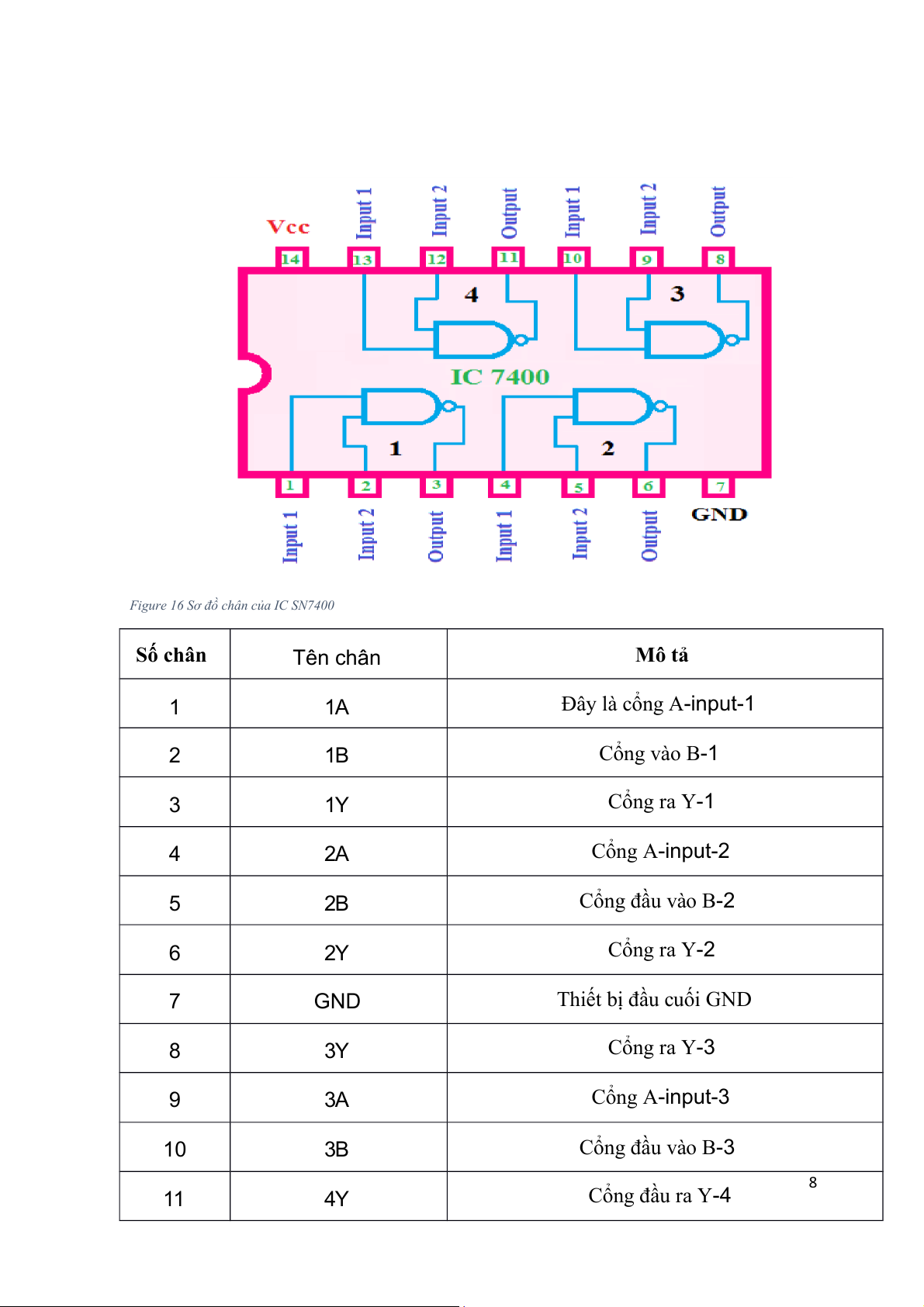

• Cathode chung (CC): Trong màn hình Cathode chung thì tất cả các cực

Cathode cả các đèn LED được nối chung với nhau với mức logic “0” hoặc nối

Mass (Ground). Các chân còn lại là chân Anode sẽ được nối với tín hiệu logic

mức cao (HIGHT) hay mức logic 1 thông qua 1 điện trở giới hạn dòng điện 9

để có thể đưa điện áp vào phân cực ở Anode từ a đến G để có thể hiển thị tùy ý.

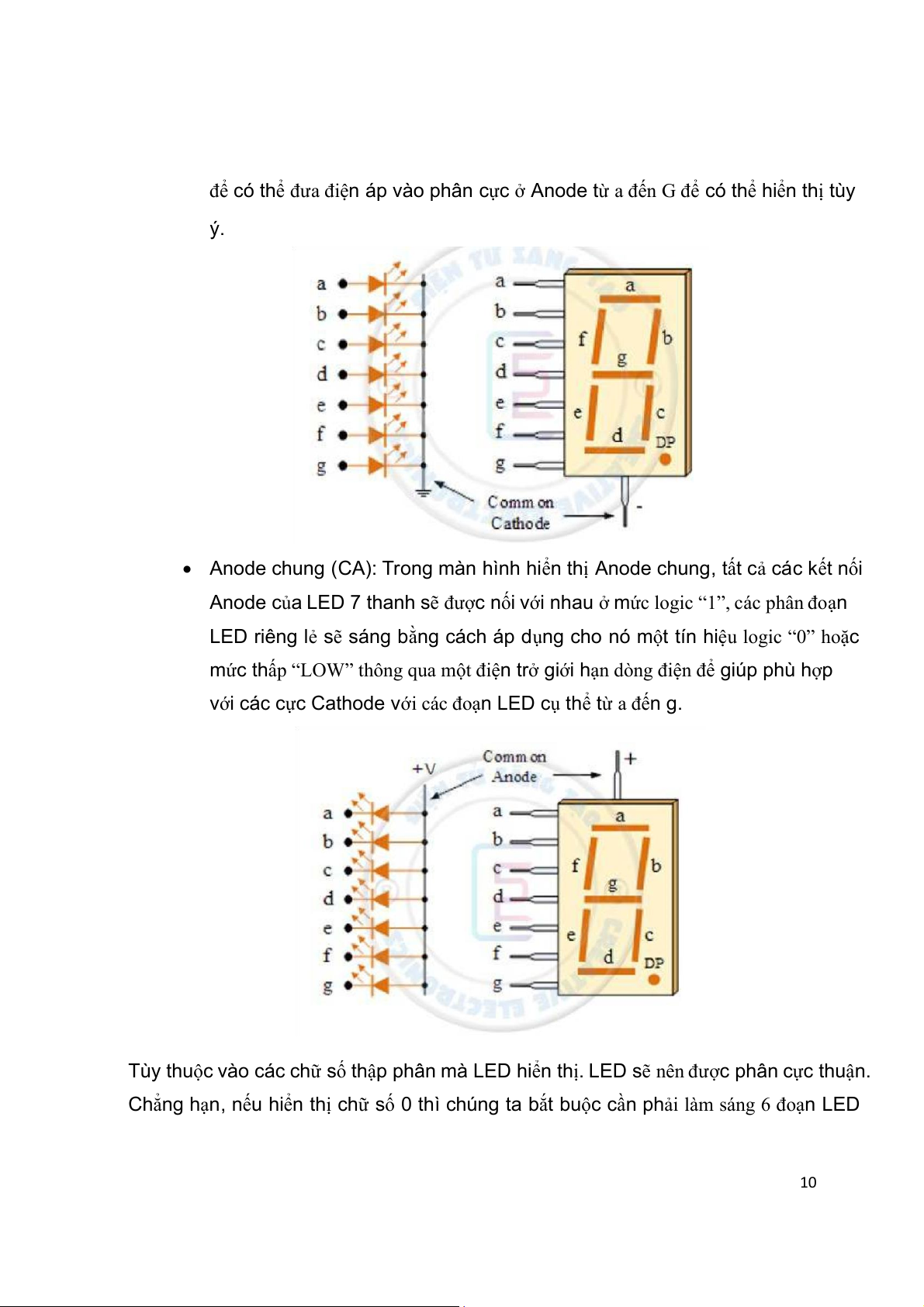

• Anode chung (CA): Trong màn hình hiển thị Anode chung, tất cả các kết nối

Anode của LED 7 thanh sẽ được nối với nhau ở mức logic “1”, các phân đoạn

LED riêng lẻ sẽ sáng bằng cách áp dụng cho nó một tín hiệu logic “0” hoặc

mức thấp “LOW” thông qua một điện trở giới hạn dòng điện để giúp phù hợp

với các cực Cathode với các đoạn LED cụ thể từ a đến g.

Tùy thuộc vào các chữ số thập phân mà LED hiển thị. LED sẽ nên được phân cực thuận.

Chẳng hạn, nếu hiển thị chữ số 0 thì chúng ta bắt buộc cần phải làm sáng 6 đoạn LED 10

tương ứng đó à a, b, c, d, f. Do đó, các con số khác nhau sẽ được thể hiện từ 0 – 9 trên màn hình.

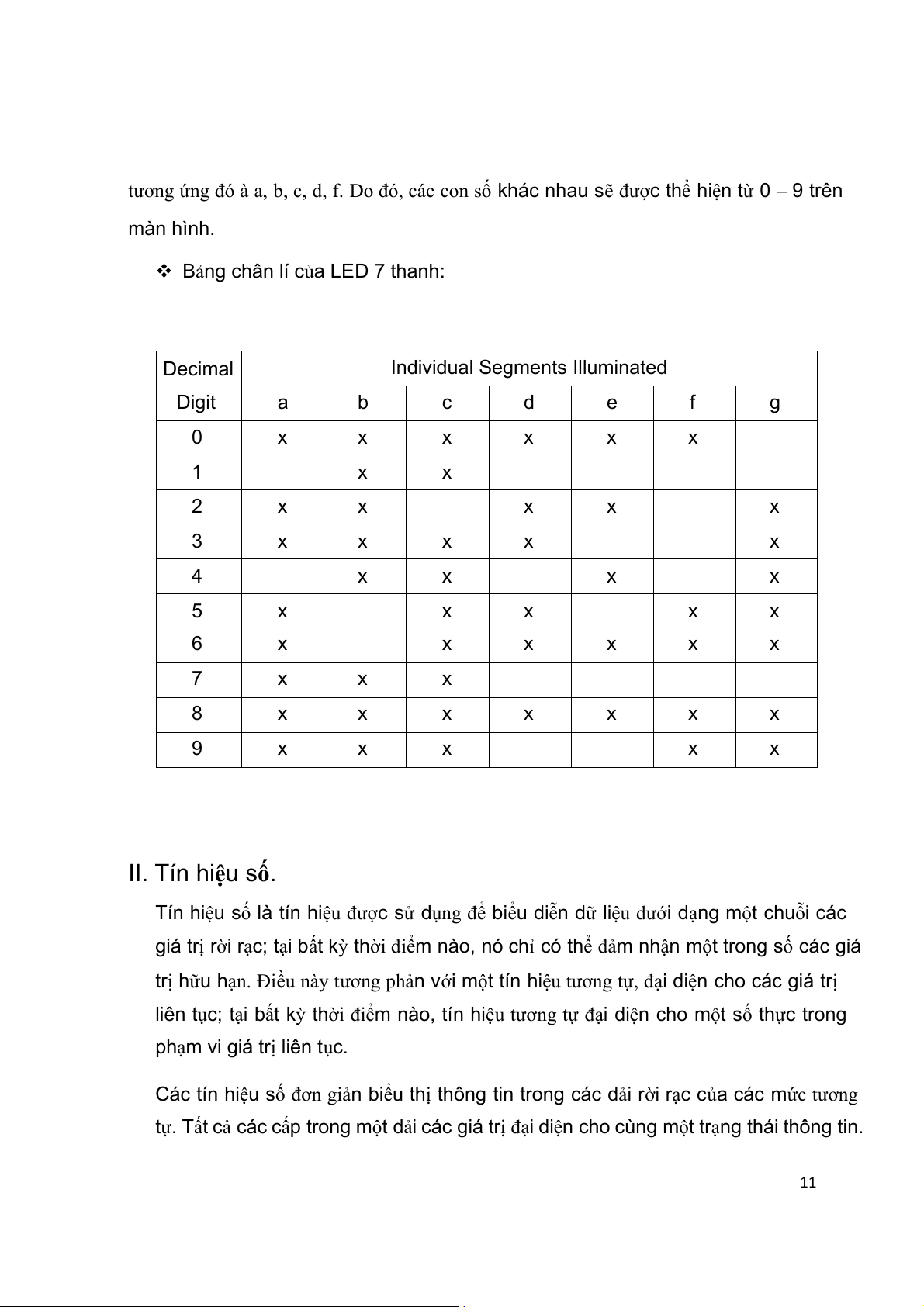

❖ Bảng chân lí của LED 7 thanh: Decimal

Individual Segments Il uminated Digit a b c d e f g 0 x x x x x x 1 x x 2 x x x x x 3 x x x x x 4 x x x x 5 x x x x x 6 x x x x x x 7 x x x 8 x x x x x x x 9 x x x x x

II. Tín hiệu số.

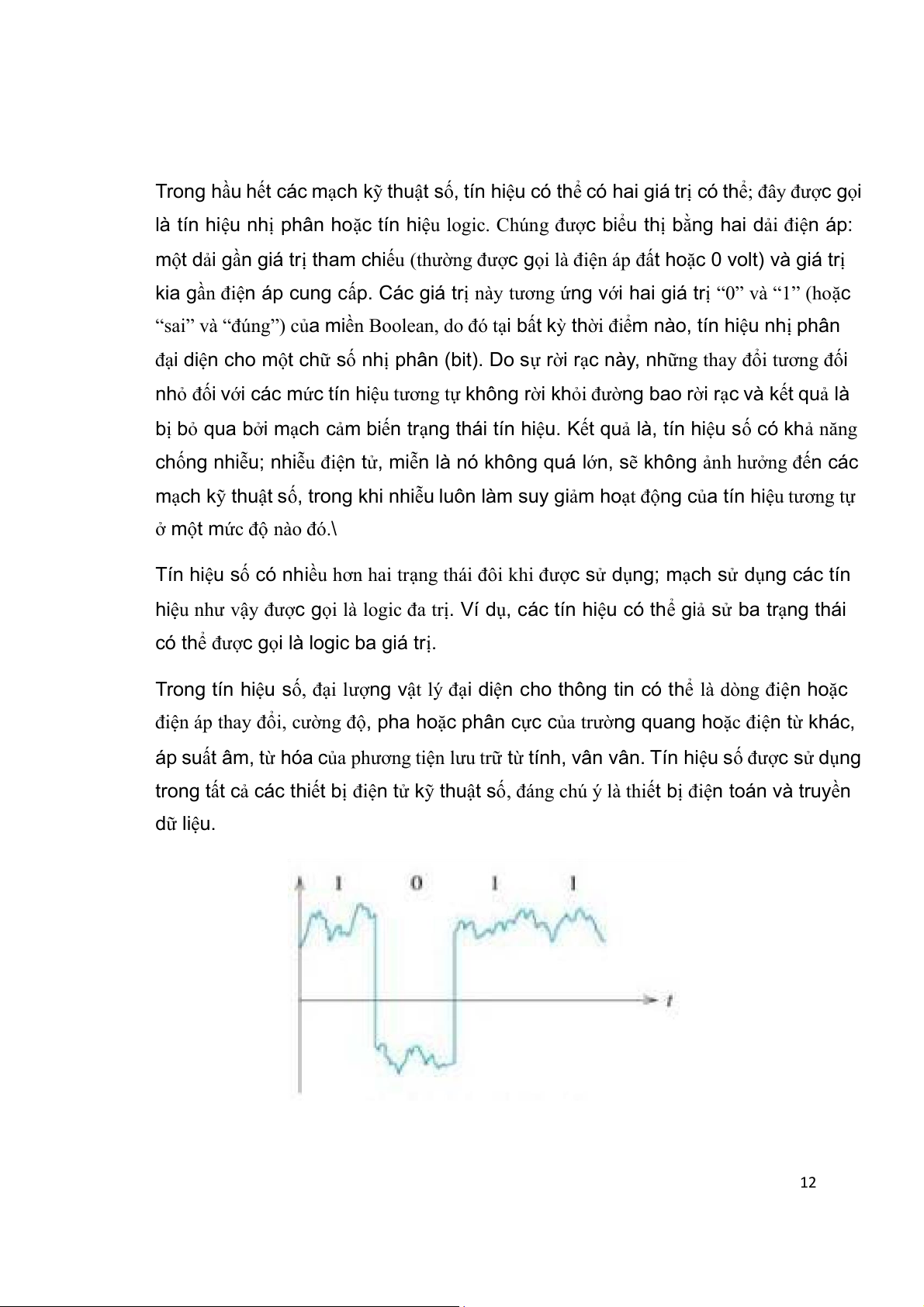

Tín hiệu số là tín hiệu được sử dụng để biểu diễn dữ liệu dưới dạng một chuỗi các

giá trị rời rạc; tại bất kỳ thời điểm nào, nó chỉ có thể đảm nhận một trong số các giá

trị hữu hạn. Điều này tương phản với một tín hiệu tương tự, đại diện cho các giá trị

liên tục; tại bất kỳ thời điểm nào, tín hiệu tương tự đại diện cho một số thực trong

phạm vi giá trị liên tục.

Các tín hiệu số đơn giản biểu thị thông tin trong các dải rời rạc của các mức tương

tự. Tất cả các cấp trong một dải các giá trị đại diện cho cùng một trạng thái thông tin. 11

Trong hầu hết các mạch kỹ thuật số, tín hiệu có thể có hai giá trị có thể; đây được gọi

là tín hiệu nhị phân hoặc tín hiệu logic. Chúng được biểu thị bằng hai dải điện áp:

một dải gần giá trị tham chiếu (thường được gọi là điện áp đất hoặc 0 volt) và giá trị

kia gần điện áp cung cấp. Các giá trị này tương ứng với hai giá trị “0” và “1” (hoặc

“sai” và “đúng”) của miền Boolean, do đó tại bất kỳ thời điểm nào, tín hiệu nhị phân

đại diện cho một chữ số nhị phân (bit). Do sự rời rạc này, những thay đổi tương đối

nhỏ đối với các mức tín hiệu tương tự không rời khỏi đường bao rời rạc và kết quả là

bị bỏ qua bởi mạch cảm biến trạng thái tín hiệu. Kết quả là, tín hiệu số có khả năng

chống nhiễu; nhiễu điện tử, miễn là nó không quá lớn, sẽ không ảnh hưởng đến các

mạch kỹ thuật số, trong khi nhiễu luôn làm suy giảm hoạt động của tín hiệu tương tự

ở một mức độ nào đó.\

Tín hiệu số có nhiều hơn hai trạng thái đôi khi được sử dụng; mạch sử dụng các tín

hiệu như vậy được gọi là logic đa trị. Ví dụ, các tín hiệu có thể giả sử ba trạng thái

có thể được gọi là logic ba giá trị.

Trong tín hiệu số, đại lượng vật lý đại diện cho thông tin có thể là dòng điện hoặc

điện áp thay đổi, cường độ, pha hoặc phân cực của trường quang hoặc điện từ khác,

áp suất âm, từ hóa của phương tiện lưu trữ từ tính, vân vân. Tín hiệu số được sử dụng

trong tất cả các thiết bị điện tử kỹ thuật số, đáng chú ý là thiết bị điện toán và truyền dữ liệu. 12

Tín hiệu số nhận được có thể bị suy giảm do nhiễu và biến dạng mà không nhất thiết

ảnh hưởng đến các số.

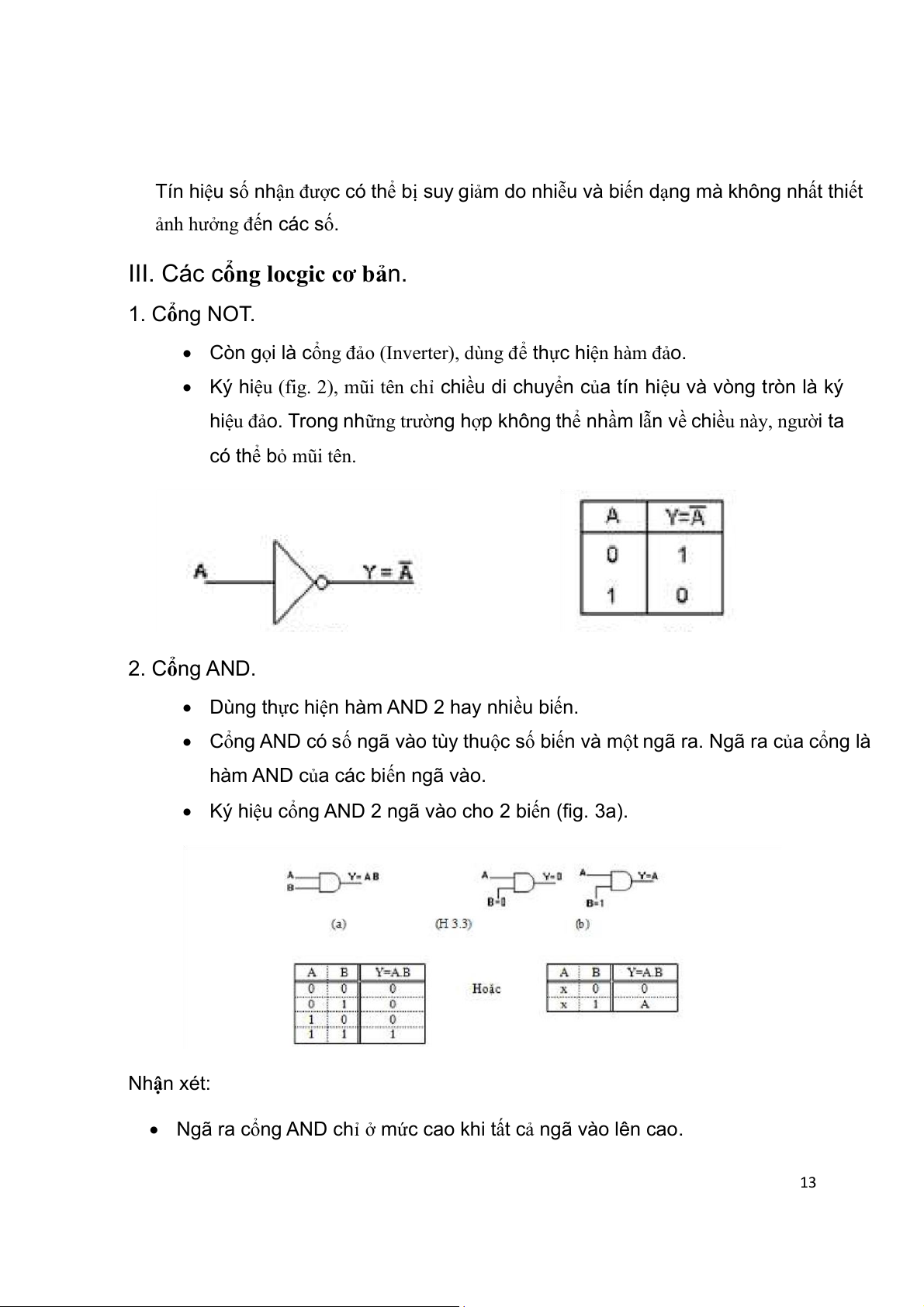

III. Các cổng locgic cơ bản. 1. Cổng NOT.

• Còn gọi là cổng đảo (Inverter), dùng để thực hiện hàm đảo.

• Ký hiệu (fig. 2), mũi tên chỉ chiều di chuyển của tín hiệu và vòng tròn là ký

hiệu đảo. Trong những trường hợp không thể nhầm lẫn về chiều này, người ta có thể bỏ mũi tên. 2. Cổng AND.

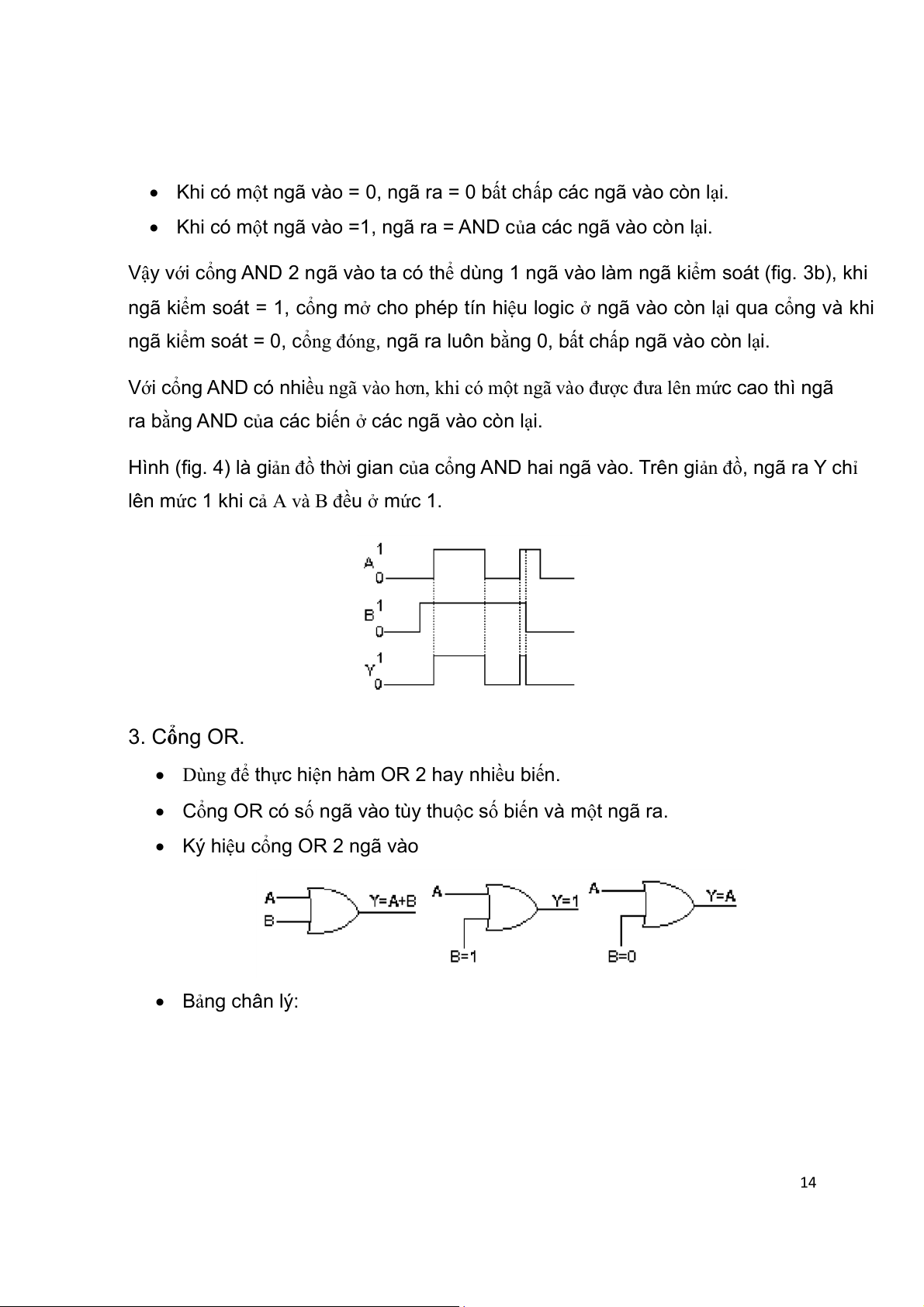

• Dùng thực hiện hàm AND 2 hay nhiều biến.

• Cổng AND có số ngã vào tùy thuộc số biến và một ngã ra. Ngã ra của cổng là

hàm AND của các biến ngã vào.

• Ký hiệu cổng AND 2 ngã vào cho 2 biến (fig. 3a). Nhận xét:

• Ngã ra cổng AND chỉ ở mức cao khi tất cả ngã vào lên cao. 13

• Khi có một ngã vào = 0, ngã ra = 0 bất chấp các ngã vào còn lại.

• Khi có một ngã vào =1, ngã ra = AND của các ngã vào còn lại.

Vậy với cổng AND 2 ngã vào ta có thể dùng 1 ngã vào làm ngã kiểm soát (fig. 3b), khi

ngã kiểm soát = 1, cổng mở cho phép tín hiệu logic ở ngã vào còn lại qua cổng và khi

ngã kiểm soát = 0, cổng đóng, ngã ra luôn bằng 0, bất chấp ngã vào còn lại.

Với cổng AND có nhiều ngã vào hơn, khi có một ngã vào được đưa lên mức cao thì ngã

ra bằng AND của các biến ở các ngã vào còn lại .

Hình (fig. 4) là giản đồ thời gian của cổng AND hai ngã vào. Trên giản đồ, ngã ra Y chỉ

lên mức 1 khi cả A và B đều ở mức 1. 3. Cổng OR.

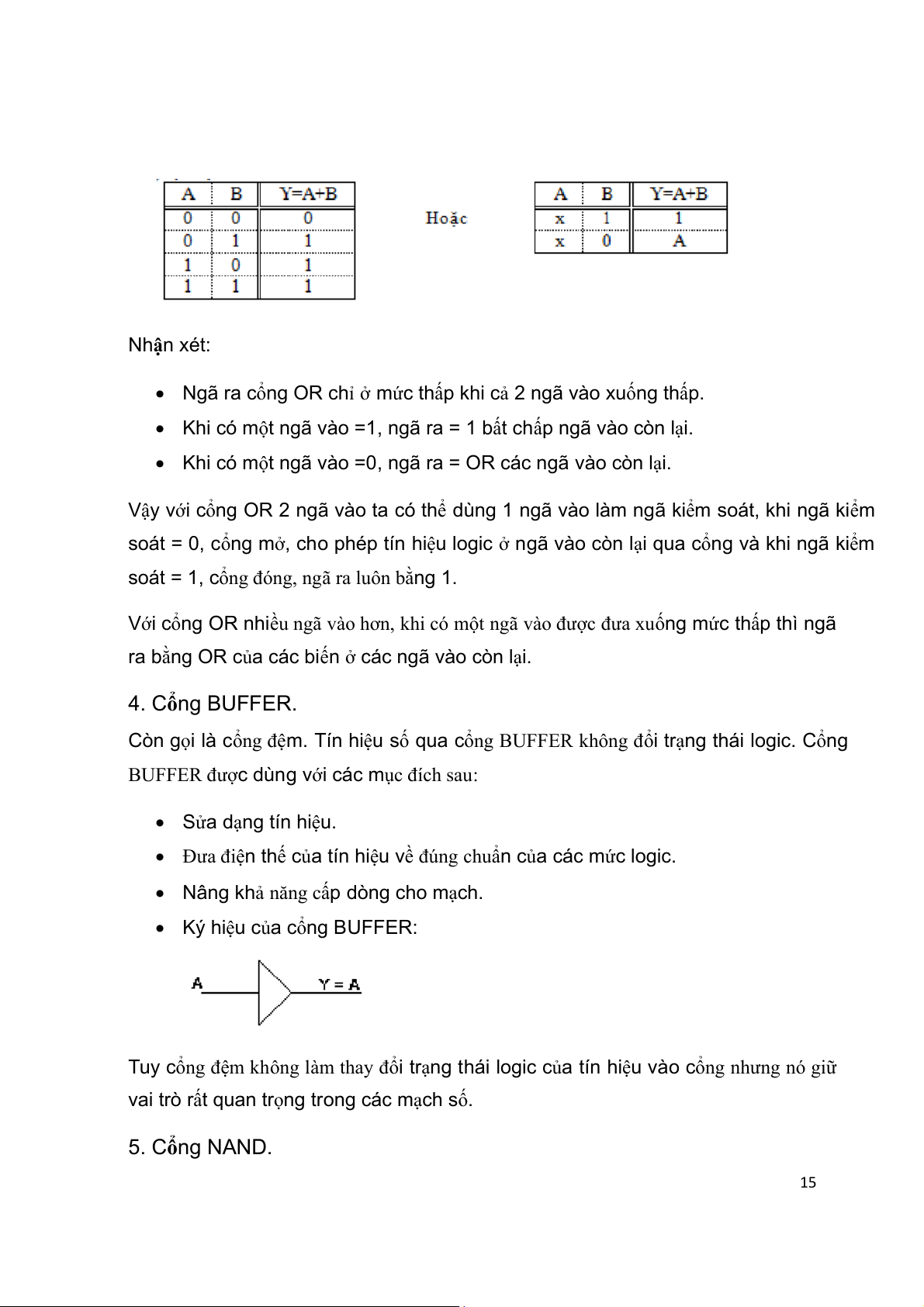

• Dùng để thực hiện hàm OR 2 hay nhiều biến.

• Cổng OR có số ngã vào tùy thuộc số biến và một ngã ra.

• Ký hiệu cổng OR 2 ngã vào • Bảng chân lý: 14 Nhận xét:

• Ngã ra cổng OR chỉ ở mức thấp khi cả 2 ngã vào xuống thấp.

• Khi có một ngã vào =1, ngã ra = 1 bất chấp ngã vào còn lại.

• Khi có một ngã vào =0, ngã ra = OR các ngã vào còn lại.

Vậy với cổng OR 2 ngã vào ta có thể dùng 1 ngã vào làm ngã kiểm soát, khi ngã kiểm

soát = 0, cổng mở, cho phép tín hiệu logic ở ngã vào còn lại qua cổng và khi ngã kiểm

soát = 1, cổng đóng, ngã ra luôn bằng 1.

Với cổng OR nhiều ngã vào hơn, khi có một ngã vào được đưa xuống mức thấp thì ngã

ra bằng OR của các biến ở các ngã vào còn lại. 4. Cổng BUFFER.

Còn gọi là cổng đệm. Tín hiệu số qua cổng BUFFER không đổi trạng thái logic. Cổng

BUFFER được dùng với các mục đích sau: • Sửa dạng tín hiệu.

• Đưa điện thế của tín hiệu về đúng chuẩn của các mức logic.

• Nâng khả năng cấp dòng cho mạch.

• Ký hiệu của cổng BUFFER:

Tuy cổng đệm không làm thay đổi trạng thái logic của tín hiệu vào cổng nhưng nó giữ

vai trò rất quan trọng trong các mạch số. 5. Cổng NAND. 15

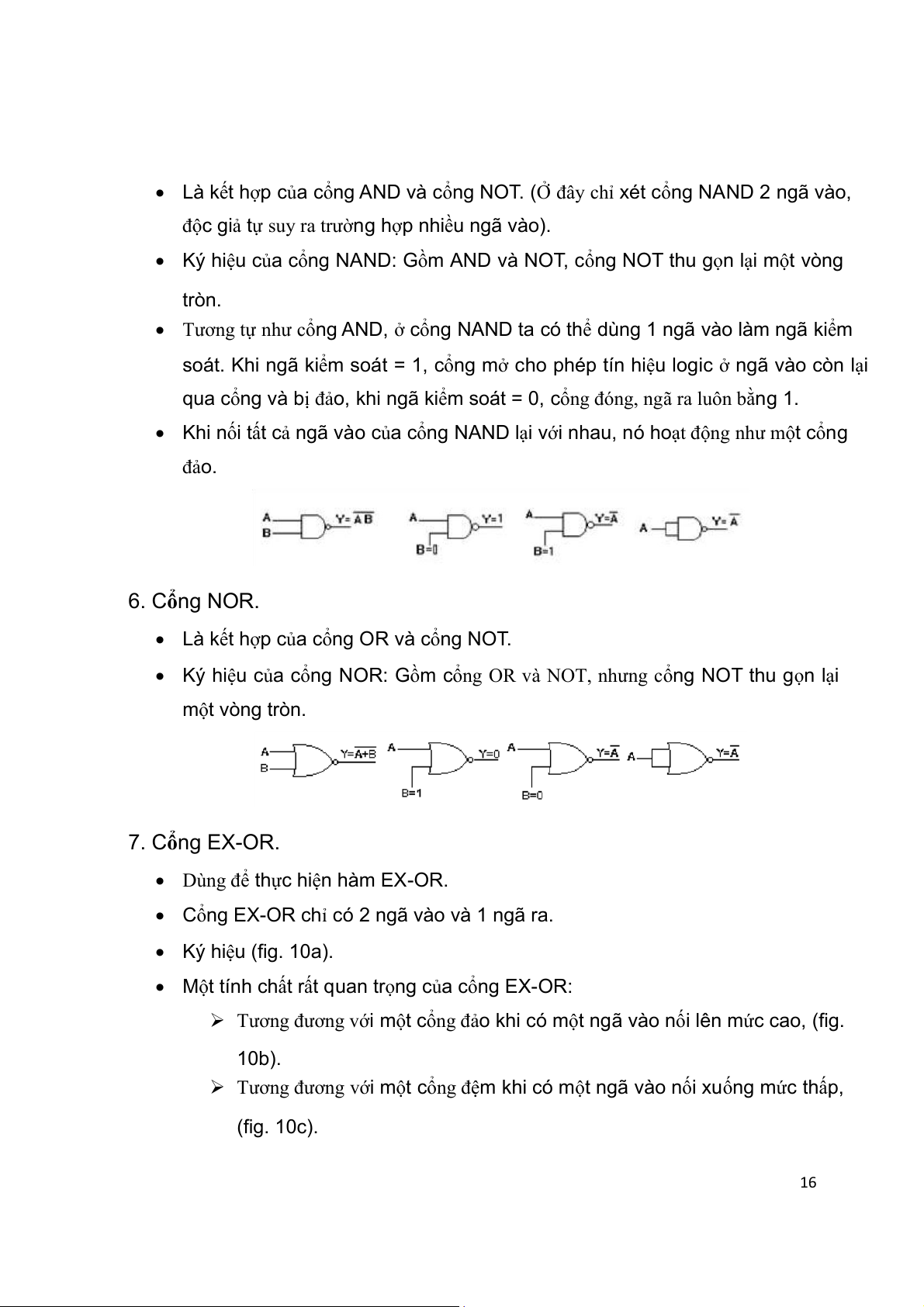

• Là kết hợp của cổng AND và cổng NOT. (Ở đây chỉ xét cổng NAND 2 ngã vào,

độc giả tự suy ra trường hợp nhiều ngã vào).

• Ký hiệu của cổng NAND: Gồm AND và NOT, cổng NOT thu gọn lại một vòng tròn.

• Tương tự như cổng AND, ở cổng NAND ta có thể dùng 1 ngã vào làm ngã kiểm

soát. Khi ngã kiểm soát = 1, cổng mở cho phép tín hiệu logic ở ngã vào còn lại

qua cổng và bị đảo, khi ngã kiểm soát = 0, cổng đóng, ngã ra luôn bằng 1.

• Khi nối tất cả ngã vào của cổng NAND lại với nhau, nó hoạt động như một cổng đảo. 6. Cổng NOR.

• Là kết hợp của cổng OR và cổng NOT.

• Ký hiệu của cổng NOR: Gồm cổng OR và NOT, nhưng cổng NOT thu gọn lại một vòng tròn. 7. Cổng EX-OR.

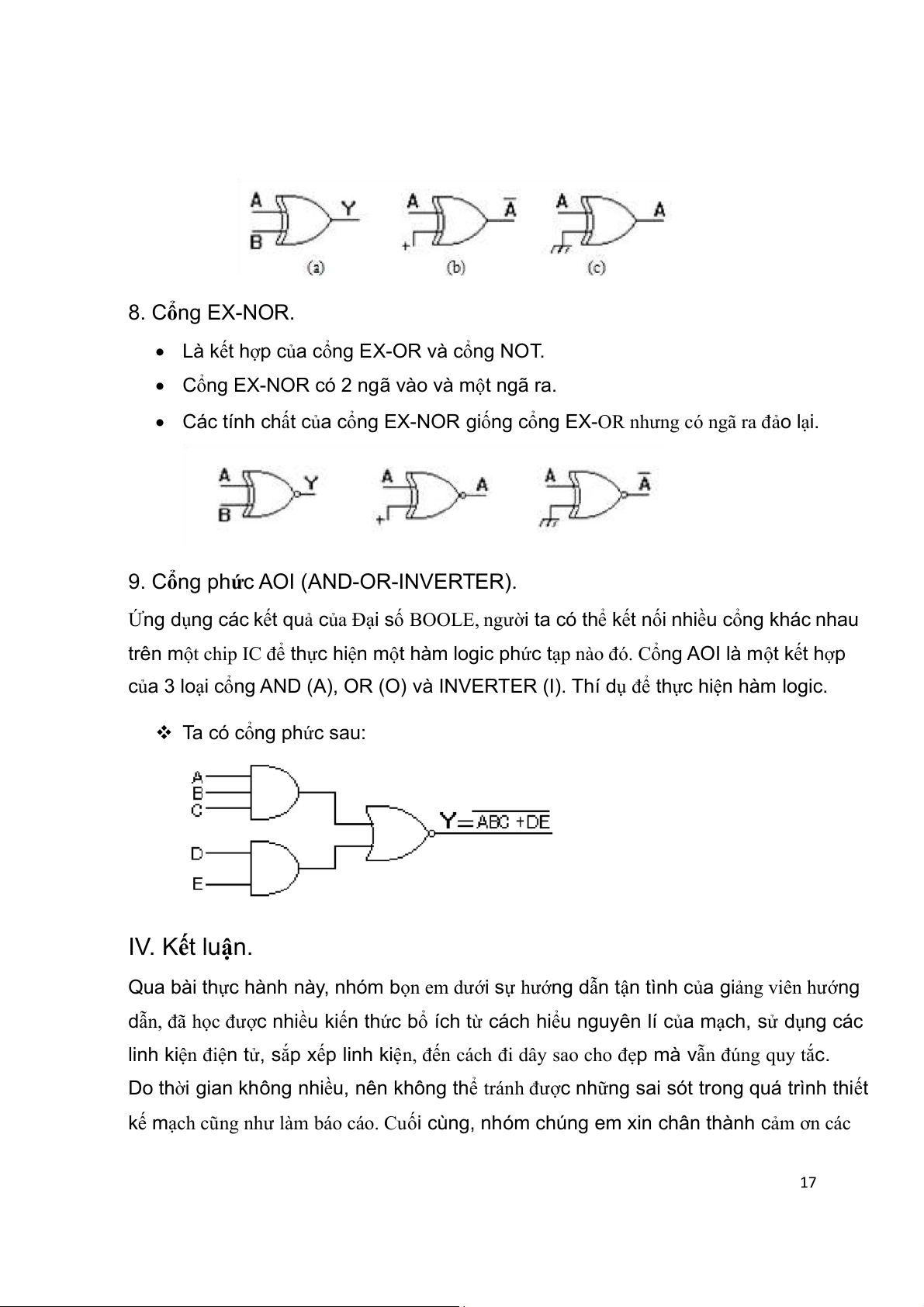

• Dùng để thực hiện hàm EX-OR.

• Cổng EX-OR chỉ có 2 ngã vào và 1 ngã ra. • Ký hiệu (fig. 10a).

• Một tính chất rất quan trọng của cổng EX-OR:

➢ Tương đương với một cổng đảo khi có một ngã vào nối lên mức cao, (fig. 10b).

➢ Tương đương với một cổng đệm khi có một ngã vào nối xuống mức thấp, (fig. 10c). 16 8. Cổng EX-NOR.

• Là kết hợp của cổng EX-OR và cổng NOT.

• Cổng EX-NOR có 2 ngã vào và một ngã ra.

• Các tính chất của cổng EX-NOR giống cổng EX-OR nhưng có ngã ra đảo lại .

9. Cổng phức AOI (AND-O - R INVERTER).

Ứng dụng các kết quả của Đại số BOOLE, người ta có thể kết nối nhiều cổng khác nhau

trên một chip IC để thực hiện một hàm logic phức tạp nào đó. Cổng AOI là một kết hợp

của 3 loại cổng AND (A), OR (O) và INVERTER (I). Thí dụ để thực hiện hàm logic. ❖ Ta có cổng phức sau:

IV. Kết luận.

Qua bài thực hành này, nhóm bọn em dưới sự hướng dẫn tận tình của giảng viên hướng

dẫn, đã học được nhiều kiến thức bổ ích từ cách hiểu nguyên lí của mạch, sử dụng các

linh kiện điện tử, sắp xếp linh kiện, đến cách đi dây sao cho đẹp mà vẫn đúng quy tắc.

Do thời gian không nhiều, nên không thể tránh được những sai sót trong quá trình thiết

kế mạch cũng như làm báo cáo. Cuối cùng, nhóm chúng em xin chân thành cảm ơn các 17

thầy cô giảng viên đã tận tình giúp đỡ và chỉ bảo chúng em trong suốt quá trình học tập và thực hành. 18