Preview text:

ĐẠI HỌC BÁCH KHOA HÀ NỘI

TRƯỜNG ĐIỆN – ĐIỆN TỬ

BÁO CÁO MÔN THỰC TẬP CƠ BẢN

ĐỀ TÀI: MẠCH KỸ THUẬT SỐ VỚI BỘ ĐẾM THUẬN

(từ 00 đến 59)

Giáo viên hướng dẫn: Tào Văn Cường Mã lớp: 742333 Sinh viên thực hiện: MSSV Trịnh Tuấn Quốc 20220078 Phạm Viết Luật 20224048

Hà Nội, ngày 29 tháng 03 năm 2024 MỤC LỤC I.

CƠ SỞ LÝ THUYẾT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1. Tìm hiểu về tín hiệu số và ứng dụng . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1. Tín hiệu số . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.2. Ứng dụng. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Các cổng logic cơ bản và thuật toán logic . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2.1. Cổng NOT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2.2. Cổng AND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2.3. Cổng OR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2.4. Cổng NAND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 2.5 Cổn

g NOR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3. Các ICs và LED 7 thanh trong mạch đếm thuận . . . . . . . . . . . . . . . . . . . 5

3.1. IC đếm 74LS90 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.2. IC giải mã 74LS47 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

3.3 IC 74LS00 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

3.4. LED 7 thanh . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 II.

THỰC HÀNH . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

1. Tên bài thực hành . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2. Linh kiện . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3. Sơ đồ khối . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

4. Nguyên lý hoạt động . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

5. Sơ đồ thiết kế . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

I. CƠ SỞ LÝ THUYẾT

1. Tìm hiểu về tín hiệu số và ứng dụng

1.1. Tín hiệu số

- Tín hiệu số là tín hiệu được sử dụng để biểu diễn dữ liệu dưới dạng một

chuỗi các giá trị rời rạc, tại bất kỳ thời điểm nào, nó chỉ có thể đảm nhận một

trong số các giá trị hữu hạn. Điều này tương phản nới một tín hiệu tương tự, đại

diện cho các giá trị liên tục, tại bất kỳ thời điểm nào, tín hiệu tương tự đại diện

cho một số thực trong phạm vi giá trị liên tục.

- Các tín hiệu số đơn giản biểu thị thông tin trong các dải rời rạc của các

mức tương tự. Tất cả các cấp trong một dải các giá trị đại diện cho cùng một giá

trạng thái thông tin. Trong hầu hết các mạch kỹ thuật số, tín hiệu có thể có hai giá

trị, đây được gọi là tín hiệu nhị phân hoặc tín hiệu logic. Chúng được biểu thị

bằng hai dải điện áp, một dải gần giá trị tham chiếu (thường được gọi là điện áp

đất (hoặc 0 volt) và giá trị kia gần điện áp cung cấp. cá giá trị này tương ứng với

hai giá trị “0” và “1” (hoặc “sai” hoặc “đúng”) của miền Boolen. Do đó tại bất kỳ

thời điểm nào, tín hiệu nhị phân đại diện cho một chữ số nhị phân (bit). Do sự rời

rạc này, những thay đổi tương đối nhỏ đói với các mức tín hiệu tương tự không

rời khỏi đường bao rời rạc và kết quả là bị bỏ qua bởi mạch cảm biến trạng thái

tín hiệu. Kết quả là, các tín hiệu số có khả năng chống nhiễu, nhiễu điện tử, miễn

là nó không quá lớn, sẽ không ảnh hưởng đến các mạch kỹ thuật số, trong khi

nhiễu luôn làm suy giảm hoạt động của tín hiệu tương tự ở một mức độ nào đó.

- Tín hiệu số có nhiều hơn hai trạng thái đôi khi được sử dụng, mạch sử

dụng các tín hiệu như vậy được gọi là logic đa trị.

- Trong tín hiệu số, đại lượng vật lý đại diện cho thông tin có thể là dòng

điện hoặc điện áp thay đổi, cường độ, pha hoặc phân cực của trường quang hoặc

điện tử khác, áp suất âm, từ hóa của phương tiện lưu trữ từ tính,…Tín hiệu số

được sử dụng trong tất cả các thiết bị điện tử kỹ thuật số, đáng chú ý là thiết bị

điện toán và truyền dữ liệu.

1.2. Ứng dụng

- Công nghệ xử lý tín hiệu số là công nghệ bùng nổ nhanh chóng trong

ngành công nghiệp điện tử và viễn thông hiện nay. Xử lý tín hiệu số có nhiều ứng

dụng da dạng, ví dụ như trong lĩnh vực điện tử y sinh, trong điều chỉnh động cơ

diesel, xử lý thoại, các cuộc gọi điện thoại khoảng cách xa, xử lý tiếng nói, xử lý 1

âm thanh, và tăng cường chất lượng hình ảnh và truyền hình. Các công nghệ trên

MPEG hay WMV hiện nay đều dựa trên tiến bộ của công nghệ xử lý tín hiệu số.

2. Các cổng logic cơ bản và thuật toán logic 2.1. Cổng NOT

- Định nghĩa: Cổng NOT là một cổng logic và thường được gọi là Bộ đệm đảo. - Ký hiệu - Bảng trạng thái - Biểu thức logic: Q=

- Nhận xét: Ngõ vào và ngõ ra có mức logic trái ngược nhau. 2.2. Cổng AND

- Định nghĩa: Cổng AND là một cổng logic dùng để thực hiện hàm AND

hai hay nhiều biến. Cổng AND có các ngõ tùy thuộc số biến và một ngõ ra. Ngõ

ra của cổng là hàm AND của các biến ngõ vào. - Ký hiệu - Bảng trạng thái 2

- Biểu thức logic: Q = A.B

- Nhận xét: Ngõ ra cổng AND chỉ ở mức cao khi tất cả các ngõ vào lên cao.

Khi có một ngõ vào bằng 0, ngõ ra bằng 0 bất chấp các ngõ vào còn lại. 2.3. Cổng OR

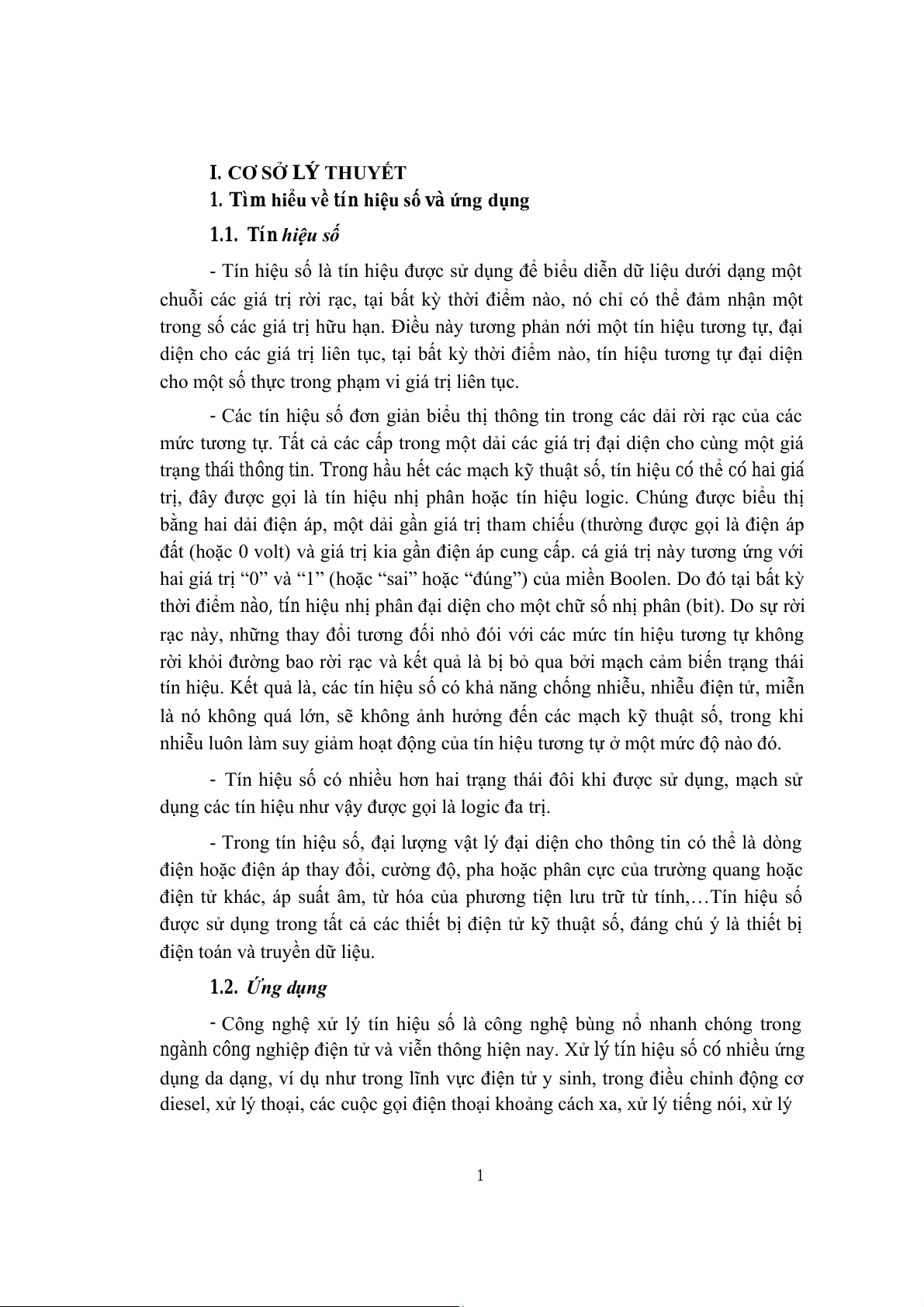

- Định nghĩa: Cổng OR là một cổng logic thực hiện thuật toán bằng các tín hiệu đầu vào. - Ký hiệu: - Bảng trạng thái:

- Biểu thức logic: Q = A + B

- Nhận xét: Ngõ ra cổng OR chỉ ở mức thấp khi tất cả các ngõ vào xuống

thấp. Khi có một ngõ vào bằng 1, ngõ ra bằng 1 bất chấp các ngõ vào còn lại. 2.4. Cổng NAND

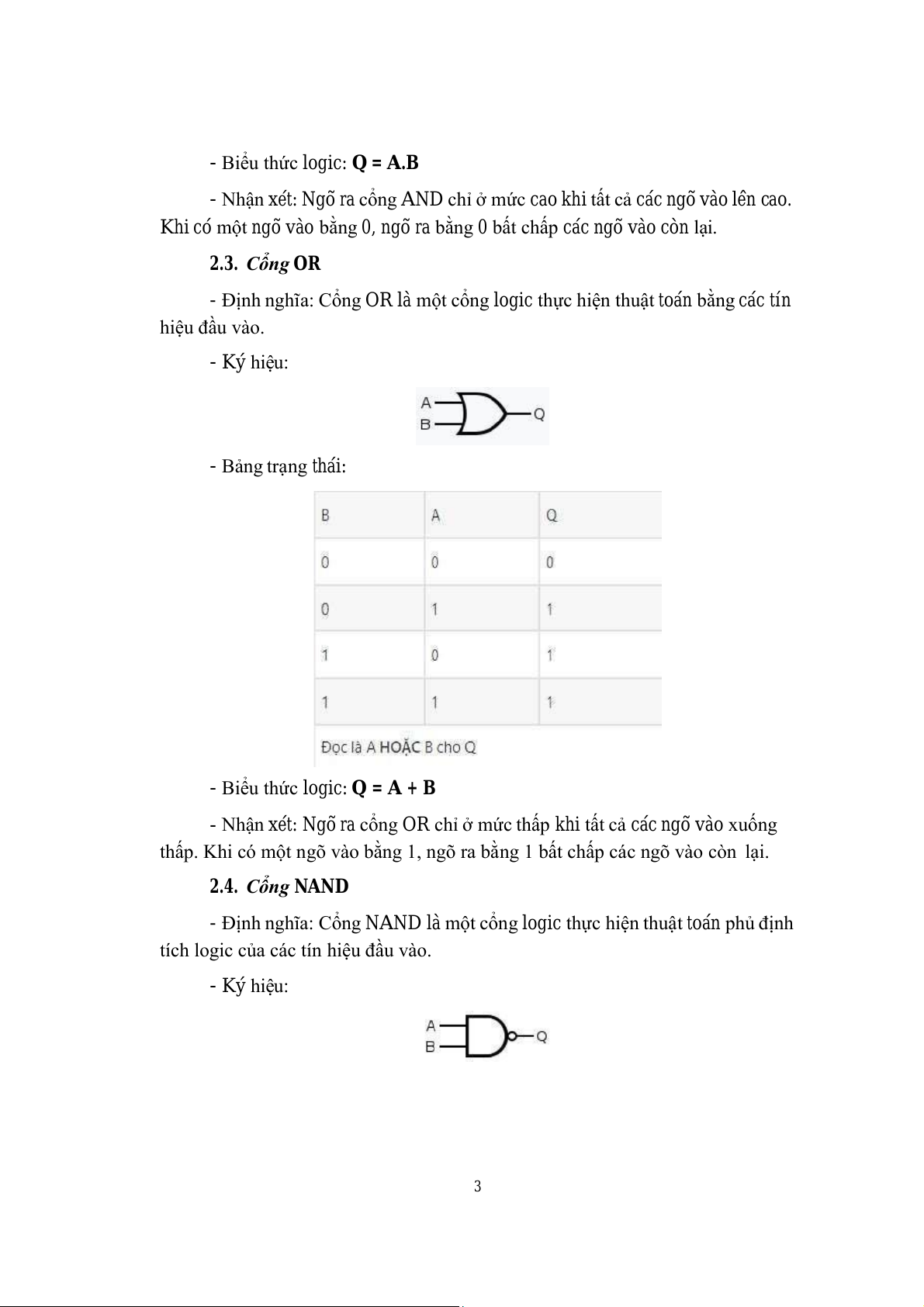

- Định nghĩa: Cổng NAND là một cổng logic thực hiện thuật toán phủ định

tích logic của các tín hiệu đầu vào. - Ký hiệu: 3 - Bảng trạng thái: - Biểu thức logic: - Nhận xét:

+ Ngõ ra cổng NAND = 1 khi có ít nhất 1 ngõ vào của nó bằng 0.

+ Ngõ ra cổng NAND = 0 khi tấ tcả các ngõ vào của nó bằng 1. 2.5 Cổng NOR

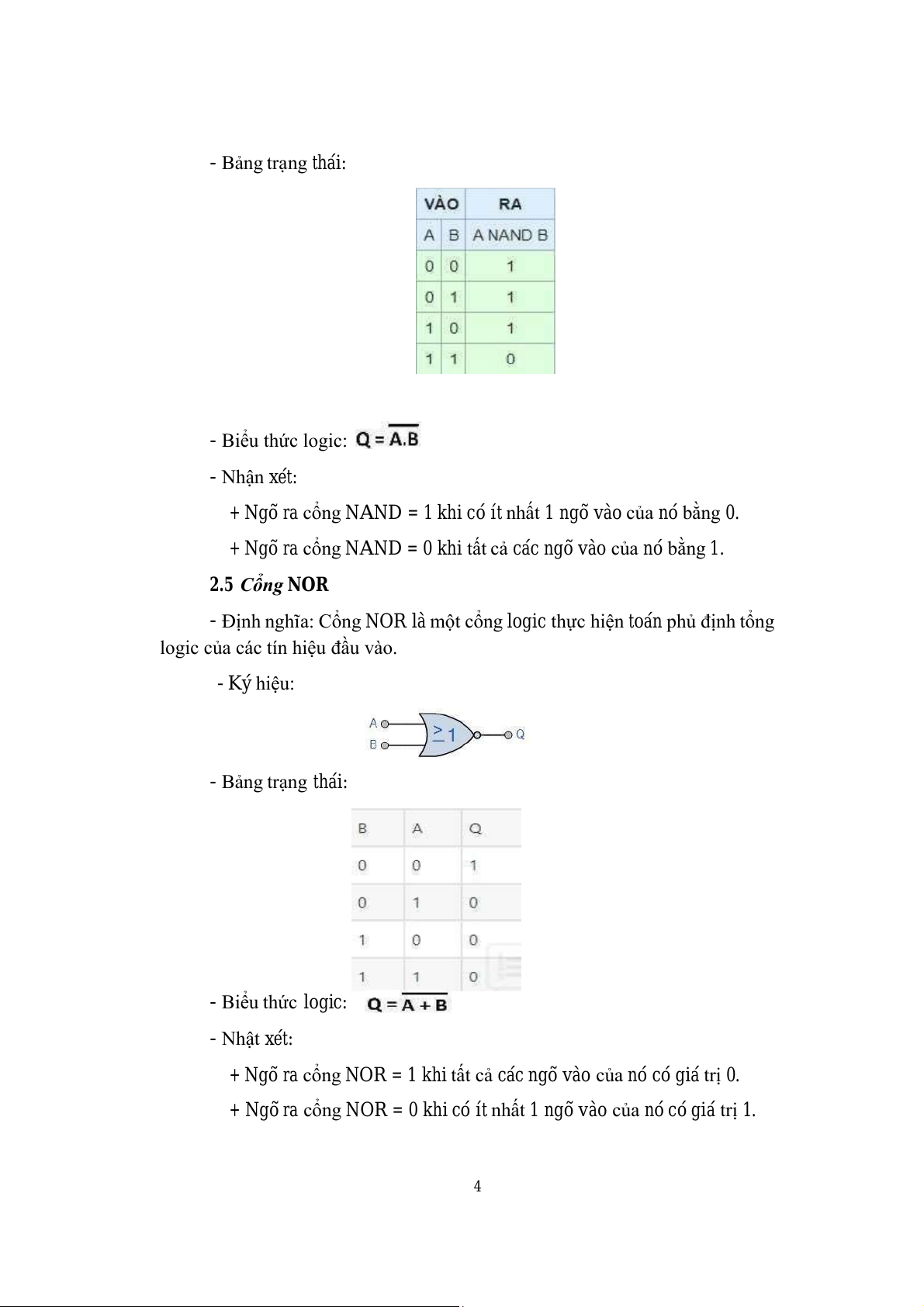

- Định nghĩa: Cổng NOR là một cổng logic thực hiện toán phủ định tổng

logic của các tín hiệu đầu vào. - Ký hiệu: - Bảng trạng thái: - Biểu thức logic: - Nhật xét:

+ Ngõ ra cổng NOR = 1 khi tất cả các ngõ vào của nó có giá trị 0.

+ Ngõ ra cổng NOR = 0 khi có ít nhất 1 ngõ vào của nó có giá trị 1. 4

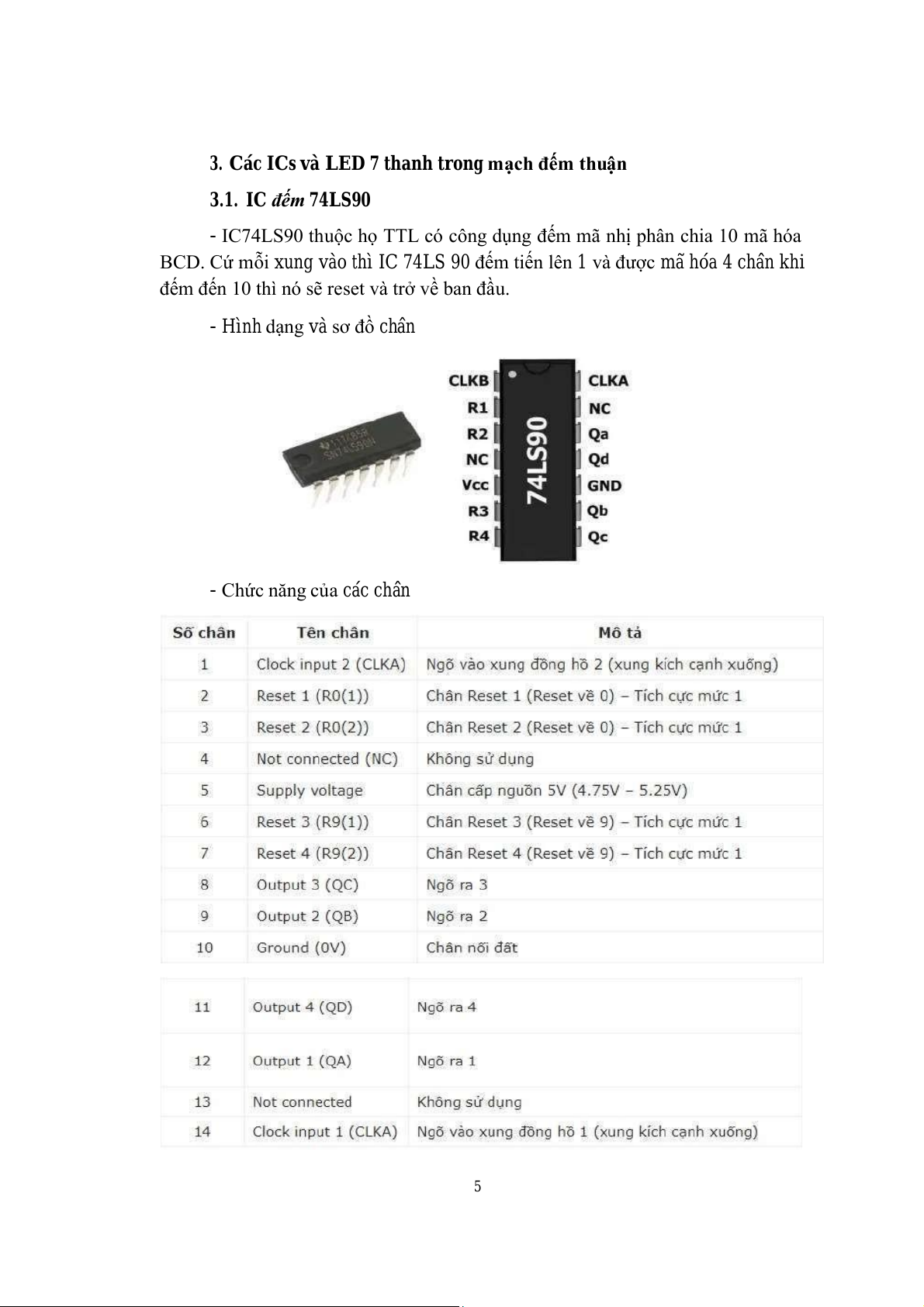

3. Các ICs và LED 7 thanh trong mạch đếm thuận 3.1. IC đếm 74LS90

- IC74LS90 thuộc họ TTL có công dụng đếm mã nhị phân chia 10 mã hóa

BCD. Cứ mỗi xung vào thì IC 74LS 90 đếm tiến lên 1 và được mã hóa 4 chân khi

đếm đến 10 thì nó sẽ reset và trở về ban đầu.

- Hình dạng và sơ đồ chân

- Chức năng của các chân 5

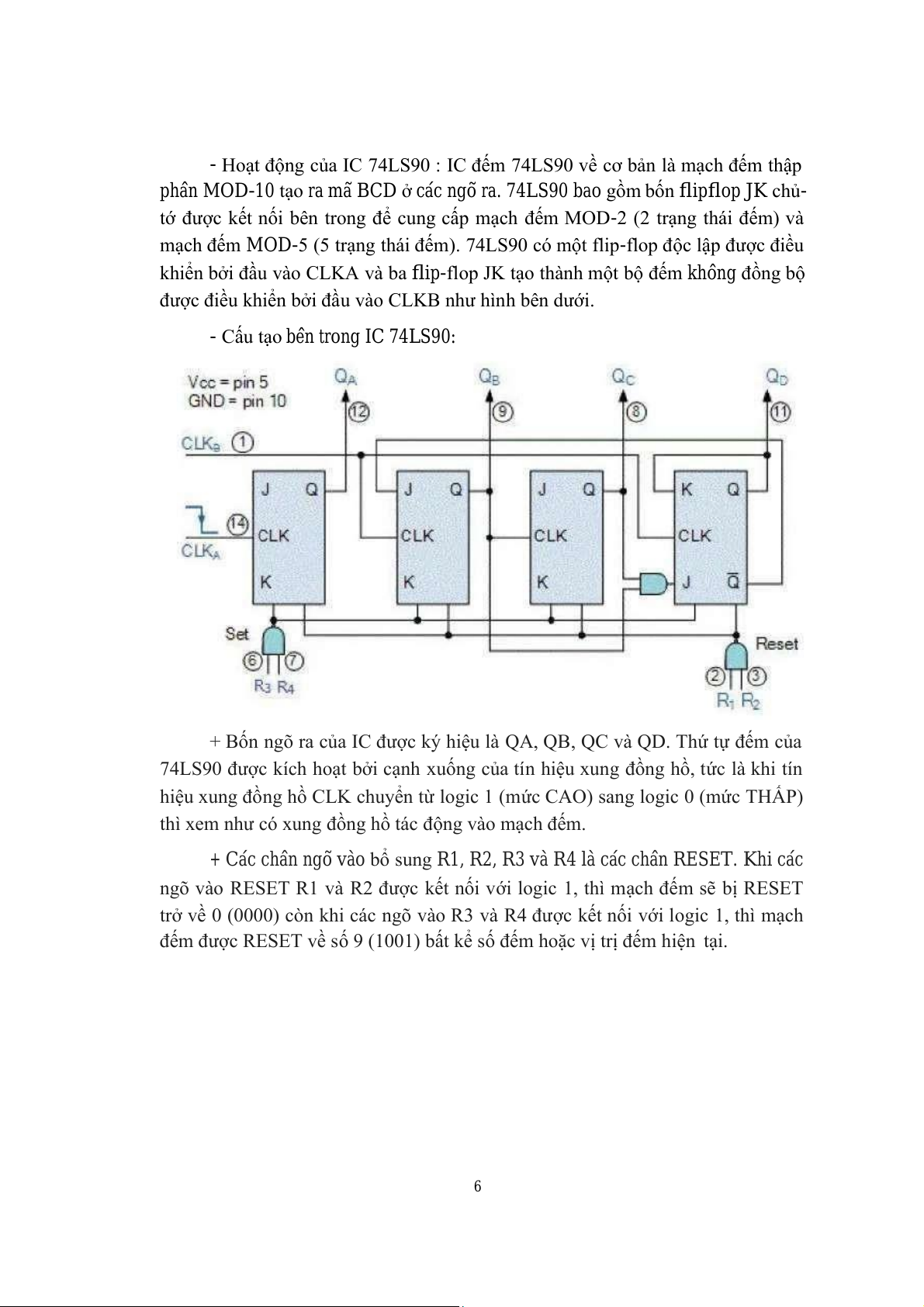

- Hoạt động của IC 74LS90 : IC đếm 74LS90 về cơ bản là mạch đếm thập

phân MOD-10 tạo ra mã BCD ở các ngõ ra. 74LS90 bao gồm bốn flipflop JK chủ-

tớ được kết nối bên trong để cung cấp mạch đếm MOD-2 (2 trạng thái đếm) và

mạch đếm MOD-5 (5 trạng thái đếm). 74LS90 có một flip-flop độc lập được điều

khiển bởi đầu vào CLKA và ba flip-flop JK tạo thành một bộ đếm không đồng bộ

được điều khiển bởi đầu vào CLKB như hình bên dưới.

- Cấu tạo bên trong IC 74LS90:

+ Bốn ngõ ra của IC được ký hiệu là QA, QB, QC và QD. Thứ tự đếm của

74LS90 được kích hoạt bởi cạnh xuống của tín hiệu xung đồng hồ, tức là khi tín

hiệu xung đồng hồ CLK chuyển từ logic 1 (mức CAO) sang logic 0 (mức THẤP)

thì xem như có xung đồng hồ tác động vào mạch đếm.

+ Các chân ngõ vào bổ sung R1, R2, R3 và R4 là các chân RESET. Khi các

ngõ vào RESET R1 và R2 được kết nối với logic 1, thì mạch đếm sẽ bị RESET

trở về 0 (0000) còn khi các ngõ vào R3 và R4 được kết nối với logic 1, thì mạch

đếm được RESET về số 9 (1001) bất kể số đếm hoặc vị trị đếm hiện tại. 6

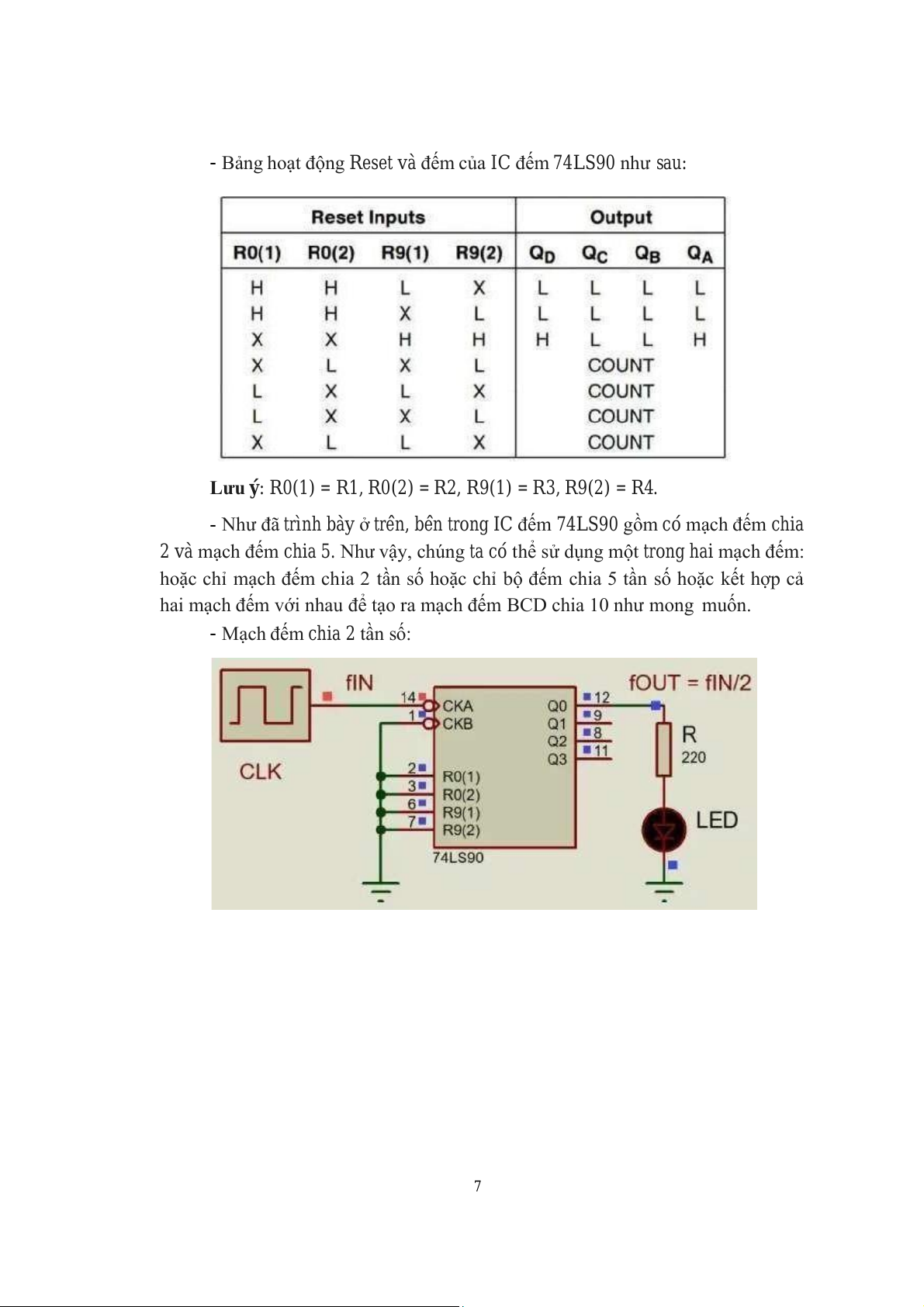

- Bảng hoạt động Reset và đếm của IC đếm 74LS90 như sau:

Lưu ý: R0(1) = R1, R0(2) = R2, R9(1) = R3, R9(2) = R4.

- Như đã trình bày ở trên, bên trong IC đếm 74LS90 gồm có mạch đếm chia

2 và mạch đếm chia 5. Như vậy, chúng ta có thể sử dụng một trong hai mạc h đếm:

hoặc chỉ mạch đếm chia 2 tần số hoặc chỉ bộ đếm chia 5 tần số hoặc kết hợp cả

hai mạch đếm với nhau để tạo ra mạch đếm BCD chia 10 như mong muốn.

- Mạch đếm chia 2 tần số: 7

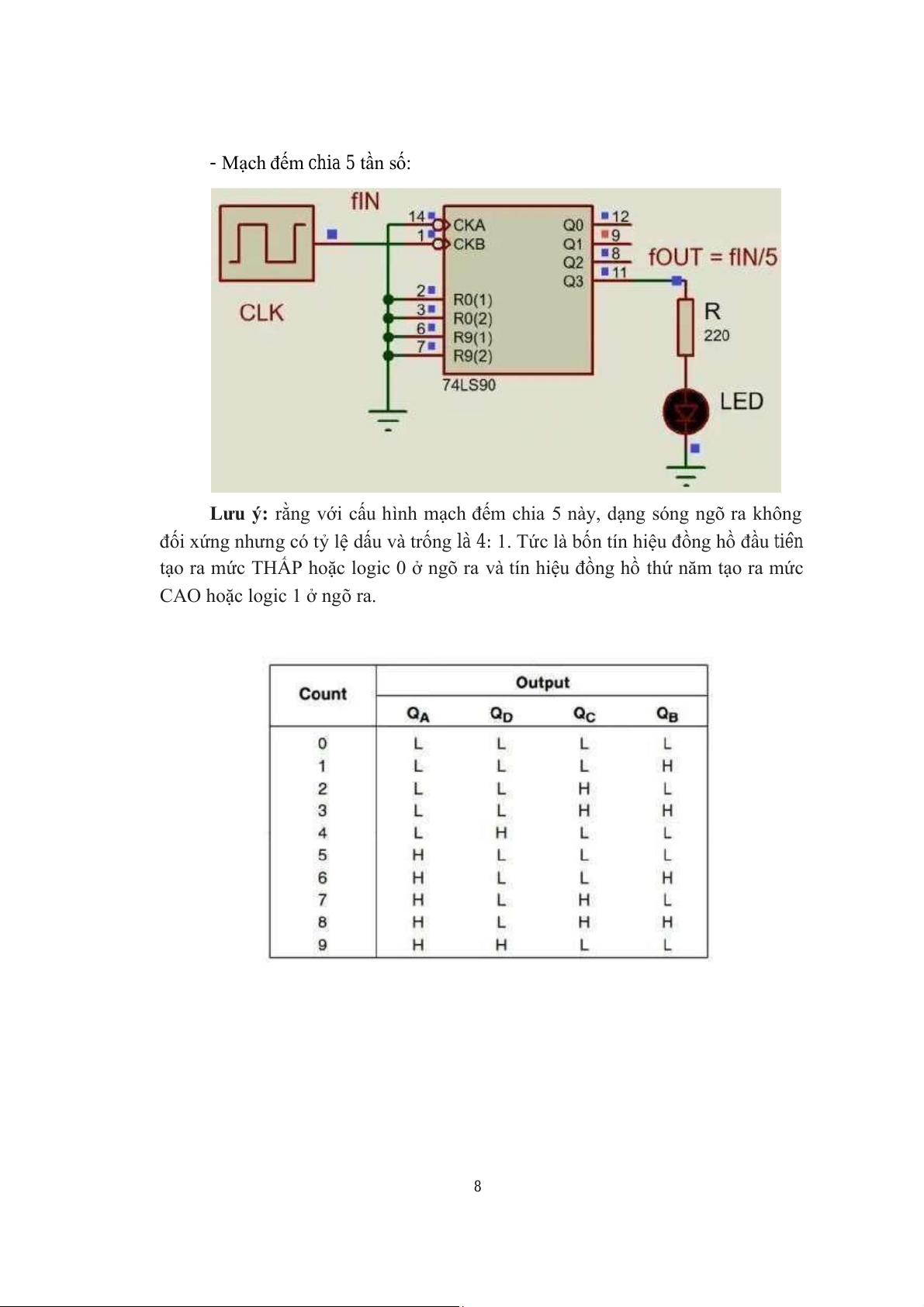

- Mạch đếm chia 5 tần số:

Lưu ý: rằng với cấu hình mạch đếm chia 5 này, dạng sóng ngõ ra không

đối xứng nhưng có tỷ lệ dấu và trống là 4: 1. Tức là bốn tín hiệu đồng hồ đầu tiên

tạo ra mức THẤP hoặc logic 0 ở ngõ ra và tín hiệu đồng hồ thứ năm tạo ra mức

CAO hoặc logic 1 ở ngõ ra. 8 - Mạch đếm chia 10:

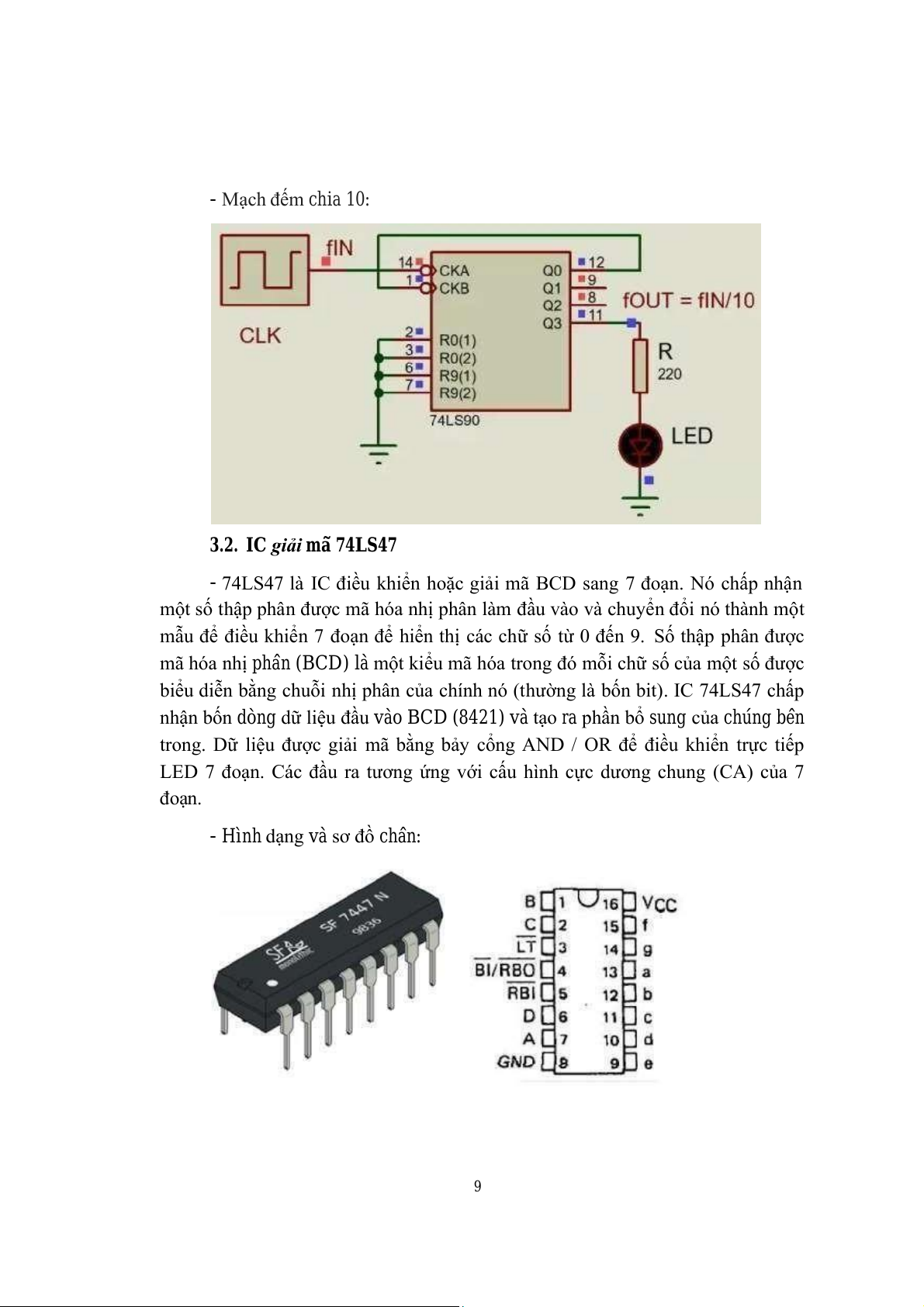

3.2. IC giải mã 74LS47

- 74LS47 là IC điều khiển hoặc giải mã BCD sang 7 đoạn. Nó chấp nhận

một số thập phân được mã hóa nhị phân làm đầu vào và chuyển đổi nó thành một

mẫu để điều khiển 7 đoạn để hiển thị các chữ số từ 0 đến 9. Số thập phân được

mã hóa nhị phân (BCD) là một kiểu mã hóa trong đó mỗi chữ số của một số được

biểu diễn bằng chuỗi nhị phân của chính nó (thường là bốn bit). IC 74LS47 chấp

nhận bốn dòng dữ liệu đầu vào BCD (8421) và tạo ra phần bổ sung của chúng bên

trong. Dữ liệu được giải mã bằng bảy cổng AND / OR để điều khiển trực tiếp

LED 7 đoạn. Các đầu ra tương ứng với cấu hình cực dương chung (CA) của 7 đoạn.

- Hình dạng và sơ đồ chân: 9 LT: Lamp Test BI: Blank Input

RBO: Ripple Blank Output RBI: Ripple Blank Input

- Nguyên lý hoạt động: 7447 thường được sử dụng ở 4 chế độ hoạt động:

+ Sáng bình thường đủ các trạng thái từ 0 ÷ 9 (thường dùng nhất). Chân

BI/RBO phải bỏ trống hoặc nối lên mức cao, chân RBI phải bỏ trống hoặc nối lên

mức cao, chân LT phải bỏ trống hoặc nối lên mức cao.

+ Chân BI/RBO nối xuống mức thấp thì tất các các đoạn của LED đều

không sáng bất chấp trạng thái của các ngõ vào còn lại.

+ Bỏ trạng thái số 0 (khi giá trị BCD tại ngõ vào bằng 0 thì tất cả các đoạn

của LED 7 đoạn đều tắt). Chân RBI ở mức thấp và chân BI/RBO phải bỏ trống

(và nó đóng vai trò là ngõ ra).

+ Chân BI/RBO phải bỏ trống hoặc nối lên mức cao và chân LT phải nối

xuống mức thấp. Tất cả các thanh của LED 7 đoạn đều sáng, bất chấp các ngõ vào

BCD. Dùng để Kiểm tra các đoạn của LED 7 đoạn (còn sáng hay đã chết). 3.3 IC 74LS00

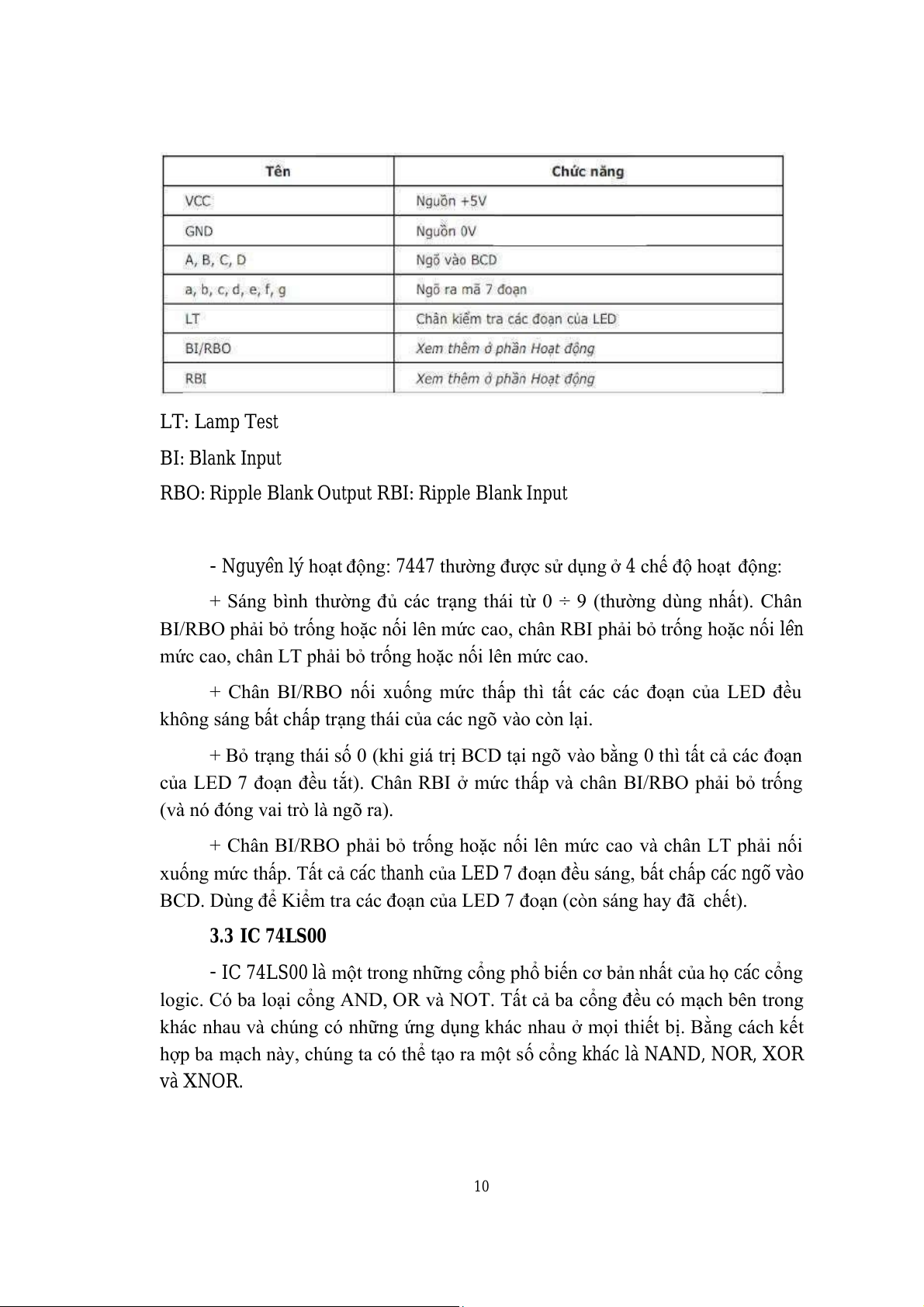

- IC 74LS00 là một trong những cổng phổ biến cơ bản nhất của họ các cổng

logic. Có ba loại cổng AND, OR và NOT. Tất cả ba cổng đều có mạch bên trong

khác nhau và chúng có những ứng dụng khác nhau ở mọi thiết bị. Bằng cách kết

hợp ba mạch này, chúng ta có thể tạo ra một số cổng khác là NAND, NOR, XOR và XNOR. 10

- Hình dạng và sơ đồ chân:

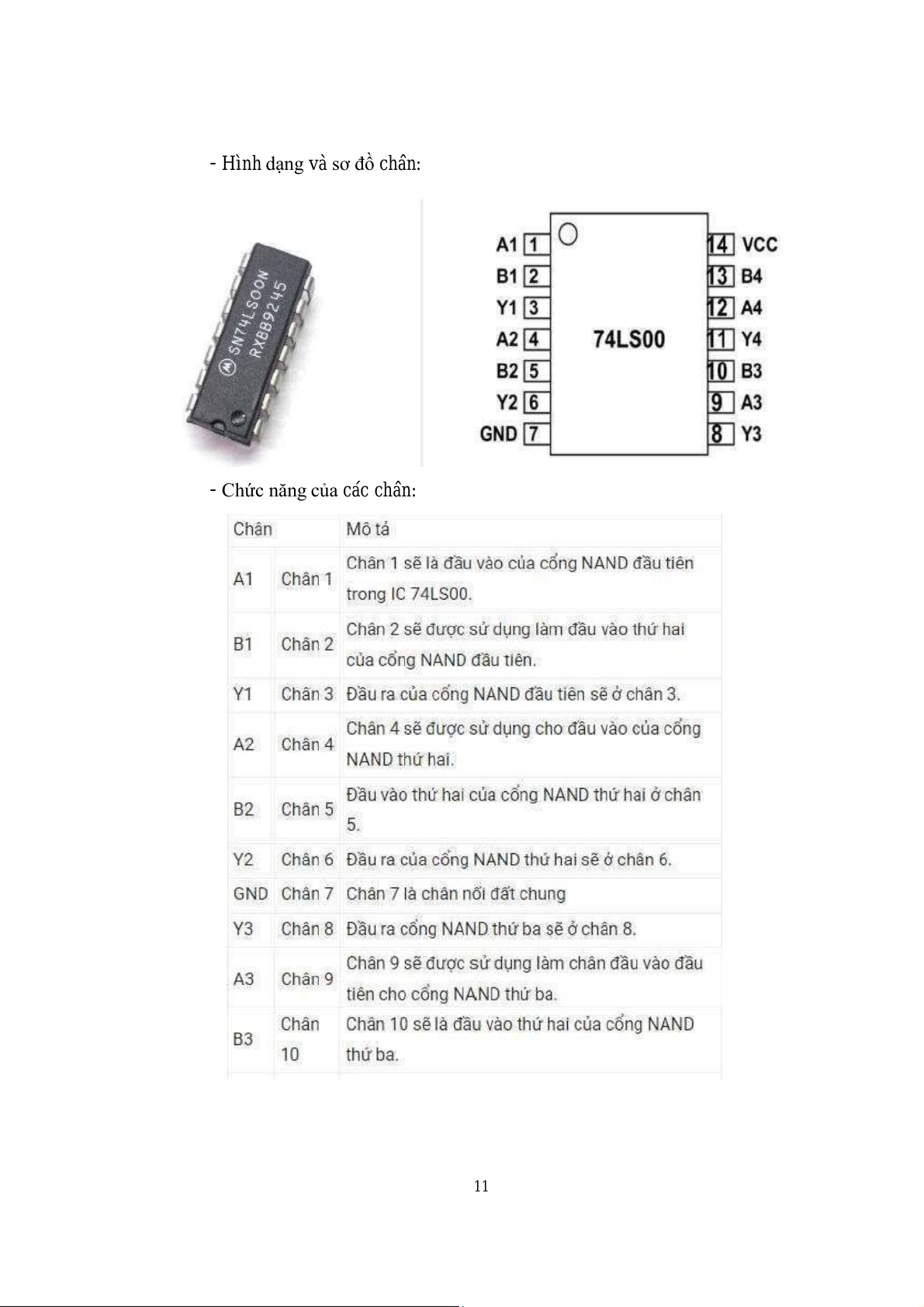

- Chức năng của các chân: 11 3.4. LED 7 thanh

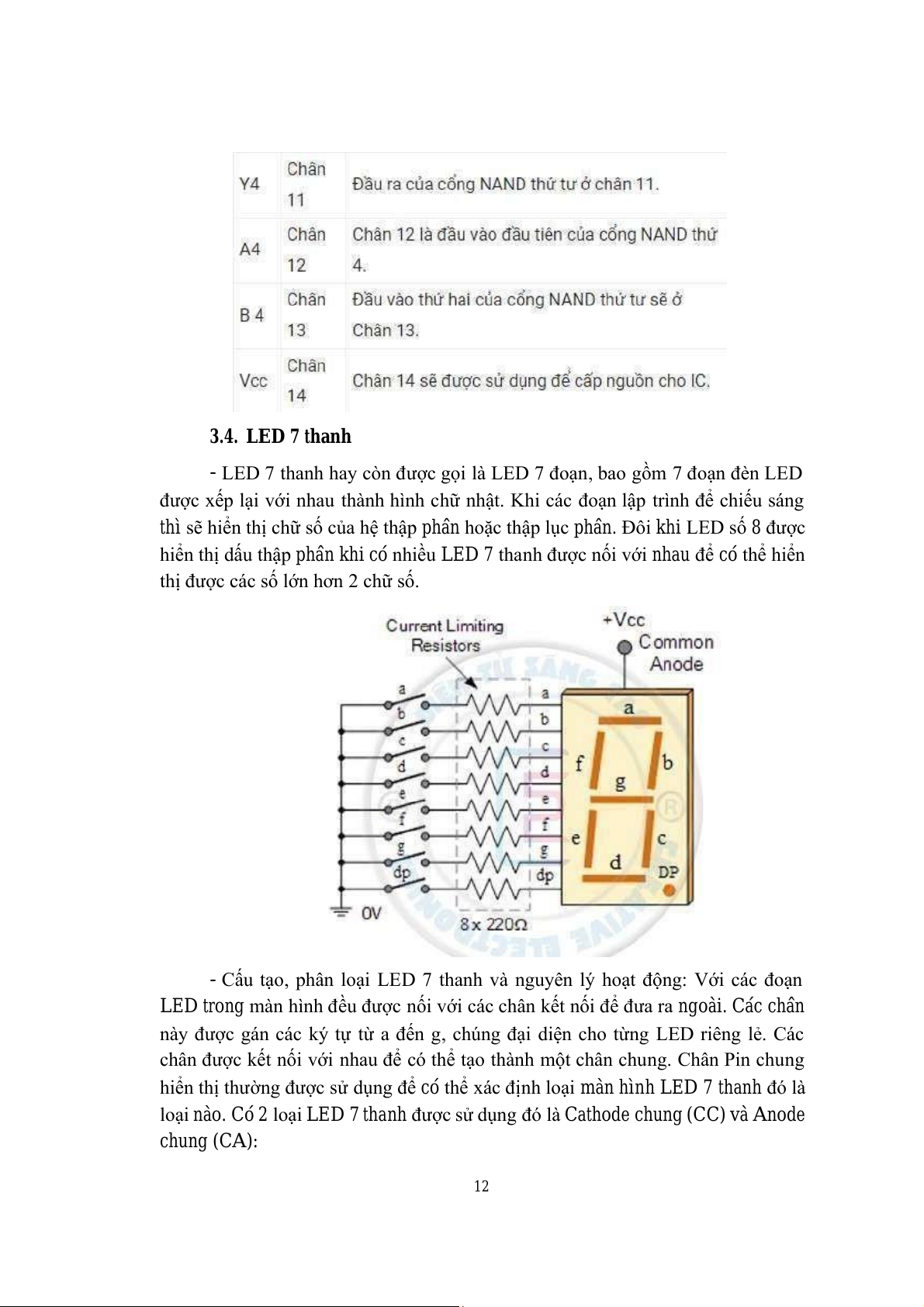

- LED 7 thanh hay còn được gọi là LED 7 đoạn, bao gồm 7 đoạn đèn LED

được xếp lại với nhau thành hình chữ nhật. Khi các đoạn lập trình để chiếu sáng

thì s ẽhiển thị chữ số của hệ thập phân hoặc thập lục phân. Đôi khi LED số 8 được

hiển thị dấu thập phân khi có nhiều LED 7 thanh được nối với nhau để có thể hiển

thị được các số lớn hơn 2 chữ số.

- Cấu tạo, phân loại LED 7 thanh và nguyên lý hoạt động: Với các đoạn

LED trong màn hình đều được nối với các chân kết nối để đưa ra ngoài. Các chân

này được gán các ký tự từ a đến g, chúng đại diện cho từng LED riêng lẻ. Các

chân được kết nối với nhau để có thể tạo thành một chân chung. Chân Pin chung

hiển thị thường được sử dụng để có thể xác định loại màn hình LED 7 thanh đó là

loại nào. Có 2 loại LED 7 thanh được sử dụng đó là Cathode chung (CC) và Anode chung (CA): 12

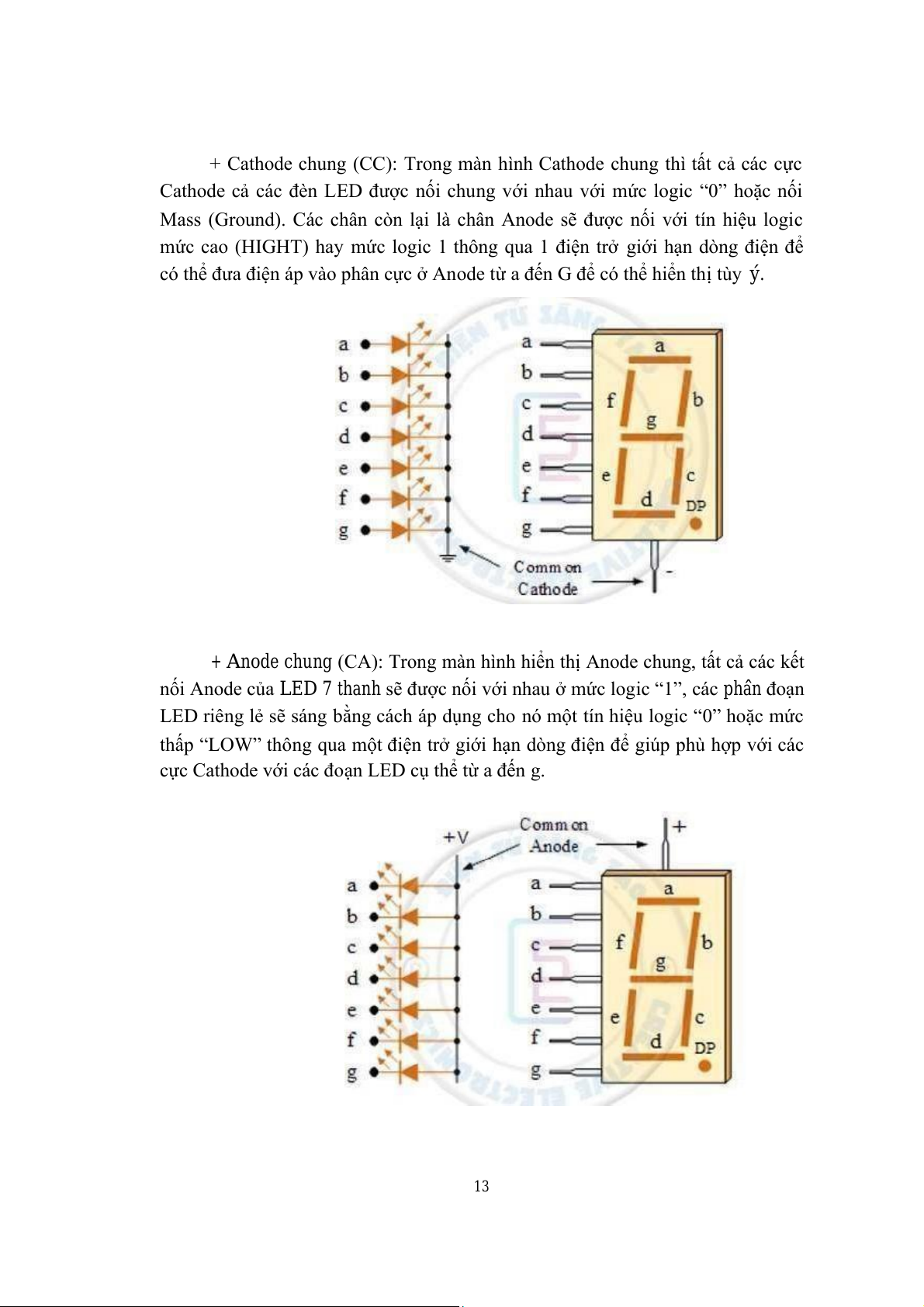

+ Cathode chung (CC): Trong màn hình Cathode chung thì tất cả các cực

Cathode cả các đèn LED được nối chung với nhau với mức logic “0” hoặc nối

Mass (Ground). Các chân còn lại là chân Anode sẽ được nối với tín hiệu logic

mức cao (HIGHT) hay mức logic 1 thông qua 1 điện trở giới hạn dòng điện để

có thể đưa điện áp vào phân cực ở Anode từ a đến G để có thể hiển thị tùy ý.

+ Anode chung (CA): Trong màn hình hiển thị Anode chung, tất cả các kết

nối Anode của LED 7 thanh sẽ được nối với nhau ở mức logic “1”, các phân đoạn

LED riêng lẻ sẽ sáng bằng cách áp dụng cho nó một tín hiệu logic “0” hoặc mức

thấp “LOW” thông qua một điện trở giới hạn dòng điện để giúp phù hợp với các

cực Cathode với các đoạn LED cụ thể từ a đến g. 13

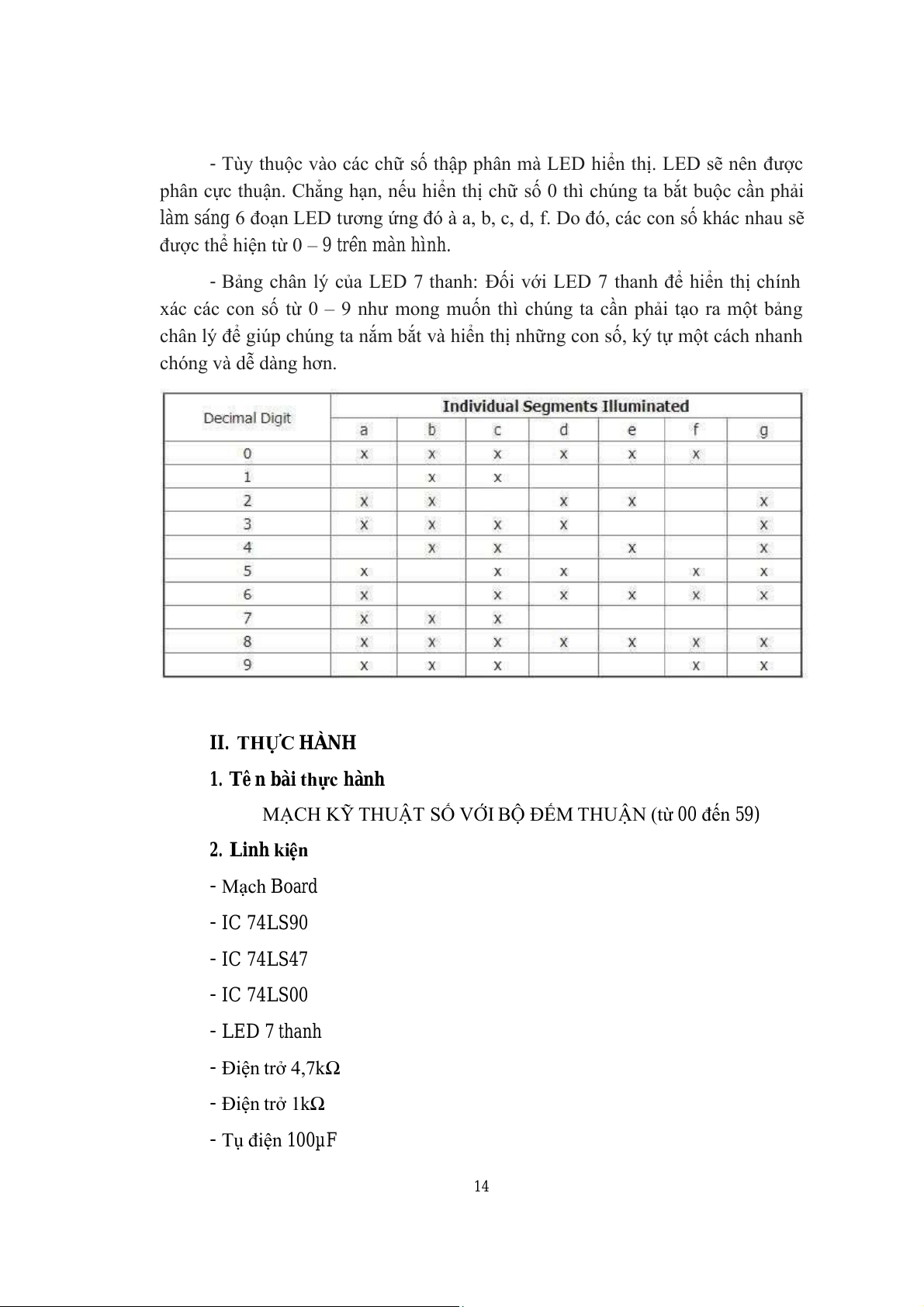

- Tùy thuộc vào các chữ số thập phân mà LED hiển thị. LED sẽ nên được

phân cực thuận. Chẳng hạn, nếu hiển thị chữ số 0 thì chúng ta bắt buộc cần phải

làm sáng 6 đoạn LED tương ứng đó à a, b, c, d, f. Do đó, các con số khác nhau sẽ

được thể hiện từ 0 – 9 trên màn hình.

- Bảng chân lý của LED 7 thanh: Đối với LED 7 thanh để hiển thị chính

xác các con số từ 0 – 9 như mong muốn thì chúng ta cần phải tạo ra một bảng

chân lý để giúp chúng ta nắm bắt và hiển thị những con số, ký tự một cách nhanh chóng và dễ dàng hơn. II. THỰC HÀNH

1. Tên bài thực hành

MẠCH KỸ THUẬT SỐ VỚI BỘ ĐẾM THUẬN (từ 00 đến 59) 2. Linh kiện - Mạch Board - IC 74LS90 - IC 74LS47 - IC 74LS00 - LED 7 thanh - Điện trở 4,7kΩ - Điện trở 1kΩ - Tụ điện 100µF 14 - Dây dẫ n - Nguồn điện 3V

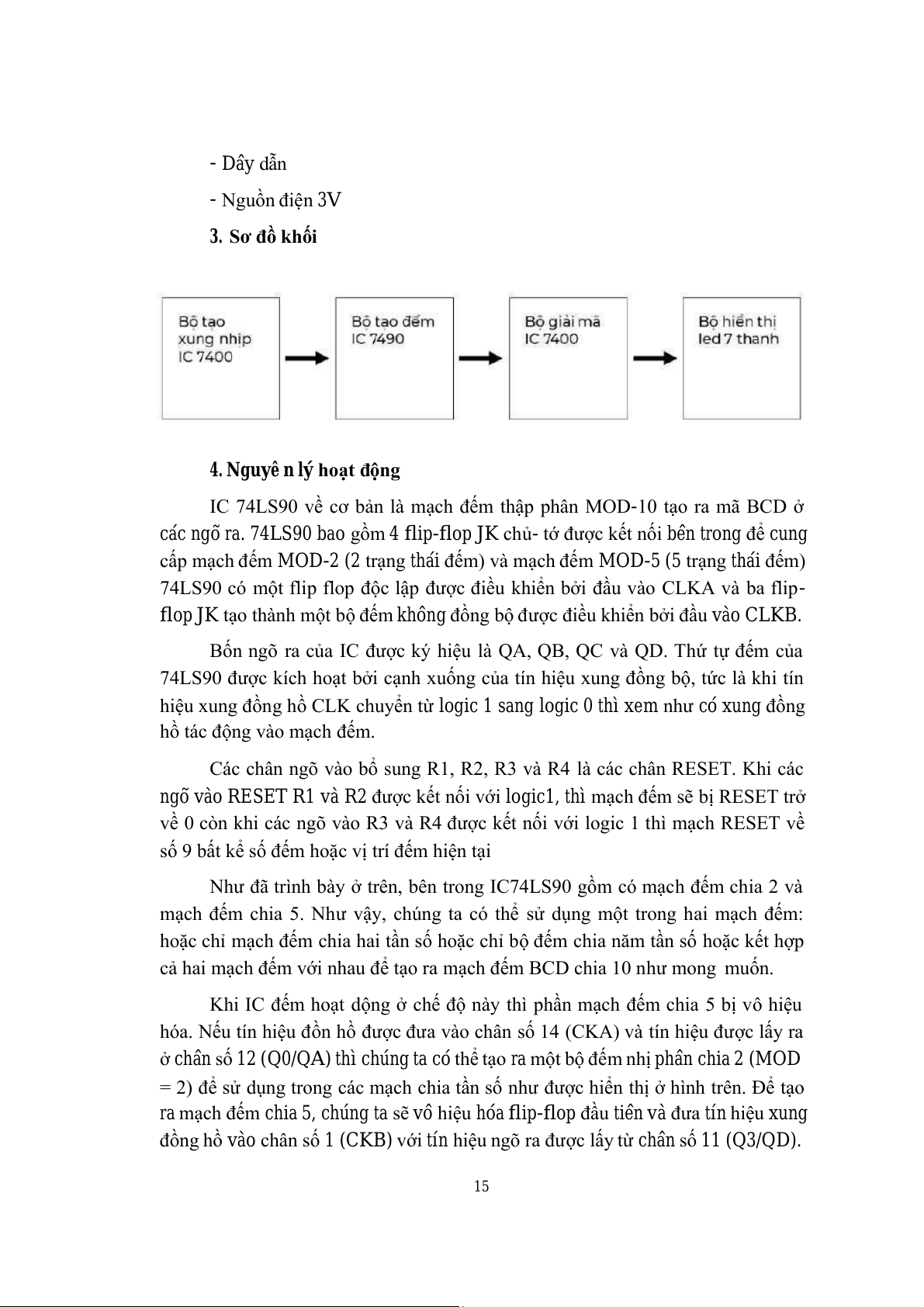

3. Sơ đồ khối

4. Nguyên lý hoạt động

IC 74LS90 về cơ bản là mạch đếm thập phân MOD-10 tạo ra mã BCD ở

các ngõ ra. 74LS90 bao gồm 4 flip-flop JK chủ- t

ớ được kết nối bên trong để cung

cấp mạch đếm MOD-2 (2 trạng thái đếm) và mạch đếm MOD-5 (5 trạng thái đếm)

74LS90 có một flip flop độc lập được điều khiển bởi đầu vào CLKA và ba flip-

flop JK tạo thành một bộ đếm không đồng bộ được điều khiển bởi đầu vào CLKB.

Bốn ngõ ra của IC được ký hiệu là QA, QB, QC và QD. Thứ tự đếm của

74LS90 được kích hoạt bởi cạnh xuống của tín hiệu xung đồng bộ, tức là khi tín

hiệu xung đồng hồ CLK chuyển từ logic 1 sang logic 0 thì xem như có xung đồng

hồ tác động vào mạch đếm.

Các chân ngõ vào bổ sung R1, R2, R3 và R4 là các chân RESET. Khi các

ngõ vào RESET R1 và R2 được kết nối với logic1, thì mạch đếm sẽ bị RESET trở

về 0 còn khi các ngõ vào R3 và R4 được kết nối với logic 1 thì mạch RESET về

số 9 bất kể số đếm hoặc vị trí đếm hiện tại

Như đã trình bày ở trên, bên trong IC74LS90 gồm có mạch đếm chia 2 và

mạch đếm chia 5. Như vậy, chúng ta có thể sử dụng một trong hai mạch đếm:

hoặc chỉ mạch đếm chia hai tần số hoặc chỉ bộ đếm chia năm tần số hoặc kết hợp

cả hai mạch đếm với nhau để tạo ra mạch đếm BCD chia 10 như mong muốn.

Khi IC đếm hoạt dộng ở chế độ này thì phần mạch đếm chia 5 bị vô hiệu

hóa. Nếu tín hiệu đồn hồ được đưa vào chân số 14 (CKA) và tín hiệu được lấy ra

ở chân số 12 (Q0/QA) thì chúng ta có thể tạo ra một bộ đếm nhị phân chia 2 (MOD

= 2) để sử dụng trong các mạch chia tần số như được hiển thị ở hình trên. Để tạo

ra mạch đếm chia 5, chúng ta s ẽvô hiệu hóa flip-flop đầu tiên và đưa tín hiệu xung

đồng hồ vào chân số 1 (CKB) với tín hiệu ngõ ra được lấy từ chân số 11 (Q3/QD). 15

Để hiển thị các số đếm trên led 7 đoạn chúng ta cần một IC giải mã BCD

sang led 7 đoạn. IC 74LS47 hoặc 74LS247 được thiết kế để làm được việc đó.

74LS47 có bốn ngõ vào cho các chữ số BCD A, B, C và D và có 7 ngõ ra để điều

khiển các đoạn của led 7 đoạn. IC giải mã hiển thị 74LS47 nhận mã BCD từ các

ngõ ra của IC đếm 74LS90 và tạo các tín hiệu cần thiết để ra điều khiển các đoạn

của led 7 đoạn để hiện thị được các số đếm. Vì IC giải mã 74LS47 được thiết kế

để điều khiển led 7 đoạn loại anode chung nên khi ngõ ra ở mức THẤP (logic 0)

sẽ làm cho LED kết nối với ngõ ra này phát sáng trong khi ngõ ra ở mức CAO

(logic 1) sẽ làm cho LED này TẮT, Đối với hoạt động bình thường, tất cả các

chân LT (Lamp Test), BI/RBO (Blanking Input/Ripple Blanking Output) và RBI

(Ripple Blanking Input) đều phải được bỏ trông hoặc kết nối với logic 1 (mức CAO)

Các ngõ vào của IC 74LS47 được kết nối với các ngõ ra tương ứmg của IC

đếm BCD 7Lưu ý rằng mặ

c dù 74LS47 có các ngõ ra tích cực mức THÁP và được

thiết kể để giải mã hiển thị trên LED 7 đoạn loại ANODE chung. IC giải mã điều

khiển 74LS48/4511 có chức năng hoàn toàn giống như IC 74LS47 ngoại trừ nó

có ngõ ra tích cực mức CAO, được thiết kế để giải mã hiển thị cho 7 đoạn loại

CATHODE chung. Vì vậy, tùy thuộc vào loại led 7 đoạn mà bạn sử dụng, bạn có

thể cần IC giải mã 74LS47 hoặc 74LS48

4LS90 để hiển thị các số đếm trên led 7 đoạn như hình trên. Số đếm hiện

thị trên led 7 đoạn tăng dần từ 0 đến 9 mỗi khi có xung đồng hồ tác động vào IC đếm.

Mạch của chúng ta là một mạch đếm số đơn giản hiển thị các số đếm từ 0

đến 9 sử dụng IC đếm 74LS90 và IC giải mã BCD sang led 7 đoạn 74LS47. Để

đếm hơn 10 thì chúng ta sẽ cần ghép hai IC đếm BCD lại với cho nhau.

Bộ đếm BCD gồm 2 chữ số sẽ được tính theo số thập phân tư 00 đến 59

(0000 0000 đến 101 1001) và sau đó sẽ tự động RESET về 00, Lưu ý rằng mặcdù

đó sẽ là bộ đếm 2 chữ số, các giá trị đại diện cho các số thập lục phân từ A đến F

không hợp lệ trong mã này.

5. Sơ đồ thiết kế 16 * Sơ đồ nguyên lý: 17