Preview text:

14:40, 10/01/2026

Chương 2: Kiến Trúc Phần Cứng AVR ATmega324P - Tài Liệu Học Tập - Studocu

.1 Giới thiệu vi điều khiển (VĐK) họ AVR

.2 Kiến trúc phần cứng VĐK ATmega324P

.3 Tổ chức bộ nhớ và thanh ghi VĐK ATmega324P .4 Các thanh ghi khác .5 Mạch dao động

.6 Các bit cầu chì (Fuse bits) .7 Hoạt động reset

Nguyễn Lý Thiên Trường 2 14:40, 10/01/2026

Chương 2: Kiến Trúc Phần Cứng AVR ATmega324P - Tài Liệu Học Tập - Studocu

2.1 Giới thiệu vi điều khiển họ AVR

AVR: Advanced Virtual RISC hoặc Alf and Vegard RISC (tên c

2 nhà thiết kế Alf-Egil Bogen và Vegard Wollan).

AVR là vi điều khiển 8 bit (ngoại trừ AVR32 là vi điều khiển 32

bit) dạng RISC (Reduced Instruction Set Computer) theo kiế

trúc Harvard được Atmel (nay là Microchip) phát triển năm 1996.

➢Lưu ý: Vi điều khiển (VĐK)

8 bit là VĐK có kích thước data b

là 8 bit, thanh ghi 8 bit, bộ ALU xử lý các phép toán số học v

logic trên toán hạng 8 bit (ALU 8 bit),… Nguyễn Lý Thiên Trường 14:40, 10/01/2026

Chương 2: Kiến Trúc Phần Cứng AVR ATmega324P - Tài Liệu Học Tập - Studocu

2.1 Giới thiệu vi điều khiển họ AVR

▪CISC: Complex Instruction Set Computer

▪RISC: Reduced Instructions Set Computer Nguyễn Lý Thiên Trường 14:40, 10/01/2026

Chương 2: Kiến Trúc Phần Cứng AVR ATmega324P - Tài Liệu Học Tập - Studocu

2.1 Giới thiệu vi điều khiển họ AVR Nguyễn Lý Thiên Trường 14:40, 10/01/2026

Chương 2: Kiến Trúc Phần Cứng AVR ATmega324P - Tài Liệu Học Tập - Studocu

2.1 Giới thiệu vi điều khiển họ AVR ọ AVR chia làm 4 nhóm:

Classic (AT90Sxxxx): là nhóm vi điều khiển gốc, hiện không còn được sử dụng.

Mega (ATmegaxxxx): là nhóm vi điều khiển có hơn 120 lệnh

và nhiều ngoại vi khác nhau.

Tiny (ATtinyxxxx): có ít lệnh và kích thước nhỏ so với ATmega.

AVR cho mục đích đặc biệt:các IC này cũng thuộc các nhóm

trên nhưng được trang bị thêm để thiết kế ứng dụng cụ thể.

Ví dụ như bộ điều khiển USB, bộ điều khiển LCD, bộ điều khiển mạng cục bộ, … Nguyễn Lý Thiên Trường 14:40, 10/01/2026

Chương 2: Kiến Trúc Phần Cứng AVR ATmega324P - Tài Liệu Học Tập - Studocu

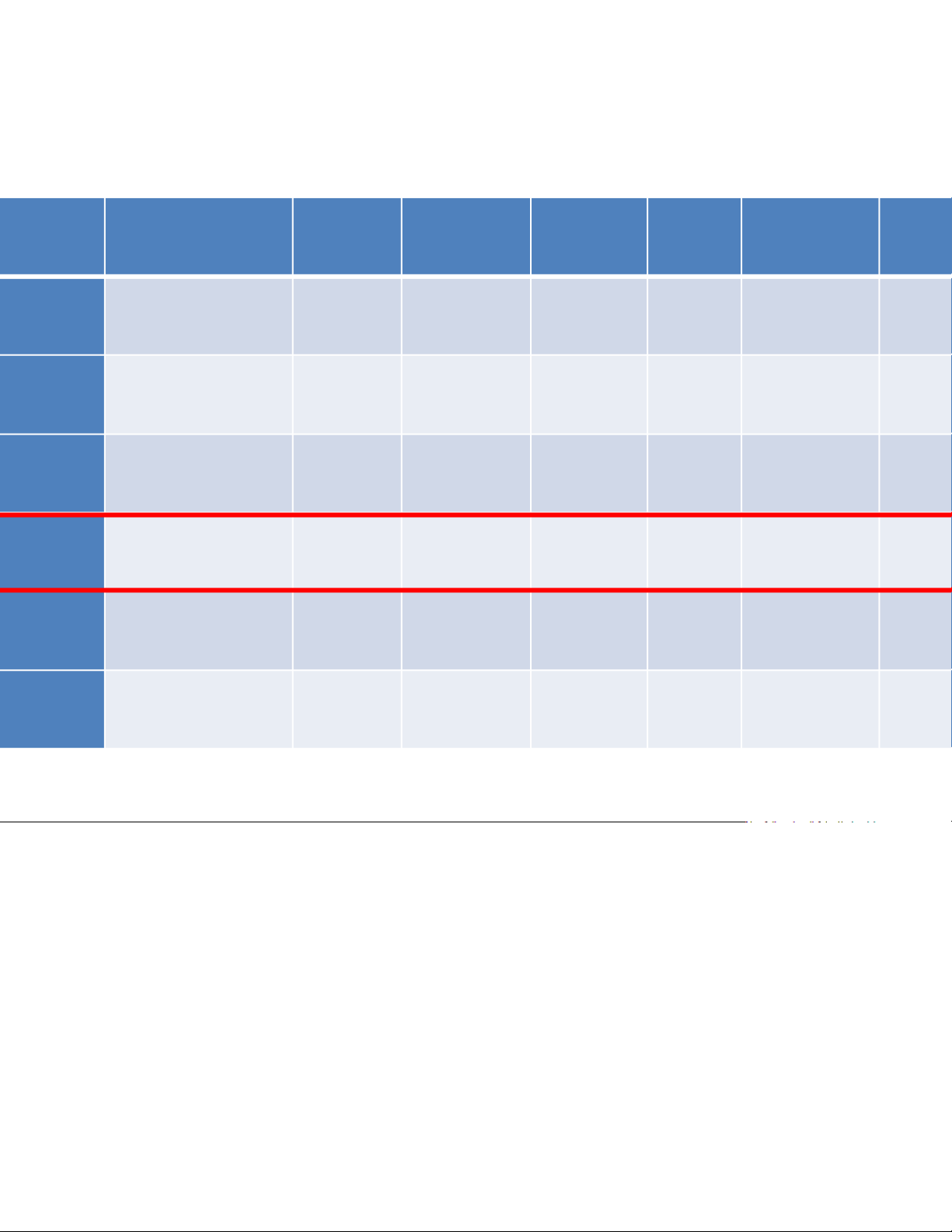

2.1 Giới thiệu vi điều khiển họ AVR IC ROM RAM EEPROM SốIc/hâ O n ADC Bộ Số c

chương trình dữ liệu dữ liệu định thời Loạ TQF ega8 8KB 1KB 0.5KB 23 8 3 PDI TQF ega16 16KB 1KB 0.5KB 32 8 3 PDI TQF ega32 32KB 2KB 1KB 32 8 3 PDI TQF ega324P 32KB 2KB 1KB 40/44 8 3 PDI TQF ega64 64KB 4KB 2KB 54 8 4 ML TQF ega1280 128KB 8KB 4KB 86 16 6 CB Nguyễn Lý Thiên Trường 14:40, 10/01/2026

Chương 2: Kiến Trúc Phần Cứng AVR ATmega324P - Tài Liệu Học Tập - Studocu

2.1 Giới thiệu vi điều khiển họ AVR Nguyễn Lý Thiên Trường 14:40, 10/01/2026

Chương 2: Kiến Trúc Phần Cứng AVR ATmega324P - Tài Liệu Học Tập - Studocu

2.1 Giới thiệu vi điều khiển họ AVR Nguyễn Lý Thiên Trường 14:40, 10/01/2026

Chương 2: Kiến Trúc Phần Cứng AVR ATmega324P - Tài Liệu Học Tập - Studocu

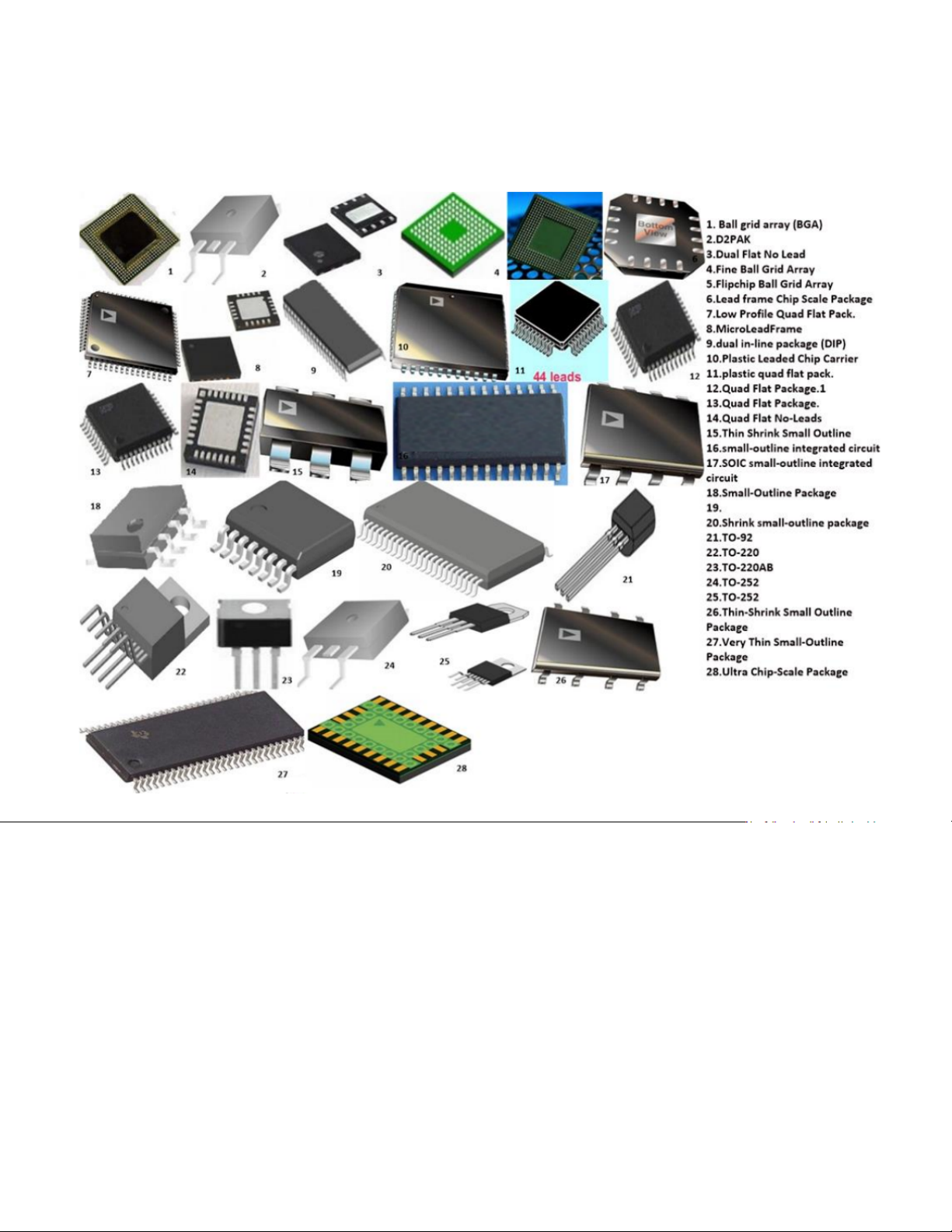

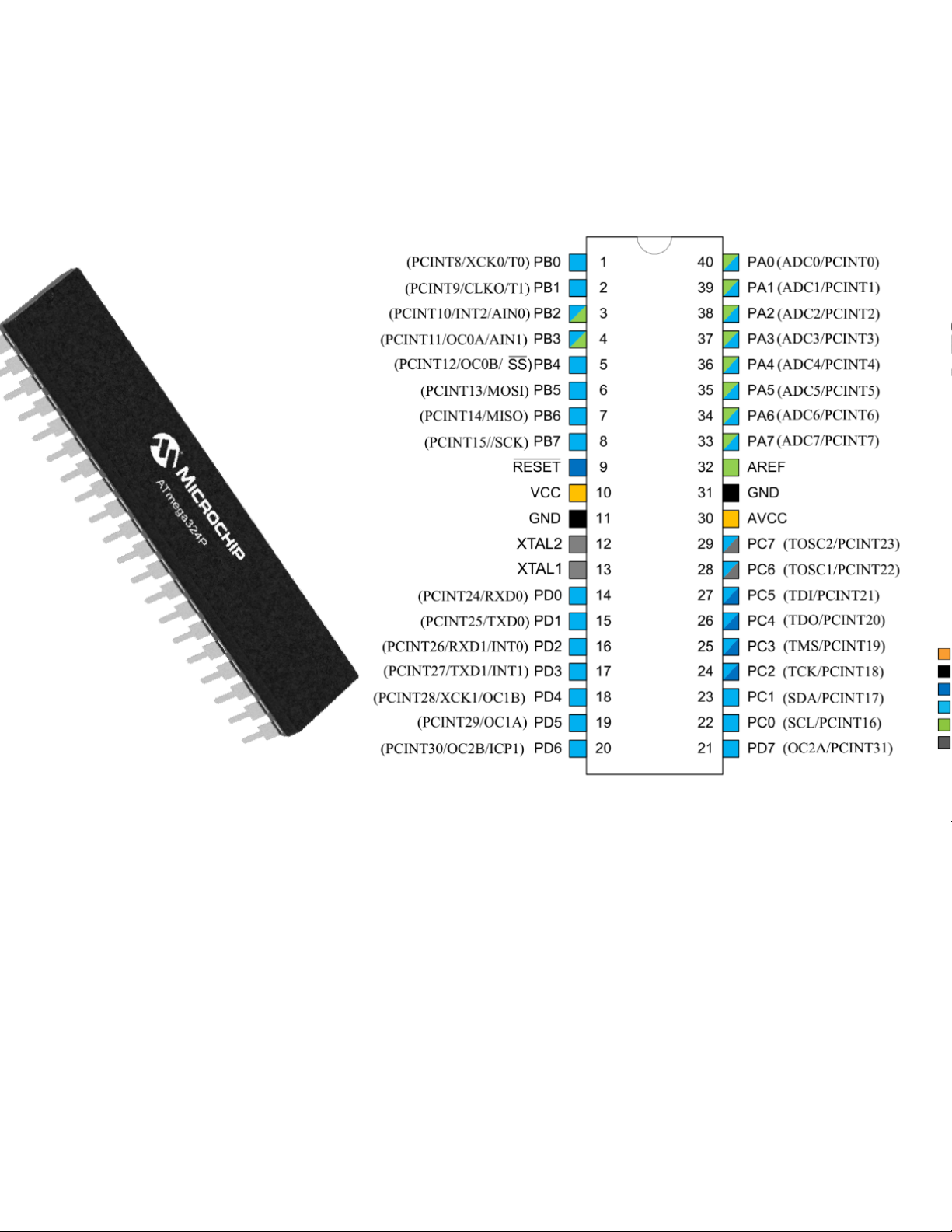

2.2 Kiến trúc phần cứng VĐK ATmega324P

stic Dual In-Line Package (PDIP) Nguyễn Lý Thiên Trường 14:40, 10/01/2026

Chương 2: Kiến Trúc Phần Cứng AVR ATmega324P - Tài Liệu Học Tập - Studocu

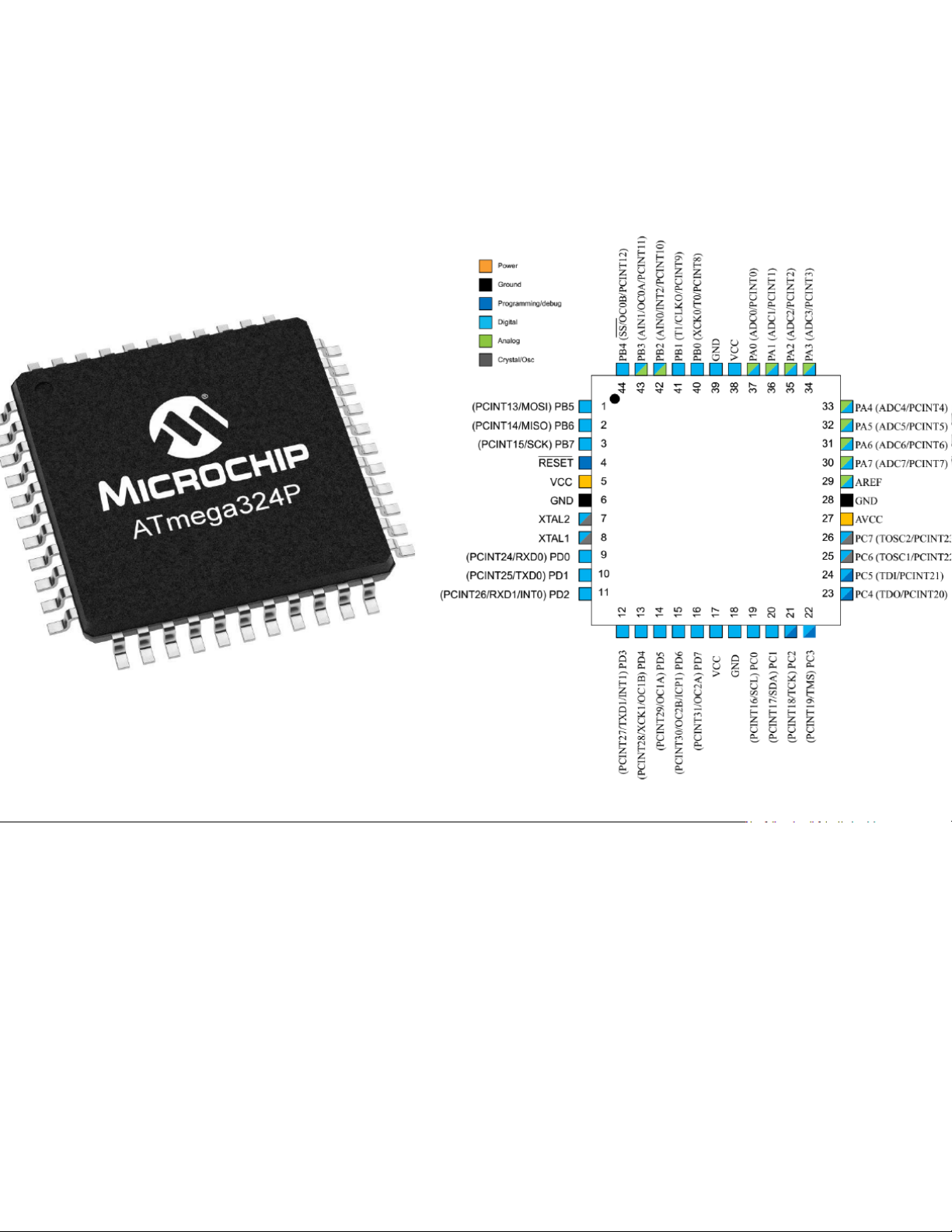

2.2 Kiến trúc phần cứng VĐK ATmega324P in Quad Flat Package (TQFP) Nguyễn Lý Thiên Trường 14:40, 10/01/2026

Chương 2: Kiến Trúc Phần Cứng AVR ATmega324P - Tài Liệu Học Tập - Studocu

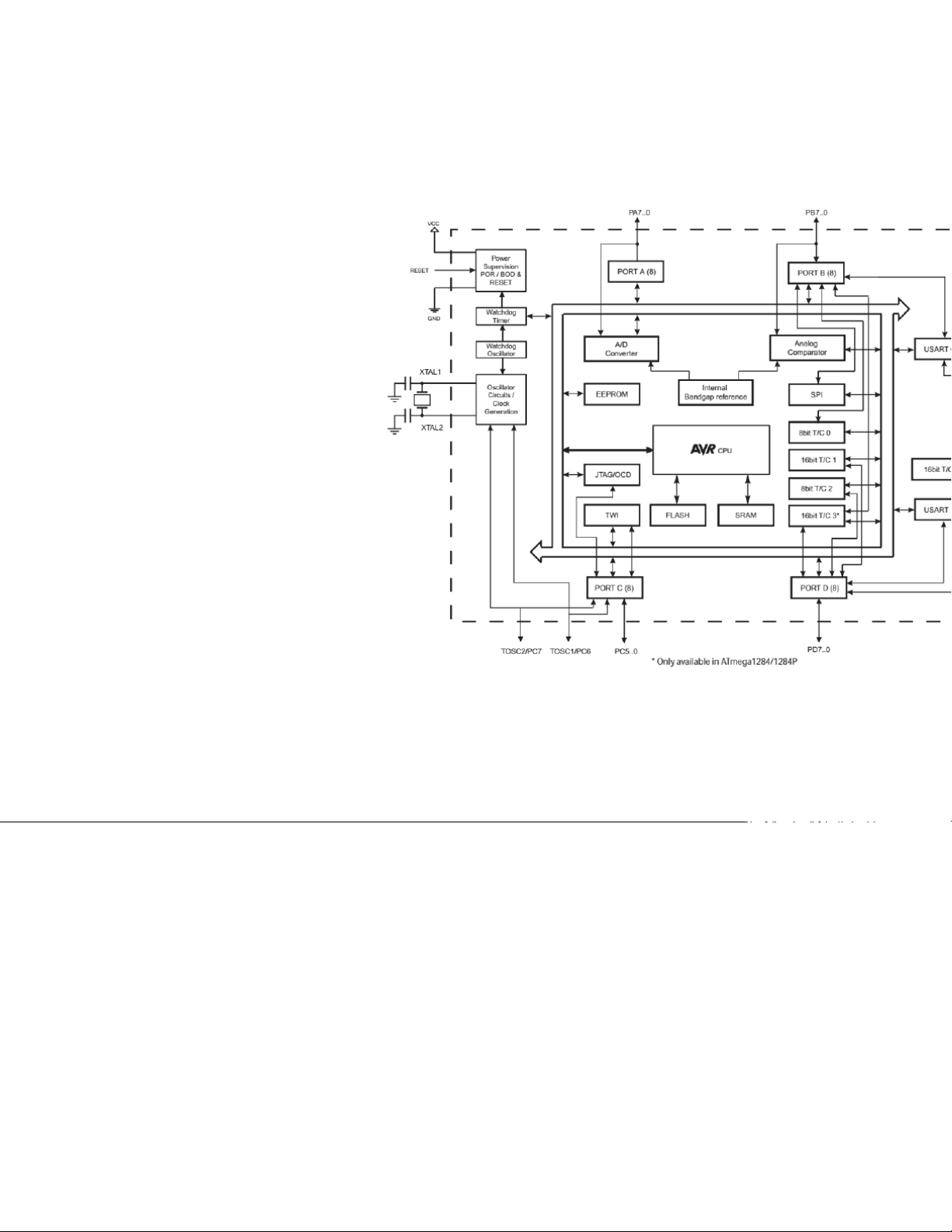

2.2 Kiến trúc phần cứng VĐK ATmega324P 14:40, 10/01/2026

Chương 2: Kiến Trúc Phần Cứng AVR ATmega324P - Tài Liệu Học Tập - Studocu

2.2 Kiến trúc phần cứng VĐK ATmega324P c tính kỹ thuật:

Tmega324P là vi điều khiển

8 bit CMOS công suất thấp theo kiến trúc RISC nâng cao. ó 131 lệnh.

a số các lệnh thực thi 1 chu kỳ xung nhịp. ó thể đạt tới 20 MIPS (Million Instructions Per

Second) với tần số 20MHz. ộ nhân 2 chu kỳ on-chip. Nguyễn Lý Thiên Trường 14:40, 10/01/2026

Chương 2: Kiến Trúc Phần Cứng AVR ATmega324P - Tài Liệu Học Tập - Studocu

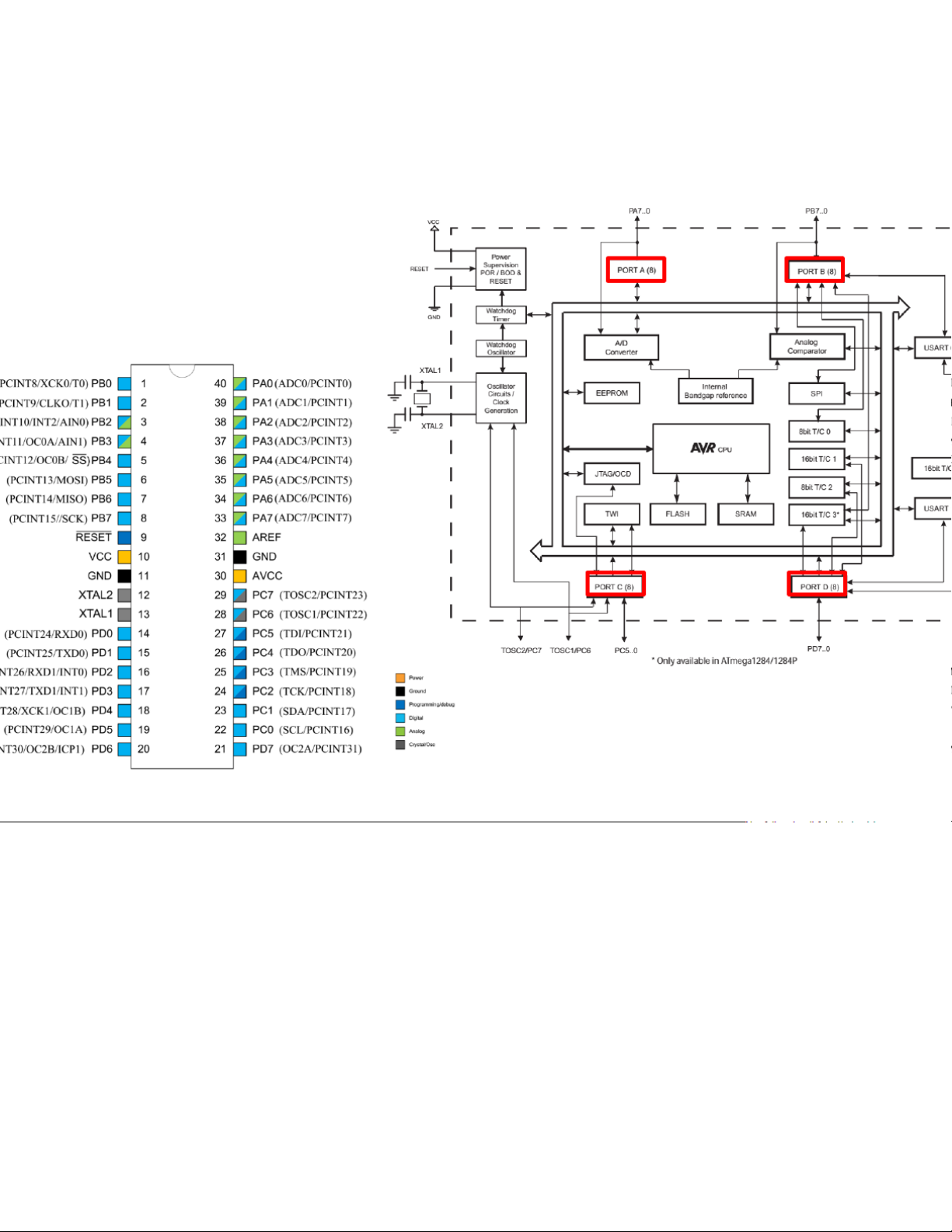

2.2 Kiến trúc phần cứng VĐK ATmega324P c tính kỹ thuật:

2 đường I/O (4 port) lập

trình được: Port A, Port B, Port C, Port D. Nguyễn Lý Thiên Trường 14:40, 10/01/2026

Chương 2: Kiến Trúc Phần Cứng AVR ATmega324P - Tài Liệu Học Tập - Studocu

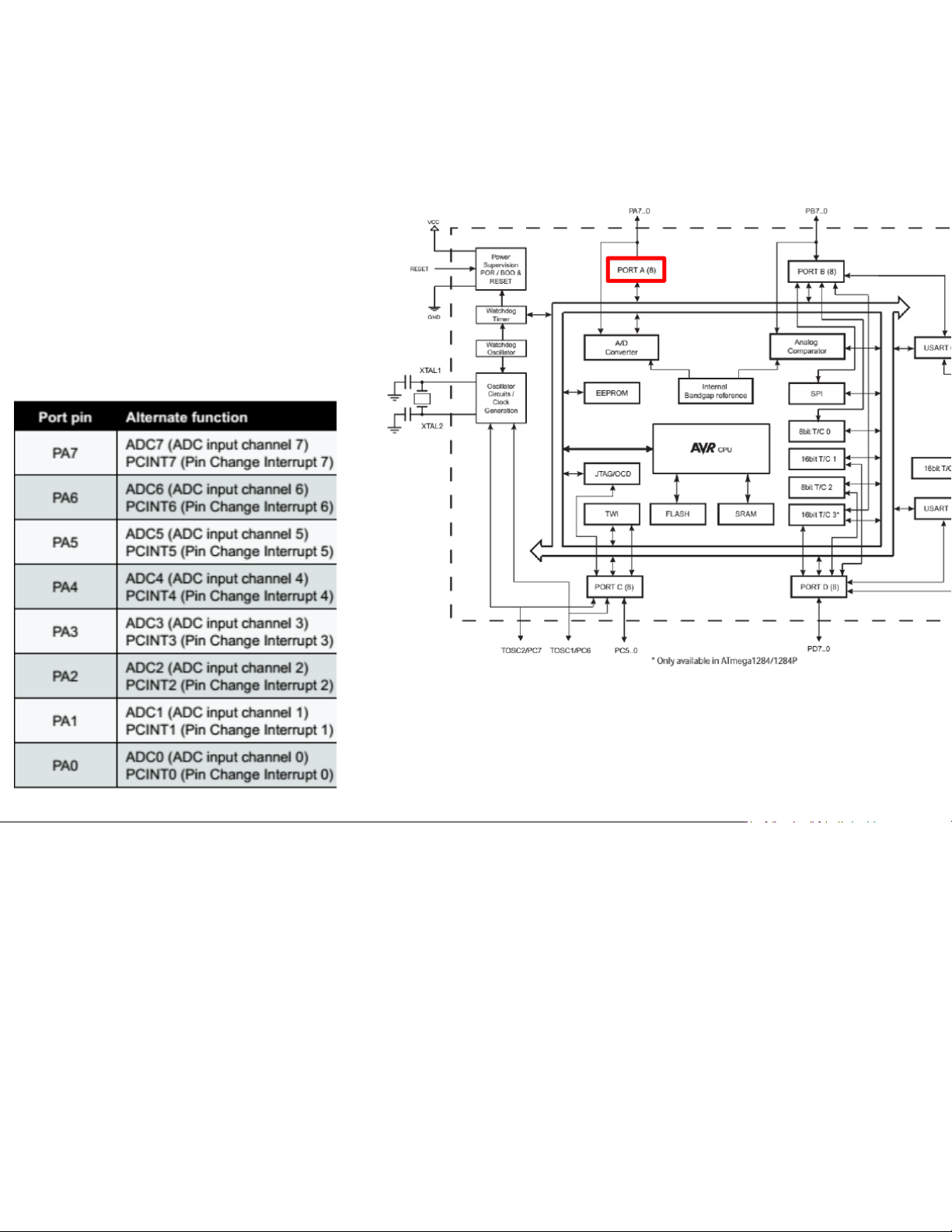

2.2 Kiến trúc phần cứng VĐK ATmega324P ort A (PA7 … PA0):

port I/O 8 bit 2 chiều có điện trở kéo

ên bên trong, có thể lập trình riêng cho ừng bit.

reset các chân port A là chân nhập.

t A cũng có chức năng khác như sau: Nguyễn Lý Thiên Trường 14:40, 10/01/2026

Chương 2: Kiến Trúc Phần Cứng AVR ATmega324P - Tài Liệu Học Tập - Studocu

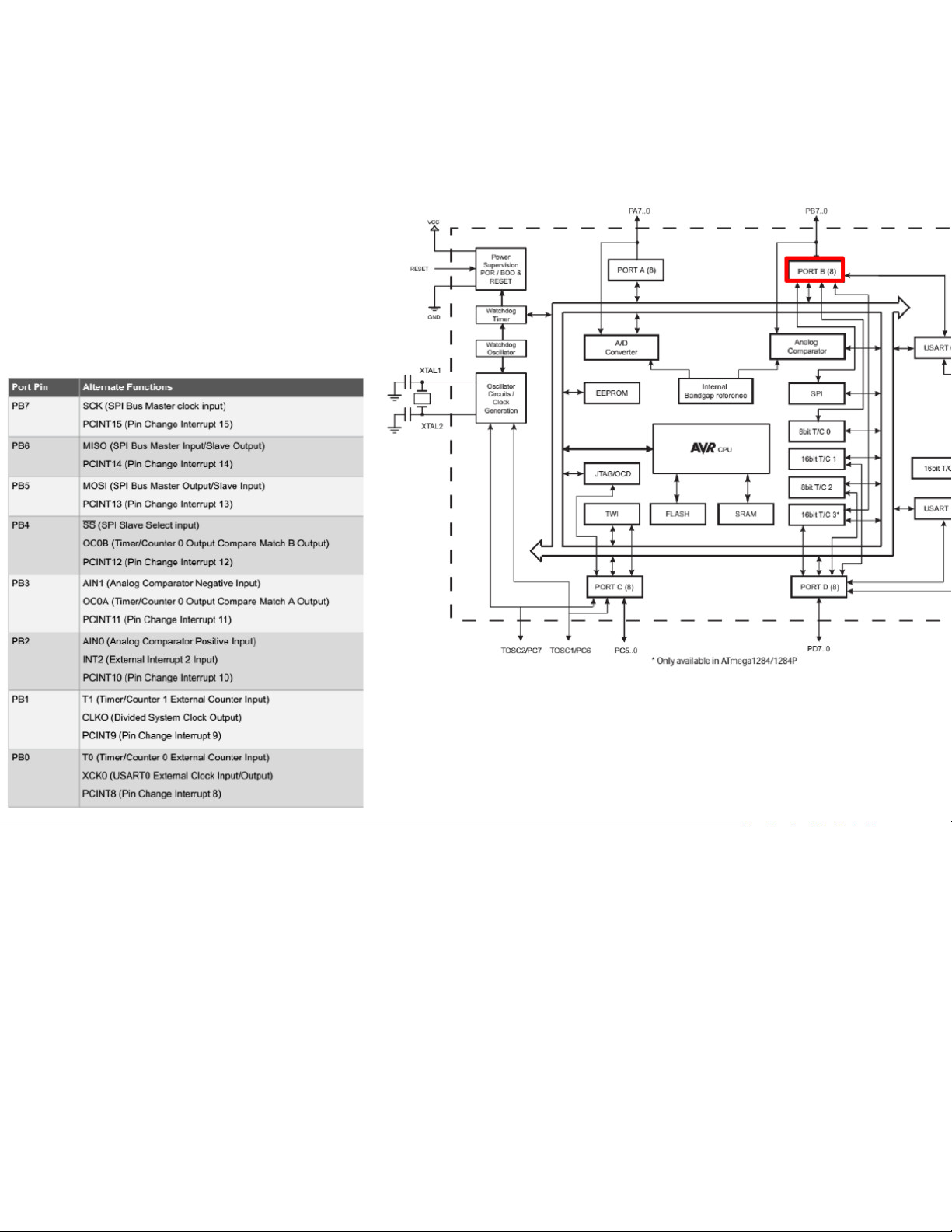

2.2 Kiến trúc phần cứng VĐK ATmega324P ort B (PB7 … PB0):

port I/O 8 bit 2 chiều có điện trở kéo

n bên trong, có thể lập trình riêng cho ừng bit.

reset các chân port B là chân nhập.

B cũng có chức năng khác như sau: Nguyễn Lý Thiên Trường 14:40, 10/01/2026

Chương 2: Kiến Trúc Phần Cứng AVR ATmega324P - Tài Liệu Học Tập - Studocu

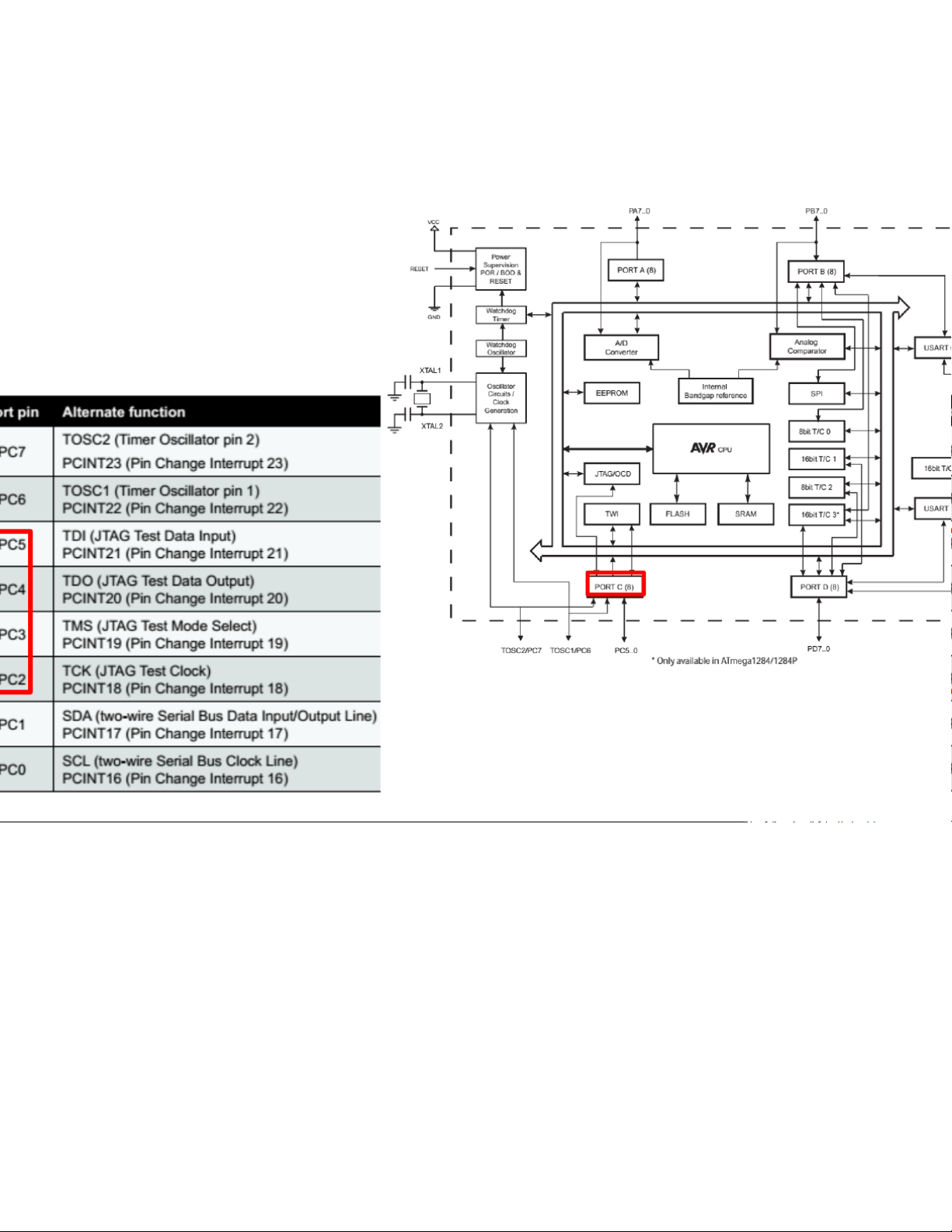

2.2 Kiến trúc phần cứng VĐK ATmega324P ort C (PC7 … PC0):

ort I/O 8 bit 2 chiều có điện trở kéo

n bên trong, có thể lập trình riêng cho ng bit.

reset các chân port C là chân nhập.

C cũng có chức năng khác như sau: Nguyễn Lý Thiên Trường 14:40, 10/01/2026

Chương 2: Kiến Trúc Phần Cứng AVR ATmega324P - Tài Liệu Học Tập - Studocu

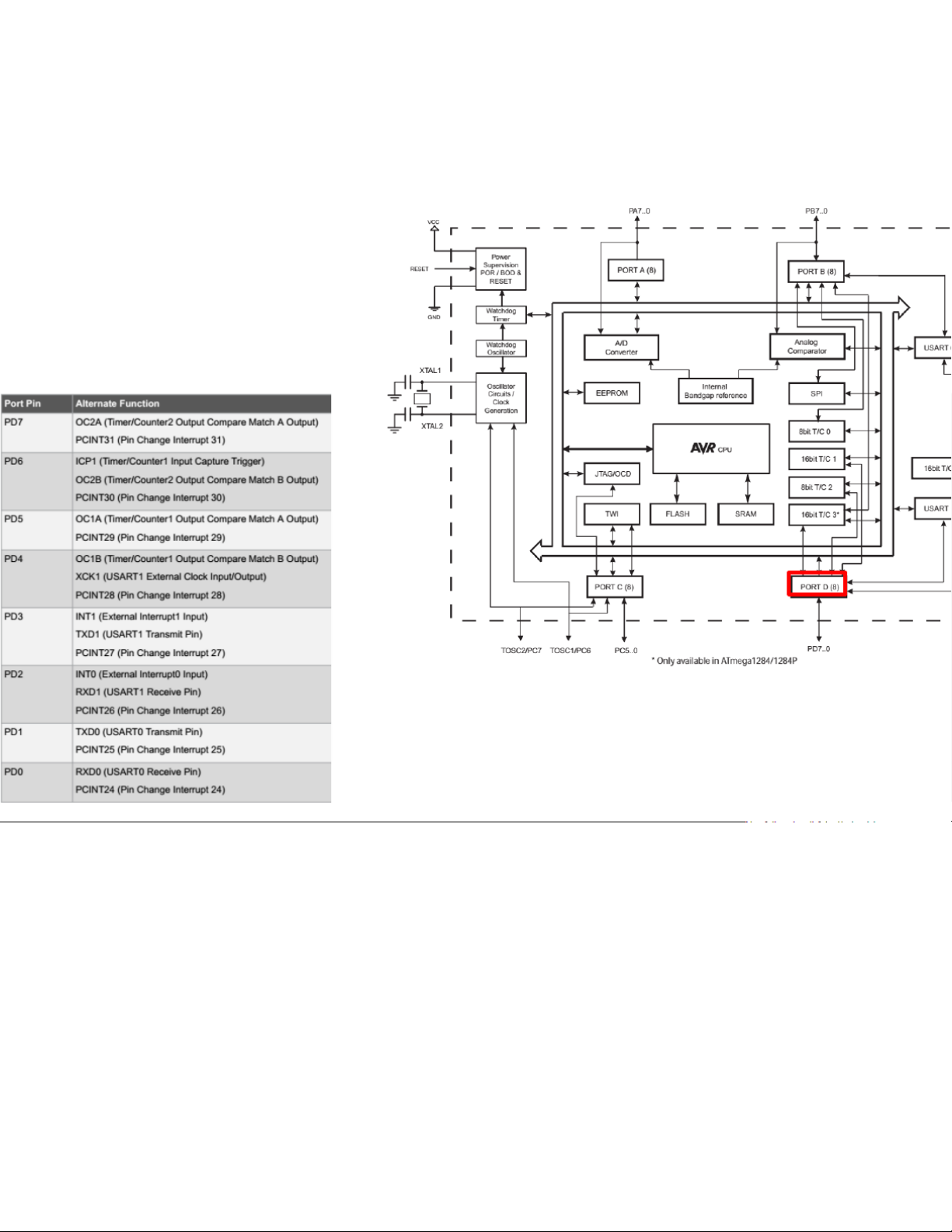

2.2 Kiến trúc phần cứng VĐK ATmega324P ort D (PD7 … PD0):

port I/O 8 bit 2 chiều có điện trở kéo

ên bên trong, có thể lập trình riêng cho ừng bit.

reset các chân port D là chân nhập.

t D cũng có chức năng khác như sau: Nguyễn Lý Thiên Trường 14:40, 10/01/2026

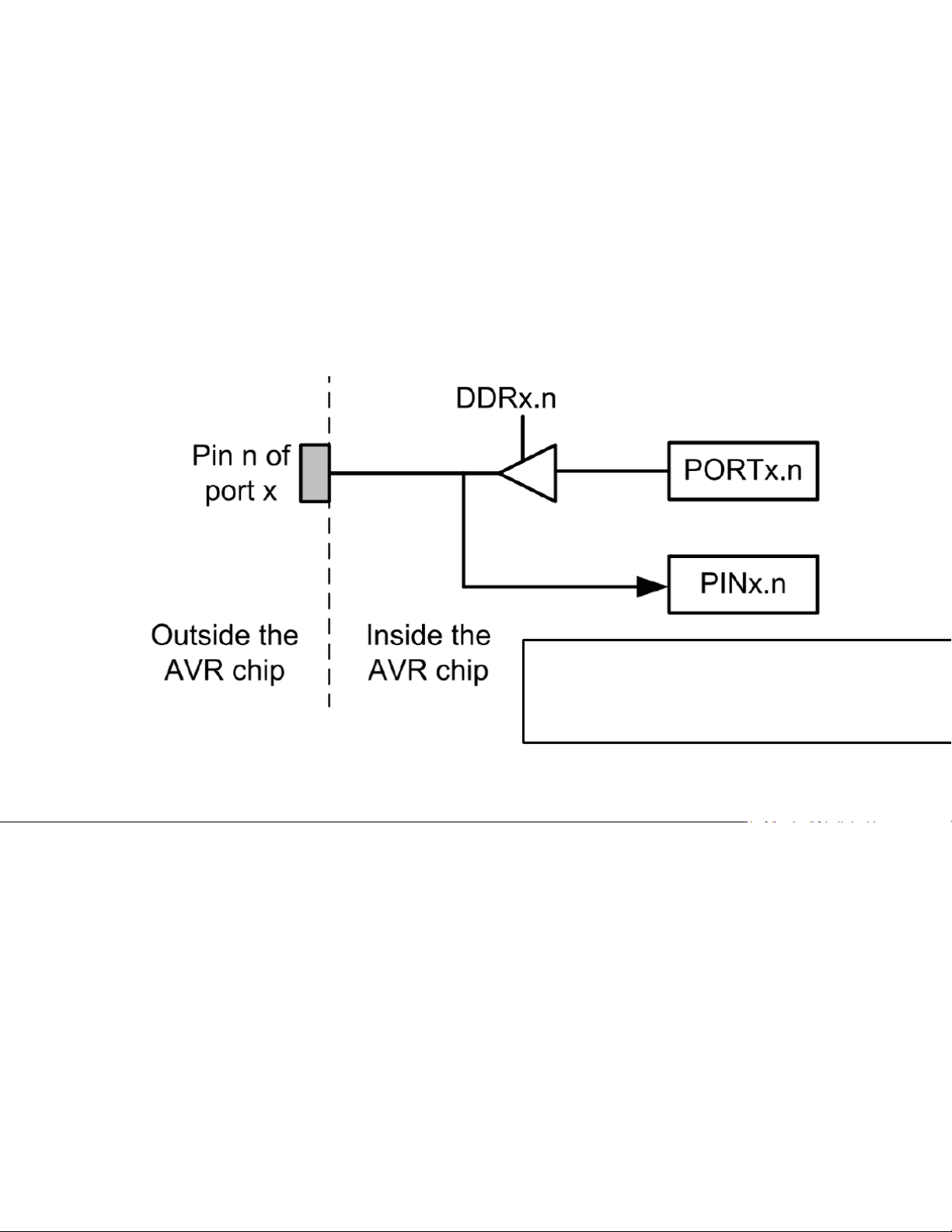

Chương 2: Kiến Trúc Phần Cứng AVR ATmega324P - Tài Liệu Học Tập - Studocu Cấu trúc chân port I/O

Tmega324P có 4 port: PortA, PortB, PortC và PortD. Các chân port này có nhiều

chức năng riêng để làm việc với ngoại vi. Nếu không dùng các chức năng này thì cá chân port có thể

dùng làm chân xuất/nhập số.

Mỗi port có 3 thanh ghi liên quan là DDRx, PORTx, PINx (với x là A, B, C, D). Chú ý mỗi chân của mỗi port có thể đi ều kh iển x uất/nhập riêng lẻ.

▪DDRx: Port x Data Direction Register ▪PORTx: Port x Data Register

•x là tên các port: x = A, B, C, D

▪PINx: Port x Input Pins Address

•n là số thứ tự chân trong port: n = 0, 1, , … 7 Nguyễn Lý Thiên Trường 14:40, 10/01/2026

Chương 2: Kiến Trúc Phần Cứng AVR ATmega324P - Tài Liệu Học Tập - Studocu Cấu trúc chân port I/O

Ví dụ: Chọn chức năng xuất cho PortA,

PortB và chức năng nhập cho PortC. Xuất giá trị H 55 ra port B. LDI

R16, 0xFF ; R16 = 0xFF = 0b1111 OUT

DDRA, R16; Port A được chọn là xu OUT

DDRB, R16; Port B được chọn là xu LDI

R16, 0x00 ; R16 = 0x00 = 0b00000 OUT

DDRC, R16 ; Port C được chọn là n

là tên các port: x = A, B, C, D LDI

R16, 0x55 ; R16 = 0x55 = 0b01010

là số thứ tự chân trong port: n = 0, 1, …, 7 OUT

PORTB, R16; xuất giá trị 55H ra Po

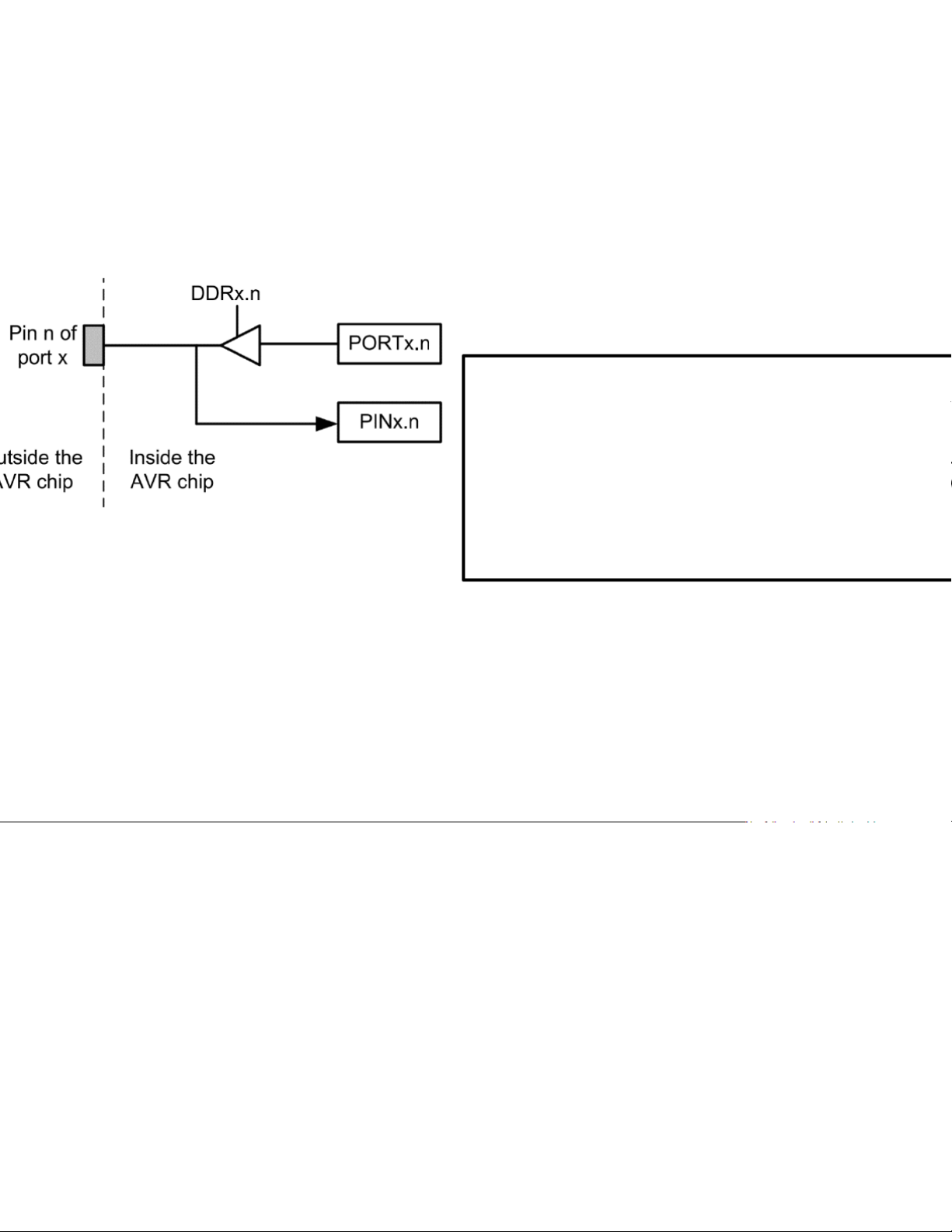

hi các giá trị 1 vào thanh ghi DDRx tại vị trí nào thì bit tương ứng của chân port đó s

là chân xuất (output), ngược lại

ghi giá trị 0 thì chân port sẽ là chân nhập (input).

Khi reset hệ thống, giá trị ban đầu của các thanh ghi DDRx là 0x00 nên các port đều l chân nhập (input). Nguyễn Lý Thiên Trường 14:40, 10/01/2026

Chương 2: Kiến Trúc Phần Cứng AVR ATmega324P - Tài Liệu Học Tập - Studocu Cấu trúc chân port I/O

Ví dụ: Nhập dữ liệu 8 bit từ port C và xuấ ra port D. LDI

R16, 0x00 ; R16 = 0x00 = 0b00000 OUT

DDRC, R16 ; Port C được chọn là n LDI

R16, 0xFF ; R16 = 0xFF = 0b1111 OUT

PORTC, R16; cho sử dụng điện trở lên ở Port C OUT

DDRD, R16; Port D được chọn là x IN

R16, PINC ; nhập dữ liệu từ Port C cất vào thanh ghi R16

là tên các port: x = A, B, C, D OUT

PORTD, R16; xuất giá trị ra Port D

là số thứ tự chân trong port: n = 0, 1, …, 7

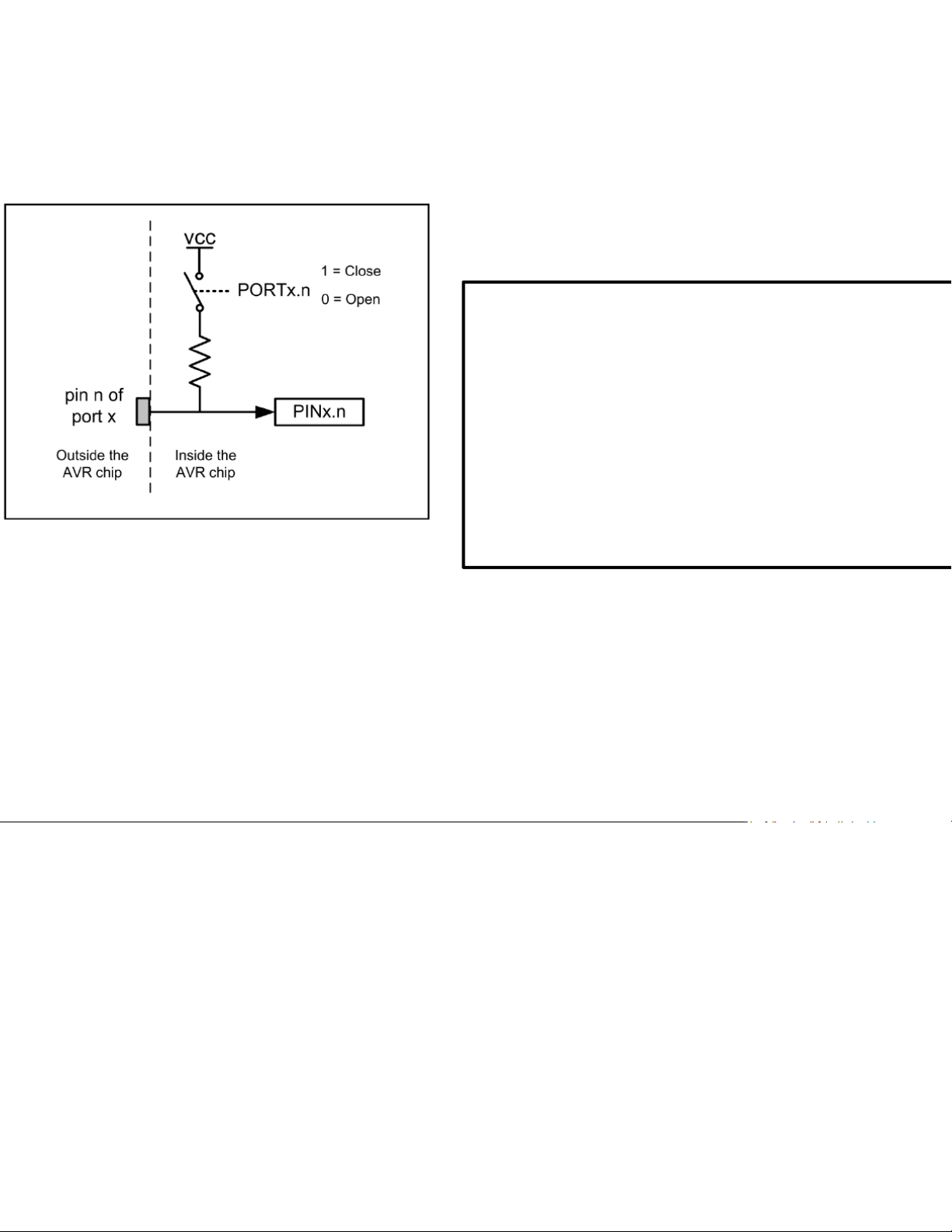

ác chân port của AVR đều có điện trở kéo lên. Việc sử dụng điện trở kéo lên đảm bảo các ngõ

vào ổn định tại mức logic mong đợi nếu các thiết bị bên ngoài không có kết nối hay ở trạng th trở kháng cao.

ể sử dụng các điện trở này thì ghi các giá trị 1 vào thanh ghi PORTx tương ứng. Nếu ghi giá trị

thì không cho phép sử dụng các điện trở kéo lên.

hi các chân port được chọn là nhập (input), thì việc đọc nội dung thanh ghi PINx sẽ có được gi

trị nhập về từ các chân port tương ứng.