Preview text:

TRƯỜNG ĐẠI HỌC BÁCH KHOA HÀ NỘI

KHOA ĐIỆN TỬ - VIỄN THÔNG ************* ĐỀ TÀI:

MẠCH KỸ THUẬT SỐ VỚI BỘ ĐẾM THUẬN (từ 00 đến 59)

Sinh viên thc hiê n:

1. Nguyn Đnh Hương- 20192898 2. Ngô Th Anh - 20192687

H Nô i, ngy 30 th"ng 9 năm 2020. 1 Mục lục

Mục lục………………………………………………………………………....2

I. Cơ sở lý thuyết……………………………………………………………….3

1.Tm hiểu về tín hiệu số v ứng dụng………………………………………..3

2. C"c cổng logic cơ bản v thuật to"n logic …………………………………3

3. Mạch dãy, mạch đm……………………………………………………….6

4.Tm hiểu về IC, số họ TTL v CMOS………………………………..……..7

II. Thực hành……………………………………………………………………9

1.Tên bi thực hnh……………………………………………………………10

2. Linh kiện…………………………………………………………………….10

3. Sơ đồ khối…………………………………………………………………...11

4.Sơ đồ thit k………………………………………………………………...12

III, Kết quả……………………………………………………………………... 12 2 I,Cơ sở lý thuyết.

1.Tìm hiểu về tín hiệu số và ứng dụng. a, Tín hiệu số.

Tín hiệu số l tín hiệu được sử dụng để biểu din dữ liệu dưới dạng một chuỗi

c"c gi" trị rời rạc; tại bất kỳ thời điểm no, nó chỉ có thể đảm nhận một trong số c"c

gi" trị hữu hạn. Điều ny tương phản với một tín hiệu tương tự, đại diện cho c"c gi"

trị liên tục; tại bất kỳ thời điểm no, tín hiệu tương tự đại diện cho một số thực trong

phạm vi gi" trị liên tục. b, Ứng dụng

Xử lý tín hiệu số có nhiều ứng dụng đa dạng, ví dụ như trong lĩnh vực điện tử y

sinh, trong điều chỉnh động cơ diesel, xử lý thoại, c"c cuộc gọi điện thoại khoảng

c"ch xa, xử lý ting nói, xử lý âm thanh, v tăng cường chất lượng hnh ảnh v

truyền hnh. C"c công nghệ nén MPEG hay WMV hiện nay đều dựa trên tin bộ của

công nghệ xử lý tín hiệu số.

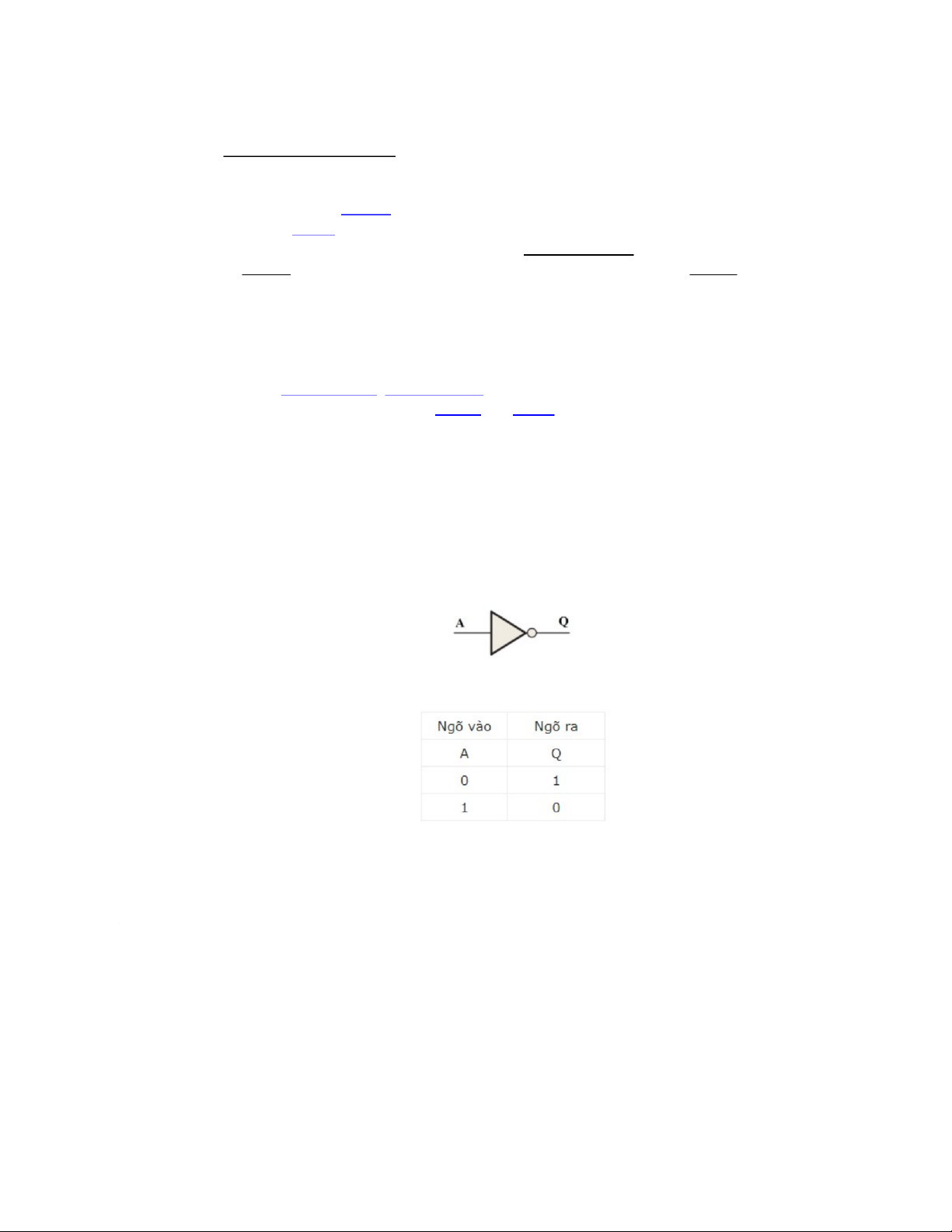

2.Các cổng logic cơ bản và thuật toán logic a, Cổng NOT

- Định nghĩa: Cổng NOT l một cổng Logic thực hiện thuật to"n phủ định

Logic tín hiệu đầu vo. - Kí hiệu: - Bảng trạng th"i: 3

Nhận xét: Ngõ vo v ngõ ra có mức logic tr"i ngược nhau. - Biểu thức logic: Q = b, Cổng AND

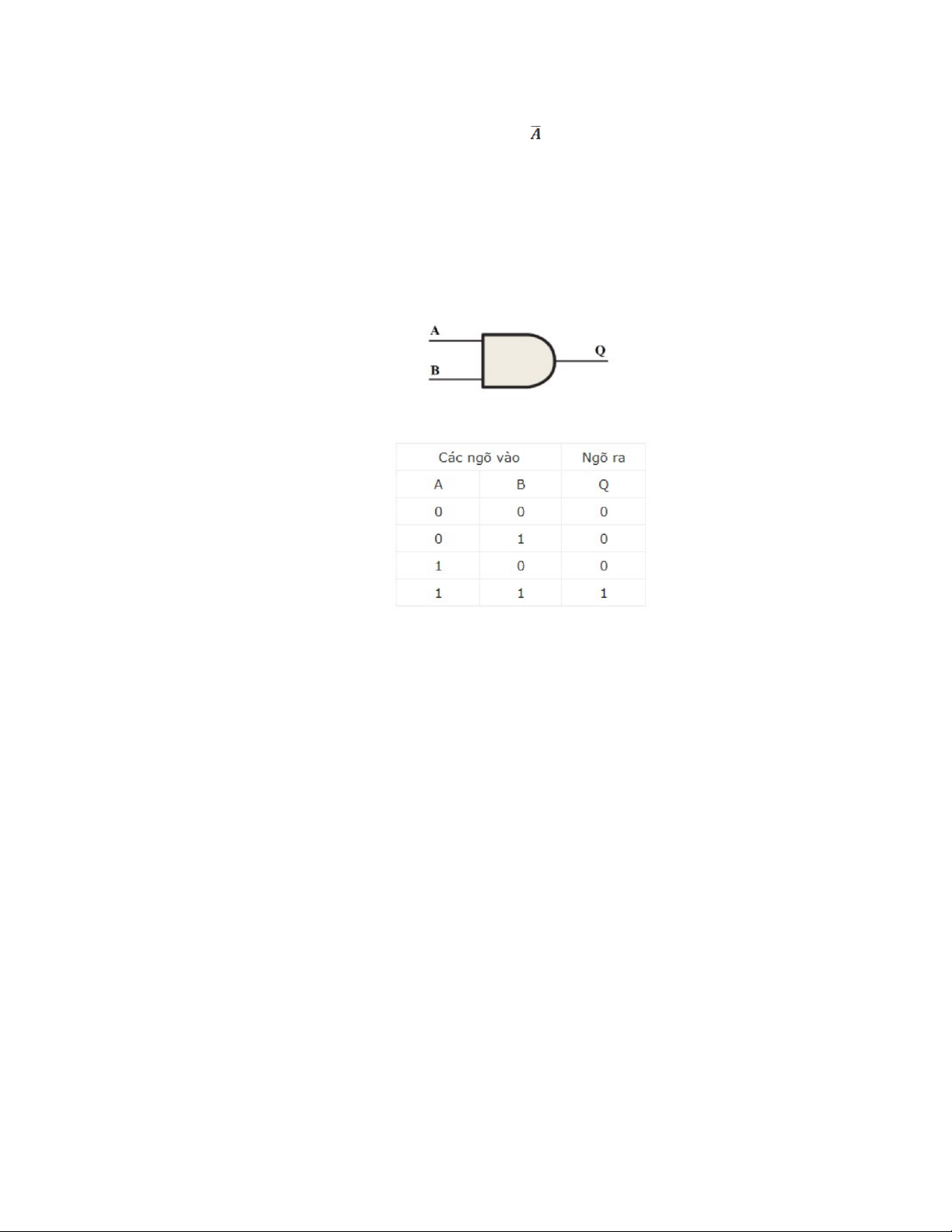

- Định nghĩa: Cổng AND l một cổng logic thực hiện thuật to"n nhân logic c"c tín hiệu đầu vo. -Kí hiệu: - Bảng trạng th"i: Nhận xét:

Ngõ ra cổng AND chỉ ở mức cao khi tất cả c"c ngõ vo lên cao.

Khi có một ngõ vo bằng 0, ngõ ra bằng 0 bất chấp c"c ngõ vo còn lại. - Biểu thức logic: Q = A.B c, Cổng OR

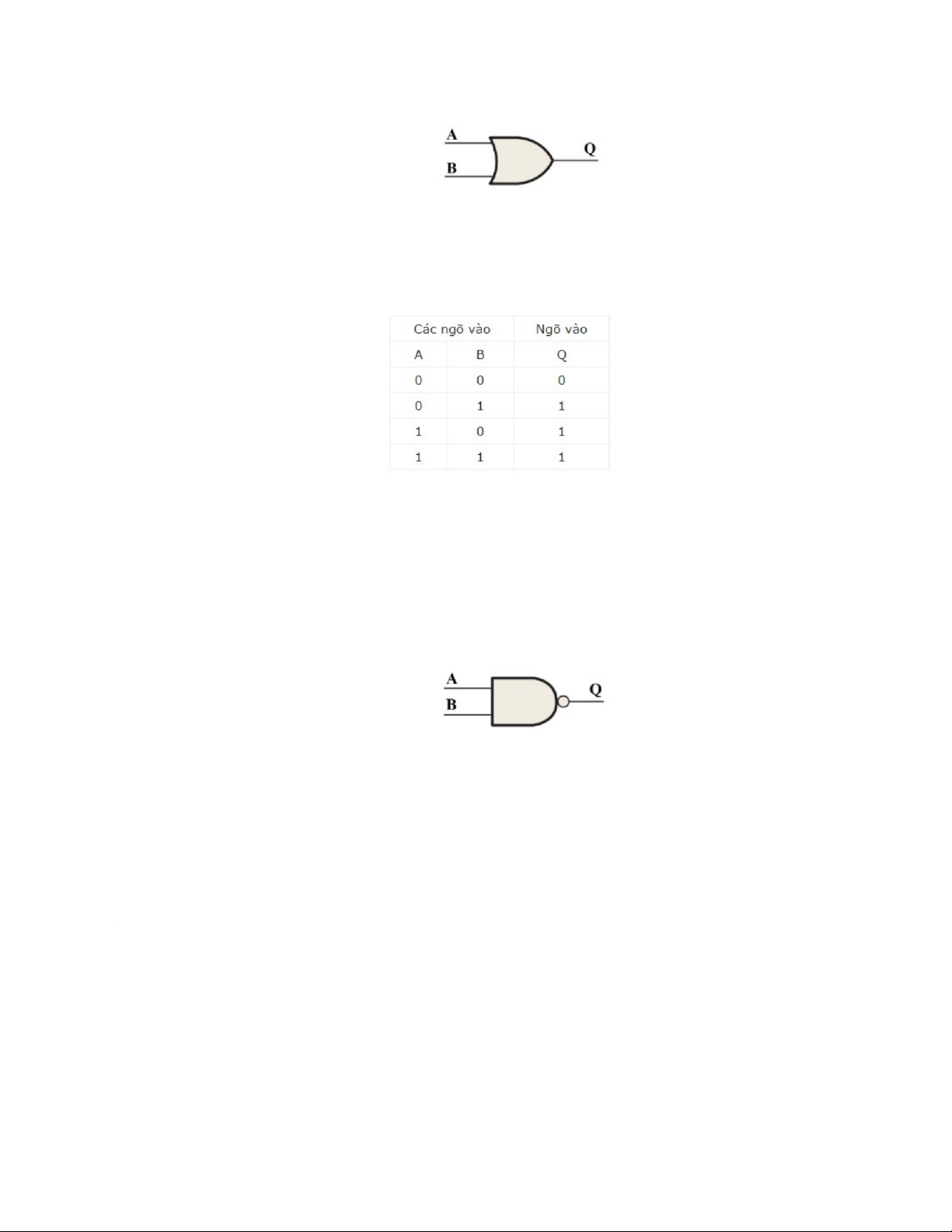

- Định nghĩa: Cổng OR l một cổng logic thực hiện thuật to"n tổng logic c"c tín hiệu đầu vo. 4 -Kí hiệu: - Bảng trạng th"i: Nhận xét:

Ngõ ra cổng OR chỉ ở mức thấp khi tất cả c"c ngõ vo xuống thấp.

Khi có một ngõ vo bằng 1, ngõ ra bằng 1 bất chấp c"c ngõ vo còn lại. - Biểu thức logic: Q = A + B d, Cổng NAND

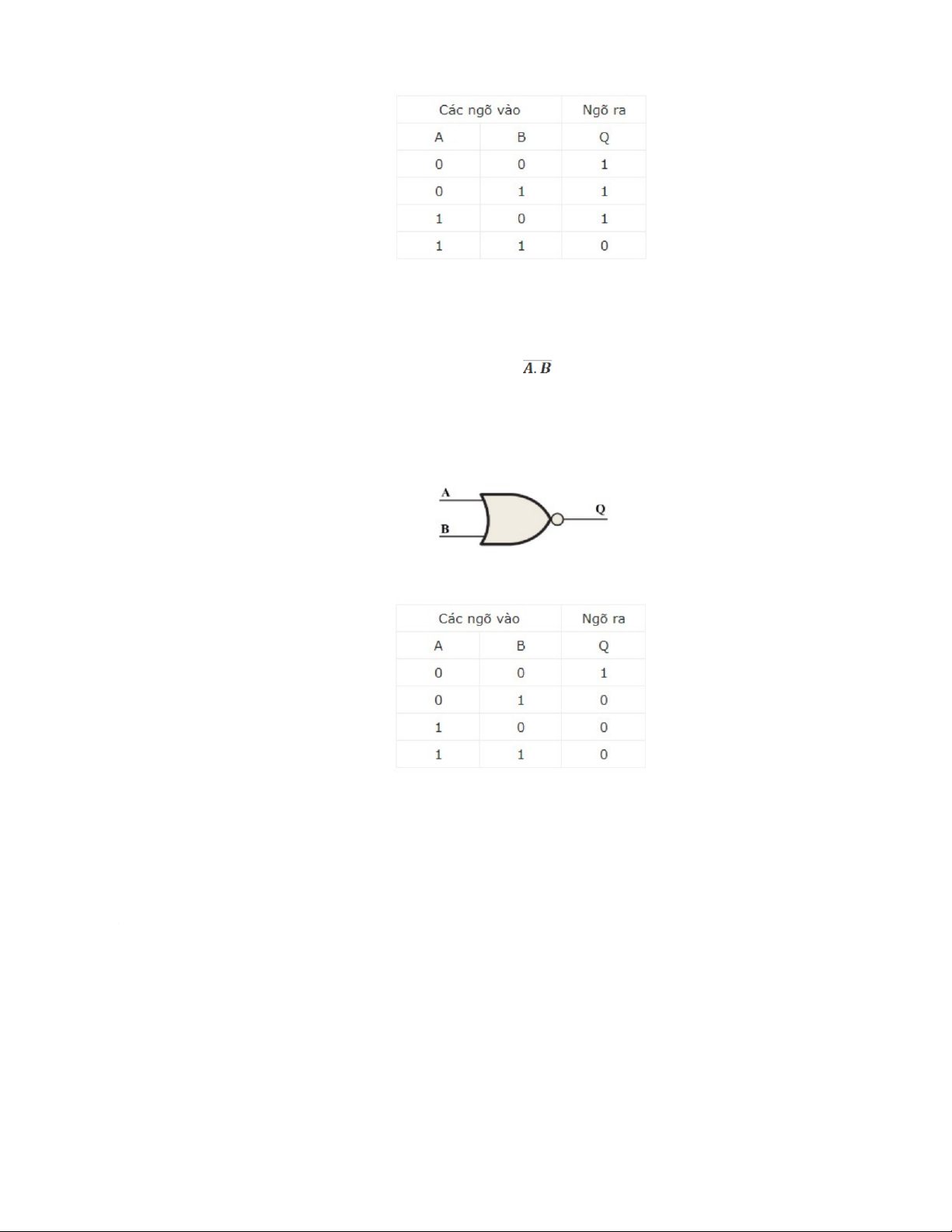

- Định nghĩa: Cổng NAND l một cổng logic thực hiện thuật to"n phủ định tích

logic c"c tín hiệu đầu vo. - Kí hiệu: - Bảng trạng th"i: 5 Nhận xét:

Ngõ ra cổng NAND = 1 khi có ít nhất 1 ngõ vo của nó bằng 0.

Ngõ ra cổng NAND = 0 khi tất cả c"c ngõ vo của nó bằng 1. - Biểu thức logic: Y = e,Cổng NOR

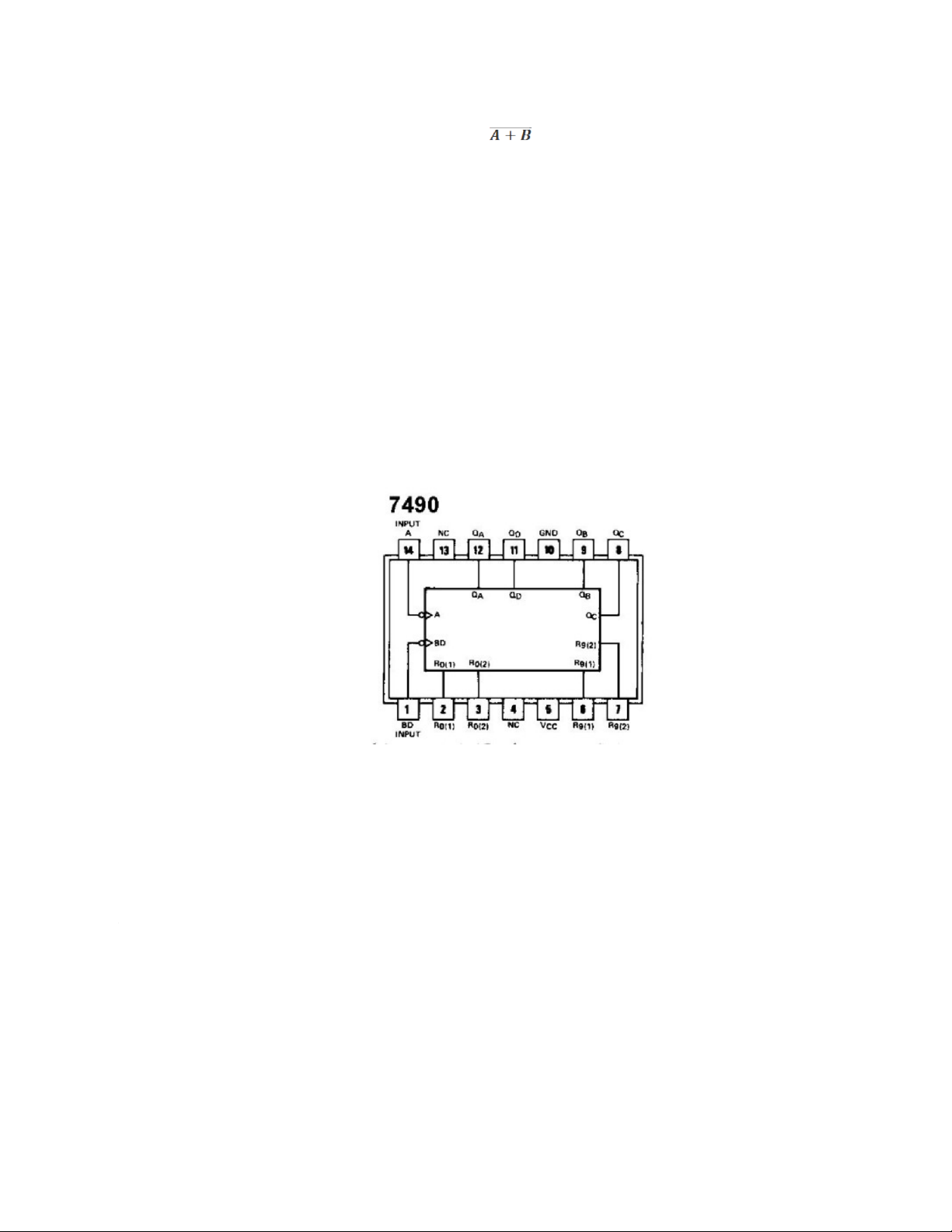

- Định nghĩa: Cổng NOR l một cổng logic thực hiện thuật to"n phủ định tổng

logic của c"c tín hiệu đầu vo. - Kí hiệu: - Bảng trạng th"i: Nhận xét:

Ngõ ra cổng NOR = 1 khi tất cả c"c ngõ vo của nó có gi" trị 0. 6

Ngõ ra cổng NOR = 0 khi có ít nhất 1 ngõ vo của nó có gi" trị 1 - Biểu thức logic: Y =

3. Mạch dãy, mạch đếm. a, Mạch đm:

-Mạch đm hay Counter l một mạch tích hợp thực hiện đm v chứa số lần

xảy ra sự kiện hoặc qu" trnh no đó, thông thường th có gắn với xung nhịp clock.

-Mạch đm sử dụng chip 74LS90 đây l chíp đm thông dụng với 2 bộ đm 5

v 2 tích hợp sẵn trong chip . Từ 2 bộ đm ny kt hợp với bảng trạng th"i chúng

ta có thể reset bộ đm trong khoảng từ 0 đn 10 . Kt hợp nhiều chip lại chúng ta

có thể đm đn c"c số lớn hơn

-IC7490 gồm 2 bộ chia l chia 2 v chia 5

+ Bộ chia 2 do input A điều khiển đầu ra QA

+ Bộ chia 5 do input B điều khiển đầu ra QB,QC,QD (trong đó QD có trọng số lớn nhất) b, Mạch dãy:

-Mạch tuần hon l mạch logic có tính chất nhớ, có khâu tr

-Trạng th"i tip theo của mạch phụ thuộc vo gi" trị của kích thích ở lối vo v

trạng th"i hiện tại của mạch. 7

-Mạch tuần tự thường hoạt động đồng bộ theo sự điều khiển của tín hiệu nhịp clock.

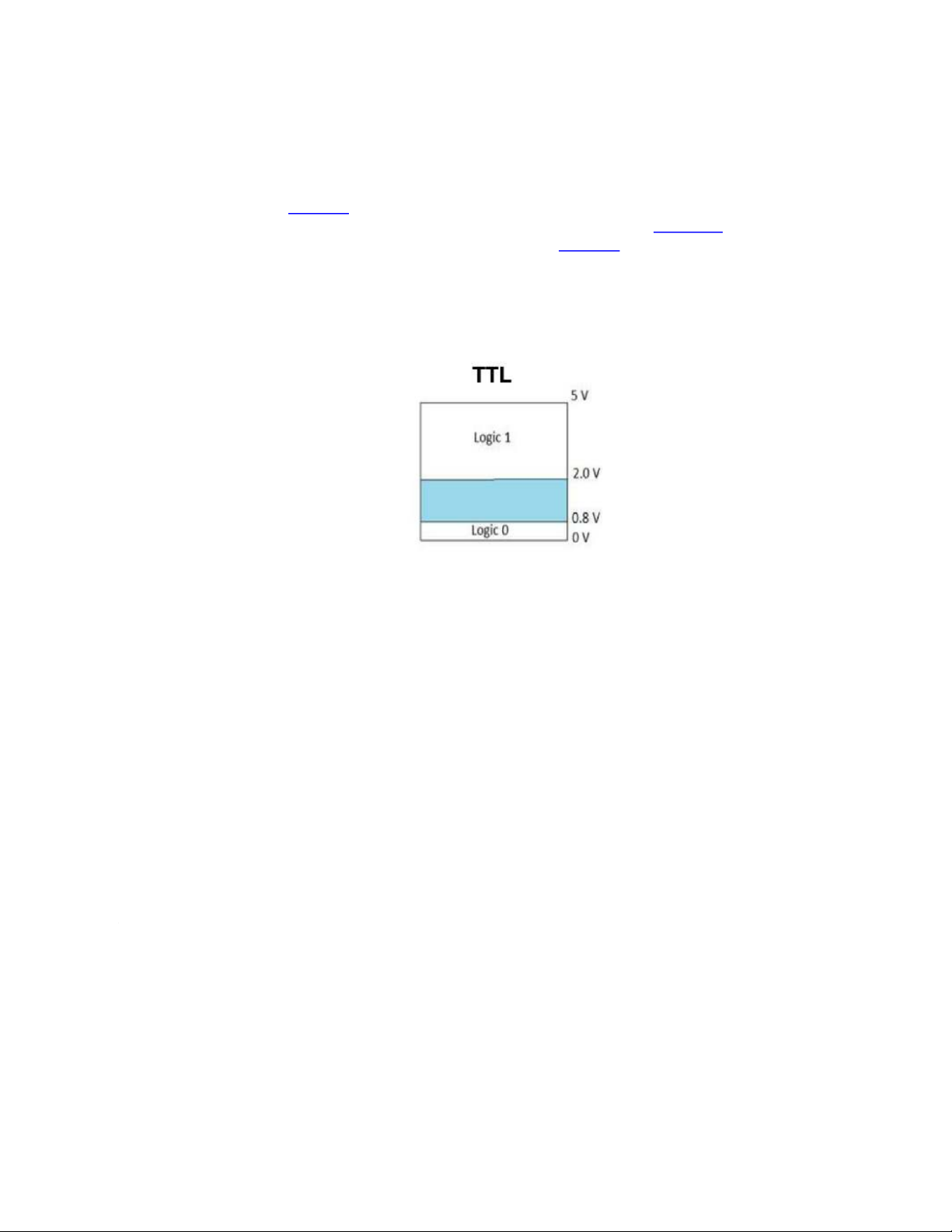

4. Tìm hiểu về IC, số họ TTL và CMOS IC họ TTL

Transistor-transistor logic hay TTL l một lớp mạch kỹ thuật số được xây dựng

từ c"c transistor lưỡng cực (BJT) v một số điện trở phụ trợ. Tên gọi transistor-

transistor logic l do nó đảm nhiệm hai chức năng, một l lm cổng logic (ví dụ

AND) v hai l chức năng khuch đại được c"c transistor thực hiện - Phân loại

+ TTL ngõ ra cực thu để hở

=> Cấu trúc của một cổng nand 2 ngõ vo v có ngõ ra cực thu để hở

Cổng NAND thường sẽ tốn kém v phức tạp hơn c"ch c"ch dùng cổng NAND cực thu để hở (open colector: CO) mặc dù cả 2 c"ch đều

dùng để thực hiện hm logic + TTL có ngõ ra 3 trạng th"i 8 - Đặc tính điện

+ Nguồn nuôi v công suất tiêu t"n: Công thức tiêu t"n được nói đn để đ"nh gi"

chất lượng của IC, rõ rng nu mạch logic no có nó thấp th được đ"nh gi" cao hơn

nhưng cũng có một tiêu chuẩn kh"c cần quan tâm l tốc độ chuyển mạch của cổng

+ Tốc độ chuyển mạch: Tích số tốc độ - công suất cng nhỏ th cổng cng tốt v

thích hợp với nhiều ứng dụng tốc độ cao hay công suất tiêu t"n thấp hay cả hai

+ Tính chống nhiu: Đôi khi c"c điện "p v dòng điện vo ra cổng logic đã được

đảm bảo ngoi vùng bất định nhưng mạch vẫn có thể hoạt động sai logic đó l do

ảnh hưởng của nhiu gồm những từ bên ngoi thâm nhập vo

+ Hệ số tải (số tỏa ra: Fanout): Hệ số tải v c"c thông số dòng "p vo ra ở trên

được coi l thông số nền tảng để tính to"n sự giao tip giữa c"c mạch TTL kh"c loại *IC họ CMOS

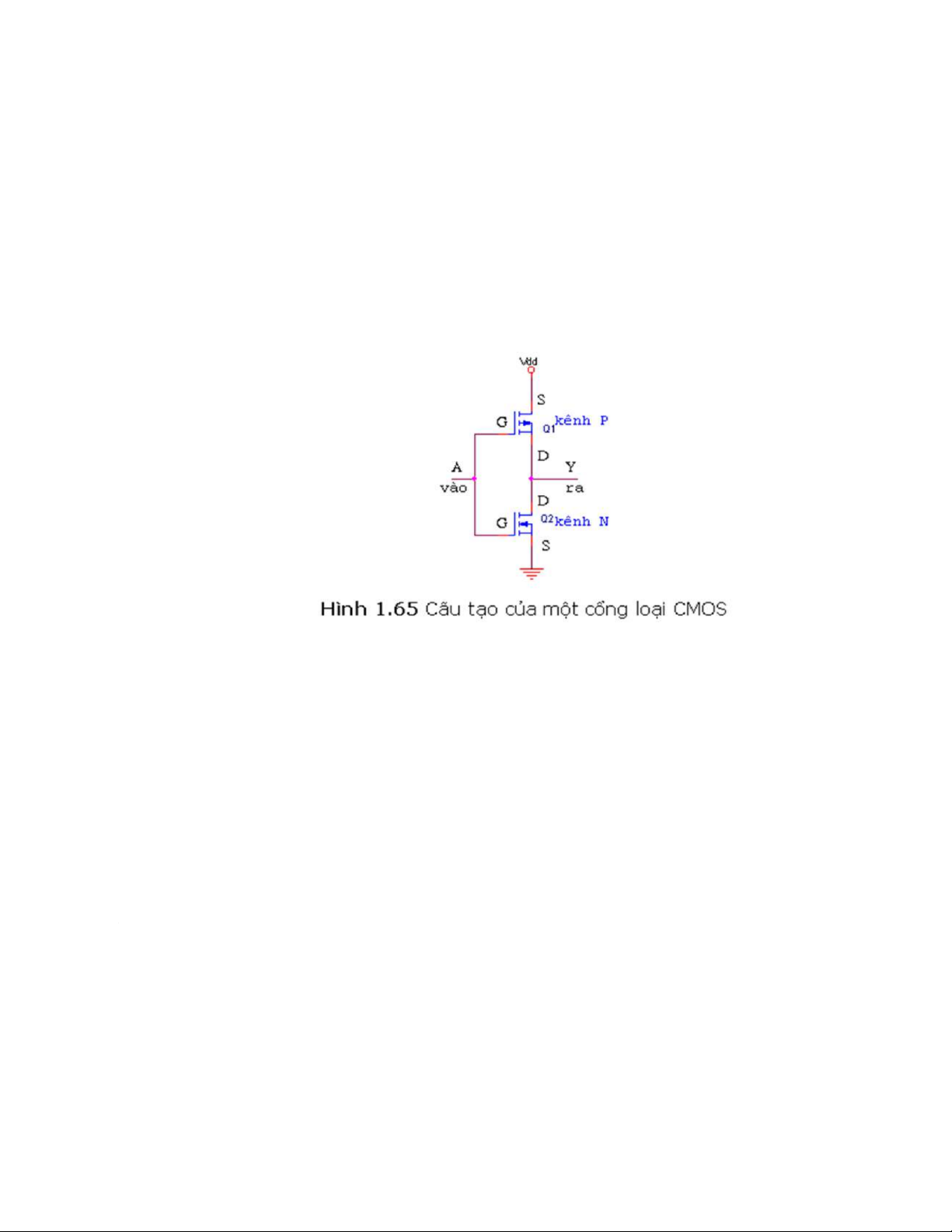

- Cấu tạo: l một cổng NOT gồm một transistor NMOS v một transistor PMOS như hnh Đặc tính kĩ thuật:

+ Công suất tiêu thụ: Khi mạch CMOS ở trạng th"i tĩnh (không chuyển mạch) th

công suất tiêu t"n PD của mạch rất nhỏ

+ Tốc độ chuyển mạch: Tốc độ chuyển mạch của CMOS th nhanh hơn hẳn loại

TTL do điện trở đầu ra thấp ở mỗi trạng th"i. Tốc độ chuyển mạch sẽ tăng lên khi

tăng nguồn nhưng điều ny cũng lm tăng công suất tiêu t"n ngoi ra nó cũng còn

ảnh hưởng bởi tải điện dung

+ Tính kh"ng nhiu: Về giới hạn nhiu nói chung l tốt hơn c"c loại TTL

+ Hệ số tải: Dòng ra của c"c CMOS kh" lớn trong lúc điện trở vo của c"c CMOS

lại rất lớn (thường khoảng 1012 ohm) tức dòng vo rất nhỏ nên số toả ra rất lớn 9 II, Thực hành. 1. Tên bài thực hành:

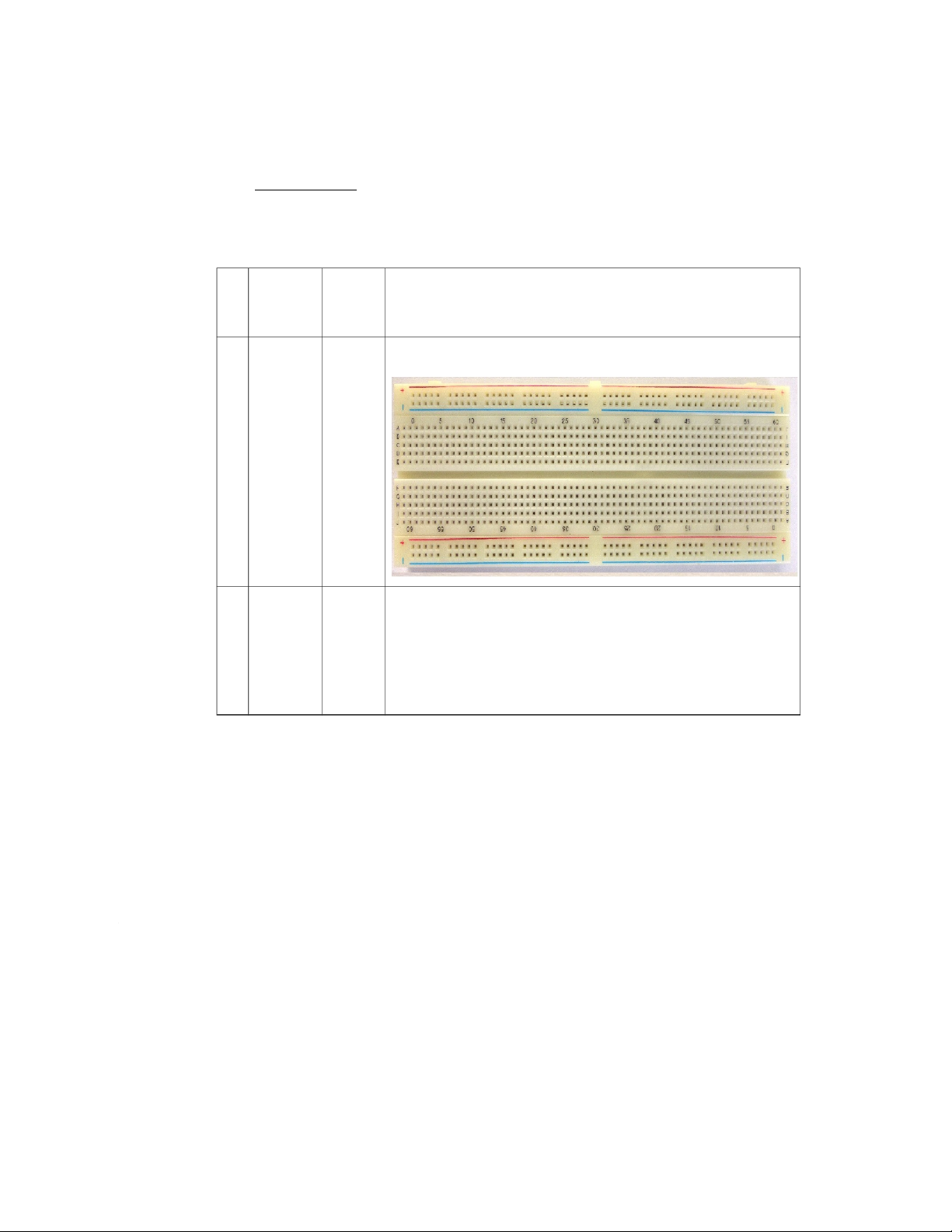

MẠCH KỸ THUẬT SỐ VỚI BỘ ĐẾM THUẬN( từ 00 đến 59) 2. Linh kiện. S Linh Số T kiện lượng Vai trò T 1 Board 1

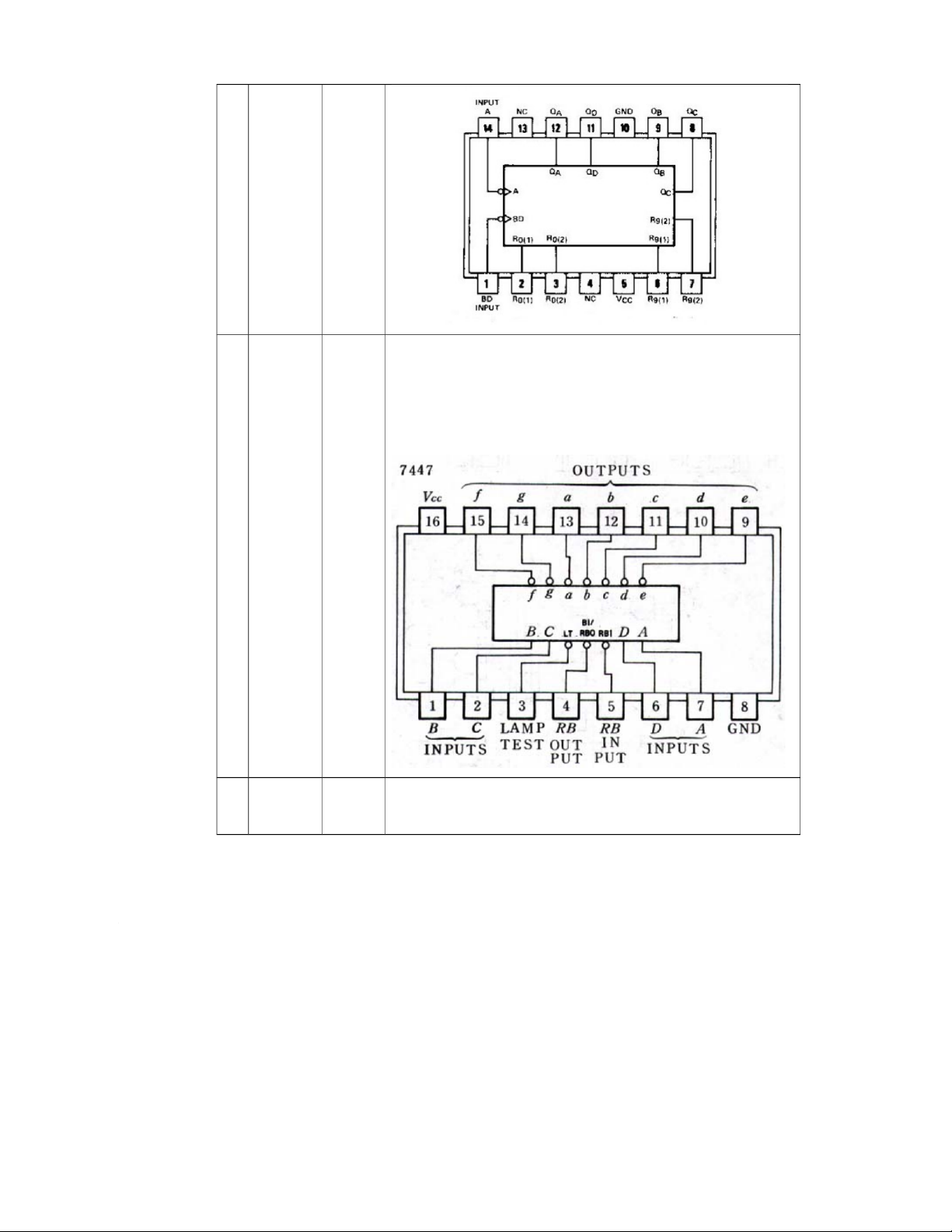

Thit bị đơn giản cho phép tạo ra mạch điện m không cần phải hn. 2 IC 2

IC 74LS90 thuộc họ TTL có công dụng đm mã nhị phân 74SL90

chia 10 mã hóa BCD. Cứ mỗi xung vo th IC 74LS90 đm

tin lên 1 v được mã hóa ra 4 chân. Khi đm đn 10 nó sẽ

reset v trở về ban đầu. IC 74LS90 ny có ứng dụng rộng

trong c"c mạch số ứng dụng đm 10 v trong c"c mạch chia tần. 10 3 IC 2

IC SN7447AN l IC giải mã ginh riêng cho LED 7 đoạn 74LS47

anode chung. IC SN7447AN chuyển đổi từ mã BCD sang mã LED 7 đoạn anode chung.

Ứng dụng khi ta cần hiện thị số trên LED 7 đoạn trong

mạch số m không cần dùng vi điều khiển, hoặc muốn tit

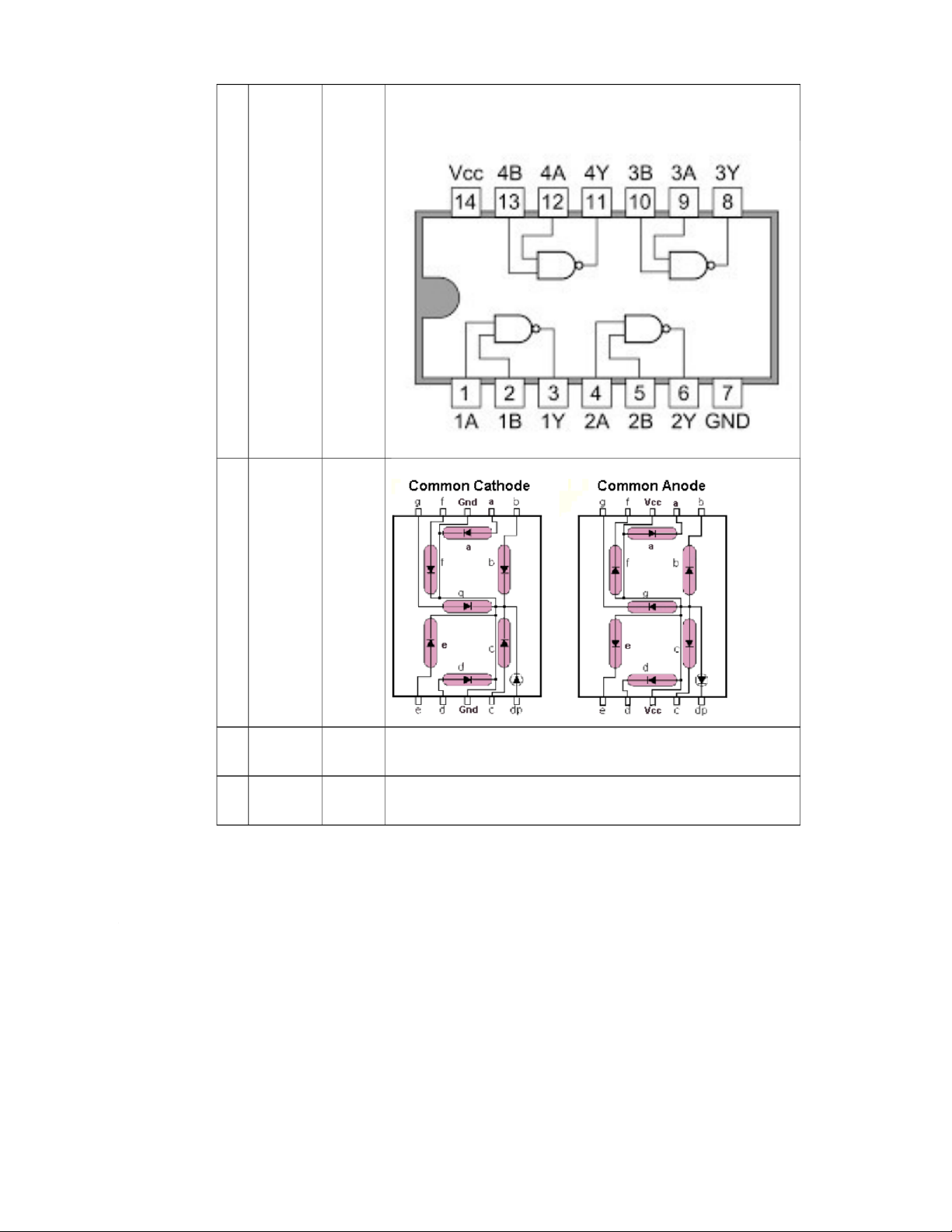

kiệm chân cho vi điều khiển. 4 IC

1IC SN7447AN l IC giải mã ginh riêng cho LED 7 đoạn 74LS00

anode chung. IC SN7447AN chuyển đổi từ mã BCD sang mã LED 7 đoạn anode chung. 11

Ứng dụng khi ta cần hiện thị số trên LED 7 đoạn trong

mạch số m không cần dùng vi điều khiển, hoặc muốn tit

kiệm chân cho vi điều khiển. 5 LED 7 2

Hiển thị số đm cho mạch đm thanh 6 Điện trở 2

Khống ch dòng điện ở mức phù hợp. 4kΩ 7 Điện trở 2

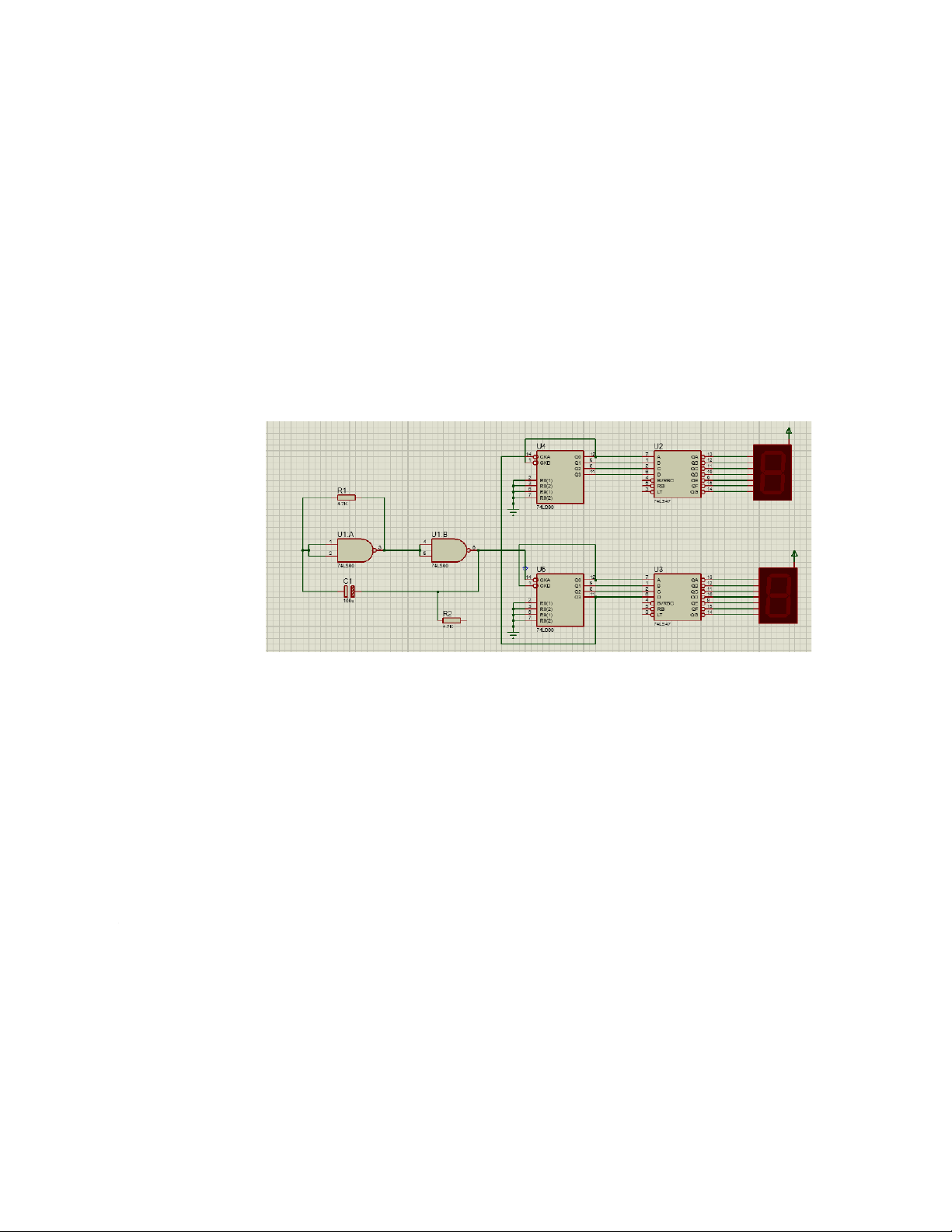

Khống ch dòng điện ở mức phù hợp. 2kΩ 12 8 Tụ điện 1 Có t"c dụng lọc 10 µF 9 Dây dẫn 5 Kt nối c"c linh kiện 20cm 10 Nguồn 1 Cung cấp nguồn điện điện 3V 3. Sơ đồ khối.

a. Nguyên lí hoạt động

IC 74LS90 về cơ bản l mạch đm thập phân MOD-10 tạo ra mã BCD ở c"c ngõ ra .

74LS90 bao gồm 4 flip-flop JK chủ- tớ được kt nối bên trong để cung cấp mạch

đm MOD-2 (2 trạng th"i đm) v mạch đm MOD-5 (5 trạng th"i đm) 74LS90 có

một flip flop độc lập được điều khiển bởi đầu vo CLKA v ba flip- flop JK tạo

thnh một bộ đm không đồng bộ được điều khiển bởi đầu vo CLKB như hnh bên dưới.

Bốn ngõ ra của IC được ký hiệu l QA, QB, QC v QD. Thứ tự đm của 74LS90

được kích hoạt bởi cạnh xuống của tín hiệu xung đồng bộ, tức l khi tín hiệu xung

đồng hồ CLK chuyển từ logic 1 sang logic 0 th xem như có xung đồng hồ t"c động vo mạch đm. 13

C"c chân ngõ vo bổ sung R1, R2, R3 v R4 l c"c chân RESET. Khi c"c ngõ vo

RESET R1 v R2 được kt nối với logic1, th mạch đm sẽ bị RESET trở về 0 còn

khi c"c ngõ vo R3 v R4 được kt nối với logic 1 th mạch RESET về số 9 bất kể số

đm hoặc vị trí đm hiện tại

Như đã trnh by ở trên, bên trong IC74LS90 gồm có mạch đm chia 2 v mạch đm

chia 5. Như vậy, chúng ta có thể sử dụng một trong hai mạch đm: hoặc chỉ mạch

đm chia hai tần số hoặc chỉ bộ đm chia năm tần số hoặc kt hợp cả hai mạch đm

với nhau để tạo ra mạch đm BCD chia 10 như mong muốn.

Khi IC đm hoạt dộng ở ch độ ny th phần mạch đm chia 5 bị vô hiệu hóa. Nu

tín hiệu đồn hồ được đưa vo chân số 14 (CKA) v tín hiệu được lấy ra ở chân số 12

(Q0/QA) th chúng ta có thể tạo ra một bộ đm nhị phân chia 2 (MOD = 2) để sử

dụng trong c"c mạch chia tần số như được hiển thị ở hnh trên. Để tạo ra mạch đm

chia 5, chúng ta sẽ vô hiệu hóa flip-flop đầu tiên v đưa tín hiệu xung đồng hồ vo

chân số 1 (CKB) với tín hiệu ngõ ra được lấy từ chân số 11 (Q3/QD).

Để hiển thị c"c số đm trên led 7 đoạn chúng ta cần một IC giải mã BCD sang led 7

đoạn. IC 74LS47 hoặc 74LS247 được thit k để lm được việc đó. 74LS47 có bốn

ngõ vo cho c"c chữ số BCD A, B, C v D v có 7 ngõ ra để điều khiển c"c đoạn

của led 7 đoạn. IC giải mã hiển thị 74LS47 nhận mã BCD từ c"c ngõ ra của IC đm

74LS90 v tạo c"c tín hiệu cần thit để ra điều khiển c"c đoạn của led 7 đoạn để hiện

thị được c"c số đm. V IC giải mã 74LS47 được thit k để điều khiển led 7 đoạn

loại anode chung nên khi ngõ ra ở mức THẤP (logic 0) sẽ lm cho LED kt nối với

ngõ ra ny ph"t s"ng trong khi ngõ ra ở mức CAO (logic 1) sẽ lm cho LED ny

TẮT, Đối với hoạt động bnh thường, tất cả c"c chân LT (Lamp Test), BI/RBO

(Blanking Input/Ripple Blanking Output) v RBI (Ripple Blanking Input) đều phải

được bỏ trông hoặc kt nối với logic 1 (mức CAO).

C"c ngõ vo của IC 74LS47 được kt nối với c"c ngõ ra tương ứmg của IC đm

BCD 7Lưu ý rằng mặc dù 74LS47 có c"c ngõ ra tích cực mức THÁP v được thit

kể để giải mã hiển thị trên LED 7 đoạn loại ANODE chung. IC giải mã điều khiển

74LS48/4511 có chức năng hon ton giống như IC 74LS47 ngoại trừ nó có ngõ ra

tích cực mức CAO, được thit k để giải mã hiển thị cho 7 đoạn loại CATHODE

chung. V vậy, tùy thuộc vo loại led 7 đoạn m bạn sử dụng, bạn có thể cần IC giải mã 74LS47 hoặc 74LS48. 14

4LS90 để hiển thị c"c số đm trên led 7 đoạn như hnh trên. Số đm hiện thị trên led

7 đoạn tăng dần từ 0 đn 9 mỗi khi có xung đồng hồ t"c động vo IC đm.

Mạch của chúng ta l một mạch đm số đơn giản hiển thị c"c số đm từ 0 đn 9 sử

dụng IC đm 74LS90 v IC giải mã BCD sang led 7 đoạn 74LS47. Để đm hơn 10

th chúng ta sẽ cần ghép hai IC đm BCD lại với cho nhau.

Bộ đm BCD gồm 2 chữ số sẽ được tính theo số thập phân tư 00 đn 59 (0000

0000 đn 101 1001) v sau đó sẽ tự động RESET về 00, Lưu ý rằng mặc dù đó sẽ l

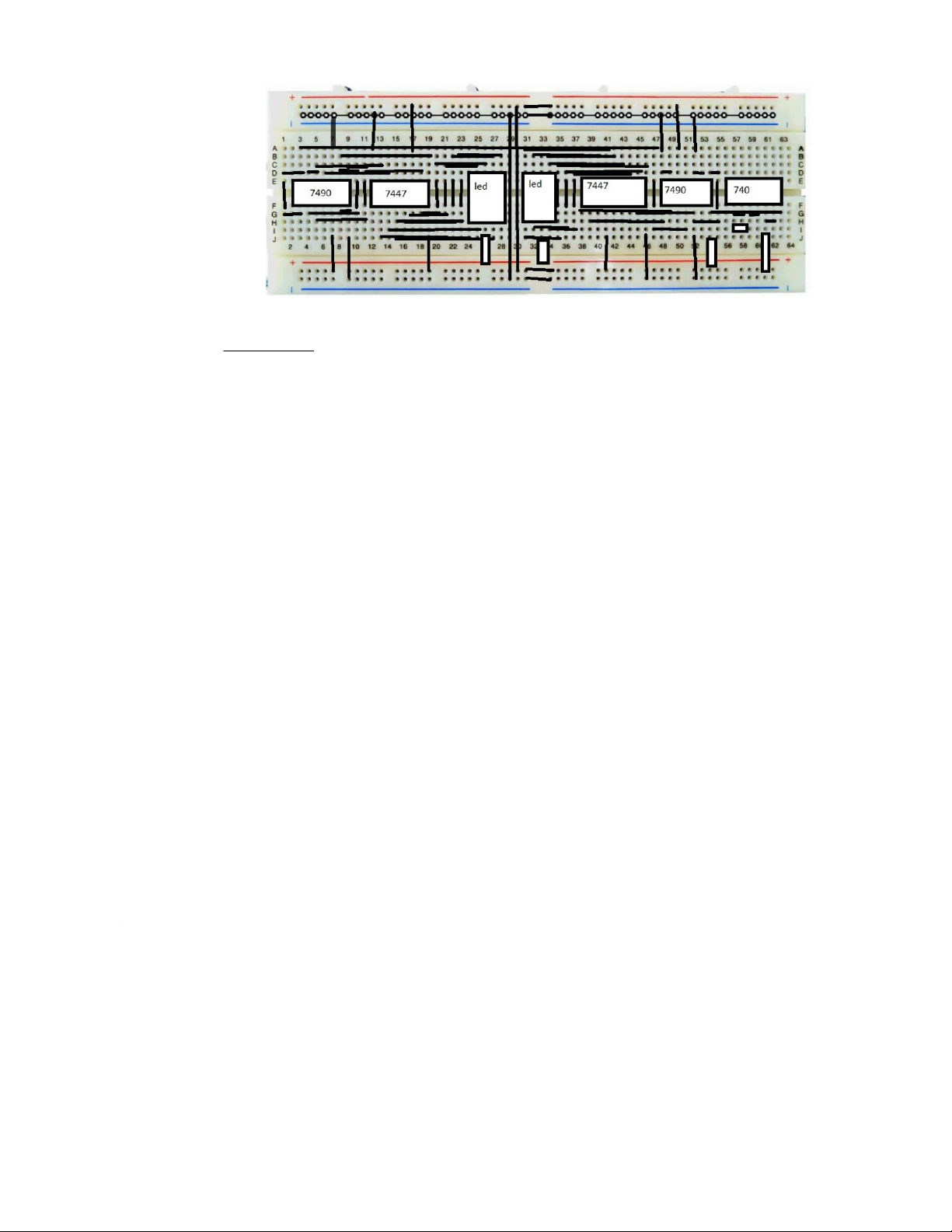

bộ đm 2 chữ số, c"c gi" trị đại diện cho c"c số thập lục phân từ A đn F không hợp lệ trong mã ny. 4 . a. Sơ đồ nguyên lí b.Sơ đồ lắp r"p 15 III,Nhận xét.

-Mạch có thit k hợp lí.

-Mạch hoạt động ổn định.

-Có tính ứng dụng thực t cao như lm đèn giao thông, đồng hồ,…. 16