Preview text:

14:17, 10/01/2026

Chương 3: Tập Lệnh AVR cho ATmega 324P - Hướng Dẫn và Ví Dụ - Studocu Chương 3 Tập lệnh AVR Tài liệu tham khảo:

1. Chương 3: Tập lệnh AVR (Giáo trình VXL) 2. AVR Instruction Set

3. Muhammad Ali Mazidi, AVR Microcontroller and Embedded Systems: Using Assembly and C,

Pearson New International Edition, 2014. 4. Datasheet ATmega324P 5. https://nicerland.com/avr/ 6. http://www.hocavr.com/

7. https://www.youtube.com/watch?v=Fr2K9pzec8g&list=PLgwJf8NK- 2e55CdbY_WnY6pejPHoojCkJ Nguyễn Lý Thiên Trường 1 14:17, 10/01/2026

Chương 3: Tập Lệnh AVR cho ATmega 324P - Hướng Dẫn và Ví Dụ - Studocu 3.1 Giới thiệu

3.2 Các phương pháp định vị địa chỉ 3.3 Các nhóm lệnh

Nguyễn Lý Thiên Trường 2 14:17, 10/01/2026

Chương 3: Tập Lệnh AVR cho ATmega 324P - Hướng Dẫn và Ví Dụ - Studocu 3.1 Giới thiệu

▪Các lệnh của vi điều khiển

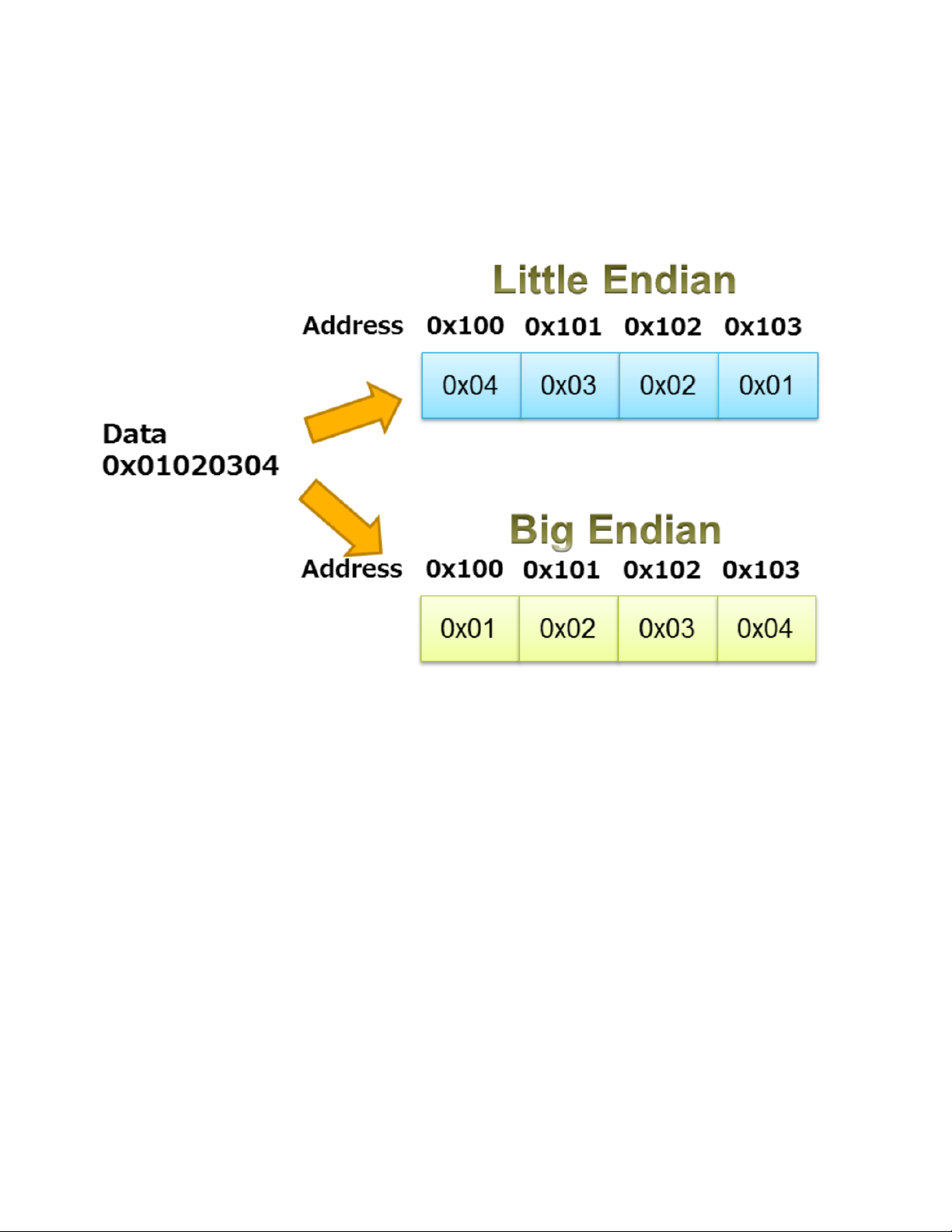

AVR được truy xuất theo từ (word).

▪Mỗi word (2 byte) mã máy được cất trong bộ nhớ chương

trình (Flash ROM) theo kiểu Little endian (tức là byte cao được lưu ở địa

chỉ cao, byte thấp được lưu ở địa chỉ thấp).

▪Đa số các lệnh có mã máy dài 2 byte, một số lệnh dài 4 byte.

▪Thời gian thực thi cho mỗi lệnh đa số là 1, 2 chu kỳ máy (MC)

và một số lệnh 3, 4 chu kỳ máy.

▪Với mỗi chip vi điều khiển khác nhau thuộc họ AVR sẽ có một

chút khác biệt có thể là về phần cứng cũ ng n hư t ập lệnh đi

kèm, do đó khi sử dụng một chip cụ thể nào chúng ta cần phải

tham khảo datasheet tương ứng. Nguyễn Lý Thiên Trường 3 14:17, 10/01/2026

Chương 3: Tập Lệnh AVR cho ATmega 324P - Hướng Dẫn và Ví Dụ - Studocu 3.1 Giới thiệu

▪Little endian và Big endian. Nguyễn Lý Thiên Trường 4 14:17, 10/01/2026

Chương 3: Tập Lệnh AVR cho ATmega 324P - Hướng Dẫn và Ví Dụ - Studocu

3.2 Các phương pháp định vị địa chỉ ▪Tổng c

ộng có 15 phương pháp định đ

ịa chỉ khác nhau. Có thể chia thành 8 nhóm như sau:

•Định địa chỉ thanh ghi đơn. •Định địa

chỉ thanh ghi (cả 2 toán hạng đều là thanh ghi).

•Định địa chỉ trực tiếp bộ nhớ SRAM. •Định địa

chỉ gián tiếp bộ nhớ SRAM (qua thanh ghi con trỏ). •Định địa chỉ trực tiếp bộ nhớ FLASH.

•Định địa chỉ gián tiếp bộ nhớ FLASH (qua thanh ghi con trỏ). •Định địa chỉ tương đối. •Định địa chỉ bit. Nguyễn Lý Thiên Trường 5 14:17, 10/01/2026

Chương 3: Tập Lệnh AVR cho ATmega 324P - Hướng Dẫn và Ví Dụ - Studocu

3.2 Các phương pháp định vị địa chỉ ▪Các

ký hiệu dùng trong phương pháp định địa chỉ và tập lệnh:

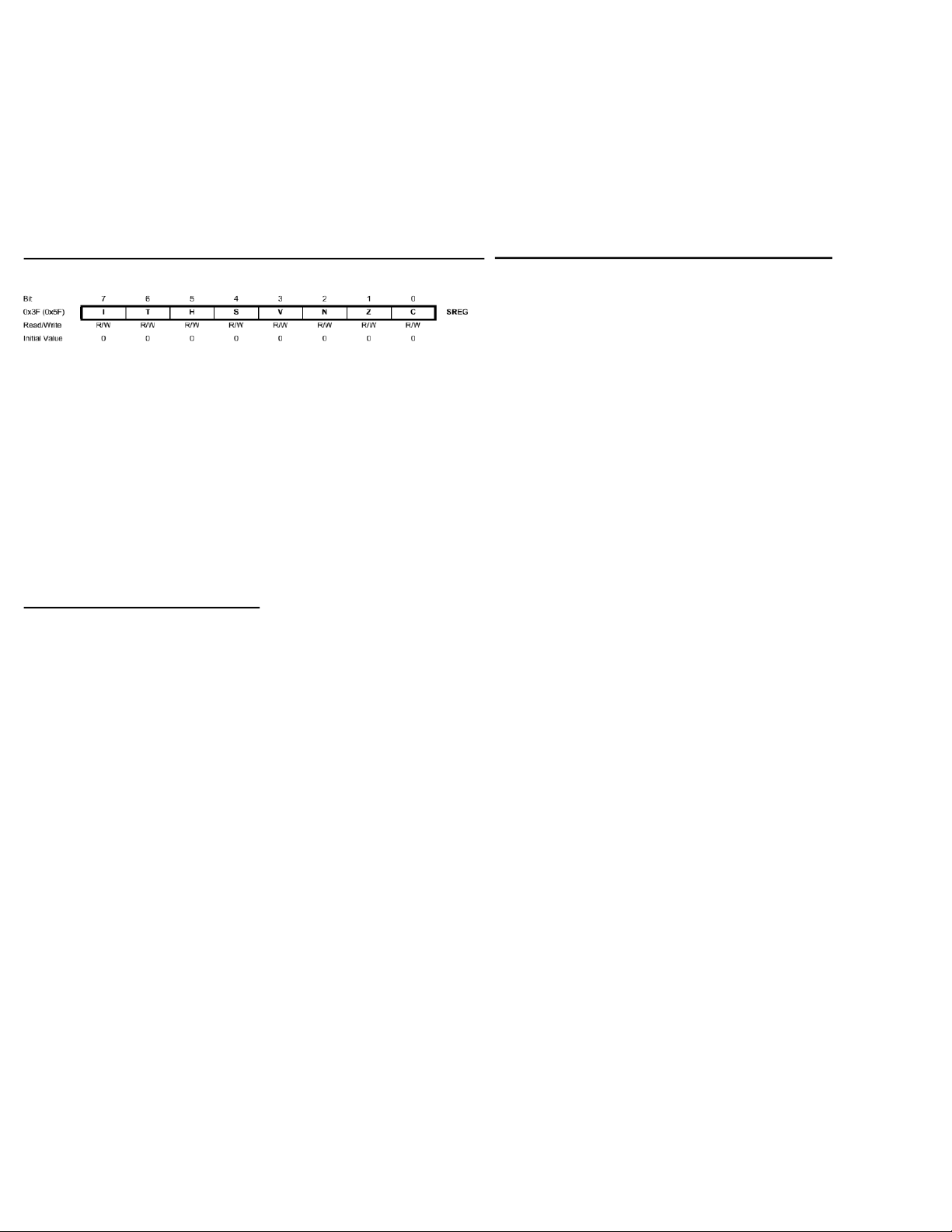

Thanh ghi trạng thái SREG và các bit trong thanh ghi Các thanh ghi và toán hạng trong lệnh SREG: thanh ghi trạng thái

Rd: thanh ghi đích/nguồn trong tập thanh ghi

Rr: thanh ghi nguồn trong tập thanh ghi

R: kết quả sau khi thực thi lệnh C: Cờ Carry Z: Cờ Zero K: hằng số dữ liệu N: Cờ âm k: hằng số địa chỉ V: Cờ tràn bù 2 S: Cờ dấu (S = N ⊕ V)

b: bit trong tập GPRs hoặc I/O REGs (3-bit) H: Cờ nhớ phân nửa s: Bit trong SREG (3-bit)

T: bit sao chép sử dụng trong các lệnh BLD và BST

I: Cờ cho phép/không cho phép ngắt toàn cục

X,Y,Z: Thanh ghi địa chỉ gián tiếp (con trỏ).

X=R27:R26, Y=R29:R28, Z=R31:R30

Hằng số và nội dung ô nhớ

A: hằng số dữ liệu A hay ô nhớ có địa chỉ là A

P: địa chỉ các I/O REGs cơ bản (I/O chuẩn).

(A): nội dung ô nhớ có địa chỉ là A

q: độ dời hoặc địa chỉ trực tiếp (6-bit) Nguyễn Lý Thiên Trường 6 14:17, 10/01/2026

Chương 3: Tập Lệnh AVR cho ATmega 324P - Hướng Dẫn và Ví Dụ - Studocu

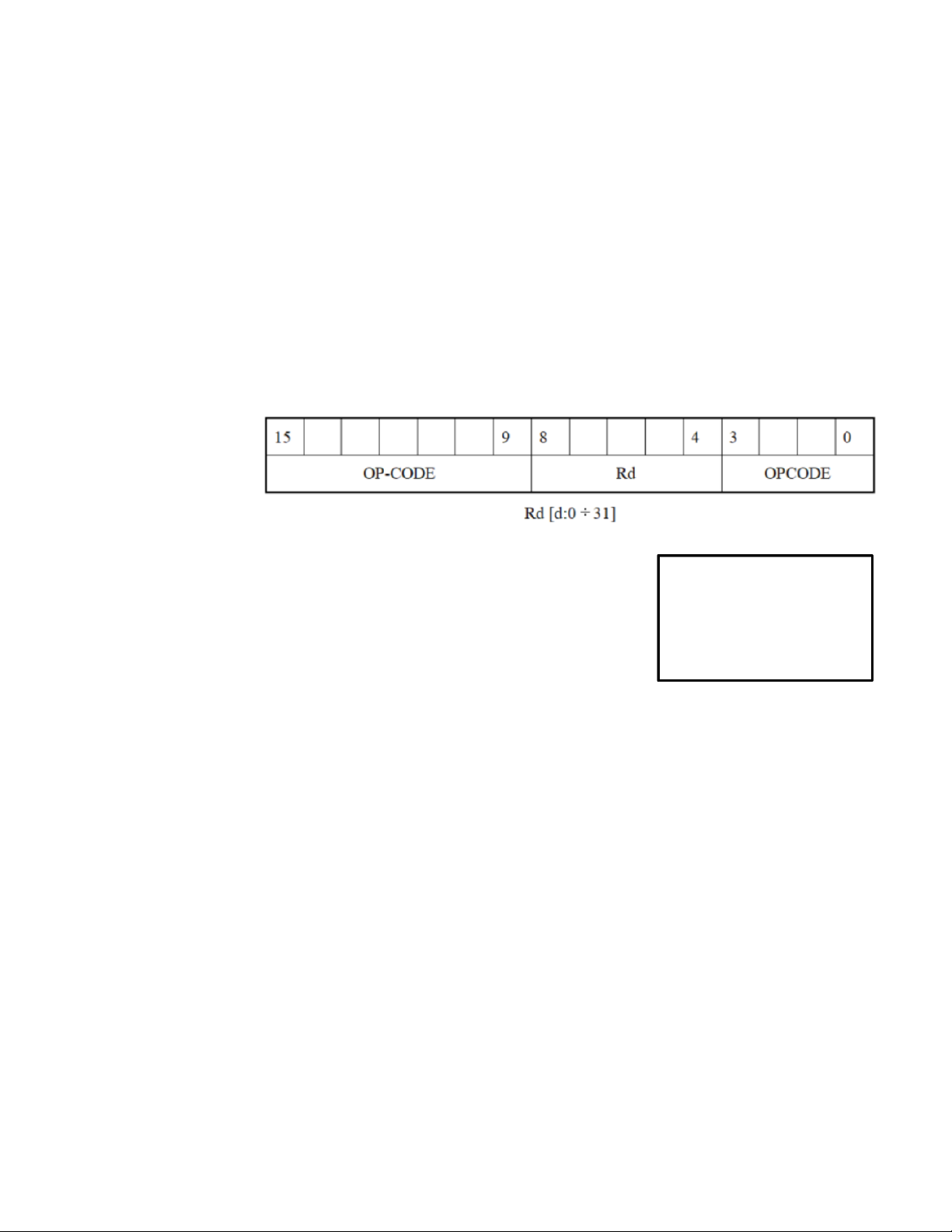

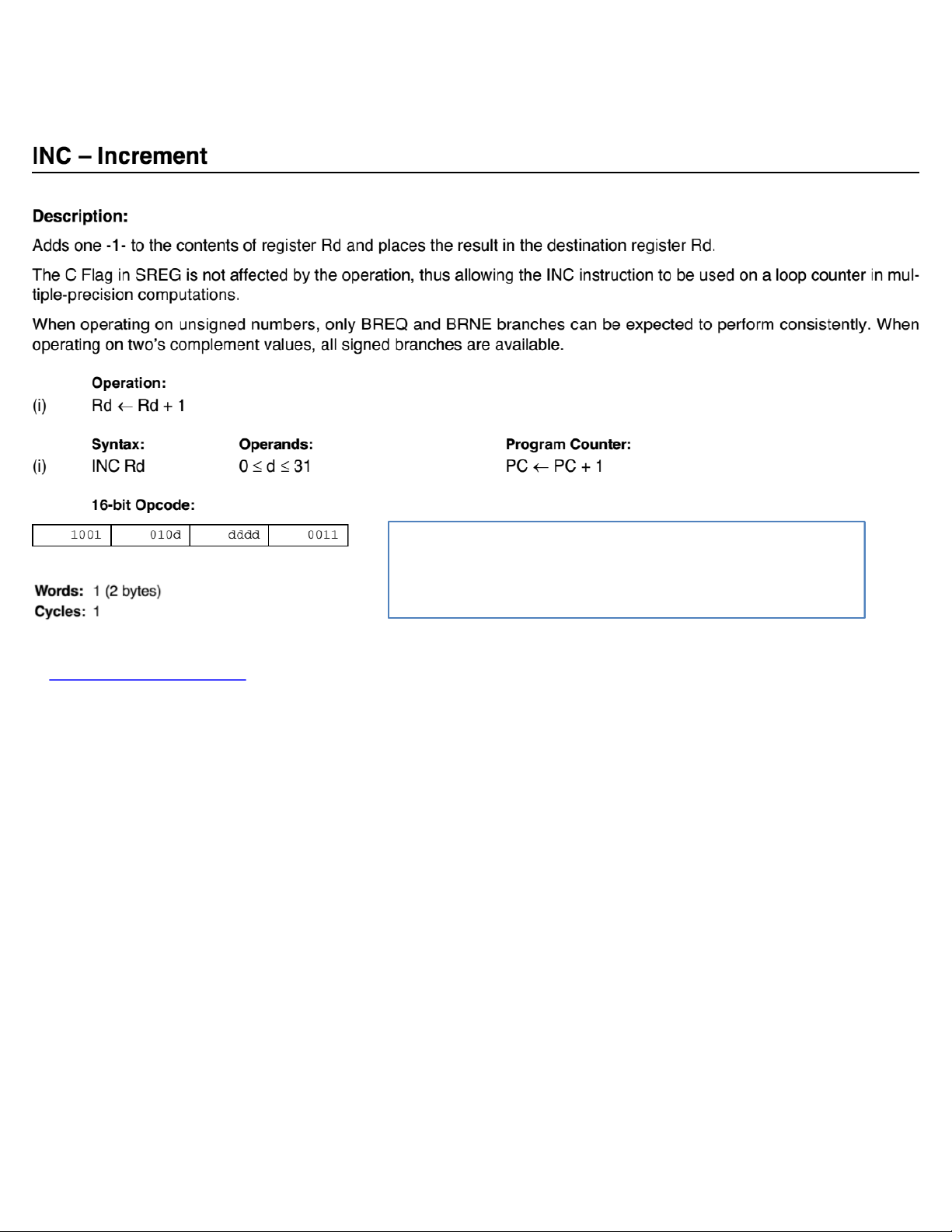

3.2.1 Định địa chỉ thanh ghi đơn

▪Phương pháp này gồm có 2 kiểu tùy theo các toán hạng được

sử dụng trong lệnh: toán hạng chỉ là một thanh ghi đơn, hay

1 thanh ghi với 1 giá trị tức thời K.

▪Đối với phương pháp có toán hạng chỉ là một thanh ghi đơn

sẽ dùng 11 bit cho opcode và 5 bit để mã hóa cho vị trí của Rd (0 d ).

31 Cấu trúc mã lệnh với toán hạng chỉ là 1 thanh ghi đơn: Ví dụ: INC

R2; tăng nội dung thanh ghi R2 lên 1 NEG

R16; tính bù 2 nội dung thanh ghi R16 Lưu ý: lệnh CLR Rd Mã máy: có cấu trúc mã máy INC R2;

0x9423 [0b1001 0100 0010 0011] như lệnh EOR Rd,Rd NEG R16;

0x9501 [0b1001 0101 0000 0001] (xem tập lệnh). Nguyễn Lý Thiên Trường 7 14:17, 10/01/2026

Chương 3: Tập Lệnh AVR cho ATmega 324P - Hướng Dẫn và Ví Dụ - Studocu Ví dụ: INC R2; tăng nội dung thanh ghi R2 lên 1

Mã máy: 0x9423 [0b1001 0100 0010 0011] ATmega Instruction Set Nguyễn Lý Thiên Trường 8 14:17, 10/01/2026

Chương 3: Tập Lệnh AVR cho ATmega 324P - Hướng Dẫn và Ví Dụ - Studocu ATmega Instruction Set Nguyễn Lý Thiên Trường 9 14:17, 10/01/2026

Chương 3: Tập Lệnh AVR cho ATmega 324P - Hướng Dẫn và Ví Dụ - Studocu

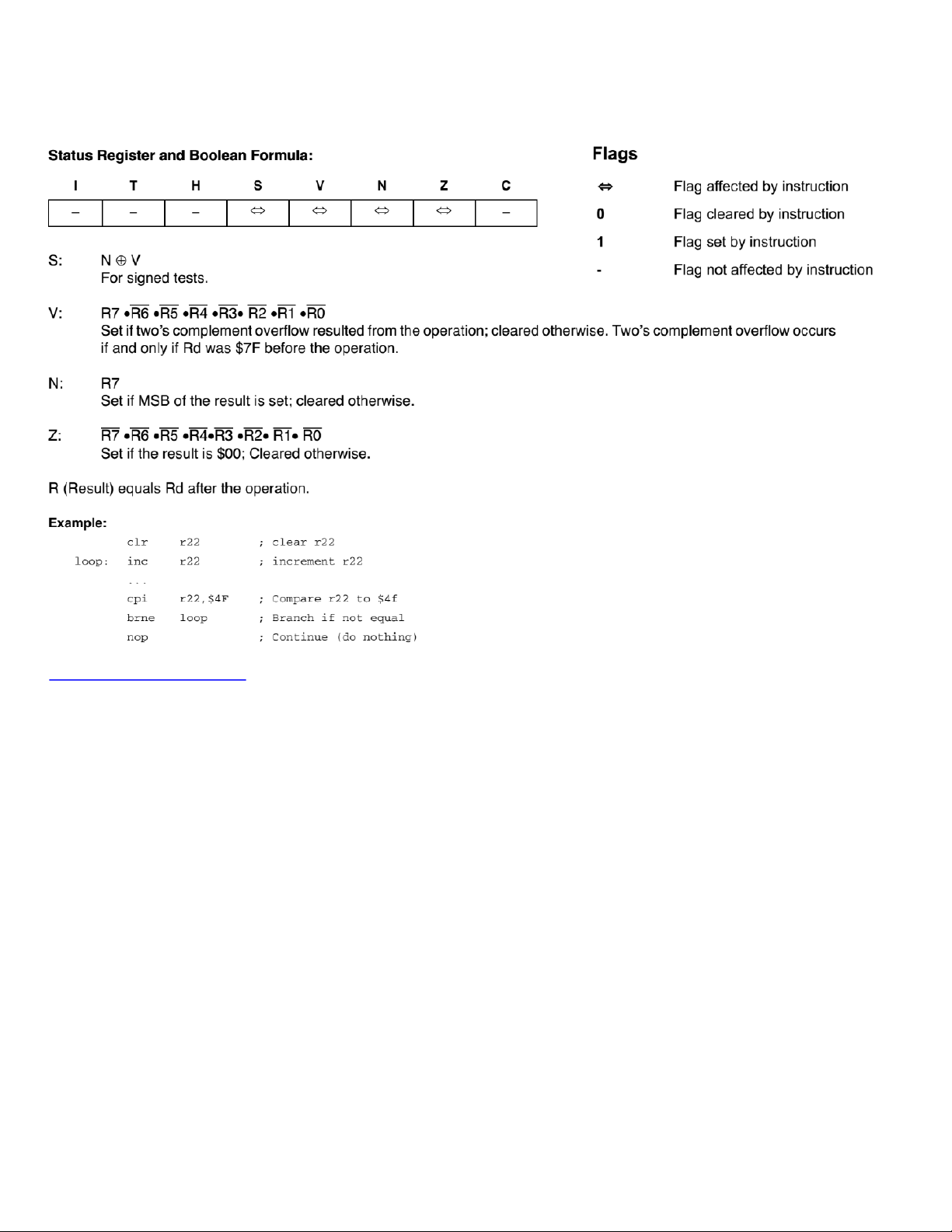

3.2.1 Định địa chỉ thanh ghi đơn

▪Phương pháp định địa chỉ thanh ghi đơn với một giá trị tức thời

(hằng số 8 bit) sử dụng 4 bit cho opcode, 4 bit cho Rd (16 d 31) và

8 bit cho dữ liệu K (Nhị phân, thập phân, thập lục phân, mã ASCII).

Cấu trúc mã lệnh với toán hạng là 1 thanh ghi với giá trị tức thời: 12 11

Ví dụ: I = Immediate: tức thời Nếu K là Lưu ý: chỉ được phép LDI R16,200; R16 = 200 số âm thì sử dụng với các thanh SUBI

R28,0x20; R28 R28 - 20H K ≥ −256

ghi từ R16÷R31 → được Mã máy: mã hóa bằ ng 4 bit nhị LDI

R16,200; 0xEC08 [0b1110 1100 0000 1000] phân có giá trị tương SUBI

R28,0x20; 0x52C0 [0b0101 0010 1100 0000] ứng từ 0÷15. Nguyễn Lý Thiên Trường 10 14:17, 10/01/2026

Chương 3: Tập Lệnh AVR cho ATmega 324P - Hướng Dẫn và Ví Dụ - Studocu

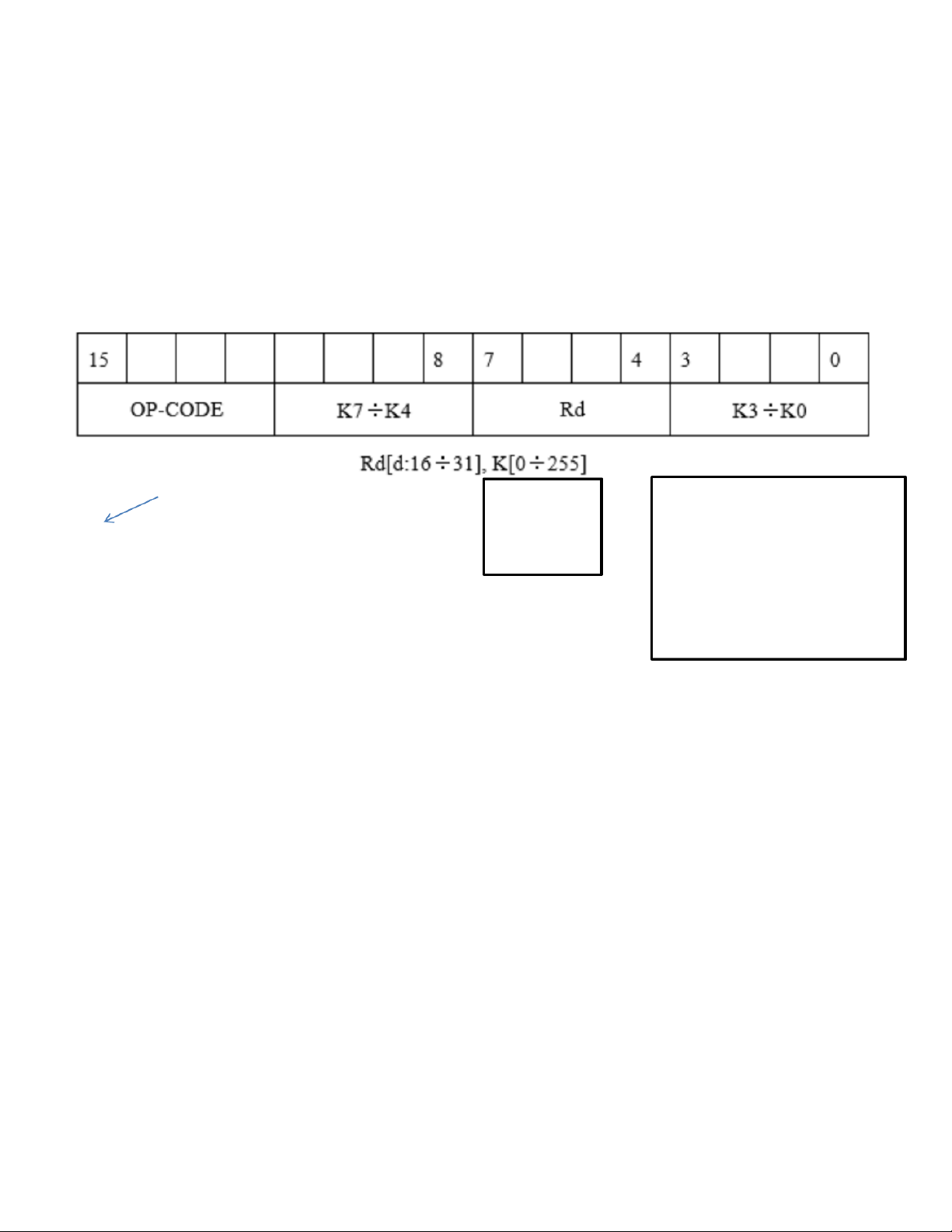

3.2.2 Định địa chỉ thanh ghi (cả 2 toán hạng)

▪Phương pháp định địa chỉ thanh ghi sử dụng trong câu lệnh có 2 toán hạng là

các thanh ghi Rd và Rr (GPRs).

▪Thực hiện các thao tác lệnh trên các dữ liệu được đặt trong 2 thanh ghi Rd và

Rr, quy ước Rr là toán hạng nguồn, Rd là toán hạng đích, kết quả cất vào Rd.

Cấu trúc mã lệnh với cả 2 toán hạng đều là thanh ghi: Ví dụ: MOV R2,R3; R2 R3 ADD R1,R16; R1 R1 + R16 Mã máy: MOV

R2,R3; 0x2C23 [0b0010 1100 0010 0011] ADD

R1,R16; 0x0E10 [0b0000 1110 0001 0000] Nguyễn Lý Thiên Trường 11 14:17, 10/01/2026

Chương 3: Tập Lệnh AVR cho ATmega 324P - Hướng Dẫn và Ví Dụ - Studocu

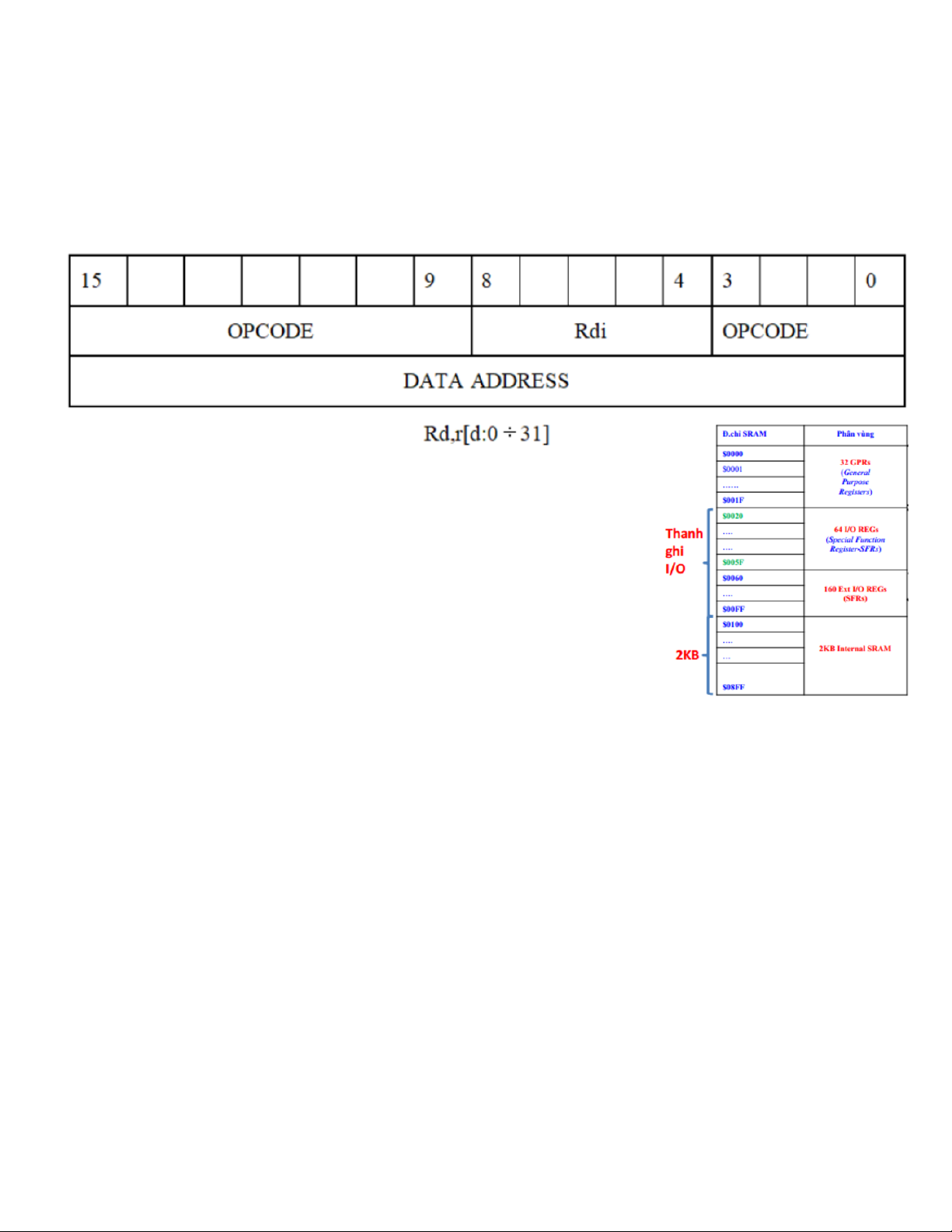

3.2.3 Định địa chỉ trực tiếp bộ nhớ SRAM

▪Dùng để truy xuất trực tiếp đến các thanh ghi I/O và vùng SRAM (Data memory).

▪Ký hiệu P (0 ≤ P ≤ 63) trong tập lệnh thực hiện trên các toán hạng là các thanh ghi I/O cơ bản,

k (0 ≤ k ≤ 8FFH) là địa chỉ các ô nhớ SRAM (toàn bộ bộ nhớ SRAM).

▪Nếu 60H ≤ k ≤ FFH (thuộc vùng I/O mở rộng): có thể thay bằng tên thanh ghi I/O tương ứng

thay vì dùng địa chỉ bộ nhớ (SRAM).

▪Sử dụng các lệnh IN và OUT để truy cập vùng I/O cơ bản (hay vùng I/O chuẩn). Thông thường là

sử dụng tên thanh ghi I/O thay vì địa chỉ I/O.

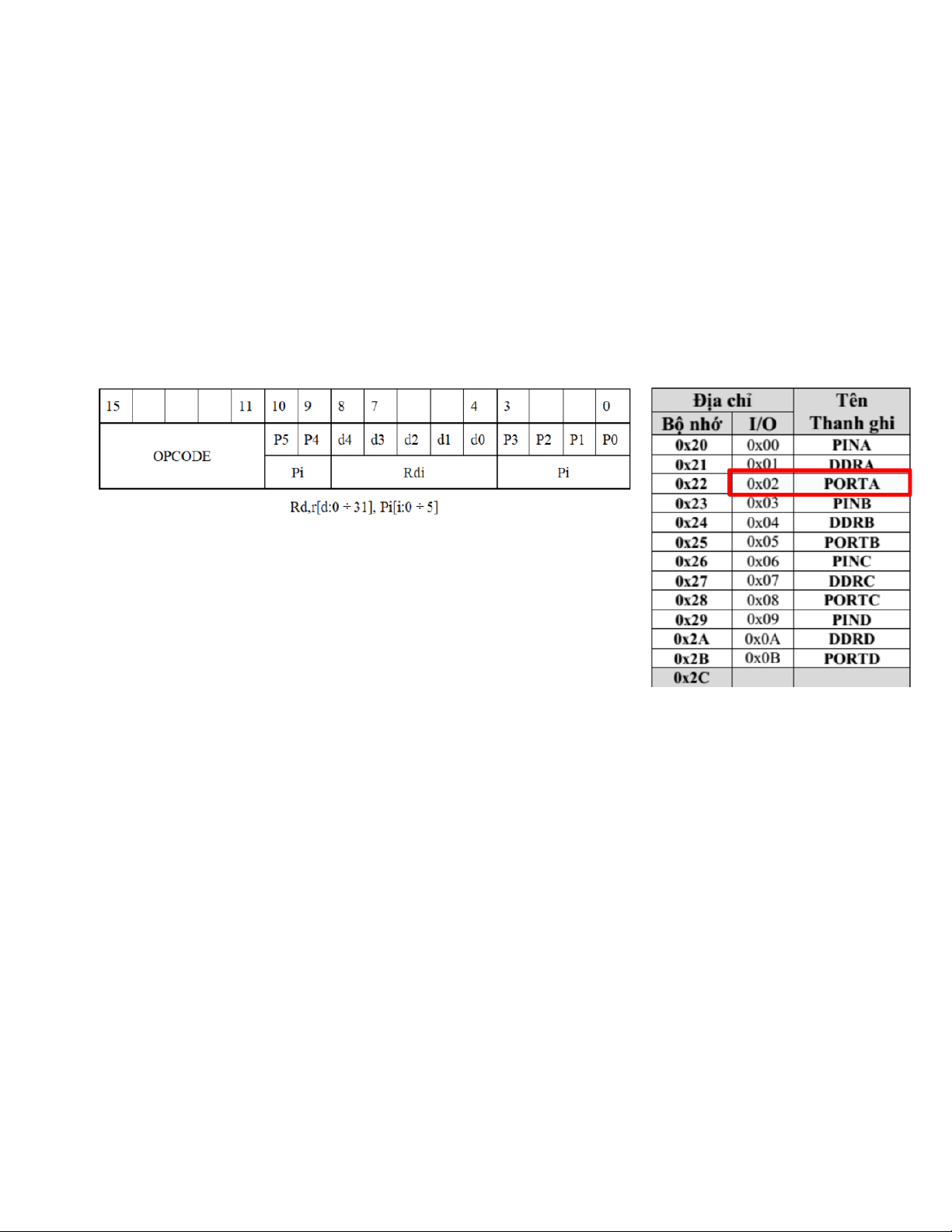

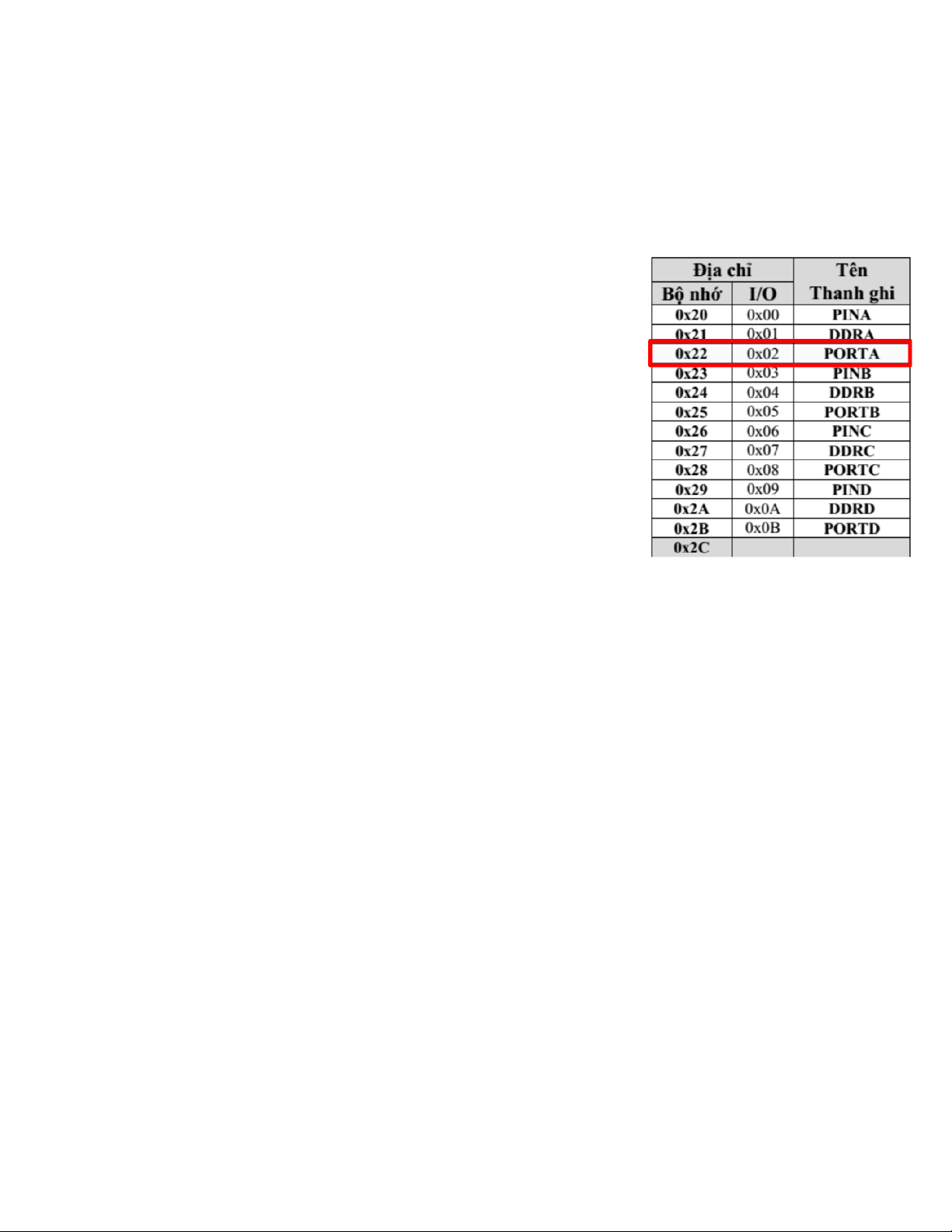

Cấu trúc mã lệnh định địa chỉ trực tiếp vùng thanh ghi I/O cơ bản: Ví dụ: OUT PORTA,R1; PORTA R1 OUT $02,R1; (02H) R1 ⇔ PORTA R1 Mã máy: OUT

PORTA,R1; 0xB812 [1011 1000 0001 0010] OUT

$02,R1; 0xB812 [1011 1000 0001 0010] Nguyễn Lý Thiên Trường 12 14:17, 10/01/2026

Chương 3: Tập Lệnh AVR cho ATmega 324P - Hướng Dẫn và Ví Dụ - Studocu

3.2.3 Định địa chỉ trực tiếp bộ nhớ SRAM

▪Sử dụng các lệnh IN và OUT để truy cập vùng I/O cơ bản (hay vùng I/O chuẩn).

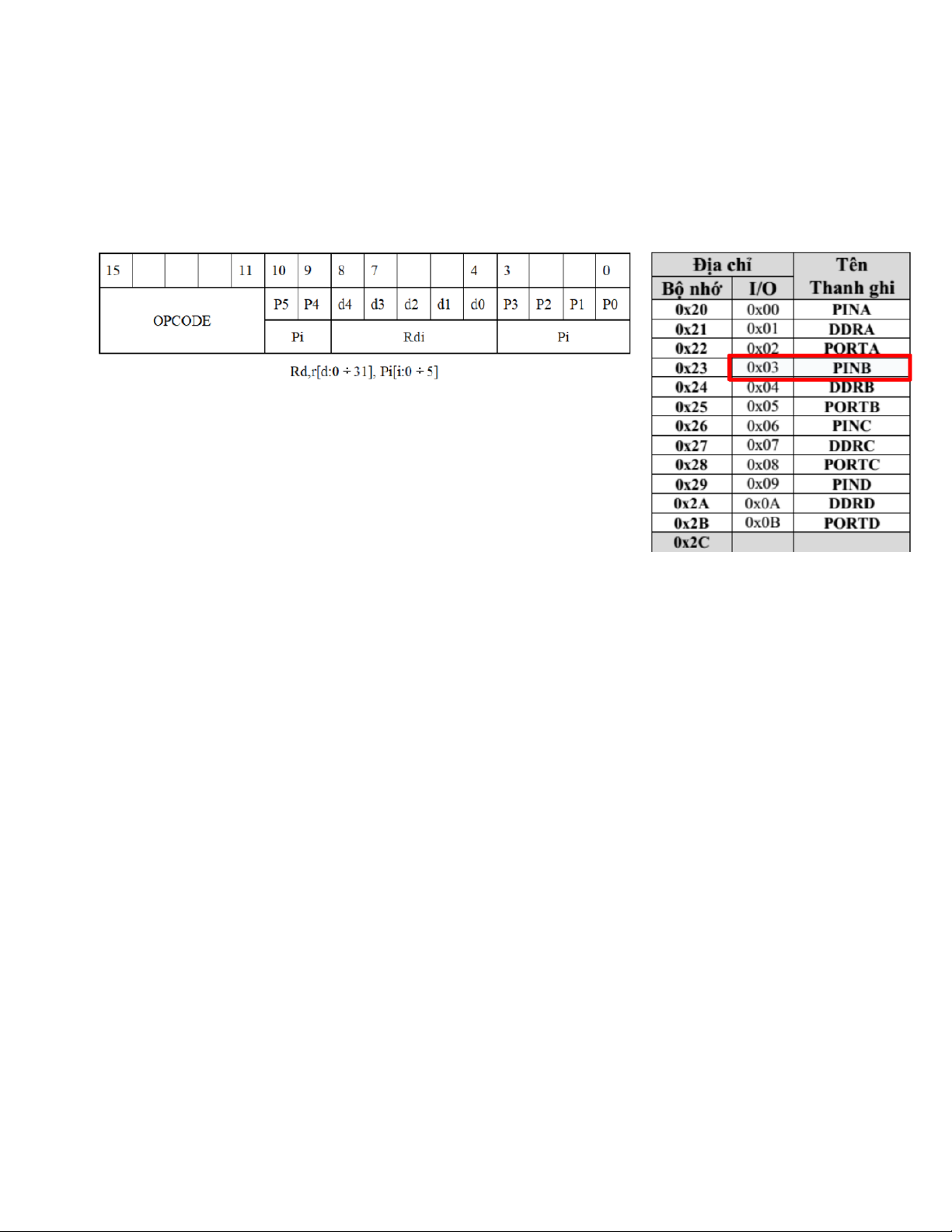

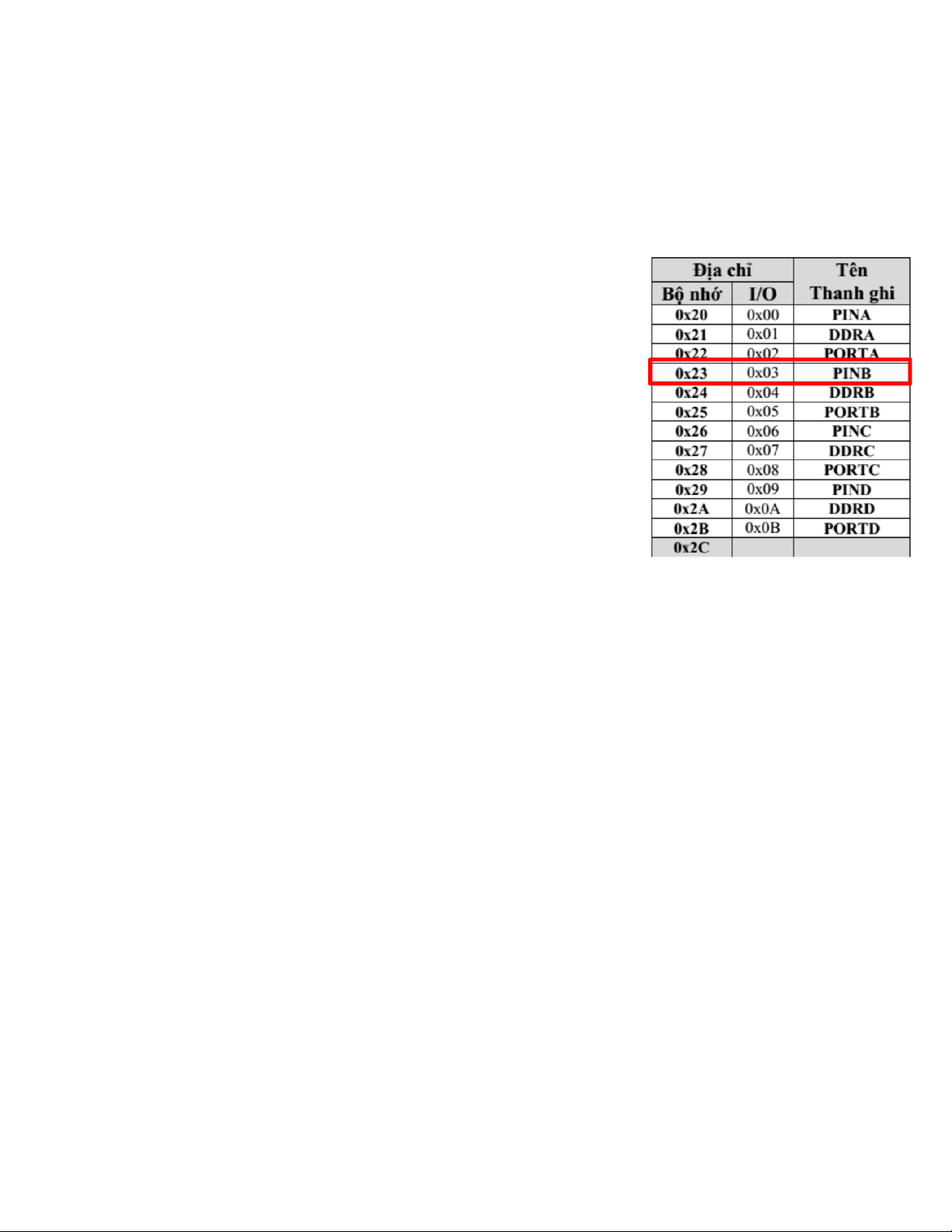

Cấu trúc mã lệnh định địa chỉ trực tiếp vùng thanh ghi I/O cơ bản: Ví dụ: IN R3,PINB; R3 PINB IN R3,$03; R3 (03H) ⇔ R3 PINB Mã máy: IN

R3,PINB; 0xB033 [1011 0000 0011 0011] IN

R3,$03; 0xB033 [1011 0000 0011 0011] Nguyễn Lý Thiên Trường 13 14:17, 10/01/2026

Chương 3: Tập Lệnh AVR cho ATmega 324P - Hướng Dẫn và Ví Dụ - Studocu

3.2.3 Định địa chỉ trực tiếp bộ nhớ SRAM

▪Mỗi thanh ghi I/O cơ bản trong không gian bộ nhớ dữ liệu sẽ có 2 địa chỉ tương ứng

đó là địa chỉ I/O và địa chỉ bộ nhớ (hay địa chỉ mem, địa chỉ dữ liệu).

▪Khi làm việc với các I/O cơ bản ta có thể dùng một trong 2 phương pháp định địa chỉ khác nhau để thực hiện lệnh

(OUT/STS, IN/LDS). Mỗi phương pháp cho kích thước mã

lệnh và thời gian thực thi lệnh khác nhau. Ví dụ: OUT PORTA,R1; PORTA R1 STS $22,R1; (22H) R1 Mã máy: OUT PORTA,R1; 0xB812 (2 byte), 1MC STS $22,R1; 0x9210, 0x0022 (4 byte) ; Thời gian thực thi: 2MC Nguyễn Lý Thiên Trường 14 14:17, 10/01/2026

Chương 3: Tập Lệnh AVR cho ATmega 324P - Hướng Dẫn và Ví Dụ - Studocu

3.2.3 Định địa chỉ trực tiếp bộ nhớ SRAM

▪Mỗi thanh ghi I/O cơ bản trong không gian bộ nhớ dữ liệu sẽ có 2 địa chỉ tương ứng

đó là địa chỉ I/O và địa chỉ dữ liệu (hay địa chỉ bộ nhớ, địa chỉ mem).

▪Khi làm việc với các I/O cơ bản ta có thể dùng một trong 2 phương pháp định địa chỉ khác nhau để thực hiện lệnh

(OUT/STS, IN/LDS). Mỗi phương pháp cho kích thước mã

lệnh và thời gian thực thi lệnh khác nhau. Ví dụ: IN R3,PINB; R3 PINB LDS R3,$23; R3 (23H) Mã máy: IN R3,PINB; 0xB033 (2 byte), 1MC LDS

R3,$23; 0x9030, 0x0023 (4 byte), 2MC Nguyễn Lý Thiên Trường 15 14:17, 10/01/2026

Chương 3: Tập Lệnh AVR cho ATmega 324P - Hướng Dẫn và Ví Dụ - Studocu

3.2.3 Định địa chỉ trực tiếp bộ nhớ SRAM

▪Sử dụng các lệnh STS và LDS để truy cập vùng I/O mở rộng và vùng Data SRAM (2KB).

Cấu trúc mã lệnh định địa chỉ trực tiếp vùng thanh ghi I/O mở rộng và SRAM: Ví dụ: LDS R0,UDR0; R0 UDR0 STS $100,R0; (100H) R0 Mã máy: LDS R0,UDR0; 0x9000, 0x00C6 STS $100,R0; 0x9200, 0x0100

➢Lưu ý: các lệnh STS và LDS dùng để truy cập trực tiếp

đến tất cả nội dung SRAM từ 000H đến 8FFH. Nguyễn Lý Thiên Trường 16 14:17, 10/01/2026

Chương 3: Tập Lệnh AVR cho ATmega 324P - Hướng Dẫn và Ví Dụ - Studocu

3.2.4 Định địa chỉ gián tiếp bộ nhớ SRAM

▪Phương pháp định địa chỉ gián tiếp qua thanh ghi thực hiện trên các lệnh dùng để truy

xuất dữ liệu vùng SRAM sử dụng các thanh ghi con trỏ X, Y hoặc Z.

▪Các thanh ghi X, Y, Z hoạt động như các con trỏ (pointer) và nội dung của các thanh ghi

này là địa chỉ của các ô nhớ trong vùng SRAM, nơi mà dữ liệu sẽ được đọc hoặc là ghi.

▪Phương pháp này được chia ra làm 4 kiểu khác nhau: dữ liệu gián tiếp, dữ liệu gián tiếp với tiền tố tr ừ (-), dữ li ệu giá ti n ếp với hậu

tố cộng (+) và dữ liệu giá t n iếp với một

độ chuyển dời q (6 bit, 0 ≤ q ≤ 63) thông qua các lệnh LD, LDD, ST, STD.

Ví dụ: Để thực hiện việc ghi giá trị 0xCC vào địa chỉ SRAM 0x 800 cùng với việc chọn

thanh ghi Y làm con trỏ trong phương pháp định địa chỉ này, ta thực hiện các lệnh sau: Bộ nhớ SRAM Gián tiếp: LDI

R16,0xCC ;lưu dữ liệu cần ghi vào R16 0x7FF LDI

R28,0x00 ;lưu địa chỉ ô nhớ vào Y 0x800 0xCC LDI R29,0X08 ;Y YH:YL R29:R28 ST Y, R16;ghi dữ liệu 0x801 Trực tiếp ? LDI R16,0xCC ;R16 = CCH STS 0x800, R16; (0x800) R16 Nguyễn Lý Thiên Trường 17 14:17, 10/01/2026

Chương 3: Tập Lệnh AVR cho ATmega 324P - Hướng Dẫn và Ví Dụ - Studocu

3.2.4 Định địa chỉ gián tiếp bộ nhớ SRAM

Ví dụ: Đọc nội dung SRAM ở ô nhớ có địa chỉ 0x cùng 800

với việc chọn thanh ghi X làm

con trỏ. Kết quả lưu vào thanh ghi R7. Bộ nhớ SRAM Gián tiếp: LDI

R27,0x08 ;lưu byte cao địa chỉ ô nhớ vào X 0x7FF LDI

R26,0x00 ; lưu byte thấp địa chỉ ô nhớ vào X 0x800 0xCC LD R7, X; đọc dữ liệu 0x801

➢Lưu ý: Thanh ghi X ≡ XH:XL ≡ R27:R26 LDI

XH,0x08 ;lưu byte cao địa chỉ ô nhớ vào X LDI

XL,0x00 ;lưu byte thấp địa chỉ ô nhớ vào X LD R7, X; đọc dữ liệu Trực tiếp? LDS R7,0x800; R7 (0x800) Nguyễn Lý Thiên Trường 18 14:17, 10/01/2026

Chương 3: Tập Lệnh AVR cho ATmega 324P - Hướng Dẫn và Ví Dụ - Studocu

3.2.4 Định địa chỉ gián tiếp bộ nhớ SRAM

▪Phương pháp định địa chỉ gián tiếp với tiền tố trừ (-) thực hiện trong câu lệnh có

các toán hạng là các thanh ghi con trỏ với ký hiệu dấu trừ phía trước X, Y, Z (-X, -Y, -Z).

▪Địa chỉ của các toán hạng được xác định bằng cách lấy nội dung của các con trỏ trừ

đi 1 trước khi thực hiện lệnh, và kết quả này sẽ giữ

nguyên trong con trỏ sau khi thực hiện xong lệnh.

▪Lưu ý: hậu tố trừ sau X, Y, Z (X-, Y-, Z-) : sai cú pháp.

Ví dụ: Đọc nội dung SRAM ở ô nhớ có địa chỉ 0x800 cùng với việc chọn thanh ghi Z làm

con trỏ kết hợp với tiền tố trừ Kết . quả lưu vào thanh ghi R7. Bộ nhớ SRAM Gián tiếp: LDI

R31,0x08 ;lưu byte cao địa chỉ ô nhớ vào Z 0x7FF LDI R30, ;

0x01 lưu byte thấp địa chỉ ô nhớ vào Z 0x800 0xCC LD R7, -Z ;Z Z - 1, đọc dữ liệu 0x801

➢Lưu ý: Thanh ghi Z ≡ ZH:ZL ≡ R31:R30 LDI

ZH,0x08 ;lưu byte cao địa chỉ ô nhớ vào Z LDI

ZL,0x01 ;lưu byte thấp địa chỉ ô nhớ vào Z LD R7, -Z ;Z Z - 1, đọc dữ liệu Nguyễn Lý Thiên Trường 19 14:17, 10/01/2026

Chương 3: Tập Lệnh AVR cho ATmega 324P - Hướng Dẫn và Ví Dụ - Studocu

3.2.4 Định địa chỉ gián tiếp bộ nhớ SRAM

▪Phương pháp định địa chỉ gián tiếp với hậu tố cộ ng (+) thực hiện trong câu lệnh có

các toán hạng là các thanh ghi con trỏ với ký hiệu dấu cộng phía sau X, Y, Z (X+, Y+, Z+).

▪Phương pháp này thực hiện xong lệnh rồi tăng nội dung con trỏ lên 1. Kết quả này

sẽ giữ nguyên trong con trỏ sau khi thực hiện xong lệnh.

▪Lưu ý: tiền tố cộng trước X, Y, Z (+X, +Y, +Z): sai cú pháp.

Ví dụ: Đọc nội dung SRAM ở ô nhớ có địa chỉ 0x800 và 0x801 cùng với việc chọn thanh ghi Z làm con trỏ k ết hợp v ới hậu tố cộng . Kết quả lưu

vào thanh ghi R7 và R8 tương ứng. Bộ nhớ SRAM Gián tiếp: 0x7FF 0x2A LDI

ZH,0x08 ;lưu byte cao địa chỉ ô nhớ vào Z LDI

ZL,0x00 ;lưu byte thấp địa chỉ ô nhớ vào Z 0x800 0xCC LD R7, Z+ ;đọc dữ liệu, Z Z + 1 0x801 0x12 LD R8, Z Nguyễn Lý Thiên Trường 20